Received 7 October 2024, accepted 26 November 2024, date of publication 29 November 2024, date of current version 10 December 2024.

Digital Object Identifier 10.1109/ACCESS.2024.3509372

# **SURVEY**

# **Transformers: A Security Perspective**

BANAFSHEH SABER LATIBARI<sup>®1</sup>, NAJMEH NAZARI<sup>®1</sup>, MUHTASIM ALAM CHOWDHURY<sup>®2</sup>, KEVIN IMMANUEL GUBBI<sup>®1</sup>, (Student Member, IEEE), CHONGZHOU FANG<sup>1</sup>, SUJAN GHIMIRE<sup>3</sup>, ELAHE HOSSEINI<sup>®1</sup>, HOSSEIN SAYADI<sup>®4</sup>, (Member, IEEE), HOUMAN HOMAYOUN<sup>®1</sup>, SOHEIL SALEHI<sup>®2</sup>, (Member, IEEE), AND AVESTA SASAN<sup>®1</sup>, (Senior Member, IEEE)

<sup>1</sup>Department of Electrical and Computer Engineering, University of California at Davis, Davis, CA 95616, USA

<sup>2</sup>Department of Electrical and Computer Engineering, The University of Arizona, Tucson, AZ 85721, USA <sup>3</sup>Department of System and Industrial Engineering, The University of Arizona, Tucson, AZ 85721, USA

<sup>4</sup>California State University at Long Beach, Long Beach, CA 90840, USA

Cantonna State University at Long Beach, Long Beach, CA 90840, USA

Corresponding author: Banafsheh Saber Latibari (bsaberlatibari@ucdavis.edu)

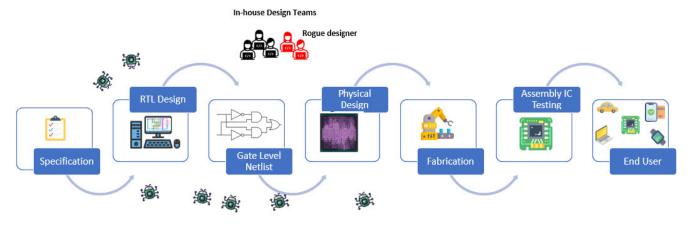

**ABSTRACT** The Transformers architecture has recently emerged as a revolutionary paradigm in the field of deep learning, particularly excelling in Natural Language Processing (NLP) and Computer Vision (CV) applications. Despite its success, the security implications of Transformers have not been comprehensively explored, encompassing a broad spectrum of both hardware and software vulnerabilities. This paper aims to address this critical gap by conducting an extensive exploration of security challenges confronting Transformers from both software and hardware perspectives. While software-related concerns like adversarial attacks, private inference, and watermarking have been studied, the paper sheds light on previously underexplored hardware threats, the study aims to contribute to a comprehensive understanding of Transformer security. It presents an in-depth analysis of recent advancements in the security of Transformers. Additionally, it outlines existing challenges and forecasts future research trends, offering insights for researchers and practitioners aiming for the secure and resilient design and deployment of Transformers. The survey categorizes different attacks and defenses related to Transformers, helping researchers identify gaps and opportunities in this area. Furthermore, it defines a roadmap for a unified security framework, serving as a foundational starting point for developers seeking to implement robust security measures.

**INDEX TERMS** Deep learning security, hardware security, NLP, transformers, vision.

#### I. INTRODUCTION

The Transformers have revolutionized various fields of artificial intelligence, offering powerful solutions in Natural Language Processing (NLP), computer vision, audio and signal processing, and multi-modal tasks. In NLP, Transformers have become essential for state-of-the-art models, enabling tasks like text classification, question answering, language modeling, understanding, and generation. Their attention mechanisms capture long-range dependencies effectively [28], [170]. In computer vision, Transformers excel in tasks such as image classification, object detection, and image captioning. Treating images as sequences of

The associate editor coordinating the review of this manuscript and approving it for publication was Peter Langendoerfer.

tokens, Transformers efficiently process visual information while preserving spatial relationships [32], [144], [167].

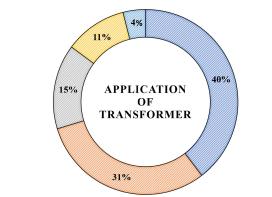

In audio and signal processing, Transformers have been used for tasks like speech recognition, music generation, and sound classification. Transformer-based models excel in deciphering timing relationships within audio data, adeptly capturing complex patterns and structures [11], [172]. Additionally, Transformers are useful in multi-modal learning, where they can handle different types of data such as text, images, and audio all at once [185], [213]. Figure 1 illustrates the demographic distribution of Transformer applications across various fields.

Nevertheless, similar to their predecessors such as Convolutional Neural Networks (CNNs), Transformers are not immune to vulnerabilities and potential security threats.

■ NLP ■ Computer Vision ■ Multi-Model ■ Audio-Speech ■ Signal

**FIGURE 1.** Transformer applications across key domains, including NLP, Computer Vision, Multi-Modal tasks, Audio and Speech, and Signal Processing. This visualization provides an overview of the versatile utilization of Transformers in various fields, emphasizing their impact on diverse domains.

Previous research has primarily focused on analyzing Transformers from a software security standpoint, often overlooking a comprehensive exploration of hardware security aspects. Software-level security analysis studies have focused on various topics, including adversarial attacks [90], [107], [126], federated learning and private inference [136], intellectual property concerns and watermarking [61], [127], as well as differential privacy [205].

In contrast to the extensive examination of software-level vulnerabilities in recent years, the susceptibility of Transformers to hardware security threats [128], [129] has received limited attention [4], [125]. This study represents a pioneering effort to provide a comprehensive analysis of Transformers from both software and hardware security perspectives, aiming to shed light on previously unattended areas and bridge the gap between software and hardware security considerations in Transformer models. This paper seeks to address this gap by offering a detailed exploration of the security challenges confronting Transformers. Through a comprehensive review of existing research in the field, it examines both hardware and software perspectives to provide a comprehensive understanding of the security landscape of Transformer-based models. By unraveling the intricacies of potential threats at both intersection of hardware and software, this study aims to contribute to a holistic understanding of Transformer security, paving the way for robust defenses in the face of evolving threats.

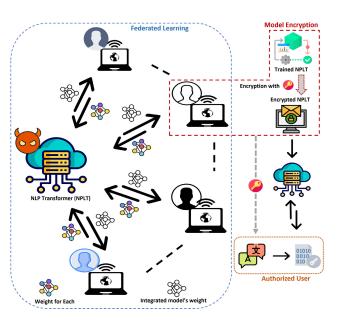

# A. COMPREHENSIVE ANALYSIS OF SOFTWARE VULNERABILITIES

Our work contributes to the field by providing a comprehensive analysis of various software-level security threats affecting Transformer-based models. While previous research predominantly focused on adversarial attacks, our study delves into a broader spectrum of security concerns. By examining various aspects such as federated learning, private inference, intellectual property concerns, watermarking, and differential privacy, we offer a thorough understanding of the security landscape surrounding the Transformer-based models. Through this comprehensive analysis, we aim to provide valuable insights that facilitate the development of more secure and resilient AI-based systems for real-world applications.

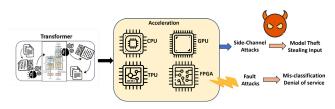

#### **B. UNRAVELING HARDWARE VULNERABILITIES**

Hardware vulnerabilities [52], [93] present unique challenges, ranging from trojans injected [50], [168], [169] during manufacturing to side-channel attacks exploiting subtle information leaks. Understanding and investigating these hardware intricacies is crucial not only for identifying vulnerabilities but also for designing effective countermeasures that fortify Transformers against malicious exploits. Within this survey paper, we delve into various emerging hardware vulnerabilities in Transformers which enhances the research community's capacity to fortify Transformers against potential malicious exploits, thereby ensuring their resilience and security across emerging applications.

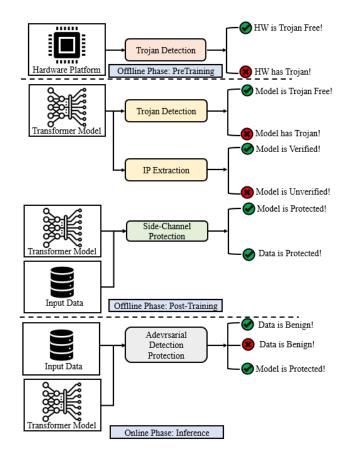

#### C. TOWARDS A UNIFIED SECURITY FRAMEWORK

Efforts to secure Transformers must transcend the conventional silos of hardware and software security. A unified framework that integrates insights from both realms is imperative. This paper advocates for a holistic approach that acknowledges the symbiotic relationship between hardware and software vulnerabilities. By fostering a comprehensive understanding of security challenges and solutions, we aim to propel the development of robust and adaptive defense mechanisms for Transformers, ensuring their continued success in an increasingly complex threat landscape. Additionally, this survey outlines existing challenges and forecasts future research trends, providing valuable insights for researchers and practitioners dedicated to the secure and resilient design and deployment of Transformers.

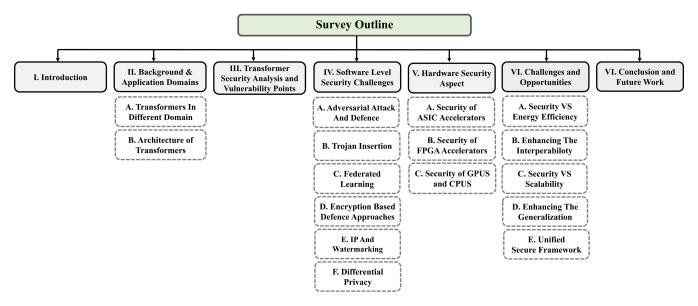

Figure 2 shows the overview of our work. The organization of this paper is as follows: Section II describes the application of Transformers and the architecture of the models. Section III covers vulnerability points in the architecture of Transformers. Section IV presents the detailed review of software-level security aspects of Transformers including adversarial attack and defense, trojan insertion, federated learning, input encryption, watermarking, and differential privacy. Section V provides a comprehensive review of the hardware security aspects of Transformers in both ASIC and FPGA accelerators. In section VI, potential research challenges and future opportunities of this emerging field of study are discussed. Finally, section VII concludes the survey.

### **II. BACKGROUND AND APPLICATION DOMAINS**

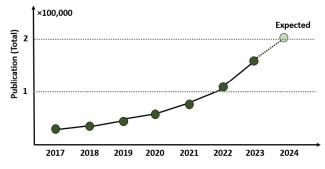

This section provides an overview of the essential background knowledge and architecture of the Transformers published extensively from 2017, as shown in Figure 3. It further explores diverse application domains where the Transformers find practical utility.

FIGURE 2. Overview of the "Transformers: A Security Perspective" paper.

#### A. TRANSFORMERS IN DIFFERENT DOMAINS

#### 1) TRANSFORMERS FOR NLP

In the era preceding Transformers, Deep Learning heavily relied on Recurrent Neural Networks (RNNs) for text comprehension. The challenge with RNNs lies in their difficulty to train and their inability to be parallelized, given their sequential word-processing nature. This is where Transformers emerged as a solution. Transformers are applied to a diverse range of NLP tasks, including but not limited to text classification, question answering, language modeling and understanding, text generation, information retrieval, text summarization, and translation [15], [22], [28], [38], [47], [85], [87], [97], [130], [137], [138], [149], [170]. The Generative Pre-trained Transformer (GPT) series from OpenAI, along with Google's models like Palm and Bard, are recognized and widely acknowledged within this group. GPT models, like GPT-4 and GPT-3.5, are advanced text generation models by OpenAI. They understand both natural and formal language, generating text in response to provided inputs called "prompts." These models are versatile, used for tasks such as content generation, code writing, summarization, conversation, and creative writing. Explore our guides for more details.

In the realm of NLP research, three developing security concerns include adversarial and backdoor attacks [184], the potential compromise of private data [113], and the vulnerabilities associated with imitation attacks [69]. These security challenges may result in problems such as unauthorized data access, financial setbacks, reputation damage and other adverse consequences [186]. GPT models, with their remarkable progress, have garnered attention for applications in healthcare and finance. However, caution is needed as they can generate biased outputs, risking the disclosure of private information. While GPT-4 outperforms GPT-3.5 on

standard benchmarks, it is more susceptible to manipulation through unauthorized system access or manipulated user prompts [173].

#### 2) TRANSFORMERS FOR VISION

Due to the remarkable capabilities of Transformers in NLP, researchers have explored their application in computer vision. Traditionally, CNNs held a central role in visionrelated tasks; however, Transformers have recently garnered attention and prominence in the realm of computer vision. Computer vision Transformers are employed for a myriad of tasks, encompassing supervised and self-supervised learning, as well as tasks such as object detection, segmentation, generation, video captioning/summarization, action recognition, and sign language recognition [16], [32], [55], [99], [121], [167], [191], [195]. Beyond these applications, fields like medical imaging, autonomous driving, and agriculture have also experienced benefits from the utilization of Transformers for image and video processing [151], [158], [164]. Transformer architectures leverage a self-attention mechanism, treating images as sequences of patches [32].

Given their distinctive design in contrast to CNNs, it is imperative to investigate Transformers' susceptibility to a range of attacks, including backdoor attacks and other security threats. Additionally, it is crucial to delve into how different Transformer architectures impact overall robustness of the system. The risks linked to these vulnerabilities become more pronounced when implementing deep learning models in safety-sensitive fields such as autonomous vehicles. In these contexts, a security breach could lead to a dangerous scenario where the vehicle fails to recognize a pedestrian due to a specific adversarial stimulus captured by the camera, posing a direct threat to the safety and reliability of the autonomous system. [160].

FIGURE 3. Analyzing the proliferation of Transformer model publications across various domains from 2017, sourced from app.dimensions.ai, with "Transformer model" as the primary keyword. Additionally, the figure projects the anticipated number of publications in 2024.

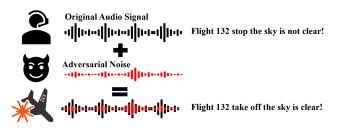

### 3) TRANSFORMERS FOR AUDIO PROCESSING

The Transformer architecture extends its applications to Audio Processing (AP) as well. Notable examples include Audio Transformers [172], Septr [142], and SpecTNT [101], showcasing successful implementations of the Transformer architecture in audio processing. The ability of Transformers to effectively capture long-range dependencies and interactions makes them especially attractive for time series modeling. This has led to significant advancements in various applications within the realm of time series analysis, [182]. Voice assistant applications like Google Home, Amazon Alexa, and Siri rely on key models-Automatic Speech Recognition (ASR) and Speaker Identification (SI). However, with the rise of IoT, security threats targeting machine learning models and hardware components have surfaced, raising concerns about information theft and privacy breaches. Transformers, a popular machine learning model, are increasingly employed in audio processing within this domain [89].

#### 4) TRANSFORMERS FOR SIGNAL PROCESSING

Researchers applied Transformers for signal processing. In [11], an automated seizure prediction framework integrated Fourier transform and a Transformer model, blending signal processing and deep learning for effective epilepsy identification. Utilizing face videos for heart rate estimation, researchers encountered challenges with time-varying ambient lighting. Neglecting optical modeling, they found poor performance in existing methods. To address this, a demodulation-based Transformer was designed for efficient rPPG signal purification [211]. In Music Source Separation (MSS), researchers examined the relevance of long-range contextual information and introduced Hybrid Transformer Demucs (HT Demucs), a model outperforming Hybrid Demucs by 0.45 dB in Signal-to-Distortion Ratio (SDR) with an extra 800 training songs, employing a cross-domain Transformer Encoder [143].

# 5) MULTI-MODELS BASED ON TRANSFORMER

Multimodal learning [185], [213] entails creating models with the ability to analyze and connect information from

various sources. Overcoming the obstacle of integration, the task involves crafting a unified network capable of addressing distinct modalities, including natural language, 2D images, 3D point clouds, audio, video, time series, and tabular data, despite their inherent disparities. Meta-Transformer [213], employing a frozen encoder, achieved multimodal perception without paired training data by mapping diverse inputs into a shared token space. The framework excelled across 12 modalities, demonstrating effectiveness in fundamental perception, practical applications, and data mining tasks according to benchmark experiments. Google recently unveiled Gemini [48], its most extensive and advanced AI model, tailored for multimodal comprehension and available in different sizes-Ultra, Pro, and Nano. With cutting-edge performance, intricate reasoning abilities, and proficiency in tasks like coding, Gemini marks a noteworthy advancement in AI, promising widespread availability and ongoing innovation.

#### **B. ARCHITECTURE OF TRANSFORMERS**

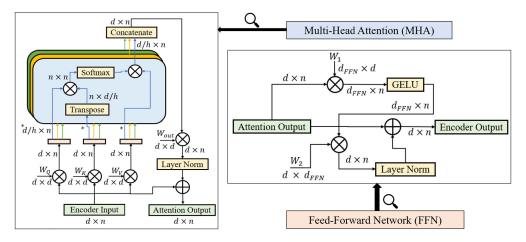

In this section, we embark on a detailed exploration of the foundational elements that make up the Transformer architecture. The Transformer architecture, as detailed in [170], typically consists of multiple Transformer blocks. Each of these blocks includes a multi-head attention (MHA) module alongside a feed-forward (FFN) module. Importantly, every block is sequentially accompanied by a Layer Normalization (LayerNorm) operation and a residual connection.

The attention mechanism enhances model accuracy by prioritizing relevant data and disregarding less important information, assigning weights to input attributes based on their significance to the output. It's particularly advantageous for tasks in NLP, computer vision, and speech recognition. Unlike CNNs which typically focus on local information, the attention mechanism can gather information globally from the entire input sequence. The MHA module in the Transformer architecture involves projection layers, matrix multiplications, and Softmax operations, as outlined in [170]. On the other hand, the FFN module comprises two projection layers separated by a nonlinear function. The specific computations for both the MHA and FFN are illustrated in Figure 4.

The MHA module begins by processing a sequence consisting of *n* tokens through a projection step. This step involves multiplying the sequence with three distinct weight matrices:  $W_Q$ ,  $W_K$ , and  $W_V$ , resulting in query, key, and value representations. These representations are then divided into *h* segments, each possessing a hidden dimension of d/h. Within each head, the query and key undergo multiplication along the hidden dimension, producing a matrix of representations, as articulated in Equation 1.

$$Q^{i} = QW_{Q}^{i}$$

$$K^{i} = KW_{K}^{i}; \quad i \in heads$$

$$V^{i} = VW_{i}^{i}.$$

(1)

FIGURE 4. Illustration detailing the computational processes within the Transformer encoder block, showcasing the multi-head attention (MHA) module and the feed-forward network (FFN) module.

FIGURE 5. Variants of Transformer networks depicted: (a) Encoder-only model conducts parallel inference for all tokens. (b) Decoder-only model follows an auto-regressive inference approach. (c) Encoder-decoder model utilizes the encoded sequence output as input for a cross-attention module.

The matrices from each head are subject to processing through the "scaled dot-product attention" function, as detailed in Equation 2, to calculate attention scores and generate output matrices. Following a Softmax operation, the resulting attention scores are then multiplied by the value segment, resulting in an activation with a hidden dimension of d/h.

$$O = SoftMax(\frac{QK^{T}}{\sqrt{d_k}})V = SV$$

(2)

The outputs from all attention heads are consolidated along the hidden dimension, resulting in a unified activation with a hidden dimension of d. This aggregated result undergoes projection using the weight matrix  $W_{out}$  within a concluding linear layer. Following this, the output undergoes normalization via LayerNorm and is combined with a residual connection, ultimately producing the final output of the MHA module. Regarding the FFN module, it is a straightforward block comprising two linear layers. Initially, the input sequence is projected from the hidden dimension d to a higher FFN dimension through the first linear layer. Subsequently, the projected sequence is transformed back to the original dimension d using the second linear layer.

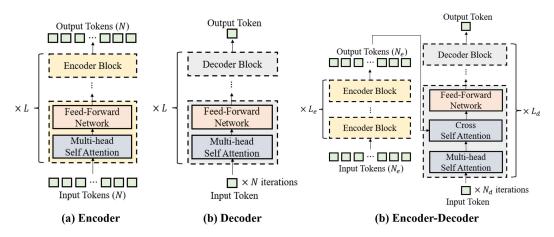

#### 1) NLP TRANSFORMER ARCHITECTURE

Figure 5 depicts various types of NLP Transformer architectures: Encoder, Decoder, and Encoder-Decoder. The Transformer architecture was originally devised as an Enncoder-Decoder model [170]. In this configuration, the encoder receives the entire source language sentence and processes it through multiple Transformer encoder blocks to distill high-level features. These features are then transmitted to the decoder, which, in turn, is responsible for the stepwise generation of tokens in the target language. In encoder-only Transformer models, the input sequence is processed directly by multiple encoder blocks as a continuous flow. This design,

FIGURE 6. Illustration outlining the fundamental structure of the (a) original Visual Transformer (ViT), highlighting the key architectural elements, (b) DeiT, (c) Swin Transformer, and (d) Two consecutive blocks of Swin Transformer.

exemplified by models like BERT, is particularly effective for tasks centered around natural language understanding. Decoder-only models, composed of recurring decoder blocks, exhibit an auto-regressive nature. This implies that the output at a specific time step relies on the outputs from previous time steps. Essentially, the model predicts a token in a sentence by considering the tokens it has generated earlier.

As a consequence, inference in decoder-only models must be executed sequentially and iteratively for each output token. An example of a decoder-only architecture is GPT-based models.

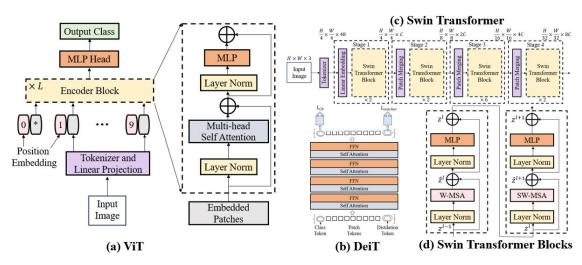

#### 2) VISION TRANSFORMER ARCHITECTURE

Figure 6-(a) illustrates the Vision Transformer (ViT) [32], designed with inspiration from the architecture of encoderonly Transformers frequently employed in NLP. ViT architecture utilizes self-attention mechanisms to process images, employing a series of Transformer blocks. Each block comprises two sub-layers: a multi-head self-attention layer and a feed-forward layer. The self-attention layer computes attention weights for each image pixel based on its relationships with others, while the feed-forward layer applies a non-linear transformation to the self-attention layer output. The multi-head attention enables simultaneous attention to different parts of the input sequence. In the design of the ViT model, a patch embedding layer is integrated alongside Transformer blocks. This involves breaking down the image into fixed-size patches and assigning each patch to highdimensional vectors. The model's final class prediction is generated by passing the last output of the Transformer block through a classification head, typically composed of a single fully connected layer. This architectural approach efficiently processes images by combining self-attention and patchbased representations. A crucial feature introduced in ViT, similar to BERT, is the incorporation of a "classification token." This token serves as a comprehensive summary of the entire input image and is appended to the sequence of patch embeddings before entering the Transformer blocks. Acting as a global context aggregator, the classification token empowers the model to consider the overall content of the image during the classification process. This integration enhances ViT's capacity to capture holistic information, resulting in improved performance across various image classification tasks. Other popular variants of ViT, such as DeiT [167] and Swin Transformer [99], are shown in parts (b) and (c) of Figure 5, respectively. DeiT employs a teacher-student strategy specifically designed for Transformers, using a distillation token to enable the student model to learn from the teacher model through attention. This approach eliminates the need for training on a huge dataset, producing a competitive convolution-free Transformer by training on ImageNet only. Swin Transformer constructs hierarchical feature maps by progressively merging image patches in deeper layers and computing self-attention within local windows, leading to linear complexity relative to the input image size. Figure 6-(d) shows Swin Transformer blocks replace the standard MSA module with a shifted window-based MSA module while keeping other layers unchanged. Each Swin Transformer block consists of a shifted window-based MSA module, followed by a 2-layer MLP with GELU nonlinearity. LayerNorm (LN) is applied before each MSA module and each MLP, with a residual connection following each module.

# III. SECURITY ANALYSIS AND VULNERABILITY POINTS IN TRANSFORMER ARCHITECTURE

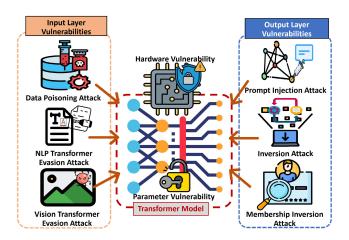

In this section, we delve into the security aspects inherent within Transformers, highlighting potential vulnerability points in which the attackers can leverage. The goal is to pinpoint areas prone to exploitation, offering insights crucial for enhancing the security of Transformer-based models. Figure 7 presents a comprehensive overview of vulnerability points in Transformer-based models, including input, output, and hardware vulnerabilities, which will be discussed in detail below.

# A. INPUT DATA

In Transformer-based models, the input data itself emerges as a critical attack point, susceptible to manipulation at various stages of the model's lifecycle. Two primary attack vectors on the input data are *data poisoning attacks* [76], [192] and *evasion attacks* [72], [217].

In data poisoning attacks, attackers strategically introduce malicious samples during the model's training phase to manipulate the learning process. By injecting deceptive data points into the training set, adversaries aim to induce the model to generate inaccurate predictions. This deliberate poisoning can have a lasting impact on the model's behavior, leading to unexpected and potentially harmful outputs during real-world usage [131].

In contrast, evasion attacks are devised after the Transformer model has been deployed in real-world scenarios. Attackers, in this case, modify specific data samples, often referred to as adversarial examples, to deceive the model into misclassifying them according to a predefined output label. This manipulation occurs at the inference stage, where the model encounters real-world data, and the attacker seeks to exploit vulnerabilities to force misclassification. Such attacks can manifest as adversarial patches and tokens. Vision Transformers may be vulnerable to adversarial patches, where manipulated regions in the input images deceive the model [49], [78], [159]. Meanwhile, in NLP tasks, attacks may occur at the token level, where adversaries manipulate specific words or segments to influence the model's output. These vulnerabilities underscore the importance of robust defense mechanisms to safeguard Transformer models against adversarial manipulations at the input data level [119], [198].

FIGURE 7. Overview of vulnerability points in Transformer models, encompassing input, output, and hardware vulnerabilities.

#### 1) MODEL OUTPUT

In addition to the input data, the model output represents a critical attack point in Transformer-based systems, with *model inversion* being a specific security threat that exploits this vulnerability. In model inversion attacks, adversaries leverage the output of a machine learning model, such as Transformers, to gain insights into some of its parameters or architectural details. This is achieved through a process of querying the model and utilizing the obtained output to infer specific characteristics of the model or input data. In the field of NLP, by meticulously analyzing the model's predictions and utilizing the output, adversaries attempt to reverse-engineer sensitive information, potentially exposing details about the training dataset [209].

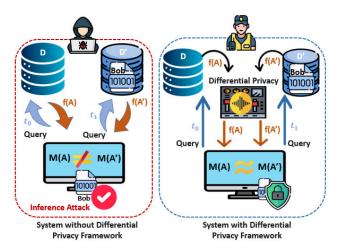

In a membership inference attack, the adversary seeks to ascertain whether specific personal information was part of the training dataset used for a target machine learning model. This attack hinges on training a separate model, known as a membership inference model, using the output or predictions generated by the target model. The attacker's model is trained to predict whether a given data point (e.g., personal information) was included in the target model's training dataset. The successful prediction by the attacker's model implies that the target model has potentially memorized or learned details about the input data, posing privacy concerns. This method underscores the need for privacy-preserving measures, such as differential privacy or data anonymization, to mitigate the risks associated with divulging sensitive information during the training process of machine learning models [68], [153].

#### **B. MODEL PARAMETERS**

In these attacks, adversaries leverage the model weights and corresponding gradients to reconstruct the original data batch. Essentially, they exploit the relationship between the model's parameters and its output to gain insights into the internal workings of the model [57]. Recent research indicates that despite the growing interest in distributed learning for enhancing data privacy on local devices, there's a concerning revelation. Publicly shared gradients during the training process have the potential to expose private training data, a phenomenon known as gradient leakage, to unauthorized third parties. TAG suggests a method to retrieve private training data of Transformer-based language models from the shared gradients [27]. Utilizing the Integrated Gradients (IG) method, saliency scores for model predictions were computed, guiding perturbation updates based on gradients' signs. IG indicated input sensitivity, with more pronounced perturbations expected at influential locations. Improved attack performance was achieved with a momentum-based iterative strategy akin to gradient descent, facilitating faster perturbation updates and aiding in escaping poor local optima. These strategies enhanced perturbation transferability across different models including ViT [106].

# C. PROMPT

*Prompt injection attacks* within large language models (LLMs) involve exploiting vulnerabilities by inserting prompts into data expected to be processed during model inference. This type of attack, known as "Indirect Prompt Injection" allows adversaries to remotely exploit LLM-integrated applications, even without direct user interaction. The primary goal is to manipulate these applications, causing unintended actions or generating content that aligns with the attacker's goals. By skillfully injecting specific prompts into data streams encountered by LLMs during inference, adversaries can influence the model's behavior, highlighting the vulnerability of LLM-Integrated Applications to strategic manipulations [2], [98], [196].

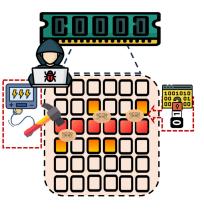

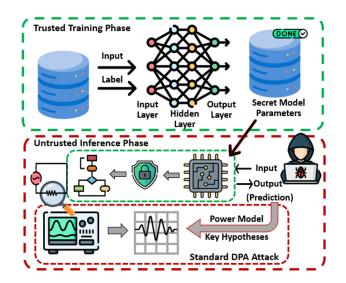

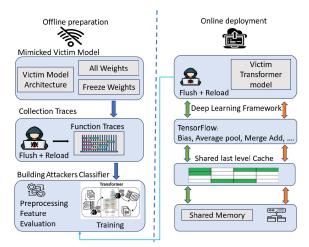

### D. UNDERLYING HARDWARE

Underlying hardware hosting calculation processes can pose vulnerabilities, particularly to hardware-oriented attacks like side-channel attacks [34], [35], [36]. These attacks, as demonstrated by studies such as [165], [166], and [190], have been proposed to compromise machine learning systems' security and privacy. These attacks could potentially threaten Transformer model hardware accelerators, which are crucial components of many AI systems. Additionally, with the global integrated circuit (IC) design flow, there is a possibility of maliciously inserting Trojans into the design, further amplifying security risks. Such Trojans could compromise the integrity and functionality of the hardware, potentially leading to severe security breaches. Moreover, there is the possibility of extracting sensitive information from memory units, adding another layer of vulnerability to the system. This underscores the importance of robust security measures and thorough validation processes in the design and deployment of Transformer-based systems, particularly in hardware-accelerated environments.

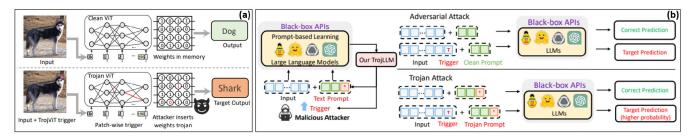

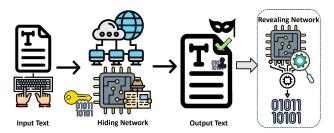

#### **IV. SOFTWARE LEVEL SECURITY CHALLENGES**

This section addresses the security concerns associated with Transformer models at the software level, encompassing adversarial attacks, Trojan insertion, federated learning, private inference, encryption-based approaches, intellectual property (IP), watermarking, and differential privacy. We conduct a comprehensive review of prior research in these domains.

#### A. ADVERSARIAL ATTACK AND DEFENCE

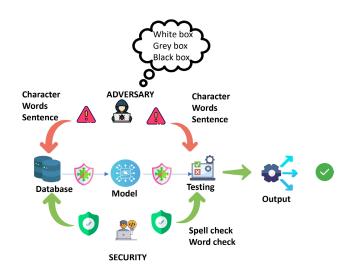

Adversarial examples [9], [79], [111], [112], [124], [193], [194] refer to manipulated input data that can deceive machine learning models while remaining imperceptible to humans. A white-box attack involves an adversarial attack where the attacker has full access to the details of the targeted model, including its architecture, parameters, and training data. With this knowledge, the attacker can develop a highly effective attack strategy. On the other hand, a black-box attack is an adversarial attack where the attacker is an adversarial attack where the attacker lacks access to the

FIGURE 8. Adversarial Attacks on NLP Transformers. Adversarial attacks are categorized into white, gray, and black box attacks, contingent on the attacker's access level. The attacks exhibit granularity at the character, word, or sentence levels. Defense strategies at different levels are proposed to prevent the attacks like checking misspellings and checking words.

details of the targeted model and can only interact with it through input-output channels. In this scenario, the attacker must rely on limited information obtained by querying the model to develop their attack strategy. Numerous studies have demonstrated the susceptibility of Transformer-based models across various applications to adversarial attacks [3], [210].

#### 1) ATTACK ON NLP TRANSFORMER MODELS

Figure 8 demonstrates an overview of adversarial attacks on NLP-based Transformers. Such attacks are classified into white, gray, and black box attacks, contingent on the attacker's access level, while showing granularity at the character, word, or sentence levels. Numerous methods have been developed in prior research to generate adversarial examples in image data, causing systems to fail [31], [90], [117]. However, these techniques cannot be readily extended to NLP models due to the distinct nature of data representation and the challenges associated with characterizing subtle alterations in text [146]. Optimization and gradient descent algorithms are used to create adversarial examples for visual applications. Due to the specific nature of textual data, there are only a limited number of white-box attacks available for NLP models. As it is challenging to compute gradients in the discrete space of textual data, one proposed approach is to determine the gradients in the continuous embedding space instead. Cheng et al. [21], proposed a white-box gradientbased method called AdvGen to generate adversarial examples targeting Neural machine translation (NMT). AdvGen generates adversarial examples using the final translation loss as a guide based on clean input data. It is applied to both the encoding and decoding stages. They showed that AdvGen improved BLEU scores by 2.8 and 1.6 points over state-of-the-art models, including Transformer, on

standard Chinese-English and English-German translation benchmarks.

This research [114] delves into the susceptibility of Transformer-based language models to adversarial attacks, particularly those categorized as "black box" attacks. Membership inference, in this context, pertains to the process of ascertaining whether a given data record was part of the training data used for the model's training. An attack involving membership inference considers the scenario where a malicious user of a black box prediction service could provide input messages resembling those of a competitor and, through the model's output, gather information about the user's data inclusion in the model's training set. This study specifically focuses on determining whether sample customer message data was incorporated into the training data when constructing a language model.

Seq2Sick [20] investigates the vulnerability of seq2seq models to adversarial attacks, comparing their robustness with CNN-based classifiers. The framework optimizes input sequences to produce desired outputs while preserving sentiment in word embeddings. It tackles discrete inputs using projected gradient descent, group lasso, and gradient regularization and addresses infinite output sequences with novel loss functions for non-overlapping and targeted keyword attacks. Seq2Sick's results show that while seq2seq models are susceptible to attacks with a high success rate, they are more robust than CNN-based models.

TextAttack [119], is a Python framework that facilitates adversarial attacks, data augmentation, and adversarial training for NLP models. TextAttack utilizes four components to construct attacks: a goal function, a set of constraints, a transformation, and a search method. TextAttack supports a range of models and datasets, including BERT, and offers implementations of 16 adversarial attacks previously proposed in the literature. The work in [197] investigates black-box attacks in NLP and offers recommendations on the most effective approach. The study revealed that in terms of attack success rate, beam search, and particle swarm optimization were the most optimal algorithms. If there is a time limitation or the input text is lengthy, using the greedy algorithm with word importance ranking is recommended, as it provides adequate performance. Also, simple greedy methods are often more effective and faster than complex algorithms like PWWS and genetic algorithms in terms of both attack success rate and speed. They showed that, on average, 10.05% of words were perturbed when BERT was used as the base model with the MR dataset and WordNet transformation.

The lack of a standardized definition and evaluation system has hindered the effective use of adversarial examples to enhance and comprehend NLP models. Perturbations often fail to preserve semantics, and 38% introduce grammatical errors. In response, the authors [118] propose a unified definition for successful adversarial examples in natural language, emphasizing modifications that not only deceive

VOLUME 12, 2024

the model but also conform to predetermined linguistic constraints. They introduce four categories of constraintssemantics, grammaticality, overlap, and non-suspicion to human readers-that NLP adversarial examples can align with depending on the context. This establishes a common vocabulary for discussing constraints on adversarial attacks, presenting distinct categories to which adversarial examples may adhere. The authors enhance the TEXTFOOLER algorithm with TFADJUSTED, incorporating a constraint enforcement mechanism to generate higher-quality NLP adversarial examples that better preserve semantics and grammaticality. Through human evaluation, the proposed algorithm produces perturbations that are less noticeable to humans, albeit with a lower attack success rate (70%) under stricter constraints. In adversarial training, TFADJUSTED's examples do not reduce model accuracy compared to TEXTFOOLER's examples.

In the work by Jin et al. [77], the authors introduced TEXTFOOLER as a method for generating adversarial text in a black-box setting. This approach comprises two primary steps: word importance ranking and a word Transformer, which serves as their method for replacing words in the text. They reduced the accuracy of almost all target models across all tasks to below 10% on the adversarial examples, with fewer than 20% of the original words perturbed In the study by Yuan et al. [203], a framework is introduced for generating adversarial samples in text data. The methodology includes the incorporation of continuously optimized perturbations into the embedding layer, subsequently amplifying them during forward propagation. The ultimate perturbed latent representations are decoded using a masked language model head to derive potential adversarial samples. The authors implement this framework by employing an attack algorithm known as Textual Projected Gradient Descent (T-PGD). The quality of the adversarial samples generated by T-PGD increases with text length. These adversarial samples achieved higher overall USE scores (similarity between original and adversarial samples) compared to baseline models, with a 97% attack success rate. This indicates that the proposed method can manipulate adversarial samples more precisely using explicit gradient information.

In the work by Liu et al. [94], the authors employed Attachable Subwords Substitution (ASS) and introduced the Character-level White-Box Attack (CWBA) method targeted at Transformer models. The proposed approach leverages Transformer models' practice of dividing words into subtokens, finding that substituting consecutive subtokens can be as impactful as modifying individual characters. To generate adversarial examples, they follow three steps: using a gradient-based technique to identify the most susceptible words, breaking these words into subtokens as replacements for the original tokens, and applying an adversarial loss to guide subtoken substitution. To ensure gradient propagation, they incorporate the Gumbel-softmax method. Their required query number was similar to the **GBDA** model and much lower than other black-box methods. Their **CWBA** outperformed DeepWordBug by 20.0 adversarial accuracy on average, showing the advantages of the white-box attack.

The study in [146] introduced a token-level gradient-based white-box adversarial attack method for Transformer-based text classifiers. This method ensures block-sparse adversarial perturbations, altering only a few words in the sentence. By selectively perturbing embedding vectors and optimizing the perturbation vector under a block-sparsity constraint, only a few tokens are modified. To preserve semantics, the modified embeddings are projected onto original token embeddings with the highest cosine similarity. Their experiments show that their attack maintains sentence semantics while reducing GPT-2's accuracy to below 5% on AG News, MNLI, and Yelp Reviews.

In [41], the proposed method, MANGO, uses gradients to navigate a continuous space of token probabilities to find adversarial examples. As an optimization-based white-box attack, MANGO reduces the disparity between adversarial loss in continuous and discrete text representations through a quantization-compensation loop. This involves iterative quantization of token representations and reoptimization to maintain the adversarial loss value.

GPTFUZZER [201], a black-box jailbreak fuzzing framework inspired by AFL, automated the creation of jailbreak templates for red-teaming LLMs, eliminating manual efforts. Employing seed selection, mutate operators, and a judgment model, it effectively tested against LLMs like ChatGPT, LLaMa-2, and Vicuna. Results showcased its ability to unveil vulnerabilities and assess LLM robustness in diverse attack scenarios.

#### 2) DEFENSE FOR NLP TRANSFORMER MODELS

In response to attacks targeting NLP Transformer models, it is crucial to deploy robust defense strategies to counter potential vulnerabilities and thwart adversarial attacks. Defense strategies at different levels are proposed to prevent the attacks like checking misspellings and checking words as shown in figure 8. The authors in [21] defend NMT models by attempting to decrease the prediction errors for the corresponding adversarial source inputs. The proposed approach consists of two main components: first, subjecting the translation model to adversarial source examples as an attack; and second, reinforcing the model by introducing adversarial target inputs, thereby improving its resilience against adversarial source inputs.

The study [80] addressed orthographic attacks on the Zeroe benchmark, encompassing various cognitive modelbased attacks. Unlike previous spelling correction modules, which were effective against simple typo attacks, they failed on the more diverse Zeroe benchmark. In response, the authors introduced a novel technique that leverages context-independent extensions of the Levenshtein distance, probability distributions from a dictionary, and BERT's masked language modeling objective. This iterative process

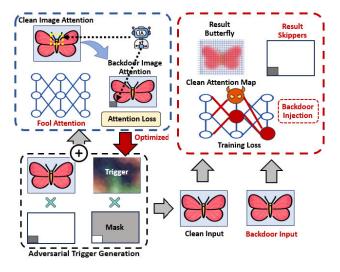

**FIGURE 9.** In the context of a backdoor attack, using a patch-wise trigger effectively disrupts the attention distribution in images. This strategy ensures that the ViTs' attention is primarily focused on the patch containing the trigger, thereby influencing the model's focus on the entire backdoor input [204].

refines word context, predicts clean words, and utilizes a source text-independent language model to generate fluent output, providing a more robust defense against diverse orthographic adversaries.

In [62], it was observed that many existing adversarial attacks fail to maintain the original text's meaning, challenging their claimed semantic preservation. The root cause was identified in the text encoders used for assessing adversarial example similarity, specifically in their training methodologies. Encoders trained through unsupervised methods exhibited difficulty recognizing antonyms. To overcome this limitation, the authors introduced a fully supervised sentence embedding approach named Semantics-Preserving Encoder (SPE). The key idea behind SPE involves supervised training using labeled datasets to mitigate issues related to antonyms within the same context. This approach clusters words significant for a given label in the vector space. The incorporation of various classifiers trained on diverse annotated datasets further enriches their arsenal of sentence vectors.

# 3) ATTACK ON VISION TRANSFORMER MODELS AND ITS TRANSFERABILITY

Recent research has highlighted the superior resilience of ViTs compared to CNNs against different perturbations, including natural corruption and adversarial attacks. The reasons behind the enhanced robustness of ViTs are a subject of debate within the research community. Some argue that the segmentation of input images in ViTs plays a central role, while others attribute it to the utilization of MSA in ViTs. In this study [107], the authors assess the robustness of ViTs against two types of adversarial attacks: whitebox and black-box attacks. The evaluation is carried out across various benchmark datasets, including CIFAR-10, CIFAR-100, and ImageNet, utilizing two ViT architectures, namely DeiT and ViT-B/16. Comparative analyses involve state-of-the-art models such as ResNet and EfficientNet under both types of attacks. The experimental outcomes reveal that ViTs generally exhibit greater robustness to adversarial examples compared to ResNet and EfficientNet. Notably, ViTs demonstrate heightened resilience to blackbox attacks. Furthermore, the study observes a correlation between increased model size in ViTs and enhanced robustness. White-box attacks involve the use of the Fast Gradient Sign Method (FGSM) and the projected gradient descent (PGD) attack, while black-box attacks employ a substitute model strategy. The authors also conduct a sensitivity analysis, discovering that adjusting hyperparameters, such as increasing Transformer layers and reducing the learning rate, can positively impact the robustness of ViTs.

Joshi et al. [78], introduced a block sparse attack on deep neural networks, with a specific focus on a patchbased approach. The study compared the vulnerability of Transformer models to traditional CNNs regarding this attack. Interestingly, the results indicated that ViTs were more susceptible to patch attacks and mixed norm attacks (a variant of their patch-based block sparse attack) compared to CNN-based with ResNets outperforming Transformer models by up to approximately 30% in robust accuracy for single token attacks. Notably, ViTs exhibited increased robustness only for smaller patch sizes, as they could effectively compensate for perturbations in patch attacks that were smaller than the token size. The authors in [176] leverage the inherent architectural aspects of vision Transformers, such as self-attention and image embedding, to craft potent transferable attacks. Initially, their model determines an 'uncertainty index' for all patches by capitalizing on the self-attention mechanism present in vision Transformers. Subsequently, after pinpointing the most uncertain patches, the model identifies the pixels significantly influencing the image embedding process as the primary sites for the attack. These attacks showcase high transferability, attributed to exploiting the image embedding and self-attention features inherent in vision Transformers. This underscores the pivotal roles played by image embedding and self-attention in bolstering the resilience of Transformers.

Figure 9. shows the backdoor training in ViT. This backdoor attack involves inserting a small, imperceptible patch (trigger) into an image during training to manipulate a ViT model's behavior. The trigger is designed to disrupt the model's attention, causing it to focus primarily on the patch with the trigger. During training, the model learns to associate this trigger with a specific incorrect prediction, regardless of the actual image content. The goal is to ensure that whenever the trigger is present, the model consistently makes the intended wrong prediction, effectively creating a backdoor in the model [204]. The research in [122] delved into the adversarial feature space of ViTs

and their transferability compared to conventional CNNs. Large ViT models exhibited low black-box transferability due to suboptimal attack procedures that underutilized ViTs' representation potential. The compositional nature of ViT models, with multiple blocks independently producing class tokens, revealed limitations in attacking only the last class token. To address this, two strategies were introduced: "Self-Ensemble," creating an ensemble of networks from a ViT model, and "Token Refinement," combining class tokens with structural information from patch tokens. Applying adversarial attacks to refined tokens within the ensemble demonstrated significantly higher transferability, showcasing the true generalization potential of ViTs. The proposed method involves augmenting the training data with adversarial examples generated through a combination of PGD and Carlini-Wagner (CW) attacks.

Wei et al. [180] proposed a method to enhance the transferability of adversarial attacks across various ViT models. The attack utilized a dual approach, combining the self-attention mechanism and the patch embedding layer. This method generates adversarial examples capable of disrupting the feature extraction process across a diverse range of neural network architectures, showcasing high transferability. They observed that the ASR decreases as more attention gradients are used during backpropagation. Bypassing all gradients of attention improves the ASR from 29.92% to 42.47%. Existing adversarial attack methods often struggle to achieve comparable levels of transferability when targeting ViTs. In the paper by Han et al. [56], the Partial Blocks Search Attack (PBSA) is introduced. PBSA aims to generate adversarial examples for ViTs with increased transferability by categorizing encoder blocks into two groups based on a block weight score. Unlike applying a uniform strategy to all blocks, distinct strategies are employed for each group. The optimization of perturbation generation involves incorporating regularization of self-attention feature maps and utilizing an ensemble of partial blocks. Additionally, the authors introduce adaptive weight adjustments for perturbations, specifically targeting the most effective pixels in the original images. The proposed PBSA method shows significantly higher transferability, outperforming baseline attacks by 12% to 26% on average. For instance, PBSA achieves a 97.38% success rate against ViT-S and 50.82% against T2T-24, while the PGD attack only reaches 84.46% and 22.12%, respectively.

The work in [104] introduced Data-Free Backdoor Attack (DBIA). Leveraging attention mechanisms, the attack generates triggers to alter model predictions. The authors outline algorithms for poisoned dataset creation and backdoor injection, involving maximum attention triggers and fine-tuning selected neurons. The DBIA attack is compared with BadNets and Trojaning in terms of data-free capability and computational cost, demonstrating a cost of at most  $O((\alpha \times m)+n)$ , where  $\alpha$  is a constant, *m* is the dataset size, and *n* is the model size. The evaluation involves three Transformer models (ViT, DeiT, Swin Transformer) trained on CIFAR-10

and ImageNet, with performance assessed using Clean Data Accuracy (CDA) and ASR. Experimental results indicate the effectiveness of the proposed DBIA attack in injecting backdoors with a high ASR.

4) DEFENSE FOR VISION TRANSFORMER MODELS

The work in [70], the authors present a novel defense mechanism known as PatchVeto, designed to provide zero-shot defense against adversarial patches targeting ViT models. Unlike traditional approaches involving the training of robust models, which may compromise accuracy, PatchVeto adopts a unique strategy. It utilizes a pretrained ViT model without additional training, maintaining high accuracy on clean inputs. PatchVeto leverages manipulation of the attention map in ViT to detect adversarial patched inputs. The method employs a voting process, where each input undergoes multiple inferences with different attention masks. This ensures that at least one inference will exclude the adversarial patch. If all masked inferences are in agreement, the prediction is considered certifiably robust, providing reliable detection of any adversarial patch without false negatives. PatchVeto achieves 67.1% certified accuracy on ImageNet for 2%-pixel adversarial patches, outperforming state-of-the-art methods, while maintaining the clean accuracy of vanilla ViT models at 81.8%.

The authors of the paper [115] argue that ViTs do not exhibit superior resilience against adversarial attacks compared to traditional CNNs under widely used threat models. Consequently, the authors assert that ViTs still require adversarial training to enhance their robustness against such attacks. The study suggests that effective adversarial training for ViTs involves the incorporation of pre-training and the utilization of the SGD optimizer. Their findings indicate that introducing random masking of gradients from specific attention blocks or applying mask perturbations on specific patches during adversarial training significantly improves the adversarial robustness of ViTs. Two proposed techniques for this enhancement are Attention Random Dropping (ARD) and Perturbation Random Masking (PRM).

In [177], the authors undertake a theoretical analysis of ViTs adversarial robustness using the Cauchy Problem. This approach allows them to quantify the propagation of robustness across different layers of the network. Their conclusions suggest that the initial and final layers exert the most significant impact on ViTs' robustness. Additionally, empirical evidence indicates that MSA enhances ViTs' adversarial robustness primarily against weak attacks like FGSM. Surprisingly, under stronger attacks such as PGD attacks, MSA contributes to the model's vulnerability, challenging previous assumptions about its role in ViTs' adversarial robustness.

The authors [152] discovered that ViTs exhibit greater robustness than CNNs against adversarial attacks, particularly in the context of high-frequency perturbations. This resilience is attributed to ViTs learning features with less low-level information, rendering them less sensitive to high-frequency perturbations. Notably, adversarial examples crafted for ViTs demonstrate higher transferability to CNNs compared to the reverse scenario. The introduction of convolutional blocks in ViTs may enhance the learning of low-level features but adversely affects adversarial robustness. Conversely, CNNs equipped with attention mechanisms demonstrate improved robustness against attacks. ViTs attain a robust accuracy (RA) of 59.8%, while CNNs achieve only 16.7% at best.

Wu et al. [183] study factors influencing ViTs' robustness, emphasizing low-level features in patch embedding and the impact of position encoding on semantic features. They advocate for a multi-stage structure for ViTs, highlighting the adverse effects of increasing Transformer blocks with large spatial resolution on robustness. Attention heads are crucial, with an optimal number enhancing robustness through diverse attentive information. The authors propose position-aware attention scaling (PAAS) and patch-wise augmentation, showing superior performance against adversarial attacks on ImageNet and robustness benchmarks.

The paper [8] investigates methods to enhance the robustness of CNNs inspired by Transformer architecture. Three key strategies, including patchifying images, using small convolutional kernels, and reducing normalization and activation functions, are explored. Experimental results on diverse benchmarks, such as Stylized-ImageNet, ImageNet-C, and ImageNet-R, demonstrate that these methods significantly improve the out-of-distribution robustness of CNNs. Notably, increasing the patch size and mimicking self-attention with larger convolution kernel sizes contribute to closing the robustness gap between CNNs and Transformers. The study introduces a CNN architecture model, leveraging these methods, capable of matching or surpassing the robustness of comparable Vision Transformer models.

In the exploration of universal adversarial perturbations for ViTs, the paper [67] introduces Inheritance Attention Matrix-based Universal Adversarial Perturbations (IAM-UAPs) by incorporating an inheritance attention weight matrix. ViTs exhibit superior robustness compared to CNNs against existing adversarial attacks, mainly attributed to the attention operator. The proposed IAM-UAP leverages the activation of the inheritance attention matrix to measure deviations between adversarial and legitimate samples. By focusing on attention-based attacks and introducing the IAM, the paper evaluates the robustness of various ViT modes against Universal Adversarial Perturbations (UAPs). Experimental results highlight the impact of IAM-UAP on attention maps, directly affecting the classification performance of ViTs and emphasizing their stronger robustness compared to CNNs.

In the assessment of adversarial robustness for image classification, this study [10] examines ViT, MLP-Mixer, and CNN architectures. It highlights that the reduced robustness of CNNs is mainly attributed to their shift invariance.

ViTs, although less shift-invariant, exhibit higher frequency responses than CNNs. Additionally, adversarial examples crafted for CNNs demonstrate poor transferability to foreign architectures, while the reverse holds true. The overall robustness ranking is ViTs being the most robust, followed by MLP-Mixers, with CNNs exhibiting the least robustness. The paper [5] introduces the Transformer-Encoder Detector module (TEDM), incorporating a Transformer encoder, a detector, and a context encoder. Leveraging an attention mechanism, TEDM enhances object detection by improving the labeling of image regions and encoding contextual statistics implicitly. This model boosts performance on both natural and perturbed images, showcasing its effectiveness in robust object detection. This work focuses on using context to improve robustness, achieving significant advancements, including up to a 13% increase in mAP scores, F1 scores, and AUC average scores compared to the baseline Faster-RCNN detector.

In the research [26], the authors studied a part of the ImageNet dataset to create a better way to train ViTs against adversarial attacks. The usual method for ViT training involves strong data augmentation, but the researchers found that this approach didn't work well for adversarial training. Instead, they discovered that by avoiding heavy data augmentation and adding techniques like warmup and larger weight decay, they significantly improved ViTs' ability to handle adversarial situations. This method proved effective for different ViT architectures and larger models.

MIA-Former [202] addresses the challenge of fitting ViTs onto resource-constrained devices, as ViTs are computationally expensive and treating all regions of images equally is unnecessary. This framework allows ViTs to input-adaptively adjust their structure at three levels of granularity: model depth, the number of model heads, and the number of tokens. Mia-former achieves this by making input-dependent decisions at each level of granularity using a MIA-controller, which is jointly trained with the ViT models via a hybrid supervised and reinforcement learning scheme. At the coarse granularity, MIA-Former first decides whether to mask out a given ViT block. When a ViT block is masked out, the outputs of the previous block skip the current block and are directly fed into the next block. However, if the current block is not skipped, Mia-former decides to mask out certain tokens and heads. Similar to the effect of ensemble models, this input-dependent control improves the model diversity and increases the difficulty of adversarial attacks against ViT's sub-blocks. The proposed method enhances ViTs' robustness accuracy against various adversarial attacks, outperforming their vanilla counterparts by 2.4% and 3.0%, respectively.

RViT, proposed by Mao et al. [109], focuses on enhancing the robustness of ViTs through a multi-faceted analysis. The key factors explored include the impact of low-level features in patch embedding, the critical role of position encoding, and the design considerations for Transformer blocks. The study emphasizes the importance of attention head completeness and compactness, with an optimal head number contributing to increased robustness. Additionally, modifications such as position-aware attention scaling and patch-wise augmentation are introduced to further enhance ViTs' robustness. Experimental results demonstrate the effectiveness of RViT across ImageNet and various robustness benchmarks.

SEViT [7], introduces a self-ensembling approach. Within the SEViT framework, feature representations (patch tokens) are extracted from the initial blocks of the ViT model, and separate intermediate classifiers, such as MLPs, are trained. By combining the predictions from these intermediate classifiers with the final ViT classifier, the self-ensemble method strengthens the robustness of ViTs against adversarial attacks. To identify adversarial samples, SEViT utilizes the consistency between predictions within the ensemble. The evaluation of SEViT was conducted on two publicly available medical datasets, with attacks generated using the Foolbox library.

The paper [159] investigates security concerns and defense strategies against Backdoor Attacks, including BadNets and Hidden Trigger Backdoor Attacks. Addressing potential threats during the model's training phase, the study introduces a feature-collision-based attack method, concealing triggers in poisoned images. It further proposes a test-time imageblocking defense, leveraging trigger localization results specific to Vision Transformers. Typically, backdoor triggers are small patches (2)-5% of the image area), influencing the model's decision. The paper utilizes a heatmap to identify influential image regions, successfully defending against backdoor attacks. Performance evaluation metrics, including Val Accuracy, ASR, and Source Accuracy, demonstrate a significant reduction in ASR with the proposed defense mechanisms.

Chang et al. [17] aimed to enhance the resilience of the ViT model by incorporating the ResNet-SE module into the Attention module. Beyond its initial role in edge and line data detection, the Attention module gains the capability to discern intricate feature information. Through the ResNet-SE module, the model enhances its feature extraction capacity by prioritizing crucial data points and suppressing extraneous details within each feature map. Integration of the SE module into the ViT model involves incorporating convolutional operations. Notably, the SE module excels in capturing local features, allowing it to effectively grasp intricate details of textures and lines. Consequently, the proposed defense method exhibits high proficiency in thwarting both white-box and black-box attacks. The accuracy of the proposed defense method is 19.812% against BIM, 17.083% against C&W, 18.802% against DeepFool, 21.490% against DI2FGSM, and 18.010% against MDI2FGSM attacks.

The research in [29] investigates ViT models' vulnerability to backdoor attacks through patch-based and blendingbased transformations, comparing their robustness to CNNs. ViT experiences a significant drop in ASR for patchbased attacks and a decline in clean-data performance for blending-based attacks. The study proposes a test-time defense using heatmaps to localize influential image patches, resulting in reduced ASR.

The work in [88] introduces ViP, a unified framework for certified robustness that enhances performance in certified detection and recovery tasks. To conduct certified detection, a small mask slides across a clean image, producing partially occluded images analyzed by a DNN. However, scalability is limited by computational complexity and reliance on CNNs with small receptive fields. To address this, the authors deploy self-supervised vision Transformers and a patch-dropping strategy. Certifiable detection is achieved by dropping a few patches and ensuring consistent predictions, while certifiable recovery involves dropping many patches and comparing majority voting predictions to sub-majority predictions. The proposed method surpasses prior techniques, with up to a 16% improvement in the certified detection rate on ImageNet. The authors also offer a theoretical guarantee for dual-patch attack detection. This method achieves a new state-of-the-art performance for certified recovery by increasing the certified accuracy by approximately 2% for all attack sizes on the ImageNet dataset.

In this study [154], the authors introduce MixVAT as a means to enhance the adversarial robustness of pre-trained vision Transformers. They achieve this by employing data-augmented virtual adversarial training. The key innovation of this work lies in reformulating the overall loss function. This is accomplished by incorporating the cross-entropy loss function with the virtual adversarial training loss, both applied to the augmented data, which is further multiplied by a hyper-parameter. The augmented data is generated through the MixUp approach applied to unlabeled data. Additionally, the local distributional smoothness of the newly created synthetic data is regularized. One of the advantages of MixUp is its ability to leverage information from two different images to generate a new synthetic data point. This new synthetic data encompasses the semantic information present in both images, thereby increasing the complexity of the training data. Ultimately, this augmentation process enhances the robustness of the models after training.

In the paper by Wang et al. [178], the authors propose an approach to assess adversarial robustness in neural networks by decomposing the network into submodules and calculating the maximal singular value for each module concerning input. The results suggest that MSA exhibits limited effectiveness in defending against adversarial attacks. The provided software includes a training module facilitating the training of a basic ViT model from scratch using the SAM optimizer. A modified ViT model, replacing its Multihead-Self-Attention with a 1-D convolutional layer, is included for comparative analysis. Additionally, an attack ensemble, employing the torchattack library, is introduced, offering FGSM, PGD, and CW attack strategies. Certified patch defenses can protect image classifiers against arbitrary changes in a bounded region but

at the cost of accuracy degradation and increased inference time.

The work in [147] presents a method to enhance certified patch defenses by using ViTs. The enhancement is a result of the inherent capability of ViT to adeptly process images that are substantially masked. The authors show that using ViTs improves certified patch robustness while reducing inference time by up to two orders of magnitude compared to previous methods. They achieve this by deploying and optimizing the ViT architecture to eliminate unnecessary tokens and reduce the smoothing process, leading to avoiding redundant computations. Furthermore, this method maintains the model's accuracy and performs inference with comparable speed to the non-robust model (ResNet).

The study by Parekh et al. [133] investigates the performance of adversarial attacks on a compressed ViT model using three advanced compression techniques: Quantization, Pruning, and Weight Multiplexing. The research explores the transferability of attacks between compressed and original models, revealing that ViTs show resistance to Spatial Attacks, while quantized models are more susceptible, with increased transferability from quantized to original models. Pruned models are generally more vulnerable to attacks than the original ones, and attack transferability decreases with higher pruning probabilities due to increased model sparsity. Weight multiplexed models demonstrate greater resistance to attacks compared to both distilled and original models. However, attacks from weight multiplexed models are more potent against the original model than those from purely distilled models, highlighting the former's enhanced resistance to attacks and the consequent generation of stronger attacks.

The ViT model, emphasizing global interaction among image patches, exhibits reduced sensitivity to local noise. However, prevailing decision-based attacks overlook variations in noise sensitivity across image regions, posing challenges in efficiently compressing noise, particularly for ViT models. Addressing this issue, the authors of the paper [155] introduce a novel attack strategy named Patch-wise Adversarial Removal (PAR). PAR considers differences in noise sensitivity among image patches and conducts a theoretical analysis of limitations in existing decision-based attacks. The approach employs a coarse-tofine search, dividing images into patches and applying noise compression to each patch individually. Furthermore, PAR tracks the noise magnitude and sensitivity of each patch, selecting the patch with the highest query value for noise compression. This strategy aims to enhance the assessment of black-box adversarial robustness in ViT models when only query access to the target model is available.

In the study presented in [24], the focus is on assessing the security of block-based image encryption methods for vision Transformers, particularly in the context of a specific adversarial attack known as the Jigsaw Puzzle Solver Attack (JPSA). The author utilizes a dataset of images to scrutinize

# IEEE Access

# TABLE 1. Summary of adversarial attack and defense techniques.

|        | Paper              | Year | Type of Attack                                       | Type of Defense                                                                                            | Result                                                                                                                                                                                                  |  |

|--------|--------------------|------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Vision | MIA-Former [202]   | 2022 | Adversarial attack                                   | Adaptive model restructure                                                                                 | 20.1% FLOPs reduction and 2.4% higher                                                                                                                                                                   |  |

|        | SEViT [7]          | 2022 | Adversarial attack                                   | Self-Ensembling                                                                                            | robustness accuracy<br>2.61% improvement in accuracy                                                                                                                                                    |  |

|        | ViP [88]           | 2022 | Patch attack                                         | Certified detection                                                                                        | 29.1% reduction in accuracy                                                                                                                                                                             |  |

|        | MixVAT [154]       | 2022 | White-box<br>Adversarial attack                      | Data-augmented virtual adversarial<br>training                                                             | 58.47% reduction in accuracy                                                                                                                                                                            |  |

|        | Smoothed ViT [147] | 2022 | Patch attack                                         | Derandomized smoothing defense<br>for certified patch                                                      | 12% more accurate and 10.7x faster than<br>ResNet50                                                                                                                                                     |  |

|        | [140]              | 2022 | Adversarial attack                                   | Ensemble training and Networks                                                                             | DINO improves ViT accuracy by 3.8% vs.<br>white-box attacks                                                                                                                                             |  |

|        | TrojViT [218]      | 2023 | Backdoor attack                                      | <i>⇒</i>                                                                                                   | TrojViT has <0.3% Clean Data Accuracy<br>loss                                                                                                                                                           |  |

|        | [5]                | 2021 | Adversarial Attacks                                  | Transformer Encoder Detector<br>Module                                                                     | 6.5% improvement in F1 score                                                                                                                                                                            |  |

|        | PatchVeto [70]     | 2021 | Adversarial Patches                                  | Zero-shot defense                                                                                          | 67.1% certified accuracy against 2%<br>adversarial patches, matching ViT's 81.8%<br>clean accuracy.                                                                                                     |  |

|        | [183]              | 2022 | Adversarial Attack                                   | Position-aware Attention scaling & patch-wise augmentation                                                 | Achieves comparable robustness to SOTA with 65% of training time.                                                                                                                                       |  |

|        | [133]              | 2022 | Adversarial Attacks                                  | Quantization, Pruning, and Weight<br>Multiplexing                                                          | High pruning sparsity reduces the<br>effectiveness of adversarial attacks;<br>Quantized models are more vulnerable to<br>black-box attacks and weight multiplexed<br>models are more robust to attacks. |  |

|        | IAM-UAP [67]       | 2021 | Universal Adversarial<br>Perturbation                | Increase in robustness by<br>Inheritance Attention Matrix                                                  | ViTs are more robust than CNNs against the<br>universal attacks. Patch size is a factor<br>affecting the robustness of ViTs.                                                                            |  |

|        | [21]               | 2019 | White-box<br>Adversarial Attack                      | Adversarial Training                                                                                       | Adversarial training improves the neural<br>machine translation task by 1.6 BLEU<br>points.                                                                                                             |  |

|        | TEXTFOOLER [77]    | 2020 | Black-box<br>Adversarial Attack                      | Data-augmented virtual adversarial training                                                                | Reduced the accuracy of target models in studied tasks to below 10% with only less than 20% of the original words perturbed.                                                                            |  |

|        | Seq2Sick [20]      | 2020 | Adversarial attack                                   | -:                                                                                                         | Only 2.2% of generated adversarial<br>examples have semantic meaning differ<br>from the original sentences.                                                                                             |  |

|        | [25]               | 2022 | Adversarial Attack                                   | Detection using statistical features                                                                       | Statistical features provide additional<br>adversarial robustness that can be leveraged<br>in ensemble detection models.                                                                                |  |