IEEEAccess Multidisciplinary : Rapid Review : Open Access Journal

Received 23 June 2024, accepted 31 August 2024, date of publication 6 September 2024, date of current version 18 September 2024. *Digital Object Identifier* 10.1109/ACCESS.2024.3455766

# **RESEARCH ARTICLE**

# A Differential PD/TIA Interface for Enhanced SNR and Baseline Wander Reduction in High-Speed CMOS Optical Receivers

### **DIAAELDIN ABDELRAHMAN<sup>®1</sup> AND MOHAMED ATEF<sup>®2</sup>, (Senior Member, IEEE)** <sup>1</sup>Electrical Engineering Department, Faculty of Engineering, Assiut University, Assiut 71515, Egypt

<sup>2</sup>Electrical and Communication Engineering Department, College of Engineering, United Arab Emirates University, Al Ain, Abu Dhabi, United Arab Emirates Corresponding author: Mohamed Atef (moh\_atef@uaeu.ac.ae)

This work was supported by United Arab Emirates University under Grant G00004546, and in part by Assiut University.

**ABSTRACT** In this paper, a photodiode (PD)/transimpedance (TIA) interface is presented. The cathode terminal of the PD is AC-coupled to one of the inputs of a pseudo-differential TIA while the anode terminal is DC-coupled to the other input of the TIA. The DC-coupled input provides a path for the low-frequency component of the input signal to reach the output. This component is extracted by a baseline wander compensation scheme (BWCS) and fed to the input to eliminate signal drift after long data runs. Compared with the conventional pseudo-differential receiver, the proposed interface improves the gain, the gain-bandwidth product (GBW), and the signal-to-noise ratio (SNR) by 5dB,  $1.37 \times$  and 4.5dB, respectively, while maintaining  $209 \times$  smaller low cutoff frequency than the AC coupled receiver. The proposed interface is compatible with any TIA topology. Post-layout simulations and analytical models validate the feasibility of the proposed technique.

**INDEX TERMS** Transimpedance amplifier, optical receiver, signal-to-noise ratio, gain-bandwidth product, baseline wander.

### I. INTRODUCTION

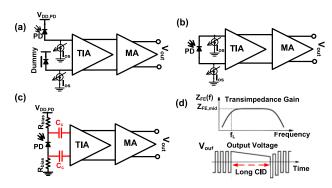

Differentia signal processing provides better immunity against common-mode disturbances than its single-ended (SE) counterpart [1]. However, differential circuit implementations usually trade off with performance metrics. For example, in the pseudo-differential (Ps-Diff) optical receiver in Fig. 1 (a), a replica transimpedance amplifier (TIA) connected to a dummy photodiode is employed to feed the common-mode signal to the second input of main amplifier (MA). This replica TIA does not contribute to signal amplification but increases power dissipation and doubles the input-referred noise power [2]. Therefore, the Ps-Diff structure achieves a 3dB worse signal-to-noise ratio (SNR) compared to its SE counterpart. A differential TIA can be employed to sense the current from both terminals of the PD as shown in Fig. 1 (b). In principle, this differential interface

The associate editor coordinating the review of this manuscript and approving it for publication was Stanley Cheung<sup>(b)</sup>.

doubles both the gain and output noise power compared to the SE structure, resulting in 3dB and 6dB improvements in the SNR compared to the SE and Ps-Diff structures, respectively.

However, differential sensing increases the effective input capacitance which reduces the bandwidth and degrades noise performance. Furthermore, biasing requirements of the PD prevent direct DC coupling. In [3], [4], and [5], AC coupling was inserted, as shown in Fig. 1(c), to isolate distinct DC voltage levels. The values of C<sub>C</sub> and R<sub>bias</sub> cannot be made arbitrarily large for bandwidth and PD biasing considerations [3], [6]. Therefore, AC coupling introduces a significantly large lower cutoff frequency  $f_L$  which causes a severe baseline wander in the output signal when the input data include a long run of consecutive identical digits (CIDs) [Fig. 1(d)].

This work leverages the gain and noise advantages of the differential interface and addresses the limitations of AC coupling by proposing 1) a novel PD/TIA interface,

FIGURE 1. Various PD/TIA interfaces (a) Pseudo-differential, (b) DC coupled differential, (c) AC coupled differential, and (d) effect of AC coupling in frequency and time domains. Ios removes the average value of the input current.

2) a novel baseline wander compensation scheme (BWCS), and 3) a cross-coupling technique for bandwidth extension. These modifications significantly improve the performance compared with the conventional structures with no power or silicon area overhead.

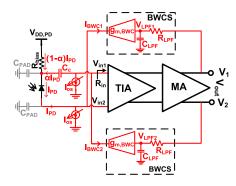

# II. THE PROPOSED PD/TIA INTERFACE WITH BASELINE WANDER COMPENSATION

Fig. 2 shows a block diagram of the proposed photocurrent sensing technique. The cathode and anode terminals of the PD are AC- and DC-coupled to the inputs of the TIA, respectively. Therefore, the low-frequency component of the input current finds a path to the output through the DC-coupled input. A baseline wander compensation scheme (BWCS) extracts the low-frequency component of each output using a low-pass filter  $C_{LPF}$  and  $R_{LPF}$ , creating  $V_{LPF1,2}$  which are converted to currents  $I_{BWC1,2}$  by a transconductance of  $g_{m,BWC}$ . The missing low-frequency information can be restored by adding  $I_{BWC1,2} = g_{m,BWC}V_{LPF1,2}$  to the input. At the PD's cathode node, the current is divided between the PD's bias resistor  $R_{bias}$  and the TIA's input impedance  $R_{in}$ . Therefore, the voltages at the receiver outputs are calculated as

$$V_2 = Z_{TIA}(s) A_{MA}(s) \left( I_{PD} - g_{m,BWC} V_{LPF1} \right)$$

(1.a)

$$V_{1} = -\alpha Z_{TIA}(s) A_{MA}(s) \left[ \frac{I_{PD}s}{(\omega_{ac} + s)} + g_{m,BWC} V_{LPF2} \right]$$

(1.b)

where,  $\alpha = R_{bias}/(R_{bias} + Z_{in})$ ,  $\omega_{ac} = 1/R_{bias}C_{ac}$  is the pole frequency associated with the AC coupling, and  $Z_{TIA}$  (s) and  $A_{MA}$  (s) represent the transfer functions of the TIA and the MA, respectively. Recognizing that  $V_{LPF1} = -V_{LPF2}$  and  $V_{LPF2}$  is low pass filtered version of  $V_2$ , the differential output is

$$V_{1} - V_{2} = -Z_{TIA}(s) A_{MA}(s) I_{PD}$$

$$\cdot \left[ 1 + \frac{\alpha s}{(\omega_{ac} + s)} + \frac{Z_{0}A_{0}(1 + \alpha) g_{m,BWC}}{(1 + s/\omega_{LPF})} \right] (2)$$

FIGURE 2. Block diagram of the proposed PD/TIA interface with BWCS.

where,  $Z_0$ , and  $A_0$  are the midband gains of the TIA and the MA, respectively, and  $\omega_{LPF} = 1/R_{LPF}C_{LPF}$  is the cutoff frequency of the LPF in the BWCS. The baseline wander is eliminated when the square brackets in (2) shrink to  $(1 + \alpha)$ , leading to

$$g_{m,BWC} = \frac{\alpha}{(1+\alpha)Z_0A_0}$$

(3.a)

$$\omega_{LPF} = \omega_{ac} \tag{3.b}$$

More specifically, (3.a) and (3.b) express the *required conditions* for the proposed BWCS to function properly (see Appendix A for detailed proof).

In the proposed frontend, the current sources  $I_{os}$  sink the average value of  $I_{PD}$  to achieve a differential operation.  $I_{os}$  is implemented by an offset compensation loop (OCL) that employs a Mega- $\Omega$  resistor and a Millar-boosted capacitance [7]. Therefore, the OCL can achieve a significantly smaller lower cut-off frequency  $\omega_{ocl}$  compared with that associated with the AC coupling and hence maintaining a negligible baseline wander.

In addition to signal amplification, the MA is required in this work so that the condition in (3.a) is satisfied with a reasonable value of the transconductance  $g_{m,BWC}$ . The overall transfer function  $Z_{FE}(s) = (V_1 - V_2)/I_{PD}$  of the proposed receiver is

$$Z_{FE}(s) = (1+\alpha) \frac{s}{(s+\omega_{ocl})} Z_{TIA}(s) A_{MA}(s) \qquad (4)$$

The lower cutoff frequency is determined by the OCL rather than being determined by the AC coupling. The gain improves by a factor of  $(1 + \alpha)$  compared to the PS-Diff structure in Fig. 1 (a) while avoiding the baseline wonder associated with the AC coupling in Fig. 1 (c). The factor  $(1 + \alpha)$  reaches 2 as  $\alpha$  approaches unity (*i.e.*,  $R_{in} \ll R_{bias}$ ).

The MA is usually designed with a sufficiently wide bandwidth so that the TIA sets the overall bandwidth Considering a typical case where the TIA's input pole  $\omega_{in}$ dominates its output pole, the 3dB bandwidth of the overall front-end in Fig. 2 is set by  $\omega_{in}$

$$\omega_{3dB} = \omega_{in} = \frac{1}{R_{in} \left(2C_D + C_{PAD} + C_{in}\right)} \tag{5}$$

|                                  |                                            |                                            |                                                                          | This work                                                                       |                                           |  |

|----------------------------------|--------------------------------------------|--------------------------------------------|--------------------------------------------------------------------------|---------------------------------------------------------------------------------|-------------------------------------------|--|

|                                  | Single-ended<br>(Reference Design)         | Pseudo-differential                        | Ac-coupled differential                                                  | Asymmetrical<br>differential<br>W/O BWCS                                        | Asymmetrical<br>differential<br>with BWCS |  |

| <sup>1</sup> Gain                | $Z_0A_0$                                   | $Z_0A_0$                                   | $2\alpha Z_0 A_0$                                                        | $(1+\boldsymbol{\alpha})Z_0A_0$                                                 |                                           |  |

| <sup>2</sup> BW                  | $\frac{1}{(C_D + C_{PAD} + C_{in})R_{in}}$ | $\frac{1}{(C_D + C_{PAD} + C_{in})R_{in}}$ | $\frac{1}{(\mathbf{2C}_{D}+C_{PAD}+C_{in})R_{in}}$                       | $\frac{1}{(\mathbf{2C}_{D}+C_{PAD}+C_{in})R_{in}}$                              |                                           |  |

| <sup>3</sup> GBW change          | l<br>Reference design                      | l<br>No change                             | $2\alpha \frac{(C_D + C_{PAD} + C_{in})}{(2C_D + C_{PAD} + C_{in})} > 1$ | $\frac{(1+\boldsymbol{\alpha})(C_D+C_{PAD}+C_{in})}{(2C_D+C_{PAD}+C_{in})} > 1$ |                                           |  |

| Integrated output<br>Noise power | $V_n^2$                                    | $2V_n^2$                                   | $2V_n^2$                                                                 | $2V_n^2$                                                                        |                                           |  |

| <sup>4</sup> SNR change          | 0dB<br><b>Reference design</b>             | -3dB                                       | +3dB                                                                     | +3dB                                                                            |                                           |  |

| $2\pi f_L$                       | ω <sub>ocl</sub>                           | $\omega_{ocl}$                             | $\omega_{ac}$                                                            | $\sim \omega_{ac}/2$                                                            | $\omega_{ocl}$                            |  |

#### TABLE 1. Performance comparison with other PD/TIA interfaces.

<sup>1</sup> The factor  $\alpha$  results from the leakage of the input current in the PD' bias resistor. Therefore,  $\alpha$  approaches unity for  $R_{in} \ll R_{bias}$ .

<sup>2</sup> All differential structures double the PD capacitance seen from each input to ground

<sup>3</sup> The GBW of each structure is divided by that of the reference single-ended design

<sup>4</sup> Output SNR =  $10 \log \frac{(i_{in}gain)^2}{output noise power}$

where,  $C_D$ ,  $C_{PAD}$ , and  $C_{in}$  are PD's capacitance, pad capacitance, and TIA's input capacitance, respectively. The bandwidth of the Ps-Diff receiver Fig. 1 (a) is given by the same expression as in (5) without the factor two in the denominator. Therefore, differential sensing reduces the bandwidth by a factor of  $1 < BW_{\downarrow} = \frac{(2C_D + C_{in} + C_{PAD})}{(C_D + C_{in} + C_{PAD})} < 2$ . A negligible bandwidth reduction (i.e.,  $BW_{\downarrow} = 1$ ) is obtained if  $2C_D \ll (C_{in} + C_{PAD})$ . Considering the gain improvement, a net improvement in the GBW is obtained as long as  $BW_{\downarrow} < (1 + \alpha)$ .

The noise power spectral densities (PSDs)  $V_{n,1}^2$  and  $V_{n,2}^2$  at the frontend outputs are derived as

$$V_{n,1(or\ 2)}^{2} = \left(I_{n,os}^{2} + I_{n,BWC}^{2} + \frac{V_{n,in1(2)}^{2}}{R_{in}^{2}} + \frac{g_{m,BWC}^{2}V_{n,2(1)}^{2}}{\left|1 + s/\omega_{LPF}\right|^{2}}\right)$$

$$|Z_{TIA}(s)A_{MA}(s)|^{2} \tag{6}$$

where  $I_{n,os}^2$  and  $I_{n,BWC}^2$  represent the thermal noise PSDs of the transistors used to realize  $I_{os}$  and  $g_{m,BWC}$ , respectively, and  $V_{n,in}^2/R_{in}^2$  includes the noise contribution from the TIA's core circuitry. The last term in (6) indicates that the proposed BWCS boosts the low-frequency noise. Since  $\omega_{LPF} \ll \omega_{3dB}$ , this boost can be ignored (this assumption is verified by simulation in Section IV-B). Therefore, the differential input-referred noise PSD  $I_{n,in}^2 = \left(V_{n,1}^2 + V_{n,2}^2\right)/|Z_{FE}(s)|^2$ is calculated as

$$I_{n,in}^{2} = \frac{2}{(1+\alpha)^{2}} \left| \frac{s + \omega_{ocl}}{s} \right|^{2} \left( I_{n,os}^{2} + I_{n,BWC}^{2} + \frac{V_{n,in}^{2}}{R_{in}^{2}} \right)$$

(7)

The input-referred noise PSD of the proposed receiver is reduced by a factor of  $(1 + \alpha)^2$  compared to that of the Ps-Diff structure in Fig. 1 (a). As  $\alpha$  approaches unity, this factor approaches four. This translates to a  $10 \log 4 = 6 \text{dB}$  enhancement in the SNR for the same input current.

126860

Table 1 summarizes the performance of the proposed receiver in comparison to other well-known PD/TIA interfaces. Compared to the single-ended and the pseudodifferential receiver, differential current sensing improves the gain by  $2\alpha$  and  $(1 + \alpha)$  in the AC-coupled receiver and the proposed receiver, respectively. The factor  $\alpha$  results from the leakage of the input current in the PD bias resistor. Therefore,  $\alpha$  approaches unity for  $R_{in} \ll R_{bias}$ , achieving a gain improvement of  $2\times$ . The bandwidth, on the other hand, is reduced by a factor of  $1 < BW_{\downarrow} = \frac{(2C_D + C_{in} + C_{PAD})}{(C_D + C_{in} + C_{PAD})} < 2$ . This factor shrinks to 1 (*i.e.*, no bandwidth reduction) for  $2C_D \ll C_{in} + C_{PAD}$ , making this technique more suitable for silicon photonic applications where the PD capacitance can be reduced to 30fF [8], [9]. Even with traditional technologies, net gain-bandwidth product improvement is achieved as long as  $BW_{\downarrow} < (1 + \alpha)$ .

Differential interfaces also double the output noise power. Considering the gain improvement, the proposed receiver improves the output SNR by  $10 \log \frac{(1+\alpha)^2}{2}$ , achieving a maximum improvement of 3dB and 6dB compared to the single-ended and pseudo-differential structures, respectively.

The AC-coupled differential receiver suffers from a high lower cutoff frequency  $\omega_{ac}$  associated with the AC coupling. The elimination of the coupling capacitor at the PD anode terminal and before the incorporation of the proposed BWCS reduces the lower cutoff frequency to approximate  $\omega_{ac}/2$ . The incorporation of the proposed BWCS significantly reduces the lower cutoff frequency to be determined by the OCL as in the single-ended structure instead of being determined by the AC coupling. The OCL usually employs Mega- $\Omega$  resistors and Millar-boosted capacitances. Therefore, the OCL can achieve a significantly smaller lower cut-off frequency  $\omega_{ocl}$ compared to that associated with AC coupling  $\omega_{ac}$ .

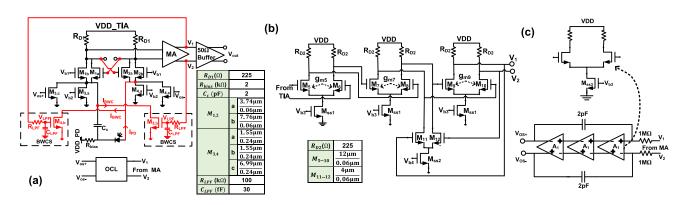

FIGURE 3. Circuit level implementations of the (a) TIA, (b) MA, and (c) OCL and transistor-level realization of the gain stage A1.

# III. CIRCUIT-LEVEL IMPLEMENTATION OF THE PROPOSED RECEIVER

In principle, the proposed sensing technique works with any TIA topology. However, with the common-gate (CG) TIA, the proposed technique has an additional advantage of improving the GBW without being limited by the voltage headroom ([1], Section IV-B). In the proposed TIA in Fig. 3 (a), the cathode and anode terminals of the PD are AC and DC coupled to two single-ended CG-TIAs, respectively. The low-frequency component of an amplified version of the TIA's output is extracted using the low-pass filter  $C_{LPF}$ and  $R_{LPF}$ , creating  $V_{LPF1,2}$ . The tail transistor  $M_3$  is split into three parts:  $M_{3,a}$ ,  $M_{3,b}$ , and  $M_{3,c}$  with gate terminals connected to a biasing voltage  $V_{b2}$  to provide a fixed biasing current,  $V_{LPF}$  to produce the current required for baseline wander compensation, and a voltage  $V_{os}$  produced by the OCL for offset cancellation, respectively. The input transistors  $M_1$  and  $M_2$  are split into two pairs: a cross-coupled pair  $M_{1,a}$ ,  $M_{2,a}$  and another pair  $M_{1,b}$ ,  $M_{2,b}$  with the gate connected to a bias voltage  $V_{b1}$ . The input resistance of the TIA in Fig. 3 (a) is calculated from the small-signal model as

$$R_{in} = \frac{1 + (g_{ds1a} + g_{ds1b} - g_{m1a}) R_{D1}}{g_{m1b} + g_{m1a} + g_{ds1a} + g_{ds1b}}$$

(8)

Therefore, an appropriately sized cross-coupled pair reduces the rate at which  $R_{in}$  increases with  $R_{D1}$  in the presence of the MOSFET short-channel effect [1]. The reduced  $R_{in}$ improves the bandwidth at no power overhead since no auxiliary amplifier is employed as in the RGC-TIA [10].

Fig. 3 (b) shows the transistor-level realization of the MA. Active feedback ( $M_{11}$  and  $M_{12}$ ) is employed for wideband performance. The midband gain of the MA is calculated as [11]

$$A_0 = g_{m5} R_{D2} \frac{g_{m7} g_{m9} R_{D2} R_{D2}}{1 + g_{m9} g_{m11} R_{D2} R_{D2}}$$

(9)

where,  $g_{mx}$  is the transconductance of transistor  $M_x$ .

The MA is usually designed with a bandwidth equal to the targeted data rate. Therefore, the TIA sets the receiver's overall bandwidth. The OCL in Fig. 3 (c) senses the difference between the DC levels at the MA outputs and returns a feedback voltage  $V_{os}$  which is then converted into current  $I_{os}$  by the transconductance of  $M_{3,c}$ . The average value of the input current is removed by subtracting  $I_{os}$  at the input node, as shown in Fig. 3 (a). The OCL employs a Millerboosted 2pF capacitor and a 1M $\Omega$  polysilicon resistor. An  $f_L < 0.15$ MHz is achieved as a tradeoff between the on-chip area and a tolerable baseline wander.

The output buffer in Fig. 3 (a) is a simple differential pair with a load resistor of  $75\Omega$ , chosen as a trade-off between signal attenuation and matching with  $50\Omega$  measurement equipment.

## **IV. PERFORMANCE VALIDATION AND COMPARISON** *A. DESIGN CONSIDERATIONS*

The resistor  $R_{LPF}$  in the BWCS in Fig. 3 (a) must be sufficiently large to prevent  $C_{LPF}$  from loading the output of the MA. Once  $R_{LPF}$  is set,  $C_{LPF}$  is calculated as  $C_{LPF} = C_c R_{bias}/R_{LPF}$  to satisfy the condition in (3.b). The transconductance in the BWCS given by (3.a) is implemented by  $M_{3,b}$  and  $M_{4,b}$  and is calculated in term of circuit parameters as

$$g_{m,BWC} = \frac{\alpha \left(1 + g_{m9}g_{m11}R_{D2}R_{D2}\right)}{\left(1 + \alpha\right)g_{m5}g_{m7}g_{m9}R_{D1}R_{D2}R_{D2}R_{D2}}$$

(10)

Following (7), the input-referred noise PSD is calculated in terms of circuit parameters as

$$I_{n,in}^2 = \frac{2 \times 4kT}{(1+\alpha)^2} \left| \frac{s + \omega_{ocl}}{s} \right|^2 \left( \gamma g_{m,M3} + \frac{1}{R_{D1}} \right)$$

(11)

where  $\gamma$  is the excess noise factor and  $g_{m,M3} = g_{m,M3,a} + g_{m,M3,b} + g_{m,M3,c}$ . The obtained noise performance is similar to that of the CG-TIA [1] but reduced by a factor  $(1 + \alpha)^2$ . The noise of  $R_{D1}$  and  $M_{3a-c}$  directly refers to the input. Therefore, for a given bias current,  $M_{3a-c}$  are realized by long-channel transistors (to reduce  $\gamma$ ) and their overdrive voltages are maximized to improve the noise performance.

The TIA's input impedance calculated from the circuit parameters using (8) is approximately  $60\Omega$ . Therefore,

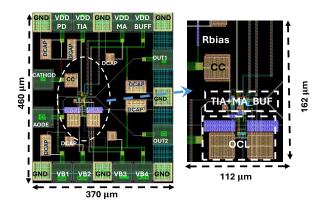

FIGURE 4. Layout of the proposed receiver.

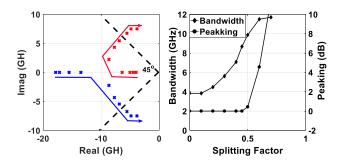

**FIGURE 5.** Impact of sizing the cross-coupled pair on (a) pole locations (b) bandwidth and peaking. The dash lines in Fig. 5 (a) make  $+45^{\circ}$  and  $-45^{\circ}$  with the horizontal axis. Therefore, the intersection of these lines with the root locus identifies the location of the Butterworth poles.

$R_{bias}$  needs to be much greater than this value to achieve  $\alpha = 1$  and hence maximum performance improvement. The maximum value of  $R_{bias}$ , on the other hand, is limited by the PD biasing. The PD and the TIA are power by  $V_{DD,PD}$  and  $V_{DD,TIA}$ , respectively (see the layout in Fig. 4). The latter is set by the CMOS technology node used in this work to 1V. Therefore, the anode terminal of the PD is DC-biased at approximately 0.3V (the required drain-tosource voltage of the tail current source). Therefore, a proper reverse bias of the PD can be maintained by setting  $V_{DD,PD}$ , for example, to 2.5V. Therefore, setting re  $R_{bias}$  to  $2k\Omega$ is sufficiently low to avoid significant DC voltage drop and maintain a proper biasing for the PD up to an input current of  $500\mu A_{pp}$  [3]. The selected value of  $R_{bias}$  along with the simulated input impedance leads to a calculated  $\alpha$ of 0.97.

### **B. POST-LAYOUT SIMULATION RESULTS**

Fig. 4 shows the layout of the proposed receiver in TSMC 65 nm CMOS technology. Post-layout simulations are performed with voltage supply and PD capacitance of 1 V and 200 fF, respectively. Pads contribute a 40 fF capacitance from each input node to the ground. Bonding wires are modeled by 0.5nH inductance. The TIA, the MA, and the OCL dissipate DC powers of 2.02mW, 6.04mW, and 3.05mW, respectively.

The effect of cross-coupling on the TIA's bandwidth is investigated in Fig. 5. A splitting factor is defined as

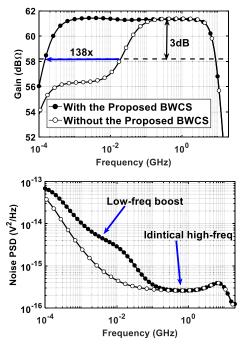

**FIGURE 6.** Post layout simulated (a) amplitude responses and (b) output noise PSD. Simulations are performed with and without the proposed BWCS under fixed power dissipation constraint.

$X_f = W_{M1a}/(W_{M1a} + W_{M1b})$ . Fig. 5 (a) shows that at  $X_f = 0$ , the TIA acts as a conventional CG-TIA with two real distinct poles. As  $X_f$  increases, the two poles move toward each other and become identical at  $X_f = 0.28$ . As  $X_f$  continues to increase, the two poles become complex and may travel to the right-hand side at a very high  $X_f$ . A splitting factor of  $X_f = 0.41$  is chosen for a Butterworth response. At this value of  $X_f$ , Fig. 5 (a) shows that the TIA achieves a bandwidth of 8.6 GHz, achieving a bandwidth extension of 2.4× compared with the case of  $X_f = 0$ . Fig. 5 (b) also shows that the proposed TIA exhibits a negligible peaking in the amplitude response up to  $X_f = 0.5$ , then the peaking starts to rapidly accumulates.

To investigate the impact of the proposed BWCS on the performance, the proposed receiver is simulated with and without the proposed BWCS. When the proposed BWCS is disabled, the gate terminals of  $M_{3b}$  and  $M_{4b}$  in Fig. 3 (a) are connected to a proper bias voltage to attain a constant power dissipation. The simulated amplitude responses in Fig. 6 (a) demonstrate that the incorporation of the proposed BWCS significantly reduces  $f_L$  from 20.4MHz to 0.151MHz. The figure also shows that the proposed receiver achieves a gain and a bandwidth of 61.3dB $\Omega$  and 8.5GHz, respectively. Fig. 6 (b) shows that the proposed BWCS boosts the output noise PSD at frequencies less than 200MHz. The integrated output rms noise voltage  $V_{n,rms}$  with and without the BWCS is 2.17mV and 2.15mV, respectively. This minor increases in  $V_{n,rms}$  demonstrates that the BWCS has a negligible impact on the noise performance and justifies our analysis in (6).

| TABLE 2. | Performance | comparison | with | CMOS | TIAs. |  |

|----------|-------------|------------|------|------|-------|--|

|----------|-------------|------------|------|------|-------|--|

|                                  | $[15]^2$  | [16] <sup>2</sup> | [17] <sup>1</sup>     | [18] <sup>1</sup> | [19] <sup>1</sup> | This                 | work1  |

|----------------------------------|-----------|-------------------|-----------------------|-------------------|-------------------|----------------------|--------|

| CMOS tech. (nm)                  | 65        | 55LP              | 65                    | 180               | 180               | 65                   |        |

| Topology                         | RGC       | RGC               | CC-CG                 | RGC               | SF                | CC-CG                |        |

| Output type                      | Diff      | Diff              | Ps-Diff               | SE                | Diff              | Diff                 |        |

| Input coupling                   | AC        | DC comp.          | DC                    | DC                | DC                | AC/DC+BWCS           |        |

| $f_L$ (MHz)                      | 30        | 0.3               | 0.0074                | NA                | NA                | 0.15                 |        |

| Inductor                         | Yes       | No                | No                    | No                | Yes               | No                   |        |

| PD Cap. (fF)                     | 200       | 200               | 200                   | 250               | 200               | 200                  |        |

| Supply (V)                       | 3         | 2-2.7             | 1.2                   | 1.8               | 3.3               | 1                    |        |

| Architecture                     | TIA+Balun | TIA+Balun         | TIA+MA                | TIA only          | TIA+MA            | TIA                  | TIA+MA |

| Gain (dBΩ)                       | 62        | 69                | 73.1                  | 59.5              | 68.4              | 51.98                | 61.3   |

| BW (GHz)                         | 9         | 9                 | 10.2                  | 3.7               | 6                 | 9.19                 | 8.5    |

| Noise (µA <sub>rms</sub> )       | NA        | NA                | NA                    | NA                | 0.56              | 1.87                 |        |

| Eq. Input noise $(pA/\sqrt{Hz})$ | 30        | 15                | 30.5 up to<br>10.2GHz | NA                | 7.2               | 20.11 up to<br>16GHz |        |

| DC Power <sup>3</sup> (mW)       | 10        | 15.7              | 9.6                   | 3                 | 83                | 2.02                 | 11.11  |

| Active Area mm <sup>2</sup>      | 0.08      | 0.07              | 0.043                 | 0.004             | NA                | 0.0181               |        |

NA: Not Available, SE: single-ended, SF: shunt-feedback CC: cross-coupled, and DC comp.: DC compensation

<sup>1</sup>Post-layout simulation <sup>2</sup>Electrically measured S-parameter combined with a PD model.

<sup>3</sup>excluding the output buffer

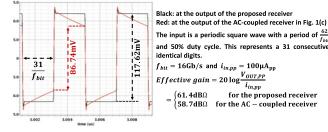

FIGURE 7. Post-layout simulated transient differential output voltage.

The proposed PD/TIA interface is compared with other interfaces in Fig. 1. The comparison is performed under a fixed power constraint. The Ps-Diff structure in Fig. 1 (a) achieves a gain, bandwidth, and  $V_{n,rms}$  of 56.33dB $\Omega$ , 12.42GHz, and 2.052mV, respectively. That is, the proposed interface improves the gain, the GBW, and the SNR by 5dB, 1.37× and 5.55dB, respectively, compared to the structure in Fig. 1 (a). The performance has significantly improved but did not reach the theoretical limit in Table 1. This is attributed to the top/bottom plate parasitic of capacitor  $C_C$  that shunts the photocurrent which reduces the signal current flowing into the TIA and lowers the TIA gain at high frequencies.

The AC-coupled architecture in Fig. 1 (c) achieves an  $f_L$  of 31.57MHz that is 209× higher than that of the proposed receiver. For accurate comparison with the AC-coupled receiver in Fig. 1 (c), the *effective* gain is calculated from the transient simulations in Fig. 7 [12], [13]. The proposed BWCS compensates for the signal drift after long runs of CIDs, improving the effective gain by 2.7 dB. The proposed receiver achieves an average input noise  $i_{n,av}$  of 20.11pA/ $\sqrt{\text{Hz}}$ . Fig. 8 shows the post-layout simulated

**FIGURE 8.** 16 Gb/s post-layout simulated eye diagrams at (a) at the sensitivity level  $(i_{in}^{pp} = 26\mu A_{pp})$  and (b) at 4× the sensitivity level  $(i_{in}^{pp} = 104\mu A_{pp})$ .

eye diagram at a data rate of 16 Gb/s various amplitudes, demonstrating the linearity of the proposed receiver at high input current amplitudes.

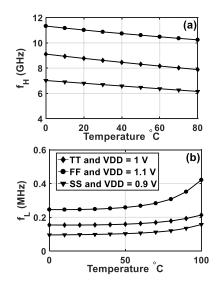

Fig. 9 shows the performance of the proposed receiver over process, voltage, and temperature (PVT) variations. The worst case higher cutoff frequency (6.12GHz) is sufficiently large to support the targeted 16Gb/s data rate [12], [13], [14]. The worst-case lower cutoff frequency (0.42MHz) is  $71 \times$  lower than that associated with AC coupling at its typical operating conditions. The proposed receiver shows a negligible amplitude peaking over all PVT conditions.

Table 2 shows that the proposed receiver achieves differential operation with comparable power to [15] and [16] that employ active balun and DC current compensation. Unlike [15] and [16], the presented receiver operates at the technology's nominal supply voltage. More importantly, the proposed BWCS significantly reduces  $f_L$  compared to the AC-coupled receiver in [15]. The proposed differential receiver achieves better noise than the Ps-Diff receiver in [17] which is implemented in the same technology

**FIGURE 9.** Performance over PVT variations (a) higher cutoff frequency and (b) lower cutoff frequency.

and employs a cross-coupled technique. Despite the differential connection that significantly increases the input capacitance, the proposed TIA alone achieves a higher GBW than the TIA in [18] that employs a modified RGC topology. The excellent noise performance of the differential receiver in [19] is achieved at the price of increased power dissipation resulting from stacking two single-ended receivers in the voltage domain while the proposed receiver achieves a good noise performance with a reasonable power dissipation.

#### **V. CONCLUSION**

A differential PD/TIA interface with a baseline compensation scheme (BWCS) has been presented. To the best of the authors' knowledge, the BWCS is used in optical receivers for the first time in this work. The presented receiver leverages the gain and noise advantages of differential connection and improves the gain-bandwidth product while avoiding the limitations of AC coupling at no power or silicon area overhead. The presented receiver operates at the technology's nominal supply voltage and requires no special design considerations. Post-layout simulation results demonstrate the feasibility of the proposed BWCS. The proposed interface has the potential to double the gain and improve the SNR by 6dB compared to the pseudodifferential interface.

### APPENDIX A

#### **REQUIRED CONDITIONS FOR THE PROPOSED BWCS**

This Appendix provides a detailed proof for the required conditions for the proposed BWCS to function properly. Starting from (1.a), the differential output is written as

$$V_1 - V_2 = -Z_{TIA}(s) A_{MA}(s) \left[ \frac{\alpha I_{PD}s}{(\omega_{ac} + s)} + \alpha g_{m,BWC} V_{LPF2} + I_{PD} - g_{m,BWC} V_{LPF1} \right]$$

(A.1)

Substituting

$$V_{LPF2} = \frac{Z_0 A_0 I_{PD}}{(1 + s/\omega_{LPF})} = -V_{LPF1}$$

results in

$$V_1 - V_2 = -Z_{TIA}(s) A_{MA}(s) I_{PD} \left[ 1 + \frac{\alpha s}{(\omega_{ac} + s)} + \frac{(1 + \alpha) Z_0 A_0 g_{m,BWC}}{1 + s/\omega_{LPF}} \right]$$

(A.2)

To eliminate the baseline wander, the square brackets in (A.2) must equal  $(1 + \alpha)$ . Therefore,

$$\left[1 + \frac{\alpha s}{(\omega_{ac} + s)} + \frac{(1 + \alpha) Z_0 A_0 g_{m,BWC}}{1 + s / \omega_{LPF}}\right] = 1 + \alpha \quad (A.3)$$

Which can be reduced to

$$\frac{\alpha s^{2}}{\omega_{LPF}} + \left[ (1+\alpha) Z_{0} A_{0} g_{m,BWC} + \alpha \right] s$$

$$+ (1+\alpha) Z_{0} A_{0} g_{m,BWC} \omega_{ac}$$

$$= \frac{\alpha s^{2}}{\omega_{LPF}} + \alpha \left( 1 + \frac{\omega_{ac}}{\omega_{LPF}} \right) s + \alpha \omega_{ac} \qquad (A.4)$$

The  $s^2$  terms cancel each other. Comparing the coefficients of  $s^0$  directly leads to

$$g_{m,BWC} = \frac{\alpha}{(1+\alpha)Z_0A_0} \tag{A.5}$$

The above equation represents the first condition in (3.a). Using this result to compare the coefficients of *s* leads to

$$(1+\alpha) Z_0 A_0 g_{m,BWC} + \alpha = \alpha \left( 1 + \frac{\omega_{ac}}{\omega_{LPF}} \right)$$

$$\alpha + \alpha = \alpha \left( 1 + \frac{\omega_{ac}}{\omega_{LPF}} \right)$$

Leading to

$$\omega_{ac} = \omega_{LPF} \tag{A.6}$$

The above equation represents the second condition in (3.b).

#### REFERENCES

- B. Razavi, Design of Integrated Circuits for Optical Communications. New York, NY, USA: McGraw-Hill, 2003.

- [2] D. Li, G. Minoia, M. Repossi, D. Baldi, E. Temporiti, A. Mazzanti, and F. Svelto, "A low-noise design technique for high-speed CMOS optical receivers," *IEEE J. Solid-State Circuits*, vol. 49, no. 6, pp. 1437–1447, Jun. 2014.

- [3] C. L. Schow, F. E. Doany, A. V. Rylyakov, B. G. Lee, C. V. Jahnes, Y. H. Kwark, C. W. Baks, D. M. Kuchta, and J. A. Kash, "A 24-channel, 300 Gb/s, 8.2 pJ/bit, full-duplex fiber-coupled optical transceiver module based on a single 'Holey," *J. Lightw. Technol.*, vol. 29, no. 4, pp. 542–553, Feb. 5, 2011.

- [4] A. V. Rylyakov, C. L. Schow, B. G. Lee, F. E. Doany, C. W. Baks, and J. A. Kash, "Transmitter predistortion for simultaneous improvements in bit rate, sensitivity, jitter, and power efficiency in 20 Gb/s CMOSdriven VCSEL links," *J. Lightw. Technol.*, vol. 30, no. 4, pp. 399–405, Feb. 9, 2012.

- [5] E. Temporiti, G. Minoia, M. Repossi, D. Baldi, A. Ghilioni, and F. Svelto, "A 3D-integrated 25Gbps silicon photonics receiver in PIC25G and 65nm CMOS technologies," in *Proc. 40th Eur. Solid State Circuits Conf. (ESSCIRC)*, Venice Lido, Italy, Sep. 2014, pp. 131–134.

- [6] K. Lakshmikumar, "A 7 pA/ √Hz asymmetric differential TIA for 100Gb/s PAM-4 links with -14dBm optical sensitivity in 16nm CMOS," in *Proc. IEEE Int. Solid-State Circuits Conf.*, May 2023, pp. 1–29.

- [7] J. Proesel, C. Schow, and A. Rylyakov, "25Gb/s 3.6pJ/b and 15Gb/s 1.37pJ/b VCSEL-based optical links in 90nm CMOS," in *Proc. IEEE Int. Solid-State Circuits Conf.*, Feb. 2012, pp. 418–420.

- [8] S. Saeedi and A. Emami, "A 25Gb/s 170μW/Gb/s optical receiver in 28nm CMOS for chip-to-chip optical communication," in *Proc. IEEE Radio Freq. Integr. Circuits Symp.*, Jun. 2014, pp. 283–286.

- [9] S. Saeedi, S. Menezo, G. Pares, and A. Emami, "A 25 Gb/s 3D-integrated CMOS/Silicon-photonic receiver for low-power high-sensitivity optical communication," *J. Lightw. Technol.*, vol. 34, no. 12, pp. 2924–2933, Jun. 9, 2016.

- [10] S. M. Park and H.-J. Yoo, "1.25-Gb/s regulated cascode CMOS transimpedance amplifier for gigabit Ethernet applications," *IEEE J. Solid-State Circuits*, vol. 39, no. 1, pp. 112–121, Jan. 2004.

- [11] S. Galal and B. Razavi, "10-Gb/s limiting amplifier and laser/modulator driver in 0.18-µm CMOS technology," *IEEE J. Solid-State Circuits*, vol. 38, no. 12, pp. 2138–2146, Dec. 2003.

- [12] D. Abdelrahman and G. E. R. Cowan, "Noise analysis and design considerations for equalizer-based optical receivers," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 66, no. 8, pp. 3201–3212, Aug. 2019.

- [13] B. Radi, D. Abdelrahman, O. Liboiron-Ladouceur, G. Cowan, and T. C. Carusone, "Optimal optical receivers in nanoscale CMOS: A tutorial," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 69, no. 6, pp. 2604–2609, Jun. 2022.

- [14] D. Abdelrahman and M. Atef, "Accurate characterization for continuoustime linear equalization in CMOS optical receivers," *IEEE Access*, vol. 10, pp. 129019–129028, 2022.

- [15] R. Costanzo and S. M. Bowers, "A current reuse regulated cascode CMOS transimpedance amplifier with 11-GHz bandwidth," *IEEE Microw. Wireless Compon. Lett.*, vol. 28, no. 9, pp. 816–818, Sep. 2018.

- [16] R. Costanzo and S. M. Bowers, "A 10-GHz bandwidth transimpedance amplifier with input DC photocurrent compensation loop," *IEEE Microw. Wireless Compon. Lett.*, vol. 30, no. 7, pp. 673–676, Jul. 2020.

- [17] W. Wu, L. Zhang, and Y. Wang, "A 20-Gb/s CMOS cross-coupled dual-feedback loop transimpedance amplifier," in *Proc. IEEE Int. Symp. Circuits Syst. (ISCAS)*, Seville, Spain, Oct. 2020, pp. 1–5.

- [18] A. Kari Dolatabadi and M. Jalali, "Power and area efficient transimpedance amplifier driving large capacitive loads based on modified RGC structure," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 67, no. 10, pp. 1740–1744, Oct. 2020.

- [19] W. Huang, X. Liu, Y. Shi, D. Li, B. Zhang, X. Gui, and L. Geng, "A lownoise stacked differential optical receiver in 0.18-μm CMOS," in *Proc. IEEE Int. Midwest Symp. Circuits Syst. (MWSCAS)*, Lansing, MI, USA, Aug. 2021, pp. 890–893.

**DIAAELDIN ABDELRAHMAN** received the B.Sc. and M.Sc. degrees in electrical engineering, electronics, and communications from Assiut University, Egypt, in 2010 and 2015, respectively, and the Ph.D. degree in electrical and computer engineering from Concordia University, Montreal, QC, Canada, in 2021. He is currently an Assistant Professor with Assiut University, Assiut, Egypt. He has authored and co-authored several scientific publications. His current research interest includes ted circuit for active University.

high-performance integrated circuits for optical links.

**MOHAMED ATEF** (Senior Member, IEEE) received the B.Sc. and M.Sc. degrees in electrical engineering, electronics, and communications from Assiut University, Egypt, in 2000 and 2005, respectively, and the Ph.D. degree from the Institute of Electrodynamics, Microwave and Circuit Engineering, Vienna University of Technology, in 2010. From 2006 to 2007, he received a Research Scholarship from the Department of Microelectronics, Czech Technical

University in Prague, where he worked on the improvement of quantum dot optical properties. He was a Postdoctoral Researcher with Vienna University of Technology, until 2012. He visited the School of Microelectronics, Shanghai Jiao Tong University, China, from 2015 to 2017. He has been an Associate Professor with Assiut University, since 2016. In 2020, he joined the Electrical Engineering Department, United Arab Emirates University, United Arab Emirates, where he is currently an Associate Professor. He is the author of two books Optical Communication over Plastic Optical Fibers: Integrated Optical Receiver Technology and Optoelectronic Circuits in Nanometer CMOS Technology. He is the author and co-author of more than 85 scientific publications. His research interests include optoelectronic integrated circuits, optical sensing, and biomedical circuits and systems. He has been a member of the Biomedical and Life Science Circuits and Systems Technical Committee, since 2018. He received the State Encouragement Award in Advanced Technological Sciences Serving the Engineering Sciences from the Egyptian Academy of Scientific Research and Technology (ASRT), in 2018. He served as a TPC Member for many IEEE conferences, such as a Lead Editor for Sensors Journal special issue, from 2019 to 2020; a Guest Editor for several IEEE TRANSACTIONS ON BIOMEDICAL CIRCUITS AND SYSTEMS special issues; an Associate Editor for IEEE TRANSACTIONS ON BIOMEDICAL CIRCUITS AND SYSTEMS, from 2020 to 2023; and has been an Associate Editor for IEEE SENSORS JOURNAL, since 2024.