Received 13 July 2024, accepted 24 July 2024, date of publication 30 July 2024, date of current version 9 August 2024. *Digital Object Identifier* 10.1109/ACCESS.2024.3435691

# **RESEARCH ARTICLE**

# Improvement of Thermal Characteristics and On-Current in Vertically Stacked Nanosheet FET by Parasitic Channel Height Engineering

# YOUNG SUH SONG<sup>1</sup>, (Member, IEEE), HYUNWOO KIM<sup>2</sup>, (Member, IEEE), AND JANG HYUN KIM<sup>3</sup>, (Member, IEEE)

<sup>1</sup>Department of Electrical and Computer Engineering, Seoul National University, Seoul 08826, Republic of Korea

<sup>2</sup>Department of Electrical and Electronics Engineering, Konkuk University, Seoul 05029, Republic of Korea

<sup>3</sup>Department of Electrical and Computer Engineering, Ajou University, Suwon 16499, Republic of Korea

Corresponding authors: Hyunwoo Kim (kimhyunwoo@konkuk.ac.kr) and Jang Hyun Kim (janghyun@ajou.ac.kr)

This work was supported in part by the National Research Foundation of Korea (NRF) grant funded by Korean Government (MSIT) under Grant NRF-2022R1A2C1093201 and Grant RS-2024-00406652; and in part by the Technology Innovation Program [Development of eGaN HEMT Device Advancement Technology Using GaN Standard Modeling Technology (ASM)] funded by the Ministry of Trade, Industry and Energy (MOTIE) under Grant 20026440.

**ABSTRACT** For improving thermal characteristics and on-current ( $I_{ON}$ ) in vertically stacked nanosheet field-effect transistor (NSFET), the effect of parasitic channel height ( $H_{parasitic}$ ) on thermal and electrical characteristics has been investigated. By increasing  $H_{parasitic}$ , it has been demonstrated that the maximum lattice temperature ( $T_{max}$ ) could be improved from 428 K to 416 K, and thermal resistance ( $R_{TH}$ ) could be improved by 9.3 %. This thermal improvement has been achieved since the increased parasitic channel height could lead to the formation of effective heat sink. The relationship between  $H_{parasitic}$  and the thermal characteristics of the device has rarely been addressed in previous studies, and we have explored this with a novel approach. In addition, regarding  $I_{ON}$ , it has been demonstrated that the proposed device structure could have 19.7 % higher  $I_{ON}$ , due to the increased fringing field effect. The origin and benefits of these thermal and electrical improvement have been thoroughly investigated through Synopsys Sentaurus three-dimensional (3D) technology computer-aided design (TCAD) simulation tool. The proposed NSFET structure is expected to be very strategic for the next-generation IC chip design with increased performance (from  $I_{ON}$  improvement) and enhanced reliability (from thermal improvement), at the same time.

**INDEX TERMS** Nanosheet field-effect transistor (NSFET), on-current ( $I_{ON}$ ), maximum lattice temperature ( $T_{max}$ ), thermal resistance ( $R_{TH}$ ).

#### I. INTRODUCTION

Continuous downscaling of the semiconductor devices has steadily required the reduction in the dimensions of transistors such as gate length [1], [2], [3]. However, as gate length decreases, a couple of undesirable short-channel effects

The associate editor coordinating the review of this manuscript and approving it for publication was Wenxin Liu<sup>(D)</sup>.

(SCEs) concomitantly arise, posing challenges in maintaining good electrostatics [4]. To address this issue, several threedimension (3D) device structures such as fin field-effect transistor (FinFET), gate-all-around (GAA) MOSFET, and nanosheet field-effect transistor (NSFET) have been proposed to enhance gate controllability [5], [6], [7], [8], [9]. Among these 3D structures, since gate fully encompasses the sheet-shaped channel, NSFET shows excellent electrostatic

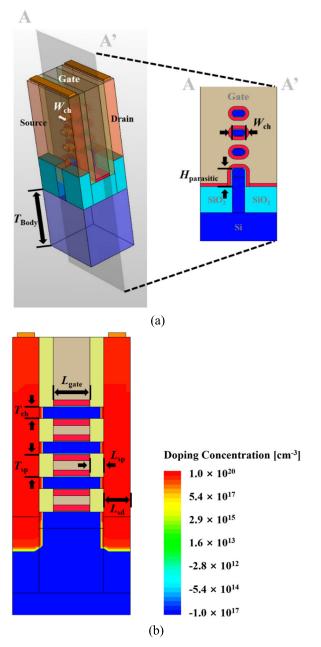

**FIGURE 1.** (a) 3-D schematic diagram and cross-sectional view of the proposed vertically stacked NSFET with the explanation of the parameter  $H_{\text{parasitic}}$ , and (b) Another cross-sectional view of the proposed vertically stacked NSFET with various parameters.

characteristics, providing superior channel control, higher on-current ( $I_{ON}$ ), and better circuit-design flexibility from flexible channel width design [10], [11], [12].

In addition to this structural development, NSFET has been steadily developed with the vertically stacked structure, since the vertically stacked NSFET enables an increased number of channels, consequently providing higher  $I_{ON}$ . Specifically, the vertically stacked NSFET could enable 2-3 times higher  $I_{ON}$ , compared to single channel NSFET [13], [14]. Due to this  $I_{ON}$  advantage, it has been widely accepted that the vertically stacked NSFET could be promising

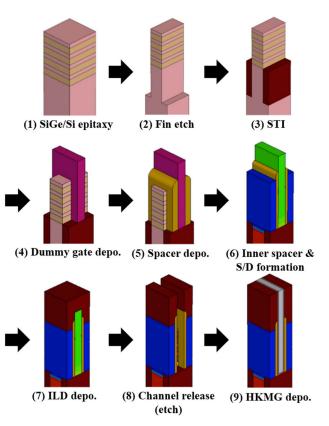

**FIGURE 2.** Illustration describing step-by-step fabrication flow of the proposed device [17]. The abbreviations of STI / depo. / ILD / HKMG stand for shallow trench isolation (STI) / deposition (depo.) / interlayer dielectric (ILD) / high- $\kappa$  metal gate (HKMG), respectively.

candidate for next-generation high performance (HP) semiconductor applications with the improved device/circuit performance [13], [14].

However, even though the vertically stacked NSFET has better gate controllability and higher on-current, its thermal characteristics are inferior to those of FinFET and single channel NSFET [13]. This is because the gate dielectric with low thermal conductivity completely encases the silicon channels, thereby making it hard to dissipate the generated heat from the channels [13]. This issue is exacerbated by the use of hafnium oxide (HfO<sub>2</sub>), which has a thermal conductivity 2–3 times lower than that of silicon dioxide (SiO<sub>2</sub>) [7], [12].

In addition, in the vertically stacked NSFET, its vertically stacked structure even makes it difficult to dissipate the heat generated from multiple channels as well. Consequently, this heat issue, known as self-heating effects (SHEs), simultaneously degrades the performance and reliability of the vertically stacked NSFET [13], [14].

When it comes to performance degradation,  $I_{ON}$  decreases due to the increased temperature caused by SHE.  $I_{ON}$  degradation from SHE is particularly of great importance, since a decrease in  $I_{ON}$  directly impacts a couple of performances at the circuit level [13], [14], [15], [16]. For instance,  $I_{ON}$  decrease at the transistor level could worsen the delay

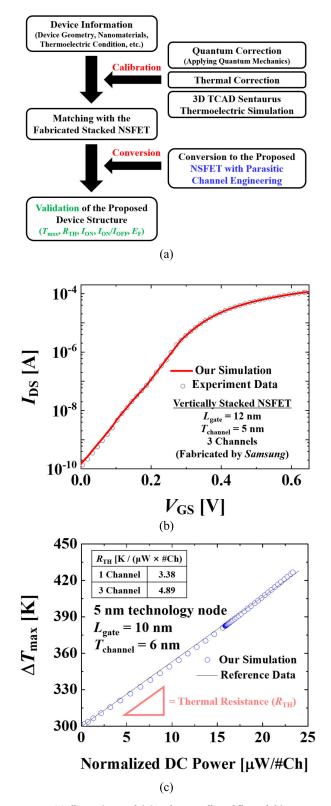

**FIGURE 3.** (a) Illustration explaining the overall workflow of this research, (b) Calibration result with electrical characteristics [23], and (c) Calibration result with thermal characteristics [20].

in a three-stage ring oscillator (RO3), inverter delay, and resistance–capacitance (RC) delay, at the same time. For

these reasons, addressing the SHE issue is crucial not only at the transistor level but also at the circuit level.

In order to improve the thermal characteristics of the vertically stacked NSFET, several approaches have been proposed by previous studies. For example, Tayal et al. have utilized titanium dioxide (TiO<sub>2</sub>) as gate dielectric, instead of HfO<sub>2</sub> [13]. However, TiO<sub>2</sub> has lower bandgap (3.0-3.2 eV), compared to HfO<sub>2</sub> (5.3-5.7 eV). Therefore, the gate current ( $I_{gate}$ ) might be significantly increased in the vertically stacked NSFET shown in previous research [13].

On the other hand, Kim et al. have utilized two different materials for spacer [9]. For example, they have utilized HfO<sub>2</sub> as inner spacer and SiO<sub>2</sub> as outer spacer. However, from these dual- $\kappa$  spacer structure, the device dimension should be increased accordingly, which might be significantly undesirable for device integration.

In this regard, we have explored a novel approach to improve the thermal characteristics in vertically stacked NSFETs without increasing the device size as in previous approach [9], or increasing the gate current as in previous approach [13]. Specifically, we have focused on the fact that the fabrication of the vertically stacked NSFET has concomitantly led to the formation of parasitic channel at the bottom of the main channels [15], [16] and the parasitic channel height ( $H_{\text{parasitic}}$ ) could affect the overall electrical characteristics and thermal characteristics of the transistor.

Therefore, we have investigated into the effect of  $H_{\text{parasitic}}$  on the electrical and thermal characteristics of the vertically stacked NSFET, and consequently demonstrated that it is possible to design the vertically stacked NSFET with decreased maximum lattice temperature ( $T_{\text{max}}$ ), decreased thermal resistance ( $R_{\text{TH}}$ ), and increased  $I_{\text{ON}}$ , with the help of parasitic channel height engineering. Importantly, the connection between  $H_{\text{parasitic}}$  and the thermal characteristics of the device has seldom been explored in earlier studies, and we have investigated this using a novel approach.

This paper is organized as follows. To begin with, careful calibration has been performed both electrically and thermally, so that more accurate and precise research could be conducted. Then, thermal characteristics such as  $T_{\text{max}}$  and  $R_{\text{TH}}$  have been investigated by analyzing the location of heat dissipation path. Thereafter, the improvement of electrical characteristics such as  $I_{\text{ON}}$  has been analyzed. Finally, potential benefits of the overall improvement of thermal and electrical characteristics in the proposed vertically stacked NSFET have been discussed.

#### **II. DEVICE STRUCTURE AND CALIBRATION PROCESS**

Fig. 1 shows the schematic structure of the vertically stacked NSFET. This vertically stacked NSFET structure could be fabricated through the gate-last fabrication process, and the detailed fabrication steps could be found in Fig. 2 [17]. For the detailed specification of this structure, device parameters at 3-nm technology node presented in the International Roadmap for Devices and Systems (IRDS, previously named as ITRS) have been utilized [18].

TABLE 1. Model parameters and the corresponding values.

| Symbol                    | Description                                      | Value | Unit <sup>a</sup> |

|---------------------------|--------------------------------------------------|-------|-------------------|

| $L_{\text{gate}}$         | gate length                                      | 16    | nm                |

| $L_{\rm sp}$              | spacer length                                    | 6     | nm                |

| EOT                       | equivalent oxide thickness                       | 1     | nm                |

| $T_{\rm HfO2}$            | hafnium oxide thickness                          | 2.7   | nm                |

| $T_{\rm SiO2}$            | silicon dioxide thickness<br>(interfacial layer) | 0.5   | nm                |

| $T_{\rm Body}$            | body silicon thickness                           | 800   | nm                |

| T <sub>ch</sub>           | channel thickness                                | 5     | nm                |

| $H_{\text{parasitic}}$    | parasitic channel height                         | 5-19  | nm                |

| $W_{\rm ch}$              | channel width                                    | 10    | nm                |

| $\kappa_{\rm HfO2}$       | HfO <sub>2</sub> thermal conductivity            | 0.27  | W/(K×m)           |

| $\kappa_{SiO2}$           | SiO <sub>2</sub> thermal conductivity            | 0.84  | W/(K×m)           |

| $\kappa_{\text{channel}}$ | silicon thermal conductivity (channel)           | 8.9   | W/(K×m)           |

| $\kappa_{sd}$             | silicon thermal conductivity (source/drain)      | 7.9   | W/(K×m)           |

| $\kappa_{\text{gate}}$    | gate metal thermal conductivity                  | 175   | $W/(K \times m)$  |

<sup>a</sup>The following units are the same as international system of units (SI) for electrical and material engineering [17]; nm = nanometer, W = Watt, K = Kelvin, m = meter.

#### A. STRUCTURE OF THE VERTICALLY STACKED NSFET

Fig. 1(a) and Fig. 1(b) illustrate the detailed structure of the vertically stacked NSFET. The gate length  $(L_{gate})$  is designed with 16 nm [18]. Regarding silicon (Si) channel, channel width  $(W_{ch})$  and channel thickness  $(T_{ch})$  are set as 10 nm and 5 nm, respectively. In addition, the gate stack is composed of 2.8 nm-thick hafnium oxide (HfO<sub>2</sub>) layer and 0.5 nm-thick interfacial silicon dioxide (SiO<sub>2</sub>) layer, so that the equivalent oxide thickness (EOT) could be designed as 1 nm [18]. Moreover, doping concentration for source/channel/drain regions are set as  $1 \times 10^{20}$  /  $1 \times 10^{17}$  /  $1 \times 10^{20}$  cm<sup>-3</sup>, respectively. The thermal conductivities of 0.27, 0.84, 8.9, 7.9, 175 W/(K $\times$ m) are applied for HfO<sub>2</sub> [19], SiO<sub>2</sub> [19], channel [20], source and drain [20], gate metal [21], respectively. This structure has been investigated using Synopsys Sentaurus three-dimensional (3D) technology computer-aided design (TCAD) simulation [22]. The detailed parameters could be found in Table 1.

#### B. WORKFLOW OF RESEARCH AND CALIBRATION PROCESS

Fig. 3(a) shows the overall workflow of this research. First, calibration of GAA MOSFET has been conducted, and then structure of the proposed vertically stacked NSFET has been validated through thermal characteristics and electrical characteristics.

In order to analyze the electrical and thermal characteristics of the vertically stacked NSFET, thermodynamics, Shockley-Read-Hall (SRH) recombination, and Fermi models are applied by Synopsys Sentaurus 3D TCAD simulation. In addition to these model physics, Trap-assisted-tunneling (TAT) and direct tunneling are applied to carefully investigate electrical characteristics of the vertically stacked NSFET.

During the calibration process, quantum correlations are performed through  $I_{DS}$ - $V_{GS}$  calibration under Synopsys Sentaurus 3D TCAD simulation [22]. During this process, we have used mobility model (phumob / Enormal (Lombardi) / high field saturation) to apply Coulomb scattering and interfacial surface roughness scattering. Firstly,  $I_{DS}$ - $V_{GS}$  calibration has been carefully conducted by applying the quantum model and velocity saturation model and gate metal work function (WF). Secondly, thermal conductivity, heat dissipation paths, and thermal boundary conduction (300 K) to each heat dissipation path have been adjusted to consider thermal characteristics of the vertically stacked NSFET. Fig. 3(b) and Fig. 3(c) show that our simulation fits electrically and thermally with the previous research [20], [23].

#### **III. RESULT AND DISCUSSION**

## A. IMPROVEMENT OF THERMAL CHARACTERISTICS IN THE VERTICALLY STACKED NSFET

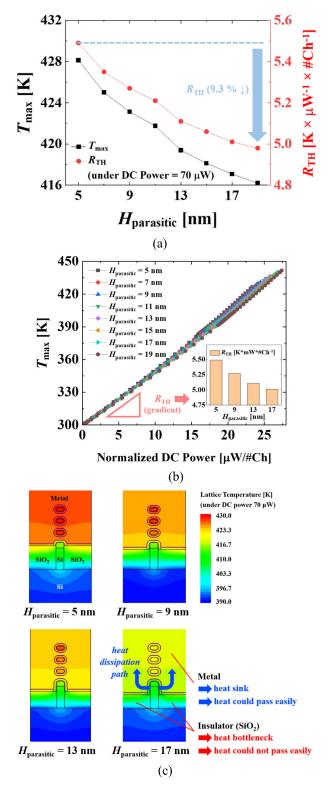

Fig. 4(a) and Fig. 4(b) illustrate how  $T_{\text{max}}$  and  $R_{\text{TH}}$  could be changed according to parasitic channel height ( $H_{\text{parasitic}}$ ) [Fig. 1(a)]. Specifically, as  $H_{\text{parasitic}}$  increases from 5 nm to 19 nm,  $T_{\text{max}}$  could be improved from 428 K to 416 K, and  $R_{\text{TH}}$ could be improved by 9.3 %.  $R_{\text{TH}}$  could be calculated from the gradient of Fig. 4(b), and the equation for  $R_{\text{TH}}$  could be found in the following [20], [21], [24], [25], and [26].

$$R_{\rm TH} = \frac{\Delta T}{\Delta P} [K/\mu W] \tag{1}$$

This thermal improvement could be explained by the phenomenon that increased  $H_{\text{parasitic}}$  leads to the formation of heat sink at the bottom of channel [Fig. 4(c)]. Specifically, when  $H_{\text{parasitic}}$  is 5 nm, SiO<sub>2</sub> is located next to parasitic channel (as shown in the first cross-sectional view in Fig. 4(c)). Since insulator (SiO<sub>2</sub>) has low thermal conductivity, heat generated by parasitic channel could not pass easily when  $H_{\text{parasitic}}$  is 5 nm. On the other hand, when  $H_{\text{parasitic}}$  is 17 nm, metal becomes located next to parasitic channel (as illustrated in the fourth cross-sectional view in Fig. 4(c)). Since metal has high thermal conductivity [Table 1], heat generated by parasitic channel could pass easily through metal when  $H_{\text{parasitic}}$  is high. Namely, since the gate metal could act as an effective heat sink, heat could be easily dissipated as  $H_{\text{parasitic}}$  increases.

Especially,  $R_{\text{TH}}$  continuously improves with increasing  $\underline{H}_{\text{parasitic}}$ . This might be explained by the structural difference between nanosheet-shaped channel and fin-shaped channel. When it comes to nanosheet-shaped channel, the heat generated by nanosheet-shaped channel is difficult to dissipate, because gate dielectric fully surrounds nanosheet-shaped channel. In contrast, when it comes to fin-shaped channel, the heat generated by fin-shaped channel could dissipate either through gate dielectric or the bottom substrate. For these reasons, it has been widely accepted that fin-shaped channel (like FinFET) is superior to thermal characteristics, compared to nanosheet-shaped channel. Therefore, as  $H_{\text{parasitic}}$  increases, the effect of fin-shaped channel (parasitic channel) might be relatively increased, compared to the effect of

FIGURE 4. (a) Effect of parasitic channel height on maximum lattice temperature and thermal resistance, (b) Change of maximum lattice temperature according to the normalized DC power, and (c) Cross-sectional view illustrating distribution of lattice temperature.

nanosheet-shaped channel (main channels). Because of this,  $R_{\text{TH}}$  has been continuously improved.

**FIGURE 5.** (a) Comparison of on-current according to parasitic channel height, and (b) Comparison of on-current/off-current ratio according to parasitic channel height.

### B. IMPROVEMENT OF ELECTRICAL CHARACTERISTICS IN THE VERTICALLY STACKED NSFET

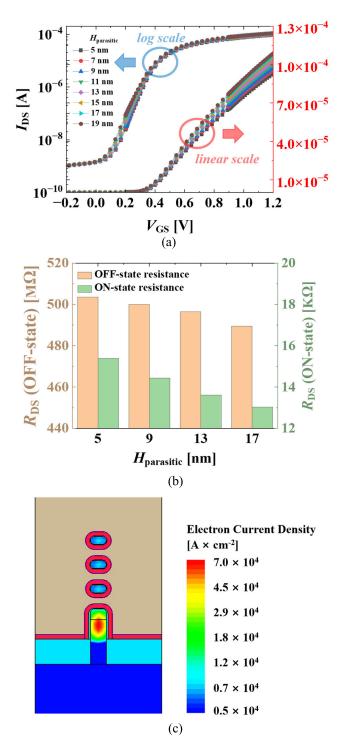

In addition to the thermal improvement discussed in the previous section, improvement of electrical characteristics has been investigated as well. Fig. 5(a), Fig. 5(b), and Fig. 5(c) show  $I_{ON}$ ,  $I_{ON}/I_{OFF}$  ratio, and transfer characteristics, respectively.

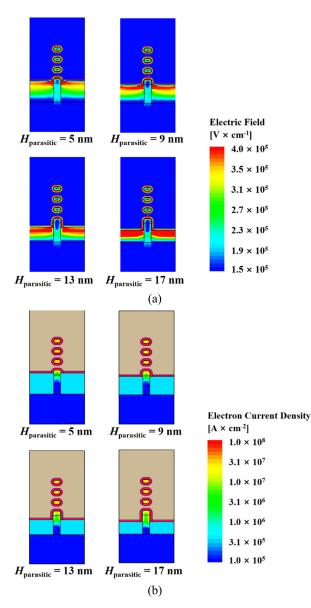

When it comes to  $I_{ON}$ , it has been demonstrated that  $I_{ON}$  could be improved by 19.7 %, as  $H_{\text{parasitic}}$  changes from 5 nm to 19 nm [Fig. 5(a)]. This phenomenon could be explained by increased fringing field effect. For example, as shown in Fig. 6(a), as  $H_{\text{parasitic}}$  increases, fringing field ( $E_F$ ) at SiO<sub>2</sub> region gradually increases. This increased  $E_F$  leads to increase in electron current density [Fig. 6(b)]. For these reasons, as  $H_{\text{parasitic}}$  increases,  $I_{ON}$  consequently increases [Fig. 5(a)]. In a similar context, regarding  $I_{ON}/I_{OFF}$  ratio, the increase in  $H_{\text{parasitic}}$  improves  $I_{ON}/I_{OFF}$  ratio becomes saturated as  $H_{\text{parasitic}}$  increases, because  $I_{OFF}$  is increased as  $H_{\text{parasitic}}$  increases. This phenomenon will be carefully explained in the next following section IV.

**FIGURE 6.** (a) Cross-sectional view illustrating amount of electric field (under  $V_{GS} = V_{DS} = 0.7$  V), and (b) Cross-sectional view describing electron current density (under  $V_{GS} = V_{DS} = 0.7$  V). As  $H_{\text{parasitic}}$  increases, the amount of electric field increases. This increased electric field leads to an increase in electron current density, thereby increasing on-current.

## C. INVESTIGATION OF THERMAL CHARACTERISTICS UNDER AC CONDITION

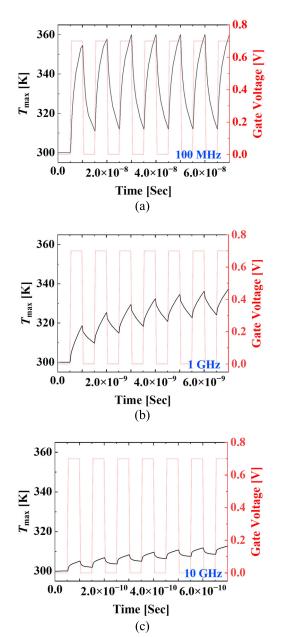

Furthermore, the thermal characteristics of the proposed structure have been investigated under various alternating current (AC) conditions. Given the practical operating condition of modern IC chips, it is also important to analyze the thermal characteristics of transistor under AC conditions. It has demonstrated that the thermal characteristics under AC signals varies from thermal characteristics under direct current (DC) signals, since the heat accumulation / heat dissipation happens repeatedly in AC condition [Fig. 7].

Specifically, it has been demonstrated that heat accumulation phenomenon could be found during ON states, while heat

FIGURE 7. Maximum temperature change under AC condition with (a) 100 MHz, (b) 1 GHz, and (c) 10 GHz.

dissipation phenomenon could be found during OFF states [Fig. 7].

In this analysis, a gate voltage of 0.7 V, an increasing time of 5 % of a period, a decreasing time of 5 % of a period, and a duty cycle of 50 % are applied to gate terminal [27]. Fig. 7(a), Fig. 7(b), and Fig. 7(c) show the thermal characteristics of the proposed structure ( $H_{\text{parasitic}} = 19 \text{ nm}$ ) under 100 megahertz (MHz) band, 1 gigahertz (GHz) band, and 10 GHz band, respectively. Specifically, in the 100 MHz band, as described in Fig. 7(a), heat accumulation and heat dissipation occur over and over again, however, the overall  $T_{\text{max}}$  rises as more cycles are applied.

This phenomenon could be explained by the phenomenon that each cycle of heat accumulation and heat dissipation

**FIGURE 8.** (a) Transfer characteristics with log scale and linear scale (under bias condition  $V_{DS} = 0.7$  V), (b) drain-source resistance ( $R_{DS}$ ) according to  $H_{\text{parasitic}}$ , and (c) Cross-sectional view illustrating electron current density.

consequently leaves residual heat. The same pattern is also observed in 1 GHz band and 10 GHz band as well [Fig. 7(b) and Fig. 7(c)]. Importantly, as the frequency increases from 100 MHz to 10 GHz, lower  $T_{\text{max}}$  is observed [Fig. 7]. This is because, compared to 100 MHz, higher frequency band such as 10 GHz has shorter heat-accumulation time.

#### TABLE 2. Performance comparison with previous research.

|                               | IEDM 2021<br>[35] | TED 2020<br>[36] | TED 2020<br>[37] | This<br>Work |

|-------------------------------|-------------------|------------------|------------------|--------------|

| $V_{\rm DD}$ [V]              | 0.7               | 0.65             | 0.65             | 0.7          |

| $T_{\rm ch}$ [nm]             | 5                 | 6                | 6                | 5            |

| $W_{\rm ch}$ [nm]             | 20                | 25               | 25               | 10           |

| $L_{\text{gate}} [\text{nm}]$ | 15                | 14               | 11.5             | 16           |

| # of stacks                   | 4                 | 3                | 2                | 3            |

| $I_{\rm ON}/I_{\rm OFF}$      | 29,600            | 29,166           | 7,307            | 35,150       |

| $P_{\rm OFF}$ [pW]            | 1,890             | 7,800            | 16,900           | 1,330        |

As a result, the lower frequency band, 100 MHz shows higher  $T_{\text{max}}$ , while the higher frequency band 10 GHz shows lower  $T_{\text{max}}$ .

The overall performance of the proposed structure has been summarized in Table 2. As shown in Table 2, our proposed structure could be expected to have improved electrical characteristics and thermal characteristics at the same time.

#### IV. LIMITATION OF THE RESEARCH AND FUTURE SCOPE OF THE RESEARCH

All in all, the proposed vertically stacked NSFET ( $H_{\text{parasitic}} = 19 \text{ nm}$ ) could operate with increased  $I_{\text{ON}}$  and improved thermal characteristics (improved reliability) at the same time. Given these factors, it is expected that the proposed NSFET configuration will be very strategic for designing next-generation high performance (HP) IC chips with improved performance and enhanced reliability.

Nevertheless, our proposed device structure has some limitation as well. For example, even though it could be true that the increased  $H_{\text{parasitic}}$  could lead to thermal and electrical improvement in the vertically stacked NSFET, it might be difficult to fabricate the vertically stacked NSFET as  $H_{\text{parasitic}}$ increases.

Specifically, considering the fact that our simulation structure has  $W_{\text{channel}}$  of 10 nm, it might be possible to fabricate the vertically stacked NSFET with 19 nm  $H_{\text{parasitic}}$  (with the aspect ratio about 2:1) [28], [29], [30]. However, it might be difficult to fabricate with higher  $H_{\text{parasitic}}$  (over the aspect ratio 3:1). Even though there was previous research showing aspect ratio of the fin-shaped silicon channel over 10:1, it might be difficult to fabricate this kind of fin-shaped channel with high yield rate [31]. In this regard, the authors would like to suggest the future research addressing the fabrication of vertically stacked NSFET with various  $H_{\text{parasitic}}$  values, so that the parasitic channel height engineering could be understood not only from the modelling perspective but also from the fabrication perspective.

In addition,  $I_{ON}/I_{OFF}$  ratio becomes saturated as  $H_{\text{parasitic}}$  reaches 19 nm, despite  $I_{ON}$  continuing to increase [Fig. 5(c)]. This is because the increased  $H_{\text{parasitic}}$  leads to higher offcurrent ( $I_{OFF}$ ) as well [Fig. 8(a) and Fig. 8(b)].

This phenomenon could be explained by illustration of electron current density during OFF-state. As shown in Fig. 8(c), it can be interpreted that most of  $I_{OFF}$  is derived by the parasitic channel (also known as 'parasitic resistance'), which leads to increased  $I_{OFF}$  in the proposed device structure. Because of this phenomenon, drain-source resistance ( $R_{DS}$ ) during OFF-state could be decreased as  $H_{parasitic}$  increases, thereby leading to undesirable increased  $I_{OFF}$  [Fig. 8(b)]. Therefore, even though our proposed structure could be strategic for high performance (HP) IC chip design, for designing low power (LP) IC chip design, other strategies such as incorporation of low power devices such as tunnel field-effect transistor (TFET) will be needed [32], [33], [34].

#### **V. CONCLUSION**

In this paper, simultaneous improvement of thermal characteristics and electrical characteristics in the vertically stacked NSFET has been demonstrated. As the height of parasitic channel increases, maximum lattice temperature and thermal resistance have been improved, since the increase of parasitic channel height leads to formation of effective heat sink. In addition to this thermal improvement, it has been demonstrated that the parasitic channel height engineering could increase on-current by 19.7 % in the vertically stacked NSFET, since the increased fringing field leads to increase of electron current density, thereby increasing oncurrent. The connection between parasitic channel height and the thermal characteristics of the device has rarely been researched in earlier studies, and we have explored this with a novel approach. Our proposed structure with the increased parasitic channel height would be strategic for future scaling technology with enhanced thermal characteristics and improved electrical performance, at the same time.

#### ACKNOWLEDGMENT

The EDA tool was supported by the IC Design Education Center (IDEC), South Korea.

#### REFERENCES

- Y. S. Abdalla and M. I. Elmasry, "Impact of technology scaling on the performance of all-time-on single-ended CMOS logic," in *Proc. IEEE North-East Workshop Circuits Syst.*, Jun. 2006, pp. 105–108, doi: 10.1109/NEWCAS.2006.250941.

- [2] O. V. Maiuri and W. R. Moore, "Implications of voltage and dimension scaling on CMOS testing: The multidimensional testing paradigm," in *Proc. 16th IEEE VLSI Test Symp.*, Jul. 1998, pp. 22–27, doi: 10.1109/VTEST.1998.670844.

- [3] Y. S. Song, S. Kim, J. H. Kim, G. Kim, J. -H. Lee, and W. Y. Choi, "Enhancement of thermal characteristics and on-current in GAA MOSFET by utilizing Al<sub>2</sub>O<sub>3</sub>-based dual-k Spacer structure," *IEEE Trans. Electron Devices*, vol. 70, no. 1, pp. 343–348, Jan. 2023, doi: 10.1109/TED.2022.3223321.

- [4] F. A. Herrera, M. Miura-Mattausch, T. Iizuka, H. Kikuchihara, Y. Hirano, and H. J. Mattausch, "Modeling of short-channel effect on multi-gate MOSFETs for circuit simulation," in *Proc. Int. Symp. Devices, Circuits Syst.*, 2020, pp. 1–4.

- [5] B. Ye, Y. Gu, H. Xu, C. Tang, H. Zhu, Q. Sun, and D. W. Zhang, "NBTI mitigation by optimized HKMG thermal processing in a FinFET technology," *IEEE Trans. Electron Devices*, vol. 69, no. 3, pp. 905–909, Mar. 2022, doi: 10.1109/TED.2021.3139566.

- [7] Y. S. Song, J. H. Kim, G. Kim, H.-M. Kim, S. Kim, and B.-G. Park, "Improvement in self-heating characteristic by incorporating heterogate-dielectric in gate-all-around MOSFETs," *IEEE J. Electron Devices Soc.*, vol. 9, pp. 36–41, 2021, doi: 10.1109/JEDS.2020.3 038391.

- [8] Y. S. Song, S. Tayal, S. B. Rahi, J. H. Kim, A. K. Upadhyay, and B.-G. Park, "Thermal-aware IC chip design by combining high thermal conductivity materials and GAA MOSFET," in *Proc. 5th Int. Conf. Circuits, Syst. Simul. (ICCSS)*, May 2022, pp. 135–140, doi: 10.1109/ICCSS55260.2022.9802341.

- [9] K. Y. Kim, Y. S. Song, G. Kim, S. Kim, and J. H. Kim, "Reliable highvoltage drain-extended FinFET with thermoelectric improvement," *IEEE Trans. Electron Devices*, vol. 69, no. 11, pp. 5985–5990, Nov. 2022, doi: 10.1109/TED.2022.3209141.

- [10] A. Veloso, G. Eneman, A. de Keersgieter, D. Jang, H. Mertens, P. Matagne, E. D. Litta, J. Ryckaert, and N. Horiguchi, "Nanosheet FETs and their potential for enabling continued Moore's law scaling," in *Proc. 5th IEEE Electron Devices Technol. Manuf. Conf. (EDTM)*, Chengdu, China, Apr. 2021, pp. 1–3, doi: 10.1109/EDTM50988.2021.94 20942.

- [11] N. Seoane, J. G. Fernandez, K. Kalna, E. Comesaña, and A. García-Loureiro, "Simulations of statistical variability in n-type FinFET, nanowire, and nanosheet FETs," *IEEE Electron Device Lett.*, vol. 42, no. 10, pp. 1416–1419, Oct. 2021, doi: 10.1109/LED.2021.3109586.

- [12] S. Rathore, R. K. Jaisawal, P. N. Kondekar, N. Gandhi, S. Banchhor, Y. S. Song, and N. Bagga, "Self-heating aware threshold voltage modulation conforming to process and ambient temperature variation for reliable nanosheet FET," in *Proc. IEEE Int. Rel. Phys. Symp. (IRPS)*, Mar. 2023, pp. 1–5, doi: 10.1109/IRPS48203.2023.10117918.

- [13] S. Tayal, B. Smaani, S. B. Rahi, A. K. Upadhyay, S. Bhattacharya, J. Ajayan, B. Jena, I. Myeong, B.-G. Park, and Y. S. Song, "Incorporating bottom-up approach into device/circuit co-design for SRAM-based cache memory applications," *IEEE Trans. Electron Devices*, vol. 69, no. 11, pp. 6127–6132, Nov. 2022, doi: 10.1109/TED.2022.32 10070.

- [14] R. Lee, J. Lee, K. Lee, S. Kim, H. Ahn, S. Kim, H.-M. Kim, C. Kim, J.-H. Lee, S. Kim, and B.-G. Park, "Vertically-stacked Si<sub>0.2</sub>Ge<sub>0.8</sub> nanosheet tunnel FET with 70 mV/Dec average subthreshold swing," *IEEE Electron Device Lett.*, vol. 42, no. 7, pp. 962–965, Jul. 2021, doi: 10.1109/LED.2021.3079246.

- [15] Y. Choi, K. Lee, K. Yeon Kim, S. Kim, J. Lee, R. Lee, H.-M. Kim, Y. Suh Song, S. Kim, J.-H. Lee, and B.-G. Park, "Simulation of the effect of parasitic channel height on characteristics of stacked gate-all-around nanosheet FET," *Solid-State Electron.*, vol. 164, Feb. 2020, Art. no. 107686, doi: 10.1016/j.sse.2019.107686.

- [16] H.-H. Liu, Y.-S. Huang, F.-L. Lu, H.-Y. Ye, and C. W. Liu, "Different infrared responses from the stacked channels and parasitic channel of stacked GeSn channel transistors," *IEEE Electron Device Lett.*, vol. 41, no. 1, pp. 147–150, Jan. 2020, doi: 10.1109/LED.2019.2952572.

- [17] Q. Zhang, J. Gu, R. Xu, L. Cao, J. Li, Z. Wu, G. Wang, J. Yao, Z. Zhang, J. Xiang, X. He, Z. Kong, H. Yang, J. Tian, G. Xu, S. Mao, H. H. Radamson, H. Yin, and J. Luo, "Optimization of structure and electrical characteristics for four-layer vertically-stacked horizontal gateall-around Si nanosheets devices," *Nanomaterials*, vol. 11, no. 3, p. 646, Mar. 2021, doi: 10.3390/nano11030646.

- [18] International Roadmap for Devices and Systems (IRDS), 2022.

- [19] E. A. Scott, J. T. Gaskins, S. W. King, and P. E. Hopkins, "Thermal conductivity and thermal boundary resistance of atomic layer deposited high-κ dielectric aluminum oxide, hafnium oxide, and titanium oxide thin films on silicon," *APL Mater.*, vol. 6, no. 5, May 2018, Art. no. 058302, doi: 10.1063/1.5021044.

- [20] I. Myeong, D. Son, H. Kim, and H. Shin, "Analysis of self heating effect in DC/AC mode in multi-channel GAA-field effect transistor," *IEEE Trans. Electron Devices*, vol. 66, no. 11, pp. 4631–4637, Nov. 2019.

- [21] I. Myeong, I. Song, M. J. Kang, and H. Shin, "Self-heating and electrothermal properties of advanced sub-5-nm node nanoplate FET," *IEEE Electron Device Lett.*, vol. 41, no. 7, pp. 977–980, Jul. 2020.

- [22] Version S-2021, Synop., Mountain View, CA, USA, 2021.

- [23] N. Loubet et al., "Stacked nanosheet gate-all-around transistor to enable scaling beyond FinFET," in *Proc. Symp. VLSI Technol.*, Kyoto, Japan, Jun. 2017, pp. T230–T231, doi: 10.23919/VLSIT.2017.7998183.

- [24] H. Kim, D. Son, I. Myeong, D. Ryu, J. Park, M. Kang, J. Jeon, and H. Shin, "Strain engineering for 3.5-nm node in stacked-nanoplate FET," *IEEE Trans. Electron Devices*, vol. 66, no. 7, pp. 2898–2903, Jul. 2019, doi: 10.1109/TED.2019.2917503.

- [25] H. Kim, D. Son, I. Myeong, M. Kang, J. Jeon, and H. Shin, "Analysis on self-heating effects in three-stacked nanoplate FET," *IEEE Trans. Electron Devices*, vol. 65, no. 10, pp. 4520–4526, Oct. 2018, doi: 10.1109/TED.2018.2862918.

- [26] I. Myeong, J. Jeon, M. Kang, and H. Shin, "Analysis of self heating effect in vertical-channel field effect transistor," in *Proc. 20th Int. Conf. Thermal, Mech. Multi-Phys. Simul. Exp. Microelectron. Microsystems*, Sep. 2019, pp. 1–5.

- [27] Y. S. Song, S. Kim, G. Kim, H. Kim, J.-H. Lee, J. H. Kim, and B.-G. Park, "Improvement of self-heating effect in Ge vertically stacked GAA nanowire pMOSFET by utilizing Al<sub>2</sub>O<sub>3</sub> for high-performance logic device and electrical/thermal co-design," *Jpn. J. Appl. Phys.*, vol. 60, no. 1, Mar. 2021, Art. no. SCCE04.

- [28] Y. Liu, S. Kijima, E. Sugimata, M. Masahara, K. Endo, T. Matsukawa, K. Ishii, K. Sakamoto, T. Sekigawa, H. Yamauchi, Y. Takanashi, and E. Suzuki, "Investigation of the TiN gate electrode with tunable work function and its application for FinFET fabrication," *IEEE Trans. Nanotechnol.*, vol. 5, no. 6, pp. 723–730, Nov. 2006, doi: 10.1109/TNANO.2006.885035.

- [29] Z. Ren, X. An, B. Zhang, S. Sun, F. Gao, M. Li, X. Zhang, and R. Huang, "High performance SiGe body-on-insulator (BOI) FinFET fabricated on bulk Si substrate using Ge condensation technique," *IEEE Electron Device Lett.*, vol. 41, no. 9, pp. 1280–1283, Sep. 2020, doi: 10.1109/LED.2020.3007333.

- [30] B. Yu, L. Chang, S. Ahmed, H. Wang, S. Bell, C.-Y. Yang, C. Tabery, C. Ho, Q. Xiang, T.-J. King, J. Bokor, C. Hu, M.-R. Lin, and D. Kyser, "FinFET scaling to 10 nm gate length," in *IEDM Tech. Dig.*, 2002, pp. 251–254, doi: 10.1109/iedm.2002.1175825.

- [31] M. J. H. van Dal et al., "Highly manufacturable FinFETs with sub-10nm fin width and high aspect ratio fabricated with immersion lithography," in *Proc. IEEE Symp. VLSI Technol.*, Oct. 2007, pp. 110–111, doi: 10.1109/VLSIT.2007.4339747.

- [32] R. Saha, D. K. Panda, R. Goswami, B. Bhowmick, and S. Baishya, "Effect of drain engineering on DC and RF characteristics in Ge-source SD-ZHP-TFET," in *Proc. Devices Integrated Circuit*, 2021, pp. 517–520.

- [33] N. N. Reddy and D. K. Panda, "Performance analysis of Z-shaped gate dielectric modulated (DM) tunnel field-effect transistor-(TFET) based biosensor with extended horizontal N+ pocket," *Int. J. Numer. Modelling, Electron. Netw., Devices Fields*, vol. 34, no. 6, pp. 1–13, May 2021, doi: 10.1002/jnm.2908.

- [34] R. Saha, D. K. Panda, R. Goswami, B. Bhowmick, and S. Baishya, "DC and RF/analog parameters in Ge-source split drain-ZHP-TFET: Drain and pocket engineering technique," *Int. J. Numer. Modelling, Electron. Netw.*, *Devices Fields*, vol. 35, no. 3, pp. 1–16, Oct. 2021, doi: 10.1002/jnm.2967.

- [35] S. Huang, Z. Wu, H. Xu, J. Guo, L. Xu, X. Duan, Q. Chen, G. Yang, Q. Zhang, H. Yin, L. Wang, L. Li, and M. Liu, "Geometric variability aware quantum potential based quasi-ballistic compact model for stacked 6 nm-thick silicon nanosheet GAA-FETs," in *IEDM Tech. Dig.*, Dec. 2021, pp. 1851–1854, doi: 10.1109/IEDM19574.2021.9720550.

- [36] S. Kim, M. Kim, D. Ryu, K. Lee, S. Kim, J. Lee, R. Lee, S. Kim, J.-H. Lee, and B.-G. Park, "Investigation of electrical characteristic behavior induced by channel-release process in stacked nanosheet gate-all-around MOS-FETs," *IEEE Trans. Electron Devices*, vol. 67, no. 6, pp. 2648–2652, Jun. 2020, doi: 10.1109/TED.2020.2989416.

- [37] D. Ryu, M. Kim, S. Kim, Y. Choi, J. Yu, J.-H. Lee, and B.-G. Park, "Design and optimization of Triple-k spacer structure in two-stack nanosheet FET from OFF-state leakage perspective," *IEEE Trans. Electron Devices*, vol. 67, no. 3, pp. 1317–1322, Mar. 2020, doi: 10.1109/TED.2020.2969445.

**YOUNG SUH SONG** (Member, IEEE) received the B.S. and M.S. degrees in electrical and computer engineering from Seoul National University (SNU), in 2018 and 2024, respectively. From June 2020 to August 2021, he was a full-time Lecturer with the Department of Computer Science, Korea Military Academy. Subsequently, he was an Assistant Professor with the Department of Computer Science, Korea Military Academy, from September 2021 to May 2023. He has authored and

co-authored over 40 research papers in journals and conferences, including IEEE TRANSACTIONS ON ELECTRON DEVICES, IEEE JOURNAL OF THE ELECTRON DEVICES SOCIETY, IEEE International Reliability Physics Symposium (IEEE IRPS), and IEEE Electron Devices Technology and Manufacturing Conference (IEEE EDTM). His current research interests include thermal management of semiconductor (also known as self-heating effect, SHE), 2D materials (MoS2, WSe2, and hBN), CMOS, graphene, CNT, III–V devices, and high electron mobility transistor. He served as a Technical Committee for the IEEE International Conference on Circuits, Systems and Simulations (IEEE ICCSS), in 2022. He also served as a guest speaker for universities, including VIT-AP University and VIT Chennai, India, in 2022, and NIT Delhi, India, in 2023. He received the "Best Paper" Award from "the Institute of Electronics and Information Engineers (IEEE)" in 2020 and "IEEE ICCSS" in 2022.

**HYUNWOO KIM** (Member, IEEE) received the B.S. degree from Kyungpook National University (KNU), Daegu, South Korea, in 2008, and the M.S. and Ph.D. degrees in electrical engineering from Seoul National University (SNU), Seoul, in 2010 and 2015, respectively. He was with Samsung Electronics, Hwaseong, South Korea, as a Senior Researcher, from 2015 to 2021. Since 2023, he has been a Faculty Member with Konkuk University (KU), Seoul, South Korea, where he

is currently an Assistant Professor with the Department of Electrical and Electronics Engineering. His current research interests include foundry logic CMOS devices, ferroelectric devices, and low power applications.

JANG HYUN KIM (Member, IEEE) received the bachelor's degree in electrical and electronic engineering from Korea Advanced Institute of Science and Technology (KAIST), in August 2009, the master's degree from the Department of Electrical and Computer Engineering, Seoul National University, in August 2011, and the Ph.D. degree from the Department of Electrical and Computer Engineering, Seoul National University. After completing his education, he was a Development

Researcher of dynamic random access memory (DRAM), SK Hynix, from September 2016 to February 2020. Subsequently, he was an Assistant Professor with the Department of Electrical Engineering, Pukyong National University, from March 2020 to February 2023. He has been an Assistant Professor with the Department of Electronic Engineering, Ajou University, since February 2023. His current research interests include logic semiconductor devices and power semiconductor devices.

...