Received 20 June 2024, accepted 7 July 2024, date of publication 15 July 2024, date of current version 26 July 2024.

Digital Object Identifier 10.1109/ACCESS.2024.3428388

# **On-Board Computer for CubeSats:** State-of-the-Art and **Future Trends**

ANGELA CRATERE<sup>10</sup>, LEANDRO GAGLIARDI<sup>10</sup>, GABRIEL A. SANCA<sup>10</sup>, FEDERICO GOLMAR<sup>2</sup>, AND FRANCESCO DELL'OLIO (Senior Member, IEEE)

Micro Nano Sensor Group, Department of Electrical and Information Engineering, Polytechnic University of Bari, 70126 Bari, Italy

<sup>2</sup>Instituto de Ciencias Físicas, Universidad de San Martín-CONICET, Buenos Aires 1650, Argentina

Corresponding author: Francesco Dell'Olio (francesco.dellolio@poliba.it)

**ABSTRACT** Over the past three decades, the acceptance of higher risk thresholds within the space industry has facilitated the widespread integration of commercial off-the-shelf (COTS) components into avionics and payloads, leading to a remarkable transformation in the design of space missions. This transformation has led to the emergence of the New Space Economy and the widespread adoption of lean or small satellites in general, particularly CubeSats. CubeSats are now widely used in commercial, scientific, and research applications due to their versatility, affordability, simplicity of development, and accelerated development timelines. On-board computing plays a crucial role in the design of CubeSat missions, as increasingly high-performance computational requirements are needed to meet the challenges of future missions. This paper systematically reviews the state-of-the-art of CubeSat Command and Data Handling (C&DH) subsystem, covering both hardware components and flight software (FSW) development frameworks. It presents an analysis of the key features and recent developments of on-board computers (OBCs) in commercial and academic institutional projects funded by governments, agencies and public institutions. It further examines the effects of space radiation on avionics components and discusses the main fault-tolerance techniques used in CubeSat platforms. Finally, this paper highlights trends and hazards for future CubeSat avionics and identify potential directions for future developments in high-performance on-board computing. By synthesizing contemporary research and industry insights, this paper aims to shed light on CubeSat OBC design, providing an overview of the existing technology landscape and the challenges to be addressed for next-generation mission needs.

**INDEX TERMS** Command and data handling (C&DH), CubeSats, on-board computer (OBC), small satellite avionics.

#### I. INTRODUCTION

**VOLUME 12, 2024**

ALL space missions aim to generate and collect data. Data acquisition is a key consideration in the design of space systems, as it plays a fundamental role in defining their objectives. Generally, space missions are based on a main payload that produces data specifically for different purposes, such as Earth observation (EO) and remote sensing, astrophysics, space environment characterization, heliophysics and space weather, and the demonstration of

The associate editor coordinating the review of this manuscript and approving it for publication was Zhenbao Liu.

new technologies. Such payload data constitute the largest data set of a mission. However, space missions additionally produce a wide range of other data, including telemetry (TM), which records the health of the spacecraft and its subsystems (power supply voltages, current draw and temperatures), attitude data, log files and configuration settings [1]. The command and data handling (C&DH) subsystem is responsible for managing the data produced onboard the satellite. This system's functions include the collection, preparation, and storage of both housekeeping and mission data, which can be used onboard or transmitted to ground stations. In addition, the C&DH subsystem often

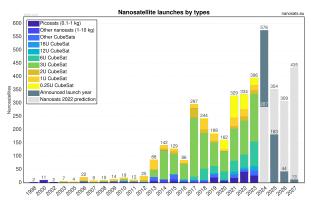

FIGURE 1. Yearly launches by nanosatellite types. From [4].

executes additional tasks, including receiving, validating, decoding, and distributing commands to other subsystems, detecting faults arising from the interaction of space radiation with electronic components and subsequent system recovery, security functions, and spacecraft timekeeping [2], [3].

In recent decades, the space sector has undergone a significant transformation due to advances in miniaturization techniques for payloads and electronic components. This factor, combined with an increased risk tolerance leading to the widespread use of commercial off-the-shelf (COTS) electronics also in space, has resulted in a growing interest in new mission concepts based on limited size, weight, power, and cost (SWaP-C), such as CubeSats. For approximately 15 years, CubeSats have been key instrument technologies dominating the space market and facilitating access to space. Until 1 January 2024, more than 2000 CubeSats have been launched [4]. According to some forecasts, almost two thousand CubeSats will be launched in the next four years (Fig. 1, [4]).

The CubeSat standard, formally known as the CubeSat Design Specification (CDS), was introduced by Stanford and California Polytechnic State Universities in 1999 [5], [6]. It specifies that a standard unit (1U) is a cube of 10 cm on one side (to be precise,  $10 \text{ cm} \times 10 \text{ cm} \times 11.35 \text{ cm}$ ) with a mass of up to 2 kg [7]. A 1U can be used as a stand-alone satellite or can be arranged with others to build larger CubeSats. The main advantage of this standardization is the possibility for launch vehicle manufacturers to implement universal deployment systems independently of the CubeSat manufacturer, such as the Poly Picosat Orbital Deployer (P-POD) or the NanoRacks CubeSat Deployer (NRCSD; [8]). The CubeSat standard also provides specific design requirements and protocols, simplifying the development process. Following the popularity of the 1U and 3U CubeSats, an advanced standard for larger CubeSats (6U, 12U and 27U) was proposed in 2011 to enable the enhancement of CubeSat capabilities and increase utilization [9].

Although originally intended as educational tools or low-cost technology demonstrators [6], [10], [11], CubeSats are currently used in a variety of applications, from commercial and telecommunication purposes [12], [13] to

high-value scientific missions [8], [11]. They offer significant cost advantages compared to traditional satellites, with a development cost of approximately USD 200 000, as opposed to the USD 150-350 million required for conventional satellites. In addition, CubeSats typically have short development times of less than one or two years, compared to the 5-15 years that are required for large mission concepts [14]. These advantages have motivated worldwide government agencies to actively support CubeSat missions, leading to the emergence of long-term programs dedicated to CubeSat technologies, such as the National Aeronautics and Space Administration's (NASA's) Cubesat Launch Initiative [15]. The European Space Agency (ESA) has provided funding for several CubeSat missions, including those with interplanetary targets (e.g., [16], [17]), as part of its General Support Technology Programme (GSTP). The Italian Space Agency (ASI) has funded the Alcor program, which includes at least 20 CubeSat missions, and has participated in the development of the first two Italian CubeSats for deep-space applications, namely LiciaCube [18] and ArgoMoon [19]. The introduction of the CubeSat standard has also opened up space exploration to private companies, leading to the emergence of the so-called New Space Economy, and has provided scientific opportunities for small educational institutions.

Recently, the popularity of CubeSat platforms has been driven by advances in silicon processes and electronics miniaturization techniques, which enable the integration of complex processor architectures into a single Field Programmable Gate Array (FPGA) or System-On-a-Chip (SoC; [3]). CubeSat C&DH subsystems have reached a state of relative maturity, with a wide range of implementation options available. The number of companies and research institutes worldwide developing their own avionics subsystem for CubeSats is increasing steadily [4]. In this context, this paper aims to systematically review the state-of-theart in OBCs for CubeSats, primarily targeting research and commercial projects funded by government agencies and private companies. Although there are several works dealing with the C&DH subsystem [2], [3], [20], [21], [22], even for small satellites [23], [24], none of them discusses in detail OBCs intended for CubeSat platforms ([1] provides only a general overview of CubeSat subsystems). Therefore, this paper meticulously reviews recent advances in CubeSat OBCs, in order to provide developers and researchers with an understanding of currently available technologies, their limitations, and the breakthroughs required for future mission needs. The purpose is to provide an overview of existing and developing architectures, valuable both to illustrate existing options for those choosing to purchase a commercial OBC for their mission, and to support architecture and component selection for those deciding to design a customized OBC based on mission-specific requirements.

The structure of the paper is as follows: §II provides basic knowledge about the C&DH subsystem, its functions, its general architecture, and the main implementation options

used in CubeSats. Furthermore, it analyzes the effects of space radiation on avionics systems and the main mitigation techniques used. § III reviews the OBC systems currently available on the market or under development, analyzing their architecture and performance based on the nature of their processing core. § IV discusses the tools used for flight software (FSW) development. § V presents future trends in avionics, identifying potential directions for next-generation systems. Finally, §VI summarizes the main lessons learned from this literature review and concludes the paper.

# II. OVERVIEW ON C&DH SUBSYSTEM: FUNCTIONS, COMPONENTS AND TECHNIQUES FOR RADIATION EFFECT MITIGATION

In this review, we specifically refer to the term *avionics* as the subsystems, electronic components and functions featured in the C&DH module.

Typically, there are two data management segments within a classical C&DH subsystem, each of which has different purposes and functions [20]. The first segment is responsible for monitoring and surveilling the satellite bus, while the second segment aims to monitor the payload, as well as process the data collected by the payload to support the spacecraft's science mission. These two data management segments can be concentrated in a single processing system or distributed between two separate processing units, namely the main OBC and the payload computer. Therefore, there are two different approaches in the design of the C&DH subsystem. In centralized architectures, all functions are concentrated in a single powerful and reliable computing infrastructure, which serves as the main OBC for satellite platform monitoring and TM management (including the processing of data produced by the attitude determination and control subsystem; ACDS), and as a processing unit for payload data. In some cases, this approach has been implemented for smaller satellites due to the constraints on the mass and volume of electronic components imposed by their limited size (e.g., [25]). However, it is generally poorly adopted because this type of architecture suffers from potential system-level failures due to its dependence on a single processor or computing unit. Moreover, this design requires high energy consumption, limited system reconfiguration possibilities and complex interfaces [23]. A centralized OBC, which also incorporates payload computer functions, is poorly scalable and must be redesigned for each mission. In distributed architectures, which are the most commonly used approach, functions are divided and shared across a computing architecture consisting of multiple modules. In this case, platform and payload control functions are assigned to different devices and processors. This approach is favoured because basic satellite tasks (such as platform management, TC decoding and maintenance reports) consume less power. More demanding tasks, such as attitude determination and control, processing of scientific data produced by the payload, intensive signal processing (e.g., data compression, time/frequency domain filtering, and feature extraction), fault monitoring or cryptography, require very high processing power and more advanced processors [21]. A distributed approach ensures the scalability of the OBC, as the modular architecture allows the hardware and software subsystems to be reused in future missions.

The design of the C&DH subsystem is a very demanding process that uses typical system engineering design techniques. It starts with the definition of the system functions, requirements, and specifications, and leads to the definition of the system architecture and the selection of electronic components. This is often an iterative process, which should consider the requirements of other satellite subsystems (this approach is called *concurrent engineering*) and, since these are systems intended for space, also the extremely harsh environmental conditions and the effects of radiation. In this section, we present the conventional avionics architecture typically used as a reference in the C&DH subsystem and OBC design process and analyze in detail the effects of radiation in avionics systems.

#### A. CONVENTIONAL AVIONICS ARCHITECTURE

The design of the avionics architecture is generally influenced by the nature of the mission, leading to significant variability in existing avionics systems. Space agencies, institutions and companies have long emphasized the need to standardize avionics systems, with the aim of making these systems scalable, enabling the reuse of elements and modules in different missions, and increasing the efficiency of subsystem design, leading to a reduction in costs and development time. To achieve this goal, it is essential to identify recurring architectural elements and precisely define their functions, interfaces, and interconnection protocols.

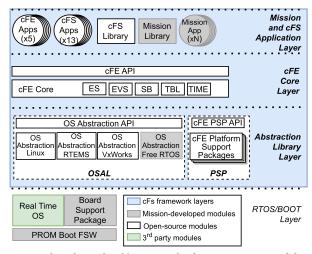

[3], [22]. In this context, the ESA's Space Avionics Open Interface Architecture (SAVOIR) initiative [26] established a functional architecture for classical satellites that serves as a reference for avionics standardization efforts.

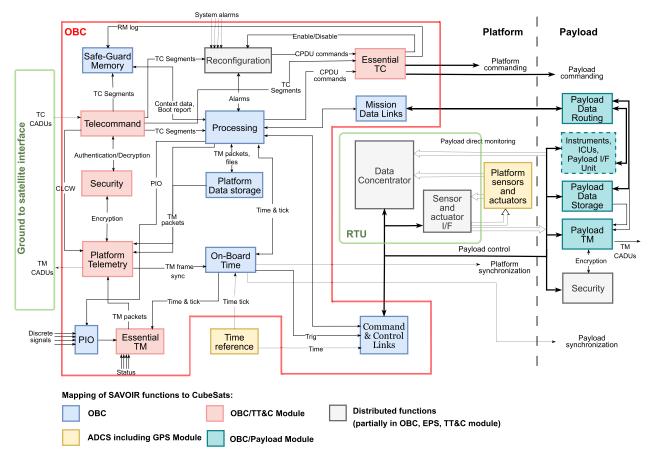

Fig. 2 shows a functional view of the SAVOIR reference architecture. In this general concept, the OBC functions include [3], [22]:

- TM handling functions. These functions include the collection of fundamental TM and the generation/encoding of TM data packets according to the Telemetry Transfer Frame (TTF) protocol. This standardizes the data structure for space data transmission over a TM link.

- Telecommand (TC) handling functions. These include receiving, authenticating, and decoding TCs sent from ground stations, distributing commands to control vital spacecraft functions, and implementing security measures to protect against unauthorized TCs. Optionally, they could also provide for the cryptography of data transmitted on the downlink.

- I/O peripheral and interface (I/F) handling functions. These support physical sensor and actuator I/Fs to acquire essential spacecraft data. Sensor monitoring can be managed directly in point-to-point mode or via a data concentrator function, typically implemented in one

FIGURE 2. SAVOIR avionics functional reference architecture [26]. The red box marks the functional blocks included in the OBC. The colored squares map the general SAVOIR functions in the various subsystems of a CubeSat. Depending on the specific CubeSat mission, TCs and TM can be handled by the main OBC or the telemetry, tracking, and command (TT&C) subsystem. Similarly, the management of the payload data and its TM may be the task of the OBC, the payload computer or both.

or more remote terminal units (RTUs)/remote interface units (RIUs).

- Time management functions. These provide a timer and generate events of synchronization, including the potential inclusion of Global Navigation Satellite System (GNSS).

- Processing and storage functions. These are responsible not only for storing and processing the critical satellite bus data but also for storing and executing the FSW.

- Fault detection and reconfiguration functions. These identify and correct faults, thus maintaining the correct operation of the processing functions even when errors occur.

- Payload data routing functions. These manage the monitoring and control of the payload units. Optionally, a function for storing telemetric payload data during periods when there is no contact with the ground stations can be included.

In the case of conventional satellites, the term C&DH subsystem is a hyperonym for various platforms and devices for processing data onboard the satellite, while the on-board computer (OBC) usually refers to hardware and software components specifically designed to manage the satellite

platform. The FWS component (§ IV) is responsible for space platform surveillance and control tasks, autonomy, and TM data processing. The HW functionalities of the OBC are limited to logic-arithmetic operations, data storage, and signal and data transmission. In the case of CubeSats, this distinction becomes more blurred, as the OBC can in many cases perform several functions within the C&DH subsystem and share tasks with other subsystems, as shown in Fig. 2. This is because there is no single, standardized approach to designing OBCs for nanosatellite platforms, and the specific functions often depend on the mission case.

The core of an OBC is the Central Processing Unit (CPU), which is responsible for managing high-level processes within the system. In general, several CPU implementation options are available, using different embedded processors. For CubeSats platforms, most often adopted CPU architectures are quite varied. Early systems use microcontroller ( $\mu$ C)-based architectures for their simplicity of implementation (often integrated with FPGA-based HW accelerators). More recent systems typically opt for integrated SoC architectures. The use of ASICs in CubeSat avionics systems is uncommon, mainly because their design and implementation are complex and expensive. Further

discussion of the OBC implementation choices in CubeSats is provided in §III.

#### **B. RADIATION EFFECTS IN SPACE**

The space environment poses harsh challenges to electronic components, mainly due to ubiquitous radiation. Space radiation produces a chaotic and inhomogeneous environment, characterized by a wide range of particles, energies, and fluxes and is strongly influenced by the level of solar activity. Radiation risk changes significantly in different orbital regions, such as low Earth orbits (LEOs), geostationary orbits (GEOs), and deep space trajectories. Three main sources of space radiation have been identified [27]:

- Radiation belts. These belts surround planets that have a magnetic field, such as Earth, Jupiter, Saturn and Uranus. These belts are responsible for trapping charged particles, especially electrons (e<sup>-</sup>) and protons (p<sup>+</sup>). The magnetic field accelerates e<sup>-</sup> up to energies of the order of 30 MeV and p<sup>+</sup> up to energies of the order of 500 MeV, creating potentially dangerous zones for electronic devices near these celestial bodies. Around the Earth, the radiation belt is called the *Van Allen belt* and is a particularly critical source of radiation for LEO missions. However, this radiation source must also be considered when planning fly-by or randezvouz missions in proximity to other planets with a magnetosphere.

- Solar flares. During solar events, such as so-called flares, solar particle events (SPEs) or coronal mass ejections (CMEs), p<sup>+</sup> with energies of up to 500 MeV and, to a lesser extent, heavy ions with energies of up to 10 MeV/nucleon can be emitted. Flares are influenced by the solar cycle, with a higher number of events occurring during periods of solar maximum.

- Cosmic rays. These high-energy ion streams come from outside the Solar System, probably produced by supernova explosions. Interstellar electromagnetic fields and shock waves scatter the ions and accelerate them to energies of thousands of GeV.

Radiation can damage or cause malfunctioning of electronic devices and systems, causing the so-called radiation-induced effects [28], [29]. These effects can have a substantial impact on the reliability of space systems, causing *faults*, i.e., incorrect hardware or software states, resulting in *errors* in programs or data structures. Such errors can lead to *failures* of space system components [30]. Radiation-induced errors can be classified into two categories: "soft" errors, which can be recovered with power cycles and can cause only temporary component failures, and "hard" errors, which can lead to permanent effects, causing hardware degradation and/or damage [29].

The effects of radiation on semiconductors should not be underestimated during the C&DH design, especially in CubeSats, in which COTS components are commonly used. These effects can be broadly classified into two main groups: cumulative effects and single-event effects (SEEs). The cumulative effects comprise ionizing phenomena, such as the total ionizing dose (TID), and nonionizing phenomena, such as the displacement damage (DD). Cumulative effects, as the term indicates, involve gradual changes in the operational parameters of devices. SEEs, instead, induce abrupt alterations or transient behavior in circuits. The following subsections analyze these effects and their impact on integrated circuit (IC) technologies in detail.

#### 1) CUMULATIVE EFFECTS

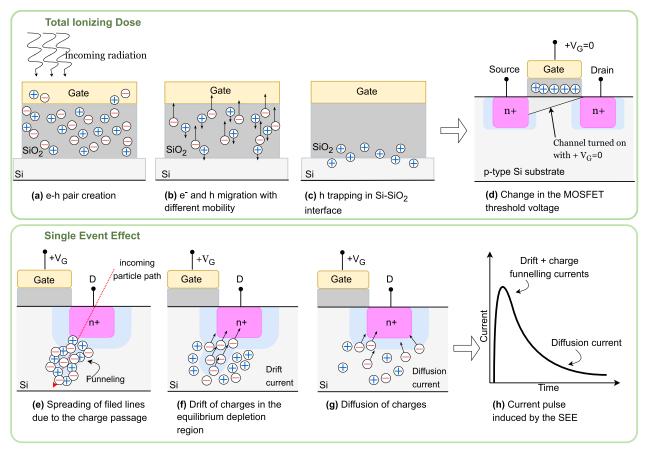

TID accounts for the amount of radiation that impacts electronic components during mission lifetime and is a critical parameter for the design of electrical circuits incorporating metal-oxide-semiconductor field-effect transistors (MOSFETs; [29], [31]). Charged particles, especially e<sup>-</sup> and p<sup>+</sup>, can directly or indirectly ionize semiconductors, creating electron-hole (e-h) pairs in the silicon dioxide layer. Fig. 3 shows the physical process behind the TID degradation mechanism and its impact on the behavior of a MOSFET. The holes created within the oxides led to progressive changes in the device performance parameters. For instance, positive charges collected in gate oxides lead to a decrease and increase in threshold voltage in N-MOS and P-MOS transistors, respectively, as positive charges gradually activate or inhibit gate activation [28], [31]. In addition to threshold voltage shifts, trapped charges are also responsible for increased current leakage, reduced carrier mobility, and increased noise levels. In worst-case scenario, functionality may be completely disabled because of the high leakage current and inability to shut off current between the transistor source and drain [32], [33].

TID is typically measured in rad, where 1 rad(material) is defined by an amount of energy equal to 100 erg deposited per gram of target material. Since the energy absorbed per unit mass varies among materials, the type of material is always specified [e.g., rad (Si)]. The SI unit is gray [Gy], which is equivalent to 100 rad.

Being a cumulative and long-term effect, TID increases over time, causing gradual semiconductor performance degradation and eventual failure of MOS devices [29], [32], [33]. Mitigation of this effect should always be considered in the design of avionics systems for space systems. TID can be mitigated through shielding, careful selection of inherently radiation-resistant components, or redundancy (§II-C). However, it must be emphasized that most CubeSat missions operate in LEO and with a short lifetime [10]. This considerably reduces the risk of TID failures for such missions. Short-duration missions in LEOs typically encounter relatively low TIDs, ranging from 1 to 10 krad(Si) per year, depending on shielding [34], [35], [36], [37]. Commercial ICs typically fail after being exposed to 3-30 krad of radiation [38]. Furthermore, TID is a relevant but not critical - factor in modern COTS  $\mu$ Cs because of manufacturing technology and size scaling, miniaturized oxides in sub-90 nm devices being less susceptible to charge accumulation. Instead, these devices are much more

vulnerable to SEEs [33]. The risk of degradation for TID increases dramatically for long-duration missions or deep-space trajectories.

The second main cumulative radiation effect, called the DD effect, refers to the gradual degradation of the electrical and optical properties of semiconductor devices due to structural damage in the crystal lattice. This damage is caused by collisions of nonionizing radiation particles, which displace Si atoms from their original lattice sites [31], [39]. In space, p<sup>+</sup>, neutrons, and heavy ions are the main sources of DD, while e contribute less because of their smaller cross section. Photons can also cause DD indirectly by producing high-energy secondary e<sup>-</sup> through the Compton effect, especially with prolonged or repeated exposures [33], [40]. DD primarily affects devices whose operating characteristics depend on the bulk properties of the materials, such as photonic and optoelectronic devices. On satellites, the most affected components are photovoltaic cells in solar panels, charge-coupled devices (CCDs) used in many payloads as particle detectors, and photodiodes used in optical communications and camera chips [33]. The performance of MOS devices in OBCs is relatively insensitive to the DD, as they are surface devices that are less affected by bulk defects. Shielding and careful component selection should also protect any critical parts of OBCs against this effect. [40].

#### 2) SEES

SEEs are caused by the prompt interaction of a radiation particle (with energy up to several hundred MeV/nucleon in the case of heavy ions) with MOS devices. SEEs are not cumulative effects. The physical mechanism that produces SEEs can be attributed to the charge deposition induced by the passage of protons and heavy ions in the oxide, followed by the charge collection at the output node of the circuit [27], [31]. Charge collection occurs immediately after the creation of traces left by ionizing particles in the oxide and is driven by three main processes, namely, drift in the depletion region, diffusion, and channeling, as shown in Fig. 3. These three charge collection processes result in a transient current pulse being driven through the device.

Charge deposition is usually modeled using the linear energy transfer (LET) quantity [27], [29], which is the amount of energy transferred per unit length traveled in the target material per unit specific mass density (MeV · cm²/mg). The higher the energy of a charged particle crossing a MOS device, the more energy is deposited on it. Based on the quantity of energy deposited, various effects result, such as single-event transients (SETs), single-event upsets (SEUs) and single-event latch-ups (SELs). The former two are typically soft failures, while the latter is a hard error.

a) SET. This term refers to the creation of a transient spike

of current or voltage in the signal path, which causes

various effects [29]. These are mostly soft errors, often

repairable with power cycling. One possible effect of

a SET is the interaction of the produced current pulse

- with the electronic system internal clock signal. This interaction can widen the clock signal at the trailing edge and can narrow it at the leading edge. This affects the processing speed of the system as a function of the clock signal [41]. In complex systems with synchronized computing nodes, the precise synchronization of all nodes can be severely compromised by a critical SET. Since charged particles can strike electronic components at any time and any place, there is no possible countermeasure to protect the system against an SET except complete radiation shielding [29]. If the voltage spike is captured by a memory cell, register or flip-flop and causes a state change, the SET can become an SEU.

- b) SEU. This occurs when the energy transfer induced by a charged particle causes a stored bit to change. resulting in a change in the state of a flip-flop or memory unit cell (from 1 to 0 or vice versa). The state change can also affect several adjacent memory cells, resulting in a so-called multiple-bit upset (MBU). The effect of an SEU depends on the location and function of the affected bit. Nondestructive effects include corruption of the information stored in a memory element and thus a change in its state. This can be resolved by updating the elements with the correct value (memory scrubbing or device restart). Destructive effects can result in damage to the CPU program, such as computation errors, deadlocks, or incorrect command execution [29]. In LEO, p<sup>+</sup> trapped in the radiation belt and produced during SPEs are the most significant source of SEUs [42], [43]. SEUs are considered a common occurrence for static random access memory (SRAM) devices exposed to radiation, since such devices are based on flip-flop technology. In contrast, flash devices, which are based on electrically erasable programmable read-only memory (EEPROM) technology, are immune to SEUs [29]. Component reliability with respect to SEUs is a major concern when developing OBCs for space applications, especially when COTS components are used. Although cumulative effects and SETs can be mitigated (even partially) by using adequate shielding, this is often not enough to prevent SEU-induced errors. Therefore, their management through the use of fault-tolerant techniques is critical in spacecraft. Watchdog timers and information redundancy techniques, such as error detection and correction (EDAC) schemes, are two of the most classic methods used to mitigate SEUs (see §II-C).

- c) SEL. This is a hard error. It occurs when the energy of the incident particle is so high that it induces an anomalous high-current state in the device, resulting in permanent device failure. If there is no overcurrent protection circuit, the device will burn out. This makes SEL one of the most dangerous SEEs for MOS devices [29]. SELs can be avoided by controlling the power consumption of the chip and separating it from the power supply line if a high current state occurs. SELs can occur in both SRAM and flash devices and

FIGURE 3. Effects of space radiation on electronic components. TID is a cumulative effect due to charge accumulation in the SiO2 layer or at the SiO2-Si interface. This is due to (a) the generation of e-h pairs in the oxide as a result of radiation-induced ionization; (b) the migration of low mobility holes to the SiO2-Si interface; and (c) the trapping of gaps by Si substrate defects or at the interface. (d) Charge accumulation leads to a progressive change in the features of MOSFETs, such as a decrease in threshold voltage in the case of an n-MOS. SEEs are due to the impact of single particles that create e-h pairs along their trajectory and generate (e) the spread of electric field lines, a phenomenon known as funneling, (f) the drift of charges in the equilibrium depletion region and g the charge diffusion, inducing (h) a transient current pulse that can lead to either a temporary or permanent failure. [31]

this mainly relies on the hardware architecture of the device.

#### C. MITIGATING SPACE RADIATION EFFECTS

Managing the effects of radiation on electronic systems is a fundamental aspect of electronic design for space applications. This task can be extremely challenging and costly. There are several strategies to reduce the radiation effects. The most basic approach involves the use of appropriate packaging and shielding. However, this method increases the overall weight of on-board components and is often insufficient to properly protect against ionization phenomena caused by high-energy photons and particles [32]. Furthermore, shielding sometimes compounds radiation effects due to nuclear reactions induced within the packaging materials, which potentially lead to the creation of secondary particles. This process, in turn, induces errors and faults [32], [42]. Shielding, which is always employed in satellites, must therefore be rigorously combined with other mitigation techniques.

Two other approaches include using radiation-hardened (rad-hard) devices and/or implementing fault-tolerant

techniques [44]. Rad-hard systems refer to those designed to be resistant to radiation-induced effects within defined limits limits (see Tab. 1). This resistance is achieved by using appropriate techniques during the manufacturing process [45]. Their development and implementation are often demanding and very expensive. Therefore, although they are widely used in large satellites, their integration into CubeSats remains limited due to their energy consumption, cost constraints, and mission lifetime. CubeSats, especially those intended for low orbits, often incorporate COTS components due to their affordability and quick availability in the market. However, COTS components are more sensitive to radiation than space-grade components [46], [47]. Therefore, their reliable use requires strategic integration with rad-hard components, mitigation techniques and extensive testing [23]. This section summarizes some of the most common key techniques for mitigating radiation-induced system failures within CubeSats. These include hardware redundancy, memory and firmware protection techniques, and protection circuit integration. Multiple of these techniques are often combined when developing an OBC. The choice of a particular technique depends on the specific OBC design and is

TABLE 1. Radiation tolerance levels of COTS, rad-tolerant and rad-hard components. Data from [3].

| Hardness level                     | COTS | Rad Tolerant                       | Rad Hardened                         |  |

|------------------------------------|------|------------------------------------|--------------------------------------|--|

| TID [krad]                         | 2-10 | 20-50                              | $> 10^2 \text{ to} > 10^3$           |  |

| SEU Threshold LET [MeV · cm²/mg]   | < 5  | 20                                 | > 60                                 |  |

| SEU Error Rate<br>[errors/bit-day] | 10-4 | 10 <sup>-7</sup> -10 <sup>-8</sup> | 10 <sup>-10</sup> -10 <sup>-12</sup> |  |

influenced by factors such as on-board processing capacity, mission duration and budget, component specifications, and radiation environment.

#### 1) HARDWARE REDUNDANCY

This technique is very successful in mitigating cumulative effects [46] and SEUs [32]. Redundancy involves the introduction of a duplicate device or component within the system that performs the same functions. Redundancy can be static or dynamic. Dynamic redundancy, also known as *cold redundancy*, activates an unpowered backup component when the original one becomes unreliable or fails completely. Dynamic redundancy is a system-level fault-tolerant technique that can mitigate degradation due to cumulative effects, in that, when one component fails due to radiation accumulation, the unpowered component can take over its tasks. Static redundancy, known as *hot redundancy*, involves the simultaneous operation of redundant components and is used to handle SEU-induced errors [44], [48].

Two commonly used static redundancy techniques are dual modular redundancy (DMR) and triple modular redundancy (TMR; [40]). They are based on the use of two or three identical modules (one of which acts as a voter in the case of TMR) operating in synchrony, performing the same functions simultaneously and comparing their respective outputs. These architectures allow for the detection of a single error in a logical path when the outputs of the modules do not match, rebooting the system when a mismatch is detected [32]. DMR can be implemented at the processing unit level of an OBC, by including two independent chips on the board in a lockstep configuration ([49]); e.g., [50]), or by using multicore processors [51]. TMR can be used at the level of hardware logic (e.g., [52]) or with other components, such as memories (e.g., [53]). The TMR approach improves fault tolerance and reliability, but carries a higher risk of multiple failures over time, potentially reducing the system lifetime [44]. For CubeSat applications, this may be acceptable due to the often short mission duration.

#### 2) MEMORY PROTECTION TECHNIQUES

Memory systems, especially SRAMs, are highly sensitive to SEUs. Memories, in particular caches and register files, are also the main components affected by SEUs in processors [54]. The most commonly used memory protection techniques on OBCs involve employing memory hardware redundancies, utilizing information redundancy techniques

such as EDAC strategies, and implementing periodic memory scrubbing.

EDAC codes are a particular class of error correction codes (ECCs) that use check bits to detect and recover errors in read or transmitted data. These codes can be implemented in hardware, software or a combination of both [55]. When implemented in hardware, the memory architecture is extended to accommodate additional check bits and is called EDAC-corrected memory or ECC memory. Software EDAC strategies are more cost-effective and are implemented in the fault detection isolation and recovery (FDIR) module, which is typically part of the FSW. Hamming codes are the most popular EDAC solutions [56], [57], [58]. They are linear block codes that allow for single-error correction and double-error detection (SECDED). In this approach, the number r of check bits, required to correct for 1-bit errors in a dataword of m bits, can be calculated according to  $m + r + 1 < 2^r$ . An example is the Hamming (12, 8) code, which converts an 8-bit dataword (m) into a 12-bit codeword (m + r), that is capable of correcting for a 1-bit error. More advanced codes, such as the Golay, Reed-Solomon (R-S) and Bose-Chaudhuri-Hocquenghem (BCH) codes, are able to detect and correct multiple errors [59].

To prevent two different particles from hitting the same word during ECC checks and to avoid the accumulation of errors that could result in MBUs, EDAC strategies are often combined with periodic memory scrubbing [60]. Memory scrubbing consists of periodically reading and comparing all data in memory, reloading them if an error is detected. By frequently checking the memory, the ECC can recover an incorrect value before further bit errors occur [32].

In recent years, a new trend that has rapidly emerged in space avionics is the adoption of novel memory technologies, which show higher tolerance to TID and SEEs than standard memories. Among these technologies, ferroelectric RAMs (FeRAMs, [61]) and magnetoresistive RAMs (MRAMs, [62]) are now widely adopted in OBCs, chosen for their ability to retain data in hostile environments, due to their operating principles. FeRAMs store data as electrical charges in polarized ferroelectric capacitors, while MRAMs store data as magnetic charges in magnetic tunnel junctions (MTJs). Their unique operating technology makes them inherently rad-hard, showing reduced vulnerability to SEEs and resistance to a TID of up to 1 Mrad [32]. Other technologies exhibiting similar radiation-tolerant properties, such as resistive RAM (RRAM, [63]) and potentially Phase-change Memories (PCMs, [32]) have also been tested in relevant environments and are poised for future opportunities. A comparison between the performances of these memory technologies and traditional memories is shown in Tab. 3.

#### 3) FIRMWARE PROTECTION TECHNIQUES

Ensuring the reliability of the FSW is a crucial task for a successful space mission. This is particularly true when considering the growing complexity of the on-board software

resulting from the use of CubeSats for increasingly complex mission purposes, the challenging real-time processing capability requirements, and the strong hardware-software dependence in avionics systems. In addition, just like data storage memories, program memory is also subject to SEU-induced failures, thus requiring the integration of fault-tolerance techniques that enable in-orbit firmware maintenance. Two key protection methods are firmware replication [64] and in-orbit firmware updating [65]. Firmware replication involves storing multiple copies of the firmware in different memory allocations or different memories, allowing the firmware to be protected against any corruption of its primary version [64]. A bootloader, a critical software component in the system, checks the integrity of the firmware image and, in case of failure, uploads the uncorrupted version into the program memory [23], [46]. However, it is worth noting that that the bootloader itself represents a single point of failure in a system with only one hardware component or OBC. Indeed, if the bootloader fails, the entire system could become inoperable, compromising mission objectives. To mitigate this risk, hardware-level redundancy, such as multiple physical components in a TMR configuration or multiple OBCs, can be implemented. The in-orbit firmware updating uses a transfer protocol and bootloader to transmit and upload a new version of the firmware image through the uplink channel, providing a facility to upgrade the firmware directly in orbit [65]. This tehnique allows for solving software issues and introducing new functions after satellite launch.

With the widespread adoption of multicore processors and systems even in CubeSat OBCs, other fault-tolerance software methods are emerging, such as firmware task rescheduling, task swapping, and checkpointing [66], [67]. In task rescheduling, a scheduler reassigns the tasks of the core affected by a fault to other processing cores in the system. Task swapping comprises methods that prevent the occurrence of a failure by monitoring the reliability of different cores for all executing applications and evaluating which specific task scheduling can reduce the soft error rate. Last, checkpointing periodically saves the state of a process during error-free execution and, in the event of a fault, restarts task execution to before the error occurred.

## 4) PROTECTION CIRCUITS

These circuits include watchdog timers and overcurrent protection circuits, which provide protection against SEUs and SELs, respectively. The watchdog timer is a clock countdown register that can be internal or external to the processor. When the timer is expired, it then resets the processor (unless the timer is updated by the processor itself), returning it to a predetermined restart position. Such timers can be implemented in both hardware and software and are used to monitor the condition of a processor [68]. If the processor jumps to an incorrect memory location due to an SEU, the watchdog timer resets the processor to a previous state using a checkpoint, thus restoring operations.

Overcurrent and overvoltage protection circuits detect high-current or high-voltage levels and trigger a reset of the power supply, preserving the device from loss of functionality induced by SELs. These circuits are typically small hardware devices that are integrated into the power supply circuit of the OBC board. They include bypass diodes and resistors, which can be used to suppress current and voltage spikes, respectively [23], and latching current limiters (LCLs), which provide timed and controlled monitoring of overcurrent states and interrupt the supply line in case of power overload [69].

#### III. CUBESAT OBCS STATE-OF-THE-ART

The landscape of CubeSat OBCs mirrors the evolutionary trajectory observed in larger spacecraft C&DH subsystems. The current generation of processors exhibits robust capabilities to manage the computational demands of CubeSat missions, offering a spectrum of options ranging from cost-effective COTS solutions to customized proprietary platforms. The emergence of new applications for LEO satellites, along with the migration of COTS electrical, electronic, and electromechanical (EEE) devices from the automotive industry to the space sector - driven by a higher acceptance of risk by the space sector - impacted the growth of the market surrounding CubeSats, which offer low-cost, rapid development solutions for technology demonstration and new mission concepts. This growth has resulted in a proliferation of companies and research institutions developing their own OBC solutions.

The currently available avionics systems can be categorized into two main types: commercial OBCs and mission-specific OBCs [70]. This differentiation is crucial to gain insight into the varied landscape of OBC systems utilized in the realm of CubeSat technology.

Commercial OBCs are single- or multi-board computers that are tested and ready as a finished product on the global market. They are referred to as commercial because they are turnkey devices that can be easily integrated into a satellite. In our analysis, this category includes OBCs marketed by leading private CubeSat companies, such as Alén Space (Spain), EnduroSat (Bulgaria), GomSpace (Sweden), Innoflight (US), ISISpace (Netherlands) and Xiphos (Canada) among others. These OBCs represent versatile solutions for different mission objectives and are designed to serve a wide range of customers and applications. They generally have a wide variety of communication interfaces, making them easy to integrate on-board. This strategic choice not only optimizes the distribution of nonrecurring engineering costs across multiple missions, but also improves the efficiency of software development through the judicious reuse of resources - attributes of considerable allure in a fiercely competitive market landscape. Moreover, they are based on established EEE components, which increases their attractiveness for critical missions requiring proven reliability [23].

Mission-specific OBCs, on the other hand, are often developed in-house by universities, research centres, or companies for missions with specific requirements and objectives.

In terms of components and manufacturing costs, they are generally less expensive than commercial OBCs because they only include the modules needed to optimize resources. However, they require large investments in terms of research and development and have the disadvantage of being designed specifically for a particular mission and thus being less versatile. Among others, our analysis places the CubeSpace processor board family developed by NASA Goddard Space Flight Center (GSFC) in this category. Although these devices feature commercial aspects, such as the incorporation of COTS components and the goal of a flexible architecture adaptable to various missions, they are primarily tailored to meet the specific needs and requirements of NASA missions, thus falling into the mission-specific OBC category.

In this section, we present a review of commercial and mission-specific OBCs currently available on the market or under development. Interesting surveys on avionics intended for small satellites already exist in the literatures [23] and [24], laying the groundwork for similar work to our exploration. However, they focus on the general category of SmallSats. Here, our focus narrows to CubeSat-type satellites, emphasizing the critical role of tailored OBCs in meeting strict constraints of low mass, small form factor and low power [70].

#### A. ARCHITECTURES

In this analysis, we categorize OBCs based on their processing units, which may include traditional µCs, radhard  $\mu$ Ps, FPGAs, and hybrid processors such as FPGA/GPU SoCs. The nature of the processing core of an OBC and its attributes, first of which are processing capabilities, speed and power consumption, are the main factors shaping the overall performance of an OBC. Therefore, they must to be carefully analyzed. We analyzed more than fifty Cube-Sat OBC projects, both commercial and mission-specific, designed by companies and research centers worldwide. Our bibliographic search was based on satellite martketplaces such as satsearch and SatCatalog; public databases such as [4]; and scientific databases such as Scopus, using "onboard data handling" and "on-board computer" as keywords and filtering specifically for "CubeSat" and "nanosatellite". Our targets were mainly research and commercial projects (scientific or technological demonstration missions) funded by government agencies and private companies. However, we also included secondary (academic/educational) projects in our analysis when we considered the results to be technologically interesting or useful from a historical perspective. Our focus was to provide a qualitative assessment of OBCs, identifying trends in their design choices, and emphasizing an understanding of their key attributes rather than quantitative metrics. A representative list of the OBCs considered in our investigation is shown in Tab. 5.

## 1) COTS $\mu$ CS

COTS  $\mu$ Cs have traditionally been the preferred option for early CubeSat avionics systems designed for LEO

missions, especially those with shorter durations and lower processing requirements. The choice of COTS  $\mu$ Cs is largely influenced by their numerous advantages, including low power consumption, minimal weight, proven reliability, easy availability in the commercial market, and user-friendly programming. These features make them perfectly suited to the limited SWaP-C resources typical of nanosatellite missions. These  $\mu$  Cs are typically built on reliable processor architectures, providing the simplest and most cost-effective solution to perform basic OBC tasks, such as telemetry management and storage, command execution, and basic attitude determination and control system (ADCS) functions. Several COTS  $\mu$ Cs have been shown to tolerate the radiation levels typically found in LEO environments [71], making them suitable for CubeSat applications. Among the options are several  $\mu$ Cs from world-leading manufacturers, such as Texas Instruments (TI; MSP430), Microchip Technology (including some PIC, ARM-based or AVR  $\mu$  Cs), ST Microelectronics (STM32).

The  $\mu$ C architecture most commonly used in CubeSat OBCs is based on the ARM Cortex family of processors [72]. These processors are widely used in CubeSat avionics for a multitude of compelling reasons. They have low power consumption, offer a balance between processing power and energy efficiency, and are readily available on the commercial market. In addition, the ARM Cortex family offers a wide range of devices with different performance levels and features, allowing space mission designers to choose the most suitable option for their specific mission requirements. Furthermore, radiation-hardened versions of some ARM Cortex processors are available, which could enable avionics systems based on them to be easily adapted to the challenges of the space environment beyond the LEO. Lastly, ARM-based processors benefit from a strong developer community that provides valuable development and debugging support, making them seamlessly integrated into nanosatellite OBCs. These advantages make ARM Cortex-based µC a common choice for a variety of CubeSat avionics applications, ranging from basic sensor interfacing to more complex data management and processing tasks. Several commercial and mission-specific OBCs are based on ARM Cortex-M and ARM Cortex-R  $\mu$ Cs (see Tab. 5 and [73], [74], [75])

The choice between the ARM Cortex-R and Cortex-M for avionic system design depends on the mission-specific requirements and associated trade-offs. The Cortex-R series is specifically designed for safety-critical applications that require robust real-time support. These processors often feature redundancy schemes for fault tolerance, such as ECCs, lockstep execution, and other safety mechanisms. The Cortex-M series is designed for highly power-efficient applications that require modest deterministic real-time processing. In CubeSat OBCs, ARM Cortex-M  $\mu$ Cs, have emerged as the preferred and most popular option [72], mainly due to their affordability, high availability, and robust development ecosystem.

Several factors influence the process of selecting a particular  $\mu$ C for avionics applications, such as computational performance, power consumption, memory requirements, peripheral needs, compatibility of the operating system (OS) and the availability of an integrated development environment [76]. This process can be challenging and may require extensive testing and qualification procedures [77]. Ultimately, the decision depends on mission requirements and priorities and is often a trade-off between computing and processing capabilities and energy efficiency. For missions with tight energy constraints and low power consumption as a priority, alternative  $\mu$ C choices include MSP430 by TI [78], [79], PIC  $\mu$ Cs by Microchip Technology or and 8-bit and 16bit AVR  $\mu$ Cs by Atmel (now Microchip Technology). Such  $\mu$ C families are renowned for their energy efficiency and simplicity of implementation and are suitable for missions engaged in simple data handling and low-power operations, which operate with less demanding computing requirements. In particular, the MSP430 finds application not only in OBCs [50], [80], [81] but also in payloads [82], [83] and other critical subsystems designed for battery-powered and energyconstrained scenarios. However, these  $\mu$ Cs have limitations in terms of processing capacity and peripheral functions compared to more robust  $\mu$ C families.

To conclude, it is important to note that while COTS  $\mu$ C are the simplest and most cost-effective option for implementing basic OBC functions, their processing limitations make them unsuitable for high computational cost operations or data-intensive applications. In addition, their deployment in missions characterized by elevated radiation levels decreases their reliability. Consequently, some missions opt for higher performance architectures, such as hybrid architectures, SoCs or GPUs.

#### 2) RAD-HARD PROCESSORS

Due to advancements in satellite technology and payload miniaturization, interest in deep-space CubeSat missions has grown in recent years [8]. The design of the C&DH subsystem for these missions is extremely challenging due to the high risk of radiation exposure, which is particularly significant for the space environment beyond the LEO. To ensure the reliability of the electronics and prevent failures caused by high levels of ionizing radiation, the OBCs of these missions cannot rely exclusively on COTS components. It is essential to incorporate radiation-hardened (rad-hard) processors or devices into these missions, especially considering their scientific relevance and costs. One of the most famous and powerful rad-hard  $\mu$ Ps, specifically designed for space applications, is the RAD750  $\mu$  P [84], [85], developed by BAE Systems. This  $\mu P$  has the same architecture and operation as the commercial IBM PowerPC 750, but is specifically designed to be resistant to a TID of up to 200 krad (Si). It is widely used in large space missions (e.g., Mars Reconnaissance Orbiter, MRO; Fermi Gamma-Ray Space Telescope, FGST; James Webb Space Telescope; JWST), claiming a flight heritage of almost 20 years. It is also available in the standardized CompactPCI 3U or 6U formats [86], which is suitable for use in minisatellites [23], [24] or 3U-6U CubeSats. Although the RAD750 has been proposed as the OBC for some deep-space CubeSat projects [87], no deep-space CubeSat mission has been launched to date using this processor. In fact, although RAD750 offers the highest radiation tolerance, its cost is prohibitive for use in nanosatellites [24], [88]. Conversely, LEON processors (based on the SPARC V8 architecture) are widely used in OBCs for deep-space CubeSats. These processors were developed specifically for space applications by ESA and are available in different models (LEON2, LEON3, LEON3-FT, etc; [89]). The FERMI OBC developed by Argotech (Italy) [90] used onboard LiciaCube and ArgoMoon, is based on this type of processor. Although the widespread adoption of rad-hard processors in the CubeSat architecture is still in a nascent stage of development, with this lack of progress mainly attributed to the significant financial investment required for the development of new rad-hard devices, these processors are expected to be increasingly used in future ESA and NASA nanosatellite missions. This prediction is especially relevant given based on the growing interest in using CubeSats beyond LEO.

#### 3) FPGAs

FPGAs have gained considerable attention in recent years for CubeSat missions, particularly due to their reprogrammable hardware nature, enabling fast and efficient parallel processing, or making them suitable for rad-hard architectures.

The use of FPGAs as central processing units in nanoatellites, both in OBC systems [52], [91] and payloads [92], has been explored for years. FPGAs differ from traditional CPUs or  $\mu$ Cs in that they consist of logic gates that can be configured to execute any function and offer parallel processing capabilities. These features offer several advantages over conventional processing units. Specifically, FPGAs allow the design of customized, application-specific architectures that exploit parallel processing capabilities to perform multiple tasks simultaneously. For data-intensive applications that benefit from parallelism and hardware acceleration, such as image processing and analysis and computer vision applications, FPGAs have shown higher energy efficiency compared to conventional hardware accelerators such as multi-core CPUs and GPUs [93].

Additionally, FPGAs allow system inputs and outputs to be reconfigured as needed, enabling system interfacing with multiple memories, sensors, and peripherals [24]. Their parallel processing capability makes them particularly suitable for complex tasks such as image processing, data compression, and sensor data fusion. Numerous space applications can benefit from the use of FPGAs for real-time on-board data preprocessing, resulting in transmission bandwidth savings, such as synthetic aperture radar [94], hyperspectral imaging [95], and optical remote sensing data processing [96]. Additionally, the programmable and configurable nature of FPGAs makes them suitable for designing whole systems on a single chip,

enabling conventional processors, and even multicore and multiprocessor systems [97], to be implemented using logic synthesis. These types of processors are called *soft-core* processors. Commercial OBCs by Sky Labs (Slovenia; [98]) and AAC Clyde Space [99] are examples of architectures that utilize soft-core processors implemented on FPGAs.

FPGAs encompass three primary process technologies: antifuse, FLASH, and SRAM based. Antifuse FPGAs are favored in early space applications [100], [101] as they boast resilience against SEEs and lower power consumption. However, they have the disadvantage of lacking reconfigurability because they are strictly one-time programmable. Flash FPGAs offer advantages similar to those of antifuse FPGAs, including non-volatility and reduced power consumption, but it is difficult to make them highly integrated and low-cost because of their manufacturing complexity. SRAM FPGAs benefit from frequent updates driven by  $\mu P$  advancements that make them the most attractive candidates for implementing complex satellite control algorithms [52], but have the disadvantage of being highly susceptible to SEUs [102], [103]. Rad-hard SRAM FPGAs are currently available and are utilized in some concepts for deep-space applications (such as the NG-MEDIUM device by NanoXplore; [104]; [105]). However, they have high costs that make them prohibitively expensive for smaller and cheaper CubeSat designs [92]. Actually, the radiation susceptibility of these devices can be mitigated by exploiting the reconfigurable hardware nature of FPGAs, which allows the implementation of specific fault-tolerant computing strategies, including internal logic redundancies [91], [103] and memory scrubbing techniques (such as the *Readback* and *Blind* scrubbing [106], [107]). These techniques make FPGAs suitable for designing rad-tolerant and rad-hard soft-core processors and systems. The ESA's LEON processors [89] are famous examples of rad-hard soft-core processors, in which radiation tolerance is achieved by incorporating redundancy and fault tolerance at the design level. The rad-tolerant architecture developed for the OBC of the RadSat mission also shows how, using a modern FPGA, an acceptable level of TID immunity can be achieved without using expensive rad-hard  $\mu$ Ps [88].

Because CubeSats have stringent SWaP-C constraints, FPGAs can be a favorable choice for implementing OBCs and data processing systems, as they provide better performance (in terms of speed) while reducing components and allowing easy implementation of error mitigation techniques.

# 4) HYBRID ARCHITECTURES, SOCS AND FAULT-TOLERANT HYBRID SYSTEMS

The emergence of hybrid architectures has the potential to revolutionize CubeSat on-board computing, greatly improving its performance in terms of processing speed and capability. Hybrid architectures refer to architectures that combine heterogeneous processing units, such as CPUs+FPGAs or CPUs+GPUs, in the same chip (SoC), module (System-on-a-Module, SoM) or board. The main advantage of using hybrid architectures in space applications is the possibility

of assigning applications and algorithms to the portion of the device for which they are best suited to achieve the desired optimal performance [108], improving the speed and throughput of the system.

SoCs are the most popular examples of hybrid architectures. These devices integrate processor cores, memories, peripherals, and FPGA and/or GPU fabrics into a single chip. This integration realizes the advantages of combining different processing modules into one IC, resulting in reduced power consumption, size, and weight, while simultaneously enhancing processing capabilities. As a result, SoCs are ideal for CubeSat applications that require high performance, compact size, and efficient power consumption.

Most state-of-the-art CubeSat OBCs are based on hybrid architectures, particularly CPU + FPGA SoCs (see Tab. 5). Popular COTS SoCs include the AMD-Xilinx Zynq-7000 family (featuring a dual-core ARM Cortex-A9 processor and a 28-nm SRAM FPGA; [109]), MicroSemi Smart-Fusion 2 FPGAs (including a ARM Cortex-A9 core and a SEU-immune flash FPGA; [110]) and AMD-Xilinx Zynq UltraScale+ MPSoC devices [111], available both as CPU+FPGA SoCs (CG devices; featuring a dual-core ARM Cortex-A43, a dual-core ARM Cortex-R5F and a 16-nm finFET FPGA fabric) and CPU+FPGA+GPU SoCs (EG devices, which integrate also a Mali-400 GPU). COTS SoCs are predominantly used in CubeSat OBCs for LEO noncritical applications. Popular examples include the Xiphos Q-Card family (Q7s and Q8s including a Zynq-7000 and a Zynq UltraScale+ MPSoC EG respectively; [112], [113]), AAC Clyde Space Kyrten-M3 (SmartFusion 2 SoC; [114]), Space Inventor Z7000-P4 (Zynq-7000; [115]), and Innoflight CFC-400 (Zynq UltraScale CG; [116]).

Recently, a Zyng UltraScale+ MPSoC EG device was deployed as deep neural network (NN) hardware accelerator onboard the Leopard Data Processing Unit (DPU), developed by KP Labs for the Intution-1 hyperspectral mission [117]. This CubeSat, launched in late 2023, is the first in-orbit demonstration of a deep NN integrated on the edge in a COTS FPGA-based accelerator. This system can be used to accelerate machine learning (ML) and deep learning (DL) models for on-board image and data processing, such as real-time object detection and classification, and data compression, applications that have attracted significant interest in recent years, especially in the EO field [118]. Leopard DPU is capable of completing up to three trillion operations per second, demonstrating the high capabilities of FPGA-based SoCs to accelerate artificial intelligence (AI) inference in space.

Due to the increasing interest in integrating AI algorithms directly onboard satellites, particularly for multispectral and hyperspectral EO missions, many projects have suggested to use CPU+GPU SoCs in the CubeSat field [119], [120], [121]. GPUs are devices consisting of lightweight cores and on-chip memories that were originally designed to accelerate graphics applications, but are now used as hardware accelerators in general-purpose computing. For example, they are used to

increase parallelism in software programs and to accelerate any kind of high-performance application, such as clustering of very large data sets [122]. Different CPU+GPU SoCs, such as the Nvidia Jetson X2i [123] and Xavier NX [124] series and the AMD Embedded G-Series SoC family [125], have been proposed in many CubeSat payload processing systems. The educational nanosatellite Multiview Onboard Computational Imager (MOCI), developed by University of Georgia and planned to be launched by 2024, is one of the first CubeSat to include a Nvidia X2i in the design of its Accelerated Flight Computer (AFC; [126], [127]). Similarly, the Space Edge One (SE-1), a small form factor (0.25 U) onboard computing system developed by Spiral Blue (Australia; [128]), utilizes a Jetson Xavier NX and underwent space testing in 2023. The Unibap SpaceCloud iX5 (Sweden; [129]) is based on a AMD G-Series SoC and is deployed in the Hyperspectral Thermal Imager (HyTI) CubeSat [130], launched in March 2024.

In addition to the goal of integrating complex AI algorithms in space, there is a clear need for high-reliability hybrid solutions. COTS SoCs offer attractive trade-offs between SWaP-C, processing performance and flexibility, but are not rad-hard by design, thus requiring fault mitigation techniques. Recent developments integrate high-performance COTS SoCs with rad-hard or rad-tolerant components in fault-tolerant hybrid OBC architectures. In these systems, the COTS SoC acts as a high-performance node (HPN) for the most demanding computations, while the rad-tolerant component acts as a reliable computing node (RCN) and external supervisor. NASA GSFC has pioneered this type of hybrid approach through the SpaceCube family of processing systems, with SpaceCube V3.0 being the latest development [131]. SpaceCube V3.0 is a computing system (3U-220mm form-factor) that features two HPNs, a Zyng UltraScale+ CG device and a Xilinx-AMD Kintex UltraScale FPGA [132], while a rad-tolerant FPGA (Microchip Technology's RTAX FPGA; [133]) acts as an external supervisor responsible for monitoring, configuring, and scrubbing the HPNs. SpaceCube V3.0 is also available in a smaller version (1U form-factor), SpaceCube v3.0 mini [134], which features a Kintex UltraScale FPGA as a HPN and a rad-tolerant ProSIC FPGA (Microchip Technologies; [135]) as a high-reliability supervisor and watchdog. Such a fault-tolerant hybrid architecture is also featured in some of the systems mentioned above (such as the Xiphos Q-card family, Innoflight CFC-400 and Unibap SpaceCloud iX5) and in the latest high-performance payload processors such as multiMIND [136], the COTS-based Highly Integrated Computer System (CHICS; [137]) and the Scalable On-board Computing for Space Avionics (ScOSA; [138]). multiMIND was developed by Thales Alenia Space Germany as part of the EIVE E/W band demonstration mission [139], which successfully flew in 2023. It is based on a Zynq UltraScale+ MPSoC EG device, with a rad-hard Vorago Cortex-M0  $\mu$ C [140] acting as a robust watchdog and anti-latch-up supervisor circuit. CHICS is currently being developed jointly by EVOLEO Technologies GmbH and Airbus Defence and Space Ottobrunn. It uses a Zynq UltraScale+ MPSoC as the central processing node, which is partitioned into isolated safe and non-safe areas according to the criticality of the application, while a rad-tolerant PolarFire FPGA (soft-core RISC-V; [141]) acts as the external supervisor. Finally, ScOSA, currently under development at the German Aerospace Center (DLR), is a modular SAVOIR-based architecture that also combines COTS-based HNPs with rad-tolerant RCNs, this time in variable numbers and configurations. The minimum configuration uses two Zynq 7020 SoCs as redundant HPNs, while an FPGA, with a rad-tolerant LEON3 soft-core processor, serves as RCN.

#### **B. DESIGN CONSIDERATIONS**

There are several key elements to consider when designing or selecting an OBC for CubeSat applications. These elements must comply with the strict constraints of low power, low mass and small form factor imposed by the standard. This section briefly discusses the factors that must be considered, such as processing core performance, power efficiency, supported types of memory and communication interfaces, and reliability in the space environment [23], [70], [73]. By incorporating these factors, the selection or design of the OBC can be customized to meet the specific requirements and challenges posed by different mission profiles.

#### 1) PROCESSING CORE PERFORMANCE

When designing or selecting an OBC, the performance of the processing core is an important parameter to consider. There are several figures of merit for assessing the performance of a processor (such as the clock rate, million instructions per second [MIPS] or million floating-point operations per second [MFLOPS]). However, for more complex CPU architectures, specific benchmarks should be used [142], [143]. The selection of the processing core should consider performance, power consumption and cost, mission data processing and transmission needs, and the role of the OBC in payload management. In missions with very limited power and where the OBC has simple tasks (limited to on-board health monitoring, TM storage, TC execution, and avionics management),  $\mu$ Cs are the most effective choice. In contrast, in satellites where the OBC has to handle the payload as well, the payload determines the computing demands. Some payloads may require significant computing resources and the use of hardware accelerators (FPGAs and/or GPUs). The processing core of the OBC should also be chosen considering the amount of data to be processed and downloaded to Earth, as it has to handle the data, the bandwidth of the communication subsystem, and the storage memory (type and capacity).

#### 2) MEMORY TYPES

In addition to the processor, the performance of an OBC depends on the memory. There are four different types

of memory in an OBC: boot memory, working memory, safeguard memory and mass storage. The boot memory is a nonvolatile read-only memory (ROM) that contains the FSW firmware and, in particular, the boot loader. This memory is usually implemented as EEPROM [73] or NOR flash memory [70]. These types of memory are inherently immune to SEE, so they are used to store critical FSW processes. The working memory is RAM memory, usually SRAM or dynamic RAM (DRAM), used for the real-time execution of FSW, including the OS kernel and software applications for satellite control. The boot loader loads the OS kernel from the ROM to the RAM and initializes the OBC [73]. The safeguard memory retains its contents after the processor is reset or reconfigured and is used to store critical FSW parameters and satellite configuration data (e.g., the health status of sensors and actuators). The FSW continuously stores selective data in the safeguard memory, which can be accessed after a fault. The safeguard memory is typically a nonvolatile memory (EEPROM, FeRAM, MRAM; [70]). Finally, the mass memory is a nonvolatile memory used to store housekeeping and payload data during periods of no contact with ground stations. Storage memories should be chosen carefully based on several factors. They should be sized considering that the satellite can transmit data to the ground only when it is in a contact window, which often lasts for only a few minutes in the case of LEO satellites. Furthermore, to allow for efficient data transmission, their capacity must be optimized to fit the communication bandwidth, because a storage capacity that exceeds the transmission speed to ground causes resource misallocation. The type of memory should be chosen on the basis of its reliability in maintaining the integrity of the stored data and its resilience to radiation effects. Several options with varying performances are available, summarized in Tab. 3.

#### 3) POWER EFFICIENCY

Power efficiency is a key consideration in the design of the OBC and the choice of CPU and memories, and is directly influenced by the size of the satellite and the available power budget. Although the CubeSat standard itself does not specify power limits, and power availability can vary significantly depending on the size and configuration of the CubeSat, the power available for the C&DH subsystem is generally severely limited. As reported in [144], the total power available on a CubeSat is typically 1-2 W for a 1U CubeSat, 5-6 W for a 3U CubeSat, and for larger CubeSats (6U+) can be around 20 W with body-mounted solar cells, potentially reaching up to 100-120 W with deployable solar cells. As a result, the power consumption of the C&DH subsystem is typically limited to a few W [144] or a few tens of W. As shown in Tab. 5, depending on technology, OBCs for CubeSat used for simple platform control and to handle routine satellite tasks can consume up to 1-5 W. while more complex systems can consume up to tens of W.

#### 4) RELIABILITY

It is crucial to design the OBC to maximize its reliability in harsh space radiation environment. This involves selecting components with sufficient radiation resistance, considering factors such as the orbit and the TID to which they will be exposed. While short-term missions in LEOs typically encounter low radiation levels [34], [35], [36], [37], extended-duration or interplanetary missions face much higher levels of exposure.

In the realm of  $\mu$ Cs, notably, MSP430 and dsPIC33 demonstrated resilience in radiation environments of up to 20 krad (Si) and 15 krad (Si) respectively [71]. Extensive research and characterization of the effects of radiation were also conducted on ARM Cortex-M architectures, which demonstrated their ability to maintain functionality when exposed to up to 50 krad (Si) [145], [146].

FPGAs generally show good TID performance, with resilience levels varying depending on the technology. Modern SRAM FPGAs can function properly in the presence of high ionizing radiation exposure (e.g., Xilinx FPGAs functioning properly up to ≥ 100 krad (Si), with values depending on the family [102]), but their reliable use in space requires specific techniques to mitigate SEU-induced errors [103]. Flash FPGAs generally have a lower acceptable TID due to the radiation-induced charge build-up in the floating gate (e.g., ProASIC 3 FPGA family, which can withstand 20-30 krad of TID [135]), although there are flash FPGAs with rad-hard TID performances (e.g, RTG4 FPGA [147], with TID tolerance up to 100 krad).

Considering the widespread use of COTS components in CubeSats and the growing interest in long-duration and/or beyond LEO missions, which entail significantly higher radiation exposure, it is crucial to conduct a thorough analysis of the radiation susceptibility of the chosen components and evaluate potential mitigation strategies (§ II-C) from the early stages of system development.

#### 5) COMMUNICATION INTERFACES

Ensuring proper data handling and effective communication between the OBC and other satellite subsystems is critical to mission success. Selecting the appropriate data bus is a critical aspect of satellite and OBC architecture design. This choice can be challenging as communication interfaces can potentially represent a bottleneck in the data processing and delivery chain. Therefore, a careful selection of components based on a trade-off analysis between several high-level requirements, such as the data rate, power consumption, availability, simplicity and reliability in the space radiation environment, is paramount [148]. Tab. 4 provides an overview of the data buses most commonly used in CubeSats, highlighting their performance and applications in some CubeSats. This section briefly covers these data buses, their main distinctive features and constraints, and general recommendations for the data bus selection.

CubeSats typically use several types of buses, the most common of which include linear and point-to-point

configurations, with some recent projects proposing wireless data buses (e.g., [149]), which have not yet reached technological maturity. Linear buses are used to connect multiple bus nodes together using the same set of wires or lanes and are widely used in CubeSats because of their simplicity, ease of implementation, and the limited amount of wiring they require [150], although they have limited performance (e.g., data rate) compared to point-to-point topology. The latter can connect only two nodes together, offering higher performance and speed. Linear buses from the military and aeronautical industry, such as MIL-1553, are widely used in large missions, but are very rarely employed in CubeSats due to their high complexity and cost [144]. Instead, the data buses commonly used in CubeSats come from the commercial and automotive industry, exploiting the widely available components and design possibilities, and include the Inter-Integrated Circuit (I<sup>2</sup>C), Controller Area Network (CAN) and RS-485, which are predominant in the majority of current systems [144], [150], [151].