Received 6 March 2024; revised 4 May 2024, 22 May 2024, and 11 June 2024; accepted 18 June 2024. Date of publication 24 June 2024; date of current version 10 July 2024. The review of this article was arranged by Editor K. Nomura.

Digital Object Identifier 10.1109/JEDS.2024.3417994

# A New 13T4C LTPO MicroLED Pixel Circuit Producing Highly Stable Driving Current by Minimizing Effect of Parasitic Capacitors and Stabilizing Capacitor Nodes

# JI-HWAN PARK<sup>10</sup><sup>1,2</sup>, KYEONG-SOO KANG<sup>10</sup><sup>1,2</sup>, CHANJIN PARK<sup>10</sup><sup>1,2</sup>, AND SOO-YEON LEE<sup>10</sup><sup>1,2</sup> (Member, IEEE)

1 Department of Electrical and Computer Engineering, Seoul National University, Seoul 08826, Republic of Korea 2 Inter-University Semiconductor Research Center, Seoul National University, Seoul 08826, Republic of Korea

CORRESPONDING AUTHOR: S.-Y. LEE (e-mail: sooyeon.lee@snu.ac.kr)

This work was supported in part by the Technology Innovation Program or Industrial Strategic Technology Development Program under Grant 20014862; in part by the Development of Driving Technology and Image Quality Improvement Technology for Flexible Microled Displays Using Active Matrix (Am) Method funded by the Ministry of Trade, Industry & Energy (MOTIE), South Korea; and in part by the EDA Tool, IC Design Education Center (IDEC), South Korea.

**ABSTRACT** In this paper, we proposed a new low-temperature polycrystalline oxide (LTPO) thin-film transistor (TFT) pixel circuit for micro light-emitting diode ( $\mu$ LED) displays that produces a highly stable and uniform driving current. The proposed pixel circuit suppresses the current level change along with the sweep signal due to the parasitic capacitances and compensates for the TFT's threshold voltage (V<sub>TH</sub>) variation-induced current error, including even falling shape. In addition, the proposed circuit produces a constant current regardless of the data voltage. As a result, a relative current error rate of less than 2% was achieved across all gray levels under the  $\pm 0.5$  V V<sub>TH</sub> fluctuation. The proposed circuit was verified using HSPICE with a low-temperature polycrystalline silicon (LTPS) TFT and amorphous indium-gallium-zinc-oxide (a-IGZO) TFT model based on the measured data. The simulation analysis confirmed that the optimal sweep signal input position and pulse width modulation (PWM) and constant current generation (CCG) parts connecting method were key design points for stable and uniform performance.

**INDEX TERMS** MicroLED ( $\mu$ LED), pixel circuit, a low-temperature polycrystalline oxide (LTPO) thinfilm transistor (TFT), threshold voltage (V<sub>TH</sub>), compensation, falling time, parasitic capacitor, coupling effect.

# I. INTRODUCTION

Micro light-emitting diode ( $\mu$ LED) is gaining extensive attention as the next generation of display due to its superior characteristics compared to the organic light-emitting diode (OLED), such as high brightness, wide color gamut, low power consumption, and resistance to burn-in [1], [2], [3], [4]. Despite its superior characteristics,  $\mu$ LED has a significant problem in wavelength shift according to current density [5], [6]. Therefore, a conventional driving method for OLED, which changes the luminance by adjusting the current level with fixed emission time, can cause color distortion according to the gray level when applied to  $\mu$ LED display. Hence,  $\mu$ LED has adopted the pulse width modulation (PWM) to change the luminance by adjusting the emission time with the constant current [7], [8], [9].

Generally, a conventional thin-film transistor (TFT)-based  $\mu$ LED pixel circuit consists of a PWM part that adjusts emission time and a constant current generation (CCG) part that produces a constant current to the  $\mu$ LED [10], [11]. The emission time is determined when the ramp-shaped sweep voltage signal (V<sub>SWEEP</sub>) changes the on/off state of the driving TFT in the PWM part (DRT\_PWM) based on the PWM data voltage. However, the subthreshold characteristics of TFTs and the slope of the sweep signal

For more information, see https://creativecommons.org/licenses/by-nc-nd/4.0/

<sup>© 2024</sup> The Authors. This work is licensed under a Creative Commons Attribution-NonCommercial-NoDerivatives 4.0 License.

cause a significant delay in the  $\mu$ LED current turning off, i.e., falling time [12]. Therefore, a circuit compensating for even falling wave-shape variation is necessary for uniform operation. In addition, due to the parasitic capacitors of TFTs between the gate and drain node (C<sub>GD</sub>) or between the gate and source node (C<sub>GS</sub>) [13], [14], continuously varying gate voltage can negatively influence the threshold voltage (V<sub>TH</sub>) compensation accuracy and the constant current supply. Therefore, both the circuit structure and operation scheme should be carefully designed to achieve more stable circuit performance, independent of the parasitic capacitance and sweep signal.

Therefore, we proposed a new 13T4C low-temperature polycrystalline oxide (LTPO) pixel circuit based on PWM driving that supplies a stable amplitude of the square current pulse to  $\mu$ LED and compensates for even falling waveshape under TFT's V<sub>TH</sub> variation. We chose the LTPO backplane because recent high-performance display devices have mainly adopted LTPO [15], [16]. The low-temperature polycrystalline (LTPS) TFT offers high mobility and stability, which is suitable for driving transistors, while amorphous indium-gallium-zinc-oxide (a-IGZO) TFT shows low leakage current, which provides an advantage to switching transistors by minimizing voltage loss from the storage capacitors [17]. The proposed circuit consists of 6 TFTs and 2 capacitors in the PWM part, and 7 TFTs and 2 capacitors in the CCG part. For the stable driving current for  $\mu$ LED, we suggest three key design points: the input position of sweep signal, the connection position between PWM and CCG parts, and the connection timing between PWM and CCG parts. Moreover, we verified the effectiveness of these design strategies by comparing proposed circuit with three slightly modified circuits. The relative current error remains below 2% across all gray levels in the proposed circuit, even with the  $\pm 0.5$  V V<sub>TH</sub> fluctuation in both the driving TFTs of the PWM and CCG parts.

#### **II. PROPOSED PIXEL CIRCUIT**

Typically, TFT-based  $\mu$ LED circuits [10], [18], [19] consist of four stages: initialization, data input, V<sub>TH</sub> compensation, and emission. In the first three stages, the PWM and CCG parts are separated by a switching transistor and concurrently operated. Then, the two parts are connected in the emission stage. In this stage, the drain node of DRT\_PWM is connected to the gate node of driving TFT in the CCG part (DRT\_CCG), enabling DRT\_PWM to directly control the on/off state of DRT\_CCG. The V<sub>SWEEP</sub> changes the sourceto-gate voltage (V<sub>SG</sub>) of DRT\_PWM so that DRT\_PWM turns from an off to an on state at a certain point based on data voltage. This state change makes the gate node of DRT\_CCG have a high voltage to turn off, enabling the operation of PWM. Typically, V<sub>SWEEP</sub> is applied directly to the gate node of DRT\_PWM to modulate its V<sub>SG</sub> directly.

In contrast, we can differentiate the proposed circuit in three aspects: the connection of the PWM and CCG parts during the data input stage, applying  $V_{SWEEP}$  to the source

**TABLE 1.** Comparison of the proposed pixel circuit with conventional  $\mu$ LED pixel circuit.

|                                                                 | 1    |      |      |          |

|-----------------------------------------------------------------|------|------|------|----------|

| Category                                                        | [10] | [18] | [19] | Proposed |

| Backplane                                                       | LTPS | LTPO | LTPS | LTPO     |

| Falling wave-shape compensation                                 | Х    | Х    | Х    | 0        |

| Sweep signal-dependent<br>temporal variation in<br>µLED current | 0    | 0    | 0    | Х        |

| PWM data-dependent<br>peak level variation in<br>μLED current   | 0    | 0    | 0    | Х        |

node of DRT\_PWM, and the indirect connection of the PWM part to the gate node of DRT\_CCG. Here, we compared the proposed pixel circuit with a conventional TFT-based pixel circuit in the Table 1.

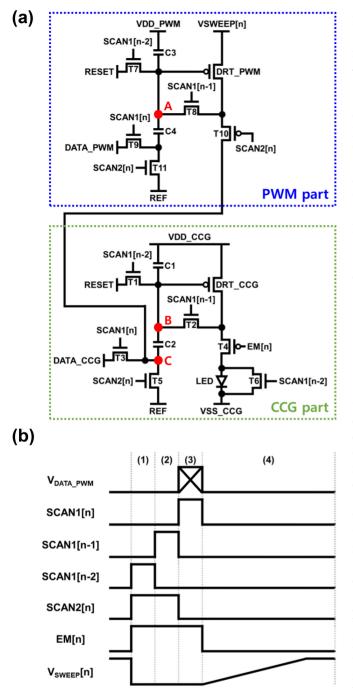

Fig. 1(a) and (b) are the proposed pixel circuit structure and its signal timing diagram. The proposed pixel circuit consists of 13 TFTs and 4 capacitors. DRT\_PWM and DRT CCG are the driving transistors of PWM and CCG parts, respectively, while T1 to T11 are the switching transistors. DRT\_PWM and DRT\_CCG are LTPS TFTs, and all switching transistors except for T4 and T10 are a-IGZO TFTs to prevent stored voltage loss in the capacitor utilizing a-IGZO's extremely low off-current characteristic. C1 to C4 are the storage capacitors that store the data voltage and V<sub>TH</sub> of each part. In particular, C2 and C4 contribute to increasing the input data voltage range by voltage dividing. The size of all TFTs is 3  $\mu$ m/3  $\mu$ m. The capacitance of C1 and C3 is 20 fF, while that of C2 and C4 is 50 fF. Moreover, the voltage signal range for SCAN1[n], SCAN2[n], and EM[n] is set to -8.5 V to 12.5 V. V<sub>DD\_CCG</sub> is set to 5 V, and both V<sub>SS CCG</sub> and the data voltage of CCG part  $(V_{DATA CCG})$  are set to -2 V. Furthermore,  $V_{DD PWM}$ ,  $V_{REF}$ , and V<sub>RESET</sub> are set to 2 V. V<sub>SWEEP</sub>[n] is swept from 6 V (V<sub>SWEEP L</sub>) to 11 V (V<sub>SWEEP H</sub>), and the data voltage range of PWM part (V<sub>DATA PWM</sub>) for adjusting emission time is set to 3 V to 10 V. Moreover, we set  $C_{GD} = C_{GS} = 0.273$ fF for LTPS TFT and  $C_{GD} = C_{GS} = 0.2$  fF for a-IGZO TFT, considering an overlap length of 0.1  $\mu$ m and the gate insulator thickness of each type of TFTs.

The proposed circuit adopts progressive emission driving, which has lower power consumption than the simultaneous one [20]. The circuit operation is divided into four stages: (1) reset, (2)  $V_{TH}$  compensation, (3) data input, and (4) emission.

(1) Reset stage: T1, T6, and T7 are turned on with SCAN1[n-2], and T5 and T11 are turned on with SCAN2[n] for the initialization. Hence, the voltage stored in capacitors C1 to C4 from the previous frame is initialized as follows:  $V_{DD\_CCG} - V_{RESET}$  for C1,  $V_{RESET} - V_{REF}$  for C2,  $V_{DD\_PWM} - V_{RESET}$  for C3, and  $V_{RESET} - V_{REF}$  for C4.

(2)  $V_{TH}$  compensation stage: T1, T6, and T7 are turned off, while T2 and T8 are turned on with SCAN1[n–1]. Subsequently, the current flows through DRT\_CCG and

FIGURE 1. (a) The proposed 13T4C  $\mu \text{LED}$  pixel circuit structure, and (b) its signal timing diagram.

DRT\_PWM until the drain node of both TFTs reaches  $V_{DD_CCG} - V_{TH_DRT_CCG}$  and  $V_{SWEEP_L} - V_{TH_DRT_PWM}$ , respectively. Here,  $V_{TH_DRT_CCG}$  and  $V_{TH_DRT_PWM}$  represent the  $V_{TH}$  of DRT\_CCG and DRT\_PWM, respectively. Moreover,  $V_{SWEEP_L}$  represents the low voltage level of the sweep signal. As a result, C1 and C3 store  $V_{TH}$  of DRT in both CCG and PWM parts.

(3) Data input stage: SCAN2[n] decreases to a low voltage to turn off T5 and T11, and SCAN1[n-1] also decreases to a

low voltage to turn off T2 and T8. Subsequently, T3 and T9 are turned on with the SCAN1[n] to apply the data voltage for each part. Therefore, node A voltage becomes  $V_{SWEEP_L}$  –  $V_{TH_DRT_PWM}$  + ( $V_{DATA_PWM}$  –  $V_{REF}$ ) × C4/(C3 + C4), and node B voltage becomes  $V_{DD_CCG}$  –  $V_{TH_DRT_CCG}$  + ( $V_{DATA_CCG}$  –  $V_{REF}$ ) × C2/(C1 + C2). Usually, PWM and CCG parts are connected in the emission stage [18], [19]. However, our circuit connects PWM and CCG parts through the SCAN2[n] signal before the emission stage to keep the stored voltage in C1 stable. The effect of the pre-connection of two parts before the emission stage will be discussed in the next section.

(4) Emission stage: SCAN1[n] and EM[n] decrease to a low voltage, so all switching TFTs are turned off except for

T4 and T10. Consequently, the current flowing through the  $\mu$ LED current can be expressed by the following equation due to the stored voltage in C1.

$$I_{\mu \text{LED}} = 0.5\mu_{\text{p}}\text{C}_{\text{ox}}(\text{W/L})$$

$$\cdot \left(\text{V}_{\text{SG}_{\text{DRT}_{\text{CCG}}} - -\text{V}_{\text{TH}_{\text{DRT}_{\text{CCG}}}}\right)^{2} \qquad (1)$$

$$I_{\mu \text{LED}} = 0.5\mu_{\text{p}}\text{C}_{\text{ox}}(\text{W/L})$$

$$\cdot \left\{ \left( V_{\text{REF}} - -V_{\text{DATA}\_\text{CCG}} \right) \times \frac{\text{C2}}{\text{C1} + \text{C2}} \right\}^2 (2)$$

where  $I_{\mu \text{LED}}$  represents the  $\mu \text{LED}$  current during the emission stage,  $\mu_p$  is mobility of DRT\_CCG, C<sub>ox</sub> is oxide capacitance, W is width of DRT\_CCG, and L is length of DRT\_CCG. As indicated by equation (2), the  $I_{\mu \text{LED}}$  is independent of the V<sub>TH\_DRT\_CCG</sub>, so the proposed pixel circuit can compensate for the V<sub>TH\_DRT\_CCG</sub> variation and supply constant current. Note that V<sub>SWEEP</sub>[n] is supplied to the source node of DRT\_PWM in the proposed circuit, while it is usually supplied to the gate node. This structure minimizes the effect of V<sub>SWEEP</sub>[n] on the shape of the square current pulse, which is caused by the coupling effect of the DRT\_PWM's parasitic capacitor. The next section also verifies how the V<sub>SWEEP</sub> connection affects the pulse amplitude.

When  $V_{SWEEP}[n]$  increases and exceeds  $V_{TH_DRT_PWM}$ , DRT\_PWM is turned on, and the  $V_{SWEEP}[n]$  is applied to node C through T10, so the node C voltage also increases. Subsequently, when  $V_{SG_DRT_CCG}$  decreases and becomes smaller than  $V_{TH_DRT_CCG}$ , DRT\_CCG turns off, leading to the termination of light emission. Meanwhile, the equation determining the end of emission can be expressed as follows:

$$V_{SG_DRT_PWM} > V_{TH_DRT_PWM}$$

(3)

$$V_{SWCED}[n] > (V_{DATA_PWM} - V_{PEE}) \times \frac{C4}{(4)}$$

$$V_{SWEEP}[n] > (V_{DATA_PWM} - V_{REF}) \times \frac{1}{C3 + C4}$$

(4)

Consequently, according to equation (4), emission time can be adjusted by comparison between  $V_{DATA_PWM}$  and  $V_{SWEEP}[n]$ , regardless of the  $V_{TH_DRT_PWM}$ . If the PWM part is connected to node B, a stored voltage loss in C1 will occur at the falling time, increasing the compensation error rate due to the falling shape deviation.

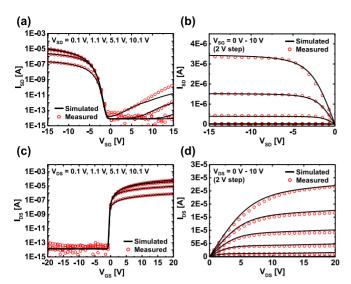

**FIGURE 2.** Measured and simulated results of (a) the transfer curve and (b) the output curve of LTPS TFT, and (c) the transfer curve and (d) the output curve of a-IGZO TFT (dotted symbol represents measured results, and black line represents simulated results).

#### **III. SIMULATION RESULTS AND DISCUSSIONS**

The proposed pixel circuit was verified using HSPICE by Synopsys. We assumed  $340 \times 422$  resolution with a 60 Hz frame rate. Additionally, the total emission time is set to 2 ms. We developed the libraries of the LTPS TFT and a-IGZO TFT based on the measured data. The fabricated LTPS TFT has a size of 300  $\mu$ m/400  $\mu$ m, and for a-IGZO TFT, the size is 24  $\mu$ m/21  $\mu$ m. The measured characteristics for LTPS TFT are V<sub>TH</sub> = -1.53 V, mobility = 80.1 cm<sup>2</sup>/V·s, and subtreshold swing (S.S) = 396.6 mV/dec. For a-IGZO TFT, the corresponding values are V<sub>TH</sub> = -0.46 V, mobility = 17.7 cm<sup>2</sup>/V·s, and S.S = 81.6 mV/dec. As shown in Fig. 2, the simulated data was well fitted based on the measured data, achieving a coefficient of determination over 0.9996.

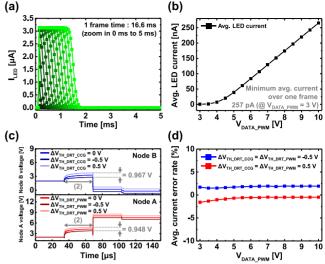

As shown in Fig. 3(a) and (b), the proposed pixel circuit can control the emission time and luminance of  $\mu$ LED by adjusting V<sub>DATA PWM</sub> based on the constant current driving. Here, the minimum average current over one frame at  $V_{DATA PWM} = 3 V$  is 257 pA. We applied simultaneous variations of  $\pm 0.5$  V to both V<sub>TH DRT CCG</sub> and V<sub>TH DRT PWM</sub> to verify the stability of the proposed circuit. Fig. 3(c) demonstrates the voltage variations of nodes A and B over time. After storing the  $V_{TH\_DRT\_CCG}$  and  $V_{TH DRT PWM}$  in stage (2), the node voltage difference of about 1 V between before and after the V<sub>TH</sub> fluctuation should be maintained until the end of the frame. This value represents the difference in V<sub>TH</sub> fluctuation for DRT\_CCG and DRT\_PWM. Therefore, the proposed circuit enables stable operation even in the V<sub>TH</sub> variations, having less than a 2% relative current error rate across all gray levels, as shown in Fig. 3(d). We compared three different circuits with proposed circuit to verify these stable results based on three key factors.

**FIGURE 3.** The simulated results of (a)  $\mu$ LED current, (b) the average  $\mu$ LED current, (c) the change of node A voltage and node B voltage over time (V<sub>DATA PWM</sub> = 8 V), and (d) the relative average current error rate.

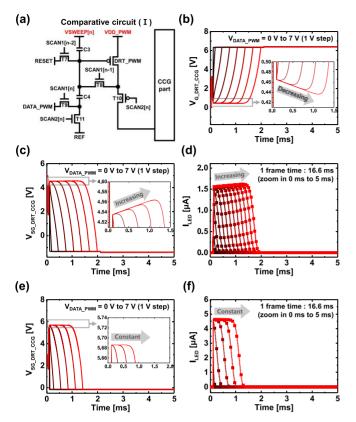

### A. INPUT POSITION OF SWEEP SIGNAL

Fig. 4(a) depicts the circuit (I) where applying point of the sweep signal and V<sub>DD\_PWM</sub> are interchanged compared to the proposed pixel circuit while the CCG part is the same as the proposed one. During emission stage of the circuit (I), the V<sub>SG DRT PWM</sub> increases as the V<sub>SWEEP</sub>[n] signal continuously decreases. When it surpasses V<sub>TH DRT PWM</sub>, DRT\_PWM is turned on to terminate light emission. This operation closely resembles the emission stage of the proposed circuit. However, as V<sub>SWEEP</sub>[n] decreases during the emission stage, the gate node voltage of DRT\_CCG decreases (V<sub>G DRT CCG</sub>) due to the C<sub>GD</sub> of DRT\_PWM, causing an increase in V<sub>SG DRT CCG</sub>, as shown in Fig. 4(b) and (c). Consequently, as illustrated in Fig. 4(d), the  $\mu$ LED current does not remain constant but increases during emission time. Such current level variation during the light emission induces wavelength shift in the  $\mu$ LED and results in image distortion. We also adjusted the parasitic capacitancerelated parameters in the TFT model library to modify C<sub>GD</sub>  $= C_{GS} = 0$  and simulated on comparative circuit (I). As can be seen from Fig. 4 (e) and (f), V<sub>SG DRT CCG</sub> and  $\mu$ LED current are not affected regardless of the change in  $V_{SWEEP}[n]$  when  $C_{GD} = C_{GS} = 0$ . Therefore, we confirm that the parasitic capacitances significantly affect the circuit operation. Therefore, it is effective to apply V<sub>SWEEP</sub>[n] at the source node of DRT\_PWM to minimize the impact of sweep signal through the parasitic capacitor to achieve high image quality.

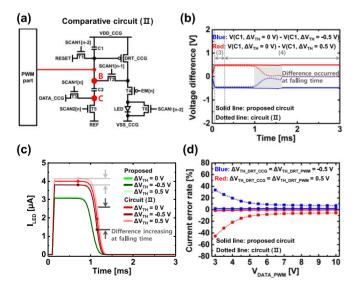

# **B. CONNECTION POSITION BETWEEN PWM AND CCG PARTS**

Fig. 5(a) illustrates the circuit (II) where the PWM part is connected to node B instead of node C of the CCG part. The PWM of circuit (II) has the same circuit structure as

**FIGURE 4.** (a) The schematic of comparative circuit (l) applying V<sub>SWEEP</sub>[n] at the gate node of DRT\_PWM, the simulation result of (b) the gate node voltage of DRT\_CCG, (c) V<sub>SG</sub> of DRT\_CCG, (d)  $\mu$ LED current (V<sub>DATA\_PWM</sub> = 0 V to 7 V), (e) V<sub>SG</sub> of DRT\_CCG when C<sub>GD</sub> = C<sub>GS</sub> = 0, and (f)  $\mu$ LED current when C<sub>GD</sub> = C<sub>GS</sub> = 0 (V<sub>DATA\_PWM</sub> = 0 V to 7 V).

**FIGURE 5.** (a) The schematic of comparative circuit (II) where the PWM part is connected to the gate node of DRT\_CCG, (b) stored voltage difference at C1 when the  $\Delta V_{TH} = 0$  V and when the  $\Delta V_{TH} = \pm 0.5$  V, (c) the simulation result of  $\mu$ LED current (V<sub>DATA\_PWM</sub> = 8 V), and (d) the relative current error rate of proposed circuit and comparison circuit.

the proposed one. Fig. 5(b) shows the simulation results of the stored voltage difference in C1 caused by  $V_{TH}$  change ( $\Delta V_{TH}$ ) as much as  $\pm 0.5$  V. The stored voltage difference

**FIGURE 6.** (a) The schematic of comparative circuit (III) connecting PWM and CCG parts at emission stage, (b) the simulation result of  $\mu$ LED current (V<sub>DATA\_PWM</sub> = 3 V to 10 V), and (c) operation in data input and emission stage of circuit (III).

in C1, corresponds to the change in V<sub>TH DRT CCG</sub>, should be maintained 0.5 V until the end of the emission, including the falling time, if the V<sub>TH</sub> compensation is as successful as the proposed one. However, in the case of a circuit (II) where the PWM part is connected to gate node of DRT CCG (node B), the stored voltage difference of 0.5 V could not be maintained. V<sub>SWEEP</sub>[n] is directly applied to node B through DRT\_PWM and T10 at the emission stage, so it affects the stored V<sub>TH DRT CCG</sub> and V<sub>DATA CCG</sub> in C1 during falling time leading to stored voltage loss. Eventually, circuit (II) has a larger  $\mu$ LED current difference during falling time as shown in Fig. 5(c). As a result, it leads to a much higher relative current error rate compared to the proposed circuit, as depicted by the dotted line in Fig. 5(d). This error rate tends to increase, particularly in low gray levels where the falling time affects  $\mu$ LED current dominantly due to shorter emission time. Therefore, compensation accuracy can be improved by indirectly connecting the CCG part.

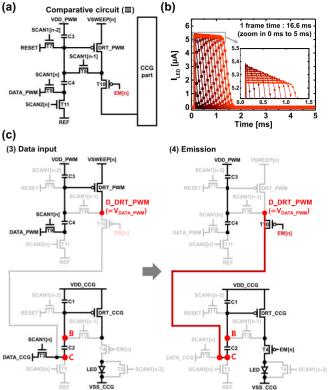

# C. CONNECTION TIMING BETWEEN PWM AND CCG PARTS

As shown in Fig. 6(a), during the emission stage, the circuit (III) connects the PWM and CCG parts by applying the EM[n] signal to T10 instead of the SCAN2[n] signal. All other circuit parameters and operations are the same as the proposed one. The simulation results show that the

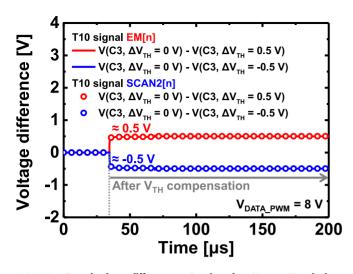

**FIGURE 7.** Stored voltage difference at C3 when the  $\Delta V_{TH} = 0$  V and when the  $\Delta V_{TH} = \pm 0.5$  V (V<sub>DATA\_PWM</sub> = 8 V).

circuit (III) produces different current levels depending on the gray level, which can cause color distortion, as depicted in Fig. 6(b). During the V<sub>TH</sub> compensation stage, the drain node of DRT\_PWM (D\_DRT\_PWM) voltage becomes  $V_{SWEEP}[n] + V_{TH DRT PWM}$ , and this node maintains a floating state. Subsequently, during the data input stage, this node voltage changes proportionally to VDATA PWM due to the coupling effect of DRT\_PWM's C<sub>GD</sub>. When EM[n] becomes a low voltage, the PWM and CCG parts are connected, and the light emission begins until DRT\_PWM is turned on. Meanwhile, the D\_DRT\_PWM voltage affects the stored voltage in C1. This is because the stored voltage value in C1 changes due to charge conservation, similar to the principle of the data input as depicted in Fig. 6(c). In contrast, the proposed circuit pre-connects PWM and CCG parts through the SCAN2[n] signal during the data input stage, and it ensures the stable node C voltage without causing voltage fluctuations in C1. Meanwhile, when the PWM and CCG parts are connected at the data input stage, the voltage at the source and drain nodes of DRT PWM have constant voltage value. As a result, the  $V_{TH_DRT_PWM}$  stored in C3 is preserved without any voltage loss due to parasitic capacitances. As shown in Fig. 7, the voltage difference stored in C3 between  $\Delta V_{TH_DRT_PWM} = \Delta V_{TH_DRT_CCG} =$ 0 V and  $\Delta V_{TH DRT PWM} = \Delta V_{TH DRT CCG} = \pm 0.5$  V is consistent with the difference in threshold voltage, regardless of the control signal applied to T10. Therefore, connecting at the data input stage does not significantly affect the compensation accuracy of the proposed pixel circuit.

#### **IV. CONCLUSION**

In this paper, we proposed a new 13T4C LTPO  $\mu$ LED pixel circuit that ensured a highly stable and uniform driving current with less than 2% relative errors throughout all gray levels. We suggested three key design points for stable operation. Firstly, the effect of parasitic capacitors can be minimized by applying the V<sub>SWEEP</sub>[n] signal to the source

node of DRT\_PWM so that the circuit can provide a stable square current pulse independent of the  $V_{SWEEP}[n]$  signal. Secondly, we designed the circuit that indirectly connects the PWM part and the gate node of DRT\_CCG to maintain the compensated stored  $V_{TH}$  in the capacitor even during falling time. Hence, the circuit can maintain not only a constant current level but also a uniform falling wave-shape under the variations of  $V_{TH_DRT_CCG}$ . Lastly, we connect the PWM and CCG parts during the data input stage to stabilize node voltage, so the circuit can ensure reliable voltage storage in C1. Thus, the current amplitude remains constant regardless of the gray level.

Through HSPICE simulation, we have systematically analyzed the proposed circuit design strategies to prove its structural advantages. In conclusion, our proposed pixel circuit can generate a constant current amplitude even during falling time, minimize the influence of the sweep signal, and ensure stable circuit operation despite variations in V<sub>TH</sub>.

#### REFERENCES

- Z. Y. Fan, J. Y. Lin, and H. X. Jiang, "III-nitride micro-emitter arrays: Development and applications," *J. Phys. D Appl. Phys.*, vol. 41, no. 9, 2008, Art. no. 94001, doi: 10.1088/0022-3727/41/9/094001.

- [2] T. Wu et al., "Mini-LED and micro-LED: Promising candidates for the next generation display technology," *Appl. Sci.*, vol. 8, no. 9, p. 1557, 2018, doi: 10.3390/app8091557.

- [3] G. Biwa, A. Aoyagi, M. Doi, K. Tomoda, A. Yasuda, and H. Kadota, "Technologies for the crystal LED display system," *J. Soc. Inf. Display*, vol. 29, no. 6, pp. 435–455, 2021, doi: 10.1002/jsid.993.

- [4] J.-H. Kim et al., "15-1: PWM pixel circuit with LTPS TFTs for micro-LED displays," *Proc. SID Tech. Dig.*, vol. 50, no. 1, pp. 192–195, 2019, doi: 10.1002/sdtp.1288.

- [5] Z. Gong et al., "Size-dependent light output, spectral shift, and self-heating of 400 nm InGaN light-emitting diodes," *J. Appl. Phy.*, vol. 107, no. 1, pp. 192–195, 2010, doi: 10.1063/1.3276156.

- [6] D.-H. Kim, Y. Park, D. Kang, K.-K. Kim, T.-Y. Seong, and H. Amano, "Combined effects of V pits and chip size on the electrical and optical properties of green InGaN-based lightemitting diodes," *J. Alloys Comp.*, vol. 796, pp. 146–152, Aug. 2019, doi: 10.1016/j.jallcom.2019.05.070.

- [7] K.-S. Kang, J.-H. Park, J. Kang, C. Park, C. Jeong, and S.-Y. Lee, "A compact amorphous In–Ga–Zn–Oxide thin film transistor pixel circuit with two capacitors for active matrix micro light-emitting diode displays," *J. Electron Devices Soc.*, vol. 11, pp. 204–209, 2023, doi: 10.1109/JEDS.2023.3261275.

- [8] C.-L. Lin et al., "Mini-LED backlight driving circuit using PWM method with power-saving mechanism," J. Electron Devices Soc., vol. 10, pp. 256–262, 2022, doi: 10.1109/JEDS.2022.3157935.

- [9] C. H. Ke, Y. S. Lin, and C. L. Lin, "A novel mini-LED backlit driving circuit using PWM mechanism with VTH and VSS I-R rise compensation," in *Proc. 29th Int. Workshop Active-Matrix Flatpanel Displays Devices*, 2022, pp. 25–28, doi: 10.23919/AM-FPD54920.2022.9851295.

- [10] Y.-H. Hong, E. Jung, Y.-R. Jeong, H. Im, and Y.-S. Kim, "Micro light-emitting diode pixel circuit based on p-type low-temperature polycrystalline silicon thin-film transistor for mobile displays," *IEEE Tran. Electron Devices*, vol. 70, no. 9, pp. 4662–4668, Sep. 2023, doi: 10.1109/TED.2023.3296068.

- [11] E. Jung, Y.-H. Hong, S. Hong, K. Park, S.-Y. Lee, and Y.-S. Kim, "61-4: A new pixel circuit based on LTPO backplane technology for micro-LED display using PWM method," in *SID Symp. Dig. Tech. Papers*, vol. 52, 2021, pp. 876–879, doi: 10.1002/sdtp.14824.

- [12] E. P.-A. Zou et al., "A new analog PWM pixel circuit with metal oxide TFTs for micro-LED displays," *IEEE Trans. Electron Devices*, vol. 69, no. 8, pp. 4306–4311, Aug. 2022, doi: 10.1109/TED.2022.3178363.

- [13] X. Cheng, S. Lee, and A. Nathan, "TFT small signal model and analysis," *IEEE Electron Device Lett.*, vol. 37, no. 7, pp. 890–893, Jul. 2016, doi: 10.1109/LED.2016.2575924.

- [14] H. Bae et al., "Extraction technique for intrinsic subgap DOS in a-IGZO TFTs by de-embedding the parasitic capacitance through the photonic C–V measurement," *IEEE Electron Device Lett.*, vol. 34, no. 1, pp. 57–59, Jan. 2013, doi: 10.1109/LED.2012.2222014.

- [15] C. L. Fan, C. Y. Chen, S. Y. Liu, and W. Y. Lin, "AMOLED pixel circuit using LTPO technology supporting variable frame rate from 1 to 120 Hz for portable displays," *Micromachines*, vol. 13, no. 9, p. 1505, 2022, doi: 10.3390/mi13091505.

- [16] H. Qiu et al., "A low power and IR drop compensable AMOLED pixel circuit based on low-temperature poly-Si and oxide (LTPO) TFTs hybrid technology," *IEEE J. Electron Devices Soc.*, vol. 10, pp. 51–58, 2021, doi: 10.1109/JEDS.2021.3132693.

- [17] J. F. Wager, "Flat-panel-display backplanes: LTPS or IGZO for AMLCDs or AMOLED displays?" *Inf. Display*, vol. 30, no. 2, pp. 26–29, 2014, doi: 10.1002/j.2637-496X.2014.tb00698.x.

- [18] J. Oh et al., "Pixel circuit with P-type low-temperature polycrystalline silicon thin-film transistor for micro light-emitting diode displays using pulse width modulation," *IEEE Electron Device Lett.*, vol. 40, no. 10, pp. 1496–1499, Oct. 2021, doi: 10.1109/LED.2021.3107152.

- [19] J. Oh, J.-H. Kim, E. Jung, J. Min, H. Im, and Y.-S. Kim, "Investigation on operation robustness of p-type low-temperature polycrystallinesilicon thin-film transistor-based micro light-emitting diode pixel circuit using pulse width modulation under component fluctuation," *J. Inf. Display*, vol. 23, no. 3, pp. 185–192, 2022, doi: 10.1080/15980316.2022.2029778.

- [20] E. Jung, Y.-H. Hong, S.-H. Ahn, H. Im, and Y.-S. Kim, "P-73: Student poster: MicroLED pixel circuit based on metal oxide thin-film transistor with progressive emission method using pulse width modulation," in *SID Symp. Dig. Tech. Papers*, vol. 53, 2022, pp. 1312–1315.