## CJE

#### RESEARCH ARTICLE

# A Multi-Channel CMOS Analog Front-End Interface IC with 157.8 dB Current Detection Dynamic Range

Kunyu WANG<sup>1,2</sup>, Wenjing XU<sup>1</sup>, Chengbin ZHANG<sup>1</sup>, Yanjun YANG<sup>3</sup>, Man-Kay LAW<sup>4</sup>, Li ZHOU<sup>1</sup>, Jie CHEN<sup>1</sup>, and Ming CHEN<sup>1</sup>

- 1. Institute of Microelectronics of the Chinese Academy of Science, Beijing 100029, China

- 2. University of Chinese Academy of Sciences, Beijing 100049, China

- 3. Zunyi Normal University, Zunyi 563006, China

- 4. Institute of Microelectronics and Dept. of ECE, FST, University of Macau, Macau 999078, China

Corresponding author: Ming CHEN, Email: chenming1@ime.ac.cn Manuscript Received May 26, 2022; Accepted February 14, 2023 Copyright © 2024 Chinese Institute of Electronics

Abstract — A high dynamic range and low-noise CMOS (complementary metal-oxide-semiconductor transistor) front-end interface integrated circuit (IC) with multi-channel detection is presented in this paper. Two different current detection channels, composed of a trans-impedance amplifier (TIA) and an integrator-differentiator TIA, are used to boost the current detection range. A capacitance-coupled instrument amplifier (CCIA) is also included to realize high precision voltage detection. A fourth-order sigma-delta modulator using a second-order loop filter and a second-order noise shaping integral quantizer is adopted to realize effective number of bits above 16 bits. The presented interface IC is implemented in 0.18-μm CMOS process with supply voltage of 3.3 V, and a proto-type electrochemical sensor platform with miniaturized sensor array is developed to verify the functionality of the interface IC. Measurement results indicate that the designed interface IC achieves 157.8 dB current detection dynamic range, and the measured input-referred current noise and voltage noise floor are 1.04 pA and 58.4 nV within 10 kHz integration bandwidths, respectively.

**Keywords** — Readout integrated circuit, Sigma-delta modulator, Complementary metal-oxide-semiconductor transistor, Current detection dynamic range.

Citation — Kunyu WANG, Wenjing XU, Chengbin ZHANG, et al., "A Multi-Channel CMOS Analog Front-End Interface IC with 157.8 dB Current Detection Dynamic Range," Chinese Journal of Electronics, vol. 33, no. 2, pp. 393–402, 2024. doi: 10.23919/cje.2022.00.137.

## I. Introduction

In the field of environmental monitoring, rapid and real-time acquisition of all kinds of pollution variables is always necessary. For example, in a water quality monitoring system, temperature, pH value, heavy metal ion concentration and non-metal ion concentration are all needed to be monitored by different sensors, the output signal of these sensors are different from each other. For electrochemical sensors, the output current ranges from  $\pm 10$  pA to  $\pm 1$  mA, while for pH sensors, the output voltage ranges from  $\pm 1$  mV to  $\pm 1$  V [1]. Moreover, heavy metal ions are usually tested by the potentiostat method, a programmable waveform generator is usually needed.

Some printed circuit-board level monitoring system has been developed [2], however, many peripheral devices are needed in these systems, and this makes these systems complicated and highly cost. Integration of multi-sensor CMOS (complementary metal-oxide-semiconductor transistor) analog front-end (AFE) chips has become the main solution for multi-variable real-time monitoring. Recently, such CMOS AFE interface integrated circuits (ICs) have been reported [3]–[12]. However, these interface ICs are designed for specific sensors and their dynamic detection range is limited, which makes them inappropriate for various signal measurements, such as water monitoring. Amperometric readout circuit with 140 dB detec-

tion range was implemented in [13], [14], while it does not have programmable bias voltage generator for potentiostat sensors. In [15], a three-electrode AFE chip with a current detection dynamic range of 120 dB is proposed, it can basically meet the detection of heavy metal ions in liquid. However, the chip cannot convert multiple input types of signals, and the system linearity is low, which makes it difficult to apply to a comprehensive water quality inspection system. Hence, new AFE interface circuits with wide input range of all kinds of signals and necessary bias voltages are needed. In order to meet the requirements of single AFE chip docking of various types of sensors, it is necessary to design a chip that can process multiple types of input signals and has large dynamic range. In this paper, to meet the requirements of connecting with various water quality monitoring sensors, it is necessary to realize the ability to process voltage and current signals, and the dynamic range of voltage signal monitoring above 60 dB and the dynamic range of current signal monitoring above 150 dB. A multi-channel CMOS AFE interface IC with 157.8 dB current detection dynamic range and 60 dB voltage detection dynamic range is proposed in this paper. An integrator cascade differentiator TIA (trans-impedance amplifier) structure is adopted to improve the current detection precision to 10 pA. A capacitance coupled instrumentation amplifier is also embedded to monitor small differential voltage signal and calibrate the offset of PGA (programmable gain amplifier). Moreover, low noise amplifiers, correlated double sample (CDS) and chopping techniques are also used to obtain high precision detection.

## II. System Architecture

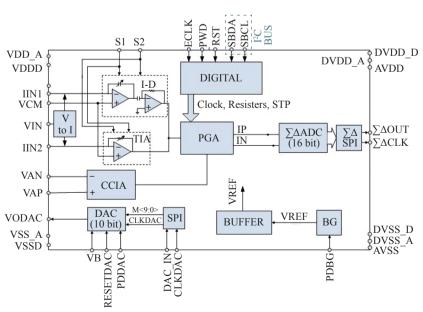

The block diagram of the system is shown in Figure 1. It includes two current detection channels with input IIN1 and IIN2, a single-ended voltage detection channel

with input VIN, and a differential voltage detection channel with input VAP and VAN. One current channel is composed of integrator cascade with differentiator (I-D), and it is used to detect current from 10 pA to 1 µA. The other current channel is composed of a traditional TIA and it is used to detect current from 1 µA to 1 mA. The switch between two channels is controlled by a feedback loop composed of PGA. ADC (analog to digital converter). data processing module, and I<sup>2</sup>C bus. When the data processing module detects the current corresponding to the ADC output code value detected is greater than 100 nA at I-D TIA detecting channel, it will send a channel switching signal to the chip through the I<sup>2</sup>C bus changing the current detecting channel to TIA channel. When the detection channel is TIA channel, the working state is opposite. Single voltage signal VIN is converted to current first through V to I circuit, and then is sent to either I-D TIA or TIA depend on its amplitude. V to I module is composed of resistors, and the resistance value is controlled by the digital circuit. According to the feedback information of the quantized value, the appropriate resistance value is used to convert the input voltage. The small differential voltage signal is processed by capacitivecoupled instrumentation amplifier (CCIA). After I-D TIA, TIA and CCIA, a PGA is followed. The PGA is used to amplifier the converted signal of all channels and changes the single-ended signal to differential signal. Then a 16 bit  $\Sigma \Lambda$  ADC is used to convert the analog signal to digital code, and the digital code is output through SPI bus. All voltage references (VRES), which includes the common mode voltage (VCM), high voltage reference (VH), and low voltage reference (VL), is provided by a bandgap (BG) and then using a buffer to increase the drive capability of VRES. Digital circuit generates all the clocks and the control signals, and I<sup>2</sup>C bus is used to configure the internal registers of the digital circuit. A 10 bit DAC is also included to generate static voltage and dynamic

Figure 1 Graphical representation of the concept lattice.

sweeping voltage used for heavy metal sensors. Low dropout regulator (LDO) provides power for digital circuit. In order to reduce power consumption, each module of the chip uses an independent power down signal, so that when only few modules are used, the other modules can be closed.

## III. Circuit Implementation

In order to achieve a very high dynamic range of current detection and a higher dynamic range of voltage detection, both the current detection channel and the voltage detection channel adopt a unique structure. In addition, a new type of ADC with high dynamic range and low power consumption is proposed in this article. These three circuits will be described in detail below.

#### 1. Current detection channel

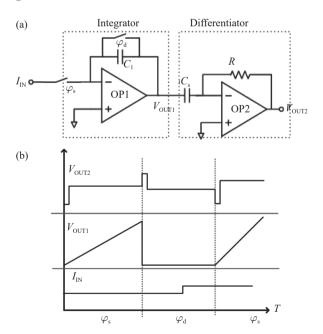

I-D TIA and TIA are the first part of current detection channels. They work alternatively, according to the input current. In order to improve the accuracy of low current measurements, a differentiator is cascaded after the current integrator, as shown in Figure 2(a). The first stage integrator consists of an operational amplifier and an integrating capacitor. The second stage differentiator is consisted of an operational amplifier, and a capacitor-resistor path. The input current is converted into a ramp wave after passing through the I-D TIA channel. The ramp wave is then converted to a DC voltage decided by the slope of the ramp wave after passing through the differentiator. Due to the high-pass filtering of the differentiator, the noise will be much smaller than the traditional integrator structure.

Figure 2 (a) The circuit diagram of the I-D TIA; (b) Output voltage of integrator and differentiator.

At  $\varphi_d$  phase, the integrator is reset to the initial state. At  $\varphi_s$  phase, the integrator integrates the input

current shown in Figure 2 (b). The output of the integrator can be calculated by the following formula:

$$V_{\rm OUT1} = \frac{I_{\rm IN} \cdot T}{C_{\rm I}} \tag{1}$$

where T represents the integrating time, which is  $\varphi_s$ , 50  $\mu$ s in this design,  $C_{\rm I}$  represents the integrating capacitor. The pulse signal in the output signal of the differentiator is the error that occurs when the integral voltage has an inflection point. Since the output signal of the differentiator at the end of the two phases is sampled by the subsequent circuit, the error pulse at the beginning of the phase will not affect the accuracy of the circuit. The output of the differentiator can be expressed as

$$V_{\text{OUT2}} = RC_{\text{s}} \cdot \frac{\mathrm{d}V_{\text{OUT1}}}{\mathrm{d}t} = RC_{\text{s}} \cdot \frac{I_{\text{IN}}}{C_{\text{I}}}$$

(2)

The overall current to voltage gain is  $C_{\rm s}R/C_{\rm I}$ . In this paper, R is set to 400 k $\Omega$ , the capacitors  $C_{\rm s}$  and  $C_{\rm I}$  are chosen to be 120 pF and 20 pF, respectively, thus the transimpedance gain of this current input channel is 63.8 dB $\Omega$ .

In order to achieve the current detection accuracy of 10 pA, the input equivalent current noise must be less than 10 pA. The main noise source is composed of four parts: input current noise, resistance noise on the differentiator, first-stage operational amplifier noise, and second-stage operational amplifier noise. The output noise of the integrator is given by

$$v_{\rm ITGR,OUT}^2 = v_{\rm fn,OP1}^2 + \frac{KT}{C_{\rm s}}$$

(3)

where  $v_{\rm ITGR,OUT}^2$  represents the output mean-square noise voltage of the integrator, A represents the gain of the amplifier,  $v_{\rm fn,OP1}^2$  represents the flicker noise of the first operational amplifier.  $KT/C_{\rm s}$  represents the thermal noise sampled by capacitor  $C_{\rm s}$ . The input equivalent noise can be derived as

$$i_{\rm ITGR,IN}^2 = \left(v_{\rm fn,OP1}^2 + \frac{KT}{C_{\rm s}}\right) / \left(\frac{T_{\rm time}}{C_{\rm I}}\right)^2$$

(4)

To calculate the noise spectral characteristics, we need to Fourier transform the differentiator. After Fourier transform, the transfer function of the differentiator can be expressed as

$$H(\omega) = \omega C_{\rm s} R \tag{5}$$

According to (3), the output mean-square noise voltage of the differentiator is given by

$$v_{\rm n,OUT}^2 = \omega^2 C_{\rm s}^2 R^2 \cdot \left( v_{\rm fn,OP1}^2 + \frac{KT}{C_{\rm s}} \right) + 4kTR + v_{\rm n,OP2}^2 \ \ (6)$$

In this equation, 4kTR and  $v_{n,OP2}^2$  are the noise generated by resistor and operational amplifier (OPAMP) 2

(OP2 in Figure 2). All the thermal noise from resistors will from the next level KT/C noise, which cannot be changed. When calculating the input equivalent noise, the second-order noise will be suppressed by the channel gain so that it is much smaller than the first-order noise and can be ignored. Since  $\omega$  equals to  $2\pi f$  which is proportional to frequency, the flicker noise of integrator and KT/C noise are canceled after multiplied by  $\omega^2$ . Hence, the input equivalent noise can be derived as

$$i_{n,\text{IN}}^{2} = \frac{\omega^{2} C_{\text{s}}^{2} R^{2} \times \left(v_{\text{fn,OP1}}^{2} + \frac{KT}{C_{\text{s}}}\right) + 4kTR + v_{\text{n,OP2}}^{2}}{\left(\frac{C_{\text{s}}R}{C_{\text{I}}}\right)^{2}}$$

(7)

The differentiator not only cancels the low frequency noise of the integrator, but also brings much higher gain to suppress the second stage noise. Compare formula (4) with (7), the total input equivalent noise of the I-D TIA is lower than the integrator.

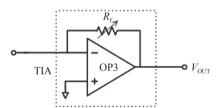

TIA circuit diagram is shown in Figure 3. The gain of TIA can be expressed by

$$V_{\rm OUT3} = -I_{\rm IN} \cdot R_{\rm f} \tag{8}$$

To cover the current detect range from 1  $\mu A$  to 1 mA, the resistor  $R_{\rm f}$  has 8 gears, which can be changed from 1 M $\Omega$  to 6.25 k $\Omega$ . To reduce quiescent current, an amplifier with class-AB output stage is used in OP3.

Figure 3 The circuit diagram of TIA.

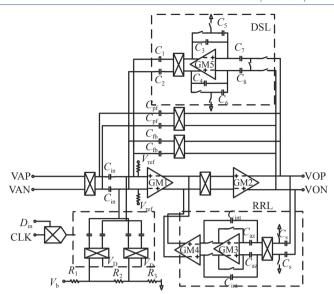

#### 2. Capacitive-coupled instrumentation amplifier

A CCIA [16]–[21] is used to detect the differential input voltage. Figure 4 shows the circuit diagram of the capacitive-coupled wideband chopper current-feedback instrumentation amplifier [22]. It comprises a main amplification stage, a chopper stage, a low noise ripple reduction loop (RRL) [23], a DC-servo loop (DSL) [24], positive feedback loop (PFL) [25], and a voltage sum capacitor feeding network. The input signal is chopped to reduce offset voltage and 1/f noise. The main amplification stage is based on a two-stage Miller-compensated OPAMP, which consists of an input transconductance GM1 and an integrator built around GM2, the closed-loop gain is set by feedback capacitance  $C_{\rm fb}$  and input capacitance  $C_{\rm in}$ :

$$Gain = \frac{C_{fb}}{C_{in}} \tag{9}$$

Figure 4 The circuit diagram of CCIA.

The PFL comprising feedback capacitance  $C_{\rm pf}$  and input capacitance  $C_{\rm in}$  increases the input impedance. If  $C_{\rm pf}$  equals to  $C_{\rm fb}$ , the input impedance is

$$Z_{\text{in\_pf}} = \frac{G}{2 \cdot f_{\text{chop}} C_{\text{in}}} \tag{10}$$

where  $Z_{\rm in\_pf}$  is the input impedance of the positive feedback path, G is the gain of the CCIA,  $f_{\rm chop}$  is the chopping frequency. The RRL loop integrate voltage ripple caused by chopping and feedback between GM1 and GM2 to cancel the impact of voltage ripple. The ripple voltage at  $V_{\rm out}$  is sensed by  $C_{\rm s}$ , demodulated by chopper, and integrated by GM3 to generate voltage singal via  $C_{\rm int}$ . The DC signal is then converted to current by transconductance GM4 to compensate for the offset of GM1. The output ripple after compensating is given by

$$V_{\rm out,ripple} = V_{\rm OS1} \times \frac{1}{G_{\rm M3}G_{\rm M4}C_{\rm L1}} \times G_{\rm M1}G_{\rm M2} \times \frac{1}{2\pi f_{\rm chop}} \eqno(11)$$

$V_{\rm OS1}$  represents the offset voltage of GM1.  $V_{\rm out,ripple}$  is independent of  $C_{\rm s}$ . A reduced  $V_{\rm out,ripple}$  can be achieved by increasing either GM3 or GM4.

The DSL is used to eliminate the large DC offset that may arise from electrochemical processes at the electrode-tissue interface. It integrates the DC voltage signal at  $V_{\rm out}$  through a switch-capacitor integrator, then the generated signal is up modulated by chopper, and is fed back to the input of GM1. The transfer function of the integrator is given by

$$H(z) = \frac{C_{7,8}}{C_{5,6} + C_{3,4} - C_{3,4}z^{-1}}$$

(12)

The combination of capacitor  $C_{7,8}$  and switch can be regarded as equivalent resistance. Because capacitor  $C_{5,6}$  is embedded in the loop, the bandwidth of the integra-

tor in DSL is different from normal integrator. The optimized bandwidth is given by

$$f_0 = \frac{f_{\rm s}C_{5,6}^2}{2\pi C_{3,4}^2} \tag{13}$$

where  $f_{\rm s}$  is the operating frequency. By choosing the value of  $C_{3,4}$  and  $C_{5,6}$  at 1250Cu and Cu (Cu is the unit capacitor about 100 fF composed by CMOS),  $f_0$  can be set to 0.01 Hz, which will make the integrator has a fast time domain response toward the DC offset voltage signal.

Moreover, a coarse DC offset compensation composed of a 3-bit DAC is also used to accelerate the total compensation speed. Through changing the control  $D_{\rm in}$ , the circuit can obtain a compensation voltage from VL to 8VL, where VL is 10 mV.

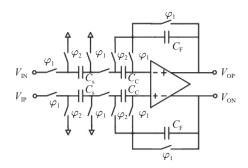

#### 3. Programmable gain amplifier

The PGA stage shown in Figure 5 converts the single input voltage or differential voltage into differential output voltage and provides amplification. The offset voltage of the amplifier is stored at the top plate of CC during  $\varphi_1$  equals high, and it will be canceled at  $\varphi_2$  becoming high. When it is single input mode, the input voltage is connected to  $V_{\rm IN}$ , and common mode voltage VCM is connected to  $V_{\rm IP}$ . The output voltage of PGA is

Figure 5 The circuit diagram of PGA.

$$V_{\rm OUT} = \frac{C_{\rm F}}{C_{\rm c}} V_{\rm IN} \tag{14}$$

$V_{\rm IN}$  is the input voltage. When it is single input mode,  $V_{\rm IN}$  equals to (VIN-VCM).

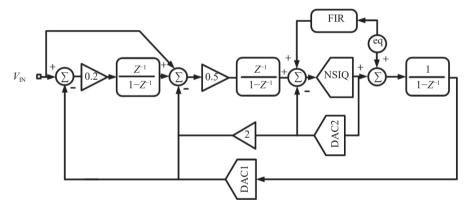

#### 4. Sigma-delta modulator

A fourth order  $\Sigma\Delta$  modulator composed of a traditional second order  $\Sigma\Delta$  modulator and a second order noise-shaped integrating quantizer (NSIQ) [26]–[28] is presented in this paper, the proposed modulator architecture is shown in Figure 6. With the aid of the digital integration in the loop [29], the NSIQ provides effective 5-bit quantization levels and two extra orders of noise-shaping using only four counting clock edges.

Figure 6 Proposed modulator architecture.

In this paper, the modulator adopts the structure of [28], and the main circuit is divided into three parts, the feedforward integration path, the second-order NSIQ quantizer and the back-end digital integrator.

The feed-forward integration path ensures an overall two-stage noise shaping capability. The second-order NSIQ quantizer provides additional second-order shaping capability. The back end integrator ensures the stability of the circuit. The overall transfer function of the proposed structure is derived as

$$D(z) = X(z) + (1 - z^{-1})^{4} EQ(z)$$

(15)

where D(z) represents the z transform of the output digital code, X(z) represents the input signal, EQ(z) represents the quantization noise.

#### IV. Results

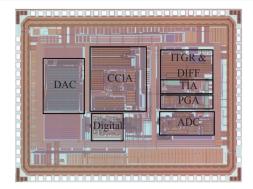

The analog front-end circuit was fabricated in a 0.18  $\mu$ m CMOS process, the chip size is 3.2 mm  $\times$  2 mm, and the photograph of the whole chip is shown in Figure 7. The measured power consumption is 16.5 mW @3.3 V.

#### 1. Single module test result

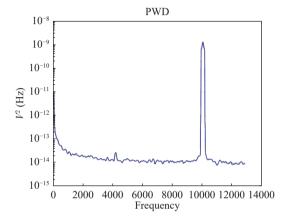

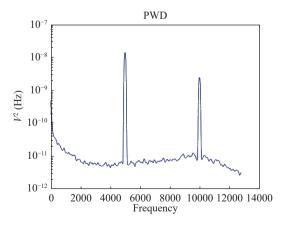

The measured output voltage noise spectrum of the I-D TIA channel is shown in Figure 8. During the channel noise test, all circuits except the test channel are turned off. The input of the test channel is connected to the DC common mode voltage VCM, and its noise spectrum characteristics are tested by a spectrum analyzer. After integrating the noise power density, the output noise is 30.9  $\mu V_{\rm RMS}$  at 10 kHz bandwidth. The gain of

Figure 7 Die microphotograph of the fabricated analog front-end chip.

Figure 8 The spectrum map of the output voltage noise of I-D TIA channel.

this channel is 2.4 M $\Omega$ , thus the input referred current noise floor is 12.88 pA<sub>RMS</sub> at 10 kHz.

The output noise of CCIA voltage spectrum measured by dynamic signal analyzer is shown in Figure 9. After integrating the noise power density, the output noise is 1.35 mV $_{\rm RMS}$  at 10 kHz bandwidth. The amplifier configures for a closed loop gain of 40. Accordingly, the input-referred noise is 33.7  $\mu V_{\rm RMS}$ .

Figure 9 Measured input referred noise of the proposed CCIA.

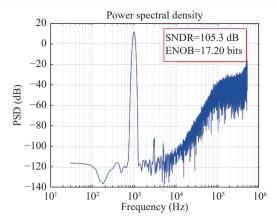

Figure 10 plots the measured spectrum of the sigmadelta modulator output with a 1 kHz input sinewave at an OSR of 50, fourth order of noise shaping ability can be seen in the figure. In a 10 kHz BW, the proposed

Figure 10 The spectrum map of the proposed DSM at  $1 \mathrm{kHz}$  signal input.

DSM achieves a signal to noise and distortion ratio (SNDR) of 105.3 dB, corresponding to 17.2 bits effective number of bits (ENOB).

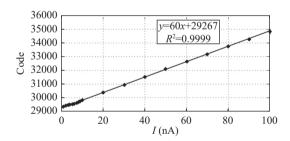

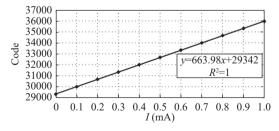

#### 2. Current and voltage channel test result

A low noise current source is used to test the current channel. When the input current is less than 1  $\mu$ A, it is measured by the I-D TIA channel. The measured output digital data versus input current is shown in Figure 11. For current above 1  $\mu$ A, it is measured by the TIA channel. Figure 12 shows the measured result of 100  $\mu$ A to 1 mA input signal. All figures show that the current test path of the AFE chip has high linearity at one range setting, and the smallest  $R^2$  are 0.9999 and 1 for I-D TIA channel and TIA channel, respectively.

Figure 11 Measured output digital data versus input current (I-T TIA).

Figure 12 Measured output digital data versus input current (TIA).

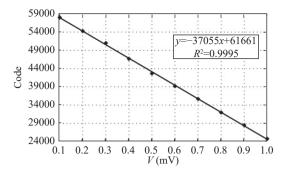

The input signal of voltage testing is generated by a high-precision voltage source. The voltage signal is converted into a current signal by the on chip V2I module, before sending to the TIA. When voltage varies from 100 mV to 1 V, the measured result is shown in Figure 13,

Figure 13 Measured output data versus single-ended input voltage.

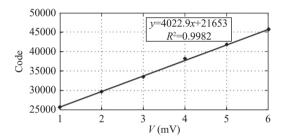

the smallest  $R^2$  is 0.9995. While the differential voltage signal is test by CCIA channel, the measured result with the voltage varying from 1 mV to 6 mV is shown in Figure 14, and the smallest  $R^2$  is 0.9982.

Figure 14 Measured output data versus input differential voltage.

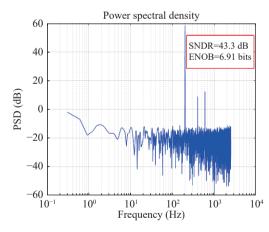

The test results of the dynamic characteristics of the current path are shown in Figure 15. Under the condition of 100 nApp 259 Hz sinusoidal signal current input, the SNDR of the whole channel reaches 43.3 dB.

Figure 15 The spectrum map of current path under 100 nApp input.

## 3. Prototype electrochemical sensor platform

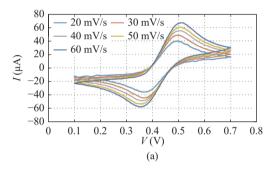

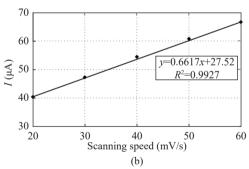

Figure 16 is the test platform for this system. The electrode materials are gold electrode, platinum electrode and AgCl electrode. Using KCN solution, the curve of current changing with scanning speed is shown in Figure 17(a), the linear relationship of the peak current with the scanning speed is shown in Figure 17(b), it can be

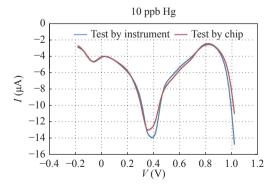

seen that the linearity is 99.27%. Figure 18 reveals the scanning voltage program of Hg<sup>2+</sup>, the I-V curves tested by chip and instrument are basically match.

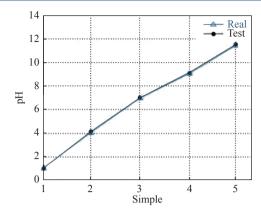

The pH sensor test results with pH values of 1.13, 4, 6.86, 9.18, and 11.5 are shown in Figure 19, the maximum deviation between the measured value and the ac-

Figure 16 Test platform environment.

Figure 17 (a) Measured sweep I-V characteristic curve of KCN; (b) The peak current versus the scan speed.

Figure 18 Measured sweep I-V characteristic curve of 10 ppb  ${\rm Hg}^{2+}.$

Figure 19 Measured of the output result of single-end voltage channel combining with pH sensor.

tual value is 0.1. Table 1 summarizes the characteristics of this AFE chip, and comparisons with prior results are made as well.

Table 1 Formal context

| V. Conclusion                           |

|-----------------------------------------|

| A multi-channel CMOS analog             |

| IC has been presented. The chip cons    |

| sensitive current detection channels ar |

| tection channels, and it provides prog  |

| waveform needed by the sensor at the    |

front-end interface sists of two highly nd two voltage degrammable voltage waveform needed by the sensor at the same time. The voltage detection dynamic range achieves 60 dB. The current detection dynamic range achieves 157.8 dB, which is larger than that of most state-of-art works. The input signals of sensors are converted into digital data with good linearity (the smallest  $R^2$  of current channel is 0.9999, the smallest  $R^2$  of voltage channel is 0.9982). The chip was fabricated in 0.18 µm CMOS process with supply voltage of 3.3 V. It achieves 12.88 pA  $_{\rm RMS}$  and 33.7  $\mu V_{\rm RMS}$ at 10 kHz bandwidth. A prototype microsystem for a multifunctional sensor was constructed. Test results show that the circuit and the entire system function properly.

| Parameters                                 | This work        | Ref. [6]             | Ref. [7]            | Ref. [8]           | Ref. [9]        |

|--------------------------------------------|------------------|----------------------|---------------------|--------------------|-----------------|

| Technology (µm)                            | 0.18             | 0.18                 | 0.09                | 0.18               | 0.18            |

| Supply (V)                                 | 3.3/1.8          | 1                    | 2.5/1               | 1.8                | 2               |

| Power                                      | 4.36 mW          | $1.55~\mu\mathrm{W}$ | $0.147~\mathrm{mW}$ | $5.22~\mathrm{mW}$ | _               |

| Current noise floor (Meas. with bandwidth) | 12.9 pA (10 kHz) | _                    | 75 fA (1 kHz)       | 204 fA (100 Hz)    | 100 fA (10 kHz) |

| Max. meas. current                         | 1 mA             | _                    | 200 pA              | 11.6 μΑ            | 200 pA          |

| Area (mm <sup>2</sup> )                    | 6.4              | _                    | 0.065               | 0.091              | _               |

| Current dynamic range (dB)                 | 157.8            | _                    | 68.5                | 155.1              | 85              |

| Voltage detection capability               | Yes              | Yes                  | No                  | No                 | No              |

| Voltage dynamic range (dB)                 | 89.4             | 73.48                | _                   | _                  | _               |

## Acknowledgement

This work was supported by the National Key Research and Development Project (Grant No. 2018YFB200 2604), the Key Foreign Cooperation Projects of Chinese Academy of Sciences (Grant No. 172511KYSB20180080), the Qianjiaohe KY Zi [2018] 317, and the Zunyi Keheji [2018] 01.

#### References

- [1] Q. W. Fan, F. Sebastiano, H. Huijsing, et al., "A  $1.8\mu W$   $1\mu V$ offset capacitively-coupled chopper instrumentation amplifier in 65nm CMOS," in Proceedings of the 2010 Proceedings of ESSCIRC, Seville, Spain, pp.170-173, 2010.

- [2] W. Lin and C. W. Fu, "Research on nA level current measuring circuit and anti-jamming technology," Micronanoelectronic Technology, vol. 45, no. 7, pp. 419-422, 2008. (in Chinese)

- [3] C. Y. Huang, M. F. Sun, and H. Y. Lin, "Design of a potentiostat with standalone signal generator for vanillylmandelic acid biosensors," in Proceedings of 2016 International Symposium on Computer, Consumer and Control, Xi'an, China, pp.606-609, 2016.

- [4] M. Amin, M. M. Isa, R. M. Sidek, et al., "An embedded pro-

- cessing of differential pulse voltammetry (DPV) data using ARM processor (LPC1768)," in Proceedings of 2015 IEEE International Circuits and Systems Symposium, Langkawi, Malaysia, pp. 80-84, 2015.

- [5] P. M. Levine, P. Gong, R. Levicky, et al., "Active CMOS sensor array for electrochemical biomolecular detection," IEEE Journal of Solid-State Circuits, vol. 43, no. 8, pp. 1859-1871, 2008.

- [6] M. Zamani, Y. Rezaeiyan, O. Shoaei, et al., "A 1.55 μW bioimpedance measurement system for implantable cardiac pacemakers in 0.18 µm CMOS," IEEE Transactions on Biomedical Circuits and Systems, vol. 12, no. 1, pp. 211-221, 2018.

- [7] J. J. Lu and J. Holleman, "A wideband ultra-low-current onchip ammeter," in Proceedings of IEEE 2012 Custom Integrated Circuits Conference, San Jose, CA, USA, pp.1-4,

- [8] S. S. Dai, R. T. Perera, Z. Yang, et al., "A 155-dB dynamic range current measurement front end for electrochemical biosensing," IEEE Transactions on Biomedical Circuits and *Systems*, vol. 10, no. 5, pp. 935–944, 2016.

- [9] S. Subhan, S. Khapli, Y. A. Song, et al., "A fully differential potentiostat circuit with integrated time-based ADCs," in Proceedings of 2019 IEEE Biomedical Circuits and Systems Conference, Nara, Japan, pp.1-4, 2019.

- [10] J. Monge, O. Postolache, A. Trandabat, et al., "Multi-node potentiostat device and multiplatform mobile application for on-field measurements," in Proceedings of 2020 International Conference and Exposition on Electrical and Power Engineering, Iasi, Romania, pp.695–698, 2020.

- [11] R. Srinath, G. N. Prasannapatil, S. P. Shetty, et al., "A capacitive sensor readout circuit with low power mode and variable gain operations," in Proceedings of 2017 International conference on Microelectronic Devices, Circuits and Systems, Vellore, India, pp.1–5, 2017.

- [12] C. Spathis, A. Birbas, K. Georgakopoulou, et al., "Noise and uncertainty in comparator/TDC sensor readout circuits," in Proceedings of 2017 International Conference on Noise and Fluctuations, Vilnius, Lithuania, pp.1–4, 2017.

- [13] M. Stanacevic, K. Murari, A. Rege, et al., "VLSI potentiostat array with oversampling gain modulation for wide-range neurotransmitter sensing," *IEEE Transactions on Biomedi*cal Circuits and Systems, vol. 1, no. 1, pp. 63–72, 2007.

- [14] K. Murari, M. Stanacevic, G. Cauwenberghs, et al., "Integrated potentiostat for neurotransmitter sensing," IEEE Engineering in Medicine and Biology Magazine, vol. 24, no. 6, pp. 23–29, 2005.

- [15] M. Chen, Y. T. Liu, Z. C. Li, et al., "A high dynamic range CMOS readout chip for electrochemical sensors," *IEEE Sen*sors Journal, vol. 16, no. 10, pp. 3504–3513, 2016.

- [16] L. Fang and P. Gui, "A 13 nV/√Hz 4.5µW chopper instrumentation amplifier with robust ripple reduction and input impedance boosting techniques," in *Proceedings of 2020 IEEE Custom Integrated Circuits Conference*, Boston, MA, USA, pp.1–5, 2020.

- [17] H. Jeon, J. S. Bang, and M. Je, "A CMRR enhancement circuit employing  $G_m$ -controllable output stages for capacitively coupled instrumentation amplifiers," *IEEE Transactions on Circuits and Systems II:Express Briefs*, vol. 67, no. 9, pp. 1539–1543, 2020.

- [18] H. Jiang, S. Nihtianov, and K. A. A. Makinwa, "An energy-efficient 3.7-nV/√Hz bridge readout IC with a stable bridge offset compensation scheme," *IEEE Journal of Solid-State Circuits*, vol. 54, no. 3, pp. 856–864, 2019.

- [19] T. N. Lin, B. Wang, and A. Bermak, "Analysis of output ripple shape and amplitude in chopper instrumentation amplifier," *IEEE Transactions on Circuits and Systems II:Express Briefs*, vol. 69, no. 2, pp. 299–303, 2022.

- [20] J. W. Zheng, W. H. Ki, L. Y. Hu, et al., "Chopper capacitively coupled instrumentation amplifier capable of handling large electrode offset for biopotential recordings," *IEEE Transactions on Circuits and Systems II:Express Briefs*, vol. 64, no. 12, pp. 1392–1396, 2017.

- [21] C. B. Zhang, L. Zhou, M. Chen, et al., "A design of readout IC with capacitively-coupled chopper current-feedback instrumentation amplifier in a 0.18 μm CMOS process," Analog Integrated Circuits and Signal Processing, vol. 102, no. 2, pp. 309–321, 2020.

- [22] R. Wu, K. A. A. Makinwa, and J. H. Huijsing, "A chopper current-feedback instrumentation amplifier with a 1 mHz 1/f noise corner and an AC-coupled ripple reduction loop," *IEEE Journal of Solid-State Circuits*, vol. 44, no. 12, pp. 3232–3243, 2009.

- [23] K. Nagaraj, "A parasitic-insensitive area-efficient approach to realizing very large time constants in switched-capacitor circuits," *IEEE Transactions on Circuits and Systems*, vol. 36,

- no. 9, pp. 1210-1216, 1989.

- [24] Q. W. Fan, F. Sebastiano, J. H. Huijsing, et al., "A 1.8 μW 60 nV/√Hz capacitively-coupled chopper instrumentation amplifier in 65 nm CMOS for wireless sensor nodes," *IEEE Journal of Solid-State Circuits*, vol. 46, no. 7, pp. 1534–1543, 2011.

- [25] T. Kim, C. Han, and N. Maghari, "A 7.2 mW 75.3 dB SNDR 10 MHz BW CT delta-sigma modulator using Gm-C-based noise-shaped quantizer and digital integrator," *IEEE Jour-nal of Solid-State Circuits*, vol. 51, no. 8, pp. 1840–1850, 2016.

- [26] T. Kim, C. Han, and N. Maghari, "28.2 An 11.4 mW 80.4 dB-SNDR 15 MHz-BW CT delta-sigma modulator using 6b double-noise-shaped quantizer," in *Proceedings of 2017 IEEE International Solid-State Circuits Conference*, San Francisco, CA, USA, pp.468–469, 2017.

- [27] T. Kim, C. Han, and N. Maghari, "A 4th-order continuous-time delta-sigma modulator using 6-bit double noise-shaped quantizer," *IEEE Journal of Solid-State Circuits*, vol. 52, no. 12, pp. 3248–3261, 2017.

- [28] K. Y. Wang, W. J. Xu, C. B. Zhang, et al., "A 240µW 17bit ENOB ΣΔ modulator using 2nd-order noise-shaped integrating quantizer," *IEICE Electronics Express*, vol. 19, no. 5, article no. 20220038, 2022.

- [29] E. Bonizzoni, A. P. Perez, F. Maloberti, et al., "Third-order ΣΔ modulator with 61-dB SNR and 6-MHz bandwidth consuming 6 mW," in Proceedings of the 34th European Solid-State Circuits Conference, Edinburgh, UK, pp.218–221, 2008.

Kunyu WANG received the B.S. degree in microelectronic engineering from Sichuan University in 2016. He is currently working toward the Ph.D. degree in the Institute of microelectronics, Chinese Academy of Sciences of Microelectronic Engineering, University of Chinese Academy of Science (UCAS), Beijing, China. His research interests include analog and mix-signal circuits design.

(Email: wangkunyu@ime.ac.cn)

Wenjing XU received the B.E. and M.E. degrees from Tianjin University, China, in 2010 and 2013, respectively. She is an research assistant in the Institute of Microelectronics of Chinese Academy of Science (IMECAS). Her research interests include CMOS image sensor and analog circuits design. (Email: xuwenjing@ime.ac.cn)

Chengbin ZHANG was born in Sichuan Proince, China, in 1989. He received the B.E. and M.E. degrees from Hunan University, Changsha, China, in 2011 and 2014, respectively. He is currently pursuing the Ph.D. degree in circuits and systems at School of Microelectronics, University of Chinese Academy of Science (UCAS), Beijing, China. He was an research assistant in the Institute of Micro-

electronics of Chinese Academy of Sciences (IMECAS) in 2017. His research interests include analog and mix-signal circuits design. (Email: zhangchengbin@ime.ac.cn)

Yanjun YANG was born in Hunan Province, China, in 1986. He received the B.E. and Ph.D. degrees form Hunan University, Changsha, China, in 2009 and 2016, respectively. He is currently a Lecturer in Zunyi Normal College. His research interests include sensor interface circuits, ADC, LDO, reference, OSC. (Email: leo yang@hnu.edu.cn)

Man-Kay LAW received the B.S. degree in computer engineering at Hong Kong University of Science and Technology (2006). He received the Ph.D. degree in electronic and computer engineering, Hong Kong University of Science and Technology (2011). He worked as a Visiting Assistant Professor, Dept. of ECE, in Hong Kong University of Science and Technology from Feb. 2011 to Aug. 2011. He worked as an

Assistant Professor, State Key Laboratory of Analog and Mixed Signal VLSI, and Dept. of ECE, FST, in University of Macau from Aug. 2011 to Aug. 2017. He is now an Associate Professor, State Key Laboratory of Analog and Mixed Signal VLSI, Institute of Microelectronics and Dept. of ECE, FST, in University of Macau from Aug. 2017 to present. His current research interests include CMOS smart temperature sensors, CMOS image sensors, integrated wireless sensing and biomedical systems, ultra-low power analog design techniques, and energy harvesting techniques.

(Email: MKLaw@um.edu.mo)

Li ZHOU was born in 1977. She received the M.E. degree from School of Information Systems, the University of Electro-Communications (UEC), Tokyo, Japan. She has been an Associate Professor in the Institute of Microelectronics of Chinese Academy of Sciences (IMECAS) since April 2005. From April 2003 to March 2005, she was a System Engineer at Information and Communications System

Design, Information and Communications Group, Hitachi Co.

Ltd, Tokyo, Japan. Her research work is focused on multimedia signal processing, analog and mixed-signal VLSI for WSN applications. She is author or co-author of more than 20 journal and conference papers. (Email: zhouli@ime.ac.cn)

Jie CHEN was born in Hubei Province, China, in 1963. He received the B.E. degree from the Harbin Engineering University, Harbin, China in 1986, and the M.E. and Ph.D. degrees from the University of Electro-Communications (UEC), Tokyo, Japan in 1991 and 1994, respectively. He was a Research Associate in UEC in 1994 and was a Research Project Leader in Advanced IC Development

Center, Yozan Inc., Tokyo, Japan from 1995 to 1997. He worked as an Associate Professor in the Network System Laboratory, the Graduate School of Information Systems, UEC, during 1998 to 2001. In 2001, he was selected as a scientist of "100 talents Program" by Chinese Academy of Sciences (CAS). He is now a Director Professor of the Institute of Analog Integrated Circuits and Signal Processing Microelectronics, CAS and a Professor of the Graduate School of CAS. His current research interests include SOC design for software-defined-radio (SDR), digital communications (CDMA and OFDM) and Data Compression. Dr. Chen is a valued member of IEEE. (Email: jchen@ime.ac.cn)

Ming CHEN was born in Hubei Province, China, in 1985. He received the B.S. degree from University of Electronic Science and Technology of China (UESTC), Chengdu, China, in 2008, and the M.E. and Ph.D. degrees from Peking University, University of Chinese Academy of Sciences, Beijing, China, in 2011 and 2017, respectively. He was an research assistant in Institute of Microelectron-

ics of Chinese Academy of Sciences in 2011. His research interests include analog and RF integrated circuits design, such as ADC, PGA and oscillator, etc.

(Email: chenming1@ime.ac.cn)