# An All-Standard-Cell-Based Synthesizable SAR ADC With Nonlinearity-Compensated RDAC

Zule Xu<sup>®</sup>, Member, IEEE, Naoki Ojima, Member, IEEE, Shuowei Li<sup>®</sup>, Student Member, IEEE, and Tetsuya Iizuka<sup>®</sup>, Senior Member, IEEE

Abstract-We propose an all-standard-cell-based synthesizable successive-approximation-register analog-to-digital converter (SAR ADC) which is automatically placed and routed (P&R) using a commercial digital implementation tool. For higher feasibility and wider input range, a differential architecture is proposed with an inverter-based resistive digital-to-analog converter (RDAC) and a four-input comparator. MOSFET gate capacitance is employed for the sampling capacitor. To mitigate its capacitance variation due to input voltage and the leakage between gate and diffusion, we leave the diffusion of the standard cell floating and only use the capacitance between gate and bulk. Two prototypes have been designed in 65-nm bulk CMOS. Prototype I has been fabricated and achieves 10 MS/s, 14.3 mW, and 28.1-dB SNDR in a 6-bit architecture. The performance is improved in Prototype II by proposing a lookup table (LUT)-compensating transistor-configurable inverter-based RDAC and an OR-AND-Inverter (OAI)-based comparator and by employing a thick-oxide diffusion-floating decoupling cell for the sampling capacitor. The default LUT is created during the design phase by a script-controlled automatic simulation routine. The power consumption is significantly reduced as well through improved timing control. Layout-parasitic-extraction (LPE) simulations of Prototype II suggest 35.7- and 47.2-dB SNDRs in 6- and 8-bit versions, respectively. The power consumptions are reduced to 0.91 and 2.52 mW, respectively.

*Index Terms*—Resistive DAC (RDAC), standard cell, synthesizable, synthesizable successive-approximation-register analog-to-digital converter (SAR ADC).

#### I. INTRODUCTION

**G** ROWING industries increasingly demand a tremendous number of microchips which nowadays are involving with more and more digital and digitally assisted analog circuits. Digital circuits are typically described in register transfer level (RTL) netlist and placed and routed (P&R) in

Manuscript received May 28, 2021; revised September 14, 2021; accepted October 6, 2021. Date of publication November 2, 2021; date of current version November 30, 2021. This work was supported in part by the Japan Science and Technology Agency (JST) Adaptable and Seamless Technology Transfer Program through the Target-Driven Research and Development (A-STEP) under Grant JPMJTR201C and in part by the Japan Society for the Promotion of Science (JSPS) KAKENHI under Grant 20K14786. (*Corresponding author: Zule Xu.*)

Zule Xu and Tetsuya Iizuka are with the Systems Design Lab, School of Engineering, The University of Tokyo, Tokyo 113-0032, Japan (e-mail: xuzule@vdec.u-tokyo.ac.jp; iizuka@vdec.u-tokyo.ac.jp).

Naoki Ojima and Shuowei Li are with the Department of Electrical Engineering and Information Systems, School of Engineering, The University of Tokyo, Tokyo 113-0032, Japan (e-mail: ojima@silicon.u-tokyo.ac.jp; lishuowei@silicon.u-tokyo.ac.jp).

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TVLSI.2021.3122027.

Digital Object Identifier 10.1109/TVLSI.2021.3122027

an automatic flow. They can be fast realized and modified to adapt to different specifications and process technologies. This feature, however, is rarely found in analog circuits. Despite a small portion in a system, analog or mixed-signal circuits often take long time to design. Moreover, to suit the existing design to another specification or process technology, the required redesign time is typically as long as the previous one.

To reduce the design or redesign time of analog circuits, synthesizable solutions using standard cells have been proposed. In these solutions, generally, analog circuits are described in RTL netlists and automatically laid out in digital P&R flows. Recent works have succeeded in time-to-digital converters (TDCs) [1]–[3], phase-locked loops (PLLs) [4]-[11], low-dropout (LDO) regulators [12]-[14], and analogto-digital converters (ADCs) [15]-[24]. As the interface between the real world and digital signal processing, ADCs are widely needed in sensor and radio frequency systems. In most development scenarios, they should be specifically designed according to system requirements, inevitably requiring long design time. Their design automation-unlike TDCs, PLLs, and LDOs that are mainly in a manner of time-domain circuits-can be more challenging due to the necessity to deal with voltage-domain signals by manipulating standard cells.

A standard-cell library lacks available components to realize two-port resistors and operational amplifiers. Thus, conventional flash, pipeline, and  $\Delta \Sigma$  architectures are less possible to be implemented. To circumvent this issue, stochastic ADCs were proposed, but the thousands of NAND comparators result in large area and high power [15], [16], [25]. Prior to them, a domino-logic-based ADC with custom-designed cells and manual layout was presented in [26]. In another work on a voltage-controlled oscillator-based (VCO-based) ADC [27], only standard cells were employed, but the circuit layout was done manually. By registering custom-designed cells to a physical library, automatic P&R flows for analog circuits were introduced [17], [19], [23], [24], [28]. Also, hybrid methods for successive-approximation-register (SAR) ADCs were proposed with SKILL language for capacitive digitalto-analog converter (CDAC) generation [29], [30]. The two works have achieved high performance at the cost of more implementation complexity.

An SAR ADC can be suitable for synthesis owing to its simple and digital-intensive architecture. A single-ended all-standard-cell-based SAR ADC with an OR-AND-Inverter (OAI)-based DAC was proposed in [21]. However, its signal

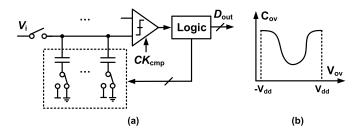

Fig. 1. (a) Conventional custom-designed SAR ADC. (b) Voltage dependence of MOSFET capacitance.

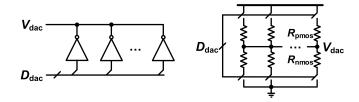

Fig. 2. Proposed inverter-based RDAC for synthesizable SAR ADC.

bandwidth is limited since the sample-and-hold (S/H) circuit is not implemented. Dyadic-digital-pulse-modulation (DDPM) DACs are proposed for synthesizable SAR ADCs in [22]. Still, they suffer from limited speed because the DACs require exponentially more cycles for output generation. In [20], we proposed a differential all-standard-cell-based SAR ADC using a floating-diffusion S/H circuit, an inverter-based resistive DAC (RDAC), and a four-input comparator. In this article, we detail the design in Prototype I and propose the improving techniques for higher performance in Prototype II. Prototype I is evaluated on silicon, and Prototype II is verified through simulations in layout-parasitic-extraction (LPE) comprising resistors and capacitors.

## II. SYNTHESIZABLE SAR ADC

An SAR ADC in a custom design typically consists of an S/H circuit which also operates as a CDAC, a dynamic comparator, and SAR logic, as shown in Fig. 1(a). Since the comparator and the logic can be realized using standard cells, one may naturally consider replacing the CDAC with MOSFET capacitors seen from the gate nodes of logic or decoupling cells. The following issues, however, cause the replacement less feasible: 1) MOSFET capacitance varies with gate-diffusion voltage, as shown in Fig. 1(b), which may lead to unpredictable errors during binary searching based on charge redistribution; 2) two-port capacitor and especially its array are uneasy to implement using a digital P&R tool; and 3) even though 2) is available, the parasitic capacitance of routing wires cannot be controlled as in custom layout, which undermines the linearity.

Due to these issues, we separate the S/H and DAC and let the capacitor work only for sampling. The binary searching is carried out via a resistive DAC, as shown in Fig. 2. Compared with the OAI-based DAC in [21], the inverterbased one features simple architecture with a similar level of performance. PMOS or NMOS transistors are turned on according to the input codes and form a voltage divider.

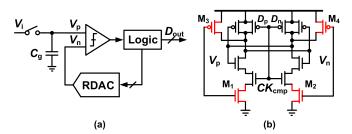

Fig. 3. (a) Possible single-ended solution, where the comparator's input common mode changes during conversion. (b) Conventional standard-cell comparator and its limited input range issue.

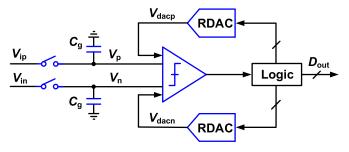

Fig. 4. Proposed differential all-standard-cell synthesizable SAR ADC.

The output voltage is calculated as

$$V_{\rm dac} = \frac{2^N - 1 - D_{\rm dac}}{2^N - 1 + (\alpha - 1)D_{\rm dac}} \tag{1}$$

where  $\alpha = (R_{\text{pmos}}/R_{\text{nmos}})$ . If the resistance of PMOS and NMOS transistors is equivalent, i.e.,  $\alpha = 1$ , then

$$V_{\rm dac} = \frac{2^N - 1 - D_{\rm dac}}{2^N - 1} \tag{2}$$

which suggests a linear relation between  $D_{dac}$  and  $V_{dac}$ . In practice,  $\alpha \neq 1$  and varies with  $V_{dac}$  that determines transistors' drain-source voltage. Consequently, this inverterbased RDAC exhibits high nonlinearity. The proposed methods to compensate the nonlinearity for moderate resolution will be described in Sections III and V.

Employing this RDAC, one can possibly derive a singleended architecture, as shown in Fig. 3(a). Since the MOSFET gate capacitor is only used for S/H, the issue of the voltagedependent capacitance during binary searching is avoided. Although the capacitance still varies with input voltage that affects the bandwidth of the sampler, this effect can be mitigated with sufficient design margin and the floatingdiffusion capacitor, which will be introduced in Sections III-C and V-C. The major issue of this architecture is the limited input range because the input common-mode voltage  $(V_{cm})$ of the conventional NAND-based comparator changes during conversion. As shown in Fig. 3(b), when  $V_{cm}$  becomes too low,  $M_1$  and  $M_2$  are turned off. Thus, the currents flowing through two paths are cut off, and the upper transistors are disabled, resulting in uncertain output. If  $V_{\rm cm}$  is too high, transistors  $M_3$ and  $M_4$  go to the subthreshold region, and the effect of their mismatch can drastically increase.

Different from the NAND+ NOR comparator in [21], to solve this issue, we propose a differential architecture, as shown in Fig. 4. Here,  $V_p - V_n$  and  $V_{dacp} - V_{dacn}$  are differential pairs,

Fig. 5. Proposed four-input NAND-based comparator for Prototype I.

Fig. 6. RDAC in Prototype I with attenuating inverters and gating control.

respectively, and their  $V_{\rm cm}$  is fixed at  $V_{\rm dd}/2$ . The comparator is extended to a four-input structure which will be described in Sections III-A and V-A. The differential architecture is also beneficial to the suppression of common-mode noise. The design and evaluation of building blocks will be described in Sections III–VI. In brief, Prototype I evaluated on silicon achieves 10 MS/s, 14.3 mW, and 28.1-dB SNDR in a 6-bit architecture; Prototype II verified with LPE netlists suggests 10 MS/s, 0.9 mW, and 35.5-dB SNDR in a 6-bit version, and 10 MS/s, 2.5 mW, and 46.5-dB SNDR in an 8-bit version. Thanks to the synthesizable design methodology, it is agile and straightforward to modify the architecture from 6 to 8 bit.

## III. CIRCUIT DESIGN OF PROTOTYPE I

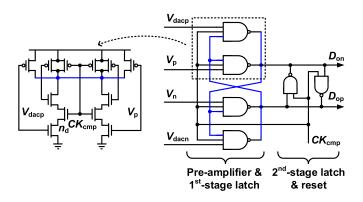

## A. Four-Input nand-Based Comparator

A NAND-based comparator can be interpreted as a preamplifier, a latch, and clock switches. To create a four-input comparator, we feed back the shorted output of one pair of the preamplifiers to the input of the other pair, similarly as in a custom design, as shown in Fig. 5. Here,  $V_p + V_{dacp}$ and  $V_n + V_{dacn}$  are compared. Two NAND2 cells at the output operate as a 2nd-stage latch to enhance the gain during comparison. Before and after comparison, they help reset the outputs.

## B. Inverter-Based RDAC

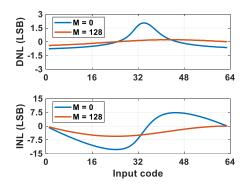

As previously discussed, the inverter-based RDAC shown in Fig. 2 suffers from nonlinearity because  $\alpha$  varies with  $V_{dac}$ . To attenuate this effect, in Prototype I, auxiliary inverters are introduced, as shown in Fig. 6. Half of the inverters are fed with 0 and the other half are with 1 to turn on their PMOS and

Fig. 7. Simulated DNLs and INLs of 6-bit RDAC in Prototype I without and with 128 attenuating inverters.

Fig. 8. (a) Leakage issue of MOSFET gate capacitor. (b) Sample-and-hold circuit in Prototype I with floating diffusion against leakage.

NMOS transistors, respectively. In this way, the variation of  $\alpha$  is suppressed. To lower the power consumption, the RDAC is only active during conversion when the end-of-conversion (EOC) signal is low. After that, logic 0 is sent to all the inverters to cut off the static current. Fig. 7 shows simulated DNLs and INLs of a 6-bit RDAC. It can be seen from the figure that the peak INL is reduced from 8.2/-12.6 LSB to 1.0/-5.0 LSB when 28 attenuating inverters (with the same unit size as in the DAC) are added.

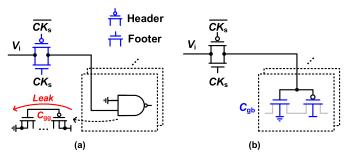

# C. Sample-and-Hold (S/H) Circuit

While it is possible to implement metal-oxide-metal (MOM) sampling capacitors using SKILL language [29], [30] or p-cell initialization by the script in a digital P&R flow [22], to mitigate implementation complexity, and to explore the possibility of an all-standard-cell-based ADC, we implement the sampling capacitor using MOSFET gate capacitance in this work. As shown in Fig. 8, in Prototype I, we use header and footer power-gating cells to make a transmission gate as the sampling switch. As for the capacitor, a conventional method is the employment of a NAND gate with one input connecting to 0 to cut off the short-circuit current, as shown in Fig. 8(a). This capacitor, however, cannot steadily hold the sampled voltage because of the leakage between the gate and diffusion. To solve this issue, we leave the power and ground ports (i.e., the diffusion) of the cell floating but retain the connections of the substrate and well. Thereby, only the gate-bulk capacitance is utilized without suffering from the leakage. Since the power and ground nodes are floating, we can replace the NAND gates with inverters for smaller area, as shown in Fig. 8(b).

Fig. 9. Simulated THDs of Prototype I where S/H is in LPE and other building blocks are in ideal Verilog-A/HDL.

Fig. 10. Chip micrograph of Prototype I.

Fig. 11. Measured DNL and INL of Prototype I.

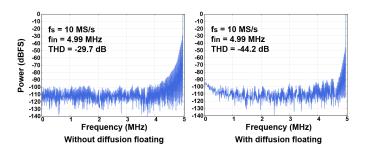

Fig. 9 shows simulated total harmonic distortions (THDs) of Prototype I where the S/H is in LPE and other building blocks are in ideal Verilog-A/HDL. With diffusion floating, the result suggests -44.2-dB THD, adequate to 6-bit resolution, whereas without diffusion floating, the THD degrades to -29.7 dB.

#### IV. EXPERIMENTAL RESULTS OF PROTOTYPE I

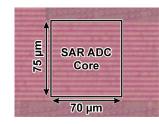

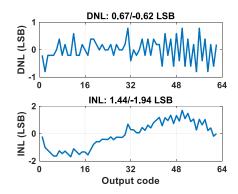

Prototype I is designed in a typical synthesizable mixedsignal circuit flow, where the digital part is synthesized, and the analog part is described in gate-level RTL. The P&R is carried out with a commercial digital automatic implementation tool. Fabricated in 65-nm bulk CMOS, the core area of Prototype I is  $0.0051 \,\mu m^2$ . Fig. 10 shows the chip micrograph. Fig. 11 shows measured DNL and INL. The peak DNL and INL are 0.67/-0.62 LSB and 1.44/-1.94 LSB, respectively, consistent with the simulated RDAC linearity shown in Fig. 7. At 10-MS/s sampling rate and 1.0-V power supply, the measured power consumption is 14.3 mW. The power consumption can be lowered by improving the gating timing of

Fig. 12. Measured spectra of Prototype I.

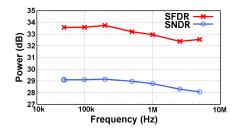

Fig. 13. Measured SFDR and SNDR with different input frequencies of Prototype I.

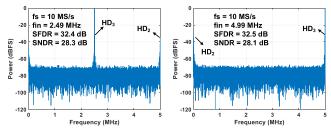

the RDAC, which will be described in Section V. Fig. 12 shows measured spectra with Nyquist-frequency (4.99 MHz) and half-Nyquist-frequency (2.49 MHz) inputs. Their measured SNDRs are 28.1 and 28.3 dB, respectively, and the former one translates to 4.4-bit ENOB and 67.73-pJ/step FoM. Fig. 13 shows the measured SNDR and SFDR versus input frequency. The performance comparison will be shown together with the results of Prototype II in Table I.

In summary, we designed and measured a 6-bit all-standardcell-based synthesizable SAR ADC as Prototype I. Its power consumption and nonlinearity due to the nonidealities of analog building blocks need to be improved. With the architecture same as the one in Fig. 4, we improved the overall performance by proposing new solutions to these building blocks. This will be described in Sections V and VI.

# V. CIRCUIT IMPROVEMENT IN PROTOTYPE II

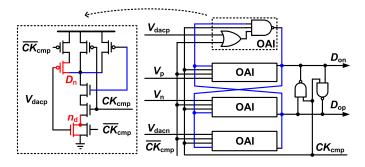

## A. OAI-Based Four-Input Comparator

As previously mentioned, a NAND comparator can be interpreted as a complementary preamplifier connected to a latch in series. If the input voltage is lower than  $V_{\text{th}}$ , the NMOS transistors of the preamplifier are turned off. Although the proposed comparator shown in Fig. 5 receives fixed common-mode input, each input can still experience low voltage. In this case, when  $CK_{\text{cmp}}$  becomes low, the reset path of a preamplifier's NMOS transistor is cut off. Thus, residue charges at the drain node ( $n_d$  in Fig. 5) remain and are uncertain. Consequently, the resulting drain voltage difference can be amplified by the latch unexpectedly during the next comparison, leading to error output. This undermines ADC's linearity especially when the input amplitude is large.

To solve this issue, we replace NAND with OAI cells in order to add a reset path for the NMOS drain nodes of

Fig. 14. Proposed OAI-based comparator where node  $n_d$  is reset by the adjacent transistor after comparison to eliminate residue charges.

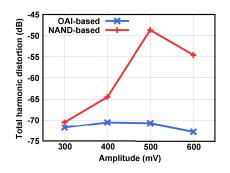

Fig. 15. Simulated ADC's THDs where comparators are in LPE and other building blocks are in ideal Verilog-A/HDL.

the preamplifier. As shown in Fig. 14, when a comparison is complete, node  $n_d$  is reset to  $V_{ss}$  by its adjacent turnedon transistor. Since the drain nodes of both PMOS and NMOS transistors of the preamplifier are reset before the next comparison, the probability of error output is greatly reduced. Fig. 15 shows simulated THDs of the SAR ADCs with NANDand OAI-based comparators in LPE and other building blocks in ideal Verilog-A/HDL. When the input amplitude grows, the THD is kept below -70 dB with an OAI-based comparator, while it degrades to -50 dB with an NAND-based one.

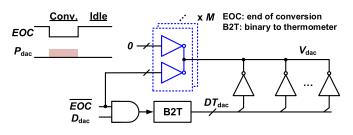

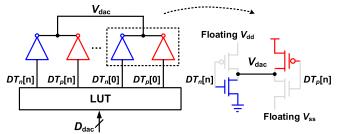

## B. Transistor-Configurable Inverter-Based RDAC With Automated Default Lookup Table (LUT) Creation in Design Phase

The feedback DAC dominates the overall ADC nonlinearity. Although we employed attenuating inverters to suppress the variation of the resistance, the linearity is still insufficient to realize moderate resolution. A natural consideration for the compensation is predistorting the input code using an LUT. Furthermore, it is demanded to separately turn on PMOS and NMOS transistors for higher compensation resolution. Based on these considerations, we proposed the improved RDAC, as shown in Fig. 16. We use two inverters for a unit, one with floating  $V_{dd}$  and the other one with floating  $V_{ss}$ . In this way, PMOS and NMOS transistors can be independently turned on. Hence, the resistors connecting to  $V_{dd}$  and  $V_{ss}$ become configurable, leading to higher compensation resolution. To realize the flowing  $V_{dd}$  and  $V_{ss}$ , two power-ground domains are defined for the macro during P&R. One domain is kept floating during the final P&R for the SAR ADC.

Fig. 16. Proposed transistor-configurable inverter-based RDAC, where PMOS and NMOS transistors can be independently turned on.

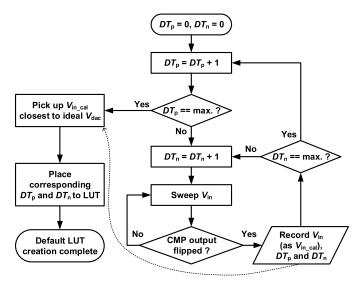

Fig. 17. Flowchart of script-controlled simulation-based default LUT creation.

The LUT as an encoder translates binary input code  $D_{dac}$ to predistorted thermometer codes  $DT_p$  and  $DT_n$ . A default LUT needs to be created during the design phase as a baseline of the nominal linearity performance. Since the SAR ADC is fully realized with standard cells, the design by transistorlevel analysis and sizing should be avoided. However, it is also impractical to determine the LUT values one by one by a significant number of manual simulations. To fully leverage the power of computer-aided design automation, we developed a Python script to control the simulation-based determination routine automatically. As shown in Fig. 17, we sweep RDAC's input and tune the input reference ramp signal to track RDAC's output voltage according to their comparison result. Once the two voltages are close enough to flip the comparator's output, the input voltage is recorded as  $V_{in_{cal}}$  as well as  $DT_p$  and  $DT_n$  in one dataset. When the sweeping is completed, from the recorded datasets, we pick up  $V_{in_{cal}}$  that is closest to the expected ideal DAC's output voltage, and place  $DT_p$  and  $DT_n$ of that dataset into the default LUT. This sweeping and tuning process requires  $2^{2N}$  times of simulations, where N is the DAC's nominal resolution. Thanks to the developed automatic routine, no tedious manual operation is required.

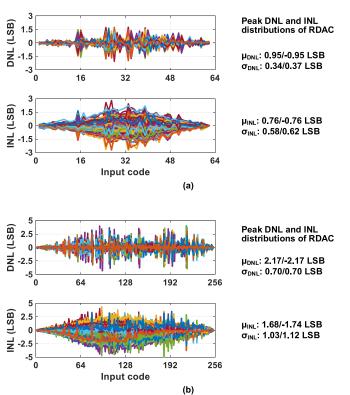

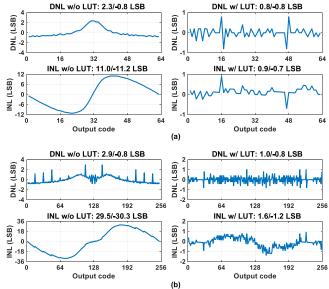

Fig. 18 shows 100-run Monte Carlo LPE simulation results of DNLs and INLs of 6- and 8-bit RDACs with their default LUTs, respectively. The mean values of peak DNL and INL

Fig. 18. 100-Run Monte Carlo LPE simulation results of (a) 6-bit and (b) 8-bit RDACs' DNLs and INLs with their default LUTs.

of the 6-bit RDAC are 0.95/-0.95 LSB and 0.76/-0.76 LSB, respectively. Their standard deviations are 0.34/0.37 LSB and 0.58/0.62 LSB, respectively. In the 8-bit one, the mean values of peak DNL and INL are 2.17/-2.17 LSB and 1.68/-1.74 LSB, respectively, and the standard deviations are 0.70/0.70 LSB and 1.03/1.02 LSB, respectively. It should be noted that the DNL exceeding -1 LSB in a DAC does not mean "missing code." From the peak INL distributions, we roughly estimate that, among 34% fabricated chips, the ENOB loss due to the RDAC nonlinearity and mismatch of the 6-bit ADC is less than 0.5 bit, while that of the 8-bit one is less than 1.5 bit. Of course, the performance can be improved by using larger size cells trading off with power consumption. It should also be noted that the LUT is possible to be configured externally for an actual chip by implementing a memory block like the all-standard-cellbased one in [31]. Then, similar automatic routine can be carried out on-chip or on-board to update the LUT values. A reconfigurable memory-based LUT also helps alleviate other process-voltage-temperature (PVT) variations at the cost of memory size and complexity. For example, an implemented  $1024 \times 1024$  memory-based LUT following [31] occupies about 0.255 mm<sup>2</sup> additional area. Alternatively, if a memory library were provided, the synthesized SRAM would be much smaller. Also, if this ADC were incorporated in an SoC, sharing its memory would be a possible choice.

The 6- and 8-bit RDACs output root-mean-square (rms) thermal noises are also simulated in LPE. The peak rms noises

Fig. 19. Intermittent RDAC enabling control in Prototype II.

Fig. 20. Bootstrap S/H circuit [21] using thick-oxide decoupling cell with floating  $V_{\rm ss}$ .

are 0.51 and 0.36 mV, respectively, sufficiently low for their resolutions.

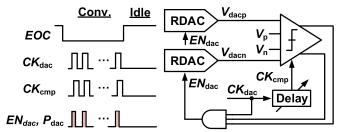

# C. RDAC Enabling Control and Bootstrapped S/H Circuit With Floating Thick-Oxide Decoupling Cell

The power consumption of the RDAC in Prototype II is lowered with the improved enabling control scheme, as shown in Fig. 19. The RDAC is only enabled for bit comparison and is disabled when each comparison ends. The enable time is about 2 ns to cover the worst case RDAC settling time. Supposing a 5-ns-period  $CK_{dac}$  shown in the figure, the duty cycle of  $EN_{dac}$  is 40%. The average power can be saved by approximately 40% as well, compared with an RDAC activated during the whole conversion period.

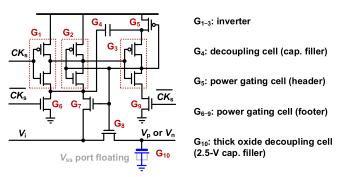

The S/H circuit is modified to the bootstrapped structure [30], as shown in Fig. 20. The type of each cell is also shown in the figure. The difference from [30] is that the sampling capacitor is changed to a thick-oxide decoupling cell for less leakage. By keeping  $V_{ss}$  port floating, the leakage is further suppressed, and the voltage-dependent capacitance variation is mitigated as well. To implement the floating  $V_{ss}$  as well as the routing of  $G_4-G_9$ , we defined several power/ground domains during P&R, following the method in [30]. In an upper-level P&R, the dedicated  $V_{ss}$  domain for the sampling capacitor is kept floating, while the power/ground domains of  $G_4-G_9$  are automatically routed by a P&R tool.

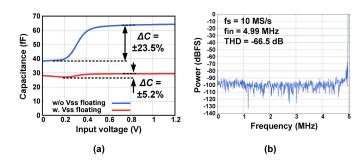

The simulated capacitance variations (with the input voltage) of the sampling capacitor are shown in Fig. 21(a). Without  $V_{\rm ss}$  floating, the capacitance varies by  $\pm 23.5\%$ ; with  $V_{\rm ss}$ floating, the variation is suppressed to  $\pm 5.2\%$ . Fig. 21(b) shows the simulated THD of the SAR ADC with S/H circuit in LPE and other building blocks in Verilog-A/HDL. The result

Fig. 21. (a) Simulated voltage-dependent capacitance variation of the sampling capacitor. (b) Simulated THD of the SAR ADC with S/H circuit in LPE and other building blocks in Verilog-A/HDL.

Fig. 22. Layout of Prototype II in 6-bit and 8-bit topologies and power breakdowns. They have same area because of unchanged floor plan.

of -66.5 dB suggests the capability of sustaining 10.75-bit ENOB thanks to these techniques.

Although one may suspect that sampling capacitor  $G_{10}$  with floating source and drain can be more sensitive to substrate noise coupling, yet simulated output spectra of the sampling circuit suggest almost no difference between the cases of floating and connected  $V_{ss}$ , when adding a 100-mV<sub>pp</sub> Gaussian random noise to the substrate of  $G_{10}$ . Nevertheless, to alleviate the substrate noise coupling when incorporating the ADC to an SoC, a guard ring is often preferred (though with some manual layout work).

## D. Discussion of Speed and Resolution

The speed of the proposed SAR ADC is mainly limited by the settling time of RDAC and the latency of LUT. LPE simulations of current designs suggest about 0.5- and 1-ns settling times of the 6- and 8-bit RDACs, respectively. Since the results are mainly limited by parasitic capacitance during P&R, they can be reduced with larger gate size and optimized wiring. Also, similar to a conventional custom SAR ADC, settling time is degraded by wire bonding, which requires sufficient decoupling capacitors. The LUT latencies of current designs are about 1 ns of both versions. Giving about 0.5 ps for sampling and about 0.7 ps for the comparator and the logic, the estimated highest conversion speeds of 6- and 8-bit SAR ADCs can be 45 and 73 MS/s, respectively. Nevertheless, since we mainly focus on the linearity improvement in Prototype II, we still designed the two ADCs with 10-MS/s sampling frequency.

Fig. 23. Simulated DNLs and INLs of (a) 6-bit and (b) 8-bit Prototype II ADCs in LPE with and without LUTs.

As for resolution, the one higher than 8-bit may be less practical because resolution is limited by the nonidealities of the RDAC, and the size of LUT increases exponentially resulting in more power consumption and area.

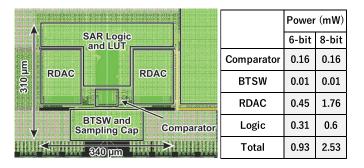

## VI. POST-LAYOUT SIMULATION RESULTS OF PROTOTYPE II

The improved SAR ADC as Prototype II is designed and implemented in 65-nm bulk CMOS. The layout covering 0.1-mm<sup>2</sup> area and the simulated power breakdowns in LPE are shown in Fig. 22. Each building block is automatically P&R, and RDACs are placed symmetrically in the macro level. Although we laid out the macro manually, it is possible to place and route it automatically using the P&R tool because the positions of building blocks and their pins are specifically known. Also, for simplicity, the floor plans for building blocks of both 6- and 8-bit versions are the same; thus, two ADCs occupy the same area. The floor plans can be, of course, optimized if the area is a concern. Verified by LPE simulations at 10-MS/s, with 1.2-V power supply, the power consumptions of the 6- and 8-bit SAR ADCs are 0.9 and 2.5 mW, respectively, thanks to the improved RDAC enabling control.

Fig. 23 shows the simulated DNLs and INLs of the two ADCs in LPE without and with their default LUTs. Without LUTs, the peak DNL and INL of the 6-bit version are 2.3/-0.8 LSB and 11.0/-11.2 LSB, respectively. Those of the 8-bit version are 2.9/-0.8 LSB and 29.5/-30.3 LSB, respectively. Thanks to the LUT-based compensation, the linearity is significantly improved. With LUT, the peak DNL and INL of the 6-bit version are 0.8/-0.8 LSB and 0.9/-0.7 LSB, respectively. Those of the 8-bit version are 1.0/-0.8 LSB and 1.6/-1.2 LSB, respectively.

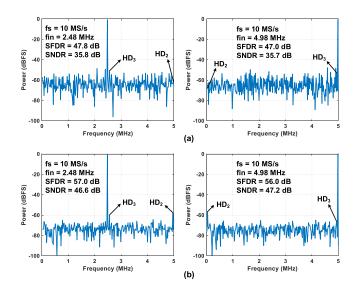

Fig. 24 shows simulated spectra of the two ADCs with Nyquist and half-Nyquist input frequencies. Transient noise is turned on for the simulations. The number of FFT points

TABLE I

Performance Comparison With State-of-the-Art Synthesizable ADCs

|                                 | Prototype I           | <sup>1</sup> Prototype II |       | Access'19       | Access'20            | TCAS-I'14             | TCAS-II'15            | CICC'19       | <sup>3</sup> TCAS-I'14 |

|---------------------------------|-----------------------|---------------------------|-------|-----------------|----------------------|-----------------------|-----------------------|---------------|------------------------|

|                                 |                       | 6-bit                     | 8-bit | [21]            | [22]                 | [16]                  | [25]                  | [19]          | [27]                   |

| Туре                            | SAR                   | SAR                       |       | SAR             | SAR                  | Stochastic            | Stochastic            | VCO-based     | VCO-based              |

| Custom cells involved?          | No                    | No                        | No    | No              | Poly res. & MOM cap. | No                    | No                    | Poly resister | No                     |

| CMOS (nm)                       | 65                    | 65                        |       | 28              | 40                   | 90                    | 130                   | 40            | 65                     |

| Active area (mm <sup>2</sup> )  | 0.0053                | <sup>2</sup> 0.1          |       | 0.002           | 0.005                | 0.18                  | 0.51                  | 0.01          | 0.026                  |

| Input range (mV <sub>pp</sub> ) | 600<br>(differential) | 2200<br>(differential)    |       | 800<br>(single) | 1000<br>(single)     | 280<br>(differential) | 800<br>(differential) | NA            | 600<br>(single)        |

| F <sub>s</sub> (MHz)            | 10                    | 10                        |       | 0.5             | 0.0028               | 21                    | 140                   | 600           | 205                    |

| BW (MHz)                        | 5                     | 5                         |       | 0.25            | 0.0014               | 10.5                  | 70                    | 4             | 25.6                   |

| SNDR (dB)                       | 28.1                  | 35.7                      | 47.2  | 34.2            | 40.4                 | 34.6                  | 28.5                  | 68.8          | 50.3                   |

| SFDR (dB)                       | 32.5                  | 45.7                      | 62.1  | 44              | 49.7                 | 41.5                  | 37.0                  | 75            | 55.3                   |

| ENOB (bit)                      | 4.4                   | 5.6                       | 7.5   | 5.4             | 6.4                  | 5.5                   | 4.4                   | 11.1          | 8.1                    |

| Power (mW)                      | 14.3                  | 0.9                       | 2.5   | 0.092           | 0.0073               | 1.1                   | 2.3                   | 1.1           | 3.3                    |

| <sup>4</sup> FoM (pJ/step)      | 67.73                 | 1.86                      | 1.38  | 4.36            | 30.87                | 1.16                  | 0.78                  | 0.06          | 0.23                   |

<sup>1</sup>Verified with LPE simulation.

<sup>2</sup>Same floor plan for the 6-bit and 8-bit versions.

<sup>3</sup>Not automatically laid out.

<sup>4</sup>FoM = Power / (2ENOB×2×BW).

Fig. 24. Simulated spectra of (a) 6-bit and (b) 8-bit Prototype II in LPE with transient noise turned on.

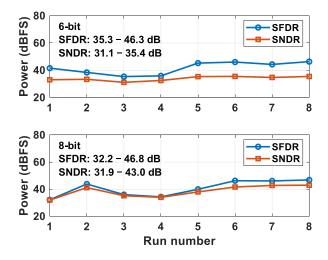

is 512. With Nyquist input frequency, the SNDRs are 35.7 and 47.2 dB, respectively, translating to 5.6- and 7.5-bit ENOBs, and 1.86- and 1.38-pJ/step FoMs, respectively. Fig. 25 shows Monte Carlo simulated SFDRs and SNDRs. Although the SNDR of the 8-bit ADC can degrade to the same level of the 6-bit one, as previously mentioned, the issue is possible to be overcome with a reconfigurable memory-based LUT.

The performance of Prototype-I and Prototype-II is compared with the state-of-the-art synthesizable ADCs in Table I. Compared with Prototype I, Prototype II is expected to have better performance in terms of input range, SNDR, and power consumption. Compared with the SAR ADCs of [21], [22], this work features higher signal bandwidth, better SNDR, and better FoM (expected from LPE simulation). The SNDR and FoM are also comparable with [16], [25] though the latter two works feature higher sampling rates. The sampling rate and the signal bandwidth of this work can be further

Fig. 25. Monte Carlo simulated SFDRs and SNDRs of 6-bit and 8-bit Prototype II in LPE.

increased by improving the internal clocking and logic latency. Although the FoMs are less comparable with [19], [27], this work is implemented using only standard cells and laid out automatically. Furthermore, the proposed SAR ADC can generally handle a larger amplitude of the input signal among the other works.

#### VII. CONCLUSION

We have presented a fully synthesizable all-standard-cellbased SAR ADC using an inverter-based RDAC, a four-input comparator, and a floating-diffusion S/H circuit. Prototype I in 6-bit architecture is measured on silicon. The performance is improved in Prototype II with proposed techniques enhancing linearity and lowering power consumption. The performance of Prototype II is verified through LPE simulations in 6- and 8-bit versions. The ADCs are described in RTL and laid out using a commercial digital automatic P&R tool. The circuits and the methodology enable fast implementation still with moderate resolution. This merit is highly demanded in the scenario of incorporating this ADC into a digital signal processing system.

#### ACKNOWLEDGMENT

EDA tools are provided through the activities of VDEC, The University of Tokyo, in collaboration with Synopsys, Inc., Cadence Design Systems, Inc., and Mentor Graphics, Inc.

#### REFERENCES

- [1] S.-J. Kim, W. Kim, M. Song, J. Kim, T. Kim, and H. Park, "A 0.6 V 1.17 ps PVT-tolerant and synthesizable time-to-digital converter using stochastic phase interpolation with 16× spatial redundancy in 14 nm FinFET technology," in *IEEE Int. Solid-State Circuits Conf.* (*ISSCC*) Dig. Tech. Papers, vol. 58, Feb. 2015, pp. 280–281.

- [2] K. Choo, H. Kim, W. Kim, J. Kim, T. Kim, and H. Ko, "A 0.02 mm<sup>2</sup> fully synthesizable period-jitter sensor using stochastic TDC without reference clock and calibration in 10 nm CMOS technology," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2018, vol. 61, no. 2, pp. 120–122.

- [3] Y. Park and D. D. Wentzloff, "A cyclic Vernier TDC for ADPLLs synthesized from a standard cell library," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 58, no. 7, pp. 1511–1517, Jul. 2011.

- [4] Y. Park and D. D. Wentzloff, "An all-digital PLL synthesized from a digital standard cell library in 65 nm CMOS," in *Proc. IEEE Custom Integr. Circuits Conf.*, Sep. 2011, pp. 4–7.

- [5] W. Kim, J. Park, J. Kim, T. Kim, H. Park, and D. Jeong, "A 0.032 mm<sup>2</sup> 3.1 mW synthesized pixel clock generator with 30 ps<sub>rms</sub> integrated jitter and 10-to-630 MHz DCO tuning range," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, vol. 56, Feb. 2013, pp. 250–251.

- [6] W. Kim, J. Park, H. Park, and D.-K. Jeong, "Layout synthesis and loop parameter optimization of a low-jitter all-digital pixel clock generator," *IEEE J. Solid-State Circuits*, vol. 49, no. 3, pp. 657–672, Mar. 2014.

- [7] W. Deng et al., "A 0.048 mm<sup>2</sup> 3 mW synthesizable fractional-N PLL with a soft injection-locking technique," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, vol. 58, Feb. 2015, pp. 1–3.

- [8] D.-J. Chang, M.-J. Seo, H.-K. Hong, and S.-T. Ryu, "A 65 nm 0.08-to-680 MHz low-power synthesizable MDLL with nested-delay cell and background static phase offset calibration," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 65, no. 3, pp. 281–285, Mar. 2018.

- [9] B. Liu *et al.*, "A 0.4-ps-jitter–52-dBc-spur synthesizable injectionlocked PLL with self-clocked nonoverlap update and slope-balanced subsampling BBPD," *IEEE Solid-State Circuits Lett.*, vol. 2, no. 1, pp. 5–8, Jan. 2019.

- [10] S. Kundu, L. Chai, K. Chandrashekar, S. Pellerano, and B. R. Carlton, "A self-calibrated 2-bit time-period comparator-based synthesized fractional-N MDLL in 22-nm FinFET CMOS," *IEEE J. Solid-State Circuits*, vol. 56, no. 1, pp. 43–54, Jan. 2021.

- [11] B. Liu et al., "A fully synthesizable fractional-N MDLL with zero-order interpolation-based DTC nonlinearity calibration and two-step hybrid phase offset calibration," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 68, no. 2, pp. 603–616, Feb. 2021.

- [12] N. Ojima, T. Nakura, T. Iizuka, and K. Asada, "A synthesizable digital low-dropout regulator based on voltage-to-time conversion," in *Proc. IEEE/IFIP Int. Conf. VLSI Syst. VLSI-SoC*, Oct. 2018, pp. 55–58.

- [13] J. Oh, J.-E. Park, Y.-H. Hwang, and D.-K. Jeong, "A 480 mA outputcapacitor-free synthesizable digital LDO using CMP-triggered oscillator and droop detector with 99.99% current efficiency, 1.3 ns response time, and 9.8A/mm<sup>2</sup> current density," in *IEEE Int. Solid-State Circuits Conf.* (*ISSCC*) Dig. Tech. Papers, Feb. 2020, pp. 382–383.

- [14] S. Bang et al., "A fully synthesizable distributed and scalable all-digital LDO in 10 nm CMOS," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2020, pp. 380–381.

- [15] S. Weaver, B. Hershberg, and U.-K. Moon, "Digitally synthesized stochastic flash ADC using only standard digital cells," in *Proc. IEEE Symp. VLSI Circuits*, Jul. 2011, pp. 266–267.

- [16] S. Weaver, B. Hershberg, and U.-K. Moon, "Digitally synthesized stochastic flash ADC using only standard digital cells," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 61, no. 1, pp. 84–91, Jan. 2014.

- [17] B. Xu, S. Li, N. Sun, and D. Z. Pan, "A scaling compatible, synthesis friendly VCO-based delta-sigma ADC design and synthesis methodology," in *Proc. 54th Annu. Design Autom. Conf.*, Jun. 2017, pp. 1–6.

- [18] O. Aiello, P. Crovetti, A. Sharma, and M. Alioto, "Fully-synthesizable current-input ADCs for ultra-low area and minimal design effort," in *Proc. 26th IEEE Int. Conf. Electron., Circuits Syst. (ICECS)*, Nov. 2019, pp. 715–718.

- [19] S. Li, B. Xu, D. Z. Pan, and N. Sun, "A 60-fJ/step 11-ENOB VCO-based CTDSM synthesized from digital standard cell library," in *Proc. IEEE Custom Integr. Circuits Conf. (CICC)*, Apr. 2019, pp. 1–4.

- [20] N. Ojima, Z. Xu, and T. Iizuka, "A 0.0053-mm<sup>2</sup> 6-bit fully-standardcell-based synthesizable SAR ADC in 65 nm CMOS," in *Proc. 17th IEEE Int. New Circuits Syst. Conf.*, Jun. 2019, pp. 1–4.

- [21] J.-E. Park, Y.-H. Hwang, and D.-K. Jeong, "A 0.5-V fully synthesizable SAR ADC for on-chip distributed waveform monitors," *IEEE Access*, vol. 7, pp. 63686–63697, 2019.

- [22] O. Aiello, P. Crovetti, and M. Alioto, "Fully synthesizable low-area analogue-to-digital converters with minimal design effort based on the dyadic digital pulse modulation," *IEEE Access*, vol. 8, pp. 70890–70899, 2020.

- [23] S.-J. Kim, Z. Myers, S. Herbst, B. Lim, and M. Horowitz, "Opensource synthesizable analog blocks for high-speed link designs: 20-GS/s 5b ENOB analog-to-digital converter and 5-GHz phase interpolator" in *Proc. IEEE Symp. VLSI Circuits*, Jun. 2020, pp. 1–2.

- [24] S.-J. Kim, Z. Myers, S. Herbst, B. Lim, and M. Horowitz, "20-GS/s 8-bit analog-to-digital converter and 5-GHz phase interpolator for open-source synthesizable high-speed link applications," *IEEE Solid-State Circuits Lett.*, vol. 3, pp. 518–521, 2020.

- [25] A. Fahmy, J. Liu, T. Kim, and N. Maghari, "An all-digital scalable and reconfigurable wide-input range stochastic ADC using only standard cells," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 62, no. 8, pp. 731–735, Aug. 2015.

- [26] S. Weaver, B. Hershberg, N. Maghari, and U.-K. Moon, "Domino-logicbased ADC for digital synthesis," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 58, no. 11, pp. 744–747, Nov. 2011.

- [27] V. Unnikrishnan and M. Vesterbacka, "Time-mode analog-to-digital conversion using standard cells," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 61, no. 12, pp. 3348–3357, Dec. 2014.

- [28] A. Waters and U.-K. Moon, "A fully automated verilog-to-layout synthesized ADC demonstrating 56 dB-SNDR with 2 MHz-BW," in *Proc. IEEE Asian Solid-State Circuits Conf. (A-SSCC)*, Nov. 2015, pp. 6–9.

- [29] M. Ding et al., "A hybrid design automation tool for SAR ADCs in IoT," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 26, no. 12, pp. 2853–2862, Dec. 2018.

- [30] M.-J. Seo, Y.-J. Roh, D.-J. Chang, W. Kim, Y.-D. Kim, and S.-T. Ryu, "A reusable code-based SAR ADC design with CDAC compiler and synthesizable analog building blocks," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 65, no. 12, pp. 1904–1908, Dec. 2018.

- [31] X. Fan, J. Stuijt, B. Liu, and T. Gemmeke, "Synthesizable memory arrays based on logic gates for subthreshold operation in IoT," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 66, no. 3, pp. 941–954, Mar. 2019.

**Zule Xu** (Member, IEEE) received the B.E. degree in electrical engineering from the Dalian University of Technology, Dalian, China, in 2006, the M.E. degree in electrical communication engineering from Tohoku University, Sendai, Japan, in 2011, and the Ph.D. degree in physical electronics engineering from the Tokyo Institute of Technology, Tokyo, Japan, in 2015.

From 2015 to 2016, he was a Researcher with the Tokyo Institute of Technology. From 2016 to 2018, he was with the Tokyo University of Science, Tokyo,

as an Assistant Professor. Since 2018, he has been with The University of Tokyo, Tokyo, as an Assistant Professor. His current research interests include data converters, PLLs, oscillators, and their design automation.

Dr. Xu is a member of the Institute of Electronics, Information and Communication Engineers (IEICE). He is serving as a Technical Program Committee Member of IEEE A-SSCC and an Associate Editor for IEICE transactions. He was a recipient of NEWCAS Best Student Paper Award in 2013, CICC Student Scholarship Award in 2013, and Yasujiro Niwa Outstanding Paper Award in 2017.

**Naoki Ojima** (Member, IEEE) received the B.S. and M.S. degrees in electronic engineering from The University of Tokyo, Tokyo, Japan, in 2018 and 2020, respectively.

He is currently with Western Digital GK, Tokyo. His current research interests include data converters, LDOs, and their design automation.

**Tetsuya Iizuka** (Senior Member, IEEE) received the B.S., M.S., and Ph.D. degrees in electronic engineering from The University of Tokyo, Tokyo, Japan, in 2002, 2004, and 2007, respectively.

From 2007 to 2009, he was with THine Electronics Inc., Tokyo, as a High-Speed Serial Interface Circuit Engineer. In 2009, he joined The University of Tokyo, where he is currently an Associate Professor with the Systems Design Lab, School of Engineering. From 2013 to 2015, he was a Visiting Scholar with the University of California at Los Angeles,

Los Angeles, CA, USA. His current research interests include data conversion techniques, high-speed analog integrated circuits, digitally assisted analog circuits, and VLSI computer-aided design.

Dr. Iizuka is a member of the Institute of Electronics, Information and Communication Engineers (IEICE). He was a member of the IEEE International Solid-State Circuits Conference (ISSCC) Technical Program Committee from 2013 to 2017 and a member of the IEEE Custom Integrated Circuits Conference (CICC) Technical Program Committee from 2014 to 2019. He is currently serving as a member of the IEEE Asian Solid-State Circuits Conference (A-SSCC) and IEEE VLSI Symposium on Circuits Technical Program Committees. He was a recipient of the 21st Marubun Research Encouragement Commendation from Marubun Research Promotion Foundation in 2018, the 13th Wakashachi Encouragement Award First Prize in 2019, and the 18th Funai Academic Prize from Funai Foundation for Information Technology in 2019. He was a co-recipient of the IEEE International Test Conference Ned Kornfield Best Paper Award in 2016. From 2016 to 2018, he served as an Editor of *IEICE Electronics Express* (ELEX).

Shuowei Li (Student Member, IEEE) received the B.S. degree in mechatronic engineering from The University of Manchester, Manchester, U.K., and the B.S. degree in electrical engineering and its automation from North China Electric Power University, Beijing, China, in 2017. He is currently pursuing the M.S. degree with the Department of Electrical Engineering and Information Systems, The University of Tokyo, Tokyo, Japan.

His current interests include high-performance SAR ADCs and their design automation.

Mr. Li is a Student Member of Information and Communication Engineers (IEICE).