# 26<sup>th</sup> International Symposium on the Physical and Failure Analysis of Integrated Circuits (IPFA 2019)

2 July – 5 July 2019 Grand Hyatt Hotel, Hangzhou, China

Technically Co-sponsored by

**Platinum Sponsor**

**Gold Sponsors**

**Media Cooperation**

# Content

| Welcoming Address                            | 1  |

|----------------------------------------------|----|

| IPFA Board                                   | 2  |

| Committee Members                            | 2  |

| Technical Program Committee                  | 3  |

| Special speakers                             | 7  |

| General Information                          |    |

| Map of the Conference Zone                   |    |

| Sponsor                                      | 11 |

| Map of the Exhibition Zone — Exhibition Hall |    |

| List of Exhibitors & Booth                   | 14 |

| Exhibitors' Information                      | 15 |

| Keynote speakers                             |    |

| Tutorials speakers                           |    |

| Invited speakers                             |    |

| Technical Program                            | 60 |

| Poster Paper Information                     | 71 |

## Welcoming Address

## Dear IPFA2019 participants,

On behalf of the organizing committees from both China and Singapore, you are cordially invited to attend the 26th IEEE International Symposium on the Physical and Failure Analysis of Integrated Circuits - IPFA. IPFA is an international conference which has been one of the major conferences in the reliability and failure analysis of devices and integrated circuits. This has been the 26th in its series and organized by the IEEE EDS Hangzhou Chapter and the IEEE Singapore Reliability/CPMT/ED Chapter. The Symposium is technically co-sponsored by the IEEE Electron Devices Society. This year the symposium will be held in Hangzhou, China.

In this symposium we have received more than 201 submissions from 15 countries, in which 54 papers were selected for oral presentations, and 101 for poster presentations. We have also 19 invited talks, along with two outstanding exchange papers contributed from ISTFA and ESREF 2018, respectively. We are also delighted to have two distinguished keynote speakers for the plenary session. Dr. Prasad Chaparala, Amazon Lab126, will speak on "Building Reliable Products Guided by Customer Obsession" and Dr. Shimeng Yu, Georgia Institute of Technology, will address on "Emerging Non-Volatile Memory's Applications in Neuro-Inspired Computing and Hardware Security". The events of IPFA 2019 include a one-day tutorial, 3 days technical paper presentation, and concurrently with exhibition from worldwide vendors. A one-day tutorial, scheduled for Tuesday, July 2, will cover seven topics in two parallel sessions. This brings up an excellent opportunity for experienced as well as engineers, scholars, professors, and students, to broaden their technical knowledge in both reliability and failure analysis techniques. Vendor exhibits presenting state-of-the-art advanced techniques and equipments on the failure analysis, testing and measurement equipments etc., which are held throughout the whole conference.

This year's symposium will not be possible without continuing support from the IPFA board in Singapore, the exhibit vendors, paper review from our program committee members, and the contributed papers from our authors. Especially, we would like to express our sincere gratitude to everyone who contributed numerous efforts of the local arrangements, especially thanks to the Program Chair, Dr. Zhiwei Liu and co-chairs, Dr. Wardhana A. Sasangka and Dr. Youlin Wu, for their dedication of hard-work in paper selections, as well as those more than 60 world experts technical committee members, in the field of reliability. Finally, special thank goes to Jasmine Leong for her help in the transformation and sharing the information from the Singapore team in their past years' experience.

We expect a truly international forum for this exciting conference. Enjoy the conference, enjoy the friendship, and enjoy your stay in Hangzhou!

2<sup>nd</sup> July, 2019

Dr. Juin J.Liou General Chair Dr. Nagarajan Raghavan General Co-Chair

## **IPFA Board**

| Chair  | Jiann Min Chin (Advanced Micro Devices)                              |

|--------|----------------------------------------------------------------------|

| Member | <b>PEY Kin Leong</b> (Singapore University of Technology and Design) |

|        | Thong Tiam Leong John (National University of Singapore)             |

|        | Chee Lip Gan (Nanyang Technological University)                      |

|        | Lim Yeow Kheng (STATS ChipPAC Pte.Ltd)                               |

|        | Vinod Narang (Advanced Micro Devices)                                |

|        | Szu Huat Goh (GlobalFoundries)                                       |

|        |                                                                      |

## **Committee Members**

| General Chair                   | Juin J. Liou (Zhengzhou University, China)                         |

|---------------------------------|--------------------------------------------------------------------|

| General Co-Chair                | Nagarajan Raghavan (Singapore University of Technology and Design, |

|                                 | Singapore)                                                         |

| TPC Chair                       | Zhiwei Liu (UESTC, China)                                          |

| <b>TPC Co-Chairs</b>            | Wardhana A. Sasangka (Singapore-MIT Alliance for Research and      |

|                                 | Technology, Singapore)                                             |

|                                 | Youlin Wu (National Chi Nan University, Taiwan)                    |

| Exhibition Chair                | Rongxiang Wu (UESTC, China)                                        |

| <b>Registration Chair</b>       | Yahong Zhai (UESTC, China)                                         |

| Publicity Chair                 | Min Ren (UESTC, China)                                             |

| <b>Publicity Co-Chairs</b>      | Yulong Zhu (Hanwa, Japan)                                          |

|                                 | Grace Lin (Integrated Service Technology)                          |

| <b>Publication Chairs</b>       | Wei Liang (GlobalFoundries, USA)                                   |

|                                 | Ruzhang Li (National Key Laboratory of Analog Integrated Circuits, |

|                                 | China)                                                             |

| Local Arrangement Chairs        | Shurong Dong (Zhejiang University, China)                          |

|                                 | Jizhi Liu (UESTC, China)                                           |

| Financial Chair                 | Yi Zheng (UESTC, China)                                            |

| <b>IPFA Singapore Secretary</b> | Jasmine Leong (Singapore)                                          |

| Volunteer Chair                 | Boan Pan (UESTC, China)                                            |

| <b>Conference Secretary</b>     | Zhen Li (UESTC, China)                                             |

## **Technical Program Committee**

## **Track 1: Sample Preparation, Metrology and Defect Characterization**

ChairRalf Heiderhoff (Bergische Universitat Wuppertal, Germany)Co-ChairVinod Narang (AMD, Singapore)MemberChih Hang Tung (TSMC, Taiwan)Liu Qing (NTU, Singapore)Erwin Hendarto (Silabs, Singapore)Sam Subramanian (NXP Semiconductors, USA)John Thong (NUS, Singapore)

## **Track 2: Case Studies on Fault Isolation**

| Chair    | Christian Boit (Technical University Berlin, Germany) |

|----------|-------------------------------------------------------|

| Co-Chair | Alfred Quah (GlobalFoundries, Singapore)              |

| Member   | Hirotoshi Terada (Hamamatsu, Japan)                   |

|          | Szu Huat Goh (GlobalFoundries, Singapore)             |

|          | Zhongling Qian (Infineon, USA)                        |

|          | Amit Jakati (GlobalFoundries, Singapore)              |

|          | Joshua Kevek (Intel, USA)                             |

## Track 3: Case Studies on Physical Failure Analysis

| Chair    | Alan Street (On Semiconductor, China)                |

|----------|------------------------------------------------------|

| Co-Chair | Ingrid De Wolf (IMEC, Belgium)                       |

| Member   | James Lee (TSMC, Taiwan)                             |

|          | Olivier Latry (University of Rouen Normandy, France) |

|          | Eckhard Langer (GlobalFoundries, Germany)            |

|          | Ruby Vollrath (Qualcomm, USA)                        |

## **Track 4: Package-Level Failure Analysis**

| Chair    | Susan Li (Cypress, USA)                             |

|----------|-----------------------------------------------------|

| Co-Chair | Jiann Min Chin (AMD, Singapore)                     |

| Member   | Bernice Zee (AMD, Singapore)                        |

|          | Wentao Qin (On Semiconductor, USA)                  |

|          | Peter Jacob (EMPA, Switzerland)                     |

|          | Yan Li (Intel, USA)                                 |

|          | Em Julius Dela Cruz (Maxim Integrated, Philippines) |

|          | Liyi Li (Intel, USA)                                |

## **Technical Program Committee**

## **Track 5: Advanced Electrical Fault Isolation Techniques**

| Chair  | Venkat Krishnan Ravikumar (AMD, Singapore) |

|--------|--------------------------------------------|

| Member | Phillippe Perdu (CNES, France)             |

|        | Kris Dickson (NXP, USA)                    |

|        | Mike Bruce (Consultant, USA)               |

|        | Christopher Nemirow (Thermofisher, USA)    |

## **Track 6: Advanced Physical Failure Analysis Techniques**

| Chair  | Christian Hobert (GlobalFoundries, Germany) |

|--------|---------------------------------------------|

| Member | Umberto Celano (IMEC, Belgium)              |

|        | Chen Changqing (GlobalFoundries, Singapore) |

|        | Michael DiBattista (VarioScale, USA)        |

|        | Hongwen He (Hisilicon Technologies, China)  |

|        | Jayhoon Chung (Texas Instruments, USA)      |

## **Track 7: Emerging Topics in Failure Analysis**

| Chair    | Zhigang Ji (Liverpool John Moores University, UK) |

|----------|---------------------------------------------------|

| Co-Chair | Samuel Chef (NTU, Singapore)                      |

| Member   | Cheryl Hartfield (ZEISS, USA)                     |

|          | Wen Qiu (AMD, Singapore)                          |

|          | Chee Lip Gan (NTU, Singapore)                     |

|          | Hong Yang (IMECAS, China)                         |

|          | Bin Gao (Tsinghua University, China)              |

|          | Sun Litao (Southeast University, China)           |

|          | Du Anyan (IMECAS, China)                          |

|          | Changze Liu (Huawei Technologies, China)          |

|          |                                                   |

## **Track 8: Transistor and NVM Device Reliability**

| Chair    | Runsheng Wang (Peking University, China)                   |

|----------|------------------------------------------------------------|

| Co-Chair | Mario Lanza (Soochow University, China)                    |

| Member   | Jim Stathis (IBM, USA)                                     |

|          | Jianfu Zhang (Liverpool John Moores University, UK)        |

|          | Shubhakar Kalya (SUTD, Singapore)                          |

|          | Kaikai Xu (UESTC, China)                                   |

|          | Felix Palumbo (National Tech. University (UTN), Argentina) |

|          | Tibor Grasser (TU Wien, Austria)                           |

|          | Francesco Maria Puglisi (University of Modena, Italy)      |

|          | Horng-Chih Lin (NCTU, Taiwan)                              |

## **Technical Program Committee**

Enrique Miranda (UAB, Spain) Ming Liu (IMECAS, China) Mingxiang Wang (Soochow University, China) Erik Bury (IMEC, Belgium) Nagarajan Raghavan (Singapore University of Technology and Design, Singapore) Jiezhi Cheng (Shandong University, China) Meng Zhang (Shenzhen University, China) Chenkun Wang (Marvell Semiconductor Inc, USA) Wang Chao (Huazhong University of Science and Technology, China) Norhayati Soin (University of Malaya, Malaysia) Alok Ranjan (SUTD, Singapore) Zhiwei Liu (UESTC, China) Stanislav Tyaginov (TU Wien, Austria) Zheng Chai (Liverpool John Moores University, UK) Nilesh Goel (BITS Pilani Dubai Campus, India) Salvatore Lombardo (CNR-IMM, Italy) Narendra Parihar (IMEC, Belgium) **Danny Shum** (NXP Singapore, Singapore) Subhali Subhechha (IMEC, Belgium) Marco Villena (Soochow University, China) You-Lin Wu (National Chi Nan University, Taiwan) Wei Zhang (Liverpool John Moores University, UK) Wei Liang (GlobalFoundries, USA)

## **Track 9: Interconnect and Packaging Reliability**

| Chair    | Jeffrey Gambino (ON Semiconductor, USA)                                              |

|----------|--------------------------------------------------------------------------------------|

| Co-Chair | Rongxiang Wu (UESTC, China)                                                          |

| Member   | Lim Yeow Kheng (STATSChipPAC, Singapore)                                             |

|          | Kristof Croes (IMEC, Belgium)                                                        |

|          | Tam Lyn Tan (GlobalFoundries, Singapore)                                             |

|          | Kuan-Neng Chen (NCTU, Taiwan)                                                        |

|          | Wenqi Zhang (NCAP, China)                                                            |

|          | Hajdin Ceric (TU Wien, Austria)                                                      |

|          | Valeriy Sukharev (Mentor Graphics, USA)                                              |

|          | Wardhana A. Sasangka (Singapore-MIT Alliance for Research and Technology, Singapore) |

|          | Christine Hau-Riege (Qualcomm, USA)                                                  |

## **Track 10: Photovoltaic Device Reliability and Failure Analysis**

MemberZhang Li (Singapore-MIT Alliance for Research and Technology, Singapore)Kunal Mukherjee (University of California, Santa Barbara, USA)Arief Suriadi Budiman (SUTD, Singapore)Ariya Sangwongwanich (Aalborg University, Denmark)Rongshan Wei (Fuzhou University, China)Yang Xu (Zhejiang University, China)Andrew Tay (SUTD, Singapore)Kristof Croes (IMEC, Belgium)

## Track 11: High Power Electronics/Wide Bandgap Device Reliability and

## **Failure Analysis**

| Chair    | Min Ren (UESTC, China)                                                               |

|----------|--------------------------------------------------------------------------------------|

| Co-Chair | Wardhana A. Sasangka (Singapore-MIT Alliance for Research and Technology, Singapore) |

| Member   | Francesco Iannuzo (Aalborg University, Denmark)                                      |

|          | Tian-Li Wu (National Chiao Tung University, Taiwan)                                  |

|          | Martin Kuball (University of Bristol, UK)                                            |

|          | Siyang Liu (Southeast University, China)                                             |

|          | Wangran Wu (Southeast University, China)                                             |

|          | Jinping Zhang (UESTC, China)                                                         |

|          | Bhawani Shankar (Indian Institute of Science, India)                                 |

|          | Zhongling Qian (Infineon, Germany)                                                   |

|          | Matteo Meneghini (University of Padova, Italy)                                       |

|          | Guoqiao Tao (Ampleon, Netherlands)                                                   |

## Track 12: 2D Materials and Devices: Reliability and Failure Analysis

| Chair                         | Yang Xu (Zhejiang University, China)                            |  |

|-------------------------------|-----------------------------------------------------------------|--|

| Co-Chair                      | Wu Xing (ECNU, China)                                           |  |

| Member                        | Kah Wee Ang (National University of Singapore (NUS), Singapore) |  |

| Alok Ranjan (SUTD, Singapore) |                                                                 |  |

|                               | Fei Hui (Technion-Israel Institute of Technology, Israel)       |  |

|                               | Yuanyuan Shi (Technion-Israel Institute of Technology, Israel)  |  |

## **Special speakers**

## **Keynote speakers:**

**Prasad Chaparala** (Amazon Lab126, USA) **Shimeng Yu** (Georgia Institute of Technology, USA)

## **Tutorials:**

Dimitris P. Ioannou (GlobalFoundries, USA)

David Su (Taiwan Semiconductor Manufacturing Company, Taiwan)

Jianfu Zhang (Liverpool John Moores University, UK)

Lihong Cao (ASE Group, TX, USA)

Francesco Iannuzzo (Aalborg University, Denmark)

Venkat Krishnan Ravikumar (AMD, Singapore)

Baozhen Li (IBM System and Technology Group, Essex Vermont, USA)

Szu Huat Goh (GlobalFoundries, Singapore)

## **Invited speakers:**

Jianfu Zhang (Liverpool John Moores University, UK) Lihong Cao (ASE Group, Austin, TX, USA) Mu-Chun Wang (Minghsin University of Science and Technology, Taiwan) Baozhen Li (IBM System and Technology Group, Essex Vermont, USA) Venkat Krishnan Ravikumar (AMD, Singapore) You Li (GlobalFoundries, USA) Christian Boit (TU Berlin, Germany) You Wang (Beihang University, China) Ching-Chun Lin (Integrated Service Technology, Taiwan) Francesco Iannuzzo (Aalborg University, Denmark) David Su (Taiwan Semiconductor Manufacturing Company, Taiwan) Xing Zhou (Nanyang Technological University, Singapore) Sun Litao (South East University, China) Dimitris P. Ioannou (GlobalFoundries, USA) Yury Illarionov (TU Wien, Austria) Wu Xing (East China Normal University, China) Bin Gao (Tsinghua University, China) Mario Lanza (Soochow University, China) Kosuke Nagashio (University of Tokyo, Japan)

## **General Information**

## **Venue of Conference**

Grand Hyatt Hangzhou 28 Hubin Rd, HuBin ShangQuan, Shangcheng Qu, Hangzhou Shi, Zhejiang Sheng, China.

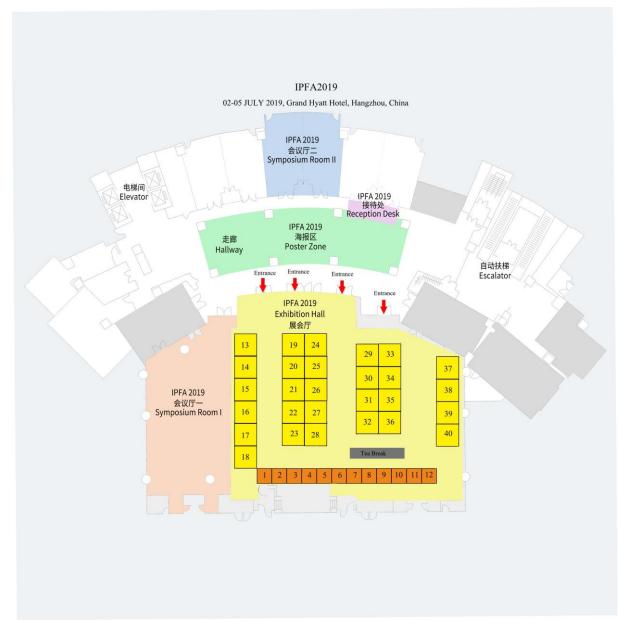

## **Registration and Information Desk and Conference Secretariat**

The registration and information desk will be arranged at the Reception Desk. The conference secretariat will be set in the Secretary Room from July 2nd to July 5th during the conference.

## **Poster Presentations**

Poster sessions will be arranged at the Poster Zone. Please refer to the Technical Program for your poster number.

Poster are supposed to put up in advance and taken off after the session. Tape is available on request from the Information Desk. Please understand that any poster remaining over the removal time will be disposed after the conference.

## Name Badge

For identification purpose, badges are expected to be worn at all times during the conference.

## Internet

Wireless connection will be available in the conference theatres. The account for log-in will be provided during the conference.

## Meal

From July 2<sup>nd</sup> to July 5<sup>th</sup>, lunches will be provided at West Lake Room which is located at the 2nd Floor in Grand Hyatt Hangzhou Hotel. Please bring your lunch coupon with you for lunch. You must show your ticket to the waitress.

## **Emergency Contact**

Please ask the help from the conference information desk.

## **General Information**

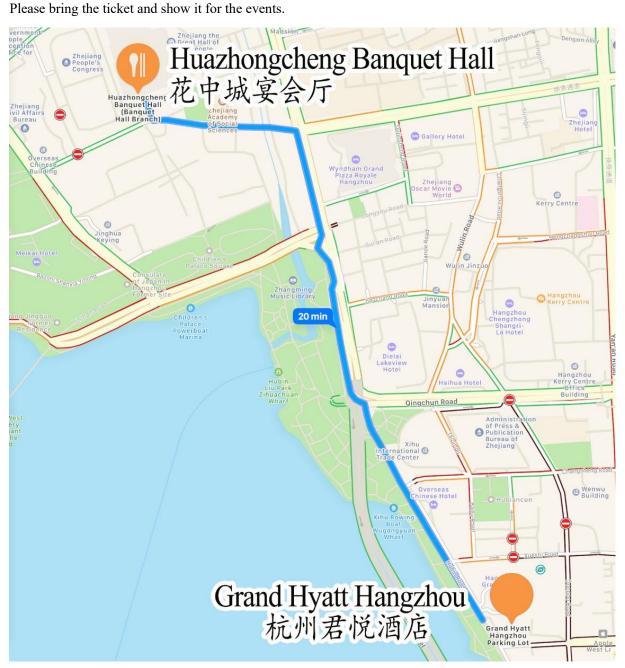

## Banquet

The banquet will be held at **Huazhongcheng Banquet Hall**, No.630 Fengqi road, Hangzhou (Southern door of The Zhejiang People's Greathall) and starts from 6:00 PM, July 4<sup>th</sup>. Please gather at the hotel lobby at 5:40, and we will take you from the Grand Hyatt Hangzhou to the Huazhongcheng Banquet Hall.

The banquet is opened to all of the IPFA2019 attendees. Please get the tickets for banquet upon registration. Please bring the ticket and show it for the events.

## Map of the Conference Zone

Please check the Room information by the different color.

## **Sponsor**

## PLATINUM SPONSOR

Thermo Fisher Scientific Booth No: B19, B24

1 Jalan Kilang Timor, #04-02 Pacific Tech Centre, Singapore 159303 Tel: +65 6272 0050 Fax: +65 6272 0034 Website: www.thermofisher.com/EM-sales Contact: Paige Tan, Event Manager Email: paige.tan@thermofisher.com

Thermo Fisher Scientific supplies innovative solutions for electron microscopy and microanalysis. We provide SEMs, TEMs and DualBeam<sup>™</sup> FIB/SEMs combined with electrical test solutions and advanced software suites to take customers from electrical localization to physical root cause. Our industry-leading workflows deliver fast, accurate answers for accelerating IC design and production decisions. Our fault isolation and analysis products provide superior images, rich feature sets, cross-sectional metrology and automation to speed process defect identification, enable root-cause analysis, reduce yield loss and accelerate time-to market for new products. Our experts engage with applications, engineering, and manufacturing teams to address today's challenges, while our leadership and significant R&D commitment are paving the way to sub-7–nanometer technologies and beyond.

## **Sponsor**

## **GOLD SPONSOR**

## Integrated Service Technology Booth No: B33

2,Bldg., No.455 Jinfeng Road, Pudong New Area, Shanghai, China 201201 Tel: 800-988-0501 Website: www.istgroup.com E-mail: marketing\_cn@istgroup.com

Founded in 2002 in China, iST began its business from IC circuit debugging and modification and gradually expanded its scope of operations. In 2016, iST established a fully integrated circuit supply chain verification and analysis engineering service platform in Shanghai to provide comprehensive services for failure analysis, reliability verification, wafer microstructure material analysis, board level reliability test and wafer grinding so on.

iST's customers cover the whole spectrum of the electronics industry from IC design, wafer manufacturing, IC packaging and testing to end products. In response to rising Cloud Intelligence (AI), Internet of Things (IoT) and Internet of Vehicles (IoV), iST not only focuses on core services but also establishes a unique and integrated automotive chip (Single Chip/Multi Chip/System-in-Package ), Board Level Reliability Test and Failure Analysis verification platform in mainland China to face the diversified national and international growing trend.

## ZEISS Booth No: B14

No. 60, Meiyue Road, Pudong new district, Shanghai, China Tel: +86-21-2082-5507 Fax: +86-21-5048-1193 Website: www.ZEISS.com/PCS Contact: Sales Support Specialist Email: spring.wang@zeiss.com

ZEISS has the most comprehensive portfolio of light, x-ray, electron beam and ion beam imaging technologies in the industry and is a leading solution provider to the global semiconductor community. Solutions span semiconductor manufacturing from wafer fab through packaging and assembly. For mask making and lithography, ZEISS provides unique solutions in the areas of zero defect, in-die metrology, critical dimension/registration and overlay control. ZEISS innovative process control and failure analysis solutions deliver actionable information to both wafer fab and packaging/assembly processes to meet the semiconductor industry's challenges for next-generation devices.

ZEISS is represented in over 40 countries around the globe with more than 40 manufacturing sites, around 50 sales and service locations, and over 20 research and development centers. Founded in 1846 in Jena, the company now has its headquarters in Oberkochen in southwest Germany. Carl Zeiss AG is wholly owned by the Carl Zeiss Stiftung (Carl Zeiss Foundation).

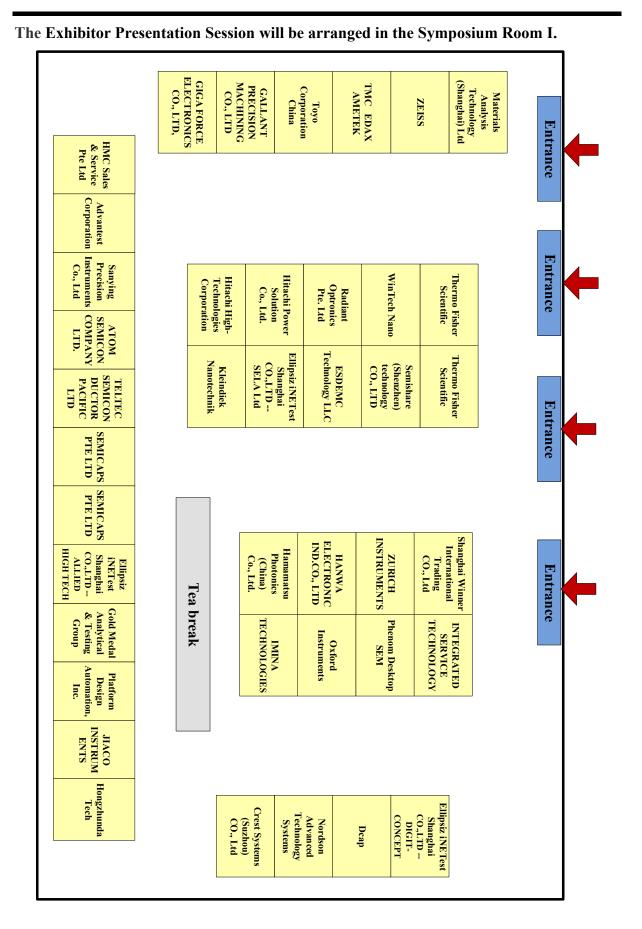

## Map of the Exhibition Zone — Exhibition Hall

## List of Exhibitors & Booth

| B01        | HMC Sales & Service Pte Ltd                                     |

|------------|-----------------------------------------------------------------|

| B02        | Advantest Corporation                                           |

| B02<br>B03 | Sanying Precision Instruments Co.,Ltd                           |

| B03<br>B04 | ATOM SEMICON COMPANY LTD.                                       |

| B05        | TELTEC SEMICONDUCTOR PACIFIC LTD                                |

| B05-B07    | SEMICAPS PTE LTD                                                |

| B08-B07    | Ellipsiz iNETest Shanghai CO.,LTD ALLIED HIGH TECH              |

| B08<br>B09 | Gold Medal Analytical & Testing Group                           |

| B10        | Platform Design Automation, Inc.                                |

| B10<br>B11 | JIACO INSTRUMENTS                                               |

| B11<br>B12 |                                                                 |

| B12<br>B13 | Hongzhunda Tech<br>Matariala Analysia Tachnalagy (Shanghai) Ltd |

| B13<br>B14 | Materials Analysis Technology (Shanghai) Ltd<br>ZEISS           |

|            |                                                                 |

| B15        | AMETEK TMC                                                      |

| B16        | Toyo Corporation China                                          |

| B17        | GALLANT PRECISION MACHINING CO.,LTD                             |

| B18        | GIGA FORCE ELECTRONICS CO.,LTD,                                 |

| B19,B24    | Thermo Fisher Scientific                                        |

| B20        | WinTech Nano                                                    |

| B21        | Radiant Optronics Pte. Ltd                                      |

| B22        | Hitachi Power Solutions Co., Ltd                                |

| B23        | Hitachi High-Technologies Corporation                           |

| B25        | Semishare (shenzhen) technology CO., LTD                        |

| B26        | ESDEMC Technology LLC                                           |

| B27        | Ellipsiz iNETest Shanghai CO.,LTD SELA Ltd                      |

| B28        | Kleindiek Nanotechnik                                           |

| B29        | Shanghai Winner International Trading CO., Ltd                  |

| B30        | ZURICH INSTRUMENTS                                              |

| B31        | HANWA ELECTRONIC IND.CO., LTD                                   |

| B32        | Hamamatsu Photonics (China) Co.,Ltd.                            |

| B33        | INTEGRATED SERVICE TECHNOLOGY                                   |

| B34        | Phenom Desktop SEM                                              |

| B35        | Oxford Instruments                                              |

| B36        | IMINA TECHNOLOGIES                                              |

| B37        | Ellipsiz iNETest Shanghai CO.,LTD DIGIT- CONCEPT                |

| B38        | DCap                                                            |

| D20        | Nordson Advanced Technology Systems                             |

| B39        | Nordson Advanced Technology Systems                             |

#### HMC Sales & Service China office

Room 23005, Blk 8, Manhattan Square No.3, Weihua Road, Suzhou Industrial Park, Suzhou, Jiangsu, China 215021

Tel/Fax: (86) 512-6500-1006 Email: alanhu@hmcasia.com

HMC Sales & Service was established in 1990 and incorporated into a Private Limited company in January 1997 with the aim of providing reliable products and quality services of the highest standard to the regional semiconductor and electronics industry. In June 1997, HMC Sales & Service Philippines was established follow by HMC Sales & Service Suzhou in October 2004.

Both Philippines and Suzhou offices was to provide a closer link with customers in that region and to meet the growing demand and expectation of the semiconductor and electronics market. HMC provide HITACHI Environmental Testing Chambers TC, TS, THB and HIRAYAMA HAST Chamber, Pressure Cooker, Pressurized LCD Liquid Processing Autoclaves. Pressurized Steam Tester, HAST board design/fabrication.

## **Advantest Corporation**

A world-class technology company, Advantest is the leading producer of automatic test equipment (ATE) for the semiconductor industry and a premier manufacturer of measuring instruments used in the design and production of electronic instruments and systems. Its leading-edge systems and products are integrated into the most advanced semiconductor production lines in the world. The company also focuses on R&D for emerging markets that benefit from advancements in nanotech and terahertz technologies, and has introduced multi-vision metrology scanning electron microscopes essential to photomask manufacturing, as well as groundbreaking 3D imaging and analysis tools. With the industry's No. 1 test technology capabilities and an internationally-renowned global support system, we pledge to redouble our efforts to grow with our customers around the world, enhance our corporate value, and contribute to a sustainable future for all.

## **Sanying Precision Instruments Co., Ltd**

Building 7, Didadonggu International, 22 Erwei Road, Dongli Economic Development Zone, Tianjin, P.R. China Tel:0086-15802222209 Contact person: Jian. Wu Email: jwu 1@sypi.com.cn

Sanying Precision Instruments Co., Ltd. (stock code: 839222) is the first professional manufacturer and supplier of high-resolution intelligent X-ray 3D fluoroscopic imaging testing equipments that has its own intellectual property in China. The Company is mainly engaged in developing and manufacturing of highresolution X-ray 3D fluoroscopic imaging testing equipment, including X-ray 3D microscope, high-precision X-ray industrial CT scanner, X-ray online testing equipment, lithium battery 3D CT scanner, full core CT scanner, plate CT scanner, 3D digital mobile testing center, and so on. In addition, the Company also provides

**Booth No: B02**

#### Booth No: B01

nondestructive imaging testing services.

As a national high-tech enterprise, Sanying has passed ISO9001:2008 quality management system certification, has a postdoctoral working station, and has strict quality control and strong R&D capability. With the concept of "technique innovation, precision manufacture and quality first", the Company is dedicated to build a high-tech industrial platform centered by micro-nano nondestructive testing technology and provide professional solutions for national defense industry, new energy, new material, petroleum geology, aerospace, health and medicine, life science and agricultural technology and so on. Sanying expects to go forward hand in hand with you.

#### ATOM SEMICON COMPANY LTD.

#### Booth No: B04

**Booth No: B05**

B35 1A2, No.1, Lising 1st Rd., East Dist., Hsinchu City 300, Taiwan (R.O.C.)

Tel: +886 3 5788474

Fax: +886 3 5788879

Website: www.atom-semi.com

E-mail: bob.lin@atom-semi.com

Contact person at the exhibition: GM Bob.Lin

ATOM provides professional services for agent products.

ATOM SEMICON was founded by GM Bob.Lin in August 2013. It is the agent for the distribution of Taiwan business of equipment Vendor, and Mr. Wang Wende is the chairman of the company. Focusing on the development of novel application fields, and cooperating with Taiwan's excellent university (NCTU, NCKU...), it has become an equipment vendor novel application field development and professional technology solution provider.

ATOM led equipment vendor products into Taiwan's semiconductor field successfully, equipment vendor product portfolio ranges from fully automated, SEMI compliant batch and cluster systems for high volume manufacturing to smaller scale R&D and pre-pilot production tools. Production-proven solutions for IC, MEMS, LED, Sensor, Biomedical materials and 3D component processing are mastered with world-class process quality, the leading equipment design, the most comprehensive process support, and the best customer care.

In the future, ATOM will continue to agent other leading application technology related products, and keep the professional technical services and industry-university cooperation to provide the best professional development experience and solutions for all future customers.

#### **Teltec Semiconductor Pacific Limited**

#### Tel: +852 2521 4213

Website: www.teltec.asia

Teltec Semiconductor Pacific Ltd is a leading Sales & Service Organization serving the Semiconductor Industry (Front & Backend) & Emerging Hi-technology Industry (MEMS, Nanotechnology, Optoelectronics & PV Solar) for over 34 years.

## \_\_\_\_\_

**Exhibitors' Information**

Applications of our represented products:

1) Substrate Cleaning: Plasma Cleaning Systems, UVO Cleaners

2) Failure Analysis: SAM, X-ray Inspection Machines, Bond Testers, Decapsulation Systems, IV Curve Tracers, EMMI, IREM

3) Reliability: Burn-in Ovens, Centrifuges, Reflow Ovens, Advanced Reliability Testers

4) IC Testing: IC Testers & Handlers, Harddockings, Interfaces, Manipulators, Automated Wafer Probe Stations

5) Photolithography: Mask Aligners, Photoresists, Maskless Exposure Systems, Spin Coaters & Hotplates

6) Metrology: AFM, Thin Film/Wafer Stress and Thickness Measurement Systems, Optical Profilers, Nanoindentors, Thermal Warpage and Strain Measurement Systems, AOI Machines

7) Deposition & Etching: Plasma Deposition & Etching Systems, ALD Systems, Sputtering & Evaporation Systems

8) Others: Solar Simulators, Nanoimprint Stamps, In-situ Aligned Wafer Bonders, Solderability Testers

#### **SEMICAPS Pte Ltd.**

SEMICAPS is a developer and manufacturer of world-leading fault localization and defect characterization equipment for the semiconductor industry. We provide solutions and services for design debug, product engineering, yield enhancement and customer returns. With the semiconductor technology node progressing towards 22nm and 14nm, more demand is anticipated for our leading edge machine to help customers analyze their advance node products.

Our products include:

a. Laser Timing Probe (LTP) - An instrument which allows the waveform at a particular node inside a semiconductor device or IC to be measured using a laser as a probe;

b. Scanning Optical Microscope (SOM) System - A multi-laser scanning optical microscope system for the active localization of integrated circuit defects using static power alteration and dynamic tester-based techniques;

c. Photon Emission Microscope (PEM) System - A highly sensitive passive fault localization system for the localization of integrated circuit defects using panchromatic imaging and spectroscopy.

## ELLIPSIZ DSS PTE LTD

Building 2, Room 1406, No. 289, ZheQiao Road, Shanghai, China Website: http://www.ellipsiz.com/

Ellipsiz is pleased to be collaborating with both our principals Allied High Tech Products, Inc, SELA & DIGIT CONCEPT to showcase their products during this IPFA 2019.

Allied High Tech Products, Inc, a US-based manufacturer with a specialized product offering of precision grinding and polishing equipment in support of electrical and physical failure analysis of electronic devices. As the leader in this field, Allied offers a complete solution for sample preparation of electronic components from sectioning, mounting, milling/grinding and polishing to measurement. Allied will

#### Booth No: B08, B27, B37, B38

**Booth No: B06-B07**

its Precision Milling/Polishing System (X-PREP®), Polishing System (MULTIPREPTM) & Substrate Measurement Instrument (X-PREP® VISIONTM).

SELA is a leading innovator in advanced solutions for the sample preparation for physical failure analysis and characterization in the semiconductor industry. Over the past 25 years, SELA has been developing technologies and offering solutions that help our customers create the best of the kind electronic devices that have become an integral part of everyday life for each of us. SELA will have a live demo for its latest Smart IR Micro Cleaving Solution MC20

DIGIT CONCEPT (DC) was founded in 1992 and is one of the leading suppliers of commercial IC Decapsulation, Cross Sectioning, Bonding and PCB Cut.

We design and manufacture state of the art equipment and this year we will show the newest ones

For SELA equipment:

China: Mr. Jacky Zhang - zhang.jacky@ellipsiz-cn.com SEA: Mr. LeeChoon Liang - lee.cl@ellipsiz.com

For ALLIED equipment:

China: Mr. ChaoLiu -liu.chao@ellipsiz-cn.com

SEA: Ms. Susan Lim - lim.susan@ellipsiz.com

For DC equipment:

China: Mr ChaoLiu –liu.chao@ellipsiz-cn.com SEA: Mr LeeChoon Liang - lee.cl@ellipsiz.com

Badge Sponsorship Introduction: DC Booth 37-38

DIGIT CONCEPT (DC) was founded in 1992 and is one of the leading suppliers of commercial IC Decapsulation, Cross Sectioning, Bonding and PCB Cut.

We design and manufacture state of the art equipment and this year we will show the newest ones:

• SesamePLASMA: new iCE\_MIP<sup>™</sup> XL release

We will be happy to present you on our booth the last release of:

- SesameLASER

- SesameACID

- SesameMECHANICAL

UP-GRADE or TRADE-IN your old equipment with iPanel<sup>™</sup> Have a fruitful IPFA 2019 with DC and ELLIPSIZ Teams

| Company Name:   | DIGIT CONCEPT SAS              |

|-----------------|--------------------------------|

| Address:        | SECQUEVILLE EN BESSIN – FRANCE |

| Website:        | www.digit-concept.com          |

| Contact Person: | Michael OBEIN                  |

| Phone:          | +33 231 354 354                |

| Email:          | m.obein@digit-concept.com      |

|                 |                                |

#### **Gold Medal Analytical & Testing Group**

Booth No: B09

No. 2 Xiangshan Avenue Zengcheng District, Guangzhou Tel: +020 32199187 Fax: +020 26225379 Website: www.gmatg.com Contact: Yu hui Luo --Sales Director; Sheng wei Zhou--Sales Director Email: sales@gmatg.com Wechat Public Number: ledqalab

Gold Medal Analytical & Testing Group is a new type of scientific research and testing institution, which is founded by Dr. Fang Fang, an expert of the National "Thousand People Program" and focuses on failure analysis of the third generation semiconductor GaN and SiC chips and devices. Gold Medal Analytical & Testing Group has set up instrument research and development centers in China and Britain. The main equipments independently developed include Microscopic Light Distribution Testing System, Microscopic Thermal Distribution Testing System and Laser Opening System. The product has been widely used by scientific research institutes and listed companies in universities, and widely praised by teachers and researchers. Excellent performance, trustworthy.

#### Platform Design Automation, Inc.

# Platform Design Automation, Inc. (PDA) provides EDA tools and a comprehensive set of services to facilitate designs using highly scaled technologies. Our years of experiences in device modeling, PDK and cell library as well as our unique EDA platform technology enable us to ensure accurate and robust design inputs including device models, PDK and cell libraries. Our EDA tools in device modeling, PDK and device characterization solutions are based on the latest technology and grow rapidly in recent years. PDA HQ is in Beijing, and has branch offices in Shanghai and Taiwan Hsinchu.

#### **JIACO Instruments**

Feldmannweg 17 2628 CT, Delft The Netherlands Tel: (31) 62526 1648 Fax: (31) 15 -278 7369 Website: www.jiaco-instruments.com Contact: Mr. Mark McKinnon – Sales Director Email: mark@jiaco-instruments.com

JIACO Instruments Microwave-Induced-Plasma (MIP) decapsulation system is a breakthrough innovation: Automated atmospheric pressure MIP decapsulation utilizing O2-only recipes. The system has been proven

#### **Booth No: B11**

for Cu, PdCu, Au, Ag bond wires and for advanced package types like 3D, SiP, WLCSP, High Tg, Chip on Board, BOAC; all without process induced damage for reliable failure analysis and quality control.

The JIACO Instruments MIP system has been in the market since mid-2016 and is now in use by many renown global companies for reliable failure analysis and quality control. We look forward to discussing your decapsulation challenges & requirements at IPFA 2019!

## Hongzhunda Tech

## Booth No: B12

CHANG ZHOU: Building 1C,Jintong Industrial Park,No.8 Xihu Road, Wujin National High Tech Industrial Development Zone Tel: 0519-86228809 SHANG HAI: RoomC-D,2nd Floor, Building 3#,133 Curie Road,433Guoshoujing Road, Pudong New Area, Shanghai Tel: 021-50905218 XIA MEN: Room 101'No34 GuanRi, Software Park Phase II, Siming District. Tel: 0592-5936290

Founded in 2014, specializing in the semiconductor industry chain customers to provide inspection and testing services, failure analysis consulting, science and technology consulting and other related technical services, committed to providing customers with efficient, fast and accurate problem solutions.

The company's service strongholds are located in Shanghai, Xiamen, Changzhou, with industry professional and technical personnel team, with strong technical and resource integration ability.

The product service object covers the university, the research institute, the semiconductor industry upstream and downstream.

Under the trend of industry differentiation becoming more and more mature, the company is the first comprehensive platform for virtual IDM, to integrate industrial resources and provide value services.

Quality policy: to provide customers with satisfactory service.

Management policy: imaginative, creative, executive, binding.

## MA-tek

## Booth No: B13

MA-tek is an independent lab with ISO-9001 and IECQ 17025 international accreditations, and filed for an IPO in August 2009. Shortly, in 2016, it is also certified by ISO-27001 on information security.

Materials Analysis (MA-eek) is world-class laboratory providing service in material analysis (MA). In line with the growth of the business's development, Ma-tek has successfully expanded to be equipped with additional Failure Analysis (FA), Reliability testing (RT), and Surface Analysis (SA) and Chemical Analysis (CA) services.

These integrations allow MA-Tek to provide superior service for its clients in various industries.

#### ZEISS

**Booth No: B14**

No. 60, Meiyue Road, Pudong new district, Shanghai, China Tel: +86-21-2082-5507 Fax: +86-21-5048-1193 Website: www.ZEISS.com/PCS Contact: Sales Support Specialist Email: spring.wang@zeiss.com

ZEISS has the most comprehensive portfolio of light, x-ray, electron beam and ion beam imaging technologies in the industry and is a leading solution provider to the global semiconductor community. Solutions span semiconductor manufacturing from wafer fab through packaging and assembly. For mask making and lithography, ZEISS provides unique solutions in the areas of zero defect, in-die metrology, critical dimension/registration and overlay control. ZEISS innovative process control and failure analysis solutions deliver actionable information to both wafer fab and packaging/assembly processes to meet the semiconductor industry's challenges for next-generation devices.

ZEISS is represented in over 40 countries around the globe with more than 40 manufacturing sites, around 50 sales and service locations, and over 20 research and development centers. Founded in 1846 in Jena, the company now has its headquarters in Oberkochen in southwest Germany. Carl Zeiss AG is wholly owned by the Carl Zeiss Stiftung (Carl Zeiss Foundation).

## AMETEK TMC and EDAX

#### **Booth No: B15**

Part A1, A4, 2nd Floor Building No.1, No.526 Fute 3rd Road East, Pilot Free Trade Zone (Shanghai), China. Tel: +86 21 58685111 Fax: +86 21 58660969 Website: www.techmfg.com www.edax.com.cn

TMC designs and manufactures advanced building floor vibration isolation systems for nanotechnology. TMC isolators support ultra precision measurements, instruments, and manufacturing. TMC products enable ultra-precision research, measurements, and manufacturing in the fields of photonics, semiconductor manufacturing, life sciences, drug discovery, and nanotechnology.

EDAX is a leading provider of innovative materials characterization systems, which are essential and commonly used for failure analysis. EDAX products include stand alone tools, integrated tools for EDS-EBSD, EDS-WDS, and EDS-EBSD-WDS, and a free-standing Micro-XRF bench-top elemental analyzer providing small and micro-spot X-ray analysis and mapping.

#### GALLANT PRECISION MACHINING CO., LTD.

No.5-1 Innovation 1'st Rd., Science Based Industrial Park, Hsinchu, 30076 Taiwan TEL: +886-3-563-9999 Website: www.gpmcorp.com.tw Email: andrewchen@gpmcorp.com.tw Contact Person: Andrew Chen

The headquarter of GMP group is located at Hsinchu Science Park, with additional research facilities and manufacturing centers located in Central Taiwan Science Park. Taichung Industrial Park, and Suzhou, China.

GPM provides services throughout Taiwan, China, and South-East Asia with a 24 hour full after-sales service and support to assist customers solving any production related issues.

GPM devotes to develop leading technologies for making equipment with new process, especially integrates IBM's Picosecond Imaging Circuit Analysis (PICA) on advanced IC Characterization and Failure Analysis, which has made GPM fully grasp technical advantages and market opportunities.

## **Giga Force Electronics Co., Ltd**

GIGA FORCE ELECTRONICS CO., LTD, was founded in 2008 and had kept moving forward to integration services for semiconductor back-end field. We provide one stop turnkey solution from PCB Design/Fabrication/SMT, Reliability Qualification, Failure-Analysis, Material-Analysis, Assembly& Testing and Equipment& Component sales. GIGA FORCE had achieved the high-tech enterprise and the specialized new-tech enterprises certification, also we had obtained ISO9001 and CNAS certification, Giga Force had established close relationship with many Enterprises, University and Research Institutes. Our service has been widely recognized by many Tier-1 world-wide customers. GIFA FORCE IPOed in Y2016, the stock code is 870641.

## **Exhibitors' Information**

#### TOYO CORPORATION CHINA

ROOM 310, #228 Meiyuan Road, Jing'An District, Shanghai, China. Tel: +86-21-63809633 Website: www.toyochina.com.cn Contact: Jerhyn Chen Email: chencongyu@toyochina.com.cn

Magnetic Fault Isolation for static failure. TOYO introduces a new use of a scanning super conducting quantum interference device SQUID microscope to image magnetic fields generated by currents in an integrated circuit at room temperature. SQUIDs are the most sensitive magnetic sensor known and they can be designed to measure fields as small as 1fT, which is 40 billion times smaller than the Earth's magnetic field. With the strong penetration of magnetic field and the high sensitivity of the detector, SQUID became a new method to be used in various applications.

#### Booth No: B16

**Booth No: B18**

#### **Thermo Fisher Scientific**

1 Jalan Kilang Timor #04-02 Pacific Tech Centre Singapore 159303 Tel: +65 6272 0050 Fax: +65 6272 0034 Website: www.thermofisher.com/EM-sales Contact: Paige Tan, Event Manager Email: paige.tan@thermofisher.com

Thermo Fisher Scientific supplies innovative solutions for electron microscopy and microanalysis. We provide SEMs, TEMs and DualBeam<sup>™</sup> FIB/SEMs combined with electrical test solutions and advanced software suites to take customers from electrical localization to physical root cause. Our industry-leading workflows deliver fast, accurate answers for accelerating IC design and production decisions. Our fault isolation and analysis products provide superior images, rich feature sets, cross-sectional metrology and automation to speed process defect identification, enable root-cause analysis, reduce yield loss and accelerate time-to market for new products. Our experts engage with applications, engineering, and manufacturing teams to address today's challenges, while our leadership and significant R&D commitment are paving the way to sub-7–nanometer technologies and beyond.

#### WinTech Nano

WinTech Nano is a leading 24 hour running service laboratory providing one-stop analytical services. Our professional services cover Structure Analysis, Material Characterization and Electrical Failure Analysis. WinTech Nano has world-class analytical instruments including: 3D X-Ray, OBIRCH, EMMI, FIB, TEM, TOF-SIMS, D-SIMS, XPS, etc. Our fast and reliable analysis result gives the best support to R&D and production customers.

#### RADIANT OPTRONICS PTE LTD

621 Aljunied Road #03-03 Lipo Building Singapore 389834 Tel: (65) 6288 5252 Fax: (65) 6858 5822 Website: www.radiantoptronics.com Contact: Mr Christopher Cheong, Director Email: chris@radiantoptronics.com

Radiant Optronics Pte Ltd specializes in sample Preparations equipment for Failure Analysis applications. Our equipment consists of: Radiant Laser Decapsulators, Ultratec Mechanical Decapsulators, Muegge Plasma Decapsulators. Infrared Microscopes. Please visit our website - www.radiantoptronics.com

Booth No: B19, B24

#### Booth No: B20

## Hitachi Power Solutions Co., Ltd

Hitachi Power Solutions develops and provides our original Scanning Acoustic Tomographs and their transducers used for non-destructive testing of semiconductor and electronic devices. We have very abundant experiences in this field for more than 30 years.

We have very wide products' lineup consisting of FineSAT series, FSLine series, WaferLine and ES-5100. The FineSAT series can be utilized to inspect wide variety of electronic devices and materials not only in laboratories but also in mass-production lines. FSLine series are optimum for large scale mechanical parts and materials such as sputtering targets. The WaferLine is an automated system for bonded Si wafers, MEMS wafers and other applications. ES-5100 can realize extremely high-speed testing on combination with phased array transducers. These tools achieves many kinds of inspection in conjunction with wide variety of optional parts and software.

We can also offer appropriate transducers selected from the wide variety of lineup or customize transducers to customers' samples.

Please feel free to consult us.

## Hitachi High-Technologies Corporation

Room 1405,Beijing Fortune Bldg.No.5Dong San Huan Bei-Lu, Chao Yang District, Beijing 100004,P.R.C. Tel:(86)10-6590-8705 Fax:(86)10-6590-8710

Homepage:www.hitachi-hightech.com

Contact: jinrong.liu

Mail: jinrong.liu.ue@hitachi-hightech.com

Hitachi High-Technologies Corporation aims to be a successful enterprise trusted by all our stakeholders and contributing to social progress through business activities that emphasize value creation through high-tech solutions. We are committed to open, transparent, and reliable business practices. As we continue to grow, we will value environmental responsibility and strive to build a prosperous community, contributing as a corporate citizen with passion and pride in our work.

Business Policy:

To place the customer first, growing with our customers by providing the best solutions, consistently a step ahead of market needs.

To contribute to value creation in the global community through synergies between our strengths in cuttingedge technologies and our capabilities as an established trading company.

To aim for reliability and excellence based on our core assets of talent and technical resources, and to maximize our corporate value.

## Semishare (Shenzhen) technology CO., LTD

Semishare Instruments Shenzhen Office Web site: www.semishare.com Leo Mobile: +86-18124555912

## Booth No: B23

Booth No: B22

SEMISHARE committed to the sharing business of advanced semicon technology, focusing on promoting China's fast growth in the semiconductor industry. Our target is be a leading total solution partner to our clients. Currently, we have our semiconductor equipment agent business group and semicon equipment manufacturing plant which makes probe station and laser repairing machine in Shenzhen, China.

SEMISHARE equipment agent business group provide the world famous semiconductor testing equipment and processing equipment. Testing equipment including probe station, laser repair system, IV / CV tracer and source meter

SEMISHARE's products and solutions have been successfully used in most IC/LED/LCD foundries and R&D centers in China.

## ESDEMC Technology LLC

## Booth No: B26

4000 Enterprise Drive, Suite 103, Rolla, MO, 65409, USA Contact: Rachel Phone: +1 573-202-6411 Fax: +1 877-641-9358 Website: www.esdemc.com E-mail: info@esdemc.com; rachel@esdemc.com

ESDEMC Technology develops, manufactures, and markets ESD and EMC related products. We are devoted to delivering creative, flexible, and cost effective ESD and EMC solutions and top-level consulting services. We also offer customized design services to satisfy all of our customers' needs.

We provide:

- Pulsed IV-Curve Solutions;

- Probe Station Solutions System Level ESD Solutions

- cable discharge solutions;

- EMC&RF solutions and Hight voltage measurement

- High voltage supply system

ESDEMC Technology LLC offers top specification Transmission Line Pulse (TLP) Solutions. Our design team has over 20-years' experience with tough high voltage and high frequency designs. ESDEMC has been providing great System Level ESD Consulting for the industry. We offer ESD failure analysis, test solutions and ESD design consulting. We have been the OEM for other ESD/EMC companies.

## **KLEINDIEK NANOTECHNIK**

Aspenhaustr. 25 72770 Reutlingen Germany Tel: +49 7121 345 395 0 Fax: +49 7121 345 395 55

Website: www.kleindiek.com Contact: info@kleindiek.com

Kleindiek Nanotechnik is a customer oriented, innovative high-tech company specialized on manufacturing micro- and nano-positioning systems for a wide range of applications - including electrical fault isolation at the nano-scale.

Our customer-driven approach is focused on providing complete and innovative solutions for each of our market segments: researchers, industrial customers and enterprises.

Our product development philosophy is the direct solution of the specific underlying problem. The simplicity, homogeneity and harmony of our designs guarantee maximum manoeuvrability and highest resolution while maintaining the smallest outer dimensions.

## Shanghai Winner International Trading CO., LTD

Booth No: B29

RM708, Building 2, NO. 268, Taihong Road, Hongqiao CBD, Shanghai, China Tel: 021-31037266 Fax: 021-64200918 Website: www.ghitcsh.com Contact: Mr. Heng Email: michael@ghitcsh.com

As a professional supplier of nanotechnology solutions, Shanghai Winner International Trading Co., Ltd. is committed to the sales and production of semiconductor equipment, laboratory physical and chemical analysis equipment, electron microscopy and supporting equipment. At present, it is the agent of Lattice Gear Precision Fixed-point Slicing System, IBSS plasma cleaning system, Tousimis critical point dryer, Swiss IMINA nanomanipulator in China. The sales and after-sales service of the district, as well as the solution of localized in-situ electron microscopy and sample preparation equipment, meet the application needs of scientific research and industrial users.

## **Zurich Instruments**

Room 2015-2016, Block A, Gateway International Plaza, No.325 Tianyaoqiao Road., Xuhui District, Shanghai 200030, China. Tel: +86 21-64870285/87 Website: www.zhinst.cn E-mail: info.cn@zhinst.com Contact person at the exhibition: Dr. Luo Lu, luo.lu@zhinst.com Social media channels: https://twitter.com/Zhinst https://twitter.com/Zhinst

#### https://www.youtube.com/zhinst

Zurich Instruments is a technology leader developing and selling advanced test & measurement instruments for dynamic signal analysis. These devices are used in many fields of application by high-technology research laboratories and industrial development sites.

Zurich Instruments' vision is to revolutionize instrumentation in the high-frequency (HF) and ultra-high-frequency (UHF) range by incorporating the latest analog and digital technology into powerful measurement systems for unprecedented functionality. Best-in-class performance, differentiating features, new measurement solutions, and premium customer support complete the unique offering.

The product philosophy is derived from observing the complexity of many laboratory setups: devices are stacked upon each other and numerous interconnects introduce an unnecessary potential for errors. We help users to reduce the complexity of their setups by combining the required functions into fewer boxes. Further we use our application know-how to help customers to choose the right instrument, to quickly get started and obtain first results.

#### HANWA ELECTRONIC IND. CO., LTD.

#### Booth No: B31

Booth No: B32

689-3 OGAITO, WAKAYAMA, JAPAN, 649-6272 TEL: +81-73-477-4435 FAX: +81-73-477-3445 Website: http://www.hanwa-ei.co.jp/ Contact: Mr. Keiichi Hasegawa Email: info@hanwa-ei.co.jp

We are the worldwide ESD/CDM/TLP tester maker in providing customers with good quality and service of ESD testers over 30 years throughout the world. We have acquired the largest market share of ESD industry in Japan and have developed various new ESD testers over many years. Also, we are one of committee member of EOS/ESD Association, Inc.

Here is our products: - High pin count automatic ESD tester, HED-G5000 / HED-N5000 - Full Automatic ESD tester, HED-S5000R - CDM Tester, HED-C5000R - Wafer Level HBM tester, HED-W5300D – TLP Tester, HED-T5000 HED-G5000 is an automatic ESD tester with ultra low parasitic capacitance and allows you to have ESD test with Max.2048 pins. Perfectly it corresponds with the worldwide standards: ESDA, JEDEC, AEC and JEITA.

If you are interested in these products and other ESD Testers, please contact us anytime. E-mail: info@hanwa-ei.co.jp TEL: +81-73-477-4435 FAX: +81-73-477-3445

#### Hamamatsu Photonics

Hamamatsu has been working with the Photon for more than 60 years since 1953. Our products applied widely in medical biology, HEP, universal detection technology, rigorous analysis etc. We have established ourselves as the top company of photoelectron conversion technologies in the world. Members of Hamamatsu

28

## **Exhibitors' Information**

consider ourselves a research and development company, and we believe that the only way to achieve sustainable growth is to maintain our technological advantages. It is our job and passion to advance photonic technologies. In order to make more contribution to Chinese photonics industries, Hamamatsu Photonics (China) Co., Ltd. was established in Oct 2011 and to be responsible for sales, marketing, technology support and after-sales service in China.

What's more, we realize that pursuing the knowledge of photonics technologies alone, by ourselves, is like reaching for the stars with a ladder. Thus we will work together with colleagues around the world, who share our passion and the belief that understanding photonic technologies will lead to broader applications and also generate new industries for the advancement of humankind.

## **Integrated Service Technology**

2,Bldg., No.455 Jinfeng Road, Pudong New Area,

Shanghai, China 201201 Tel:800-988-0501 Website:www.istgroup.com E-mail: marketing\_cn@istgroup.com

Founded in 2002 in China, iST began its business from IC circuit debugging and modification and gradually expanded its scope of operations. In 2016, iST established a fully integrated circuit supply chain verification and analysis engineering service platform in Shanghai to provide comprehensive services for failure analysis, reliability verification, wafer microstructure material analysis, board level reliability test and wafer grinding so on.

iST's customers cover the whole spectrum of the electronics industry from IC design, wafer manufacturing, IC packaging and testing to end products. In response to rising Cloud Intelligence (AI), Internet of Things (IoT) and Internet of Vehicles (IoV), iST not only focuses on core services but also establishes an unique and integrated automotive chip (Single Chip/Multi Chip/System-in-Package), Board Level Reliability Test and Failure Analysis verification platform in mainland China to face the diversified national and international growing trend.

## Phenom Desktop SEM

Room 501-503, Tower E, German Centre, No.88 Keyuan Road, Pudong, Shanghai Tel: 400 857 8882 Fax: 021-28986858 Web: www.phenom-china.com Email: info@phenom-china.com Contact person: Di Zha, Marketing Manager

Phenom-World is a global leading supplier of Desktop Scanning Electronic Microscopes, and the company focuses on imaging solutions for submicron scale and nanoscale applications. Our SEM-based systems are

## Booth No: B34

used in a wide range of markets and applications, such as material science, electronics, nano-particle, biomedical sciences, textile fiber and geological sciences, etc.

Phenom Scientific Instrument (Shanghai) Co., Ltd., the Chinese exclusive agency of Phenom-World is responsible for marketing and sales of Phenom Desktop SEM in China to provide the professional technical support and testing services.

Phenom Scientific Instrument (Shanghai) Co., Ltd. has a high-qualified application supporting team, it has built test center and service center in Shanghai, Beijing, Guangzhou and Chengdu. Nowadays the users of Phenom Desktop SEM in China are more than 1000.

## **Oxford Instruments**

## Booth No: B35

Shanghai, China Tel: 400-678-0609 Website: www.oxinst.cn Contact: Shirley GAO/ Marketing Specialist Email: Info.china@oxinst.com

Oxford Instruments plc is a leading provider of high technology products, systems and tools to the world's leading industrial companies and scientific research communities.

We use innovation to turn smart science into world-class products that support research and industry to address the great challenges of the 21st Century.

We are proud to be recognised as the leaders in what we do and for the difference we make in the world.

## **Imina Technologies SA**

## Booth No: B36

**Booth No: B39**

Tel: +31 630666760 Website: https://imina.ch/ Contact: Mr. Rob Claassen Email: claassen@imina.ch

Imina Technologies' Nanoprobing Turnkey Solutions have up to 8 nanoprobers based on a unique accurate and stable motion technology to position probe tips with precision and establish steady contacts with the device under test. Various configurations and solutions are offered to adapt with your specific SEM-FIB or Optical Microscope equipment and FA test routines. The Nanoprobing module of Precisio<sup>™</sup> software suite provides a step by step assistance to guide the operator from setting up measurement campaigns, to landing probes and acquire data, ensuring a smooth and intuitive workflow." to get to quantitative data easy and fast.

## Suzhou Nordson Electronics Equipment Co., Ltd

Building 7, No.666, Jianlin Rd, Suzhou, China 215129 Cell: +86 13701819063 Fax: +86 512 6665 3218

Website: www.nordson.com Contact: Mr. Cotton Yang (Sales Manager) Email: Cotton.Yang@nordson.com

Nordson Advanced Technology Electronics Systems is the industry leader in several fields of Semiconductor and Electronics assembly. Through our group of leading edge technology companies ASYMTEK Precision Dispensing, DAGE Bond Test and Materials Testing, DAGE MXI Stand Alone X-Ray, DIMA Hot Bar Soldering, MARCH Plasma Cleaning, MATRIX AXI In-line X-Ray, SELECT Selective Soldering, SONOSCAN Acoustic Micro Imaging and YESTECH AOI Inspection, we deliver standard and customized solutions to customers worldwide for the most challenging Manufacturing and Test & Inspection Issues. Nordson is involved in all of the leading edge manufacturing challenges in today's complicated electronics and semiconductor supply chain. From component manufacturing to MEMS and module assembly, through board assembly, test, inspection, failure analysis and final assembly, Nordson works with our customers to optimize the process through process and application expertise. Delivering complete solutions to the issues and problems of our customers through hardware, software and first class customer support. For more information, please visit www.nordson.com.

#### Crest Systems (Suzhou) Co., Ltd

**Booth No: B40**

03-04, 3F, B Building, Ascendas-Xinsu Industrial Square, No.5 Xinghan Street, Suzhou, Jiangsu, China Tel: (86)512-6741 2701 Fax: (86)512-6741 0973 Website: www.crest-systems.com Contact: Mr.Brad-Business Manager Email: Brad.liu@crest-group.net

Crest Systems (Suzhou) Co.,Ltd, Crest is committed to the world famous brand of high-tech testing equipment and related products to the majority of customers in China and South of Asia.

We are located in China, Malaysia, Thailand, Singapore and other regions, for customer to provide first-class detection equipment and solutions, industries covering semiconductors, aerospace, universities, automotive electronics, research institutions and other fields.

Our equipment includes: Imina-Nanoprobe, Nordson Dage Bond-tester, Nordson Dage X-ray Inspection System, Nordson MatriX, Nordson MARCH, Nordson Yestech, Nordson Sonoscan C-SAM Tester, Olympus microscope, NSC-decap system, etc.

We uphold the principle of first-class products, service first. Believe us, choose us, will bring you more surprises!

## **Keynote speakers**

Prasad Chaparala Amazon Lab126, USA

Prasad Chaparala is the Director of Reliability Engineering at Amazon Lab126 in Sunnyvale, California. He is responsible for reliability engineering of a broad range of consumer electronic devices such as Echo smart speakers, Kindle ereaders, Fire tablets, and Fire TV products. Prior to this, he was the Vice President of Product and Reliability Engineering at Alta Devices from 2010 to 2014. Before

joining Alta Devices, he was with National Semiconductor for 14 years in various process and reliability engineering roles. He received a Ph.D in Reliability Engineering from the University of Maryland, College Park. He has contributed to more than 50 publications in international journals and conference proceedings and holds 18 US patents. He is a recipient of three Best Paper awards at IEEE International Reliability Physics Symposium (IRPS). Additionally, he was served as the General Chair for the 2014 IRPS and was a member of the Board of Directors for IRPS.

#### **Building Reliable Products Guided by Customer Obsession**

With the rapid proliferation of consumer IoT devices that are embedded into everyday life, building both affordable and reliable hardware that continues to meet the highest customer expectations is of paramount importance. This is particularly challenging for new applications where customer-use conditions can vary broadly and can be unpredictable. Unlike other established industries such as semiconductor, automotive or aerospace where widely accepted reliability standards exists, there are no industry reliability standards for consumer electronics devices. In-depth understanding of customer usage environments, patterns, and expectations is critical in deriving appropriate system-level reliability specifications and test methods in order to build reliable devices that surpass customer expectations. This talk will provide an overview of how system-level reliability requirements for devices such as the Amazon Echo and Fire TV products are defined by working backwards from customer needs. The talk will cover various advanced engineering approaches in defining reliability specifications and test methods through user surveys, statistical analysis and machine learning techniques and customer feedback.

## **Keynote speakers**

Shimeng Yu Georgia Institute of Technology, USA

Shimeng Yu is an associate professor of electrical and computer engineering at the Georgia Institute of Technology in Atlanta, Georgia. He received the B.S. degree in microelectronics from Peking University, Beijing, China in 2009, and the M.S. degree and Ph.D. degree in electrical engineering from Stanford University, Stanford, California, in 2011 and in 2013, respectively. From 2013 to 2018, he was

an assistant professor of electrical and computer engineering at Arizona State University, Tempe, Arizona.

## Emerging Non-Volatile Memory's Applications in Neuro-Inspired Computing and Hardware Security

Emerging non-volatile memory (eNVMs) technologies have made significant advances in the past decade as storage class memory and embedded memory with extensive industrial research and development. This presentation will survey the recent progresses of using eNVMs for new applications beyond data storage in the era of artificial intelligence (AI) and Internet of Things (IoT), in particular for 1) neuro-inspired computing and 2) hardware security. Firstly, I will introduce the individual components of the deep neural network hardware – the eNVM based synaptic devices and neuronal devices. Secondly, I will discuss the crossbar array architecture that embeds the computation into memory array, namely compute-in-memory approach, and show the array-level and chip-level demonstration results. Then, I will introduce the "NeuroSim" framework, a device-circuit-algorithm co-design simulator that benchmarks the non-ideal effects of eNVMs on the machine learning accelerator performance. Lastly, I will introduce how to leverage the eNVM's variability as physical unclonable function (PUF), a hardware security primitive for device authentication and cryptographic key generation. Through the presentation, the potential reliability issues and failure mechanisms of these new applications will be discussed.

## **Tutorials speakers**

## Dimitris P. Ioannou GlobalFoundries, Hopewell Junction, NY 12533, USA

Dimitris Ioannou is a Senior Member of Technical Staff at GlobalFoundries. He received his B.S degree in Physics from the University of Thessaloniki, Greece, and the M.S. and Ph.D. degrees in Electrical Engineering from George Mason University, Fairfax, VA. In 2006, he joined IBM where he played a critical role in the characterization and modeling of reliability mechanisms in advanced Silicon

On Insulator (SOI) High-k/Metal Gate CMOS technologies including IBM's 3D TSV technology. As of 2015 he is with GlobalFoundries where he leads the RF reliability of advanced SOI CMOS and SiGe BiCMOS devices. He has published over 40 papers in the field of CMOS reliability.

## Reliability of 3D Through-Silicon-Via (TSV) Technologies

3D integration has emerged as viable solution for meeting the growing demands and requirements of advanced CMOS systems such as higher performance, increased functionality, lower power consumption, all, at a smaller footprint. This tutorial will provide an overview of the key features of 3D TSV technologies and the challenges associated with them. It will discuss the impact of 3D TSV integration on FEOL, BEOL and package reliability highlighting the unique aspects of the TSV structure such as differential thermal expansion mismatch and the high aspect ratio structure. It will also discuss potential processing related reliability issues such as contamination effects, wafer thinning, dicing and packaging. Finally, it will provide with an overview of available mitigation strategies for these reliability challenges.

## **Tutorials speakers**

#### David Su

Taiwan Semiconductor Manufacturing Company, Inc., Taiwan (Retired)

David Su was Director of the Failure Analysis Division of TSMC in charge of reliability-related failure analysis, materials and surface analysis including TEM, and chemical analysis from 2000 until 2018. Prior to joining TSMC, he was Director of TEM and FIB Technology Development at Accurel Systems in Sunnyvale, California (1998-2000). From 1991 to 1998 he was TEM Specialist at the Materials

Analysis Group of Philips Semiconductors in Sunnyvale, California. He was an adjunct professor at the Department of Materials Engineering at San Jose State University in San Jose, California from 1989 to 1991. David Su received his B.S. degree in Chemical Engineering from the University of Sao Paulo, Brazil and his M.S. and Ph. D. degrees in Chemical Engineering from Stanford University. He has been a board member of the Taiwan Microscopy Society since 2004. He was a board member of the Electronic Device and Failure Analysis Society of the U. S. (2014-2016) and Chair of the Sematech Integrated-Circuit Failure Analysis Council (2013). He was chairman of the 2010 IRPS Failure Analysis Technical Program and was International Chair for ISTFA 2010, 2011 and International Co-Chair in 2013.

## Principles and Applications of TEM and FIB in the Semiconductor Industry

The demands of failure and materials analysis for advanced technology nodes of the integrated circuit industry have pushed Transmission Electron Microscopy (TEM) and Focused Ion Beam (FIB) systems to their limits, especially the need to obtain 3D information both visually and compositionally in the nanometer size range. In this tutorial, the principles and applications of these techniques will be discussed. In addition to conventional imaging and elemental analysis, techniques such as strain measurement, tomography will be presented. The important area of sample preparation will be addressed as well as efforts to automate both data acquisition and sample preparation. Finally, advances in FIB circuit editing will also be discussed.

Jianfu Zhang Liverpool John Moores University, UK

Jianfu Zhang received B.Eng. degree in electrical engineering from Xi'an Jiao Tong University in 1982 and Ph.D. degree from University of Liverpool in 1987. He joined Liverpool John Moores University (LJMU) as a Senior Lecturer in 1992, became a Reader in 1996, and a Professor in 2001.

Dr. Zhang has worked on the qualification of devices and processes for over 30 years, specializing in defects, ageing, modeling, and lifetime prediction of CMOS technologies. He is the author or coauthor of over 200 journal/conference papers, including 55 papers in IEEE Transactions and Electron Device Letters, 19 papers at IEDM/Symposium of VLSI Technology, and 35 invited papers/book chapters. He is/was a member of the technical program committee of several international conferences, including IEDM. His research has been supported by IMEC, ARM, Synopsys, Qualcomm, and the Engineering and Physical Sciences Research Council of UK.

#### **BTI: Testing and Predictive Modelling**

Bias temperature instabilities (BTI) of MOSFETs are well known ageing processes and their qualification is essential for CMOS technologies. To modelling BTI and qualify device lifetime, the common practice is to extract BTI model based on accelerated ageing tests. Several models were proposed by early works and their ability to fit the test data is often demonstrated. This tutorial will show that some models cannot accurately predict the BTI under use-conditions, where ageing is slow. The As-grown-Generation (AG) model is introduced and its predictive capability is demonstrated. The key for the success of AG model is an accurate separation of defects into as-grown defects and generated defects. After presenting a defect framework and the evidences for it, this tutorial will describe the detailed techniques for the defect separation and a step-by-step guide for their implementation. It will be shown that different defects have different ageing kinetics and how the correct time exponent can be extracted independent of test conditions. AC modelling and defect discharging also will be addressed. The connection and difference between AG model and the JEDEC procedure will be clarified.

Lihong Cao ASE Group, Austin, TX, USA

Lihong Cao is a Director in ASE Group responsible for new packaging technology development (2.5D/3D, FOWLP, FOCoS, PoP, SIP, SESUB), technology promotion, new product introduction, technical program management, strategic planning, and business engagement. Her focusing spans from design, process qualification, root cause analysis and production enablement in HPC (High Performance Computing), AI/MI (Artificial & Machine Intelligence) and 5G/mmWave.

Prior to joining ASE, as a Sr. Manager in AMD, she led global package analysis operations to support product development, qualification, production and customer issues for 28/16/14/7nm technology. She was also in charge of failure analysis technique development and roadmap for advanced package analysis. She not only has semiconductor industries experience, but also had academic and professional experience in National Research Institute and Universities.