# Digital Mismatch Correction for Bandpass Sampling Four-Channel Time-Interleaved ADCs in Direct-RF Sampling Receivers

Takao Kihara<sup>10</sup>, Member, IEEE, Tomoya Takahashi, and Tsutomu Yoshimura, Member, IEEE

Abstract—Time-interleaving analog-to-digital converters (ADCs) decrease the required sampling rate for one ADC to achieve giga samples per second (GS/s) rates. The gain and timing mismatches among the ADCs generate aliasing signals, degrading the spurious-free dynamic range of the time-interleaved ADC (TI-ADC). The conventional digital correction methods for TI-ADCs have not considered an application to direct-radio-frequency (RF) sampling receivers. We present a digital correction method for bandpass sampling four-channel TI-ADCs in the receivers. The proposed method, based on a correction method for two-channel TI-ADCs, reduces the in-band aliasing signals of the four-channel TI-ADCs by using in-phase/quadrature-phase (I/O) downconversion mixers, cascaded integrator-comb (CIC) filters, and automatic gain control (AGC) in the receiver. This allows the correction circuit including mismatch estimation to have fewer building blocks than the conventional methods: seven adders, seven multipliers, and no finite-impulse-response filters. Simulations and measurements show that the proposed method reduces the aliasing signals of 1.2 GS/s 12-bit four-channel TI-ADCs to less than -80 dBFS.

*Index Terms*—Time-interleaved analog-to-digital converter (ADC), digital correction, mismatch, direct-RF sampling receiver, cascaded integrator-comb (CIC) filter, automatic gain control (AGC).

#### I. INTRODUCTION

**D**IRECT-RADIO-FREQUENCY (RF) sampling receivers [1], [2], as shown in Fig. 1, benefit from technology scaling and design automation, because most of the building blocks consist of digital circuits. We can greatly reduce the design cost and time to market of RF transceivers for emerging or future Internet of Things (IoT) wireless standards by replacing the conventional direct-conversion

Manuscript received July 14, 2018; revised December 7, 2018; accepted February 19, 2019. Date of publication March 28, 2019; date of current version May 15, 2019. This work was supported in part by the Yazaki Memorial Foundation for Science and Technology through MIC/SCOPE under Grant 165107001 and Grant 185107001, and in part by the JSPS KAKENHI under Grant 16K16030. This paper was recommended by Associate Editor A. Apsel. (*Corresponding author: Takao Kihara.*)

T. Kihara and T. Yoshimura are with the Department of Electrical and Electronic Systems Engineering, Osaka Institute of Technology, Osaka 535–8585, Japan (e-mail: takao.kihara@oit.ac.jp; tsutomu. yoshimura@oit.ac.jp).

T. Takahashi was with the Division of Electrical and Electronic Engineering, Graduate School of Engineering, Osaka Institute of Technology, Osaka 535–8585, Japan.

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TCSI.2019.2903650

Analog | Digital

Fig. 1. Block diagram of a direct-RF sampling receiver.

or heterodyne RF receivers with the direct-RF sampling receivers. One of the biggest challenges of this receiver is to realize an analog-to-digital converter (ADC) sampling gigahertz RF signals. Although subsampling ADCs can digitize and downconvert the RF signals to around DC, we need to remove unwanted signals, separated by a few hundred megahertz from the desired signals (a few gigahertz), before the ADCs. This imposes stringent requirements on anti-aliasing filters. Time-interleaved ADCs (TI-ADCs) achieve gigasamples per second (GS/s) rates [1], [2] and relax the filter requirements. The TI-ADC also has bandpass noise shaping around  $k\omega_s/M$  (k = 0, ..., M - 1) if it consists of low-pass delta-sigma ADCs [3], where  $\omega_s = 2\pi f_s$ , and  $f_s$  and M are the sampling frequency of the TI-ADC and the number of the ADC channels, respectively. A high in-band signal-to-noise ratio (SNR) can be achieved by setting  $k\omega_s/M$  to the carrier frequency of the RF signal,  $\omega_c$ . In particular,  $\omega_s/4$  (=  $\omega_c$ ) also simplifies a complex in-phase/quadrature-phase (I/Q) mixer in the receiver [1]. However, the characteristic mismatches among the ADCs in the TI-ADC, i.e., gain and sampling-time mismatches, generate aliasing signals [4], [5], degrading the spurious-free dynamic range (SFDR). This decreases its achievable effective number of bits (ENOB).

Digital correction methods have been proposed to compensate for the mismatches of *M*-channel TI-ADCs. It is difficult to apply these methods for bandpass sampling TI-ADCs in direct-RF sampling receivers in terms of sampling

1549-8328 © 2019 IEEE. Translations and content mining are permitted for academic research only. Personal use is also permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

rates, complexity, and convergence. A method presented by Matsuno et al. [6] reduces the aliasing signals of any M-channel TI-ADCs by using pseudo-aliasing signals generated from the derivation and Hadamard transform of the signals output from the TI-ADCs. Although the correction circuit consists of fewer building blocks than other methods [7], i.e., 7 adders, 12 multipliers, and 1 finite-impulse response (FIR) filter (derivative filter) in a four-channel TI-ADC, it assumes real signals whose spectra are symmetric around DC. On the other hand, the direct-RF sampling receiver finally downconverts and decimates the signals into low-data-rate I/Q complex signals whose spectra are asymmetric around DC. This means that the correction circuit needs to deal with high-data-rate signals before downconversion and decimation. Methods for two- and four-channel TI-ADCs proposed by Singh et al. [5], [8] transform the real signals of the TI-ADCs into I/Q complex signals to correct the mismatches by using the I/Q imbalance compensation method [9]. Although these methods are more appropriate for TI-ADCs in direct-RF sampling receivers, they require FIR filters, Hilbert transform filters (HTFs), to achieve the complex signals. In addition, the signal processing becomes more complex as M increases; the method for M = 2 uses only one FIR, whereas the method for M = 4 requires two extra FIR filters, i.e., low-pass filter (LPF) and high-pass filter (HPF), to extract the mismatch aliasing signals around DC and  $\omega_s/2$  in a four-channel TI-ADC, respectively. The resulting correction circuit for M = 4 without learning algorithms has 3 FIR filters, 27 adders, and 21 multipliers. Finally, no methods discuss the case when TI-ADCs deal with low-power input signals, degrading the convergence time of the correction methods.

In this paper, we present a digital correction method for a bandpass sampling four-channel TI-ADC in a direct-RF sampling receiver, consisting of I/Q downconversion mixers, cascaded integrator-comb (CIC) filters, and automatic gain control (AGC). The main contributions of this work are threefold: 1) we reduce the in-band aliasing signal of the four-channel TI-ADC, i.e., the complex conjugate of the aliasing signal around  $-\omega_s/4$ , by using the two-channel method [5] (implemented by seven adders and seven multipliers), assuming the TI-ADC deals with band-limited ( $< \omega_s/4$ ) input signals at  $\omega_s/4$ ; 2) our correction circuit needs no FIR filters and operates at lower sampling rates, because the I/Q mixer generates the complex signals and the CIC filter decimates them; 3) the AGC adjusts the average amplitudes of the input signals for the correction circuit to improve its convergence time. The proposed method can be applied to bandpass sampling *M*-channel TI-ADCs, but limiting their bandwidths to  $\omega_s/M$ . This has little impact on the overall performances of the bandpass sampling TI-ADCs, because they sample narrowband RF signals with high-frequency clocks. For example, assuming  $f_s = 3.6$  GHz and M = 4, we have a bandwidth of 900 MHz, which covers the signal bandwidths,  $f_{BW}$ , for most wireless applications. This paper analyzes the method from [10] in more detail and describes the AGC and the implementation on a field-programmable-gate-array (FPGA) device.

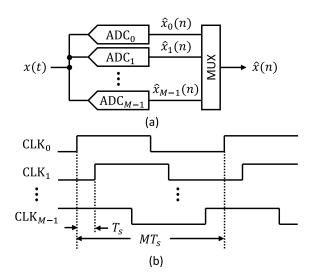

Fig. 2. (a) Block diagram of an *M*-channel TI-ADC and (b) a timing chart of the clocks.

This paper is organized as follows. Section II generalizes the aliasing signals of a bandpass sampling *M*-channel TI-ADC and derives their expressions. Then, we illustrate the aliasing signals that our method reduces for M = 4, implying that our method can be applied to bandpass sampling *M*-channel TI-ADCs. Section III shows the proposed correction method and its building blocks. Section IV shows the implementation on an FPGA and verifies the validity of the method with simulations and measurements of 12-bit four-channel TI-ADCs. Finally, Sec. V concludes the paper.

# II. MISMATCH ALIASING SIGNAL

ADCs in a TI-ADC have different characteristics owing to sampling clock skew and process variation. This causes aliasing signals in the multiplexed output signal of the TI-ADC,  $\hat{x}(n)$ , with a period of  $T_s$  (= 1/ $f_s$ ). Figure 2 shows a block diagram of an *M*-channel TI-ADC and a timing chart of the clocks. The *k*th ADC converts the analog input signal, x(t), into the digital signals,  $\hat{x}_k(n)$ , with a period of  $MT_s$ . Although the difference between the sampling time of the adjacent ADCs is ideally  $T_s$ , it varies with the clock skew. In addition, the ADCs, especially track-and-hold (T&H) circuits, have different gain owing to process variation. In the following, we use the transfer function of the ADC,  $G_k(j\omega)$ , with the gain and sampling-time mismatches,  $\Delta_{gk}$  and  $\Delta_{tk}$ , respectively:

$$G_k(j\omega) = (1 + \Delta_{gk})e^{j\omega\Delta_{tk}}.$$

(1)

#### A. Bandpass Sampling M-Channel TI-ADC

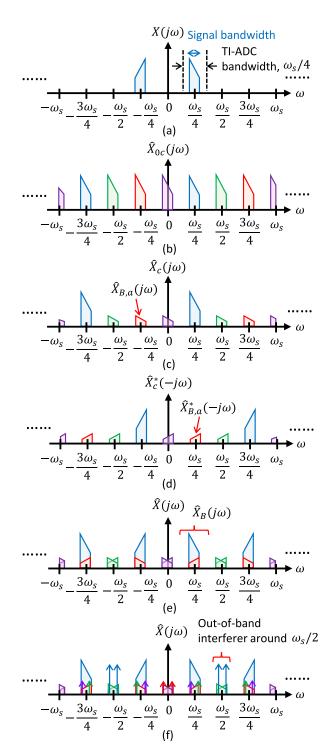

An *M*-channel TI-ADC dealing with band-limited  $(\langle \omega_s/M \rangle)$  input signals at  $\omega_s/4$  suffers from only an aliasing signal at  $-\omega_s/4$ . The spectrum of x(t),  $X(j\omega)$ , is shown in Fig. 3(a), where  $X_p(j\omega)$  is the positive frequency component of  $X(j\omega)$ , i.e., the spectrum of the analytic signal of x(t). The bandwidth of x(t) is assumed to be less than  $\omega_s/M$ . As the sampling frequencies of the ADCs in the *M*-channel

Fig. 3. Spectra of (a) x(t), the complex signals of (b)  $\hat{x}_0(n)$  and (c) x(n), (d) the complex conjugate of (c), (e) the real signal of  $\hat{x}(n)$ , and (f)  $\hat{x}(n)$  with an out-of-band interferer around  $\omega_s/2$ .

TI-ADC are  $\omega_s/M$ , aliasing signals appear at each  $\omega_s/M$ . The spectra of the input analytic signal sampled by the ADCs,  $\hat{X}_{kc}(j\omega)$ , are given by

$$\hat{X}_{kc}(j\omega) = \frac{1}{MT_s} \sum_{l=-\infty}^{\infty} e^{-j\frac{2k\pi}{M}l} G_k(j\omega) X_p\left(j\left(\omega - l\frac{\omega_s}{M}\right)\right).$$

(2)

Figure 3(b) shows  $\hat{X}_{0c}(j\omega)$  for M = 4, where the green, red, and purple spectra represent the aliasing signals for

l = 4m + 1, 4m + 2, 4m + 3 ( $m \in \mathbb{Z}$ ), respectively, against the desired (blue) signal for l = 4m. As these aliasing signals for  $l \neq Mm$  have different phases at the output of each ADC, they disappear in the multiplexed $\hat{x}_k(n)$ ,  $\hat{x}(n)$ . However, the spectrum of the complex signal of  $\hat{x}(n)$ ,  $\hat{X}_c(j\omega)$ , has the aliasing signals owing to the gain and samplingtime mismatches,  $G_0(j\omega) \neq \ldots \neq G_{M-1}(j\omega)$ , as shown in Fig. 3(c), where  $\hat{X}_c(j\omega)$  is expressed as

$$\hat{X}_{c}(j\omega) = \sum_{k=0}^{M-1} \hat{X}_{kc}(j\omega)$$

$$= \frac{1}{MT_{s}} \sum_{l=-\infty}^{\infty} \left\{ G_{0}(j\omega) + e^{-j\frac{2\pi}{M}l} G_{1}(j\omega) + \dots + e^{-j\frac{2\pi(M-1)}{M}l} G_{M-1}(j\omega) \right\} X_{p} \left( j \left( \omega - l\frac{\omega_{s}}{M} \right) \right). \quad (3)$$

Its complex conjugate,  $\hat{X}_c^*(-j\omega)$ , is described in Fig. 3(d). The complex conjugate of an aliasing signal at  $-\omega_s/4$ ,  $\hat{X}_{B,a}^*(-j\omega)$ , appears at  $\omega_s/4$  in  $\hat{X}_c^*(-j\omega)$ . The spectrum of the aliasing signal,  $\hat{X}_{B,a}(j\omega)$ , is  $\omega_s/2$  far from the desired signal and then is given by Eq. (3) for l = -M/2:

$$\hat{X}_{B,a}(j\omega) = \frac{1}{MT_s} \sum_{k=0}^{M-1} (-1)^k G_k(j\omega) X_p\left(j\left(\omega + \frac{\omega_s}{2}\right)\right), \quad (4)$$

where M = 4 for the four-channel TI-ADC. Finally, we have the spectrum of the real signal of  $\hat{x}(n)$ ,

$$\hat{X}(j\omega) = \hat{X}_c(j\omega) + \hat{X}_c^*(-j\omega), \tag{5}$$

as shown in Fig. 3(e). Its in-band spectrum,  $\hat{X}_B(j\omega)$ , has the desired signal and  $\hat{X}^*_{B,a}(-j\omega)$ , expressed as

$$\hat{X}_{B}(j\omega) = \frac{1}{MT_{s}} \sum_{k=0}^{M-1} G_{k}(j\omega) X_{p}(j\omega) + \hat{X}_{B,a}^{*}(-j\omega).$$

(6)

A mismatch correction removes  $\hat{X}^*_{B,a}(-j\omega)$ , which corresponds to the aliasing of a two-channel TI-ADC in the frequency range of 0 to  $\omega_s/2$  as shown in [5]. This means that a correction method for two-channel TI-ADCs can be applied to bandpass sampling *M*-channel TI-ADCs, greatly reducing the complexity of the correction circuit.

A band-pass filter (BPF) before the TI-ADC allows us to adopt this correction concept. RF receivers deal with not only the desired (band-limited) signals but also out-of-band interferers. Aliasing signals owing to the interferers around  $l\omega_s/M$  appear within the signal band of  $\hat{X}(j\omega)$  as shown in Fig. 3(f), where an out-of-band interferer at  $\omega_s/2$  enters into a four-channel TI-ADC. A BPF, generally used as the first stage in the RF receiver (Fig. 1), reduces the interferer to the level such that the aliasing signals do not affect the sensitivity of the receiver.

#### **III. MISMATCH CORRECTION**

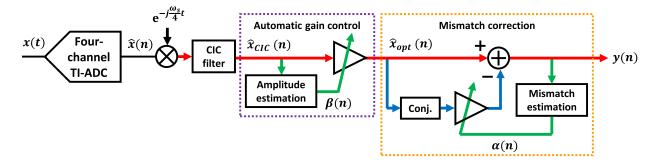

Figure 4 shows the proposed correction architecture for a four-channel TI-ADC, consisting of a complex mixer, CIC filters, AGC, and mismatch correction with mismatch estimation. We assume that a direct-RF sampling receiver digitizes

Fig. 4. Block diagram of the proposed correction architecture for a direct-RF sampling receiver.

Fig. 5. Spectra of (a) the downconverted and (b) CIC-filtered signals.

and decimates input RF signals, x(t), whose carrier frequency and bandwidth are  $\omega_s/4$  and less than  $\omega_s/4$ , respectively. The conventional methods [5], [6], [8], [11] use the signals directly output from the ADCs, whereas the proposed method employs the downconverted and decimated signals. This allows the correction circuit to operate at lower sampling rates and remove the out-of-band aliasing signals degrading the estimation accuracy. The AGC block adjusts the amplitude of the signal output from the CIC filter to an appropriate level.

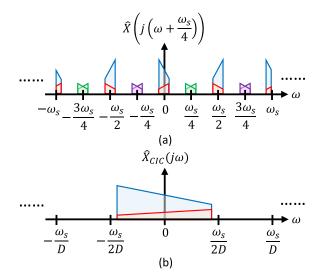

# A. Complex Mixer and CIC Filter

The complex mixers followed by the CIC filters extract in-band signals from the output signals of the TI-ADC. The spectrum of output signals of a four-channel TI-ADC,  $\hat{X}(j\omega)$  shown in Fig. 3(e), has the in-band signals,  $\hat{X}_B(j\omega)$ , expressed by Eq. (6). First, the complex mixer multiplies  $\hat{x}(n)$ with  $\exp(-j(\omega_s/4)t)$  to downconvert  $\hat{X}_B(j\omega)$  to baseband. Figure 5(a) shows the spectrum of the downconverted signal,  $\hat{X}(j(\omega+\omega_s/4))$ , which is  $\hat{X}(j\omega)$  shifted left by  $\omega_s/4$ . The inband signals appear around DC, whereas the mismatch aliasing signals appear around  $\pm \omega_s/4$  and  $\pm 3\omega_s/4$ . Second, the CIC filter decimates the downconverted signals and removes the aliasing signals, folded into the desired band by decimation as shown in Fig. 5(b). The transfer function of a CIC filter,

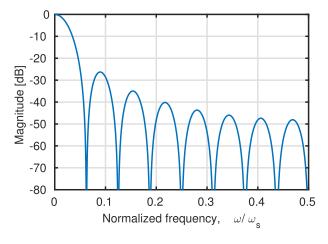

Fig. 6. Calculated frequency response of a CIC filter with D = 16 and L = 2.

$H_{CIC}(z)$ , is generally expressed as

$$H_{CIC}(z) = \left(\frac{1}{D} \cdot \frac{1 - z^{-D}}{1 - z^{-1}}\right)^L,$$

(7)

where *D* is the number of decimation and *L*, determined from the required attenuation [12], is the order of the filter. Figure 6 shows the calculated frequency response of a CIC filter with D = 16 and L = 2, which has a null at every  $\omega_s/D$ . Thus, we remove the aliasing signals around  $\pm l\omega_s/4$  ( $l \neq 0$ ) by setting *D* to four or more. Although the CIC filter reduces the desired signal around DC, this reduction is limited in the case where  $f_s$  is very high compared with the bandwidth of the signal. For example, assuming the above CIC filter with  $f_s = 3.6$  GHz and  $f_{BW} = 30$  MHz, we can calculate the maximum reduction as only 0.12 dB.

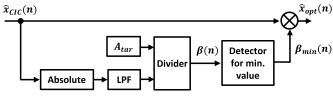

## B. Automatic Gain Control

The AGC adjusts the average amplitude of  $|\hat{x}_{CIC}(n)|$  to a target amplitude,  $A_{tar}$ , improving the convergence time of the mismatch correction, as will be explained in Sec. III-C. The AGC, as shown in Fig. 7, adopts a feed-forward topology with a faster convergence speed than feed-back topologies. The AGC multiplies  $\hat{x}_{CIC}(n)$  by a coefficient,  $\beta(n)$ , to generate  $\hat{x}_{opt}(n)$ :

$$\hat{x}_{opt}(n) = \beta(n)\hat{x}_{CIC}(n).$$

(8)

Fig. 7. Block diagram of the AGC.

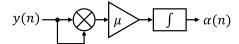

Fig. 8. Block diagram of the mismatch estimation.

We achieve  $\beta(n)$  by dividing  $A_{tar}$  by the expected (absolute) value of the amplitude of  $\hat{x}_{CIC}(n)$ ,  $E[|\hat{x}_{CIC}(n)|]$ :

$$\beta(n) = \frac{A_{tar}}{E[|\hat{x}_{CIC}(n)|]}.$$

(9)

The expected value is calculated with an LPF whose transfer function,

$$H_{LPF}(z) = \frac{b}{1 - az^{-1}},$$

(10)

where a and b are feedback and feedforward coefficients of the filter, respectively.

We adopt the minimum value of  $\beta(n)$ ,  $\beta_{min}(n)$ , for the output of the AGC. The calculation of  $|\hat{x}_{CIC}(n)|$  introduces much harmonic distortion at the output of the AGC,  $\beta(n)$ , because it involves the squared real and imaginary parts of  $\hat{x}_{CIC}(n)$ . The LPF cannot decrease the distortion adequately owing to one tap and, thus,  $\beta(n)$  varies slightly according to the amplitude of  $\hat{x}_{CIC}(n)$ . We eliminate the distortion by keeping  $\beta(n)$  constant,  $\beta_{min}(n)$ .

## C. Mismatch Estimation and Correction

The correction circuit removes the mismatch aliasing signal from the decimated and adjusted signal,  $\hat{x}_{opt}(n)$ , by using the complementary auto-correlation function (CACF) [5] and adaptive signal processing. The aliasing signal is the complex conjugate of the desired signal,  $\hat{x}_{CIC}^*(n)$ , as shown in Fig. 5(b). Thus,  $\hat{x}_{opt}(n)$  can be corrected by subtracting  $\hat{x}_{opt}^*(n)$  multiplied with a coefficient,  $\alpha$ :

$$y(n) = \hat{x}_{opt}(n) - \alpha(n)\hat{x}_{opt}^*(n), \qquad (11)$$

where y(n) is the output signal of the correction circuit as shown in Fig. 4. The conjugate of y(n),  $y^*(n)$ , can be detected by its CACF, defined as

$$C_{y}(\tau) \stackrel{\text{def}}{=} E[y(n)y(n-\tau)], \qquad (12)$$

where  $\tau$  is the time lag. If y(n) has no complex conjugate, the CACF is calculated as

$$C_{y}(\tau) = E[y(n)(y^{*}(n-\tau))^{*}] = 0.$$

(13)

The least mean square (LMS) algorithm reduces  $C_y(\tau)$  close to zero by updating  $\alpha(n)$  according to

$$\alpha(n+1) = \alpha(n) + \mu y^{2}(n),$$

(14)

where  $\mu$  is the adaptive step size.

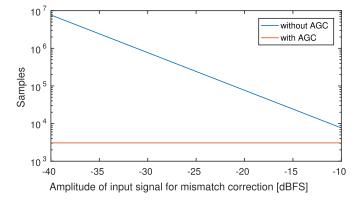

Fig. 9. Calculated convergence time of  $\alpha(n)$  with and without the AGC for  $A_{tar} = FS/4$ , FS = 1, and  $\mu = 2^{-6}$ .

Figure 8 shows a mismatch estimation block realizing Eq. (14). As shown in Appendix, using Eqs. (4), (6), and (14), we can derive  $\alpha(n)$  as

$$E[\alpha(n)] \approx \frac{E[\hat{x}_{opt}^{2}(n)]}{2E[\hat{x}_{opt}(n)\hat{x}_{opt}^{*}(n)]} \Big\{ 1 - \Big(1 - 2\mu R_{opt}(0)\Big)^{n} \Big\}, \quad (15)$$

where the auto-correlation function (ACF) of  $x_{opt}(n)$  is defined as

$$R_{opt}(\tau) \stackrel{\text{def}}{=} E[\hat{x}_{opt}(n)\hat{x}^*_{opt}(n-\tau)].$$

(16)

When *n* goes to infinity,  $E[\alpha(n)]$  converges to

$$\lim_{n \to \infty} E[\alpha(n)] = \frac{E[\hat{x}_{opt}^2(n)]}{2E[\hat{x}_{opt}(n)\hat{x}_{opt}^*(n)]}.$$

(17)

Its convergence time depends on  $\mu$  and  $R_{opt}(0)$ , i.e., the power of  $\hat{x}_{opt}(n)$ , as shown in Eq. (15).

The AGC increases the amplitude of  $\hat{x}_{opt}(n)$  to improve the convergence speed for a small  $\hat{x}_{opt}(n)$ . Figure 9 shows the calculated time when  $\alpha(n)$  reaches 95% of the convergence value with and without the AGC for  $A_{tar} = FS/4$  and  $\mu = 2^{-6}$ , where the full-scale range, *FS*, is equal to one and "dBFS" means dB relative to a full-scale sine wave with an input amplitude of *FS*/2 (see [13]). The convergence time without the AGC increases as the amplitude of  $\hat{x}_{CIC}(n)$  decreases. On the other hand, the time with the AGC does not depend on the amplitude of  $x_{opt}(n)$ , because the amplitude is adjusted to *FS*/4.

The mismatch correction generates the third-order intermodulation (IM<sub>3</sub>) products for two-tone input signals. The mismatch estimation block (Fig. 8) squares y(n) to generate harmonic distortion in  $\alpha(n)$ , then multiplied by  $\hat{x}_{opt}(n)$  and finally subtracted from  $\hat{x}_{opt}(n)$ . This results in  $\hat{x}_{opt}^3(n)$ , causing the IM<sub>3</sub> products at the output of the correction block that deals with two-tone signals. These products can be reduced by decreasing  $\mu$  without FIR filters. Although the correction with a lower  $\mu$  needs more convergence time, the AGC alleviates this problem. We use  $\mu = 2^{-48}$  in the simulation, as will be presented in Sec. IV-A, to obtain a resolution of 12 bits, i.e., an SFDR of 72 dB.

| Block      | Parameter              | Variable         | Value               |

|------------|------------------------|------------------|---------------------|

|            | Number of data         | N                | $2^{20}$            |

|            | Sampling frequency     | $f_s$            | 1                   |

|            | Input full-scale range | FS               | 1                   |

| TI-ADC     | Gain mismatches        | $\Delta_{g0,g1}$ | $0, -2^{-10}$       |

|            |                        | $\Delta_{g2,g3}$ | $-2^{-11}, -2^{-9}$ |

|            | Timing mismatches      | $\Delta_{t0,t1}$ | $0, -2^{-7}$        |

|            |                        | $\Delta_{t2,t3}$ | $-2^{-9}, -2^{-8}$  |

| CIC filter | Number of decimation   | D                | 16                  |

|            | Order                  | L                | 2                   |

|            | Target amplitude       | $A_{tar}$        | FS/4                |

| AGC        | Feedback gain of LPF   | a                | $1 - 2^{-6}$        |

|            | Feedfoward gain of LPF | b                | $2^{-6}$            |

| Correction | Adaptive step size     | $\mu$            | $2^{-48}$           |

| Input      | Frequency              | $f_{in1}$        | $0.2551 f_s$        |

| signal     |                        | $f_{in2}$        | $0.2582 f_s$        |

|            | Amplitude              | $A_{in}$         | FS/40               |

TABLE I SIMULATION CONDITIONS

# IV. VERIFICATION

### A. Simulations

The proposed correction architecture (Fig. 4) is verified by using MATLAB/Simulink simulations of a 12-bit four-channel TI-ADC. Simulation conditions are listed in Table I.

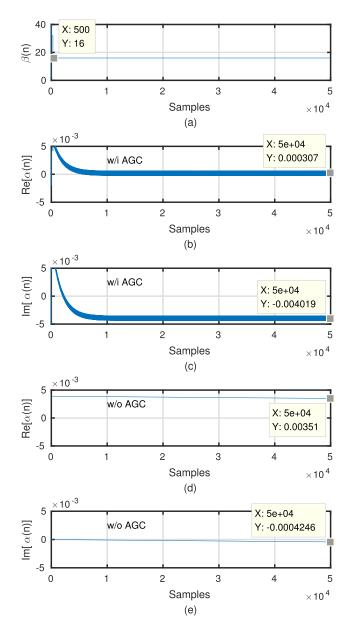

First, we demonstrate the effectiveness of the AGC in the convergence of  $\alpha(n)$ . Figures 10(a), (b), and (c) show the gain of the AGC,  $\beta(n)$ , the real part of  $\alpha(n)$  with the AGC,  $\operatorname{Re}[\alpha(n)]$ , and the imaginary part,  $\operatorname{Im}[\alpha(n)]$ , respectively. After  $\beta(n)$  settled to 16, the average values of  $\text{Re}[\alpha(n)]$ and  $\text{Im}[\alpha(n)]$  gradually converged to 0.0006 and -0.0041, respectively. These values were corresponding to the results calculated from Eq. (17) for the simulated gain and timing mismatches of the TI-ADC as shown in Table I. A larger amplitude of  $\hat{x}_{opt}(n)$  oscillates  $\alpha(n)$  more seriously, because Eq. (15) indicates that  $\alpha(n)$  depends on  $R_{opt}(0)$ , i.e., the power of  $\hat{x}_{opt}(n)$ . This causes the IM<sub>3</sub> products at the output of the correction block. We suppress the oscillation by using a low  $\mu$ , 2<sup>-48</sup>, not to influence the SFDR of the TI-ADC. On the other hand, Fig. 10(d) and (e) represent  $\text{Re}[\alpha(n)]$  and  $Im[\alpha(n)]$  without the AGC, respectively. The average values of Re[ $\alpha(n)$ ] and Im[ $\alpha(n)$ ] did not reach 0.0006 and -0.0041 at all, respectively, even after 50,000 samples.

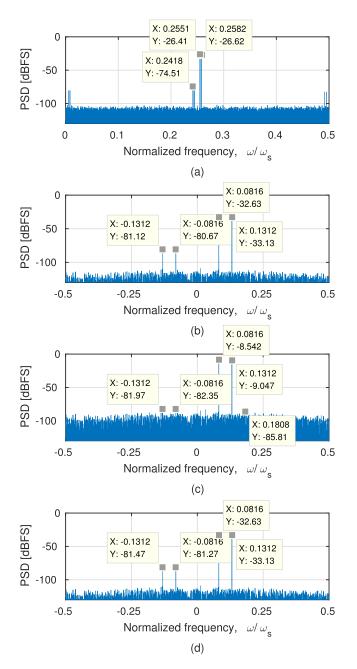

Next, we show that the proposed architecture works properly. Figure 11(a) represents an output power spectrum density (PSD) of the TI-ADC, whereas Fig. 11(b), (c), and (d) represent the output PSDs of the CIC filter and the correction block with and without the AGC, respectively. The AGC adjusted the power of the input signals to -8.5 and -9.0 dBFS, respectively, and the mismatch correction reduced a -74.5 dBFS aliasing signal in Fig. 11 (a) to -81.9 dBFS to obtain an SFDR of 72.9 dB. The IM<sub>3</sub> products were limited to -85.8 dBFS as shown in Fig. 11 (c). This implies that our method can reduce the mismatch aliasing signals of the desired signals combined with an interferer at the adjacent channel. Considering the impact of the interferer on the error vector magnitudes (EVMs) of the received signals, we need to place an FIR (low-pass) filter before the mismatch correction block, as shown in Fig. 1, to reduce the interferer. On the other hand,

Fig. 10. Simulated convergence behaviors of (a)  $\beta(n)$ , (b) Re[ $\alpha(n)$ ] and (c) Im[ $\alpha(n)$ ] with the AGC, and (d) Re[ $\alpha(n)$ ] and (e) Im[ $\alpha(n)$ ] without the AGC.

the correction without the AGC did not decrease the aliasing signals adequately, resulting in an SFDR of 48.1 dB, because  $\alpha(n)$  did not converge.

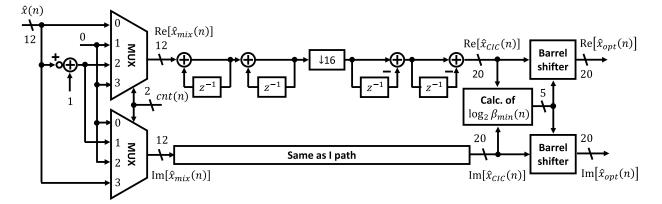

### B. Implementation

We implement the correction architecture without a TI-ADC, as shown in Fig. 4 with Table I, on an FPGA, Intel Cyclone V (FPGA 5CEBA4F23C7N [14]). Figure 12 shows the detailed block diagram of the complex mixer, CIC filter, and AGC. The complex mixer consists of two multiplexers, selecting  $\{\hat{x}(n), 0, -\hat{x}(n), 0\}$  for the I path and  $\{0, -\hat{x}(n), 0, \hat{x}(n)\}$  for the Q path with cnt(n), because  $exp(-j\omega_s t/4)|_{t=nT_s}$  is expressed as  $cos(n\pi/2) - j sin(n\pi/2)$ . This structure needs no multiplier, reducing the implementation cost. The CIC filter with D = 16 and L = 2 adopts a

Fig. 11. Simulated output spectra of (a) the four-channel TI-ADC, (b) the CIC filter, (c) the mismatch correction with the AGC, and (d) without the AGC for two -26 dBFS input signals.

recursive architecture, easily implemented with adders, delays, and a decimator.

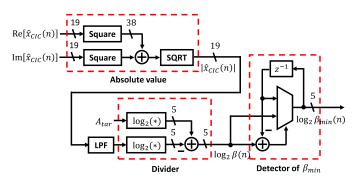

The AGC has two barrel shifters and a calculation block for  $\log_2 \beta_{min}(n)$ to obtain  $\beta_{min}(n)\hat{x}_{CIC}(n)$ where  $\beta_{min}(n)$  is expressed as a power of 2. This significantly simplifies the AGC circuit. Figure 13 shows a block diagram of the calculation of  $\log_2 \beta_{min}(n)$ . of First, the block the absolute value calculates  $|\hat{x}_{CIC}(n)|$ by using  $\sqrt{\operatorname{Re}[\hat{x}_{CIC}(n)]^2 + \operatorname{Im}[\hat{x}_{CIC}(n)]^2}.$ Second, the divider (subtractor) calculates  $\log_2 \beta(n)$  $(= \log_2 A_{tar} - \log_2 |\hat{x}_{CIC}(n)|)$ . Finally, the detector obtains  $\beta_{min}(n)$  by comparing  $\log_2 \beta(n)$  with  $\log_2 \beta(n-1)$ . It outputs  $\log_2 \beta(n)$ , whereas keeps the previous value,  $\log_2 \beta(n-1)$ ,

TABLE II Occupied Logic Resources of the Correction Architecture on Cyclone V FPGA

| Block                       | Used logic resources |             |

|-----------------------------|----------------------|-------------|

| DIOCK                       | ALM                  | DSP         |

| Complex mixer & CIC filters | 155 (0.84%)          | 0 (0%)      |

| AGC                         | 429 (2.32%)          | 11 (16.67%) |

| Mismatch correction         | 155 (0.84%)          | 11 (16.67%) |

| Total                       | 739 (4.00%)          | 22 (33.33%) |

for  $\log_2 \beta(n) - \log_2 \beta(n-1) = 1$ , i.e.,  $\beta(n) = 2\beta(n-1)$ , determined by the peak-to-average power ratio (PAPR) of the input signal.

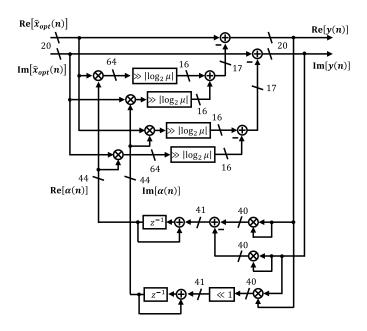

The mismatch correction as shown in Fig. 14 subtracts  $\alpha(n)\hat{x}_{opt}^*(n)$ , expressed by Eq. (18), from  $\hat{x}_{opt}(n)$  to remove the aliasing signals in y(n),

$$\alpha(n)\hat{x}^*_{opt}(n) = \operatorname{Re}[\alpha(n)]\operatorname{Re}[\hat{x}_{opt}(n)] + \operatorname{Im}[\alpha(n)]\operatorname{Im}[\hat{x}_{opt}(n)] + j(\operatorname{Im}[\alpha(n)]\operatorname{Re}[\hat{x}_{opt}(n)] - \operatorname{Re}[\alpha(n)]\operatorname{Im}[\hat{x}_{opt}(n)]).$$

(18)

The coefficient of  $\alpha(n)$  is estimated by multiplying squared y(n), given by Eq. (19), with  $\mu = 2^{-48}$ ,

$$y^{2}(n) = \operatorname{Re}[y(n)]^{2} - \operatorname{Im}[y(n)]^{2} + j2\operatorname{Re}[y(n)]\operatorname{Im}[y(n)].$$

(19)

The coefficient of  $\mu$  is realized by a bit shift operator " $\gg |\log_2 \mu|$ " inserted before the subtraction of  $\alpha(n)\hat{x}_{ant}^*(n)$ .

Table II summarizes the logic resources of the proposed correction architecture on the FPGA. An adaptive logic module (ALM) has an eight-input fracturable look-up table, two dedicated embedded adders, and four dedicated registers. The circuits used 739 ALMs and 22 DSP blocks in total.

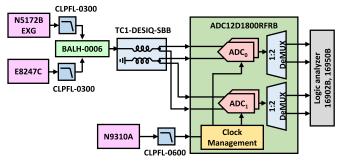

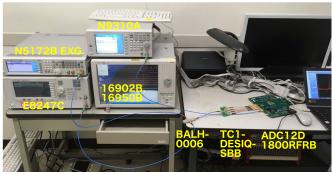

## C. Measurements

The correction architecture is also verified by using a commercial 1.2 GS/s 12-bit four-channel TI-ADC (TI ADC12D1800RF [15]). Figures 15 and 16 show the block diagram and photograph of the measurement setup, respectively. The frequencies of the sampling clock and two input signals were 600, 306.12, and 309.84 MHz, generated from three signal generators, Keysight N9310A, N5172B EXG, and E8247C, respectively. The output data were acquired with a logic analyzer, Keysight 16902B with 16950B.

The measured output data were corrected by the correction circuits with D = 16 and  $A_{tar} = FS/4$  realized on the FPGA as shown in Sec. IV-B. First, Fig. 17(a) shows the measured output spectrum of the TI-ADC for  $2^{20}$  samples and a -30 dBFS input signal at 306.12 MHz ( $\omega/\omega_s = 0.2551$ ). The second- and third-order harmonic distortions of the input signal and their aliasing signals appeared at the output, because the low-pass filter (Crystek CLPFL-0300) after the signal source could not decrease the distortions sufficiently; it reduced the second-order harmonic (612.24 MHz,  $\omega/\omega_s =$ 0.2602) by only 16 dB. Figures 17(b), (c) and (d) show the output spectra of the CIC filter, AGC, and correction circuit on the FPGA, respectively. The AGC increased the input signal

Fig. 12. Block diagram of the complex mixer, CIC filter, and AGC.

Fig. 13. Block diagram of the calculation of  $\log_2 \beta_{min}(n)$ .

Fig. 14. Block diagram of the mismatch correction.

(downsampled to  $\omega/\omega_s = 0.0816$ ) from -36.39 dBFS to -6.28 dBFS. The correction circuit reduced a -44.55 dBFS aliasing signal at -0.0816 (downsampled) to -88.57 dBFS. These results also show that the circuits produce do not any harmonic distortions except for the distortions of the input signal. Second, Fig. 18(a), (b), (c), and (d) represent the measured output spectra of the ADC, CIC filter, AGC, and correction

Fig. 15. Block diagram of the measurement setup.

Fig. 16. Photograph of the measurement setup.

circuit, respectively, for -27 dBFS input signals at 306.12 and 309.84 MHz. These spectra also included the second- and third-order harmonic distortions of two input signals and their aliasing signals owing to the same reason as the single-tone input signal. The AGC adjusted the input signals at 0.2551 and 0.2582 and the correction circuit eliminated the aliasing signals at -0.0816 and -0.1312. In both Fig. 17 and 18, DC-offset mismatches among ADCs generated spurs at DC, which were not the target of this correction.

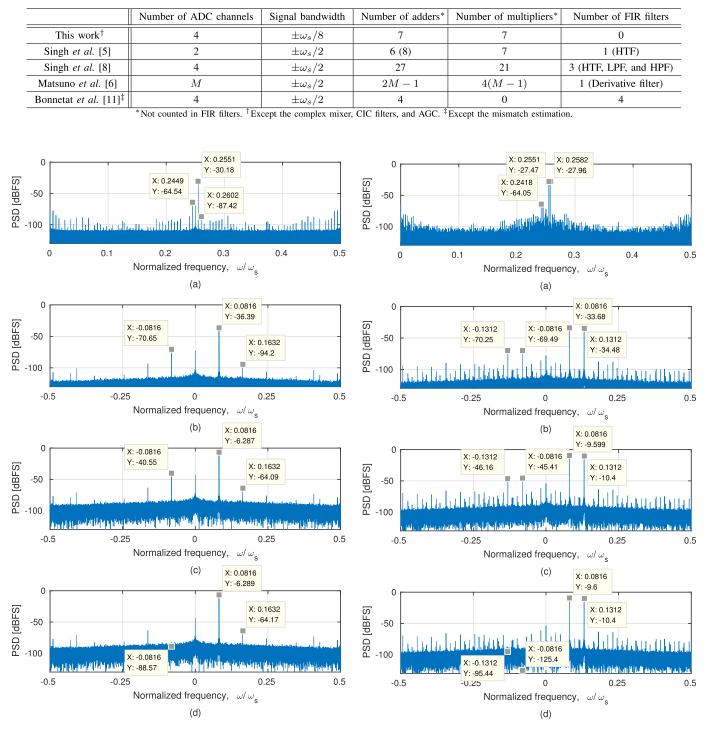

# D. Hardware Comparison

Table III compares the proposed method with the previously reported methods. Our method uses seven adders, seven multipliers, and no FIR filters, except in the complex mixer, CIC filters, and AGC. These blocks are generally included in the digital front-end circuits of direct-RF sampling

Fig. 17. Measured output spectra of (a) ADC12D1800RF, (b) the CIC filter, (c) AGC, and (d) correction circuit on the FPGA for a -30-dBFS input signal at 306.12 MHz.

Fig. 18. Measured output spectra of (a) ADC12D1800RF, (b) the CIC filter, (c) AGC, and (d) correction circuit on the FPGA for -27 dBFS input signals at 306.12 and 309.84 MHz.

receivers [1], [16]. The conventional method [5] presents two types of configurations correcting a two-channel TI-ADC. The type I needs six adders and seven multipliers, whereas the type II requires eight adders and seven multipliers. Both the types use HTFs to generate I/Q complex signals. The method in [8] is the extended version of the method in [5] to a four-channel TI-ADC, and needs more adders, multipliers, and FIR filters. The numbers of adders and multipliers in [6] depend on that of ADC channels. In addition, an FIR filter is required for the derivative of input signals. The last method [11] for a four-channel TI-ADC employs four FIR filters, which consists of many adders and multipliers.

# V. CONCLUSION

We present the digital correction method for a bandpass sampling four-channel TI-ADC in a direct-RF sampling receiver. The method removes aliasing signals owing to the gain and sampling-time mismatches of the ADCs by using the CACF and adaptive signal processing of the input signals downconverted and decimated by a complex mixer and CIC filters in the receiver. An AGC adjusts the amplitude of the input signal for the correction to improve the convergence time. The MATLAB/Simulink simulations and measurements show that the aliasing signals of 1.2 GS/s 12-bit four-channel TI-ADCs are reduced to less than -80 dBFS. The proposed correction method needs no FIR filters and fewer adders and multipliers than the conventional methods.

# Appendix

# DERIVATION OF $\alpha(n)$

This appendix derives  $\alpha(n)$  of Eq. (15) in Sec. III-C. We calculate the expected value of Eq (14) as

$$E[\alpha(n+1)] = E[\alpha(n)] + \mu E[y^2(n)].$$

(20)

From Eq. (11), the square of y(n) is expressed as

$$y^{2}(n) = \hat{x}_{opt}^{2}(n) - 2\alpha(n)\hat{x}_{opt}(n)\hat{x}_{opt}^{*}(n) + \alpha^{2}(n)\hat{x}_{opt}^{*2}(n) \approx \hat{x}_{opt}^{2}(n) - 2\alpha(n)\hat{x}_{opt}(n)\hat{x}_{opt}^{*}(n) \quad (\because \alpha(n) \ll 1).$$

(21)

Substituting Eq. (21) into Eq. (20), we obtain

$$E[\alpha(n+1)] \approx E[\alpha(n)] + \frac{\mu}{2\pi} E\left[\hat{x}_{opt}^{2}(n) - 2\alpha(n)\hat{x}_{opt}(n)\hat{x}_{opt}^{*}(n)\right] \\ = \left(1 - \frac{\mu}{\pi} E[\hat{x}_{opt}(n)\hat{x}_{opt}^{*}(n)]\right) E[\alpha(n)] + \frac{\mu}{2\pi} E[\hat{x}_{opt}^{2}(n)].$$

(22)

Therefore, solving Eq. (22) for  $E[\alpha(n)]$ , we have

$$E[\alpha(n)] = \frac{E[\hat{x}_{opt}^{2}(n)]}{2E[\hat{x}_{opt}(n)\hat{x}_{opt}^{*}(n)]} \times \left\{ 1 - \left(1 - 2\mu E[\hat{x}_{opt}^{2}(n)]\right)^{n} \right\}, \\ = \frac{E[\hat{x}_{opt}^{2}(n)]}{2E[\hat{x}_{opt}(n)\hat{x}_{opt}^{*}(n)]} \left\{ 1 - \left(1 - 2\mu R_{opt}(0)\right)^{n} \right\}.$$

(23)

#### REFERENCES

- [1] E. Martens *et al.*, "RF-to-baseband digitization in 40 nm CMOS with RF bandpass  $\Delta\Sigma$  modulator and polyphase decimation filter," *IEEE J. Solid-State Circuits*, vol. 47, no. 4, pp. 990–1002, Apr. 2012.

- [2] J. Lee, J. Kim, and S. Cho, "A 1.8 to 2.4-GHz 20 mw digitalintensive RF sampling receiver with a noise-canceling bandpass lownoise amplifier in 90 nm CMOS," in *IEEE Radio Freq. Integr. Circuits Symp. Dig. Papers*, Anaheim, CA, USA, May 2010, pp. 293–296.

- [3] Y. G. Yoon, J. Kim, T. K. Jang, and S. Cho, "A time-based bandpass ADC using time-interleaved voltage-controlled oscillators," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 55, no. 11, pp. 3571–3581, Dec. 2008.

- [4] N. Kurosawa, H. Kobayashi, K. Maruyama, H. Sugawara, and K. Kobayashi, "Explicit analysis of channel mismatch effects in timeinterleaved ADC systems," *IEEE Trans. Circuits Syst. I, Fundam. Theory Appl.*, vol. 48, no. 3, pp. 261–271, Mar. 2001.

- [5] S. Singh, L. Anttila, M. Epp, W. Schlecker, and M. Valkama, "Analysis, blind identification, and correction of frequency response mismatch in two-channel time-interleaved ADCs," *IEEE Trans. Microw. Theory Techn.*, vol. 63, no. 5, pp. 1721–1734, May 2015.

- [6] J. Matsuno, T. Yamaji, M. Furuta, and T. Itakura, "All-digital background calibration technique for time-interleaved ADC using pseudo aliasing signal," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 60, no. 5, pp. 1113–1121, May 2013.

- [7] C. H. Law, P. J. Hurst, and S. H. Lewis, "A four-channel time-interleaved ADC with digital calibration of interchannel timing and memory errors," *IEEE J. Solid-State Circuit*, vol. 45, no. 10, pp. 2091–2103, Oct. 2010.

- [8] S. Singh, L. Anttila, M. Epp, W. Schlecker, and M. Valkama, "Frequency response mismatches in 4-channel time-interleaved ADCs: Analysis, blind identification, and correction," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 62, no. 9, pp. 2268–2279, Sep. 2015.

- [9] L. Anttila, M. Valkama, and M. Renfors, "Circularity-based I/Q imbalance compensation in wideband direct-conversion receivers," *IEEE Trans. Veh. Technol.*, vol. 57, no. 4, pp. 2099–2113, Jul. 2008.

- [10] T. Takahashi, T. Kihara, and T. Yoshimura, "Correction of mismatches in time-interleaved A/D converters for digital-RF receivers," in *Proc. IEEE Int. Conf. Electron., Circuits Syst.*, Batumi, Georgia, Dec. 2017, pp. 9–12.

- [11] A. Bonnetat, J.-M. Hodé, G. Ferré, and D. Dallet, "Correlation-based frequency-response mismatch compensation of quad-TIADC using real samples," *IEEE Trans. Circuits Syst.*, *II, Exp. Briefs*, vol. 62, no. 8, pp. 746–750, Aug. 2015.

- [12] T. Kihara, H. Yano, and T. Yoshimura, "Design of cascaded integratorcomb decimation filters for direct-RF sampling receivers," in *Proc. IEEE Int. Symp. Circuits Syst.*, Baltimore, MD, USA, May 2017, pp. 1–4.

- [13] R. Schhreier and G. C. Temes, Understanding Delta–Sigma Data Converters, 1st ed. Hoboken, NJ, USA: Wiley, 2005.

- [14] Intel. (2016). FPGA5CEBA4F23C7N, Cyclone V FPGA. [Online]. Available: https://www.altera.co.jp

- [15] Texas Instruments. (2016). ADC12D1800RF, 12-Bit, Single 3.6 GSPS RF Sampling ADC (Rev. H). [Online]. Available: http://www.ti.com

- [16] M. Vucic and M. Butorac, "All-digital high-dynamic automatic gain control," in *Proc. IEEE Int. Symp. Circuits Syst.*, Taipei, Taiwan, May 2009, pp. 1032–1035.

Takao Kihara received the B.S., M.S., and Ph.D. degrees in electronic engineering from Osaka University, Osaka, Japan, in 2005, 2006, and 2009, respectively. He was with the Renesas Electronics Corp., Japan, from 2009 to 2014, where he was developing LTE/WCDMA CMOS transmitters and Bluetooth low energy CMOS receivers. Since 2014, he has been an Assistant Professor with the Osaka Institute of Technology, Japan. His current research interests include direct-RF sampling receivers. He is a member of the Institute of Electronics and

Information and Communication Engineers (IEICE). He was a recipient of the 2010 IEICE Best Paper Award. He served as an Associate Editor for *IEICE Electronics Express* (ELEX) from 2015 to 2018.

**Tsutomu Yoshimura** was born in Fukui, Japan, in 1966. He received the B.S. and M.S. degrees in physics from the University of Tokyo, in 1989 and 1991, respectively, and the Ph.D. degree in electrical engineering from Hiroshima University in 2005. From 1993 to 2007, he was with the Mitsubishi Electric Corporation, Itami, Japan, where he contributed toward the design of system LSIs for optical communication systems. From 2007 to 2017, he was an Associate Professor with the Osaka Institute of Technology, where he has been a Professor, since

2017. His interests include the design of high-speed analog and digital circuits, including phase-locked loop circuits. He is also interested in investigating the interference and coupling issues between closed-loop systems. He is a member of the Institute of Electronics, Information and Communication Engineers of Japan (IEICE). He was a recipient of the 2007 IEEE Circuits and Systems Society Darlington Best Paper Award.