# Device Modelling for Bendable Piezoelectric FET-Based Touch Sensing System

Shoubhik Gupta, *Student Member, IEEE*, Hadi Heidari, *Member, IEEE*, Anastasios Vilouras, *Student Member, IEEE*, Leandro Lorenzelli, *Member, IEEE*, and Ravinder Dahiya, *Senior Member, IEEE*

Abstract—Flexible electronics is rapidly evolving towards devices and circuits to enable numerous new applications. The high-performance, in terms of response speed, uniformity and reliability, remains a sticking point. The potential solutions for high-performance related challenges bring us back to the timetested silicon based electronics. However, the changes in the response of silicon based devices due to bending related stresses is a concern, especially because there are no suitable models to predict this behavior. This also makes the circuit design a difficult task. This paper reports advances in this direction, through our research on bendable piezoelectric oxide semiconductor field effect transistor (POSFET) based touch sensors. The analytical model of POSFET, complimented with Verilog-A model, is presented to describe the device behavior under normal force in planar and stressed conditions. Further, dynamic readout circuit compensation of POSFET devices have been analyzed and compared with similar arrangement to reduce the piezoresistive effect under tensile and compressive stresses. This approach introduces a first step towards the systematic modeling of stress induced changes in device response. This systematic study will help realize high-performance bendable microsystems with integrated sensors and readout circuitry on ultra-thin chips (UTCs) needed in various applications, in particular, the electronic skin (e-skin).

*Index Terms*—Device modeling, e-skin, flexible electronics, interfacing circuit, POSFET, tactile sensing.

### I. Introduction

THE field of flexible and printed electronics has received considerable interest in recent years and is seen as the future of electronics, as also indicated by electronics industry roadmap [1]. So far, the progress in this field has mainly come through organic semiconductors and various printing and stamping techniques [2]–[5]. The devices from organic semiconductors gain from the inherent mechanical flexibility, but due to poor charge carrier mobility of these materials

Manuscript received June 12, 2016; revised September 1, 2016; accepted September 29, 2016. Date of publication November 16, 2016; date of current version November 23, 2016. This work was supported in part by the European Commission under Grant Agreements PITN-GA-2012-317488-CONTEST, EPSRC Engineering Fellowship for Growth - PRINTSKIN (EP/M002527/I), EPSRC First Grant (EP/M002519/I), and EPSRC Centre for Doctoral Training in Integrative Sensing Measurement (EP/L016753/I). Authors are thankful to the support received for this work from James Watt Nanofabrication Centre (JWNC) and Electronics Systems Design Centre (ESDC). This paper was recommended by Associate Editor A. Mazzanti.

- S. Gupta, H. Heidari, A. Vilouras, and R. Dahiya are with the Bendable Electronics and Sensing Technologies (BEST) group in School of Engineering, University of Glasgow, Glasgow, G12 8QQ, UK (e-mail: Ravinder.Dahiya@glasgow.ac.uk).

- L. Lorenzelli is with Microsystems Technology Research Unit, Fondazione Bruno Kessler, 38122 Trento, Italy.

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TCSI.2016.2615108

$(1 \text{ cm}^2/\text{V.s} \text{ (maximum reported } 43 \text{ [6]) cf.} \sim 1000 \text{ cm}^2/\text{V.s}$ for single crystal silicon) the devices are slow. Factors such as large channel lengths (>20 $\mu$  m cf. <100 nm in deep submicrometer technology [5]) of printed devices is another reason why these devices are slow. The high-performance in terms of device response, speed, uniformity, reliability, and stability are critical for flexible electronics to address the fast computation and communication needs of many emerging applications such as e-skin in robotics, smart cities, and internet of things. For example, in robotics the feedback from tactile skin over the body should be fast enough (<ms) for quick action [7]-[10]. For these reasons, recently the field of flexible electronics has seen renewed interest in silicon, with devices and circuits made from transfer printed silicon nanowires (NWs) and ultra-thin chips (UTCs) [11], [12]. A hybrid mix of circuits from inherently flexible materials like organic polymers and inorganic semiconductors in new forms such as NWs and UTCs will be an interesting development [12]. This will also benefit from advances such as 3D integrated circuits (ICs) and heterogeneous integration.

Irrespective of the material and circuits are made from, they exhibit stress-induced variations in response when they are bent. For example, in tactile skin, or e-skin, the electronics are required to conform to 3D surfaces, and this means electronics should bend [13], [14]. The bending of electronics in this case (and in many other applications) induces stress on the devices, which results in deviation or alteration of the performance from the designed values [15], [16]. A few attempts made to include stress-induced effects in device models are mainly related to strained silicon devices [17]–[19]. This paper reports advances in this direction through our research on bendable piezoelectric oxide semiconductor field effect transistors (POSFET) and the associated interface circuitry. This paper extends our work reported in [20], where we presented the analytical model of POSFET devices using the piezoelectric capacitor model and the underlying physics related to metal-oxide-semiconductor field effect transistors (MOSFETs). This extended paper compliments the analytical model of POSFETs with Verilog-A model to describe their behavior under normal force and stressed conditions. The focus is on the characteristics of stressed POSFET devices and their electromechanical response. The cancellation of the stress induced changes in the response of the readout circuit, due to tensile and compressive stress, has been studied along with the use of mobility enhancement to alter the sensitivity of the sensor under bent conditions. The results presented in this paper include the first approach towards a systematic analysis

of the response of planar and stressed on-chip conventional configuration of POSFET devices with arrangements, such as source follower, differential op-amp and chopper amplifier.

This paper is organized as follows: A brief description of the state-of-the-art related to various flexible electronics device modelling schemes is given in Section II. The structure and working of POSFET devices is presented in Section III. A detailed discussion of the analytical model of POSFET is given in Section IV. This section also includes the Verilog-A model, which defines the behavior of planar and stressed POSFET. Section V presents various on-chip circuit implementation for POSFET device in planar, compressive and tensile stress and their simulation results. Finally, the major outcomes are summarized in Section VI.

### II. STATE OF THE ART OF BENDABLE DEVICE MODELLING

Devices and circuits on flexible substrates get stressed when they, or their substrate, are bent and this results in major changes in the parameters, such as charge-carrier mobility, threshold voltage etc. It is important to understand how these parameters change so as to ensure the reliable functioning of circuits on flexible substrates when they are bent. A circuit designer should be aware of potential shifts in behavior of devices due to mechanical stress or strain—which may be because of bending during their use, or other factors such as fabrication related stress. The bending induced stress is known to affect the performance of CMOS solid-state sensors in terms of offset voltage and sensitivity [15], [21].

The external stress also changes the energies between the conduction and valence band, by shifting the energy spectrum, which is reflected as a change of the charge carrier mobility [22]. The is also termed as the piezoresistive effect, which should be considered while designing circuits on UTCs [23]. The advanced MOS compact models available today can be used to account for layout-induced stress effects, but they are insufficient to handle bending related large stress [24].

To model this effect, two approaches have been explored in literature. The first approach defines charge carrier mobility of a device as a function of strain and then uses the modified mobility with standard equations in simulation tools like Verilog-A [25]. In this case, total mobility is expressed as:

$$\mu_n^{tot} = \sum_{i=1}^3 p^{(i)} \cdot \mu_{n,str}^{(i)} \tag{1}$$

where  $p^{(i)}$  is the relative population of each conduction valley and  $\mu_{n,str}^{(i)}$  strain dependent mobility for the  $i^{th}$  valley. The term  $\mu_{n,str}^{(i)}$  is expressed as:

$$\mu_{n,str}^{(i)} = \frac{\beta \cdot \mu^L}{1 + (\beta - 1) \cdot h^{(i)} + \beta \cdot \left(\frac{\mu^L}{\mu^{LI}} - 1\right)} \cdot m_{(i)}^{-1} \quad (2)$$

where  $m_{(i)}^{-1}$  is the scaled effective mass tensor for the  $i^{\text{th}}$  valley,  $\mu^L$  is the lattice mobility,  $\mu^{LI}$  is the lattice mobility which takes into account the scattering due to doping,  $\beta$  is a function of strain in silicon, and  $h^{(i)}$  is a physical parameter, details of which are given in [26]. This approach is mostly used to study the effect of bending on standalone devices. The second approach involves using the changes in energy levels, and

could also be used to study circuit performance on flexible or bendable substrates. Modern compact models such as BSIM4 usually provides a set of parameters related to material, like band gap, bulk mobility, work function, electron affinity etc., which affect the electrical characteristics [27]. However, the requirement of a priori knowledge of stress values and dependence on material parameters makes the above mentioned approaches inconvenient for circuit designers. Therefore, in the presented work, we have used the analytical equations along with Verilog-A, to investigate the effect of bending on the performance of single POSFET devices and associated readout circuits.

The impact of piezo-resistive effect can be minimized by: a) surface structural arrangement, such as fabricating the devices and circuits in the neutral plane of overall structure, b) suitable layouts which are stress independent, and c) dynamic circuit compensation methods. For example, if a priori information is available about the orientation of stress, then the circuits could be designed along the crystal axis experiencing minimum effects of bending. However, if stress appears arbitrarily then the fabrication process corner needs to be wider to ensure proper functioning of circuit [28]. A full compact, and Cadence environment friendly model has been reported recently to compensate the effect of piezoresistive effect in CMOS based bendable hall sensor [16]. A few works using basic compensation circuits such as inverters and ringoscillators etc. have been reported, as well as to mitigate the bending related deviations in device performance [29]. The structural arrangement to mitigate the stress related effects include depositing an encapsulation layer on top of the device in such a way that the device appears on a neutral plane where there is no strain. However, there are practical difficulties for realizing electronics in the neutral plane, especially when then top surface is required to be open to receive external stimuli. A combination of the above approaches could perhaps offer better solution.

# III. BENDABLE POSFET TOUCH SENSOR DEVICE

# A. POSFET Device Structure

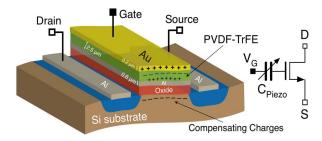

POSFET devices make a key building block of our e-skin related research [30]. The detailed design and various implementations of planar POSFET devices have been reported in our previous works [13], [14], [31]. However, a short description is given here for quick reference. The structure of POSFET is similar to ferroelectric random access memory (FeRAM) device, where a stack of ferroelectric material and gate oxide is used as the gate dielectric. The read and write operations of FeRAMs are governed by the voltage applied over the ferroelectric material [32]. In POSFETs, a piezoelectric material lies between the gate electrode of underlying MOS device and the top metal as shown in Fig. 1. In other words, the device structure can be defined as a piezoelectric capacitor coupled to gate electrode of MOSFET [14]. The piezoelectric material by its virtue produces charge when pressed and this is given as [33]:

$$D_{33} = d_{33}T_3 + \varepsilon_{33}^T E_3 \tag{3}$$

Fig. 1. Illustration of bendable POSFET.

where D is the electric displacement, T is the mechanical stress, E is the electric field,  $\varepsilon_{33}^T$  is the dielectric constant under constant stress, and  $d_{33}$  is the piezoelectric constant in thickness mode. The charges produced by piezoelectric effect modulate the channel current, which is then used to quantify the applied force. Various piezoelectric materials such as PZT, AlN, and PVDF, etc., could be used to make the piezoelectric layer of POSFETs. PZT shows a high piezoelectric coefficient but the presence of lead makes it less attractive for many applications, especially those related to biomedical field. AlN is a good alternative, but it exhibits low piezoelectric coefficient and needs high temperature for sintering, which makes it difficult to use when materials such as aluminum are used for interconnections. Also, challenges in ensuring the crystal orientation (002) during deposition makes AlN less attractive. Therefore, in POSFETs we have used piezoelectric polymer, P(VDF-TrFE), which has moderate piezoelectric coefficient, easy and low temperature processing and inherent mechanical flexibility.

POSFET devices provide high-performance, thanks to the silicon based CMOS technology. Like silicon based solid-state sensors, POSFETs have high speed, better sensitivity and excellent integration with readout and signal conditioning electronics [14]. Moreover, it can be miniaturized to obtain high spatial resolution and can be advanced towards system on chip. However, the intrinsic rigid and brittle nature of silicon substrate limits their placement to planar surfaces only.

## B. Design and Tactile Sensing Chip Layout

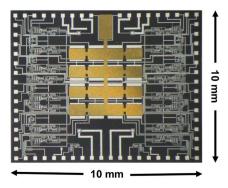

The new design of POSFET based touch sensing system is influenced by human tactile spatial resolution. For example, in channel width of 3276  $\mu$ m to achieve high aspect ratio of 273. The total active area is 0.36 cm² and overall chip size is 1cm ×1cm, as shown in Fig. 2. fingertips we need high density of sensors (to achieve 1 mm tactile acuity [10]) and therefore we have designed a 4 × 4 array of sensors. Each sensor has channel length of 12  $\mu$ m and

The tactile sensing chip fabrication is based on NMOS technology, using p-well in n-type wafer, single metal and single poly. Serpentine shape of gate is chosen to accommodate this high channel width in a compact active area of 750  $\mu$ m  $\times$  1000  $\mu$ m per device. After transistor fabrication, the piezoelectric layer is spin coated from a solution prepared by dissolving P(VDF-TrFE) pellets in RER500 solvent. This is followed by annealing of piezoelectric layer in nitrogen

Fig. 2. Image of fabricated tactile sensing chip using CMOS technology.

ambient at 150°C. After the top metal (gold) is evaporated. The P(VDF-TrFE) is then selectively dry etched using oxygen plasma from areas not covered by gold. Finally, the processed wafers are thinned down using anisotropic wet etching to obtain bendable POSFET chips.

### IV. ANALYTICAL AND VERILOG-A MODEL

A simple analytical model is presented here to define the output and transfer characteristic equations of POSFET. A Verilog-A model is also developed to investigate the response of tactile sensing device for a wide range of applied forces (0-2N) under planar, and stressed condition.

# A. Analytical Model

One of the most important process during fabrication of POSFET is poling—the process of aligning the dipoles along a preferred direction. This is done by applying high electric field across the piezoelectric layer. Before poling, the dipoles are randomly oriented in the polymer and no piezoelectricity is observed. In presence of high electric field, carbon-fluorine and carbon-hydrogen covalent bonding rotate around the main chain of the polymer molecule, leading to the effect of piezoelectricity in molecule [34], [35]. With suitable steps, such as grounding all metal layers underneath the piezoelectric layer, the impact of poling on devices could be avoided [13], [36]. The effect of poling on electrical characteristics of POS-FET is investigated here through new mathematical model. This model combines the hysteresis property of piezoelectric polymer with standard MOSFET equations. To calculate the amount of polarization charges due to applied electric filed, Miller et al [37], have proposed simple equation which relates the polarization charges to the electric field.

These equations are:

$$P^{+}(E) = P_{s} tanh\left(\frac{E - Ec}{2\delta}\right) + \varepsilon_{F} \varepsilon_{o} E \tag{4}$$

$$\delta = E_c \left( ln \left( \frac{1 + \frac{P_r}{P_s}}{1 - \frac{P_r}{P_s}} \right) \right)^{-1}$$

(5)

$$P^{-}(E) = -P^{+}(-E) \tag{6}$$

Here,  $P_s$  is saturation polarization, which is the maximum polarization charge achieved during the process of poling.

This can be extracted from the level at which hysteresis loop saturates.  $P_r$  is remnant polarization, the polarization charge left when electric field is removed after poling.  $E_c$  is the coercive field at which the polarization changes their polarity.  $P^+(E)$  and  $P^-(E)$  denotes positive going (lower) branch and negative-going (upper) branch of hysteresis curve, respectively.

During poling, the switching polarization,  $P_{sw}$ , is developed in the polymer.  $P_{sw}$  is the amount of polarization switched from one remnant polarization state to the maximum polarization state of the opposite polarity. With transistor underneath the piezoelectric layer, the  $P_{sw}$  results in creation of an extra layer of charge in the semiconductor channel to maintain charge neutrality. These extra charges can be termed as compensation charge,  $P_{comp}$ , and can be written as:

$$P_{comp} = P_{sw} = P_r + P_s \tag{7}$$

Thus, after poling there is a fixed amount of charge present at oxide-semiconductor interface which results in changes of the flat band voltage. The flat band voltage of transistor is defined as the difference between the gate metal work function,  $\mathcal{O}_M$ , and the semiconductor workfunction  $\mathcal{O}_S$ , and is expressed as:

$$V_{FB} = \emptyset_M - \emptyset_s \tag{8}$$

This change leads to either increase, or decrease in the flat band voltage depending on the poling direction. In case of POSFET devices, poling is done by applying positive voltage on the top metal and keeping the gate metal at ground. This condition creates a layer of negative charges at the oxide-semiconductor interface and so the flat band voltage for n-MOSFET decreases, and can be expressed as:

$$V_{FB\_eff} = V_{FB} - \left(\frac{P_s + P_r}{C_{ox}}\right) \tag{9}$$

The threshold voltage of transistor is directly related to the flat band voltage according to the following equation:

$$V_{th} = V_{FB} + 2\emptyset_F + \frac{\sqrt{2\epsilon_s N_a (2\emptyset_F + V_{SB})}}{C_{ox}}$$

(10)

where  $\emptyset_F$  is the fermi potential, and  $N_a$  is the doping concentration of bulk silicon. A change in the flat band voltage results in a change in the threshold voltage, which can be written as:

$$V_{th\_eff} = V_{th} - \left(\frac{P_s + P_r}{C_{ox}}\right) \tag{11}$$

After quantifying the change in threshold voltage due to poling, and taking into account the overall device capacitance, which is the in series combination of the polymer capacitance and oxide capacitance, the characteristic current equation of POSFET in linear and saturation region can be written as:

$$I_{ds} = \begin{cases} \mu_n C_{stack} \left(\frac{W}{L}\right) \left\{ \left(V_{gs} - V_{th_{eff}}\right) V_{ds} - \left(\frac{1}{2}\right) V_{ds}^2 \right\} \\ \mu_n C_{stack} \left(\frac{W}{2L}\right) \left(V_{gs} - V_{th_{eff}}\right)^2 \end{cases}$$

(12)

where

$$\frac{1}{C_{stack}} = \frac{1}{C_{ox}} + \frac{1}{C_{PVDF}}$$

TABLE I Values Used in the Proposed Model

| Symbol               | Parameter                           | Value |

|----------------------|-------------------------------------|-------|

| W                    | Channel Width (µm)                  | 3276  |

| L                    | Channel Length $(\mu m)$            | 12    |

| $\mu$                | Carrier mobility $(cm^2/V.s)$       | 850   |

| $t_{ox}$             | Oxide thickness $(nm)$              | 45    |

| $t_{pvdf}$           | PVDF thickness (μm)                 | 2.5   |

| $\mathcal{E}_{pvdf}$ | Permittivity of PVDF                | 12    |

| $\varepsilon_{ox}$   | Permittivity of oxide               | 3.9   |

| $P_r$                | Remnant polarization $(nc/cm^2)$    | 33    |

| $P_s$                | Saturation polarization $(nc/cm^2)$ | 13    |

| $E_c$                | Coercive field $(kV/cm)$            | 160   |

| $V_{th}$             | Threshold voltage $(V)$             | 1.5   |

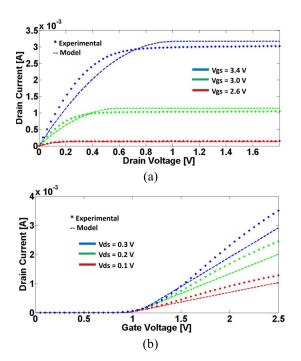

Fig. 3. (a) Characteristic curves of POSFET at different gate voltages, and (b) transfer curves of POSFET at different drain voltages.

Both parts of (12) are simulated in MATLAB, using the parameters given in Table I, and plotted against the experimental measurements performed over the device with channel width 3276  $\mu$ m and length 12  $\mu$ m, as shown in Fig. 3.

The reasonable match with the experimental values observed in output characteristics, validates the proposed analytical model. The minor deviation observed in transfer characteristics between the simulated and experimental results could be attributed to the change in charge distribution in the polymer upon biasing the top metal. The polarization charge distribution in piezoelectric polymer depends upon the voltage applied across it (4) and at higher gate voltages this charge affects the channel region minority carriers. Since this dynamic behavior is not included in the model, we observe the deviation.

# B. Verilog-A Model

The physico-mechanical model described in the previous subsection could be adapted to fully characterize the POSFET

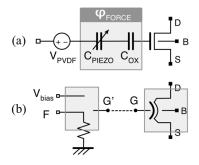

Fig. 4. (a) POSFET macro-model structure, and (b) strained POSFET Verilog-A sub-circuit blocks and external connections.

devices [20]. Starting from these physical models we have implemented a general macro-model in Verilog-A. We have considered the standard 0.18- $\mu$ m CMOS technology in our model implementations. To this end, POSFET was considered to comprise of two fully uncoupled stages: an electromechanical stage (i.e., P(VDF-TrFE) capacitor) where it is assumed that in bent condition the area of contact between the stimuli and the sensor remains the same, and so the charge produced due to piezoelectric layer remains unchanged. The second stage is the electronic stage which is underlying MOSFET experiencing bending stress. However, this assumption does not follow the condition of charge neutrality of the POSFET structure, given by:

$$\sigma_I + \sigma_P + \sigma_s = 0 \tag{13}$$

where  $\sigma_I$ ,  $\sigma_P$ , and  $\sigma_S$  are the charge densities at the interface of gate electrode–piezoelectric polymer, in the bulk of the piezoelectric polymer, and in the semiconductor, respectively. Usually  $\sigma_s$  is much smaller than  $\sigma_I$  and  $\sigma_{P_s}$ , and constant with respect to the applied force, and therefore (13) reduces to:

$$\sigma_I + \sigma_P = 0 \tag{14}$$

With this the electronic stage can be considered as fully uncoupled from the electromechanical stage.

The formulated approach discussed in previous sections leads to the POSFET equivalent macro-model shown in Fig. 4(a). The capacitors  $C_{PVDF}$  and  $C_{ox}$  can be written as the equivalent capacitor  $C_{stack}$ , defined as:

$$C_{Stack} = \frac{C_{PVDF}C_{OX}}{C_{PVDF} + C_{OX}} \tag{15}$$

On the application of force, the piezoelectric layer accumulates charge according to (3), which can be approximately written as:

$$Q = d_{33}F \tag{16}$$

The new dipoles will align according to the bias voltage polarity, resulting the creation of a potential ( $\varphi_{Force}$ ) which changes the effective gate voltage of the transistor, i.e.,

$$\varphi_{Force} = \frac{d_{33}F}{C_{PVDF}} \tag{17}$$

From (17) it is clear that the potential  $\varphi_{Force}$  can be modelled as a linear voltage-controlled voltage source, with

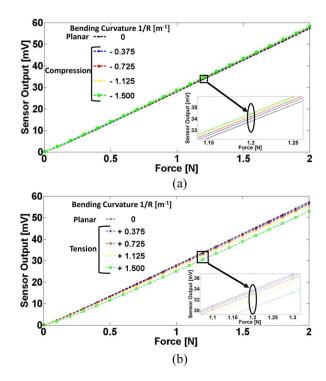

Fig. 5. Response of planar and strained POSFET to dynamic force using different (a) compressive and (b) tensile bending stresses.

its value depending both on the applied force and the capacitance  $C_{PVDF}$ .

The macro-model has been defined as two sub-circuit blocks presented in Fig. 4(b), showing the outer connections, where  $V_{bias}$ , G', G, D, B, S stand for the bias voltage applied to the top electrode, the connection towards the gate of the MOSFET, the gate, the drain, the bulk, and the source of the strained MOSFET, respectively. The terminal F stands for the independent applied force source, modelled by a voltage source connected to a dummy resistor. This voltage is used to control the potential  $\varphi_{Force}$  of the macro-model. The voltage difference created during this event is given by (17) and affects the gate voltage of transistor which can be written as:

$$V_{gs_{eff}} = V_{gs} + \frac{d_{33}F}{C_{pvdf}} \tag{18}$$

Assuming the device working in saturation region and when force is applied, the change in current can be written as:

$$\Delta I_{ds} = \mu_n C_{stack} \left(\frac{W}{2L}\right) \left(V_{gs_{eff}} - V_{th_{eff}}\right)^2 - \mu_n C_{stack} \left(\frac{W}{2L}\right) \left(V_{gs} - V_{th_{eff}}\right)^2$$

(19)

Due to change in the current, the output voltage of the device changes proportionally with the applied force, as is shown in Fig. 5.

As explained in Sec. II, the bending-induced stress in silicon chip changes the electronic transport properties, and the channel resistivity changes as well [38]. This is eventually reflected as a change in drain current. The threshold voltage changes proportionally with the applied stress and a gain of more than 50% in electron mobility can be expected in the

case of uniaxial stress applied to Si-crystal. In this work, compressive as well as tensile stress has been applied, which leads to an increase and decrease in the drain current of the transistor, respectively. This eventually shows up as an increase, or decrease, in the output voltage of the source follower configuration, as is shown in Fig. 5.

The change of the sensitivity of the stressed POSFET device varies between 1% and 7% with respect to its planar counterpart. This shows that bendability of sensors not only allow them to conform to the curved surfaces, but also improves their performance under appropriate conditions.

# V. TOWARDS STRESS-INDEPENDENT SENSING CIRCUITRY

Nullifying, or minimizing the mechanical stress effects on the active sensing devices and circuits requires an accurate and systematic simulation study. Stress affects the transistor's performance and consequently varies the output signals of the analog and digital circuit building blocks. Furthermore, in CMOS-compatible sensors, such as piezoelectric pressure, temperature, chemical/biological, or other sensors, stress introduces offsets that affect the sensitivity and detection of static and low frequency environment signals. In order to fabricate ICs that function within specifications, both planar as well as during mechanical deformation, the effects of stress must be considered in the design process. This section presents some techniques such as correlated double sampling (CDS) and chopper amplifier circuits to dynamically cancel the piezoresistive effects due to mechanical stress. These techniques help us obtain a stress-independent operation of sensor interface in bendable electronic systems.

Various applications have different set of requirements which lead to varied specifications. In some cases, the range of force experienced by the sensor is not defined and hence we need the sensor to maintain reliable functionality in a wide range of applied contact force. For this reason, in past we biased the POSFET device in common drain mode, popularly known as source follower configuration [14], [39]. The major advantages of this configuration are simplicity, stability and predictability with very high input impedance and low output impedance. In case of POSFETs, the gate is floating and the sensor is biased using constant current source. The force is applied using shaker which presses the sensor with sinusoidal varying signals [36]. Since the current is constant, the voltage at the source follows the input. Because of less than unity gain, the POSFET sensor could be used for wide force range.

However, when the sensor output voltage is restricted by the available voltage line, the range of applied force is limited. In other words, for limited voltage the sensitivity can be adjusted as per the desired force range. For example, in e-skin for robots the preferred range is set by the human daily sensing range (0.1-1 N) [10]. The output voltage produced for this range of force should be within the maximum voltage available from the supply over robot.

Considering these conditions, we have proposed a new operational amplifier circuit configuration where one of the differential pair transistors has been replaced with POSFET model in the positive input [40]. This nullifies the noise, common to both input transistors, and rescues the signal difference

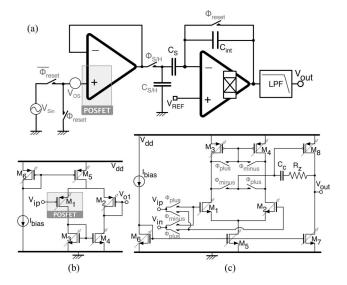

Fig. 6. (a) Block diagram of the proposed readout circuit for POSFETs. (b) Schematic diagram of the POSFET biasing as voltage follower, and (c) Schematic circuit diagram of two stage single-ended amplifier.

by directly measuring the input terminals. Using a differential pair configuration, we can also reduce the environmental noise entering at the output. Furthermore, the differential type amplifiers allow dynamic cancellation to reduce any change in response, due to the piezoresistive effect and circuit noises etc. using techniques, such as chopper stabilization and correlated double sampling [41].

Fig. 6(a) shows the simplified block diagram of the proposed microsystem. This scheme employs the bendable MOS transistors implemented by Verilog-A description using the parameters extracted from a standard 0.18- $\mu$ m CMOS technology. The transistor model predicts the performance of device under stress, and makes it easy to obtain bendable large-scale integrated circuit.

Based on the theoretical concepts and experimental results from literature related to the piezoresistive effect, and the observed behavior of the tested transistors, the drain current is modified due to mobility variation and threshold-voltage parameters in the BSIM4 model [19]. Two parameters are defined in the MOS models in order to perform simulations: the radius of curvature (R) from -1.5 to 1.5 m and the stress orientation ( $\theta$ ) between  $0^{\circ}$  and  $90^{\circ}$  versus wafer crystal direction. The thickness of wafer, h = 500  $\mu$ m, and the Young's modulus for silicon, E  $\cong$  169 GPa has been considered in model [42].

The proposed scheme utilizes the POSFET in a differential pair as a positive input transistor to configure a voltage follower, as shown in Fig. 6(b). In order to sense the applied force, the output voltage (V<sub>01</sub>), which is equal to the surface potential of the bottom electrode, is acquired. The circuit functions as follows: When the POSFET op-amp is configured as voltage follower, any difference in input stage gets amplified at the output. So whenever the sensor experiences some contact force stimulus (while the other transistor remains at fixed bias voltage) the amplified difference appears at the output. The entire readout employs the CDS technique to reduce the

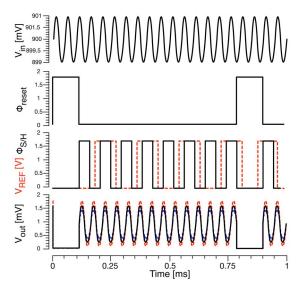

Fig. 7. Simplified timing diagram of a complete readout operation with transient response of output voltage. Black line shows the output voltage in planar state, where the red and blue dotted lines show the transient response under compression and tension, respectively.

amplifier's offset and noises due to piezo-resistive effects of uniaxial bending stress, as well as to lower the effect of the finite amplifier gain. A chopper amplifier is considered as a modulation approach to further cancel the input-referred noises including 1/f and offset [43]. Fig. 6(c) shows the two stage chopper amplifier with chopping frequency of 40 kHz, which has been employed in the integrator. In order to avoid output buffers, a switched-capacitor, used as low pass filter (LPF), has been used to drive the output pins [44].

The readout circuit has been designed in a standard 0.18- $\mu m$  CMOS technology. In this design, POSFET bias circuit is biased with external current source of value  $1\mu A$ , and chopper amplifier bias current is  $10~\mu A$  with 1.8~V. A sinusoid input signal with amplitude of 2mV corresponding to the applied force has been used on the top electrode of piezoelectric layer. On application of force, input at the POSFET terminal changes, which is then amplified by the circuit. This amplification can be tuned so that the output remains below the maximum voltage value.

Fig. 7 shows the timing diagram and waveforms of the input and output of the POSFET readout circuit. Resetting frequency and chopping clock frequency have been set to 1.25 kHz and 40 kHz, respectively.

The proposed circuit is also simulated under compression and tension by using the Verilog-A model for POSFET and MOS transistors. In this case study, we considered small bending curvature to introduce stress in the circuit. Simulation of the POSFET with readout circuit shows a maximum 12.5% increase in peak-to-peak voltage for compression (bending curvature =  $-1.5 \text{ m}^{-1}$ ) and a maximum 9% reduce in peak-to-peak voltage for tension (bending curvature =  $+1.5 \text{ m}^{-1}$ ).

# VI. CONCLUSION

With flexible electronics gaining interest, the need for highperformance has also gained prominence. In this regard, silicon based flexible electronics is being explored and the work presented here is one example. For designing of electronics on flexible silicon it is also important to advance the circuit design tools by developing new models. The investigations in this paper about response of POSFET devices in presence of stress is a step in that direction. The presented analytical and Verilog-A model have been used to fully characterize the device for electrical and mechanical responses for a wide range of applied forces, showing a variation in the sensitivity of the stressed POSFET device between 1% and 7% with respect to its planar counterpart. Further, the effects of stress on the readout circuit have been analyzed and techniques to dynamically minimize the piezo-resistive effect due to mechanical stress have been presented. In the simulations, different radii of curvature and stress orientations have been used, showing a maximum increase of 12.5% in peak-to-peak voltage for compressive stress, and a maximum decrease of 9% in peak-to-peak voltage for tensile stress. Future work will be focused on the investigation of the response of the readout circuit using different stresses at different MOS models of the circuit, introducing also the effects of bending in the electromechanical stage of the Verilog-A POSFET macromodel.

### REFERENCES

- S. Khan, L. Lorenzelli, and R. S. Dahiya, "Technologies for printing sensors and electronics over large flexible substrates: A review," *IEEE Sensors J.*, vol. 15, no. 6, pp. 3164–3185, Jun. 2015.

- [2] M. Singh, H. M. Haverinen, P. Dhagat, and G. E. Jabbour, "Inkjet printing—Process and its applications," *Adv. Mater.*, vol. 22, no. 6, pp. 673–685, 2010.

- [3] S. Dasgupta, R. Kruk, N. Mechau, and H. Hahn, "Inkjet printed, high mobility inorganic-oxide field effect transistors processed at room temperature," ACS Nano, vol. 5, no. 12, pp. 9628–9638, 2011.

- [4] R. R. Søndergaard, M. Hösel, and F. C. Krebs, "Roll-to-roll fabrication of large area functional organic materials," *J. Polymer Sci. B, Polymer Phys.*, vol. 51, no. 1, pp. 16–34, 2013.

- [5] S. Khan, N. Yogeswaran, W. Taube, L. Lorenzelli, and R. Dahiya, "Flexible FETs using ultrathin Si microwires embedded in solution processed dielectric and metal layers," *J. Micromech. Microeng.*, vol. 25, no. 12, p. 125019, 2015.

- [6] Y. Yuan et al., "Ultra-high mobility transparent organic thin film transistors grown by an off-centre spin-coating method," Nature Commun., vol. 5, Jan. 2014, Art. no. 3005.

- [7] R. S. Dahiya, P. Mittendorfer, M. Valle, G. Cheng, and V. J. Lumelsky, "Directions toward effective utilization of tactile skin: A review," *IEEE Sensors J.*, vol. 13, no. 11, pp. 4121–4138, Nov. 2013.

- [8] R. Dahiya, G. Metta, M. Valle, and G. Sandini, "Tactile sensing—From humans to humanoids," *IEEE Trans. Robot.*, vol. 26, no. 1, pp. 1–20, Feb. 2010.

- [9] R. S. Dahiya and S. Gennaro, "Bendable ultra-thin chips on flexible foils," *IEEE Sensors J.*, vol. 13, no. 10, pp. 4030–4037, Oct. 2013.

- [10] R. Dahiya and M. Valle, Robotic Tactile Sensing Technologies and System. New York, NY, USA: Springer, 2013.

- [11] K. Balasundaram et al., "Porosity control in metal-assisted chemical etching of degenerately doped silicon nanowires," Nanotechnology, vol. 23, no. 30, p. 305304, Aug. 2012, doi: 10.1088/0957-4484/23/30/305304.

- [12] J. N. Burghartz, W. Appel, C. Harendt, H. Rempp, H. Richter, and M. Zimmermann, "Ultra-thin chip technology and applications, a new paradigm in silicon technology," *Solid-State Electron.*, vol. 54, no. 9, pp. 818–829, 2010.

- [13] R. S. Dahiya et al., "Towards tactile sensing system on chip for robotic applications," *IEEE Sensors J.*, vol. 11, no. 12, pp. 3216–3226, Dec. 2011.

- [14] R. S. Dahiya, A. Adami, L. Pinna, C. Collini, M. Valle, and L. Lorenzelli, "Tactile sensing chips with POSFET array and integrated interface electronics," *IEEE Sensors J.*, vol. 14, no. 10, pp. 3448–3457, Oct. 2014.

- [15] H. Heidari, E. Bonizzoni, U. Gatti, F. Maloberti, and R. Dahiya, "CMOS vertical Hall magnetic sensors on flexible substrate," *IEEE Sensors J.*, to be published.

- [16] H. Heidari, N. Wacker, S. Roy, and R. Dahiya, "Towards bendable CMOS magnetic sensors," in *Proc. IEEE Ph.D. Res. Microelec*tron. Electron., Jun./Jul. 2015, pp. 314–317.

- [17] H. M. Nayfeh, J. L. Hoyt, and D. A. Antoniadis, "A physically based analytical model for the threshold voltage of strained-Si n-MOSFETs," *IEEE Trans. Electron Devices*, vol. 51, no. 12, pp. 2069–2072, Dec. 2004.

- [18] Y. Tan, X. Li, L. Tian, and Z. Yu, "Analytical electron-mobility model for arbitrarily stressed silicon," *IEEE Trans. Electron Devices*, vol. 55, no. 6, pp. 1386–1390, Jun. 2008.

- [19] H. Heidari, W. T. Navaraj, G. Toldi, and R. Dahiya, "Device modelling of bendable MOS transistors," in *Proc. IEEE Int. Symp. Circuits Syst. (ISCAS)*, Montreal, QC, Canada, May 2016, pp. 1358–1361.

- [20] S. Gupta, H. Heidari, L. Lorenzelli, and R. Dahiya, "Towards bendable piezoelectric oxide semiconductor field effect transistor based touch sensor," in *Proc. IEEE Int. Symp. Circuits Syst.*, May 2016, pp. 345–348.

- [21] G. C. Dogiamis, B. J. Hosticka, and A. Grabmaier, "Investigations on an ultra-thin bendable monolithic Si CMOS image sensor," *IEEE Sensors J.*, vol. 13, no. 10, pp. 3892–3900, Oct. 2013.

- [22] Y. Sun, S. Thompson, and T. Nishida, "Physics of strain effects in semiconductors and metal-oxide-semiconductor field-effect transistors," *J. Appl. Phys.*, vol. 101, no. 10, p. 104503, 2007.

- [23] Z. Z. Wang, J. Suski, and D. Collard, "Piezoresistive simulation in MOSFETs," Sens. Actuators A, Phys., vols. 37–38, pp. 357–364, Aug. 1993.

- [24] T. Irisawa et al., "Electron mobility and short-channel device characteristics of SOI FinFETs with uniaxially strained (110) channels," IEEE Trans. Electron Devices, vol. 56, no. 8, pp. 1651–1658, Aug. 2009.

- [25] H. Alius, H. Rempp, Z. Yu, and T. Gneiting, "A new MOSFET model for the simulation of circuits under mechanical stress," in *Proc. MOS-AK Workshop*, London, U.K., 2014.

- [26] S. Dhar, H. Kosina, V. Palankovski, S. E. Ungersboeck, and S. Selberherr, "Electron mobility model for strained-Si devices," *IEEE Trans. Electron Devices*, vol. 52, no. 4, pp. 527–533, Apr. 2005.

- [27] M. V. Dunga et al., "BSIM4. 6.0 MOSFET model," 2006.

- [28] H. Richter et al., "Technology and design aspects of ultra-thin silicon chips for bendable electronics," in Proc. IEEE Int. Conf. IC Design Technol., May 2009, pp. 149–154.

- [29] T. Sekitani, U. Zschieschang, H. Klauk, and T. Someya, "Flexible organic transistors and circuits with extreme bending stability," *Nature Mater.*, vol. 9, pp. 1015–1022, Nov. 2010.

- [30] R. Dahiya, W. T. Navaraj, S. Khan, and E. O. Polat, "Developing electronic skin with the sense of touch," *Inf. Display*, pp. 2–6, 2015.

- [31] R. Dahiya, A. Adami, C. Collini, and L. Lorenzelli, "POSFET tactile sensing arrays using CMOS technology," Sens. Actuators A, Phys., vol. 202, pp. 226–232, Nov. 2013.

- [32] H. Ishiwara, "Ferroelectric random access memories," J. Nanosci. Nanotechnol., vol. 12, pp. 7619–7627, Oct. 2012.

- [33] R. S. Dahiya, M. Valle, and L. Lorenzelli, "SPICE model for lossy piezoelectric polymers," *IEEE Trans. Ultrason., Ferroelect., Freq. Con*trol, vol. 56, no. 2, pp. 387–395, Feb. 2009.

- [34] B. Ploss, "Dielectric nonlinearity of PVDF-TrFE copolymer," *Polymer*, vol. 41, no. 16, pp. 6087–6093, 2000.

- [35] J. Li, C. Wang, W. Zhong, and P. Zhang, "Geometry and electronic structure of PVDF/TrFE copolymer," Synth. Met., vol. 135, pp. 471–472, Apr. 2003.

- [36] R. Dahiya, G. Metta, M. Valle, A. Adami, and L. Lorenzelli, "Piezoelectric oxide semiconductor field effect transistor touch sensing devices," Appl. Phys. Lett., vol. 95, no. 3, p. 034105, 2009.

- [37] S. L. Miller, R. D. Nasby, J. R. Schwank, M. S. Rodgers, and P. V. Dressendorfer, "Device modeling of ferroelectric capacitors," *J. Appl. Phys.*, vol. 68, no. 12, p. 6463, 1990.

- [38] J. L. Ma, Z. F. Fu, Q. Wei, and H. M. Zhang, "Uniaxial stress induced electron mobility enhancement in silicon," *Silicon*, vol. 5, no. 3, pp. 219–224, 2013.

- [39] L. Barboni, R. S. Dahiya, G. Metta, and M. Valle, "Interface electronics design for POSFET devices based tactile sensing systems," in *Proc. IEEE RO-MAN Conf.*, Sep. 2010, pp. 686–690.

- [40] S.-J. Kim and E. Yoon, "Label-free CMOS bio sensor with on-chip noise reduction scheme for real-time quantitative monitoring of biomolecules," *IEEE Trans. Biomed. Circuits Syst.*, vol. 6, no. 3, pp. 189–196, Jun. 2012.

- [41] M. Belloni, E. Bonizzoni, A. Fornasari, and F. Maloberti, "A micropower chopper—CDS operational amplifier," *IEEE J. Solid-State Circuits*, vol. 45, no. 12, pp. 2521–2529, Dec. 2010.

- [42] N. Wacker, H. Richter, M.-U. Hassan, H. Rempp, and J. N. Burghartz, "Compact modeling of CMOS transistors under variable uniaxial stress," *Solid-State Electron.*, vol. 57, no. 1, pp. 52–60, 2011.

- [43] H. Heidari, E. Bonizzoni, U. Gatti, and F. Maloberti, "A current-mode CMOS integrated microsystem for current spinning magnetic Hall sensors," in *Proc. IEEE Int. Symp. Circuits Syst.*, Jun. 2014, pp. 678–681.

- [44] H. Heidari, E. Bonizzoni, U. Gatti, and F. Maloberti, "A CMOS current-mode magnetic Hall sensor with integrated front-end," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 62, no. 5, pp. 1270–1278, May 2015.

University of Glasgow.

Shoubhik Gupta (S'15) received the B.Tech (Electrical) degree from Indian Institute of Technology Kanpur. Currently he is working toward the Ph.D. degree in BEST group, School of Engineering at University of Glasgow, U.K. His research focus is on ultra-thin chips and their application in flexible electronics, especially e-skin. He has been a recipient of the Marie Curie fellowship from European Commission, Nano-Undergraduate Research Fellowship from University of Notre Dame, USA, and Principle Early Career Mobility Scholarship from

Hadi Heidari received the Ph.D. degree in microelectronics from the University of Pavia, Italy. He is a Lecturer with the joint school of University of Glasgow, U.K., and UESTC, China. Prior to this, he was a postdoctoral researcher in the BEST group in School of Engineering, University of Glasgow, U.K. Between 2008 and 2011, he was with Hamrah-e-Avval, Iran, and Azad University, Iran. His research is focused on device modelling, CMOS sensors, sensor interfaces, and ultra-thin chips.

Dr. Heidari is social media chair of IEEE Sensors 2016, and publicity chair of IEEE Sensors 2017. He is IEEE Sensors Council Young Professional reprehensive, and a committee member of the IEEE Sensors Council UKRI Chapter. He received honorary mention paper award at the IEEE ISCAS 2014, Gold Leaf award at IEEE PRIME 2014, and was corecipient of ISSCC 2016 Silk Road Award.

Anastasios Vilouras (S'16) received the B.Sc. degree in physics from Aristotle University of Thessaloniki, Greece, and the M.Sc. degree on bioelectronics and biosensors from University of Edinburgh, U.K. He is part of the Centre for Doctoral Training in Integrative Sensing and Measurement (CDT-ISM) of University of Glasgow, U.K., where he is currently working towards his Ph.D. degree in Bendable Electronics and Sensing Technologies (BEST) group focusing mainly on CMOS-based bendable ion sensors for chemical

and bio-chemical measurements.

Leandro Lorenzelli received the Laurea degree in electronic engineering from the University of Genoa, Genoa, Italy, in 1994, and the Ph.D. degree in electronics materials and technologies from the University of Trento, Trento, Italy, in 1998. During the Ph.D. course, his research activity concerned the development of electrochemical CMOS-based microsensors. In 1998, he joined the staff of the ITC-IRSTMicrosystems Division, Trento, and was involved in the realization of microsystems for biomedical, environmental, and agro-food applications.

Since 2005, he has been responsible for the Microsystems Technology Research Unit, Fondazione Bruno Kessler, Trento. His main scientific interests are in the processing technologies for both bio-microelectromechanical system and micro-transducers.

Ravinder Dahiya (S'05–M'09–SM'12) received the Ph.D. degree from the Italian Institute of Technology, Genoa, Italy. He is Reader and EPSRC Fellow in School of Engineering at University of Glasgow, Italy K

His multidisciplinary research interests include Flexible and Printable Electronics, Electronic Skin, Tactile Sensing, Robotics, and Wearable Electronics. He has published more than 150 research articles, 3 books (including 2 at various stages of publication), and 9 patents (including 7 submitted). He has led

many international projects funded by European Commission, EPSRC, the Royal Society, and the Royal Academy of Engineering.

He is Distinguished Lecturer of IEEE Sensors Council (2016–2018). Currently he serves on the Editorial Boards of IEEE TRANSACTIONS ON ROBOTICS and IEEE SENSORS JOURNAL and has been guest editor of 4 Special Journal Issues. He is founding chair of the IEEE UKRI sensors council chapter. He was General Chair of IEEE PRIME 2015 and is the Technical Program Chair (TPC) of IEEE Sensors 2017. He holds prestigious EPSRC Fellowship and received in past the Marie Curie Fellowship and Japanese Monbusho Fellowship. He received 2016 Technical Achievement Award from IEEE Sensors Council, International Association of Advanced Materials Medal for the year 2016, and the 2016 Microelectronic Engineering Young Investigator Award. In 2016, he was included in the list of Scottish 40UNDER40. He received best paper awards 2 times and another 2 second best paper awards as coauthor in international conferences.