# Frequency-Domain Analysis of Reconfigured Incremental $\Delta\Sigma$ ADCs on the Example of the Exponential Phase

Paul Kaesser<sup>®</sup>, Graduate Student Member, IEEE, Omar Ismail<sup>®</sup>, Graduate Student Member, IEEE, Johannes Wagner<sup>®</sup>, Member, IEEE, Robert F. H. Fischer<sup>®</sup>, Senior Member, IEEE, and Maurits Ortmanns<sup>®</sup>, Senior Member, IEEE

*Abstract*— In this paper, analysis of linear time-variant systems is applied to incremental Delta-Sigma (I-DS) ADCs with periodic architectural reconfiguration in the frequency domain. The analysis will then be applied to the example of linear-exponential I-DS ADCs as a state-of-the-art dynamic reconfiguration technique. It is shown how a matched reconstruction filter of the reconfigured linear-exponential incremental Delta-Sigma modulator (I-DSM) can be mathematically derived. Using the calculated overall transfer functions of the linear-exponential I-DS ADC, accurate performance predictions can be given. The proposed method allows the accurate prediction of performances and gives insight and understanding of the performance improvements and trade-offs achieved by reconfiguration techniques in I-DS ADCs in general and the exponential phase in particular.

*Index Terms*—Incremental, delta-sigma, transfer function, reconfiguration, linear-exponential, frequency domain, exponential phase.

#### I. INTRODUCTION

THE advances in CMOS scaling over the past decades have significantly improved digital circuits, leading to efficient signal processing in the digital domain. However, this shift has increased the demand for high-performance analog-todigital converters (ADCs), which are essential for meeting the speed and power requirements of modern signal processing. The traditional Delta-Sigma (DS) ADC, which is based on oversampling and noise shaping and trades circuit precision for time, is commonly used in this trend [1]. However, its averaging behavior makes it unsuitable for applications that require sample-to-sample conversion. One solution to this drawback is the incremental Delta-Sigma (I-DS) ADC, which offers the benefits of Nyquist-rate behavior by applying a periodic reset [2].

Manuscript received 26 April 2023; revised 3 August 2023; accepted 29 August 2023. Date of publication 13 September 2023; date of current version 26 October 2023. This work was supported by the German Research Foundation under DFG Grant OR 245/10-3. This article was recommended by Associate Editor H. Zhang. (*Corresponding author: Paul Kaesser.*)

Paul Kaesser, Omar Ismail, Johannes Wagner, and Maurits Ortmanns are with the Institute of Microelectronics, University of Ulm, 89081 Ulm, Germany (e-mail: paul.kaesser@uni-ulm.de).

Robert F. H. Fischer is with the Institute of Communications Engineering, University of Ulm, 89081 Ulm, Germany.

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TCSI.2023.3310655.

Digital Object Identifier 10.1109/TCSI.2023.3310655

The I-DS ADC shares the principles of oversampling and noise-shaping with free-running DS ADCs, but its behavior differs significantly. This is because of the periodic reset, which requires the modeling of the I-DS ADC as a linear timevariant (LTV) system, rather than as a linear time-invariant (LTI) system. In order to account for this, in most prior art [1], [3], [4] it was exclusively analysed in the time domain. A frequency-domain description has been elaborated for I-DS ADCs in [5] and [6], which regards the incremental Delta-Sigma modulator (I-DSM) as a finite impulse response filter, and allows to derive an overall STF and NTF. Thereby, the effect of discarding an input sample and hold (S/H) on the signal filtering property was implicitly described. Furthermore, it was analyzed how the folding of higher Nyquist zones leads to aliasing of signal and quantization noise. Finally, the method allows to precisely predict the performance of I-DS ADCs with respect to the employed reconstruction filter.

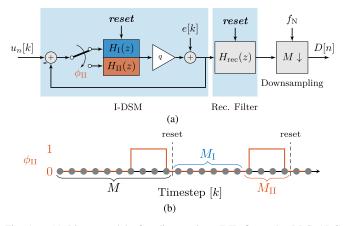

Recent research has aimed to overcome the lesser performance offered by I-DS ADCs in comparison to its freerunning counterparts. Several techniques have been proposed to address these shortcomings, exploiting the finite number of operating cycles of I-DS ADCs. As a result, dynamic reconfiguration of the architecture has been proposed as a solution. The general idea of architectural reconfiguration is visualized in Figure 1a, where the modulators' loop filter is (e.g. periodically) switched between two different filters,  $H_{I}(z)$ and  $H_{\text{II}}(z)$ . Reconfiguration of loop-filter non-idealities and internal bitwidth have been shown [7], [8], where intrinsically linear low resolution operation is alternated with high resolution operation within every conversion cycle. A deactivation of the input signal as recuperation phase (RP) towards the end of a conversion cycle was introduced in [9] resulting in a improved maximum stable amplitude (MSA) and signalto-quantization-noise ratio (SQNR). Another reconfiguration technique - the linear-exponential operation of I-DS ADC - was introduced by [10], who proposed to switch the modulator from a 1st order linear to an exponential I-DS ADC towards the end of each Nyquist conversion cycle. Because of the exponential feedback of the quantization error towards the end of each conversion cycle, a boost of the SQNR was achieved [10]. Even though the operation was described in the time domain, and its impact both simulated

© 2023 The Authors. This work is licensed under a Creative Commons Attribution 4.0 License. For more information, see https://creativecommons.org/licenses/by/4.0/

Fig. 1. (a) Linear model of a discrete-time (DT) first-order I-DS ADC switching between the two loop filter functions  $H_{\rm I}(z)$  and  $H_{\rm II}(z)$  and (b) its timing diagram including the reset and the reconfiguration signal.

and measured, performance prediction by applying the concept of frequency-domain description, deriving the overall transfer function of the I-DSM due to the linear-exponential reconfiguration, and thereby the gain of a deeper understanding of the operation of the exponential phase is still missing in the state of the art (SoA).

This manuscript closes this gap by calculating the transfer functions of a reconfigurable I-DS ADC and proving its practicability by applying frequency-domain analysis to the time-variant linear-exponential reconfiguration. Furthermore, it is shown how to calculate a matched reconstruction filter to optimally fit the reconfigured linear-exponential I-DS ADC.

The paper is organized as follows: Section II shortly reviews I-DS ADC operation and frequency-domain analysis. Section III introduces the calculation of transfer functions for reconfigurable I-DS ADCs. Section IV reviews the concept of the linear-exponential I-DS ADC, and introduces the calculation of its matched reconstruction filter and transfer functions. Section V extends the frequency-domain analysis to account for quantization and thermal noise in the presence of varying exponential phase parameters. Section VI gives a conclusion.

#### II. OVERVIEW ON I-DS ADCs

# A. Working Principle of I-DS ADCs

The linearized block diagram of a discrete-time (DT) I-DS ADC is shown in Figure 1a, featuring the I-DSM, the digital reconstruction filter and the periodically applied reset to both. Between two resets the I-DS ADC operates for a defined number of M samples. By assuming an infinitely small reset length, M corresponds to the oversampling ratio (OSR) of a free-running Delta-Sigma modulator (DSM), and one Nyquist cycle ends after M clock cycles. In contrast to free-running DSM, where the decimation filter is usually assumed an ideal brickwall filter, the performance analysis of I-DS ADCs has to take the modulator, the digital reconstruction filter and the periodic reset into account.

# B. Overall Transfer Functions in I-DS ADCs

Through most SoA I-DS ADC were analyzed and described in the time domain [1], [3], [4], which lacked accuracy in performance prediction. Due to the applied reset in I-DS ADCs, they behave like time-variant systems. Therefore, it was proposed to model the I-DS ADCs as FIR filter, which allows to consider the time-variant system as LTI system between two reset signals for a finite number of samples M. This FIR filter model was initially used for time-domain analysis [11], and later considered for a frequency-domain analysis for a first order DT I-DSM [12] or arbitrary DT or continuous-time (CT) I-DSM [5]. As we largely rely on the theory of this, the idea is shortly reviewed. For simplicity and readability a normalized sampling frequency  $f_s = 1$  is assumed in all succeeding equations. The overall STF or NTF of a freerunning DT DS ADC, are

$$TF_{\text{free}}(z) = TF_{\text{m}}(z) \cdot H_{\text{rec}}(z)$$

(1)

with  $TF_m(z)$  being either the signal transfer function (STF) or noise transfer function (NTF) of the free-running modulator and  $H_{rec}(z)$  being the transfer function of the free-running reconstruction/decimation filter. By multiplying a rectangular window rect<sub>M</sub> [k] in the time domain, which models the reset, it is possible to calculate the transfer functions of the I-DS ADC. The multiplication of rect<sub>M</sub> [k] corresponds to a circular convolution in the frequency domain with its discrete-time Fourier transform (DTFT):

$$TF_{\text{incr}}(f) = TF_{\text{free}}(e^{j2\pi f}) \circledast X_{\text{rect},M}(f)$$

(2)

with  $TF_{incr}(f)$  being either  $STF_{incr}(f)$  or  $NTF_{incr}(f)$  of the I-DS ADC and

$$X_{\text{rect},M}(f) = DTFT\{\text{rect}_M[k]\}$$

(3)

$$= \frac{\sin\left(M\pi f\right)}{\sin\left(\pi f\right)} \cdot e^{-j\pi f \cdot (M-1)}.$$

(4)

As decimating causes a folding back of all higher Nyquist zones into the in-band, it is possible to predict the in-band noise at the decimated output by integrating the overall  $NTF_{incr}(f)$  from 0 to  $f_S/2$ . By omitting an input S/H, the overall  $STF_{incr}(f)$  shows the attenuation of input signals in higher Nyquist zones, before they are aliased back into the in-band of the decimated output.

## III. TRANSFER FUNCTION CALCULATION OF RECONFIGURED I-DS ADCS

Recently, several approaches have been presented [7], [9], [10] to further improve the performance of I-DS ADCs by periodically reconfiguring its architecture during every Nyquist conversion cycle. This reconfiguration basically causes a change of the systems transfer functions during one conversion cycle; therefore, the system can not be described as LTI system between two resets anymore. This is illustrated in Figure 1a, where the loop filter transfer function changes after  $M_{\rm I}$  samples from  $H_{\rm I}(z)$  to  $H_{\rm II}(z)$  for the remaining  $M_{\rm II}$  samples. The according timing diagram is shown in Figure 1b. In the following, an approach is presented to calculate the transfer functions of reconfigured I-DS ADCs as LTV system.

In general, LTI systems like free-running or usual I-DS ADCs, can be fully characterized by only one impulse

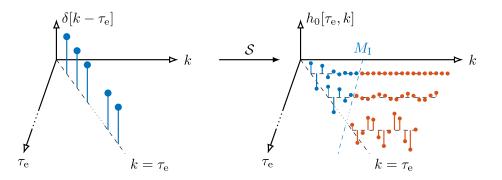

Fig. 2. Time-variant impulse response illustrated for some exemplary excitement time steps. LTV system is reconfigured after  $M_I$  time steps.

response. In reconfigured systems this is not possible anymore since the impulse response changes over time and therefore depends on the time of excitement  $\tau_e$ . A (deterministic) LTV system is only fully characterized if the reactions of the system to discrete-time unit pulses at all excitation times

$$\tau_{\rm e} \quad \forall \tau_{\rm e} \in \mathbb{Z} \tag{5}$$

are known [13]. The time-variant impulse response  $h_0[\tau_e, k]$  of an LTV system S, which is dependent on the parameters 1) observation time k and 2) time of excitement  $\tau_e$ , is then defined as

$$h_0[\tau_{\rm e},k] \stackrel{\rm der}{=} \mathcal{S}\left\{\delta\left[k-\tau_{\rm e}\right]\right\}.$$

(6)

Figure 2 gives a visualization of the excitement at  $k = \tau_e$  and the reactions (exemplary impulse responses) assuming a causal system. Every unit impulse with a different time of excitement of the left side corresponds with an impulse response on the right side after it is applied to the LTV system. It is important to notice that depending on the time of excitement  $\tau_e$  the impulse response of the LTV system can be different. The impulse responses in Figure 2 relate to the LTV system of Figure 1, where the first LTI system is switched to a second one after  $M_{\rm I}$  timesteps resulting in an LTV system. Every unit impulse with a time of excitement before  $M_{\rm I}$  corresponds at the beginning with the impulse response of the first system until the reconfiguration is happening. Afterwards the second system is excited by the set of internal states at the time of reconfiguration. This may lead to a different impulse response for each  $\tau_e$  before  $M_I$ . For each excitement after  $M_I$  the impulse response corresponds to the impulse response of the second system.

In case of a reconfigured I-DS ADC with oversampling M,  $h_0[\tau_e, k]$  in (6) is a matrix with dimensions  $M \times M$ , representing the impulse responses of the I-DS ADC to every possible time of excitement  $\tau_e \in [1, M]$  and time of observation  $k \in [1, M]$ .

In order to calculate each impulse response, it is necessary to know the internal states of the I-DSM during the reconfiguration process. Therefore, it is required to calculate the internal states of the first system to a Dirac excitement for  $M_{\rm I}$ steps. This can be done in time domain using the state space

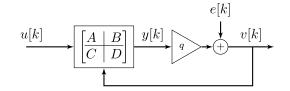

Fig. 3. State space representation of a Sigma-Delta modulator (SDM).

representation

$$x[k+1] = A x[k] + B \begin{bmatrix} u[k] \\ v[k] \end{bmatrix}$$

$$y[k] = C x[k] + D \begin{bmatrix} u[k] \\ v[k] \end{bmatrix}$$

(7)

of the modulator. Thereby, the modulator is described in time domain using the ABCD matrix instead of the loop filter transfer function. The state space representation of a DSM is illustrated in Figure 3 [1]. The state space representation can be used to represent both, a DSM and an I-DSM, with the only difference being that for the I-DSM the states are reset after every *M*-th sample.

In order to calculate the overall impulse response matrix of the I-DS ADC  $h_0[\tau_e, k]$  it is necessary to derive the impulse response matrix of the incremental modulator  $h_{0,m}[\tau_e, k]$ , excluding the reconstruction filter, at first. Therefore, the state space representation  $ABCD_I$  of the first and  $ABCD_{II}$  of the second system reconfiguration is required. This enables the computation of the impulse responses for every time of excitation  $\tau_e$ . Before the point of reconfiguration the impulse response corresponds to the impulse response of the first system  $h_I[k]$

$$h_{0,\mathrm{m}}[\tau_{\mathrm{e}}, k + \tau_{\mathrm{e}} - 1] = h_{\mathrm{I}}[k] \begin{cases} \tau_{\mathrm{e}} \in [1, M_{\mathrm{I}}] \\ k \in [1, M_{\mathrm{I}} - \tau_{\mathrm{e}} + 1]. \end{cases}$$

(8)

Since only causal systems are considered, all values of  $h_{0,m}$  before the time of excitation  $\tau_e$  have to be 0. This leads to the observation time index  $k + \tau_e - 1$ , where  $h_I[k]$  is inserted in  $h_{0,m}$ .

At the point of reconfiguration, the initial states of the second system have to be set according to the final states of the first system at this sampling point

$$x_{\rm II}[1] = x_{\rm I}[M_{\rm I} - \tau_{\rm e} + 2].$$

(9)

Then, the further points of the impulse response can be calculated using the state space representation of the second system  $ABCD_{II}$

$$x_{\Pi}[k+1] = A_{\Pi} x_{\Pi}[k] + B_{\Pi} \begin{bmatrix} u[k] \\ v[k] \end{bmatrix}$$

$$y_{\Pi}[k] = C_{\Pi} x_{\Pi}[k] + D_{\Pi} \begin{bmatrix} u[k] \\ v[k] \end{bmatrix}$$

$$v_{\Pi}[k] = q \cdot y_{\Pi}[k] \quad k \in [1, M_{\Pi}]$$

(10)

leading to

$$h_{0,\mathrm{m}}[\tau_{\mathrm{e}}, k + \tau_{\mathrm{e}} - 1] = v_{\mathrm{II}}[k] \begin{cases} \tau_{\mathrm{e}} \in [1, M_{\mathrm{I}}] \\ k \in [M_{\mathrm{I}} - \tau_{\mathrm{e}} + 2, M_{\mathrm{II}}]. \end{cases}$$

(11)

For every excitation point, which comes later in time than the reconfiguration point, the impulse response only depends on the second system and can therefore be calculated from the impulse response of the second system  $h_{II}[k]$ .

$$h_{0,\mathrm{m}}[\tau_{\mathrm{e}}, k + \tau_{\mathrm{e}} - 1] = h_{\mathrm{H}}[k] \begin{cases} \tau_{\mathrm{e}} \in [M_{\mathrm{I}} + 1, M] \\ k \in [1, M - \tau_{\mathrm{e}} + 1] \end{cases}$$

(12)

The according algorithm to calculate  $h_{0,m}[\tau_e, k]$  can be found in the Appendix.

After  $h_{0,m}[\tau_e, k]$  of the time-reconfigurable I-DSM is derived, the time-invariant reconstruction filter can be included by performing a circular convolution of the impulse response of the reconstruction filter  $h_{rec}[k]$  with  $h_{0,m}[\tau_e, k]$  for every excitation point  $\tau_e$ . The calculated matrix

$$h_0[\tau_{\rm e}, k] = h_{0,\rm m}[\tau_{\rm e}, k] \circledast h_{\rm rec}[k]$$

(13)

now fully characterizes the reconfigured I-DS ADC. Note that the DTFT of (13) over the observation time k would yield the delay Doppler-spread function, while the DTFT over the time of excitement  $\tau_e$  actually yields the required time-variant transfer function  $TF_{incr}(f)$  [13]. It is important to note here, that the transfer function depends on the time of observation k and therefore differs for different time of observations. So far, the reconfigured ADC is still described by M different transfer functions depending on the time of observation. Since decimation is applied in an I-DS ADC the only transfer function of concern to describe the I-DS ADC is the one where the observation time is set to k = M. This yields the impulse response vector

$$h[\tau_{\rm e}] = h_0 \left[\tau_{\rm e}, M\right] \tag{14}$$

and the resulting transfer function can be derived by doing the DTFT

$$TF_{\text{incr}}(f) = \mathcal{F}\{h[\tau_e]\}.$$

(15)

Please note here, that although the final impulse response  $h[\tau_e]$ , which characterizes the decimated I-DS ADC, is a Mx1 Matrix, it is absolutely vital to derive the MxM matrix  $h_0[\tau_e, k]$  first. Only the MxM matrix  $h_0[\tau_e, k]$  is able to fully describe the undecimated I-DS ADC and allows to include the reconstruction filter.

The derived analysis can be applied to any reconfiguration of I-DS ADC, which is periodically applied within every Nyquist-conversion cycle. To prove its practical applicability, the method is next used to analyze a reconfigurable, namely the linear-exponential (LE), I-DS ADC [10].

# IV. TRANSFER FUNCTIONS OF THE LINEAR-EXPONENTIAL I-DS ADC

#### A. Linear-Exponential Working Principle

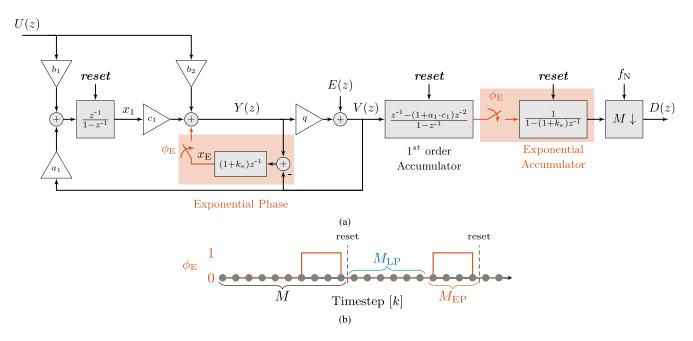

The linear-exponential (LE) I-DS ADC described in [10] consists of a first-order DT modulator that reconfigures the loop filter into an exponential phase (EP) towards the end of each conversion cycle. The proposed architecture of the LE I-DS and its timing diagram are shown in Figure 4: During the linear phase, it is a simple first-order discrete-time I-DSM using multi-bit quantization and a first-order COI reconstruction filter. After  $M_{LP}$  samples the exponential phase is turned on, where an additional feedback path in the modulator is enabled, which feeds the quantization noise back to the quantizer input and features an exponential gain  $(1+k_E)$ . The summation of the error feedback can e.g. be realized by an active amplifier as used in [10]. This reconfiguration leads to a change of the modulators' loop filter transfer function from

$$H_{\rm L}(z) = \frac{z^{-1}}{1 - z^{-1}} \tag{16}$$

to

$$H_{\rm E}(z) = \frac{z^{-1}}{1 - z^{-1}} \cdot \frac{1}{1 - (1 + k_{\rm E})z^{-1}} \tag{17}$$

for the last  $M_{\rm EP}$  samples of each conversion cycle.

#### B. Linear-Exponential Reconstruction Filter

The digital reconstruction filter for the linear-exponential I-DS ADC of [10] was implemented in a way that it matches the structure of the analog modulator, similar to [14], but it was only shown for a specific set of coefficients. It basically consists of a first-order accumulator and an exponential accumulator which is switched on for the samples in the exponential phase. The reconstruction filter shown in Figure 4 is derived as a generalized version of [10], as it works for any set of coefficients scaling coefficients of the I-DSM. For  $a_1 = -1$  and  $c_1 = 1$  it matches the filter of [10].

Apart from its actual time-variant implementation in Figure 4, the digital reconstruction filter can be written as a time-invariant finite impulse response (FIR) filter, since there is no feedback path in the reconstruction filter. In [10], the FIR coefficients have again been shown for a specific set of coefficients; in the following the FIR filter coefficients for the LE reconstruction filter are generally derived in order to make the subsequent analysis reproducible to the reader.

The digital reconstruction filter can be chosen to match the analog I-DSM by choosing its transfer function to  $1/NTF_m$ , where  $NTF_m$  is the free-running NTF of the analog loopfilter (LF) [1]. Assuming q = 1, which is usually the case for a

Fig. 4. (a) Model of the two-phase linear-exponential I-DS ADC and (b) its timing diagram including the reset and the exponential phase signal [10].

multi-bit quantizer, the analog modulators' NTF of the linear phase is

$$NTF_{\rm m,L}(z) = \frac{1 - z^{-1}}{1 - a_1 c_1 z^{-1}}$$

(18)

and

$$NTF_{\rm m,E}(z) = NTF_{\rm m,L}(z) \cdot (1 - (1 + k_{\rm E})z^{-1})$$

(19)

of the exponential phase. This leads to the matched reconstruction filters

$$H_{\rm rec,L}(z) = \frac{1 - a_1 c_1 z^{-1}}{1 - z^{-1}}$$

(20)

and

$$H_{\rm rec,E}(z) = H_{\rm rec,L}(z) \cdot \frac{1}{1 - (1 + k_{\rm E})z^{-1}}.$$

(21)

To derive the FIR filter weights for this reconstruction filter over the operating time span  $k \in [1, M]$ , we first take the impulse response for the linear phase

$$h_{\text{rec},L}[k] = \mathcal{Z}^{-1}\{H_{\text{rec},L}(z)\} \ k \in [1, M]$$

(22)

for *M* samples. To account for the exponential phase,  $h_{\text{rec},L}[k]$  has to be combined with the  $M_{\text{EP}} + 1$  samples long impulse response of the exponential accumulator

$$h_{\rm rec,E}[k] = \mathcal{Z}^{-1} \left\{ \frac{1}{1 - (1 + k_{\rm E})z^{-1}} \right\} \ k \in [1, M_{\rm EP} + 1] \ (23)$$

by convoluting the two impulse responses. This leads to the weights of the linear-exponential reconstruction filter

$$w[k] = h_{\text{rec}, L}[k] * h_{\text{rec}, E}[k] \ k \in [1, M].$$

(24)

Therefore the general weights of the reconstruction filter (with  $M = M_{LP} + M_{EP}$  are

$$w[k] = \begin{cases} \frac{a_{1}c_{1}(1+k_{\rm E})^{M_{\rm EP}+1}-a_{1}c_{1}}{k_{\rm E}}, & k \in [1, M_{\rm LP}-1] \\ \frac{(a_{1}c_{1}-k_{\rm E})(1+k_{\rm E})^{M-k+1}-a_{1}c_{1}}{k_{\rm E}}, & k \in [M_{\rm LP}, M] \end{cases}$$

(25)

which are constant during the linear phase and show an exponential characteristic during the exponential phase. With these weights, the normalized FIR-implemented reconstruction filter of the linear-exponential I-DS ADC in Figure 4a becomes:

$$H_{\rm rec,LE}(z) = \frac{\sum_{k=1}^{M} w(k) z^{(k-1)}}{\sum_{k=1}^{M} w(k)}$$

(26)

#### C. Linear-Exponential Transfer Functions

To derive the overall transfer functions of the linearexponential I-DS ADC, the method of Section III will be applied. As shown in Figure 4a, the exponential phase only feeds back the quantization error E(z) into the modulator, if a multi-bit quantizer is used (q = 1). The overall STF is defined from the input U(z) to the overall output D(z) for E(z) = 0. Therefore, the exponential phase has no influence on the STF of the modulator and the STF of the linear-exponential I-DSM ADC is determined by the reconstruction filter [5], which was derived in (26).

The NTF of the free-running modulator on the other hand changes from the linear phase

$$NTF_{m,L}(z) = \frac{1 - z^{-1}}{1 - (1 + qa_1c_1)z^{-1}}$$

(27)

to

$$NTF_{\rm m,E}(z) = \frac{1 - (2 + k_{\rm E})z^{-1} + (1 + k_{\rm E})z^{-2}}{1 - (1 + qa_1c_1)z^{-1}}$$

(28)

after the point of reconfiguration to the exponential phase (EP). This leads to the impulse responses

$$h_{m,L}[k] = \mathcal{Z}^{-1}\{NTF_{m,L}(z)\}$$

(29)

of the linear phase and

$$h_{m,E}[k] = \mathcal{Z}^{-1}\{NTF_{m,E}(z)\}$$

(30)

of the exponential phase. Furthermore, to combine these transfer functions to the overall NTF of the incremental modulator the state space representations have to be established first. The definition of the states

$$x[k] = \begin{bmatrix} x_1[k] \\ x_E[k] \end{bmatrix}$$

(31)

can be derived from Figure 4a. Note that only one input, namely v[k], was defined for the state space representation because the input signal u[k] = 0 for the NTF calculation. This leads to the state space representation of the linear phase:

$$ABCD_{\rm L} = \begin{pmatrix} 1 & 0 & a_1 \\ c_1 \cdot (1 + k_{\rm E}) & 0 & -(1 + k_{\rm E}) \\ \hline c_1 & 0 & 0 \end{pmatrix}$$

(32)

and of the exponential phase:

$$ABCD_{\rm E} = \begin{pmatrix} 1 & 0 & a_1 \\ c_1 \cdot (1+k_{\rm E}) & 1+k_{\rm E} & -(1+k_{\rm E}) \\ \hline c_1 & 1 & 0 \end{pmatrix}$$

(33)

Using  $ABCD_{L}$  it is possible to calculate the internal states during the linear phase for the first  $M_{LP}$  samples and using an excitation with a discrete-time Dirac pulse  $e[k] = \delta[k]$  at the quantizer:

$$x_{L}[k + 1] = A_{L}x_{L}[k] + B_{L}v[k]$$

$$y_{L}[k] = C_{L}x_{L}[k] + D_{L}v[k]$$

$$v_{L}[k] = q \cdot y_{L}[k] + \delta[k]$$

for  $k \in [1, M_{LP}]$

(34)

Afterwards the impulse response matrix  $h_0[\tau_e, k]$  of the linear-exponential I-DS can be derived following the steps described in Section III by first obtaining the modulators impulse response  $h_{0,m}[\tau_e, k]$  and then combining it with the impulse response of the reconstruction filter. For excitation and sampling points before the point of reconfiguration, the modulators' impulse response matrix  $h_{0,m}[\tau_e, k]$  equals the values of the linear phase impulse response  $h_{m,L}[k]$ . To calculate the matrix values for an excitation time before but an observation time after reconfiguration ( $\tau_e \leq M_{LP}$ ,  $k > M_{LP}$ ),  $ABCD_E$  is required and the internal states are set to the values of the linear phase internal states during reconfiguration. To derive the matrix values for sampling and excitation points after reconfiguration, only the impulse response of the exponential phase  $h_{m,E}[k]$  is required. Afterwards the modulators' impulse response matrix  $h_{0,m}[\tau_e, k]$  is convoluted with the impulse

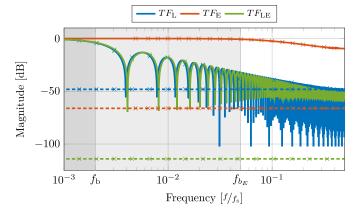

Fig. 5. Overall transfer functions of the linear I-DS at M = 256, exponential I-DS at M = 10, and reconfigured linear-exponential I-DS ADC at  $M_{\rm EP} = 10$ , M = 256, (i.e.  $M_{\rm LP} = 246$ ). Solid: Calculated STF. Dashed: Calculated NTF. X-marks: Simulation at distinct single-sinusoidal frequencies.

response of the reconstruction filter from (26) to obtain the overall impulse response matrix

$$h_0[\tau_{\rm e},k] = h_{0,\rm m}[\tau_{\rm e},k] \circledast \mathcal{Z}^{-1} \left\{ H_{\rm rec,LE}(z) \right\}$$

(35)

of the linear-exponential I-DS. Decimation leads to setting the observation time to k = M. Then, the overall NTF is obtained by performing the DTFT:

$$NTF_{\rm LE}(f) = \mathcal{F}\{h_0[\tau_{\rm e}, M]\}$$

(36)

# D. Comparison of Analysis to Simulation

To verify the calculations, Figure 5 shows the calculated TFs together with simulations (x-marks) to assess the NTF and STF of the linear-exponential I-DS ADC. For the simulations, sinusoidal test signals are inserted both, at the input of the I-DSM (STF) as well as at its quantizer (NTF) in the frequency range  $f = 0 \dots f_s/2$ ; their magnitude and thus attenuation by the STF/NTF are then calculated from the folded back versions in the frequency range  $f = 0 \dots f_N/2$  after the decimation filter. Firstly, the transfer functions of the linear I-DS ADC  $TF_{L}(z)$  is shown, then the transfer functions of the exponential I-DS  $TF_{\rm E}(z)$ , and finally the transfer functions of the reconfigured linear-exponential I-DS ADC  $TF_{LE}(z)$ . The transfer function of the linear and the exponential I-DS ADC can be calculated in the same way like the linear-exponential one, but since no reconfiguration is happening it can be also calculated using the basic approach outlined in II-B. In the example in Figure 5, the linear I-DS uses M = 256, the linear-exponential M = 256 and  $M_{\rm EP} = 10$ , which is based on [10], and the exponential I-DS transfer function is shown for M = 10. The loop-filter scaling has been chosen with  $b_1 = b_2 = c_1 = 1$  and  $a_1 = -1$  as in [10].

The overall STF of the I-DS ADC is determined by the reconstruction filter. As seen in Figure 5, the linear phase  $STF_L(f)$  shows the typical behaviour of a 1st order I-DS ADC with chain of integrators (CoI) filter, i.e. a *sinc* shape [5]; the exponential phase  $STF_E(f)$  resembles the STF seen in higher order I-DS with CoI filters [5]. The STF of the linear-exponential I-DS ADC  $STF_{LE}(f)$ , whose reconstruction filter was derived in (26), shows again a *sinc* shape, but with

the notches shifted to slightly higher frequencies than the pure linear I-DS ADC. As seen in Figure 5, calculations and simulations match excellently for the STF.

The NTFs are also depicted in Figure 5; most importantly, predictions by the introduced analytical approach for transfer functions of reconfigurable I-DS ADC and simulations match excellently for the NTF again. The commonly known noise-shaping of free-running DSM is no longer seen in incremental operation, as was shown in [6]; despite, the NTF shows a rather flat course as a result of the used matched reconstruction filters. This leads to an overall spectral suppression of the quantization error, before all higher Nyquist bands are folded into the in-band in the decimating reconstruction filter. It can be noted that the transfer functions of the nonreconfigured I-DS ADCs  $TF_{L}(z)$  and  $TF_{E}(z)$  can also be calculated using the LTI approach of [6]. But, it can be seen in Figure 5 that none of them is even close to the reconfigured linear-exponential transfer functions  $TF_{LE}(z)$  and, therefore, it wouldn't be possible to predict any performances correctly without the LTV approach introduced in this paper. Interestingly, although the exponential I-DS is only simulated for M =10 compared to the linear I-DS with a simulated M = 256,  $NTF_{\rm E}(f)$  shows significantly more noise suppression than  $NTF_{\rm L}(f)$ . The enormous improvement of quantization noise (QN) suppression by combining linear and exponential phase is then clearly seen. At this point it is interesting to ask: if the exponential phase operates so much better than the linear phase, why would we not slightly extend the exponential phase and completely omit the long linear phase? The answer lies with the sensitivity of the exponential phase to mismatch [10], which will be further discussed in the next section.

# V. FURTHER ANALYSIS OF THE LINEAR-EXPONENTIAL I-DS ADC BASED ON THE TRANSFER FUNCTIONS

After Section III has derived a general methodology to derive the transfer function of reconfigurable I-DS ADC and Section IV has applied this in particular to the linearexponential I-DS ADC, this can be used to get a deeper understanding of the trade-offs of the linear-exponential I-DS. The influence of the parameters  $M_{\rm EP}$  (exponential operation time) and  $k_{\rm E}$  (exponential gain) as well as the operation under coefficient mismatch have already been discussed in [15] based on simulations. In the following the influence of these variable parameters will be further analysed concerning their influence on the transfer functions; thereafter, the NTF will be used to predict the SONR of the LE I-DS ADC, while the STF is used to predict the thermal noise penalty factor (NPF) [11], an effect which is known in I-DSM to worsen the input referred thermal noise over the noise of a free-running DSM. Finally, analog/digital mismatch will be investigated as well as reconstruction filters other than the ideal one in Figure 4a.

### A. Influence of Parameters $M_{\rm EP}$ and $k_{\rm E}$ on STF and NTF

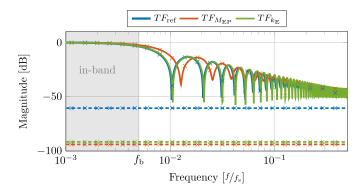

Calculation and simulation for STF and NTF of the linearexponential I-DS with varying parameters  $M_{\rm EP}$  and  $k_{\rm E}$  are plotted in Figure 6. As before,  $b_1 = b_2 = c_1 = 1$  and  $a_1 = -1$  are chosen, but the oversampling is changed to

Fig. 6. Overall STFs and NTFs of the linear-exponential I-DS with varying  $M_{\rm EP}$  and  $k_{\rm E}$  at M = 100. For the reference transfer functions  $M_{\rm EP} = 5$  and  $k_{\rm E} = 0.2$  is chosen. For  $TF_{M_{\rm EP}}$ ,  $M_{\rm EP}$  is altered to 25 and for  $TF_{k_{\rm E}}$ ,  $k_{\rm E}$  is modified to 2.

M = 100. At first, a reference design  $TF_{ref}$  with  $M_{EP} = 5$  and  $k_E = 0.2$  is chosen. The parameters are chosen under the condition of a good visualization of the effect of the changing parameters on the transfer functions. Therefore, the parameters in the reference design here are changed compared to the parameters used in earlier sections. For  $TF_{M_{EP}}$ ,  $M_{EP}$ is changed to 25 while  $k_E$  is kept to 0.2; for  $TF_{k_E}$ ,  $k_E$  is changed to 2, while  $M_{EP}$  is kept to 5. In both cases, either by increasing  $M_{EP}$  or increasing  $k_E$ , the NTF changes in a similar way; it keeps the same shape but achieves similarly more noise suppression, though it will be seen next that excessively increasing  $k_E$  leads to instability. The STF stays almost unaltered while  $k_E$  is increased, but the sinc-shaped notches are shifted towards higher frequencies while  $M_{EP}$  is increased; it will be seen next that this affects the NPF.

## B. SQNR of LE I-DS ADC Based on Its NTF

The SQNR calculation is done with

$$SQNR_{est} = 10 \cdot \log_{10} \left( \frac{P_{in}}{IBN_{est}} \right)$$

(37)

using the integrated in-band noise

$$IBN_{\text{est}} = \frac{\Delta^2}{12} \cdot \frac{1}{f_{\text{s}}} \int_{-f_{\text{s}/2}}^{f_{\text{s}/2}} |NTF(f)|^2 \,\mathrm{d}f, \qquad (38)$$

with the signal power  $P_{\rm in}$ , the quantizer step size  $\Delta$  and the I-DS ADCs' overall noise transfer function NTF. In case of the LE I-DS ADC the NTF corresponds to the  $NTF_{\rm LE}(f)$  derived in (36). The course of the NTF of the I-DS under variable  $k_{\rm E}$  and  $M_{\rm EP}$  were already shown in Figure 6, and a respective change of the SQNR is thus expected.

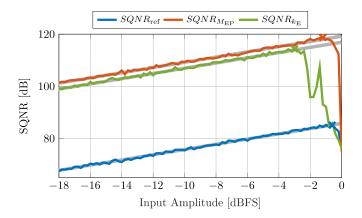

The predicted and simulated SQNR of the I-DS ADC in Figure 4a are shown in Figure 7 for 3 different sets of  $M_{\rm EP}$ and  $k_{\rm E}$ . As before,  $b_1 = b_2 = c_1 = 1$  and  $a_1 = -1$  are chosen. Again, the reference design  $SQNR_{\rm ref}$  with  $M_{\rm EP} =$ 5 and  $k_{\rm E} = 0.2$  is shown. For  $SQNR_{M_{\rm EP}}$ ,  $M_{\rm EP}$  is changed to 25 while  $k_{\rm E}$  is kept at 0.2; for  $SQNR_{k_{\rm E}}$ ,  $k_{\rm E}$  is changed to 2, while  $M_{\rm EP}$  is kept at 5. It can be seen that the calculated SQNR using the proposed approach achieves excellent matching with all simulated results, which validates again the correctness of the calculated NTF in (36). Furthermore, it is shown that

Fig. 7. SQNR and MSA simulation and prediction over amplitude for the linear-exponential I-DS ADC at M = 100. For the reference I-DS ADC  $M_{\rm EP} = 5$  and  $k_{\rm E} = 0.2$  is chosen. For  $SQNR_{M_{\rm EP}}$   $M_{\rm EP}$  is altered to 25 and for  $SQNR_{k_{\rm E}}$   $k_{\rm E}$  is modified to 2.

the SQNR can be similarly boosted by both parameters  $M_{\rm EP}$ and  $k_{\rm E}$ , as expected from the NTF in Figure 4a. Concerning stability and MSA, it can also be seen in Figure 7 that an increase of  $k_{\rm E}$  reduces the MSA. Generally it is known that the conditional stability of DSM depends on the input amplitude, the loopfilter scaling and the number of quantizer levels. During the exponential phase, stability (and MSA) are additionally highly influenced by the factor  $k_{\rm E}$ . This is since  $k_{\rm E}$ determines the amplification of the fed back quantization error, and more  $k_{\rm E}$  or larger quantization error (i.e. lower number of bits) can lead to quantizer overload. Thus, stability and MSA are co-defined by the inter-dependency of  $k_{\rm E}$  and the number of quantizer levels during EP in an I-DS ADC. This is also why a multi-bit quantizer is absolutely necessary for stable operation during EP. On the contrary, as also seen in Figure 7, stability and MSA are independent of the number of EP samples  $M_{\rm EP}$ .

It is also worth noting that large  $k_{\rm E}$  (as e.g.  $k_{\rm E} = 2$  in Figure 7) does not yield in an abrupt drop of SQNR for larger amplitudes, cf. Figure 7, as the instability only occurs during the exponential phase, while the linear phase is still stable for the higher amplitudes.

# C. Noise Penalty Factor of LE I-DS ADC Based on Its STF

It is known from literature that I-DS ADCs suffer from a NPF [11], which describes the effect that input referred thermal noise of an I-DS ADC appears amplified towards the output of the reconstruction filter. The NPF is dominated by the choice of the reconstruction filter and worse for higher order I-DS ADCs [11]; as the exponential phase appears like an increased order, it is interesting to analyze the NPF for the linear-exponential I-DS ADC.

The noise at the output of an I-DS due to an input referred thermal noise and the NPF  $\beta_{npf}$  can be calculated by

$$P_{\rm N,out} = P_{\rm N,in} \frac{\beta_{\rm npf}}{M} \tag{39}$$

with

$$\beta_{\rm npf} = \frac{P_{\rm N,out,actual}}{P_{\rm N,out,min}} = \frac{M}{f_{\rm s}} \int_{-f_{\rm s}/2}^{f_{\rm s}/2} |STF(f)|^2 \,\mathrm{d}f \qquad (40)$$

TABLE I NPF VALUES OF THE LE I-DS ADC FOR DIFFERENT SETS OF PARAMETERS

| Parameters from  | [10] | $TF_{\rm ref}$ | $TF_{M_{\rm EP}}$ | $TF_{k_{\rm E}}$ |

|------------------|------|----------------|-------------------|------------------|

| M                | 256  | 100            | 100               | 100              |

| $k_{\mathrm{E}}$ | 1.0  | 0.2            | 0.2               | 2                |

| $M_{\rm EP}$     | 10   | 5              | 25                | 5                |

| NPF              | 1.03 | 1.02           | 1.22              | 1.04             |

being the noise penalty factor of the I-DS ADC [11].  $P_{N,out,actual}$  describes the actual thermal noise power at the output of the I-DS ADC and  $P_{N,out,min}$  the minimal one. In [10] it was already mentioned that the NPF becomes worse for the linear-exponential I-DS, but the reason was not assessed nor the effect generally quantified. But having derived the analysis for the STF of the linear-exponential I-DSM in Section IV-C, it is possible to calculate the NPF from (40).

When looking at simulation and analysis of STF in Figure 5, we saw that the notches of  $STF_{LE}(f)$  were slightly shifted towards higher frequencies compared to  $STF_{L}(f)$ ; this consequently leads to a larger integral over the STF and thus to worse NPF in (40). Further investigating the simulation and analysis over parameter  $k_{\rm E}$  and  $M_{\rm EP}$  in Figure 6, we could observe that an increase in  $k_{\rm E}$  had only minor influence, whereas the increase in  $M_{\rm EP}$  was actually responsible for the shift of the STF-notches. This leads, in the extreme case of an only exponentially operating I-DS, to the largely flat course of  $STF_{\rm E}(f)$  in Figure 5, which consequently yields the worst NPF behaviour. The NPF values of the parameter set from [10], the reference set, the  $M_{\rm EP}$  and  $k_{\rm E}$  parameter set can be seen in Table I. A more detailed simulation based analysis of the NPF in dependency of  $M_{\rm EP}$  and  $k_{\rm E}$  can be found in [15]. Considering this finding, an increase of  $k_{\rm E}$  instead of  $M_{\rm EP}$  seems preferable for higher SQNR. On the other hand, we have seen that excessively increasing  $k_{\rm E}$  leads to a decrease in stability, which was seen in Figure 7. Therefore, setting the parameters  $M_{\rm EP}$  and  $k_{\rm E}$  of the exponential phase is a compromise between boosting the SQNR while keeping the NPF low, and the modulator stable.

# D. Mismatch Limitations of Performance Increase During Exponential Phase

As it was already shown by simulation in [15], given a certain analog/digital mismatch in the linear-exponential I-DS ADC in Figure 4a, the possible performance improvement of the exponential phase is limited. This limitation is caused by the mismatch between the analog loopfilter coefficients (like  $k_E$ ) and the digital reconstruction filter during the exponential phase. This is not the case during the linear phase, where mismatches between analog loopfilter and digital reconstruction filter are highly tolerated. Since a certain target SQNR is firstly based on the linear phase to achieve a base-resolution, whereas the exponential phase boosts the SQNR to a final value, under mismatch a longer linear phase is needed, and the duration of the useful exponential phase is reduced.

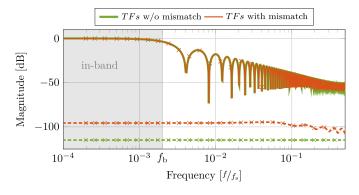

This effect is illustrated with an exemplary coefficient mismatch in the LE NTF in Figure 8. There, the overall transfer

Fig. 8. Overall transfer functions of the linear I-DS at M = 256 and  $M_{\rm EP} = 10$  without coefficient mismatch (green) and with a mismatch for  $k_{\rm E}$  of 1% between the analog modulator and the digital filter (red).

functions of the LE I-DS are again simulated and calculated at M = 256 and  $M_{\rm EP} = 10$ , and all scaling coefficients as in Section V-B: firstly, without coefficient mismatch in green, and secondly using an analog-digital mismatch in red; thereby, the exponential-phase gain  $k_{\rm E}$  has been varied by +1% in the analog I-DSM over its digital counterpart in the reconstruction filter in Figure 4a, which causes the most significant mismatch between the analog modulator and the digital filter. Since the exponential phase has no effect on the modulators STF, a mismatch of  $k_{\rm E}$  has no impact on the STF. On the other hand, the suppression of the NTF drops by almost 20dB for the given example even for the small mismatch. Comparing the mismatch affected transfer functions in Figure 8 with the ideal transfer functions in Figure 5, it can be seen that while the ideal LE transfer function gives a significant boost to lowering the NTF, the mismatch-affected boost is compromised. The large 1% coefficient variation in Figure 8 was chosen for better visualization of the impact of analog vs. digital mismatch on the transfer functions in the linear-exponential I-DS ADC; especially for switched-capacitor (SC) based loopfilter implementations, much better relative capacitor and thus coefficient matching can be achieved. E.g., the original implementation of the linear-exponential I-DS ADC in [10] reports a coefficient variation of 0.2%. Thus, 0.2% will also be used for further analysis and simulations in the following as an exemplary but realistic assumption.

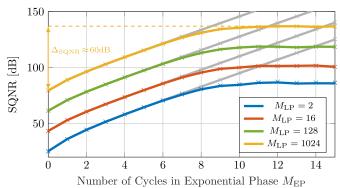

This mismatch-affected boost is further simulated and compared to analytical prediction in Figure 9; there, the achievable SQNR of the LE I-DS ADC is simulated and calculated for a Gaussian distributed random mismatch of all analog coefficients with  $\sigma_{\text{coeff}} = 0.2\%$  over 200 Monte Carlo runs; the mean SQNR is plotted for both the simulation (x-marks) and calculation from the underlying transfer functions (solid). The grey curves and x-marks depict the simulated and predicted ideal SQNR without coefficient mismatch for comparison. The simulation and analysis is thereby performed over the length of the exponential phase  $M_{\text{EP}}$  for different durations of the linear phase  $M_{\text{LP}}$  as parameter, using a 16-level quantizer,  $k_{\text{E}} = 1$ , and again all other scaling coefficients as in Section V-B.

Firstly, it can be seen that the predictions with (color) and without (gray) coefficient mismatch show excellent matching to the simulation points. Furthermore, it can be seen that for

Fig. 9. Achievable SQNR values of the LE I-DS ADC over the length of the exponential phase  $M_{\rm EP}$  for different duration of the linear phase  $M_{\rm LP}$  and a 16-level quantizer. Simulated (x-marks) and predicted (solid), calculated using the transfer functions, SQNR values. The SQNR values in color are the derived mean values for a coefficient mismatch of 0.2% over 200 Monte Carlo runs and the SQNR values in gray are derived without mismatch.

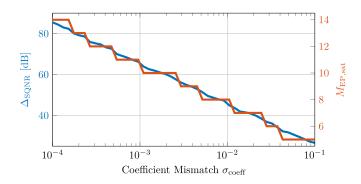

Fig. 10. Maximum achievable SQNR boost  $\Delta_{\text{SQNR}}$  (blue) and required exponential phase duration  $M_{\text{EP,sat}}$  (red) of the LE I-DS ADC over different coefficient mismatch values  $\sigma_{\text{coeff}}$ . The SQNR values are calculated with the transfer functions with all I-DSM coefficients varied using a standard distribution with standard deviation  $\sigma_{\text{coeff}}$ .  $M_{\text{EP,sat}}$  is defined as the length of the exponential phase, where the mean SQNR value is closer than 3dB to its final mean settling value. Accordingly,  $\Delta_{\text{SQNR}}$  is defined as the boost of the SQNR achieved by the exponential phase at  $M_{\text{EP,sat}}$ .

a specific coefficient mismatch the achievable SQNR settles towards a maximum and cannot be further boosted by an increase of the duration of the exponential phase  $M_{\rm EP}$ . Interestingly, the possible performance boost by the exponential phase appears to be approximately constant for a given mismatch, e.g.  $\Delta_{\rm SQNR} \approx 60$ dB for the chosen 0.2% mismatch, and the only way to achieve a certain SQNR is by choosing an appropriately larger duration of the linear phase  $M_{\rm LP}$ .

This can be further explored over a larger parameter space by using the SQNR predictions via transfer functions without relying on more simulations. Therefore, in Figure 10 it is analysed how the possible SQNR boost of the exponential phase  $\Delta_{SQNR}$ , as well as the useful length of the exponential phase to achieve this SQNR boost ( $M_{EP,sat}$ ) depend on coefficient mismatch.  $M_{EP,sat}$  is thereby defined as the length of the exponential phase, where the mean SQNR value is closer than 3dB to its final mean settling value. Accordingly,  $\Delta_{SQNR}$  is defined as the boost of the SQNR achieved by the exponential phase at  $M_{EP,sat}$ . The results are calculated from the transfer functions, where all analog loopfilter coefficients are varied with a standard distribution and the standard deviation  $\sigma_{coeff}$ .

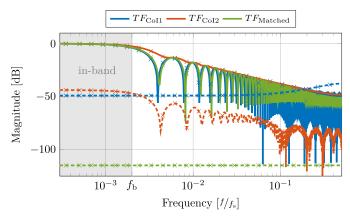

Fig. 11. Overall STFs and NTFs of the linear-exponential I-DS ADC at  $M_{\rm EP} = 10$ , M = 256,  $k_{\rm E} = 1$  and with different reconstruction filters (first order CoI, second order CoI and matched filter). Solid: Calculated STF. Dashed: Calculated NTF. X-marks: Simulation at distinct single-sinusoidal frequencies.

All parameters are chosen as for Figure 9. It can be seen that there is a linear correlation between  $\Delta_{SQNR}$  and the coefficient mismatch  $\sigma_{coeff}$ : the higher the coefficient mismatch is, the lower is the achievable  $\Delta_{SQNR}$  by the exponential phase, and therefore the shorter is the length of the exponential phase until the performance can't be increased anymore.

#### E. Influence of Reconstruction Filters on STF and NTF

Throughout Section IV and the derivation so far, the description and analysis of the linear-exponential I-DS ADC has been based on a matched reconstruction filter as shown in Figure 4a. One might raise the question how other commonly used reconstruction filters as e.g. a CoI filter perform. The shown derivation obviously allows to also include this into the analysis, and simulations and calculations of the overall transfer functions of the LE I-DS ADC using a first order CoI, a second order CoI and a matched reconstruction filter are exemplary shown in Figure 11. The first order CoI filter shows - similar to the matched reconstruction filter - a sinc shaped STF with the notches of the matched filter slightly shifted to higher frequencies (solid lines). On the contrary, the overall NTF shows completely distorted shapes (dashed lines) and it becomes clear why the matched filter is necessary to get the desired SQNR performance boost: only the matched reconstruction filter yields a powerful suppression of the NTF leading to a SQNR of about 139dB. The first order CoI only gives a SQNR of 63dB. Even moving to a higher order CoI filter, the exponential phase still yields no actual improvement and the SQNR = 88dB. This SQNR degradation is not really surprising as already a tiny mismatch between the analog and digital filter caused a large drop in SQNR, cf. Section V-D, and thus ideal exponential phase QN suppression is only seen for an ideally matched filter.

### VI. CONCLUSION

This manuscript intends to close a gap in the state of the art, which is the calculation of transfer functions of reconfigured I-DS ADCs. The newly derived calculation method is explained and then exemplarily applied to the linear-exponential I-DS ADC leading to a detailed analysis of the exponential phase as a dynamic reconfiguration technique in I-DS ADCs. Accurate performance predictions are possible and influence of non-idealities can be included. Furthermore, the mathematical derivation of the reconfigured matched reconstruction filter could be shown. Such analysis allows to accurately predict simulation results of dynamically reconfigured I-DS ADC and help to understand the underlying mechanisms of performance improvements and trade-offs. The analysis can be applied to any other dynamically reconfigurable I-DS ADC.

#### APPENDIX A

#### ALGORITHM TO CALCULATE IMPULSE RESPONSE MATRIX

To calculate the impulse response matrix  $h_{0,m}[\tau_e, k]$  of the reconfigured DSM it is required to have the state space representation of the two systems  $ABCD_I$  and  $ABCD_{II}$ , the impulse response of the first system  $h_I[k]k \in [1, M_I]$ , of the second system  $h_{II}[k]k \in [1, M_{II}]$  and the internal states of the first system during the impulse response calculation  $x_I[i, k]i \in [1, n], k \in [1, M_I]$  with *n* being the order of the modulator. This information enables the usage of the following algorithm to calculate the impulse response matrix  $h_{0,m}[\tau_e, k]$ .

| Algorithm 1 Calculate Impulse Response Matrix                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------|

| <b>Require:</b> $ABCD_{I}$ , $ABCD_{II}$ , $x_{I}[i, k]$ , $h_{I}[k]$ , $h_{II}[k]$                                           |

| for $\tau_e = 1 : M$ do                                                                                                       |

| if $\tau_{\rm e} \leq M_{\rm I}$ then                                                                                         |

| $h_{0,\mathrm{m}}[\tau_{\mathrm{e}},\tau_{\mathrm{e}}:M_{\mathrm{I}}] \leftarrow h_{I}[1:M_{\mathrm{I}}-\tau_{\mathrm{e}}+1]$ |

| $x_{II}[:, 1] \leftarrow x_{I}[:, M_{\mathrm{I}} - \tau_{\mathrm{e}} + 2]$                                                    |

| for $k = 1 : M_{\text{II}}$ do                                                                                                |

| $y[k] \leftarrow C_{II} \times x_{II}[:,k] + D_{II} \times u[k]$                                                              |

| $x_{II}[:, k+1] \leftarrow A_{II} \times x_{II}[:, k] + B_{II} \times u[k]$                                                   |

| end for                                                                                                                       |

| $h_{0,\mathrm{m}}[\tau_{\mathrm{e}}, M_{\mathrm{I}}+1:M] \leftarrow y$                                                        |

| else                                                                                                                          |

| $h_{0,\mathrm{m}}[\tau_{\mathrm{e}},\tau_{\mathrm{e}}:M] \leftarrow h_{II}[1:M-\tau_{\mathrm{e}}+1]$                          |

| end if                                                                                                                        |

| end for                                                                                                                       |

#### REFERENCES

- S. Pavan, R. Schreier, and G. C. Temes, Understand Delta-Sigma Data Converters, 2nd ed. Hoboken, NJ, USA: Wiley-IEEE Press, 2017.

- [2] R. van de Plassche and R. E. J. van Der Grift, "A five-digit analogdigital converter," *IEEE J. Solid-State Circuits*, vol. SSC-12, no. 6, pp. 656–662, Dec. 1977.

- [3] J. Markus, J. Silva, and G. C. Temes, "Theory and applications of incremental ΔΣ converterss," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 51, no. 4, pp. 678–690, Apr. 2004.

- [4] Z. Tan, C.-H. Chen, Y. Chae, and G. C. Temes, "Incremental delta-sigma ADCs: A tutorial review," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 67, no. 12, pp. 4161–4173, Dec. 2020.

- [5] J. Wagner, P. Vogelmann, and M. Ortmanns, "On the signal filtering property of CT incremental Sigma-Delta ADCs," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 66, no. 11, pp. 1780–1784, Nov. 2019.

- [6] J. Wagner, P. Vogelmann, and M. Ortmanns, "Performance evaluation of incremental Sigma-Delta ADCs based on their NTF," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 67, no. 12, pp. 2813–2817, Dec. 2020.

- [7] P. Vogelmann, J. Wagner, M. Haas, and M. Ortmanns, "A dynamic power reduction technique for incremental ΔΣ modulators," *IEEE J. Solid-State Circuits*, vol. 54, no. 5, pp. 1455–1467, May 2019.

- [8] B. Wang, S.-W. Sin, U. Seng-Pan, and R. P. Martins, "A high resolution multi-bit incremental converter insensitive to DAC mismatch error," in *Proc. 12th Conf. Ph.D. Res. Microelectron. Electron. (PRIME)*, Jun. 2016, pp. 1–4.

- [9] P. Vogelmann, J. Wagner, A. Hänsler, and M. Ortmanns, "Improved SQNR and MSA in incremental ΔΣ modulators by using a recuperation phase," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 65, no. 5, pp. 557–561, May 2018.

- [10] B. Wang, S.-W. Sin, U. Seng-Pan, F. Maloberti, and R. P. Martins, "A 550-μw 20-kHz BW 100.8-dB SNDR linear-exponential multi-bit incremental ΣΔ ADC with 256 clock cycles in 65-nm CMOS," *IEEE J. Solid-State Circuits*, vol. 54, no. 4, pp. 1161–1172, Apr. 2019.

- [11] J. Steensgaard et al., "Noise-power optimization of incremental data converters," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 55, no. 5, pp. 1289–1296, Jun. 2008.

- [12] S. Bannwarth, A. Wenzler, and W. Mathis, "On the transfer behaviour of incremental Sigma Delta Converters," in *Proc. VXV Int. Symp. Theor. Eng.*, Jun. 2009, pp. 1–5. [Online]. Available: https://ieeexplore.ieee. org/document/5760639?arnumber=5760639

- [13] A. Gersho, "Characterization of time-varying linear systems," Proc. IEEE, vol. 51, no. 1, p. 238, Jan. 1963.

- [14] C. Lyden, "Single shot sigma-delta analog to digital converter," U.S. Patent 5189419, Feb. 23, 1993.

- [15] P. Kaesser, O. Ismail, C. Rudorf, J. Wagner, and M. Ortmanns, "Linearexponential I-DS ADCS: Analysis, limitations and higher order," in *Proc. IEEE Int. Symp. Circuits Syst. (ISCAS)*, May 2023, pp. 1–5.

**Paul Kaesser** (Graduate Student Member, IEEE) received the B.Sc. and M.Sc. degrees in electrical engineering from the University of Ulm, Ulm, Germany, in 2018 and 2021, respectively, where he is currently pursuing the Ph.D. degree with the Institute of Microelectronics, under the supervision of Prof. Maurits Ortmanns. His research interests include system-level modeling and optimization of sigma-delta ADCs.

**Omar Ismail** (Graduate Student Member, IEEE) received the B.Sc. degree in electronics engineering from German University in Cairo, Cairo, Egypt, in 2019, and the M.Sc. degree in communications technology from the University of Ulm, Ulm, Germany, in 2021, where he is currently pursuing the Ph.D. degree in the field of high resolution incremental sigma-delta A/D converters, under the supervision of Prof. Dr.-Ing. Maurits Ortmanns.

Johannes Wagner (Member, IEEE) received the B.Sc. and M.Sc. degrees in electrical engineering from the University of Ulm, Ulm, Germany, in 2015, where he is currently pursuing the Ph.D. degree with the Institute of Microelectronics, with a focus on system-level modeling and optimization of sigma-delta modulators. His research interests include the system-level analysis of CMOS analog and mixed-signal ICs and in particular incremental sigma-delta ADCs. He received the Best Demo Award from ICECS 2016.

**Robert F. H. Fischer** (Senior Member, IEEE) received the Dr.-Ing. and Habilitation degrees from the University of Erlangen–Nürnberg, Erlangen, Germany, in 1996 and 2001, respectively. From 1992 to 1996, he was a Research Assistant with the Telecommunications Institute, University of Erlangen–Nürnberg. In 1997, he was with the IBM Research Laboratory, Zürich, Switzerland. In 1998, he returned to the University of Erlangen–Nürnberg. In 2005, he spent a sabbatical with ETH Zürich, Zürich. Since 2011, he has been a

Full Professor with the University of Ulm, Ulm, Germany. He is currently teaching the undergraduate and graduate courses on signals and systems and digital communications. He authored the textbook *Precoding and Signal Shaping for Digital Transmission* (Wiley, 2002). His current research interests include fast, reliable, and secure digital transmission, including single-carrier and multicarrier modulation techniques, information theory, coded modulation, digital communications, signal processing, and especially precoding and shaping techniques. He was a recipient of the Dissertation Award from Technische Fakultét, University of Erlangen–Nürnberg, in 1997, the Publication Award of the German Society of Information Techniques in 2000, the Wolfgang Finkelnburg Habilitation Award in 2002, and the Philipp-Reis-Preis in 2005.

**Maurits Ortmanns** (Senior Member, IEEE) received the Dr.-Ing. degree from the University of Freiburg, Breisgau, Germany, in 2004. From 2004 to 2005, he was with Sci-Worx GmbH, Hannover, Germany, in the field of mixed-signal circuits for biomedical implants. In 2006, he joined the University of Freiburg, as an Assistant Professor. Since 2008, he has been a Full Professor with the University of Ulm, Ulm, Germany, where he is currently the Head of the Institute of Microelectronics. He has authored the textbook

*Continuous-Time Sigma-Delta A/D Conversion*, authored or coauthored several other book chapters, and more than 250 IEEE journal articles and conference papers. He holds several patents. His research interests include mixed-signal integrated circuit design with a special emphasis on data converters and biomedical applications.