Received 6 June 2023; revised 24 July 2023; accepted 21 August 2023. Date of publication 8 September 2023; date of current version 17 October 2023. Digital Object Identifier 10.1109/OJSSCS.2023.3311418

# Design Techniques for Energy-Efficient Analog-to-Digital Converters

MOONHYUNG JANG<sup>10</sup><sup>1</sup> (Member, IEEE), XIYUAN TANG<sup>10</sup><sup>2,3</sup> (Member, IEEE), YONG LIM<sup>4</sup> (Member, IEEE), JOHN G. KAUFFMAN<sup>10</sup><sup>5</sup> (Member, IEEE), NAN SUN<sup>6</sup> (Senior Member, IEEE), MAURITS ORTMANNS<sup>10</sup><sup>5</sup> (Senior Member, IEEE), AND YOUNGCHEOL CHAE<sup>10</sup><sup>7</sup> (Senior Member, IEEE) (Invited Paper)

<sup>1</sup>Department of Electrical Engineering, Stanford University, Stanford, CA 94306, USA

<sup>2</sup>Institute for Artificial Intelligence, Peking University, Beijing 100871, China

<sup>3</sup>School of Integrated Circuits, Peking University, Beijing 100871, China

<sup>4</sup>System LSI Division, Samsung Electronics, Hwaseong 18448, South Korea

<sup>5</sup>Institute of Microelectronics, University of Ulm, 89081 Ulm, Germany

<sup>6</sup>Department of Electronic Engineering, Tsinghua University, Beijing 100084, China

<sup>7</sup>Department of Electronic Engineering, Yonsei University, Seoul 03722, South Korea

CORRESPONDING AUTHOR: Y. CHAE (e-mail: ychae@yonsei.ac.kr)

**ABSTRACT** The energy efficiency of analog-to-digital converters (ADCs) has improved steadily over the past 40 years, with the best reported ADC efficiency improving by nearly six orders of magnitude over the same period. The best figure-of-merit (FoM) is achieved with a limited class of ADC in terms of resolution and speed, but the coverage of the best FoM ADC has been expended. Many ADCs with the record FoM open up new applications and often incorporate multiple combinations of architectural and circuit innovations. It would be very interesting to follow a path of relentless optimization that could be useful to further expand the operating bandwidth of energy-efficient ADCs. To help along this path, this review article discusses the design techniques that focus on optimizing energy efficiency, involving successive approximation, pipelining, noise-shaping, and continuous-time operation.

**INDEX TERMS** Analog-to-digital converter (ADC), continuous-time (CT), delta-sigma modulation, energy efficient, low power, noise-shaping (NS), pipelining, successive approximation.

#### I. INTRODUCTION

THERE have been remarkable innovations in analog-todigital converter (ADC) design, and all performance metrics in ADCs have also been improved [1], [4], [5], [6]. Over time, the performance comparison between ADCs has been made with the energy efficiency, with ADCs with high energy efficiency becoming the most important [5], [6]. The race for higher energy efficiency has led to constant innovations in technologies, architectures, and circuits [6], taking ADCs to levels of energy efficiency that people in the past could not have imagined. As a result, the best reported ADC efficiency has improved nearly by six orders of magnitude over the past 40 years.

In addition, achieving best-in-class energy efficiency is extremely important, as it defines the frontier of what is possible and also opens up new applications. After a closer look at the reported data, one can notice that the best figure-of-merit (FoM) is only achieved with a limited class of ADCs in terms of resolution and speed. However, the coverage of the best FoM ADCs has been expended steadily to higher bandwidth. Given this trend, it would be interesting to take a look at recent examples of energy-efficient ADCs: how their architectures and circuits are smartly arranged and achieve such high energy efficiency, because they can be very useful for further improvements.

In this review article, the focus is on architectures and circuit techniques to achieve high power efficiency. In this context, the generic ADCs' basic functionality is omitted, and many recent examples are described instead. In Section II, the ADC FoM and the trend toward energy efficiency are discussed to properly assess the design techniques. Considering the ADC trends over the last decade, the techniques for SAR ADCs are first discussed in Section III, since SAR ADCs have become ubiquitous in scaled CMOS due to their superior efficiency. Next, the design techniques to improve the resolution, pipelining, and noise-shaping (NS) are covered in Section IV. Furthermore, Section V discusses continuous-time (CT) ADCs, which are gaining popularity as a successful alternative with many hybridizations. A brief conclusion is drawn in Section VI.

### **II. ADC FIGURE OF MERIT**

Over the last four decades, thousands of ADCs have been published, sometimes with different motivations researchers, readers, designers, and reviewers, needed a way to compare their performances. ADCs are probably among the most specified building blocks for integrated circuits, and no research paper today misses to state at least one FoM. The two most commonly used FoMs are the Walden FoM<sub>W</sub>, proposed in 1994 [1], and the Schreier FoM<sub>S</sub>, described by Schreier in his textbook published in 2005 [2] but proposed as early as 1997 in [3]. The nowadays used expression for those FOMs are

$$FOM_W = \frac{P}{2^{ENOB} \cdot f_N} \tag{1}$$

$$FOM_S = DR_{dB} + 10 \cdot \log\left(\frac{BW}{P}\right)$$

(2)

where *P* is the power consumption, ENOB is the effective number of bits,  $f_N$  is the effective Nyquist frequency, BW is the useful signal bandwidth, and DR is the dynamic range of the ADC. FoM<sub>S</sub> in (2) is essentially the same definition as that in [3] that  $a \times 2$  in power, bandwidth, and DR are equally weighted. In contrast, FoM<sub>W</sub> in (1), which is the inverse of the original definition in [1], weights resolution less, i.e.  $a \times 4$  in power and bandwidth are treated equally to  $a \times 2$  in resolution. Thus, FoM<sub>W</sub> generally favors lowresolution designs, whereas thermal noise-limited designs exclusively use FoM<sub>S</sub>. Also, DR in (2) has been replaced by the signal-noise-(distortion) ratio and, thus, effectively again by ENOB, in order to take into account the increase in noise-floor and distortion for full-scale input signals.

Many other FoMs have been proposed over the past two decades, including supply voltages, technology, area consumption, and more [4], [5]. Although the underlying idea is valid that more parameters justify a good design, only Walden- and Schreier-FoM are used today. As trend lines indicate the majority of ADCs are now limited by thermal noise, FoM<sub>S</sub>, which equally values bandwidth, resolution, and power consumption, is the surviving FoM metric in the most recent publications.

Today, Murmann's ADC performance survey [6] covers all ISSCC and VLSI publications on ADCs since 1997 and is referred to in almost all publications on ADCs. Even larger databases have been gathered in [5], where an overview of ADC surveys can also be found. It has turned out over the years that while individual, excellent, and even performanceleading designs are missing when referring only to [6], the general trend lines are well captured. It is though important to keep emphasizing that a single number like the FoM does

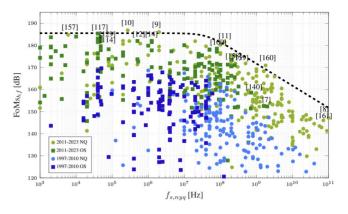

FIGURE 1. FoM<sub>S</sub> versus f<sub>snyq</sub> of published ADCs based on [6].

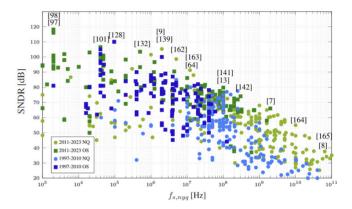

FIGURE 2. SNDR versus f<sub>snyq</sub> of published ADCs based on [6].

not tell the whole story of an ADC; FoM comparisons should be made between ADCs in the same performance range and ideally between ADCs intended for similar applications. Furthermore, power consumed for calibration engines, decimation filters, and input/reference buffers, which are often neglected in reporting FoMs, have to be considered. Fortunately, the recent state-of-the-art (SOTA) shows an increasing focus on ADCs with easier drivability, implicit filtering, better and calibration-free linearity, etc., rather than just on the next record FoM.

Two charts are shown in Figs. 1 and 2. First, the reported FoM<sub>S</sub> and second, the reported SNDR, both over the achieved Nyquist frequency. In both plots, older designs are separated from newer publications, and we separate Nyquist (NQ) ADC from oversampling and NS (OS) ADC [6]. This is done to show the current front of the SOTA. Moreover, in the next sections, it allows for highlighting a few architectures and designs defining this front. The charts also show that it is very rare for a single ADC to outperform in more than one performance plot and only [7], [8], and [9] achieve this.

Both charts show data points split into an early and a late time period and separate Nyquist-rate and oversampling (or NS) ADCs. This allows us to see the tremendous performance evolution over the last decade, which is partially due to technology, but evenly important due to innovations

FIGURE 4. Schematic of (a) SA latch and (b) FIA [27].

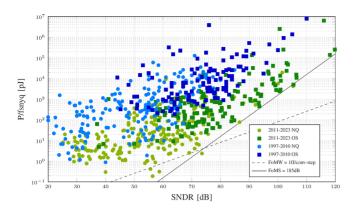

FIGURE 3. P/f<sub>snyq</sub> vs. SNDR of published ADCs based on [6].

on circuit and architectural levels. Moreover, when we look at the evolution of ADC efficiency over reported SNDR, we can see that even though Nyquist ADC has usually been outperformed by NS ADCs, recent contributions impressively show the opposite [9], [10], [11] (see Fig. 3).

The SAR ADC has become an essential part of energyefficient ADCs and is one of the most energy-efficient ADCs to the fastest ADCs. The use of NS in SAR ADCs blurs the distinction between delta–sigma ( $\Delta\Sigma$ ) ADCs [12], and  $\Delta\Sigma$ ADCs also include the SAR ADC as a quantizer in SOTA works [13]. Therefore, hybrid ADCs are gaining popularity [14] and becoming a successful alternative to classical architecture.

#### **III. DESIGN TECHNIQUES FOR SAR ADC**

In the last decade, the SAR ADC has dominated the development of energy-efficient ADCs for low-to-medium resolution applications, leveraging both technology scaling and circuit techniques [15]. A SAR ADC consists of three main blocks: 1) the comparator; 2) the SAR logic; and 3) the DAC. While the power consumption of the SAR logic benefits directly from technology scaling, reducing the comparator and DAC power consumption relies on various innovative techniques. In this section, emerging techniques for energy-efficient SAR ADCs are reviewed, with a focus on comparator and DAC design.

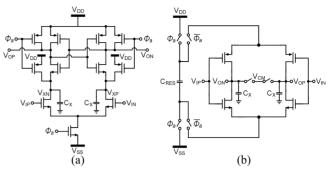

## A. LOW-POWER COMPARATORS

As the critical circuit block that converts the difference between the input signal and the analog DAC voltage into a digital output, the comparator directly determines the SAR ADC performance. A comparator usually consists of a preamplifier that amplifies the input signal, followed by a latch to resolve the final decision. The strong-arm (SA) latch is one of the most popular designs [16], [17], [18], as shown in Fig. 4(a). When  $\phi_a$  is low, the comparator is turned off with the integration nodes  $V_{XP}/V_{XN}$  and output nodes  $V_{OP}/V_{ON}$  reset to  $V_{DD}$ . When amplification starts, the integration nodes are discharged at different rates depending on the input voltages. Eventually, the latch operates and makes its decision. Over the past few decades, various techniques have been investigated to outperform the SA latch. Schinkel et al. [19] introduced a two-stage dynamic comparator that separates the latch stage from the preamplifier, thus accelerating comparison speed. However, the latch's input starts from in the triode region, equivalently reducing the pregain and degrading the overall accuracy. To address this, Miyahara and Matsuzawa [20] and van Elzakker et al. [21] modified this by ensuring the latch's input transistor starts in the saturation region, reducing the comparator offset and noise. Hsieh and Hsieh [22] proposed cascaded input pairs for higher preamplifier gain through vertical stacking of input transistors, resulting in an improvement of energy efficiency.

Another observation is that the load capacitor  $C_X$  of the preamplifier (preamp) discharges completely during the comparison, thus consuming a fixed amount of energy:  $2C_X$  $V_{\rm DD}^2$ . A large  $C_X$  is usually required to suppress the noise, and so this energy consumption often dominates in a lownoise comparator design. Hence, there is a strong need to improve the preamp's energy efficiency. Liu et al. [23] presented a bidirectional dynamic comparator to save the preamp's reset power. The preamp consists of nMOS and pMOS input pairs. During the first half of the amplification, the pMOS input turns on, and the preamp outputs are charged up from the ground. Once the preamp outputs exceed  $V_{DD}/2$ , the pMOS side turns off and the nMOS pair continues the second half of amplification, restoring the preamp outputs to their initial state at the end of the amplification. This avoids reset power, while still achieving the same gain and noise performance as the conventional design.

Although only the initial portion contributes to the noise performance, the preamp's load capacitors are fully discharged [24], [25]. Bindra et al. [26] proposed a dynamically biased preamp to address this issue by incorporating a degeneration capacitor at the source of the input pair. This dynamically turns off the gate-source voltage  $V_{\rm GS}$  of the input pair and prevents the load from being fully discharged. In addition, the reduced  $V_{\rm GS}$  boosts the  $g_m/I_D$ , which increases its gain, resulting in an improvement of energy efficiency. Tang et al. [27] further improved energy efficiency by introducing the floating inverter amplifier (FIA). As shown in Fig. 4(b), a CMOS inverter is adopted as a preamp, but its power supply is connected to a floating reservoir capacitor that ensures a constant common-mode output voltage. It elongates the amplification time and increases the gain. It avoids the common-mode discharge of the loading capacitor, resulting in significant energy savings. In addition, the reservoir capacitor makes the gain insensitive to input common-mode voltage and PVT variations and boosts the preamp's  $g_m/I_D$  similar to [26]. Therefore, a dynamic comparator with an FIA preamp showed a  $7 \times$  improvement in energy efficiency compared to the SA latch.

# B. SYSTEM-LEVEL COMPARATOR POWER REDUCTION TECHNIQUES

In addition to optimizing the standalone comparator, many architecture-level solutions have been explored to reduce the comparator power consumption. Note that only one of the comparisons during SAR conversion has a differential input that is less than half LSB. In theory, it must be ensured that the comparator's noise is minimal during this critical comparison. Given this, Harpe et al. [28] proposed a judgment circuit to identify the critical comparison cycle by detecting the comparison time. Once identified, it repeats the comparison multiple times and adopts the majority result, effectively reducing the comparator noise. Accordingly, a comparator can be reconfigured into a low-noise mode for critical decisions.

Another approach is to provide redundancy in SAR conversion that can tolerate errors in earlier bits. Based on that, Giannini et al. [29] proposed a two-comparator scheme, where the low-power comparator in the early bits and the low-noise comparator for the last few bits after the redundancy. Harpe et al. [30] further simplified the comparator design by proposing a load-switching comparator that dynamically changes the comparator's loading capacitor, thus changing its noise performance, without incurring an offset mismatch as in the two-comparator approach. In addition, statistical estimations were explored to improve the energy efficiency of the comparator. By utilizing the maximum-likelihood estimator (MLE) [31] or Bayes estimator (BE) [32], the residue voltage of the comparator input can be estimated, which is used to reduce the noise of SAR ADCs effectively.

## C. CDAC DESIGNS AND CDAC SWITCHING TECHNIQUES

DAC switching is one of the power contributors in SAR ADCs that often limits energy efficiency. To reduce switching energy, the capacitive DAC (CDAC) is commonly used and should be sized to match the thermal noise limit to achieve the best power and area efficiency. However, this is usually impeded by the minimum capacitor size offered by the foundries. The use of custom metal–oxide–metal (MOM) capacitors is becoming increasingly popular. For instance, Harpe et al. [33] reported a CDAC array with a 0.5-fF unit capacitor, and Huang et al. [34] enclosed the top plate of the CDAC with the bottom plate, reducing the parasitic effects

#### 148

| TABLE 1. | Average Switching Energy of a 10-Bit SAR ADC [15] | - |

|----------|---------------------------------------------------|---|

|----------|---------------------------------------------------|---|

| Architecture           | Conversion<br>energy $(CV^2)^*$ | Reset<br>energy (CV <sup>2</sup> )* | Normalized total energy | No. of<br>unit cap** |

|------------------------|---------------------------------|-------------------------------------|-------------------------|----------------------|

| Conventional           | 682.65                          | 0                                   | 1                       | 2 <sup>N+1</sup>     |

| Monotonic              | 255.5                           | 0                                   | 0.37                    | 2 <sup>N</sup>       |

| <b>Bi-directional</b>  | 42.7                            | 191.5                               | 0.34                    | 2 <sup>N-1</sup>     |

| V <sub>cm</sub> -based | 170.2                           | 0                                   | 0.25                    | 2 <sup>N</sup>       |

| Split-cap              | 170.2                           | 255.5                               | 0.63                    | 2 <sup>N+1</sup>     |

\* Normalized to the same V<sub>FS</sub> and C<sub>dac</sub>

\*\* Calculated for a N-bit differential SAR DAC

associated with the top plate. A unit-length capacitor consists of two strips, the capacitor value of which is defined by the difference in the strip length, giving a unit capacitor of 125 aF [35].

Besides the capacitor size reduction, various switching techniques for the CDAC array have been investigated. The conventional switching technique is a trial-and-error approach [36]. About 50% of switching energy goes into the reset operation, which is quite power consuming. To overcome these limitations, CDAC switching techniques have been explored. Liu et al. [37] proposed the monotonic switching technique. By employing top plate sampling and resetting the DAC's bottom plates to  $V_{refp}$ , the reset power and the MSB switching power are eliminated. However, changing the top-plate common-mode voltage can degrade the ADC linearity due to the varying comparator offset [38]. Sanyal and Sun [39] presented the bidirectional switching technique. The MSB capacitors are reset to the opposite reference, reducing the common-mode variation. Zhu et al. [40] reported the  $V_{\rm cm}$ -based switching technique. The DAC's bottom plates are connected to  $V_{\rm cm}$ , eliminating the reset power and keeping the common-mode voltage constant. To eliminate the use of additional V<sub>cm</sub>, Ginsburg and Chandrakasan [41] split each capacitor into two equal subcapacitors that are reset to  $V_{refp}$  and  $V_{refn}$ , respectively. This is equivalent to the V<sub>cm</sub>-based switching, but it brings reset power. Tai et al. [42] introduced a more systematic approach called a detect-and-skip (DAS) technique, where a small coarse DAC resolves the first few MSB bits, while the large fine DAC resolves the remaining LSBs. The MSB results are applied directly to the fine DAC, avoiding unnecessary switching. The DAS technique is widely used, especially for designs requiring large DAC arrays. Table 1 compares the average conversion energy, reset energy, and the total number of required unit capacitor elements. The designers should also notice that with the unit capacitor size reduction, capacitor mismatches may become the limitation of the ADC linearity. Powerful techniques have been proposed to address this concern, including calibration [43] and mismatch error shaping [44].

#### D. KT/C CANCELATION TECHNIQUE

The sampling kT/C noise represents a fundamental SNR limit for discrete-time (DT) ADCs and the SAR ADC is no exception. The limitation of the DAC switching energy still comes from the DAC size, which is determined by

FIGURE 5. Active sampling circuit with a 2-stage amplifier [46].

FIGURE 6. SAR ADC with kT/C noise cancelation [47].

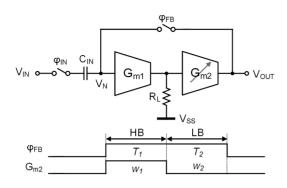

the kT/C noise limit. Hence, it is highly desirable to figure out ways to reduce the capacitor size without incurring a kT/C noise penalty. Kapusta et al. [45] proposed a sampling circuit with a kT/C noise cancelation. Inspired by [45], Li et al. [46] explored an active sampler, which decouples the noise PSD and BW. This is achieved by using an active sampling circuit with a specially designed two-stage amplifier, as shown in Fig. 5. The input-referred noise PSD is inversely proportional to the first stage  $g_{m1}$ . By placing the dominant pole at the second-stage output, the noise BW is proportional to  $g_{m1}r_{o1}g_{m2}$ , where  $r_{o1}$  is the first-stage output impedance. It successfully decouples the noise PSD and BW and, thus, the total integrated noise is presented in the form of  $r_{o1}g_{m2} \times kT/C$ . By introducing a switchable  $g_{m2}$  stage, this work provides high bandwidth initially for signal sampling and low bandwidth toward the end for noise reduction.

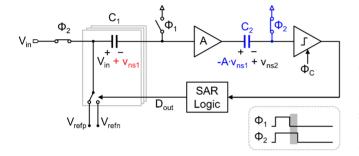

A more popular design is proposed in [47], as shown in Fig. 6, which is also inspired by [45]. In a classic SAR ADC, a capacitor  $C_2$  and a switch  $\phi_2$  are added to form an additional sampling stage at the preamp output. When the  $\phi_1$  phase is complete, the sampling kT/ $C_1$  noise across  $C_1$  is represented as an offset at the preamp input. During the  $\phi_2$  phase, it is amplified and stored via the  $C_2$ . Since the  $C_2$  operates as an offset cancelation capacitor, the kT/ $C_1$ noise at the comparator input is canceled. The sampling noise on  $C_2$  can be attenuated by the preamp gain. Hence, both  $C_1$  and  $C_2$  can be small without introducing excessive noise penalty. Although an additional preamp is required, it is worth considering the substantial power and area savings for the ADC input driver and reference buffer. Although the kT/C cancelation technique is relatively new, it has been

FIGURE 7. Frequency response of a ring amplifier.

quickly adopted by the community and is widely used in emerging energy-efficient ADC designs [48], [49], [50], [51].

# IV. DESIGN TECHNIQUES FOR PIPELINING AND NOISE-SHAPING

Pipelining and NS are effective ways to improve the resolution of ADCs. Especially in combination with SAR ADCs, the high energy efficiency can be maintained even for medium-to-high resolution applications. Such an ADC requires two additional blocks: 1) the residue amplifier for pipelining operation and/or 2) the loop filters for NS operation. This section surveys emerging techniques for implementing residue amplifiers and loop filters.

## A. LOW-POWER RESIDUE AMPLIFIERS

A pipelined SAR ADC typically consists of two lowresolution SAR ADCs coupled with a residue amplifier. However, the use of a conventional OTA-based amplifier consumes a significant amount of power and, thus, the design of an energy-efficient residue amplifier is essential to improving energy efficiency.

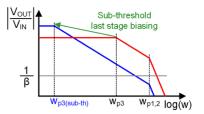

### 1) RING AMPLIFIER

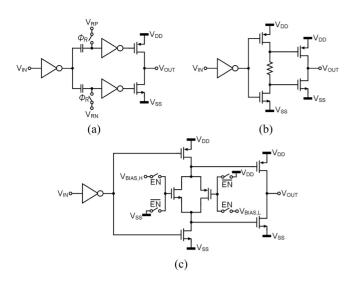

Hershberg et al. [52] proposed a ring amplifier, which is essentially a three-stage inverter-based amplifier, but the differentiated stabilization strategy makes the ring amplifier more efficient than conventional multistage OTAs. The multistage OTAs typically use frequency compensation to form the dominant pole at the first-stage output and push the other poles of subsequent stages to sufficiently higher frequencies, requiring a significant power consumption, thus leading to their efficiency reduction. A ring amplifier employs an opposite stabilization strategy for higher energy efficiency. In the steady state, a ring amplifier forms the dominant pole at the last stage output  $(w_{p3(subth)}$  in Fig. 7) by operating the last stage in the subthreshold region, while maximizing the bandwidth of internal amplifier nodes  $(w_{p1,2})$  in Fig. 7). This subthreshold operation minimizes the static current and also provides the benefit of relatively higher stage gain and near rail-to-rail output swing. It also provides a reasonably constant open-loop gain. On the other hand, during its slewing, the ring amplifier fully drives to achieve maximum drive strength from the last stage. This dynamic operation provides the core benefit of the ring amplifier: slew-based charging. Even with small last-stage transistors, the ring amplifier can still produce a high slew rate, which

FIGURE 8. Ring amplifiers in the literature. (a) First [52], (b) Self-biased [55], and (c) CMOS switch biased [55], [58].

means that the second stage can be loaded minimally and, thus, a nondominant pole is easily formed. Furthermore, the multistage configuration enables high gain. To achieve the dynamic biasing of the last stage, the first ring amplifier [52] splits the second stage into two paths and applies an offset voltage to the second-stage inputs using floating capacitors, as shown in Fig. 8(a). However, the offset voltage is sensitive to PVT variations and, thus, requires additional trimming or digital calibration [53]. This offset voltage is later moved to the third-stage inputs without splitting the second stage [54] to control the last-stage bias more precisely.

Lim and Flynn [55] eliminated the need for an external bias by using a resistor placed between the drains of the second inverter, as shown in Fig. 8(b). The resistor dynamically generates the last-stage biases by using the short circuit current of the second stage. The self-biasing technique is further employed in the fully differential version [56], which consists of a current-reused differential pair for the first stage. This demonstrates robustness to variations in supply voltage and temperature. The self-biasing technique is also applied to the first stage with a reverse offset to improve the bandwidth and slew rate of the second stage [57], [59]. However, it relies on absolute resistance, which can lead to instability due to small offset, or slow settling and reduced gain due to excessive offset. To address this issue, a tunable resistor based on a CMOS switch [55], [58] was used, as shown in Fig. 8(c). However, extra care is required to achieve PVT robustness, such as monitoring the ring amplifier behavior using an on-chip stochastic ADC [60], [61], or background digital calibration [62]. To achieve robust PVT biasing, instead of a self-biasing resistor, a floating current source is used like a class-AB biasing circuit [49], [63]. The second-stage inputs are individually biased with the current mirrors during the sampling phase, and the bias voltages are stored on capacitors.

FIGURE 9. (a) Dynamic amplifier with common-mode voltage detector [65] and (b) operation waveform.

For high-resolution ADCs, a composite ring amplifier [54] has been introduced, consisting of a coarse ring amplifier with fast slew but low gain, and a fine ring amplifier with high gain but slow slew. The coarse ring amplifier automatically turns off after slewing, and then the fine ring amplifier takes over high gain amplification. It achieved 75.9-dB SNDR at 20 MS/s and consumed 2.96 mW, resulting in 171.2-dB FoM<sub>S</sub>. A similar strategy is applied in [64], utilizing two parallel output stages. The ADC achieved 91-dB SNDR at 15 MS/s and consumed 9.8 mW, resulting in 179.8-dB FoM<sub>S</sub>. For high-speed operation [58], [59], [60], [61], [62], [63], the gain of the ring amplifier is compromised to achieve a high slew rate and wide bandwidth, but this is also aided by the gain calibration. A single-channel ADC using ring amplifiers [58] achieved 58.1-dB SNDR with firstorder gain calibration at 600 MS/s and consumed 14.5 mW, resulting in 161.9-dB FoM<sub>S</sub>. The linearity of the fast ring amplifier is further improved in [59], and the ADC achieves 57.1-dB SNDR at 1 GS/s while consuming 24.8 mW.

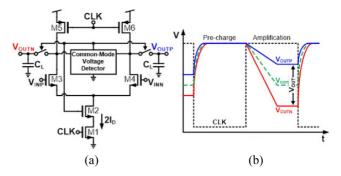

### 2) DYNAMIC AMPLIFIER

Most dynamic amplifiers [65], [66], [67], [68], [69], [70], [71], [72], [73] are basically  $G_m$ -C integrators that stop integration when the integrated output reaches a desired gain. This can be used as an energy-efficient open-loop residue amplifier. One of the early approaches to control the integration time is the technique of detecting the commonmode voltage at the output [65], as shown in Fig. 9(a). The dynamic amplifier operation is described in Fig. 9(b). When a clock is low, the output load capacitors  $C_L$  are precharged to the supply voltage. As the clock goes high, the tail current source  $(M_1)$  turns on, and as a result, the outputs start discharging and integrating the differential output current of  $G_m \times V_{IN}$  on the load capacitors, where  $G_m$ is the transconductance of the input transistors  $(M_3$  and  $M_4$ ). The integration continues until the output commonmode voltage reaches the desired common-mode voltage  $(V_{\rm COM})$ . The common-mode voltage detector then stops the tail current, thereby finishing the integration. The gain of the dynamic amplifier is expressed as  $G_m \times T_{int}/C_L$ , where  $T_{\rm int}$  is the integration time. The dynamic amplifier also filters out the input noise with the integrator noise bandwidth

FIGURE 10. (a) Schematic of the capacitively degenerated dynamic amplifier [74] and (b) its timing diagram.

of  $1/2T_{int}$ . However, the gain of this dynamic amplifier is relatively small ( $\leq 10$ ) due to the limited output commonmode voltage swing range. Furthermore, the open-loop gain is sensitive to PVT variations and, thus, requires continuous background analog or digital calibration for the residue amplification [66], [67], [68], [69], [70].

There are several approaches to improve the gain of dynamic amplifiers, suitable for residue amplifiers. The cascode integrator [68] increases gain by extending the effective output common-mode voltage swing through two-step integration. The cascode device automatically switches the integration current between two integration capacitors as soon as the first integration turns on the cascode device. The resulting dynamic amplifier gain is about  $16\times$ , which is applied in an 80-MS/s pipelined SAR ADC, achieving 68-dB SNDR and 172.3-dB FoM<sub>S</sub> with background digital gain calibration. Another approach is to add fixed bypass currents [71], which reduce the common-mode charging current of the  $C_L$ , thus increasing the integration time and gain. The resulting gain is  $13.3\times$ , which is applied in a 132-MS/s 5-MHz bandwidth NS SAR ADC, yielding 79.74-dB SNDR and 180.1-dB FoM<sub>S</sub>.

A PVT-stabilized dynamic amplifier has been actively investigated. Huang et al. [72] eliminated the need for background gain calibration and achieved impressive PVT robustness; low gain variation of 1.5% and 1.2% at a supply voltage ranging from 1.25 to 1.35 V and a temperature ranging from -5 °C to 85 °C, respectively. The  $T_{int}$  of the dynamic amplifier is determined to be proportional to  $C_L/G_m$ using the slew rate of a replica amplifier. The technique is applied in a 330-MS/s pipelined SAR ADC, which achieves a 67.7-dB SNDR and 171.9-dB FoM<sub>S</sub> with only foreground analog gain calibration.

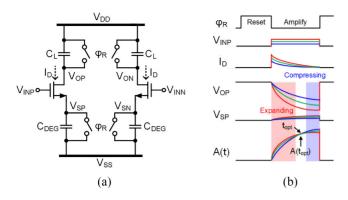

Akter et al. [74] introduced a capacitively degenerated dynamic amplifier (Fig. 10) which is a completely different approach. The weak inversion input pair provides an exponential V–I relation, and a charge transfer-based amplification occurs with a degeneration and load capacitors ( $C_{\text{DEG}}$  and  $C_L$ ). After capacitors are reset,  $C_{\text{DEG}}$  is charged with  $I_D$  and  $V_S$  is started to increase (gain (A(t)) expanding). As  $C_{\text{DEG}}$  is charged, it becomes strongly degenerating

FIGURE 11. Schreier's FoMs versus speed of NS ADCs from 2012 to present according to loop filter implementation based on [6].

the input pair, and A(t) exhibits compression. The crossing point between expanding and compressing  $(t_{opt})$  ensures linear signal-independent gain  $A(t_{opt})$  of  $C_{DEG}/(2nC_L)$  (n =weak inversion slope-factor). Kim et al. [75] investigated a weak inversion slope-factor (n) compensation to further improve the linearity. By adding a degeneration MOS pair cross-coupled to the outputs, it achieves 11.4-dB SFDR improvement compared to [74]. A PVT-robust capacitively degenerated dynamic amplifier was introduced in [76] which is used as a residue amplifier of pipeline SAR ADC. The ADC achieves 65-dB SNDR and 79.8-dB SFDR at 50 MS/s, and 0.7/1.86-dB SNDR variations over 0.8–1.0-V supply and 0 °C–100 °C temperature variation using an on-chip timing generator.

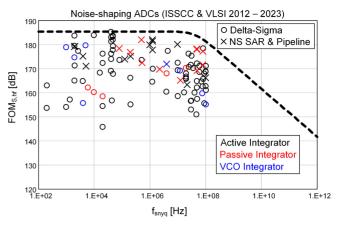

### **B. LOW-POWER LOOP FILTERS**

The loop filters are one of the key building blocks in NS ADCs that determine energy efficiency and are implemented in different ways depending on the target applications. The loop filters of NS SAR ADCs can be simplified than  $\Delta\Sigma$  ADCs, because they normally process a small residue, and many recent NS SAR ADCs are implemented without OTAs. In  $\Delta\Sigma$  ADCs, however, active integrators are dominantly used, which normally aim for a higher SQNR, and the loop filters handle a large residue with a small number of quantizer bits, compared to NS SAR ADCs. Fig. 11 shows NS ADCs (BW  $\leq$  50 MHz) that have been presented at ISSCC and VLSI symposium [6]. They can be classified by their implementations: 1) passive integrator; 2) active integrator; and 3) VCO-based integrator.

## 1) PASSIVE INTEGRATORS

The passive integrators have advantages over the others in the perspective of simplicity, PVT robustness, and power consumption. However, they suffer from insufficient gain and a lack of driving capability. Therefore, the recent advances in energy efficiency are being made in NS SAR ADCs rather than  $\Delta\Sigma$  ADCs. There are three strategies for passive integrators: using 1) a multi-input comparator;

FIGURE 12. NS technique using capacitor stacking and buffering [12].

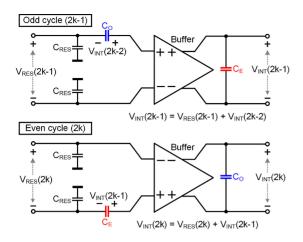

2) a capacitor-stacking technique; or 3) an interstage gain (or buffer) between passive integrators. Fredenburg and Flynn [77] introduced the use of a multi-input comparator. The multiple signal and residue inputs are matched to the filter's coefficients and added to the current domain, allowing for improved NS with the passive integrators. Although the additional input path results in increased noise, it is simple and power efficient, and is therefore becoming popular [78], [79], [80], [81], [82], [83], [84], [85]. The noise penalty of the multi-input comparator can be avoided by using a capacitor-stacking technique [86]. Each residue is sampled into multiple capacitors and stacked in a series configuration to obtain the desired gain. The parasitic capacitance of the stacked capacitors can limit the number of stacking (and, thus, the gain) and contribute to gain error. Therefore, careful design is required to minimize top/bottom parasitic capacitance. A few outstanding NS ADCs show up, achieving an FoM<sub>S</sub> of 178 dB [87]. An interstage gain (or buffer) has been used in [12], [88], [89], and [90], allowing cascading of passive integrators without gain loss and implementation of a high-order NS. In particular, Liu et al. [12] implemented a fourth-order NS using a unity-gain buffer and a capacitor stacking technique for the residue integration and achieved 93.3-dB SNDR and FoM<sub>S</sub> of 182 dB. Fig. 12 shows a simple first-order example, where the integration is realized by stacking a residue capacitor ( $C_{\text{RES}}$ ) and an integration capacitor ( $C_O$  or  $C_E$ ) and the stacking result is stored on the output capacitor ( $C_E$  or  $C_O$ ) of the buffer. Even and odd phases are achieved by shuffling  $C_E$  and  $C_O$ . In this way, four groups of capacitors and buffers achieve the fourth-order NS, which is very energy efficient and robust to PVT variations.

## 2) ACTIVE INTEGRATORS

Loop filters using active integrators provide high gain and driving capability, which offers lots of freedom in architecture development. Since the first integrator has a substantial influence on the overall ADC performance, the research efforts aimed at improving the 1st integrator's noise, linearity, and energy efficiency. An inverter-based integrator is widely

FIGURE 13. CT  $\Delta \Sigma$  ADC with OTA stacking [111].

used because of its simplicity and noise efficiency [31], [91], [92], [93], [94], [95], [96], [97], [98], [99], [100], [101], [102]. It was first investigated in  $\Delta\Sigma$  ADCs [91], [92] and remains popular today, regardless of DT or CT loop filters. Recently, an inverter-based dynamic integrator has been investigated to improve energy efficiency [14], [50], [103], [104], [105]. For example, Tang et al. [14] used a twostage FIA as a loop filter, allowing an aggressive NTF with PVT tolerance. Wang et al. [50] introduced an error-feedback (EF)-CIFF loop filter with an open-loop FIA to obtain thirdorder NS, thus achieving outstanding FoMs of 182 dB. This is further developed into a fourth-order loop filter [103]. Liu et al. [104] used an FIA in an incremental zoom ADC to realize self-timed operation. A single-stage FIA using the correlated level shifting (CLS) technique was introduced by Hu et al. [105] to increase the loop filter's gain.

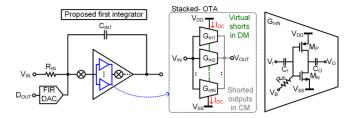

Steiner and Greer [97] introduced integrator-stacking to improve energy efficiency. However, it requires a high supply voltage and extra effort to deal with the integrator's mismatch. In [106], a dynamic power reduction in an incremental  $\Delta\Sigma$  ADC is introduced by utilizing nonuniform weights in a cascade-of-integrator (CoI) filter. Using the same principle of nonuniform CoI filter weights as [106], [107] has implemented a single-bit to multibit reconfigurable incremental DSM taking advantage of a first phase intrinsically linear single-bit DAC and a second phase multibit operation with low quantization noise, in order to achieve 104-dB DR and 106-dB SFDR. Chandrakumar and Markovic [108] added a capacitively coupled gain stage before the 1st integrator in the  $\Delta\Sigma$ -loop, which effectively reduces the noise and power of the loop filter. An OTA-stacking introduced in [109] improves the noise-current tradeoff [110]. Mondal et al. [111] used stacked OTA in the first integrator, as shown in Fig. 13. The AC-coupled inverters are stacked and reuse the current, and they are differentially decoupled with their source nodes, effectively shorted. Therefore, with a 3-stack OTA, the CT  $\Delta\Sigma$  ADC obtains  $3 \times$  Gm-boosting, thus achieving a SOTA FoM<sub>S</sub> of 183.3 dB.

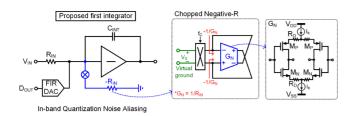

Jang et al. [112] introduced a negative-R (NR) assisted integrator. By including NR at the integrator's virtual ground, OTA noise (both thermal and 1/f noise) is attenuated and the integrator's distortion is also canceled, thus significantly improving the energy efficiency. To reduce 1/f noise for narrowband applications, the chopped OTAs are widely used, but chopping in CT  $\Delta\Sigma$  ADCs causes quantization-noise

FIGURE 14. CT  $\Delta\Sigma$  ADC with chopped NR [114].

folding [113]. In [114], the chopped NR is applied to the first integrator (Fig. 14). The OTA noise is attenuated by the NR [115], and then NR is chopped to remove its 1/f noise. With the chopped NR, the *O*-noise aliasing can be reduced by 30 dB compared to the chopped OTA [116]. Therefore, the CT  $\Delta\Sigma$  ADC with the chopped NR achieves an FoM<sub>S</sub> of 181.9 dB.

Lee and Moon [117] proposed the single-ended ring amplifier with the pseudo-pseudo-differential (PPD) architecture in the first integrator. The pole of the first stage is placed out-of-band so that the stability of the second and third stages is not compromised. The steady-state bandwidth is also kept low to filter the noise in the first stage, which provides additional area and power savings. The DT  $\Delta\Sigma$  ADC with PPD-based ring amplifier [118] achieves an FoM<sub>S</sub> of 185.3 dB with an area of  $0.0375 \text{ mm}^2$ .

### 3) LOOP FILTERS WITH VCO INTEGRATORS

Loop filters using VCO integrators are relatively new and offer several advantages over the active or passive integrators in the perspective of infinite dc gain, power efficiency, and scaling friendliness. However, the VCO integrator usually suffers from VCO nonlinearity that limits the linearity performance. Therefore, architectural development and circuit techniques to improve VCO linearity or circumvent this issue have been investigated.

A VCO-based integrator in [119] consists of two pseudodifferential  $G_m$ -CCOs and their calibration unit. The use of an open-loop  $G_m$ -CCO limits the NS to the first order and requires its calibration to cancel out the large nonlinearity. In [120], the VCO is placed in a feedback loop, which significantly improves the linearity. In [121], a third-order loop filter was implemented with VCO-based integrators, which however suffers from VCO nonlinearity and limits the ADC linearity. In [122], passive and VCO integrators were combined by using a parasitic capacitor at the VCO input. While a second-order loop filter was achieved, its SNDR was still limited to less than 70 dB.

More recently, Huang et al. [123] introduced differential pulse-code modulation (DPCM) to make the VCO processes a small error, thereby minimizing VCO nonlinearity. With an OSR of 32, -40-dB signal attenuation was achieved at the VCO input, significantly improving its linearity and achieving -105-dB THD. However, this requires a high-resolution 11-bit DAC and is truncated to 9 bits, resulting in a truncation error and, hence, SQNR leakage. To address this issue,

FIGURE 15. VCO-based  $\Delta \Sigma$  ADC with PVG feedforward technique [125].

a noise shaping of truncation error was introduced in [124], and excellent efficiency was achieved.

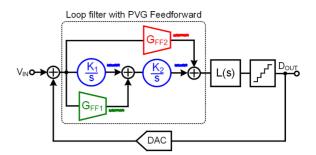

Pochet et al. [125] implemented a third-order  $\Delta\Sigma$  ADC with VCO-based integrators, whose nonlinearity is leveraged with a pseudo-virtual ground (PVG) feedforward technique (Fig. 15). The VCO-based integrator uses a  $G_m$ -CCO followed by a phase-frequency detector (PFD) that extracts the integrator's phase difference and whose outputs control the current in the next-stage CCO. The first integrator input, i.e., the PVG node of the ADC, is tapped and forwarded to the other integrators' outputs using  $G_m$ -cells, which reduces the signal swings significantly. As a result, it achieved 92.1-dB SNDR with a 1.8-V input and a FoMs of 179.6 dB.

### V. TECHNIQUES FOR CONTINUOUS-TIME ADCS A. LOW POWER $\Delta \Sigma$ ADCS

$\Delta\Sigma$  ADCs have classically been used for highest resolution ADCs and achieved the best energy efficiencies in their class. Over the past two decades, their operating frequencies have expanded from classical narrowband audio and sensor readout applications to wideband applications [126], mainly due to the benefits of their CT implementation. While a few years ago, there was a distinct Nyquist gap for high-efficiency and high-resolution ADCs, i.e., there were mainly  $\Delta\Sigma$  ADCs in the leading front. It is very interesting to note that concerning energy efficiency Nyquist rate ADCs are in the lead across all frequency ranges in Fig. 1 nowadays.  $\Delta\Sigma$  ADCs still dominate the high-resolution domain from narrowband up to about 1-GS/s Nyquist frequency, but a few outstanding Nyquist converters appear in the 1-10-MS/s conversion range [9]. Next, we take a look at the leading front, discussing which architectures promise the best power efficiency in the narrowband and wideband, and which techniques yield the best resolution (see Figs. 1-3).

# 1) TECHNIQUES FOR NARROWBAND $\Delta\Sigma$ ADCS

Over the last few years, several zoom ADCs have been reported that achieve both high energy efficiency and high resolution. Chae et al. [94] originally proposed for a quasistatic input, where a coarse SAR ADC performed a single conversion per Nyquist clock cycle that set the reference levels of an incremental  $\Delta\Sigma$  ADC. This operation originally defined the name zoom ADC. On the contrary, more recent zoom ADCs justified as the coarse ADC runs on the same clock frequency as the  $\Delta\Sigma$  ADC, which allows continuous updating of the reference and, thus, uses wider bandwidth. This implementation achieved outstanding resolution and efficiency in [98], where a dynamic zoom ADC was proposed over a 1-kHz band, in [101] over an audio bandwidth, and over a 50-kHz band in [127]. From an architectural point of view, the zoom ADC is the same as the 0-X MASH ADC. The fact that they achieved such a leading position is actually very interesting, as this is also observed in very wideband designs, as will be discussed in Section V-B.

The audio ADC in [128] actually dates from 1997 and still has a distinct spot in SNDR versus  $f_{nyq}$  comparison. In Fig. 2, the work competes with the much more recent work from [126] but achieves an FoM<sub>S</sub> of only 158 dB, about 25 dB worse than the leading SOTA today. Three more energy-efficient audio ADCs are mentioned here, first, the work of Lee and Moon [117], where a DT single-loop  $\Delta\Sigma$  ADC is implemented using ring-amplifier-based integrators in a mature 180-nm CMOS process. Lo et al. [129] proposed a CT  $\Delta\Sigma$  ADC, which offers easier drivability and an implicit anti-aliasing filter, in contrast to [117]. It uses a tri-level DAC like [128] but is based on a currentsteering DAC. Similarly, Jang et al. [114] also used a CT  $\Delta\Sigma$  ADC with a trilevel DAC but additionally employed an FIR DAC [130], [131] and a chopped negative resistor to increase the energy efficiency.

In the sensor and industrial frequency range, we can then highlight a few further designs. First, Theertham et al. [132] implemented again a CT  $\Delta\Sigma$  ADC employing an FIR DAC and chopping, where the chopping artifacts advantageously fall into the FIR notches, as also originally proposed in [130]. Also, this design is implemented in a mature 180-nm technology.

The incremental ADC of Hsieh and Hsieh [10] has a distinct spot in the efficiency comparisons. As an incremental  $\Delta\Sigma$  ADC is actually a Nyquist ADC, but it should not be mentioned in comparison to the  $\Delta\Sigma$  ADC. The design is very low voltage with only a 400mV supply and uses an opamp-less time-domain loop filter. This is an example of the recent trend to employ time-domain signal processing that scales nicely with technology. Finally, the until now fastest published incremental  $\Delta\Sigma$  ADC shall be mentioned [133], which employs an incremental SMASH architecture and variable bit-width to achieve 2 MS/s and an intrinsic linearity of 97 dB.

## 2) TECHNIQUES FOR WIDEBAND $\Delta\Sigma$ ADCS

Wideband  $\Delta\Sigma$  ADC obviously has different demands than narrowband implementations. The excessive sampling frequency is usually avoided, as it poses severe challenges to clock generation, decimation filter operation, and signal integrity in the overall system. From the beginning, therefore, techniques were used that allowed a reduction of the oversampling ratio. Most wideband  $\Delta\Sigma$  ADC are nowadays multibit designs [126], as they come with intrinsically better

FIGURE 16. Block diagram of the CT dual-loop SMASH in [13].

resolution, more aggressive NS, and about 3–4-dB higher maximum stable amplitude (MSA). Only a few exceptional designs have shown that single-bit implementations can compete with the efficiency and performance of their multibit counterparts [134]. Moreover, almost exclusively wideband  $\Delta\Sigma$  ADC are implemented with CT loop filters. The CT loop filter not only offers better drivability due to its resistive or  $G_m$ -based input [135] but also features implicit signal filtering; often reduced to an implicit anti-aliasing filter. It also allows the attenuation of out-of-band interference signals [136], which can be even enhanced by embedding analog [137] or mixed-signal filtering [138]. It is worth noting that such features can lead to significant advantages for a system's complexity and power consumption, but are not covered in any FoM<sub>S</sub> in Figs. 1 and 2.

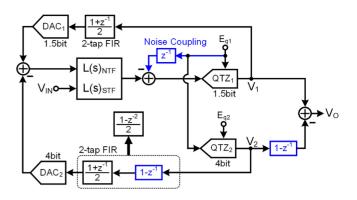

Looking at the front of the SOTAs, it is worth mentioning that most of the leading designs are MASH  $\Delta\Sigma$  ADCs. The early design in [139] is a multibit cascaded 2-2-0  $\Delta\Sigma$  ADC and keeps a distinct spot in the SNDR versus bandwidth (see in Fig. 2). Cenci et al. [100] achieved excellent efficiency for a wideband  $\Delta \Sigma$  ADC, where a coarse SAR ADC and a fine  $\Delta\Sigma$  ADC were used to achieve 0-X MASH, effectively the same architecture as a zoom ADC. Also, Liu et al. [140] employed a 1-1-1 MASH for the incredibly wideband design, achieving a sweet spot in energy efficiency. Qi et al. [13] aimed for extended linearity, where a 3-0 sturdy MASH ADC was employed (Fig. 16), achieving 90-dB linearity without calibration. It was based on a noise-coupled SAR ADC in the first stage and a requantization in the second stage to build the CT Sturdy MASH loop filter. This achieves a leading spot in the resolution comparison, leaving alone that the uncalibrated linearity is not even reflected there. These designs, some of which are at the front of SOTAs in the SNDR or efficiency comparison, suggest that the MASH concept offers distinct advantages.

Nonetheless, other architectures also achieve outstanding performance. He et al. [141] implemented a CT  $\Delta\Sigma$  ADC with excellent linearity. Its third-order multibit loop filter not only uses DAC mismatch correction, but also allows on-chip calibration for unequal DAC rise and fall times and, thus, ISI reduction. Finally, the outstanding wideband designs of Shibata et al. [7] and Shibata et al. [142] should be

mentioned. Shibata et al. [142] was the most wideband  $\Delta\Sigma$  ADC at the time of its publication and allowed to expand the possible performance goals for  $\Delta\Sigma$  ADC into the GHz range. It employs a sixth-order loop filter that can be reconfigured from lowpass to band-pass operation. However, two external inductors were employed for efficient bandpass filtering.

# B. CT- AND DT HYBRID ADCS

Classically, the multibit quantizer in wideband  $CT\Delta\Sigma Ms$  consists mainly of flash ADCs. In this case, the design complexity increases rapidly to increase the quantization bits. It can be leveraged by the energy-efficient ADCs and, thus, early hybridization starts with replacing the flash ADC with the SAR ADC [143], [144], [145], [146]. By embedding the SAR ADC, the quantizer bits are rapidly increased, thus reducing the loop filter order and OSR. However, the introduction of the SAR ADC inevitably brings additional delays. A dedicated delay compensation path is often developed for stability reasons [147]. Also, multibit feedback DAC suffers from mismatch errors that require calibration or dynamic element matching [148].

More hybridization at the architectural level can be considered to further improve performance. Wu et al. [149] introduced noise coupling (NC) in the SAR quantizer. In a SAR operation, the quantization error is naturally produced at the comparator input, which can be easily extracted and fed back into the loop filter for extra NC. It further improves the NS effect and loop-filter stability can be co-designed between the NC SAR and the remaining conventional loop-filter. As a result, it realized a sixth-order NS with a fourth-order loop filter and a second-order NC and achieved a 75.3-dB SNDR at 45-MHz-BW with a low OSR of 10. Jang et al. [150] explored the NC implementation in a digital domain, further simplifying the loop filter design.

The researchers also tried to leverage the recent NS SAR ADCs. Liu et al. [151] proposed to embed a second-order NS SAR in the loop filter and, hence, only one OTA is required to realize the third-order noise shaping. Shi et al. [152] further extended the design by combining a single-amplifierbiquad (SAB) loop filter with a second-order NS SAR. It realizes a fourth-order noise shaping with only one OTA, resulting in exceptional efficiency. Note that the stability of the hybrid fourth-order CT-DT  $\Delta\Sigma$  ADC is similar to a second-order CT  $\Delta\Sigma M$ , which greatly simplifies the loop filter design.

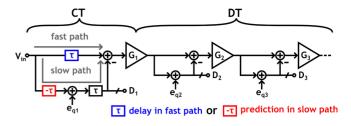

To take full advantage of CT ADCs, some traditional DT architectures are being converted to their CT counterparts. Gubbins et al. [153] proposed incorporating a CT-ADC as the first stage of a pipelined ADC. Together with anti-aliasing filtering, the use of resistive input can greatly simplify the system design. The CT pipeline stage has two delay paths; one comes from the input as the fast path, and the other goes through the first-stage quantizer as the slow path, as shown in Fig. 17. Path delays must be matched to avoid signal overflow in the following stages. Usually, either a positive delay in the fast path [154] or a negative delay

FIGURE 17. Continuous-time pipeline architecture.

(prediction) in the slow path [153] can be added. However, the analog delay suffers from PVT variations and requires careful design. Removing the sampling process improves the ADC conversion speed, e.g., the design in [154] runs at 9 GS/s.

Similarly, Shen et al. [155] introduced the CT 1st stage to the SAR design. With the sampling operation removed, it does not suffer from kT/C noise and, thus, the 13-bit SAR only requires a small DAC of 120 fF. The first stage operates at high speed, minimizing slow path delay. Together with the built-in redundancy, no additional delay is required for path matching. This concept has been extended to other advanced architectures. Li et al. [156] implemented a CT NS SAR for inherent anti-aliasing filtering from the CT front-end and achieved great energy efficiency from the NS SAR. A dutycycled integrator is adopted to deal with the timing conflict between the NS SAR and the CT integrator.

In the past few years, researchers have explored various CT-DT hybrid architectures. The first stage is usually implemented with CT front-ends that feature easy driving, sampling-free, and anti-aliasing filtering. The DT quantizer is used to increase energy efficiency.

### **VI. CONCLUSION**

Over the last ten years, the energy efficiency of ADCs has improved substantially thanks to constant innovations in both architectures and circuits. The available bandwidth of the best FoM ADCs has been expanded by almost the same factor. In this context, the energy efficiency of ADCs is still improving, and these trends are exacerbated by hybrid ADCs. The clear distinction between ADC architectures becomes blurred when looking at the best FoM ADCs that leverage the architecture combinations. Due to many advantages, CT ADCs are gaining more and more attention, and additional hybridization with CT and DT promises successful alternatives to classic architectures.

#### REFERENCES

- R. Walden, "Analog-to-digital converter technology comparison," in *Proc. IEEE GaAs IC Symp.*, 1994, pp. 217–219.

- [2] R. Schreier and G. C. Temes, Understanding Delta-Sigma Data Converters. Hoboken, NJ, USA: Wiley, 2005, pp. 443–446.

- [3] S. Rabii and B. A. Wooley, "A 1.8-V digital-audio sigma-delta modulator in 0.8μm CMOS," *IEEE J. Solid-State Circuits*, vol. 32, no. 6, pp. 783–796, Jun. 1997.

- [4] M. Vogels and G. Gielen, "Architectural selection of A/D converters," in Proc. Design Autom. Conf., 2003, pp. 974–977.

- [5] B. Jonsson. "A/D-converter performance evolution." 2012. [Online]. Available: https://converterpassion.wordpress.com

- [6] B. Murmann. "ADC performance survey 1997–2023." 2023. [Online]. Available: www.stanford.edu/murmann/adcsurvey.html

- [7] H. Shibata, V. Kozlov, Z. Ji, A. Ganesan, H. Zhu, and D. Paterson, "A 9GS/s 1GHz-BW oversampled continuous-time pipeline ADC achieving –161dBFS/Hz NSD," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, Feb. 2017, pp. 278–279.

- [8] R. L. Nguyen et al., "8.6 a highly reconfigurable 40-97gs/s DAC and ADC with 40GHz AFE bandwidth and sub-35fJ/conv-step for 400Gb/s coherent optical applications in 7nm Finfet," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, Feb. 2021, pp. 136–138.

- [9] J. Steensgaard, R. Reay, R. Perry, D. Thomas, G. Tu, and G. Reitsma, "A 24b 2MS/s SAR ADC with 0.03ppm INL and 106.3dB DR in 180nm CMOS," in *Proc. IEEE Int. Solid- State Circuits Conf.* (*ISSCC*), Feb. 2022, pp. 168–170.

- [10] S.-E. Hsieh and C.-C. Hsieh, "A 0.4V 13b 270Ks/s SAR-ISDM ADC with an opamp-less time-domain integrator," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, Feb. 2018, pp. 240–242.

- [11] J.-C. Wang and T.-H. Kuo, "A 0.82mW 14b 130MS/s pipelined-SAR ADC with a distributed averaging correlated level shifting (DACLS) ringamp and bypass-window backend," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, Feb. 2022, pp. 162–164.

- [12] J. Liu, D. Li, Y. Zhong, X. Tang, and N. Sun, "A 250kHz-BW 93dB SNDR 4th-order noise-shaping SAR using capacitor stacking and dynamic buffering," in *Proc. IEEE Int. Solid-State Circuits Conf.* (*ISSCC*), Feb. 2021, pp. 369–371.

- [13] L. Qi, A. Jain, D. Jiang, S.-W. Sin, R. P. Martins, and M. Ortmanns, "A 76.6dB-SNDR 50MHz-BW 29.2mW noise-coupling-assisted CT sturdy MASH ΔΣ modulator with 1.5b/4b quantizers in 28nm CMOS," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, Feb. 2019, pp. 336–338.

- [14] X. Tang et al., "A 13.5b-ENOB second-order noise shaping SAR with PVT-robust closed-loop dynamic amplifier," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, Feb. 2020, pp. 162–164.

- [15] X. Tang et al., "Low-power SAR ADC design: Overview and survey of state-of-the-art techniques," *IEEE Trans. Circuits Syst. I, Reg. Paper*, vol. 69, no. 6, pp. 2249–2262, Jun. 2022.

- [16] W. C. Madden and W. J. Bowhill, "High input impedance, strobed CMOS differential sense amplifier," U.S. 4910713 A, Mar. 1990. Accessed: May 23, 2023. [Online]. Available: https://patents.google. com/patent/US4910713A/en

- [17] T. Kobayashi, K. Nogami, T. Shirotori, Y. Fujimoto, and O. Watanabe, "A current-mode latch sense amplifier and a static power saving input buffer for low-power architecture," in *Symp. VLSI Circuits Dig. Tech. Papers*, Jun. 1992, pp. 28–29.

- [18] J. Montanaro et al., "A 160-MHz, 32-b, 0.5-W CMOS RISC microprocessor," *IEEE J. Solid-State Circuits*, vol. 31, no. 11, pp. 1703–1714, Nov. 1996.

- [19] D. Schinkel, E. Mensink, E. Klumperink, E. van Tuijl, and B. Nauta, "A double-tail latch-type voltage sense amplifier with 18ps setup+hold time," in *Proc. IEEE Int. Solid-State Circuits Conf.* (*ISSCC*), Feb. 2007, pp. 314–605.

- [20] M. Miyahara and A. Matsuzawa, "A low-offset latched comparator using zero-static power dynamic offset cancellation technique," in *Proc. IEEE Asian Solid-State Circuits Conf. (ASSCC)*, Nov. 2009, pp. 233–236.

- [21] M. van Elzakker, E. van Tuijl, P. Geraedts, D. Schinkel, E. A. M. Klumperink, and B. Nauta, "A 10-bit charge-redistribution ADC consuming 1.9μW at 1 MS/s," *IEEE J. Solid-State Circuits*, vol. 45, no. 5, pp. 1007–1015, May 2010.

- [22] S.-E. Hsieh and C.-C. Hsieh, "A 0.44-fJ/conversion-step 11-bit 600-kS/s SAR ADC with semi-resting DAC," *IEEE J. Solid-State Circuits*, vol. 53, no. 9, pp. 2595–2603, Sep. 2018.

- [23] M. Liu, K. Pelzers, R. van Dommele, A. van Roermund, and P. Harpe, "A106nW 10 b 80 kS/s SAR ADC with duty-cycled reference generation in 65 nm CMOS," *IEEE J. Solid-State Circuits*, vol. 51, no. 10, pp. 2435–2445, Oct. 2016.

- [24] P. Nuzzo, F. D. Bernardinis, P. Terreni, and G. V. der Plas, "Noise analysis of regenerative comparators for reconfigurable ADC architectures," *IEEE Trans. Circuits Syst. I, Reg. Paper*, vol. 55, no. 6, pp. 1441–1454, Jul. 2008.

- [25] T. Sepke, P. Holloway, C. G. Sodini, and H.-S. Lee, "Noise analysis for comparator-based circuits," *IEEE Trans. Circuits Syst. I, Reg. Paper*, vol. 56, no. 3, pp. 541–553, Mar. 2009.

- [26] H. S. Bindra, C. E. Lokin, D. Schinkel, A. Annema, and B. Nauta, "A 1.2-V dynamic bias latch-type comparator in 65-nm CMOS with 0.4-mV input noise," *IEEE J. Solid-State Circuits*, vol. 53, no. 7, pp. 1902–1912, Jul. 2018.

- [27] X. Tang et al., "An energy-efficient comparator with dynamic floating inverter amplifier," *IEEE J. Solid-State Circuits*, vol. 55, no. 4, pp. 1011–1022, Apr. 2020.

- [28] P. Harpe, E. Cantatore, and A. van Roermund, "A 10b/12b 40 kS/s SAR ADC with data-driven noise reduction achieving up to 10.1b ENOB at 2.2 fJ/conversion-step," *IEEE J. Solid-State Circuits*, vol. 48, no. 12, pp. 3011–3018, Dec. 2013.

- [29] V. Giannini, P. Nuzzo, V. Chironi, A. Baschirotto, G. Van der Plas, and J. Craninckx, "An 820μW 9b 40MS/s noise-tolerant dynamic-SAR ADC in 90nm digital CMOS," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, Feb. 2008, pp. 238–610.

- [30] P. Harpe, Y. Zhang, G. Dolmans, K. Philips, and H. De Groot, "A 7-to-10b 0-to-4MS/s flexible SAR ADC with 6.5-to-16fJ/conversionstep," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, Feb. 2012, pp. 472–474.

- [31] B. Verbruggen, J. Tsouhlarakis, T. Yamamoto, M. Iriguchi, E. Martens, and J. Craninckx, "A 60 dB SNDR 35 MS/s SAR ADC with comparator-noise-based stochastic residue estimation," *IEEE J. Solid-State Circuits*, vol. 50, no. 9, pp. 2002–2011, Sep. 2015.

- [32] L. Chen, X. Tang, A. Sanyal, Y. Yoon, J. Cong, and N. Sun, "A 0.7-V 0.6 μW 100-kS/s low-power SAR ADC with statistical estimationbased noise reduction," *IEEE J. Solid-State Circuits*, vol. 52, no. 5, pp. 1388–1398, May 2017.

- [33] P. J. A. Harpe et al., "A 26 μW 8 bit 10 MS/s asynchronous SAR ADC for low energy radios," *IEEE J. Solid-State Circuits*, vol. 46, no. 7, pp. 1585–1595, Jul. 2011.

- [34] G.-Y. Huang, S.-J. Chang, Y.-Z. Lin, C.-C. Liu, and C.-P. Huang, "A 10b 200MS/s 0.82mW SAR ADC in 40nm CMOS," in *Proc. IEEE Asian Solid-State Circuits Conf. (A-SSCC)*, Nov. 2013, pp. 289–292.

- [35] P. Harpe, "A compact 10-b SAR ADC with unit-length capacitors and a passive FIR filter," *IEEE J. Solid-State Circuits*, vol. 54, no. 3, pp. 636–645, Mar. 2019.

- [36] J. L. McCreary and P. R. Gray, "All-MOS charge redistribution analog-to-digital conversion techniques. I," *IEEE J. Solid-State Circuits*, vol. 10, no. 6, pp. 371–379, Dec. 1975.

- [37] C.-C. Liu, S.-J. Chang, G.-Y. Huang, and Y.-Z. Lin, "A 10-bit 50-MS/s SAR ADC With a monotonic capacitor switching procedure," *IEEE J. Solid-State Circuits*, vol. 45, no. 4, pp. 731–740, Apr. 2010.

- [38] L. Chen, A. Sanyal, J. Ma, X. Tang, and N. Sun, "Comparator common-mode variation effects analysis and its application in SAR ADCs," in *Proc. IEEE Int. Symp. Circuits Syst. (ISCAS)*, May 2016, pp. 2014–2017.

- [39] A. Sanyal and N. Sun, "SAR ADC architecture with 98% reduction in switching energy over conventional scheme," *Electron. Lett.*, vol. 49, no. 4, pp. 248–250, Feb. 2013.

- [40] Y. Zhu et al., "A 10-bit 100-MS/s reference-free SAR ADC in 90 nm CMOS," *IEEE J. Solid-State Circuits*, vol. 45, no. 6, pp. 1111–1121, Jun. 2010.

- [41] B. P. Ginsburg and A. P. Chandrakasan, "500-MS/s 5-bit ADC in 65-nm CMOS with split capacitor array DAC," *IEEE J. Solid-State Circuits*, vol. 42, no. 4, pp. 739–747, Apr. 2007.

- [42] H.-Y. Tai, Y.-S. Hu, H.-W. Chen, and H.-S. Chen, "11.2 A 0.85fJ/conversion-step 10b 200kS/s subranging SAR ADC in 40nm CMOS," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, Feb. 2014 pp. 196–197.

- [43] H.-S. Lee, D. A. Hodges, and P. R. Gray, "A self-calibrating 15 bit CMOS A/D converter," *IEEE J. Solid-State Circuits*, vol. 19, no. 6, pp. 813–819, Dec. 1984.

- [44] Y.-S. Shu, L.-T. Kuo, and T.-Y. Lo, "An oversampling SAR ADC with DAC mismatch error shaping achieving 105 dB SFDR and 101 dB SNDR over 1 kHz BW in 55 nm CMOS," *IEEE J. Solid-State Circuits*, vol. 51, no. 12, pp. 2928–2940, Dec. 2016.

- [45] R. Kapusta, H. Zhu, and C. Lyden, "Sampling circuits that break the kT/C thermal noise limit," *IEEE J. Solid-State Circuits*, vol. 49, no. 8, pp. 1694–1701, Aug. 2014.

- [46] Z. Li et al., "A SAR ADC with reduced kT/C noise by decoupling noise PSD and BW," in *Proc. IEEE Symp. VLSI Circuits*, Jun. 2020, pp. 1–2.

IEEE Open Journal of the Solid-State Circuits Society

- [47] J. Liu, X. Tang, W. Zhao, L. Shen, and N. Sun, "A 13b 0.005mm<sup>2</sup> 40MS/s SAR ADC with kT/C noise cancellation," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, Feb. 2020, pp. 258–260.

- [48] Z. Wang et al., "A 150kHz-BW 15-ENOB incremental zoom ADC with skipped sampling and single buffer embedded noiseshaping SAR quantizer," in *Proc. IEEE Int. Solid-State Circuits Conf.* (ISSCC), Feb. 2023, pp. 9–11.

- [49] M. Zhan, L. Jie, X. Tang, and N. Sun, "A 0.004 mm<sup>2</sup> 200MS/S pipelined SAR ADC with kT/C noise cancellation and robust ring-amp," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, Feb. 2022, pp. 164–166.

- [50] T. Wang, R. Wu, V. Gupta, and S. Li, "A 13.8-ENOB 0.4 pF-C<sub>IN</sub> 3rd-order noise-shaping SAR in a single-amplifier EF-CIFF structure with fully dynamic hardware-reusing kT/C noise cancelation," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, Feb. 2021, pp. 374–376.

- [51] H. Zhuang, N. Sun, L. Tao, Y. Li, and O. Li, "A fully-dynamic kT/Cnoise-canceled SAR ADC with trimming-free dynamic amplifier," in *Proc. IEEE Custom Integr. Circuits Conf. (CICC)*, 2023, pp. 1–2.

- [52] B. Hershberg, S. Weaver, K. Sobue, S. Takeuchi, K. Hamashita, and U. K. Moon, "Ring amplifiers for switched capacitor circuits," *IEEE J. Solid-State Circuits*, vol. 47, no. 12, pp. 2928–2942, Dec. 2012.

- [53] B. Hershberg, "Ring amplification for switched capacitor circuits," Ph.D. dissertation, Dept. Elect. Eng., Oregon State Univ., Corvallis, OR, USA, Jun. 2012.

- [54] B. Hershberg and U. K. Moon, "A 75.9dB-SNDR 2.96mW 29fJ/convstep ringamp-only pipelined ADC," in *Proc. Symp. VLSI Circuits*, 2013, pp. C94–C95.

- [55] Y. Lim and M. P. Flynn, "A 100 MS/s, 10.5 bit, 2.46 mW comparatorless pipeline ADC using self-biased ring amplifiers," *IEEE J. Solid-State Circuits*, vol. 50, no. 10, pp. 2331–2341, Oct. 2015.

- [56] Y. Lim and M. P. Flynn, "A 1 mW 71.5 dB SNDR 50 MS/s 13 bit fully differential ring amplifier based SAR-assisted pipeline ADC," *IEEE J. Solid-State Circuits*, vol. 50, no. 12, pp. 2901–2911, Dec. 2015.

- [57] Y. Chen, J. Wang, H. Hu, F. Ye, and J. Ren, "A 200MS/s, 11 bit SAR-assisted pipeline ADC with bias-enhanced ring amplifier," in *Proc. IEEE Int. Symp. Circuits Syst. (ISCAS)*, 2017, pp. 1–4.

- [58] J. Lagos, B. Hershberg, E. Martens, P. Wambacq, and J. Craninckx, "A single-channel, 600-MS/s, 12-b, ringamp-based pipelined ADC in 28-nm CMOS," *IEEE J. Solid-State Circuits*, vol. 54, no. 2, pp. 403–416, Feb. 2019.

- [59] J. Lagos, B. P. Hershberg, E. Martens, P. Wambacq, and J. Craninckx, "A 1-GS/s, 12-b, single-channel pipelined ADC with dead-zonedegenerated ring amplifiers," *IEEE J. Solid-State Circuits*, vol. 54, no. 3, pp. 646–658, Mar. 2019.

- [60] B. Hershberg, N. Markulić, J. Lagos, E. Martens, D. Dermit, and J. Craninckx, "A 1-MS/s to 1-GS/s ringamp-based pipelined ADC with fully dynamic reference regulation and stochastic scope-onchip background monitoring in 16 nm," *IEEE J. Solid-State Circuits*, vol. 56, no. 4, pp. 1227–1240, Apr. 2021.

- [61] B. Hershberg et al., "A 4-GS/s 10-ENOB 75-mW ringamp ADC in 16-nm CMOS With background monitoring of distortion," *IEEE J. Solid-State Circuits*, vol. 56, no. 8, pp. 2360–2374, Aug. 2021.

- [62] J. Lagos et al., "A 10.1-ENOB, 6.2-fJ/conv.-step, 500-MS/s, ringampbased pipelined-SAR ADC with background calibration and dynamic reference regulation in 16-nm CMOS," *IEEE J. Solid-State Circuits*, vol. 57, no. 4, pp. 1112–1124, Apr. 2022.

- [63] M. Zhan, L. Jie, and N. Sun, "A 10mW 10-ENOB 1GS/s ringamp-based pipelined TI-SAR ADC with split MDAC and switched reference decoupling capacitor," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, Feb. 2023, pp. 272–274.

- [64] A. ElShater et al., "A 10mW 16b 15MS/s two-step SAR ADC with 95dB DR using dual-deadzone ring amplifier," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, Feb. 2019, pp. 70–72.

- [65] J. Lin, M. Miyahara, and A. Matsuzawa, "A 15.5 dB, wide signal swing, dynamic amplifier using a common-mode voltage detection technique," in *Proc. IEEE Int. Symp. Circuits Syst. (ISCAS)*, 2011, pp. 21–24.

- [66] B. Verbruggen, J. Craninckx, M. Kuijk, P. Wambacq, and G. Van der Plas, "A 2.6 mW 6 bit 2.2 GS/s fully dynamic pipeline ADC in 40 nm digital CMOS," *IEEE J. Solid-State Circuits*, vol. 45, no. 10, pp. 2080–2090, Oct. 2010.

- [67] B. Verbruggen, M. Iriguchi, and J. Craninckx, "A 1.7 mW 11b 250 MS/s 2-times interleaved fully dynamic pipelined SAR ADC in 40 nm digital CMOS," *IEEE J. Solid-State Circuits*, vol. 47, no. 12, pp. 2880–2887, Dec. 2012.

- [68] F. van der Goes et al., "A 1.5 mW 68 dB SNDR 80 Ms/s 2× interleaved pipelined SAR ADC in 28 nm CMOS," *IEEE J. Solid-State Circuits*, vol. 49, no. 12, pp. 2835–2845, Dec. 2014.

- [69] B. Verbruggen, K. Deguchi, B. Malki, and J. Craninckx, "A 70 dB SNDR 200 MS/s 2.3 mW dynamic pipelined SAR ADC in 28nm digital CMOS," in *Proc. Symp. VLSI Circuits*, 2014, pp. 1–2.

- [70] B. Malki, B. Verbruggen, P. Wambacq, K. Deguchi, M. Iriguchi, and J. Craninckx, "A complementary dynamic residue amplifier for a 67 dB SNDR 1.36 mW 170 MS/s pipelined SAR ADC," in *Proc. Eur. Solid State Circuits Conf. (ESSCIRC)*, 2014, pp. 215–218.

- [71] C.-C. Liu and M.-C. Huang, "A 0.46mW 5MHz-BW 79.7dB-SNDR noise-shaping SAR ADC with dynamic-amplifier-based FIR-IIR filter," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, Feb. 2017, pp. 466–467.

- [72] H. Huang, H. Xu, B. Elies, and Y. Chiu, "A non-interleaved 12-b 330-MS/s pipelined-SAR ADC with PVT-stabilized dynamic amplifier achieving sub-1-dB SNDR variation," *IEEE J. Solid-State Circuits*, vol. 52, no. 12, pp. 3235–3247, Dec. 2017.

- [73] X. Tang, X. Yang, J. Liu, W. Shi, D. Z. Pan, and N. Sun, "A 0.4-to-40MS/s 75.7 dB-SNDR fully dynamic event-driven pipelined ADC with 3-stage cascoded floating inverter amplifier," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, Feb. 2021, pp. 376–378.

- [74] M. S. Akter, K. A. A. Makinwa, and K. Bult, "A capacitivelydegenerated 100dB linear 20-150MS/s dynamic amplifier," in *Proc. IEEE Symp VLSI Circuits*, Jun. 2017, pp. C136–C137.

- [75] Y. Kim et al., "A 41 μW 16 MS/s 99.2 dB-SFDR capacitively degenerated dynamic amplifier with nonlinear-slope-factor compensation," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, Feb. 2020, pp. 358–360.

- [76] H. Yoon, C. Lee, T. Kim, Y. Kwon, and Y. Chae, "A 65-dB-SNDR pipelined SAR ADC Using PVT-robust capacitively degenerated dynamic amplifier," *IEEE J. Solid-State Circuits*, vol. 58, no. 4, pp. 961–971, Apr. 2023.

- [77] J. Fredenburg and M. Flynn, "A 90MS/s 11MHz bandwidth 62dB SNDR noise-shaping SAR ADC," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, Feb. 2012, pp. 468–469.

- [78] Z. Chen, M. Miyahara, and A. Matsuzawa "A 9.35-ENOB, 14.8 fJ/conv.-step fully-passive noise-shaping SAR ADC," in *Proc. IEEE Symp VLSI Circuits*, Jun. 2015, pp. C64–C65.

- [79] Y.-Z. Lin, C.-H. Tsai, S.-C. Tsou, R.-X. Chu, and C.-H. Lu, "A 2.4-mW 25-MHz BW 300-MS/s passive noise shaping SAR ADC with noise quantizer technique in 14-nm CMOS," in *Proc. IEEE Symp VLSI Circuits*, Jun. 2017, pp. C234–C235.

- [80] W. Guo, H. Zhuang, and N. Sun, "A 13b-ENOB 173dB-FoM 2nd -order NS SAR ADC with passive integrators," in *Proc. IEEE Symp* VLSI Circuits, Jun. 2017, pp. C236–C237.

- [81] J. Liu, S. Li, W. Guo, G. Wen, and N. Sun, "A 0.029mm2 17-fJ/conv.-step CT  $\Delta\Sigma$  ADC with 2nd-order noise-shaping SAR quantizer," in *Proc. IEEE Symp VLSI Circuits*, Jun. 2018, pp. C201–C202.

- [82] K. Jeong, G. Yun, S. Ha, and M. Je, "A 600mVPP-input-range 94.5dB-SNDR NS-SAR-nested DSM with 4th-order truncation-error shaping and input-impedance boosting for biosignal acquisitions," in *Proc. IEEE Symp VLSI Circuits*, Jun. 2022, pp. C52–C53.

- [83] Y. Song, Y. Zhu, C. H. Chan, and R. P. Martins, "A 2.56mW 40MHz-bandwidth 75dB-SNDR partial-interleaving SAR-assisted NS pipeline ADC with background inter-stage offset calibration," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, Feb. 2020 pp. 164–165.

- [84] H. Zhang, Y. Zhu, C.-H. Chan, and R. P. Martins, "A 25MHz-BW 75dB-SNDR inherent gain error tolerance noise-shaping SARassisted pipeline ADC with background offset calibration," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, Feb. 2021, pp. 380–381.

- [85] H. Zhang, Y. Zhu, C.-H. Chan, and R. P. Martins, "A 25MHz-BW 77.2dB-SNDR 2nd-order gain-error-shaping and NS pipelined SAR ADC based on a quantization-prediction- unrolled scheme," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, Feb. 2023, pp. 174–175.

- [86] Y.-Z. Lin, C.-Y. Lin, S.-C. Tsou, C.-H. Tsai, and C.-H. Lu, "A 40MHz-BW 320MS/s passive noise-shaping SAR ADC with passive signal-residue summation in 14nm FinFET," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, Feb. 2019, pp. 330–331.

- [87] J. Liu, X. Wang, Z. Gao, M. Zhan, X. Tang, and N. Sun, "A 40kHz-BW 90dB-SNDR noise-shaping SAR with 4× passive gain and 2ndorder mismatch error shaping," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, Feb. 2020, pp. 158–159.

- [88] J. L. A. de Melo, J. Goes, and N. Paulino, "A 0.7 V 256 μW ΔΣ modulator with passive RC integrators achieving 76 dB DR in 2 MHz BW," in *Proc. IEEE Symp VLSI Circuits*, Jun. 2015, pp. C290–C291.

- [89] B. Nowacki, N. Paulino, and J. Goes, "A 1V 77dB-DR 72dB-SNDR 10MHz-BW 2-1 MASH CT ΔΣΜ," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, Feb. 2016, pp. 274–275.

- [90] L. Jie, B. Zheng, H. Chen, R. Wang, and M. P. Flynn, "A 4th-order cascaded-noise-shaping SAR ADC with 88dB SNDR over 100kHz bandwidth," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, Feb. 2020, pp. 160–161.

- [91] Y. Chae, I. Lee, and G. Han, "A 0.7V 36μW 85dB-DR audio ΔΣ modulator using class-C inverter," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, Feb. 2008, pp. 490–491.

- [92] R. van Veldhoven, R. Rutten, and L. J. Breems, "An inverter-based hybrid ΔΣ modulator," in *Proc. IEEE Int. Solid-State Circuits Conf.* (*ISSCC*), Feb. 2008, pp. 492–493.

- [93] Y. Chae and G. Han, "Low voltage, low power inverter-based switched-capacitor Delta-Sigma modulator," *IEEE J. Solid-State Circuits*, vol. 44, no. 2, pp. 458–472, Feb. 2009.

- [94] Y. Chae, K. Souri, and K. A. A. Makinwa, "A 6.3 μW 20 bit incremental zoom-ADC with 6 ppm INL and 1 μv offset," *IEEE J. Solid-State Circuits*, vol. 48, no. 12, pp. 3019–3027, Dec. 2013.

- [95] L. Breems et al., "A 2.2GHz continuous-time ΔΣ ADC with -102dBc THD and 25MHz BW," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, Feb. 2016, pp. 272–273.

- [96] B. Gonen, F. Sebastinao, R. van Veldhoven, and K. A. A. Makinwa, "A 1.65mW 0.16mm<sup>2</sup> dynamic zoom-ADC with 107.5dB DR in 20kHz BW," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, Feb. 2016, pp. 282–283.

- [97] M. Steiner and N. Greer, "A 22.3b 1kHz 12.7mW switchedcapacitor  $\Delta\Sigma$  modulator with stacked split-steering amplifiers," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, Feb. 2016, pp. 284–286.

- [98] S. Karmakar, B. Gönen, F. Sebastiano, R. Van Veldhoven, and K. A. A. Makinwa, "A 280μW dynamic-zoom ADC with 120dB DR and 118dB SNDR in 1kHz BW," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, Feb. 2018, pp. 238–240.

- [99] B. Gonen, S. Karmakar, R. van Veldhoven, and K. A. A. Makinwa, "A low power continuous-time zoom ADC for audio applications," in *Proc. IEEE Symp VLSI Circuits*, Jun. 2019, pp. C224–C225.

- [100] P. Cenci et al., "A 3.2mW SAR-assisted CT ΔΣ ADC with 77.5dB SNDR and 40MHz BW in 28nm CMOS," in *Proc. Symp. VLSI Circuits*, 2019, pp. C230–C231.

- [101] E. Eland, S. Karmakar, B. Gönen, R. van Veldhoven, and K. Makinwa "A 440μW, 109.8dB DR, 106.5dB SNDR discrete-time Zoom ADC with a 20kHz BW," in *Proc. IEEE Symp. VLSI Circuits*, 2020, pp. 1–2.

- [102] S. Lee, S. Park, Y. Kim, and Y. Chae, "A 0.6V 86.5dB-DR 40kHz-BW inverter-based continuous-time delta-sigma modulator with PVTrobust body-biasing technique," in *Proc. IEEE Symp VLSI Circuits*, Jun. 2021, pp. 1–2.

- [103] T. Wang, T. Xie, Z. Liu, and S. Li, "An 84dB-SNDR low-OSR 4th-order noise-shaping SAR with an FIA-assisted EF-CRFF structure and noise-mitigated push-pull buffer-in-loop technique," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, Feb. 2022, pp. 418–419.

- [104] Y. Liu et al., "A 4.96μW 15b self-timed dynamic-amplifier-based incremental zoom ADC," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, Feb. 2022, pp. 170–171.

- [105] Y. Hu, Y. Zhao, W. Qu, L. Ye, M. Zhao, and Z. Tan, "A 2.87µW 1kHz-BW 94.0dB-SNDR 2-0 MASH ADC using FIA with dynamicbody-biasing assisted CLS technique," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, Feb. 2022, pp. 410–411.

- [106] P. Vogelmann, M. Haas, and M. Ortmanns, "A 1.1mW 200kS/s incremental ΔΣ ADC with a DR of 91.5dB using integrator slicing for dynamic power reduction," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, Feb. 2018, pp. 236–237.

- [107] M. A. Mokhtar, O. Ismail, P. Vogelmann, J. G. Kauffman, and M. Ortmanns, "A 40 kS/s calibration-free incremental  $\Delta\Sigma$  ADC achieving 104 dB DR and 105.7 dB SFDR," in *Proc. IEEE Eur. Solid-State Circuits Conf. (ESSCIRC)*, Sep. 2023, p. 9155.

- [108] H. Chandrakumar and D. Markovic, "A 15.2-ENOB continuous-time  $\Delta \Sigma$  ADC for a 7.3 $\mu$ W 200mVpp-linear-input-range neural recording front-end," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, Feb. 2018, pp. 232–233.

- [109] L. Shen, A. Mukherjee, S. Li, X. Tang, N. Lu, and N. Sun, "A 0.6-V tail-less inverter stacking amplifier with 0.96 PEF," in *Proc. IEEE Symp VLSI Circuits*, Jun. 2019, pp. C144–C145.

- [110] S. Mondal and D. A. Hall, "A 13.9-nA ECG amplifier achieving 0.86/0.99 NEF/PEF using AC coupled OTA-stacking," *IEEE J. Solid-State Circuits*, vol. 55, no. 2, pp. 414–425, Feb. 2020.