# Analysis and Optimization of the Loss Distribution for a Two Stage AC/DC Power Supply

# Lukas Fräger and Jens Friebe

**Abstract** This paper presents the analysis and optimization procedure of a two-stage bidirectional AC/DC power supply. The exemplary power supply consists of a silicon carbide based active front end and a dual active bridge DC/DC converter. It is designed to supply 600 V DC applications from universal low voltage AC grids with a power up to 6 kW.

The paper includes the topology and design considerations, as well as an in-depth loss distribution analysis based on a validated loss model. The loss model is then utilized for an operation space optimization. A special focus is drawn to the loss model and the optimization: It is based on analytical equations optimized for a low calculation effort. This enables quick modeling of a large operation space. Those results can both be used to validate design considerations as well as to optimize operating parameters.

The presented dynamic operating parameter optimization enables a loss reduction at full load by 14% and at half load by even 48%. By means of the optimization the operating area can be expanded, losses decreased, and thermal stress reduced.

Index Terms: AC-DC Power Conversion, DC-DC Power Conversion, DC Power Systems, Modeling, Optimization Methods, Power Electronics

# I. INTRODUCTION

N¹URRENT developments in industry and society lead to the need for high power AC/DC power supplies in low voltage grids (e.g. charging stations, energy storages, DCgrids for industry, on board chargers for special vehicles [1] [2] [3] [4]). In addition, bidirectional supplies are favored for future applications to feed power back into the grid (e.g., braking energy, integration of renewables and batteries, vehicle to grid). Energy prices, thermal stress and cost for cooling effort drive the need for highly efficient power supplies with lowest heat dissipation under all operating conditions. Trends in vehicular applications (more electric road, railway, air) as well as stationary applications (cabinet space, machine size) increase the need for more volumeefficient supplies with higher power-densities [5] [6]. A wide input voltage range is required to support universal grid voltages [7].

This paper presents the optimization by operating parameter adaptation of a three phase, 6 kW power supply designed with high power density and high efficiency.

This work was submitted for review to OJPEL Special Compendium on Digital Design of Power Electronics Device and Equipment on 21st Oct. 2023.

This work was partly supported by the German Federal Ministry for Economic Affairs and Climate Action under grant number 03EN2010A-G. Corresponding Author: Jens Friebe.

Lukas Fräger works for Block Transformatoren-Elektronik GmbH, Max-Planck-Str. 36-46, 27283 Verden, Germany (email: lukas.fraeger@block.eu)

Jens Friebe works for the University of Kassel, Wilhelmshöher Allee 71, 34121 Kassel, Germany (email: friebe@uni-kassel.de)

Recently, much work has been published on design space optimization [8] [9] [10] [11]. Design space optimization can help increase efficiency, power density, and reduce cost for a given operating point [11]. However, the results presented in this paper reveal an additional potential of optimizing operating parameters after the design is fixed. Especially in the context of a large operating space (e.g., wide input voltage ranges, adjustable output voltage, partial load operation), the use of an optimization algorithm to find suitable operating parameters (e.g. DC-link voltages, switching frequencies) reduces losses and thermal stress.

Current relevant work on loss models for wide bandgap (WBG) based power converters was, amongst others, published in [12] [13] [14] [15]. The introduced analytical loss model presents a trade-off between calculation speed, accuracy, and flexibility. Compared to the analytical approach in [12], fewer and simpler calculation steps are needed. By differentiating between three transition types, accuracy and usability at high ripple currents is improved compared to [14] [15]. Fastest models as in [13] rely on pre-calculated or measured look-up tables. To increase flexibility, the presented model is based on analytical equations. The magnetics loss model based on [16] [17] is simplified for the specific application in power electronic converters and possibilities for pre-calculation are exploited.

The design of the exemplary power supply (system specification, component, and topology selection) is based on references and is briefly presented in Ch. II and Ch. III. For optimizing design and operation, a detailed, precise yet calculation efficient modeling approach is developed and

explained in detail in Ch. IV. The loss model is verified by comparison to measurement results of a built-up power supply (Ch. V and Ch. VI) and used to optimize its operating parameters for different operating conditions (Ch. VII and Ch. VIII).

#### II. SYSTEM SPECIFICATION

The power supply is designed to supply loads up to 6 kW at a controlled DC output voltage of 600 V from universal three phase low voltage grids. TABLE I gives an overview of different international nominal grid voltages. For universal applicability at affordable cost the supply is specified to work in grids from nominal 200 V to 480 V line to line AC voltage. Support of grids with an AC-voltage of 600 V would have a large influence on component selection and design and would thus counteract a volume and efficiency optimized design.

TABLE I

EXCERPT OF INTERNATIONAL GRID VOLTAGES [7]

| Country / Region | Three Phase line to line grid voltage(s) |

|------------------|------------------------------------------|

|                  |                                          |

| EU               | 400 V                                    |

| USA/Canada       | 208 V, 480 V , 600 V                     |

| Japan            | 200 V                                    |

| China            | 380 V                                    |

The DC output voltage is set to  $V_{DC} = 600 \text{ V}$  with an adjustable range from 550 V to 700 V. The output voltage of 600 V results from the rectified operating voltage range of available off-the-shelf inverters ( $V_{AC,ll} = 380 \text{ V} \dots 480 \text{ V}$ , comp. [18]); the output voltage range enables to comply with different upcoming standards for future DC-grids [2] [4] [19] [20]. For system efficiency optimization the output voltage can be adjusted (lower voltage  $\rightarrow$  lower switching losses, higher voltage  $\rightarrow$  lower conduction losses).

As connections to open DC-grids as in [2] [4] [19] [20] are possible applications for the presented power supply, a galvanic isolation is favored, especially when the grids are supposed to have an independent earthing concept (e.g. grounded  $\Delta$ -AC-grid to mid-point grounded DC-grid). Also, when connecting multiple supplies in parallel, an isolation can help reduce circular currents between the converters.

A resulting exemplary specification is given in Table II. The findings presented in the following chapters may be adopted to any other multi-stage power-electronics based converter.

TABLE II SPECIFICATION OF THE AC/DC-POWER SUPPLY

| Specified Value                   | Value                |

|-----------------------------------|----------------------|

| Input voltage range $(V_{AC,ll})$ | 200 V 480 V          |

| Output voltage ( $V_{DC,Out}$ )   | 600 V (550 V 700 V)  |

| Power                             | 6 kW                 |

| Isolation type                    | Reinforced acc. [21] |

#### III. SYSTEM SPECIFICATION AND DESIGN CONSIDERATIONS

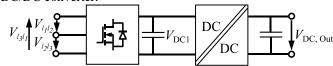

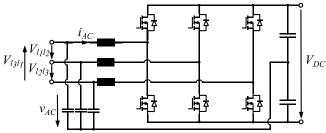

A block diagram of the investigated system is given in Fig. 1. The system consists of two stages: A bidirectional active

front end (AFE) and a bidirectional, galvanically isolated DC/DC converter.

Fig. 1: Block diagram of a two stage AC/DC power supply with a three-phase input  $(L_1, L_2, L_3)$  and DC output  $(V_{DC,Out})$ .

# A. Topology Considerations

Both, the AFE as well as the DC/DC converter must provide bidirectional power flow. Due to the recent developments in wide bandgap (WBG) technologies, efficient converters can be built with Silicon Carbide (SiC) MOSFETs in a standard two-level topology [22].

For the AFE, a three leg, two-level inverter with an integrated All-Pole-LC filter is used. Due to the use of high switching frequencies (~100 kHz), it is possible to reduce the volume of the LC-filter components compared to conventional AFEs (2 ... 16 kHz switching frequency) and integrate it in one housing with the AFE [23].

The specified values for the AFE are shown in Table III: The input voltage range corresponds to the input voltage range of the complete power supply. The AFE output voltage is the DC-link voltage  $V_{\rm DC1}$ . To enable a system optimization, the AFE must support a large voltage range for the DC-link voltage and its range must comply with the maximum input voltage  $V_{AC,II}$ , while allowing a control reserve  $R_{\rm C.96}$ :

$$V_{\rm DC1,min} = V_{\rm AC,ll} \cdot \sqrt{2} \cdot (1 + R_{\rm C,\%})$$

(1)

Additionally, a 10% margin for voltage fluctuations [7] [24] should be considered. For the defined input voltage range this results in an operating DC-link voltage range of 300 V...750 V.

The losses of the AFE mainly depend on the DC-link voltage (switching and AC-filter losses) and input current (switching and conduction losses) [25]. The highest losses at a given power thus appear for a low input voltage (following high input currents) and a high DC-link voltage.

TABLE III

SPECIFICATION OF BIDIRECTIONAL ACTIVE RECTIFIER

| Specified Value                   | Value         |

|-----------------------------------|---------------|

| Input voltage range $(V_{AC,ll})$ | 200 V480 V    |

| DC-link voltage range $(V_{DC1})$ | 300 V750 V    |

| Power                             | 6 kW          |

| Power flow                        | Bidirectional |

The specification of the DC/DC stage is shown in Table IV. It complies with the DC-link voltage range of the AFE as an input voltage and the power supply output voltage range as output voltage. Further, the DC/DC converter must provide the galvanic isolation.

TABLE IV

SPECIFICATION OF THE DC/DC CONVERTER

| Specified Value                 | Value               |

|---------------------------------|---------------------|

| Input voltage range $(V_{DC1})$ | 300 V 750 V         |

| Output voltage ( $V_{DC,Out}$ ) | 600 V (550 V 700 V) |

| Power                           | 6 kW                |

| Power flow | Bidirectional        |

|------------|----------------------|

| Isolation  | Reinforced acc. [21] |

Many different DC/DC converter topologies can be found in literature [26] [27] [28]. However, for resonant topologies in higher power applications (>2 kW), expensive capacitors are needed in addition to the transformer. Also, resonant topologies tend to have a limited bidirectional capability in terms of transfer ratio: In one direction, most resonant topologies have a maximum transfer-ratio equal to the transformer turns ratio. Thus, operated at a high AC input voltage  $V_{\rm AC,ll}$  and thus a high DC input voltage  $V_{\rm DC1,min}$ . To provide full bidirectionality, be able to vary the DC-link voltage and to lower component cost, a dual active bridge (DAB) is chosen for the DC/DC converter.

# B. System Description

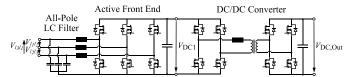

A resulting overview schematic is given in Fig. 2. All power semiconductors are assumed to be SiC MOSFETs, which allow a high switching frequency as well as a high efficiency for the given voltage levels [22]. All half bridges are 2-level configurations to keep the component count and cost low.

To comply with electromagnetic compatibility (EMC) standards, a grid filter in front of the AFE is needed [29]. The examined filter topology is an all-pole LC-filter, that damps common as well as differential mode currents.

The input and output stage of the DAB converter are comprised of full bridges to utilize the full voltage range at the input and output stage and thus reduce the currents. Also, this configuration enables the use of the third level and thus advanced modulation strategies [30] [31] [32].

Fig. 2: Schematic diagram of a two stage AC/DC power supply with a three-phase input  $(L_1, L_2, L_3)$  and DC output  $(V_{DC,Out})$ .

# IV. MODEL DESCRIPTION

The presented loss model can be divided into component loss models and topology dependent current/voltage models. The components models include a half bridge semiconductor loss model as well as the magnetic loss models both for the LC-filter chokes and for the medium frequency transformer. The topology dependent current models are described for the AFE and the DC/DC converter separately and may be extended to further topologies.

## A. Component Loss Models

## 1. Semiconductor Loss Modeling

The semiconductor losses mainly depend on the RMS current, the current during the switching instance, the DC-link voltage as well as the component parameters and the drive circuit. They are mainly distinguished into switching and

conduction losses while neglecting some additional smaller losses like leakage or driving losses.

# a) Switching Losses

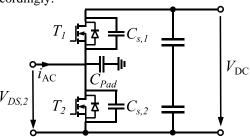

While the component parameters are given by the semiconductor manufacturer, the switching currents are calculated. Most simple models assume hard switching for all transitions. Especially with WBG semiconductors higher ripple currents are possible and thus more soft transitions may occur and have a large influence on the switching losses. In Fig. 3, the schematic diagram of the half bridge switching cell with parasitic capacitances is shown. With double pulse tests, distinguishing between capacitor currents (currents into  $C_s$ ) and channel currents (currents through T) is not possible (comp. [33]). While many models neglect this difference, the presented approach separates those currents and calculates the losses accordingly.

Fig. 3: Circuit diagram of a half bridge switching cell with parasitic capacitances.

The total switching capacitance  $C_{\rm ac}$  is given by the sum of the output capacitances of the MOSFETs  $C_{\rm s,i}$  (charge related capacitance) and the parasitic capacitance of the switching node  $C_{\rm Pad}$ , while the parasitic capacitance of the inductor is neglected:

$$C_{ac} = C_{s,1} + C_{s,2} + C_{Pad}$$

(2)

One switching instance always describes the transition from one semiconductor in the on state to the other being turned on. As the switching processes are nearly the same for the transitions from  $T_1$  conducting to  $T_2$  conducting and vice versa, here only the transition from  $T_2$  to  $T_1$  is described in detail.

For each switching instance, three cases are distinguished:

- I. Hard transition:  $C_{ac}$  must be charged by the turned-on semiconductor.

- II. Mixed transition:  $C_{ac}$  is only partially charged during the dead time:  $i_{AC} < \frac{C_{ac} \cdot V_{DC}}{t_{dead}}$

- III. Soft transition:  $C_{ac}$  is charged by the inductor current within the dead-time.

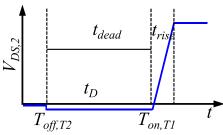

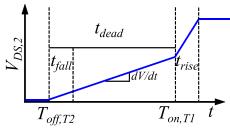

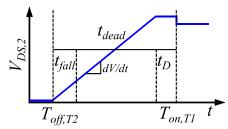

The voltage waveforms for all three transitions are shown in Fig. 4 through Fig. 6. Here  $t_{\rm rise}$  and  $t_{\rm fall}$  refer to the rise and fall time of the MOSFET respectively. The dead time is represented by  $t_{\rm dead}$ ,  $t_{\rm D}$  describes the diode conducting time.

Fig. 4:  $V_{DS,2}(t)$  at hard transition  $(i_{AC} < 0)$ .

Fig. 5:  $V_{DS,2}(t)$  at mixed transition  $0 < i_{AC} < \frac{c_{ac} \cdot V_{DC}}{t_{dead}}$

Fig. 6:  $V_{DS,2}(t)$  at soft transition  $(i_{AC} > 0)$ .

Fig. 7 shows the algorithm flowchart to decide which transition will occur for the transition from  $T_2$  to  $T_1$ .

Losses can only occur, when the voltage and the current at the transistor are unequal to zero. However, it is important to distinguish between charging currents of the parasitic output capacitance and channel currents inside the MOSFET.

Fig. 7: Switching loss calculation flowchart for transition from  $T_2$  to  $T_1$ .

The losses are separated into turn-off losses  $E_{\rm off}$ , turn-on losses  $E_{\rm on}$ , diode losses  $E_{\rm D}$ , charging losses  $E_{\rm chg}$ , and reverse recovery losses  $E_{\rm rr}$ . Turn-on, turn-off, and diode loss energies are calculated with the integral over the apparent power loss during the transition with the transistors drain source voltage  $v_{\rm DS}$  and the input current  $i_{{\rm AC},i}$ . The half bridge input current at a switching instance  $i_{{\rm AC},i}$  is assumed to be constant during the switching instance:

$$E_{\text{loss}} = \int v_{\text{DS}} \cdot i_{AC,i} \, dt = i_{AC,i} \int v_{\text{DS}} \, dt \tag{3}$$

As the voltage waveform is approximated by a linear transition, the losses can be calculated with the turn-off and turn-on time  $t_{\rm fall}$  and  $t_{\rm rise}$ , the total switching capacitance  $C_{\rm ac}$ , the DC link voltage  $V_{\rm DC}$ , the dead time  $t_{\rm dead}$ , and the reverse-recovery charge  $Q_{\rm rr}$ :

$$E_{\text{off}} = \frac{\left(i_{\text{AC},i} \cdot t_{\text{fall}}\right)^2}{2 \cdot C_{\text{ac}}} \tag{4}$$

$$E_{\rm on} = \frac{V_{\rm DC} \cdot i_{\rm AC,i} \cdot t_{\rm rise}}{2} \tag{5}$$

$$E_{\rm D} = t_{\rm dead} \cdot V_{\rm D} \cdot i_{{\rm AC},i} \tag{6}$$

$$E_{\rm rr} = \frac{1}{3} \cdot Q_{\rm rr} \cdot V_{\rm DC} [34] \tag{7}$$

$$E_{\rm chg} = \frac{(V_{\rm DC})^2 \cdot C_{\rm ac}}{2} \tag{8}$$

By calculating turn on / turn off losses ( $E_{\rm off}$ ,  $E_{\rm on}$ ) apart from the charging related losses  $E_{\rm chg}$ , the model differentiates charging and channel currents for the different transitions. A deep discussion on the differentiation between channel and charging currents is given in [35]. The addition in dependence of the occurring transition leads to the switching energies:

$$E_{\text{sw},i} = \begin{cases} E_{\text{chg}} + E_{\text{on}} + E_{\text{rr}} + E_{\text{D}} & (I) \\ E_{\text{off}} + \frac{1}{2} \left( V_{\text{DC}} - \frac{t_{\text{dead}} \cdot i_{\text{AC},i}}{C_{\text{ac}}} \right)^{2} \cdot C_{\text{ac}} & (II) \\ E_{\text{D}} + E_{\text{off}} & (III) \end{cases}$$

(9)

The average switching energy  $\overline{E_{\rm sw}}$  can be calculated with the N transition points over one (fundamental or switching) period (e.g. N=2 for one switching period):

$$\overline{E_{\rm sw}} = \frac{1}{N} \cdot \sum_{i=1}^{N} E_{{\rm sw},i} \tag{10}$$

With the switching frequency  $f_s$ , the switching power losses  $P_{sw}$  can be modeled:

$$P_{\rm sw} = \overline{E_{\rm sw}} \cdot f_{\rm s} \tag{11}$$

## b) Conduction Losses

The conduction losses are calculated with the currents Fourier components  $a_{k,\text{avg}}$  of the current and the on-state resistance of the MOSFET  $R_{\text{DS,on}}$  for the M most relevant frequencies:

$$P_{\text{cond}} = \sum_{k=0}^{M} R_{\text{DS,on}} \cdot a_{k,\text{avg}}^{2}$$

(12)

# 2. Magnetics Loss Modeling

Magnetic losses depend on many different parameters: Core material, winding configuration, used litz-wire, temperature and current [16]. However, calculation of such complex models for each optimization step is not useful and would not be an efficient solution. Since many of those parameters will not change during runtime, it is possible to simplify the model beforehand and use the simplified model for loss calculation.

## a) Winding Losses

Winding losses are current dependent losses, which depend on the amplitude and the frequency of the current. It is possible to model those losses with a frequency dependent resistance R(f) [16]. This resistance includes all winding losses including ohmic losses as well as skin and proximity effect. R(f) can be found using FEMM simulations. The winding losses can then be calculated for K windings with the M most relevant frequencies and the currents Fourier components  $a_{\text{avg.}i.j}$ :

$$P_{\text{loss,winding}} = \sum_{i=0}^{K} \sum_{j=0}^{M} R_j(f_i) \cdot \alpha_{\text{avg},i,j}^2$$

(13)

With this approach, the tradeoff between accuracy and complexity can be easily adjusted by the number of evaluated frequencies M. The calculation during runtime is a convolution and thus very efficient.

## b) Core Losses

The core losses are calculated with the improved generalized Steinmetz equation (IGSE) [17]. The material parameters  $\alpha$ ,  $\beta$  and  $k_s$  are given or calculated in advance. As for high switching frequencies core materials such as powder or ferrite are used, core losses induced by low frequency components (e.g. 50 Hz, 60 Hz) can be neglected and only the ripple related core losses need to be calculated.

The integral of the IGSE (14) can be simplified to (15), where  $m_k$  is the core mass, B flux density and  $\Delta B_{pp}$  the peak-to-peak flux density difference:

$$P_{\text{loss,core},i} = k_{\text{s}} \cdot m_{\text{k}} \cdot \frac{1}{2T} \int_{t}^{t+T} \left| \frac{dB}{dt} \right|^{\alpha} \left( \Delta B^{\beta - \alpha} \right) dt [6]$$

(14)

$$P_{\text{loss,core},i} = 2 \cdot k_{\text{s}} \cdot m_{\text{k}} \cdot \left| \Delta B_{\text{pp}} \right|^{\beta - \alpha} \cdot \left( \left( 2 \cdot \frac{\Delta B_{\text{pp}} \cdot f_{\text{s}}}{1 - \Phi_{\%}} \right)^{\alpha} \right)$$

(15)

# B. Topology Specific Parameter Model

The topology specific parameter models must provide currents and voltages to calculate the device losses with the according equations.

## 1. DC/DC Converter Parameter Model

The power transfer of the dual active bridge depends on the phase shift between primary and secondary switching bridge. For single phase shift modulation, the phase shift  $\phi$  can be expressed in dependence of the transferred power P, the input and output voltage  $V_1$  and  $V_2$  and the transformer stray inductance  $L_{\sigma}$  and turns ratio n:

$$\Phi_{\%} = \frac{\operatorname{sgn}(P)}{2} \cdot \left( \frac{1}{2} - \sqrt{\frac{1}{4} - \frac{2 \cdot \operatorname{abs}(P) \cdot f_{s} \cdot L_{\sigma}}{n \cdot V_{1} \cdot V_{2}}} \right) \tag{16}$$

# a) Current Modeling

The current modeling must provide currents for both the semiconductor loss model as well as the magnetics loss model. The semiconductor loss model needs currents at commutation instances to calculate switching losses. RMS currents are needed to calculate the semiconductor conduction losses. The magnetics loss model needs the Fourier coefficients of the current to calculate winding losses and the voltage waveform to calculate core losses.

## (1) Currents at Commutation

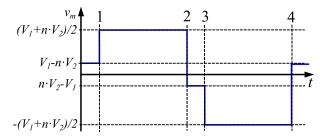

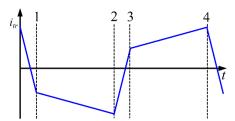

The commutation points for the primary and secondary switching bridge are shown in Fig. 9 and Fig. 8 in respect to the transformer current (Fig. 9) and voltage at the magnetizing inductance (Fig. 8).

Fig. 8: Typical voltage waveform of the voltage  $v_{\rm m}$  at the magnetizing inductance  $L_{\rm m}$  of a DAB transformer with indicated switching instances 1...4.

Fig. 9: Typical transformer current waveform  $i_{\rm tr}$  of a DAB converter with indicated switching instances 1...4.

In forward operation points 1 and 3 are the commutation of the secondary bridge; points 2 and 4 of the primary bridge. All calculations are done for the primary side and transformed for the secondary by means of the transformer turns ratio. Equations (17) and (18) give the currents for the primary half bridge at switching instances 1 through 4.  $T_s = 1/f_s$  is the switching period, and  $\Delta T = \Phi_{\%} \cdot T_s$  is the time shift between primary and secondary full bridge, where  $\Phi_{\%}$  is the percental phase shift.

$$i_{1,3} = \pm \frac{\Delta T}{2} \cdot \frac{V_1 + n \cdot V_2}{L_c} - \frac{T - |\Delta T|}{4}$$

(17)

$$i_{2,4} = \mp \frac{\Delta T}{2} \cdot \frac{V_1 + n \cdot V_2}{L_s} + \frac{T - |\Delta T|}{4}$$

(18)

# (a) Fourier analysis of DAB current

To simplify the analytic Fourier analysis of the DAB current, the first half of the current waveform is mirrored leaving only positive frequency components in the Fourier spectrum. The Fourier coefficients  $a_k$  can be expressed by means of the commutation times  $t_{1...4}$ , the currents at commutation  $i_{1...4}$  and the switching period  $T_s = 1/f_s$ :

$$a_{k} \cdot \frac{T_{s}}{4} = \int_{0}^{t_{1}} \frac{i_{1}}{t_{1}} \cdot t \cdot \sin(2\pi \cdot kf_{s}t) dt + \int_{t_{1}}^{t_{2}} \left(\frac{i_{2} - i_{1}}{t_{2} - t_{1}} \cdot (t - t_{1}) + i_{1}\right) \cdot \sin(2\pi \cdot kf_{s}t) dt +$$

(19)

$$\int_{t_2}^{T_s/2} \left( -\frac{i_1}{t_1} \cdot (t - t_2) + i_2 \right) \cdot \sin(2\pi \cdot k f_s t) dt$$

## b) Medium Frequency Transformer Flux Density Modeling

The flux density can be calculated with the voltage  $v_{\rm m}$  at the magnetizing inductance  $L_{\rm m}$  as well as the core cross section  $A_{\rm k}$  and the primary number of turns  $N_1$ . The voltage waveform  $v_{\rm m}$  is shown in Fig. 8. If  $V_1 - n \cdot V_2 \ll \frac{1}{2} \cdot (V_1 + n \cdot V_2)$ , the peak-to-peak flux density  $\Delta B_{pp}$  can be approximated with the percental phase shift  $\Phi_{\%}$ , the input and output voltage  $V_1$  and  $V_2$ , the transformer turns ratio n, core cross section  $A_{\rm k}$  and primary turns number  $N_1$  and the switching frequency  $f_s$ :

$$\Delta B_{\rm pp} = (1 - \Phi_{\%}) \cdot \frac{(V_1 + n \cdot V_2)/2}{2 \cdot A_{\rm k} \cdot f_{\rm s} \cdot N_1}$$

(20)

# 2. Active Rectifier Parameter Model

## a) Current and Duty Ratio Modeling

Fig. 10: Circuit diagram of the investigated inverter system

The phase currents including the ripple current must be modeled. For this purpose, the RMS input current as well as the input voltage and the DC-link voltage are needed. The model is given for a neutral point connected LC-filter as shown in Fig. 10. All three phases are independent and thus all calculations are only shown for one half bridge.

#### (1) Duty Ratio

The duty ratio d is important for modeling the current. Modern inverter systems are often operated in overmodulation. Thus, it is important to consider not only sinusoidal modulation but also different overmodulation strategies [36].

# (a) Sinusoidal Modulation

The duty ratio d for sinusoidal modulation can be calculated with the phase voltage  $v_{\rm AC}$  and the DC-link voltage  $V_{\rm DC}$ :

$$d(t) = \frac{v_{AC}(t)}{V_{DC}} + \frac{1}{2}$$

(21)

#### (b) Overmodulation

To realise a modulation index M>1, overmodulation is used [36], which must be considered in the loss model. As many different overmodulation strategies exist in literature (cf. [36]) and even more proprietary strategies are implemented, the loss model is adapted to allow arbitrary modulation forms. It is set

by replacing the calculation of the duty ratio by an arbitrary function:

$$d(t) = f(v_{AC}(t)) \tag{22}$$

## b) Fundamental Current and Voltage

The fundamental current component is controlled and for the exemplary case will be assumed to be sinusoidal and in phase with the grid voltage  $v_{AC}$ . Then,  $v_{AC}(t)$  can be expressed with the RMS input voltage  $V_{AC,rms}$  and the input (grid) frequency  $f_G$ :

$$v_{\rm AC}(t) = \sqrt{2} \cdot V_{\rm AC,rms} \cdot \sin(2\pi \cdot f_{\rm G} \cdot t) \tag{23}$$

Using the model for high switching frequencies, the phase difference between grid and modulated voltage can be neglected. The current can be expressed with the RMS input current  $I_{\rm rms}$  and the input (grid) frequency  $f_{\rm G}$ :

$$i_{\rm AC}(t) = \sqrt{2} \cdot I_{\rm rms} \cdot \sin(2\pi \cdot f_{\rm G} \cdot t).$$

(24)

## c) Ripple Current

The filter resonance frequency  $f_r$  must be designed much lower than the switching frequency  $f_s$  of the converter [29]. Thus, the capacitor voltage  $V_C$  can be assumed as constant over one switching period. The peak-to-peak ripple current  $\Delta I_{\mathrm{pp},i}$  for a given input voltage  $V_{\mathrm{AC},i} = v_{\mathrm{AC}}(t_i)$  and given DC-link voltage  $V_{\mathrm{DC}}$  can be calculated with the inductance of the LC-filter inductor L:

$$\Delta I_{\text{pp},i} = \frac{(V_{\text{DC}}/2 - V_{\text{AC},i}) \cdot (V_{\text{AC},i} + V_{\text{DC}}/2)}{f_{\text{s}} \cdot L \cdot V_{\text{DC}}}$$

(25)

With the assumption of an asymmetric triangular current waveform the Fourier coefficients  $a_{k,i}$  of the ripple current can be calculated efficiently with the duty ratio  $d_i = d(t_i)$  [25]:

$$\frac{a_{k,i}}{\Delta I_{\text{pp},i}} = \frac{2(\sin(\pi d_i k) - \sin(\pi k) + \pi(1 - d_i) \cdot \cos(\pi d_i k_i))}{\pi^2 \cdot (1 - d_i) \cdot k^2} + \frac{2\sin(\pi d_i k) - 2\pi d_i k \cdot \cos(\pi d_i k)}{\pi^2 \cdot d_i \cdot k^2}$$

(26)

The average harmonic contents of the ripple current over one period is estimated by taking N evenly distributed samples at the times  $t_i$ :

$$a_{k,\text{avg}} = \sum_{i=0}^{N} a_{k,i} \tag{27}$$

# 3. Combined Current

The combined current at the switching instance i results from the addition of both the ripple current component  $\Delta I_{\mathrm{pp},i}$  and the fundamental current component  $I_{\mathrm{AC},i}=i_{\mathrm{AC}}(t_i)$ . For the switching losses, especially the currents at the switching instance are relevant. During the switching process, the current is assumed to stay constant. The currents for the transitions from low to high  $I_{\mathrm{T2}\to\mathrm{T1}}$  and from high to low  $I_{\mathrm{T1}\to\mathrm{T2}}$  can then be calculated:

$$I_{\text{T2}\to\text{T1}} = I_{\text{AC},i} - \frac{\Delta I_{\text{pp},i}}{2}$$

(28)

$$I_{\text{T1}\to\text{T2}} = I_{\text{AC},i} + \frac{\Delta I_{\text{pp},i}}{2}$$

(29)

For the inductor losses the Fourier coefficients are needed. As the fundamental current and the ripple current are at different frequencies, the Fourier coefficients can be seen as independent and the current results from the combination of all Fourier coefficients. The influence of the phase of the ripple current relative to the fundamental current can be neglected if different bias magnetization does not affect the losses.

## C. Loss Calculation

The presented equations for the device loss calculation (semiconductors/magnetics) can now be combined with the topology specific parameter model to calculate the losses of each component. The results are presented in Ch. VII.

## V. MEASUREMENT RESULTS AND MODEL VERIFICATION

To verify the model, the power supply described in Ch. III was built up. For high efficiency and high power-density the power supply was built up using SiC-MOSFETs and an initial switching frequency of 100 kHz was chosen. However, the later presented modeling results reveal different optima regarding the switching frequencies for both AFE and DAB.

The transformer turns ratio is set to 1:1 for first evaluation. However, depending on preferred grids and operation conditions other optima may be found [37].

# A. Hardware Description

The hardware topologies are chosen as described in Ch. III. Table V shows the devices and materials used for the AFE and DC/DC converter.

| Semiconductors      | Infineon IMZ120R090M1H       |             |

|---------------------|------------------------------|-------------|

| DC Capacitors       | Vishay MKP1848C, 900 V 50 μF |             |

| AFE Inductor        | Core Material                | Sendust 60µ |

|                     | Core Size                    | 62x33x25    |

|                     | Turns                        | 35          |

| MF-Transformer      | Core Material                | Epcos N87   |

|                     | Prim. Turns                  | 12          |

|                     | Sec. Turns                   | 12          |

|                     | Litz Wire                    | 1400x0.05mm |

| Driving Voltage     | On: 15 V                     | Off: 0 V    |

| Switching Frequency | 100 kHz                      |             |

| Dead Time           | 160 ns                       |             |

|                     |                              |             |

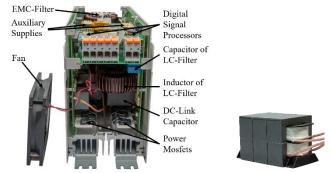

The built-up power supply is shown in Fig. 11. The all-pole LC-filter, an additional EMI filter, auxiliary supply and the MF-transformer are integrated in the housing. It provides an overall power density of 0.6 kW/l.

Fig. 11: Built up power supply without housing and removed fan (left) and MF-transformer (right), which is located inside the housing behind the inductors

## B. Measurement Results and Model Verification

For the model verification the losses of the AFE and the DC/DC converter are measured individually and compared to the modeling results.

All measurements were taken with the measurement equipment denoted in Table VI.

# TABLE VI MEASUREMENT EQUIPMENT

| Equipment      | Туре                              |

|----------------|-----------------------------------|

| Oscilloscope   | Tek MSO Series 4, 500 MHz, 12 bit |

| Current Probe  | TCP0030A                          |

| Voltage Probe  | THDP0200                          |

| Power Analyzer | Yokogawa WT1800                   |

# 1. AFE Model Verification

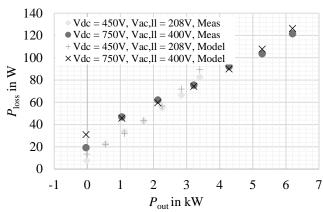

The model is verified by comparison to the measurement results. In Fig. 12 a comparison between the simulated and measured losses is shown for two different operating points: Grey indicates the measurements and simulations at a DC-link voltage of 450 V and an RMS AC voltage of 208 V. Black indicates the measurements and simulations at a DC-link voltage of 750 V and an RMS AC voltage of 400 V. For both operating points the x-marker represents the model results while the bullet-marker represents the measurement results. In all points except open load the model can predict the losses very accurately. At open-load operation the deviation is 60% or 10 W. This reveals a poor estimation of constant losses by the model. However, for the optimization constant losses may be negligible. For  $V_{AC,ll} = 400 \text{ V}$  the relative deviation is smallest for medium power, for  $V_{\rm AC,ll} = 208 \, \rm V$  the deviation increases with power. This indicates that current related losses  $(E_{\rm off}, E_{\rm on}, E_{\rm D})$  are slightly over-estimated while voltage related losses ( $E_{chg}$ ,  $E_{rr}$ ) are underestimated. When excluding the open load operation, the model's average deviation is at 3.5% (including the open load operation expands the average deviation to 12%).

Fig. 12: Measured and modeled AFE losses at different powers  $P_{\rm Out}$  and different DC-link voltages  $V_{\rm DC1}$  at an input voltage of  $V_{\rm AC,ll}=400~{\rm V}$  and  $V_{\rm AC,ll}=208~{\rm V}$ .

## 2. DC/DC Converter Model Verification

To validate the loss model of the DC/DC converter, measurements at different operating points are presented and compared to the model result.

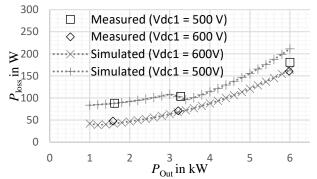

Fig. 13: Measured and modeled DAB losses at different powers  $P_{\rm Out}$  and different DC-link voltages  $V_{\rm DC1}$  at an output voltage of  $V_{\rm DC,Out} = 600$  V.

Fig. 13 shows the results of modeling and measuring at different powers and input voltages. The average deviation over all measurements taken is 11.2% and provides a good basis for loss optimization of the overall power supply. Largest deviations can be found at the boundary between hardand soft-switching operation. When applying the model for optimization, the optimum found should be verified for sensitivity to device tolerances.

## VI. SYSTEM MEASUREMENT RESULTS

# A. Loss Distribution

First, the losses of the AFE and the DC/DC converter are analyzed independently. Thermal monitoring of the AFE semiconductors temperature by thermocouple measurements during the loss measurements presented in Fig. 14 showed that with initial operating parameters the output power limit at  $V_{\rm AC,ll} = 208 \, \rm V$  is  $P_{\rm Out} = 3.2 \, \rm kW$ . Thus, measurements with nominal power are only shown for  $V_{\rm AC,ll} = 400 \, \rm V$ .

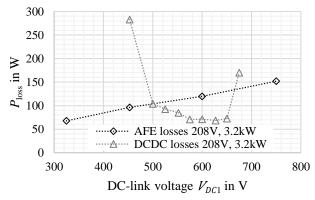

Fig. 14: Measured and interpolated losses at  $P_{\text{Out}} = 3.2 \text{ kW}$ ,  $V_{\text{AC,ll}} = 208 \text{ V}$  and  $V_{\text{DC,out}} = 600 \text{ V}$  of the AFE and the DC/DC converter.

Fig. 14 shows the loss distribution among DC/DC converter and AFE at  $P_{\rm Out} = 3.2 \, {\rm kW}$  and  $V_{\rm AC,ll} = 208 \, {\rm V}$  for different DC-link voltages  $V_{DC1}$ . Clearly, the loss distribution is influenced by the DC-link voltage: The AFE-losses increase nearly linearly with a higher DC-link voltage. The DC/DC converter losses increase strongly at transfer ratios far away from 1 (above 1.2 and below 0.9). Modeling results reveal that the converter leaves the soft switching region here. Between a DC-link voltage of  $V_{DC1} = 500 \text{ V}$  and  $V_{DC1} = 650 \text{ V}$ , the DC/DC converter losses slightly decrease with a rising DClink voltage. In this region, the losses can be distributed among DC/DC converter and AFE by means of the DC-link voltage  $V_{DC1}$ . Minimum losses for the AFE can be found at  $V_{\rm DC1} = 500 \, \text{V}$ ; minimum losses for the DC/DC converter at  $V_{\rm DC1} = 625$  V. Further, for 500 V  $\leq V_{\rm DC1} \leq 650$  V, the AFE losses dominate due to the low input voltage  $V_{AC.11}$ .

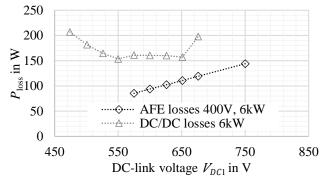

Fig. 15: AFE and DC/DC converter losses at  $P_{\rm Out} = 6$  kW,  $V_{\rm AC,ll} = 400$  V and  $V_{\rm DC,Out} = 600$  V in dependence on the DC-link voltage  $V_{\rm DC1}$ .

Fig. 15 shows the losses of the DC/DC converter and AFE at  $P_{\rm Out} = 6$  kW and  $V_{\rm AC,ll} = 400$  V in dependence of the DC-link voltage. The soft switching region is increased compared to the measurements at  $P_{\rm Out} = 3.2$  kW. Minimum losses are at  $V_{\rm DC1} = 550$  V for the DC/DC converter and at  $V_{\rm DC1} = 575$  V for the AFE, respectively. It may be noted, that the AFE and thus the system may operate at  $V_{\rm DC1,min} \ge 575$  V for input voltages  $V_{\rm AC,ll} \ge 400$  V (cmp. (1)).

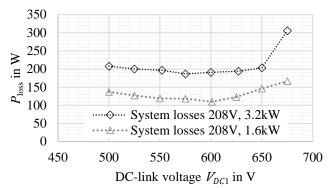

Fig. 16 and Fig. 17 show the overall losses for different power and input voltage levels. Fig. 16 includes the system losses at  $V_{AC,ll} = 208 V$ , Fig. 17 at  $V_{AC,ll} = 400 V$ .

Fig. 16: System losses at  $V_{\rm AC,II} = 208$  V,  $V_{\rm DC,Out} = 600$  V in dependence of the DC-link voltage  $V_{\rm DC1}$  for different output powers.

At  $V_{\rm AC,ll} = 208$  V the lowest overall losses for 1.6 kW and 3.2 kW are at  $V_{\rm DC1} = 575$  V and  $V_{\rm DC1} = 600$  V respectively. However, losses of the AFE can be reduced by approximately 15% if operated at  $V_{\rm DC1} = 500$  V instead. This may be favorable as the AFE losses dominate for low input voltages.

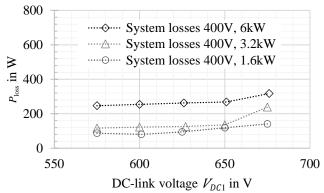

Fig. 17 presents the system losses at  $V_{\text{AC,II}} = 400 \text{ V}$  at different output powers. At  $P_{\text{Out}} = 6 \text{ kW}$  and  $P_{\text{Out}} = 3.2 \text{ kW}$ , the system losses are minimum at  $V_{\text{DC1}} = V_{\text{DC1,min}} = 575 \text{ V}$ . At  $P_{\text{Out}} = 1.6 \text{ kW}$ , losses become minimal at  $V_{\text{DC1}} = 600 \text{ V}$ .

At all presented operating points, the DC/DC converter losses would yet be lower for higher DC-link voltages (cmp. Fig. 14 and Fig. 15). It may be concluded that for the presented operating points a transformer turns ratio smaller than 1:1 would be favorable in terms of system efficiency.

Fig. 17: System losses at  $V_{AC,II} = 400 \text{ V}$ ,  $V_{DC,Out} = 600 \text{ V}$  in dependence of the DC-link voltage  $V_{DCI}$  for different output powers.

#### B. System Efficiency

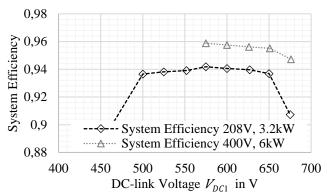

To complete the picture of the evaluated power supply, the overall system efficiency in dependence of the DC-link voltage  $V_{DC1}$  is analyzed. The measurement results are given in Fig. 18.

Fig. 18: System efficiency for  $P_{\rm Out}=3.2~{\rm kW}$  and  $P_{\rm Out}=6~{\rm kW}$  in dependence of the DC-link voltage at an input voltage of  $V_{\rm AC,II}=208~{\rm V}$  and  $V_{\rm AC,II}=208~{\rm V}$ , respectively, and an output voltage  $V_{\rm DC,out}=600~{\rm V}$ .

Maximum efficiency for both  $V_{\rm AC,ll} = 400 \, V$  as well as  $V_{\rm AC,ll} = 208 \, \rm V$  is achieved for a DC-link voltage of  $V_{\rm DC1} = 575 \, \rm V$ . Towards high/low transfer ratios between DC-link and output voltage, the efficiency drops clearly as it leaves the soft switching region of the DAB.

As the AFE-efficiency is much higher at larger input voltages  $V_{\rm AC,ll}$ , the overall efficiency is higher at an input voltage of  $V_{\rm AC,ll} = 400$  V.

#### VII. MODEL RESULTS AND OPTIMIZATION

With the developed model, the systems losses can be modeled for arbitrary operating points and the loss distribution can be described. First, individual model and optimization results of the two stages are presented, secondly the optimization results for the complete power supply given.

# A. Model Results of the AFE

1. Loss Distribution Among Components and Loss Mechanism

Fig. 19: AFE losses in dependence of  $f_{\text{S,AFE}}$  at a power of 5 kW, an input voltage of  $V_{\text{AC,II}} = 400 \text{ V}$  and a DC-link voltage of  $V_{\text{DC1}} = 600 \text{ V}$ .

Fig. 19 shows the AFE losses in dependence of the AFE switching frequency  $f_{S,AFE}$ . The optimum in terms of the overall losses is at  $f_{S,AFE} = 52$  kHz. However, losses may be distributed between semiconductors and inductors: Minimum semiconductor losses are at  $f_{S,AFE} = 34$  kHz.

## 2. Parametric Simulation of AFE Losses

To analyze the losses in the operation space, parametric simulations are conducted. Fig. 20 shows the results of the parametric simulation of the AFE losses for an input voltage of  $V_{\rm AC,ll} = 208 \, \rm V$  at a variable DC-link voltage  $V_{\rm DC1}$  and transfer power  $P_{\rm Out}$ . It is clearly visible, that the losses increase both with higher powers and with higher DC-link voltages. Further, around open load, the quasi-resonant region with lower losses can be seen.

Fig. 20: AFE model results for a parameter variation of  $V_{\rm DC,1}$  at  $V_{\rm AC,II}$  = 208 V.

# 3. Operation Space Optimization of AFE

From the modeling and measurement results it is clear, that both the switching frequency as well as the DC-link voltage have a major influence on the AFE losses.

In terms of the AFE losses, the DC-link voltage should always be at its minimum (cmp. 5.3.2). However, in combination with the DC/DC converter, the DC-link voltage  $V_{\rm DC1}$  may be considered in the context of a system optimization.

Fig. 21: Diagram with the optimum AFE switching frequency  $f_{\text{S,AFE}}$  for minimum AFE losses at different DC-link voltages  $V_{\text{DC1}}$  in dependence of the power  $P_{\text{Out}}$  for an input voltage of  $V_{\text{AC,II}} = 400 \text{ V}$ .

The optimum switching frequency  $f_{\rm S,AFE}$  in dependence of the output power  $P_{\rm Out}$  and the DC-link voltage  $V_{\rm DC1}$  can be found with an optimization algorithm. The allowable operating space for the AFE switching frequency is influenced by the filter's resonance frequency and the maximum frequency which dead-time, controller, and drive circuits can provide. Fig. 21 shows the result of a brute force optimization of the AFE switching frequency  $f_{\rm S,AFE}$  in dependence of the output power  $P_{\rm Out}$  for different DC-link voltages  $V_{\rm DC1}$ .

The optimum switching frequency  $f_{\rm S,AFE}$  is both dependent on the DC-link voltage  $V_{\rm DC1}$  as well as the transferred power: The higher the power, the lower the optimum switching frequency; the higher the DC-link voltage, the higher the optimum switching frequency. The reasons can be analyzed as follows: At lighter loads, the core losses dominate. As the inductance stays the same,  $\Delta B_{\rm pp,\it i}$  and thus the core losses decrease with a higher switching frequency (cmp. (14)).  $\Delta B_{\rm pp,\it i}$  and with it the influence of the core losses increases with higher DC-link voltages. Thus, the optimum switching frequency increases with higher DC-link voltages.

## B. Model Results of the DC/DC Converter

# 1. Loss Distribution Among Components and Loss Mechanism

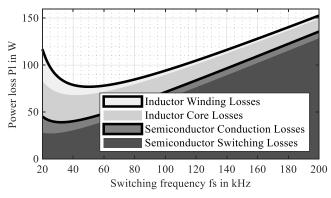

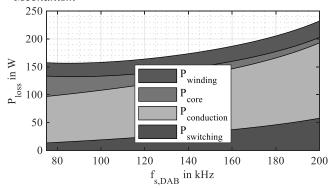

Fig. 22: DAB loss distribution depending on switching frequency  $f_{S,DAB}$  at a power of  $P_{out} = 6$  kW.

To analyze the distribution of the losses among the different components and loss mechanisms, Fig. 22 shows the losses in the DAB in dependence of the switching frequency  $f_{S,DAB}$ . The optimum switching frequency for a power transfer of 6 kW is at  $f_{S,DAB} = 82$  kHz. However, between 75 kHz and 100 kHz, overall losses only slightly change. Thus, the loss distribution among the components may be optimized according to the model results: With higher switching frequencies, the losses can be moved from the magnetics towards the semiconductors.

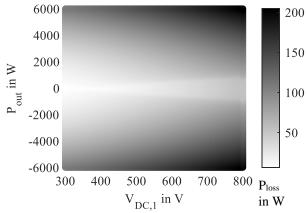

# 2. Parametric Simulation of DAB Losses

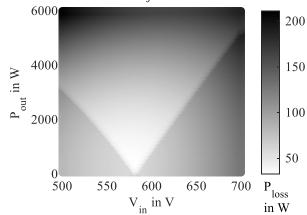

Fig. 23: DAB model results for a parameter variation of  $V_{\rm DC1}$  at  $V_{\rm DC,out} = 600 \, \rm V$

To get an overview of the losses in the operation space, a parametric loss simulation is shown in Fig. 23. Clearly visible is the soft switching area, that gets wider towards higher powers. Further, the influence of the magnetizing inductance can be seen: The soft switching region is slightly shifted towards the boost operation. At higher powers, where the ohmic losses clearly dominate inside the soft switching region, slight buck operation leads to the lowest power loss.

## 3. Operation Space Optimization of DAB

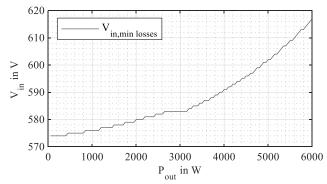

The DAB model shows that the minimal losses for a constant output voltage  $V_{\rm DC,Out}$  depend on the transferred power and the input voltage  $V_{\rm DC1}$ .

Fig. 24: Optimum DAB input voltage  $V_{\rm DC1}$  in dependence of the transferred power at an output voltage of  $V_{\rm DC,out} = 600 \, \rm V$  and a fixed switching frequency of  $f_{\rm S,DAB} = 100 \, \rm kHz$ .

Fig. 24 shows the optimum input voltage  $V_{\rm DC1}$  in dependence of the transferred power. It can be seen, that with higher powers the optimum input voltage rises. In turn, to optimize the overall system losses, the DC-link voltage  $V_{\rm DC1}$  must be considered.

For the optimization of the switching frequency  $f_{S,DAB}$ , first the allowable operating space must be defined. To prevent saturation in the DAB transformer, the maximum volt-seconds must be considered.

In the presented design, the transformer is rated for an input and output voltage of 800 V at a switching frequency of 100 kHz. The maximum volt-seconds  $A_{\rm VT}$  can be calculated with the maximum input and output voltage  $V_{\rm DC,1}$  and  $V_{\rm DC,Out}$ , the DAB switching frequency  $f_{\rm S,DAB}$  and the transformer turns ratio n:

$$A_{\text{VT,max}} = \frac{V_{\text{DC,1,max}} + V_{\text{DC,Out,max}}/n}{4 \cdot f_{\text{S,DAB}}}$$

(30)

The maximum switching frequency is limited by the digital controller and firmware architecture and the maximum allowable frequency in terms of power transfer. Thus, the limits for the DAB switching frequency can be defined with (30), the stray inductance  $L_{\sigma}$ , the output power  $P_{\text{out}}$  and the transformer turns ratio n:

$$\frac{V_{\text{DC1}} \cdot V_{\text{DC,Out}}/n}{8 \cdot L_{\sigma} \cdot P_{\text{out}}} \ge f_{\text{S,DAB}} \ge \frac{V_{\text{DC1}} + V_{\text{DC,Out}}}{4 \cdot A_{\text{VT,max}}}$$

(31)

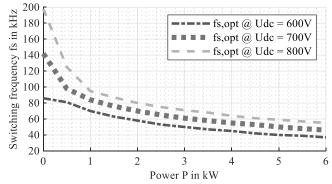

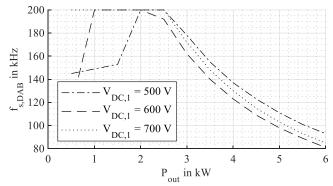

For this optimization, the switching frequencies limit is set to 200 kHz.

Fig. 25: Optimum DAB switching frequency  $f_{S,DAB}$  in dependence of the transferred power for different input voltages  $V_{DC.1}$ .

The optimization results are shown in Fig. 25. At lower powers two local optima can be found: at high switching frequencies as they reduce the transformer core losses and at medium frequencies due to the reduced switching losses. As an upper frequency limit exists there is a jump from the local optimum at medium frequencies to the maximum frequency for input voltages of  $V_{\rm DC,1} = 500 \, \rm V$  and  $V_{\rm DC,1} = 600 \, \rm V$ . At higher transfer powers the power independent core losses as well as the losses induced by the magnetizing current become less dominant. Instead, switching, winding and conduction losses are dominant. As winding and switching losses increase with higher switching frequencies, the optimum switching frequency  $f_{\rm S,DAB}$  decreases with higher transfer powers.

# VIII. SYSTEM OPTIMIZATION

With the described models for the two stages of the power supply, system optima can be found. The optimum parameters can either be found as constant parameters for the complete operation space or as dynamic operating parameters that depend on input and output conditions.

# A. Optimum Constant Operating Parameters

First, the model is used to find the optimum constant operating parameters. The conventional approach is to minimize the maximum cooling effort and thus minimize the losses at maximum power. The DC-link voltage  $V_{\rm DC,1}$  must be chosen for the maximum input voltage which is  $V_{\rm AC,ll} = 480 \, \rm V$ . Accordingly,  $V_{\rm DC,1}$  is chosen to be 700 V. Highest losses occur at the minimum input voltage (comp. Ch. VI). For the constant operating parameters thus the optimum parameters for an input voltage of  $V_{\rm AC,ll} = 208 \, \rm V$ , a DC-link voltage of  $V_{\rm DC,1} = 700 \, \rm V$  and an output power of  $P_{\rm out} = 6 \, \rm kW$  are chosen.

TABLE VII

OPTIMUM CONSTANT OPERATING PARAMETERS

| Operating Parameter | Value   |

|---------------------|---------|

| $V_{ m DC,1}$       | 700 V   |

| $f_{S,DAB}$         | 140 kHz |

| $f_{S,AFE}$         | 40 kHz  |

The resulting optimum constant operating parameters are found with a brute-force optimization and given in Table VII.

# B. Operation Space Optimization

In a second approach, the model is used to find optimum operating parameters for each set of input/output parameters.

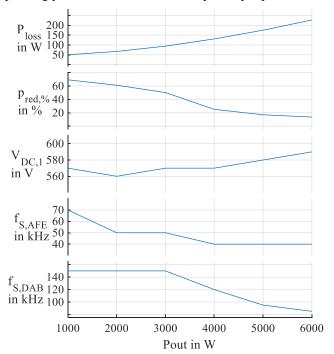

Fig. 26: System power loss  $P_{\rm loss}$  and relative loss reduction  $p_{\rm red,\%}$  of the two stage power supply at  $V_{\rm AC,II} = 400$  V and  $V_{\rm out} = 600$  V for a variable DC-link voltage  $V_{\rm DC,1}$  and variable switching frequencies of the DAB ( $f_{\rm S,DAB}$ ) and AFE ( $f_{\rm S,AFE}$ ).

Fig. 26 shows the optimization results for fixed input and output voltages ( $V_{\text{AC,ll}} = 400 \text{ V}$ ,  $V_{\text{out}} = 600 \text{ V}$ ) and a power transfer 1 kW  $\leq P_{\text{out}} \leq 6 \text{ kW}$ . The optimized parameters are the DC-link voltage ( $400 \text{ V} \cdot \sqrt{2} \leq V_{\text{DC,1}} \leq 480 \text{ V} \cdot \sqrt{2}$ ), the AFE switching frequency ( $40 \text{ kHz} \leq f_{\text{S,AFE}} \leq 100 \text{ kHz}$ ) and the DAB switching frequency ( $85 \text{ kHz} \leq f_{\text{S,DAB}} \leq 150 \text{ kHz}$ ).

The relative loss reduction  $p_{l,red,\%}$  is referred to the losses for constant parameters that are given in Table VII.

By using dynamic operating parameters losses at maximum power can be reduced by 14%. In turns, either cooling effort can be reduced, or output power increased. However, power supplies often run at partial load. At 50% output power ( $P_{\text{out}} = 3 \text{ kW}$ ) the model results promise a loss reduction of 48%. The main reason for the large reduction at lower losses is, that the optimization considers the soft switching region of the DAB and hence optimizes both switching frequency as well as DC-link voltage towards a soft switching operating point.

# IX. CONCLUSION AND OUTLOOK

The presented loss analysis and optimization model enable a detailed evaluation of system losses. Compared to previous work, the semiconductor loss model was optimized to work for high switching frequencies and the mixed transition included to account for higher ripple currents, which can occur when using WBG semiconductors. The magnetics loss model

is based on analytical equations rather than numerical solvers. Overall, the model is optimized for calculation speed by using the spacing between fundamental and switching frequency and assuming constant losses for multiple adjacent switching instances.

Thus, the model allows to quickly analyse not only the total losses but also the loss distribution among power supply stages and down to the component level.

While previous work mainly focused on the optimization during the hardware design [8] [9] [10] [11], the presented optimization is especially useful for optimizing the operating parameters for a certain design at any operating condition. In this context, DC-link voltages as well as switching frequencies are seen as operating rather than design parameters. Consequently, they are optimized depending on the operating point. With the calculation efficient loss model, wide operation spaces can either be analysed during the control development or the model can even be implemented inside a microcontroller and optimization conducted during runtime.

By means of optimizing the operating parameters, the losses can be reduced by approximately 14% at full load and even 48% at half load operation. This loss reduction does not only reduce energy consumption but also leads to lower thermal component stress at partial load and thus higher lifetime expectancy. Also, the loss reduction may be used to expand the operation space that was analyzed in Ch. VI.

Future work should focus on in depth optimization that not only considers system losses but takes into account the loss distribution among the components. It should further extend the loss model for different converter topologies to enable loss reduction and smart derating concepts in yet more applications.

## REFERENCES

- [1] R. W. D. Doncker, Fast Charging (350 kW) for Electric Vehicles Possibilities and Issues, Eindhoven, 2019.

- [2] B. Sattler and S. Wiesner, "Research Project DC-Industrie Energiewende meets Industrie 4.0," ZVEI German Electrical and Eletronic Manufacturers' Association, Frankfurt, 2019.

- [3] C. Meyer, M. Hoing, A. Peterson and R. W. D. Doncker, "Control and Design of DC-Grids for Offshore Wind Farms," *Conference Record of the 2006 IEEE Industry Applications Conference Forty-First IAS Annual Meeting*, pp. 1148-1154, 2006.

- [4] K. Kim, K. Park, G. Roh and K. Chun, "DC-grid system for ships: a study of benefits and technical considerations," *Journal of International Maritime Safety, Environmental Affairs, and Shipping*, vol. 2, no. 1, pp. 1-12, 2018.

- [5] R. Jayabalan, B. Fahimi, A. Koenig and S. Pekarek, "Applications of power electronics-based systems in vehicular technology: state-of-the-art and future trends," *Power Electronics Specialists Conference*, pp. 1887-1894, 2004.

- [6] J. Miller, "Power electronics in hybrid electric vehicle applications," *Applied Power Electronics Conference and Exposition*, pp. 23-29, 2003.

- [7] "IEC 60038:2012-04".

- [8] J. W. Kolar, "Multi-Objective Optimization in Power Electronics," Plenary Presentation at the Southern Power Electronics Conference (SPEC 2016), 2016.

- [9] J. W. Kolar, J. Biela and J. Minibock, "Exploring the pareto front of multi-objective single-phase PFC rectifier design optimization - 99.2% efficiency vs. 7kW/din3 power density," *IEEE 6th International Power Electronics and Motion Control Conference*, pp. 1-21, 2009.

- [10] M. Mogorovic and D. Dujic, "100kW, 10kHz Medium Frequency Transformer Design Optimization and Experimental Verification," *IEEE Transactions on Power Electronics*, vol. 34, no. 2, pp. 1696-1708, 2019.

- [11] H. Uemura, D. Yoshida, H. Fujimoto, Y. Okuma and J. Kolar, "Benefits and Challenges of Design Process that employs a Multi-objective Optimization Approach for Industrial Applications," *IEEE 2nd International Future Energy Electronics Conference (IFEEC)*, pp. 1-6, 2015.

- [12] D. Christen and J. Biela, "Analytical Switching Loss Modeling Based on Datasheet Parameters for MOSFETs in a Half-Bridge," *IEEE Transactions on Power Electronics*, vol. 4, no. 34, pp. 3700-3710, 2019.

- [13] L. Ceccarelli, R. Kotecha, F. Iannuzzo und A. Mantooth, "Fast Electro-thermal Simulation Strategy for SiC MOSFETs Based on Power Loss Mapping," *IEEE International Power Electronics and Application Conference and Exposition (PEAC)*, pp. 1-6, 2018.

- [14] Y. Deng, Z. Pan, H. Suryanarayana, A. Kadavelugu, L. Liu, C. Belcastro und E.-K. Paatero, "Power Loss Evaluation for Active and Magnetic Components in a SiC MOSFET-Based Power Electronic System," *IEEE Energy Conversion Congress and Exposition (ECCE)*, pp. 3228-3234, 2017.

- [15] Y. Deng, J. Li, K. H. Shin, T. Viitanen, M. Saeedifard und R. G. Harley, "Improved Modulation Scheme for Loss Balancing of Three-Level Active NPC Converters," *IEEE Transactions on Power Electronics*, Bd. 32, Nr. 4, pp. 2521-2532, 2017.

- [16] M. Kazimierczuk, High-Frequency Magnetic Components, 2nd Edition, John Wiley & Sons, 2014.

- [17] K. Venkatachalam, C. Sullivan, T. Abdallah and H.-4. Tacca, "Accurate Prediction of Ferrite Core Loss with Nonsinusoidal Waveforms Using Only Steinmetz Parameters," *IEEE Workshop on Computers in Power Electronics*, pp. 36-41, 2002.

- [18] Brochure "SINAMICS Niederspannungsumrichter", DFMC-B10032-03, Erlangen: Siemens, 2022.

- [19] ,NPR 9090:2018 nl".

- [20] Y. Neyret, "DC Microgrids Principles and Benefits,"

- 2023. [Online]. Available: https://www.dc.systems/assets/public/DC-Systems-White-Paper.pdf.

- [21] "EN IEC 61558-1:2019".

- [22] X. She, A. Q. Huang, Ó. Lucía und B. Ozpineci, "Review of Silicon Carbide Power Devices and Their Applications," *IEEE Transactions on Industrial Electronics*, Bd. 64, Nr. 10, pp. 8193-8205, 2017.

- [23] S. Langfermann, M. Owzareck and L. Fräger, "Design Space Optimization of a SiC Drive Inverter with an Integrated All-Pole Sine Filter," 23rd European Conference on Power Electronics and Applications, pp. P.1-P.10, 2021.

- [24] "IEC 61010-1 / -1-201".

- [25] L. Fräger, S. Langfermann, M. Owzareck and J. Friebe, "An analytic inverter loss model for design and operation space optimization," 23rd European Conference on Power Electronics and Applications, pp. 1-10, 2021.

- [26] P. Apte, S. Lin, L. Fräger and J. Friebe, "Design considerations for a 50 kW Dual-Bridge Series Resonant DC/DC Converter with Wide-Input Voltage Range for Solid-State Transformers," *IEEE Energy Conversion Congress and Exposition (ECCE)*, pp. 1164-1170, 2021.

- [27] A. Hillers, D. Christen and J. Biela, "Design of a Highly Efficient Bidirectional Isolated LLC resonant converter," 15th International Power Electronics and Motion Control Conference (EPE/PEMC), pp. DS2b.13-1-DS2b.13-8, 2012.

- [28] B. Zhao, Q. Song, W. Liu and Y. Sun, "Overview of Dual-Active-Bridge Isolated Bidirectional DC–DC Converter for High-Frequency-Link Power-Conversion System," *IEEE Transactions on Power Electronics*, vol. 29, no. 8, pp. 4091-4106, 2014.

- [29] R. Beres, X. Wang, F. Blaabjerg, M. Liserre and C. Bak, "A Review of Passive Power Filters for Three-Phase Grid Connected Voltage-Source Converter," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 1, no. 4, pp. 54-69, March 2016.

- [30] A. Jafari, M. S. Nikoo, F. Karakaya and E. Matioli, "Enhanced DAB for Efficiency Preservation Using Adjustable-Tap High-Frequency Transformer," *IEEE Transactions on Power Electronics*, vol. 7, no. 35, pp. 6673-6677, 2020.

- [31] V. Karthikeyan, S. Rajasekar, S. Pragaspathy and F. Blaabjerg, "A High Efficient DAB Converter under Heavy Load Conditions Using Inner Phase Shift Control," *IEEE International Conference on Power Electronics, Drives and Energy Systems (PEDES)*, pp. 1-6, 2018.

- [32] L. Fräger, N. Badenhop, S. Langfermann, M. Owzareck, D. Kampen and J. Friebe, "Dual Active Bridge Converter: Simple Peak Current Limitation by Dual Phase Shift Control," *PCIM Europe*, pp. 1-5,

2022.

- [33] J. Gottschlich, M. Kaymak, C. Martin and R. De Doncker, "A flexible test bench for power semiconductor switching loss measurements," *IEEE 11th International Conference on Power Electronics and Drive Systems*, pp. 442-448, 2015.

- [34] J. Lutz, H. Schlangenotto, U. Scheuermann and R. D. Doncker, Semiconductor Power Devices: Physics, Characteristics, Reliability, Berlin, Heidelberg: Springer-Verlag, 2011.

- [35] T. Brinker, P. Mand und J. Friebe, "Impact of GaN-HEMT Combinations with Different Die-Size on the Efficiency of a Single-Phase Photovoltaic Differential Buck Inverter," *IEEE Energy Conversion Congress and Exposition (ECCE)*, pp. 1-8, 2022.

- [36] J. Holtz, "Pulsewidth modulation-a survey," *IEEE Transactions on Industrial Electronics*, vol. 5, no. 39, pp. 410-420, 1992.

**Lukas Fräger** was born in Hamelin, Germany on 11<sup>th</sup> January 1994. He received his B.Sc. (2016) and his M.Sc. (2018) in electrical engineering at RWTH Aachen University in Aachen, North-Rhine-Westfalia, Germany.

During his studies he worked as fellow at the Institute for Production of E-Mobility components (PEM) at RWTH Aachen and was an intern at Hella GmbH&Co KG. After graduating he joined BLOCK Transformatoren-Elektronik GmbH in Verden, Germany where he is pursuing his industrial PhD in collaboration with Leibniz University of Hannover and University of Kassel in the field of power electronics. Since 2021 he is head of the electronics development and leads the electronics pre-development. Current research interests include power electronics, especially optimization, benefits and challenges of wide bandgap semiconductors and effects of high switching frequencies.

[37] L. Fräger, S. Langfermann, M. Owzareck, D. Kampen und J. Friebe, "Analysis of the Loss Distribution of a 6 kW two Stage Power Supply for 600 V DC Applications," 24th European Conference on Power Electronics and Applications, pp. 1-8, 2022.

Jens Friebe (Senior Member, IEEE) received the B.Sc., M.Sc., and Dr.-Ing. degrees in electrical engineering from the University of Kassel, Germany. He has been responsible for the research area of passive components in power electronics at the Institute for Drive Systems and Power

Electronics, Leibniz University Hannover, Germany, from 2018 to 2022. Before that, he worked for more than 13 years at SMA Solar Technology, Germany, in the field of PV-inverter topologies, wide-bandgap semiconductors, magnetic components, control strategies for high switching frequencies and power electronics packaging. He is currently head of the Power Electronics Group at the University of Kassel, Germany. He invented more than 30 granted patents in the field of power electronics.