Received 5 September 2020; accepted 14 September 2020. Date of publication 22 September 2020; date of current version 26 October 2020. The review of this article was arranged by Associate Editor Yingyi Yan.

Digital Object Identifier 10.1109/OJPEL.2020.3025658

# Electrical and Thermal Characterization of an Inductor-Based ANPC-Type Buck Converter in 14 nm CMOS Technology for Microprocessor Applications

PEDRO A. M. BEZERRA <sup>10</sup> (Member, IEEE), FLORIAN KRISMER <sup>10</sup> (Member, IEEE),

JOHANN W. KOLAR <sup>10</sup> (Fellow, IEEE), RIDUAN K. ALJAMEH <sup>10</sup> 2, S. PAREDES (Member, IEEE), R. HELLER 2,

T. BRUNSCHWILER <sup>10</sup> (Senior Member, IEEE), PIER A. FRANCESE (Senior Member, IEEE),

T. MORF <sup>10</sup> (Senior Member, IEEE), MARCEL A. KOSSEL (Senior Member, IEEE), AND M. BRAENDLI 2

<sup>1</sup>Power Electronic Systems Laboratory (PES), ETH Zurich, Zurich 8092, Switzerland <sup>2</sup>IBM Research Zurich, Rüschlikon 8803, Switzerland

CORRESPONDING AUTHOR: PEDRO A. M. BEZERRA

Part of this work was carried out within the European CarrICool Project under the Seventh Framework Program for Research and Technological Development (FP7 ICT-619488).

**ABSTRACT** Integrated Voltage Regulators (IVRs) are attractive substitutes for conventional voltage regulators located on the motherboards, due to outstanding dynamic performances and superior power densities. IVRs operate with switching frequencies in the range of 100 MHz and are assembled in highly compact packages close to the microprocessor load. This paper presents a comprehensive characterization of a PCBand inductor-based four-phase ANPC-type IVR that uses a Power Management IC (PMIC) implemented in a 14 nm CMOS technology node. The characterization is based on the results of electrical measurements, thermal inspections of the chip surface, and simulations, which enables the separation of the total losses into on-chip and off-chip loss components and the allocation of important loss components inside the chip. The investigated IVR achieves a maximum efficiency of 84.1% at an output power of  $P_{\text{out}} = 640 \,\text{mW}$  and a switching frequency of  $f_s = 50 \,\mathrm{MHz}$ . The thermal measurements reveal that the maximum efficiency of the PMIC itself is between 88 % and 90 % at  $f_s = 50 \,\mathrm{MHz}$  and  $P_{\mathrm{out}} \in [500 \,\mathrm{mW}, 600 \,\mathrm{mW}]$ ; at  $P_{\mathrm{out}} = 890 \,\mathrm{mW}$ , a chip current density of 24.7 A/mm<sup>2</sup> is achieved. The findings in particular point out that the losses in the chip-internal interconnections, i.e., the conductors of the Power Distribution Network (PDN) and the twelve stacked metal layers below the PDN, have a substantial contribution to the total losses. Furthermore, the combination of Cadence post-layout simulations with impedance networks obtained from an appropriate software tool, e.g., FastHenry, is found to establish a suitable toolbox for estimating losses in IVRs.

**INDEX TERMS** 14 nm technology, ANPC, CMOS, half-bridge, IVR, multi-phase, PMIC, stacked transistors, thermal electrical characterization.

## I. INTRODUCTION

Cloud computing in data-centers, internet-of-things devices, as well as applications related to mobile communication, automotive, and artificial intelligence drive the needs for increased data processing capabilities of modern microprocessors, which, today, operate at clock frequencies up to 5 GHz [1] and have tens of cores in their more advanced versions [1]–[3]. Increased computational power of microprocessors has

been achieved by reducing the transistors' gate widths to below 22 nm in recent technology nodes, leading to breakdown voltages of less than 1 V. However, the performance increase comes at the cost of increased power consumption, exceeding 150 W per device [4], and is accompanied by high supply currents reaching values close to 100 A considering a typical package voltage of 1.8 V [5]. In this regard, the concepts of independent Voltage Domains (VDs) for different cores or

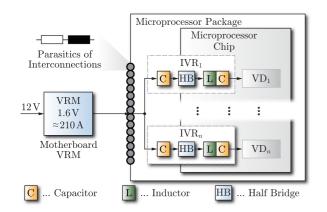

FIG. 1. Granular power delivery of a modern microprocessor system, where a single external voltage regulator provides power to multiple IVRs.

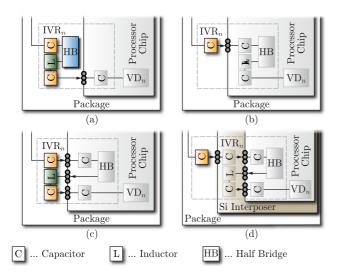

FIG. 2. Packaging solutions of IVRs providing granular power delivery in modern microprocessors. (a) Fully on-package IVR [6]; (b) fully on-die IVR [7]–[9]; (c) and (d) hybrid IVRs where the half-bridges are on the microprocessor die and the main passive components (inductors and capacitors) integrated into the package [10]–[12] or the silicon interposer [13]–[15].

parts of the core and Dynamic Voltage and Frequency Scaling (DVFS) are effective countermeasures to reduce the power demands of microprocessors, since each core can be separately operated according to its workload. This is achieved with a granular power delivery system that uses several independent Integrated Voltage Regulators (IVRs) for the different VDs, cf. Fig. 1.

Literature reveals numerous different realizations of IVRs, ranging from on-package implementations to fully chip-integrated solutions. In case of on-package implementations, a common package accommodates all components of the IVRs and the microprocessor, however, the IVRs do not reside in the microprocessor die itself (off-die), cf. Fig. 2(a) [6]. On-package IVRs allow for reduced parasitics of the supply lines (resistances, lead inductances), as compared to conventional

(off-package) voltage regulators, however, they are still too large to be suitable for microprocessor applications that require very thin cases and tens of VDs, e.g., mobile phones, laptop computers, and tablets. By contrast, in case of fully chip-integrated (on-die) IVRs, all components reside on the microprocessor die, as shown in Fig. 2(b). Fully integrated IVRs realize very low parasitics of the supply lines and enable a reduction of the number of supply connections between the package and the microprocessor die, due to the reduced total input current. However, these benefits come at the cost of substantial chip area being sacrificed for the IVRs' components [7], [8] and / or highly challenging realization of chip-integrated inductors, e.g., due to the need of complex Through Silicon Vias (TSVs) [9] and additional Back End Of Line (BEOL) post-processing steps [8]. In addition, the chip technology node used for the microprocessor defines stringent design constraints, which considerably limit the flexibility of the converter design.

In an alternative approach, denoted as hybrid IVRs in this paper, only the active switching stages of the IVRs and necessary parts of the dc capacitors reside on-die and the remaining passive components, in particular the inductors in case of buck-type solutions, are located in the package or in a lowercost second chip (silicon interposer), as shown in Fig. 2(c), (d). Hybrid IVRs can operate at very high switching frequencies of more than 100 MHz, due to the low switching losses of the microprocessor's transistors, and benefit from increased flexibilities for designing the passive components that reside in the package [10]-[12] or on the silicon interposer [13]-[16]. Compared to fully chip-integrated IVRs, hybrid solutions feature a reduction of the occupied microprocessor chip area and / or the use of less challenging connections between on-die and off-die components, at the cost of an increased number of connections to and from the microprocessor die. For both, package-based and interposer-based hybrid IVRs, high inductor and chip current densities, e.g., 3.2 A/mm<sup>2</sup> and 10.8 A/mm<sup>2</sup> respectively in [15], and efficiencies around 90 % have been reported [10], [13].

All realizations of IVRs have in common that the converter design is not straightforward, since technically reasonable realizations are feasible within relatively wide ranges of values for different design variables, e.g., switching frequency and inductor current ripple in case of a buck converter. However, the chosen values have an impact on the finally achieved efficiency. Accordingly, a systematic converter design approach, using model-based optimization, is commonly conducted [17]. In this regard, a continuous verification and refinement as well as the identification of eventually present deficiencies of the used models is important, in particular in case of emerging technologies, to gain a better understanding of the technology and to improve the accuracies of subsequent optimizations. According to a literature research, most related work focuses on electrical or thermal characterizations of selected on-package and chip-integrated components. With regard to electrical characterization, references [12], [18]–[20], for example, present measured impedance characteristics of

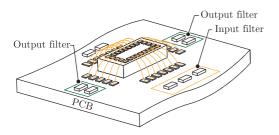

FIG. 3. Illustration of the investigated setup: the active switching stage resides in the Power Management IC (PMIC), the passive components (capacitors, inductors) on the PCB, and bond wires provide the electrical connections.

on-package conventional and coupled inductors, without and with magnetic core, or examine parasitic resistances and capacitances of key components in Through Silicon Interposers, i.e., metal layers for BEOL interconnects, TSVs, redistribution layer, and micro-bumps. In case of thermal characterizations, related publications typically focus on the identification of peak chip temperatures in order to determine measures to prevent overheating, e.g., observations of chip temperatures under different load conditions [21], [22] and thermal characterization of a microprocessor to derive guidelines for on-line thermal management [23], [24]. Only few publications discuss complete models of IVRs and provide experimental results for verification, e.g., [15], [25] for the realization of a buck-type IVR realized in 45 nm CMOS technology.

Common topologies for IVRs are Switched Capacitor (SC) and buck converters. Since SC converters have been analyzed in detail in a previous investigation [26], the authors intentionally decided to focus on a buck converter, with the aim of this paper being the identification and allocation of the loss components in a four-phase buck-type hybrid IVR, which employs a switching stage realized in 14 nm CMOS technology. Electrical and thermal measurements are conducted in order to enable a separation of on-chip losses (e.g., due to conduction and switching) and off-chip losses (e.g., in the inductors), which requires a physical separation of the chip and the inductors. The investigated IVR employs discrete inductors and capacitors that reside on a Printed Circuit Board (PCB); bond wires provide the electrical connections between chip and PCB, which is illustrated in Fig. 3. To begin with, Section II details the implemented Power Management IC (PMIC), i.e., converter specifications, main schematic diagram of the semiconductor power stage, chip lithograpy, and gate signal generation unit. Section III describes the conducted thermal and electrical characterization procedures that serve for the separation of the total losses into on-chip and off-chip components and discusses the obtained results, which reveal that the losses in the metal layers and the Power Distribution Network (PDN) of the PMIC have a substantial contribution to the total losses. The complete IVR achieves a maximum efficiency of 84.1 % and a full-load efficiency of 83.0 % and a corresponding chip current density of 24.7 W/mm<sup>2</sup>. The maximum efficiency of the PMIC itself, which is subject to increased uncertainty due

TABLE I Specifications of the Investigated four-phase IVR.

| Parameters                | Symbol                 | Value                                      |

|---------------------------|------------------------|--------------------------------------------|

| Input voltage             | $V_{\rm in}$           | 1.6 V                                      |

| Output voltage range      | $V_{ m out}$           | 0.8 V to 1.2 V                             |

| Output power              | $P_{out}$              | 800 mW                                     |

| Max. input voltage ripple | $\Delta V_{\rm in,pp}$ | $V_{\rm in} \cdot 1.2\% = 19.2 \text{ mV}$ |

| Min. output voltage       | $V_{\text{out,min}}$   | 0.6 V                                      |

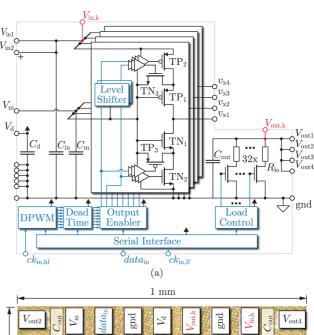

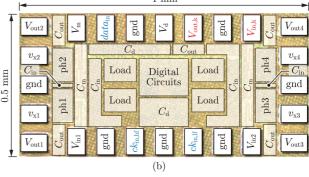

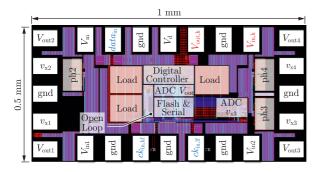

FIG. 4. (a) Simplified schematics of the PMIC containing the four-phase CMOS ANPC HBs. (b) Chip micrography of the implemented PMIC with the pads according to (a); 'ph1' to 'ph4' denote the locations of the HBs of the four converter phases; ' $C_{in}$ ,' ' $C_{out}$ ,' and ' $C_{d}$ ' refer to the positions of the corresponding capacitances realized with MOS technology; loads and gate signal generation unit are located toward the center of the PMIC.

to the measurement with thermal camera, is between 88% to 90% for output power levels between  $500\,\mathrm{mW}$  and  $600\,\mathrm{mW}$ .

# **II. PMIC IN 14 NM CMOS TECHNOLOGY**

Table I lists the specifications of the investigated IVR, which is a prototype of an IVR intended for providing power to a VD of a CPU core, and Fig. 4(a) depicts the schematics of the implemented PMIC. Since the input voltage of 1.6 V exceeds the transistors' maximum drain-source voltage of a short channel device of the technology, each switch of the

realized buck converter is composed of the two stacked transistors. Furthermore, TN<sub>3</sub> and TP<sub>3</sub> in Fig. 4(a) realize an Active Neutral Point Clamping (ANPC) circuit in order to avoid unbalanced voltages across the main power transistors during or after switching, to improve efficiency and reliability [27]. The chip consists of four CMOS Half-Bridges (HBs) with ANPC, an open-loop logic circuitry to generate the switches' gate signals, and a configurable internal resistive load.

The chip requires three supply voltages. The main supply is connected to the  $V_{\text{in}\{1,2\}}$ -pads, which share the converter input current. An auxiliary voltage is provided at the  $V_{\text{m}}$ -pad, to define the gate bias voltages for TP<sub>1</sub> and TN<sub>1</sub> and the source potentials of the clamping switches TN<sub>3</sub> and TP<sub>3</sub>. There, the applied voltage needs to be controlled to half of the input voltage,  $V_{\text{m}} = V_{\text{in}}/2$ , to avoid additional leakage currents.

The voltage supply of the auxiliary analog and digital circuits (open-loop logic circuitry, load control circuitry, serial interface, and flash memory) is connected to the  $V_{\rm d}$ -pad. A two-wire unidirectional serial interface (pads  $data_{\rm in}$  and  $ck_{\rm in,lf}$  for data and clock inputs, respectively) serves for the configuration of gate signal generation unit and on-chip load; an on-chip flash memory stores the current configuration.

The signal provided at the  $ck_{\rm in,hf}$ -pad controls the switching frequency of the CMOS ANPC HBs. The frequency of the given clock signal is divided by 16, e.g., a clock signal with a frequency of 1.6 GHz at the  $ck_{\rm in,hf}$ -pad results in a switching frequency of 100 MHz. The switched output voltages are present at the  $v_{x\{1,2,3,4\}}$ -pads and applied to the external filter inductors. The filtered output voltages are connected back to the PMIC at the  $V_{\rm out\{1,2,3,4\}}$ -pads, to utilize the chip-integrated configurable load. The chip includes two Kelvin pads,  $V_{\rm in,k}$  and  $V_{\rm out,k}$ , to allow for accurate four-point voltage measurements of the input and output voltages, respectively. Seven ground pads are used in parallel to reduce the converter losses and provide a stable reference for the internal chip circuits.

Fig. 4(b) shows the micrography of the realized PMIC in 14 nm CMOS technology. The total chip area is 0.5 mm<sup>2</sup>, from which 0.032 mm<sup>2</sup> are dedicated to the HBs of the fourphase converter [ph $\{1,2,3,4\}$  in Fig. 4(b)], 0.027 mm<sup>2</sup> to the digital circuits, and 0.052 mm<sup>2</sup> to the four chip-internal loads. The power stages are placed at the edges of the chip, to achieve a layout that features short paths to the respective input and output pads, e.g.,  $V_{\text{in},1}$  and  $v_{\text{x},1}$  in case of phase 1, in order to avoid excessive conduction losses in the Power Distribution Network (PDN) of the chip, as further detailed in Section III. Chip-integrated buffering of the supply voltages  $V_{\rm in}$ ,  $V_{\rm m}$ , and  $V_{\rm d}$  and the voltage provided to the load,  $V_{\rm out}$ , is realized with a combination of Metal-Oxide-Semiconductor (MOS) and Metal-Insulator-Metal (MIM) capacitors. The MOS capacitors are placed in the Front End Of Line (FEOL) areas marked in Fig. 4(b) and MIM capacitors are placed in the entire BEOL area of the chip excluding the pads. Fig. 5(c)

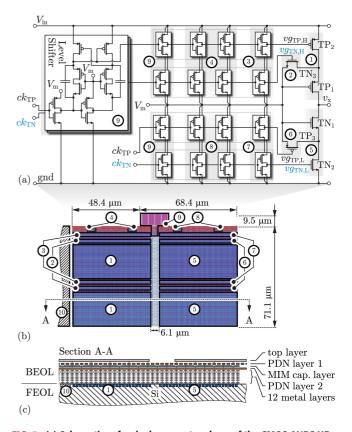

FIG. 5. (a) Schematics of a single converter phase of the CMOS ANPC HB; (b) Layout picture of the designed CMOS ANPC HB corresponding to the schematics of Fig. 5(a)). The two clamping switches, two independent gate drivers, and one level shifter increase the chip FEOL area by approximately 14% as compared to the a conventional CMOS HB with stacked transistors.

illustrates a cross-sectional drawing of the power stage, revealing FEOL, BEOL, and the general locations of MIM and MOS capacitors.

# A. POWER STAGE

Fig. 5(a) depicts a detailed schematic drawing of a single CMOS ANPC HB phase of the implemented PMIC. The output stage is composed of the main transistors (①:  $TP_1$ ,  $TP_2$ ; ③:  $TN_1$ ,  $TN_2$ ) and the clamping transistors (②:  $TN_3$  and ⑥:  $TP_3$ ). Four gate drivers, ③, ④, ⑦, ⑧, ⑨, are used for the main switches and the clamping switches, where each gate driver is composed of four inverter stages that are connected in series. Two level-shifters ⑨ adjust the voltages of the input signals in order to be suitable for the high-side gate drivers.

Fig. 5(b) presents the layout of a single converter phase corresponding to the schematics of Fig. 5(a) and Fig. 5(c) depicts a drawing of the cross section of the chip, revealing the top metal layer (contains the pads), the two layers of the PDN with the MIM capacitor layer in between, and the 12 metal layers. The FEOL area of the complete power stage is 0.0081 mm<sup>2</sup>. All main transistors (① and ⑤) are of same size, each clamping transistor (② and ⑥) and the final inverter stage of each gate driver (③ and ⑦) require 1/10 of the area of

<sup>&</sup>lt;sup>1</sup>According to [27] the ANPC topology is expected to achieve an increase of the efficiency by up to 2% at a switching frequency of 250 MHz.

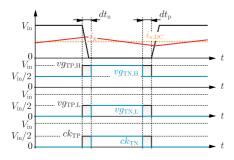

FIG. 6. Clock and gate signals of a single CMOS ANPC HB [27].

one main transistor, and the second and third stages of each gate driver (4) and (8) together need 1/50 of the area of one main transistor. The two additional gate drivers for the clamping transistors and the additional level shifter increase the total chip FEOL area by approximately 14% as compared to a conventional CMOS HB with stacked transistors. The remaining FEOL area is used to realize MOS capacitors (10).

### **B. GENERATION OF GATE SIGNALS**

Each phase of the CMOS ANPC HB uses the gate signals depicted in Fig. 6 to generate a rectangular voltage with its main transistors at the respective output node, i.e.,  $v_{x,i} = 0$  or  $v_{x,i} = V_{in}$  for  $i \in \{1, 2, 3, 4\}$ , and to balance the voltages across the stacked main transistors with the clamping transistors. The shown sequence is based on two complementary signals with dead time,  $ck_{TP}$  and  $ck_{TN}$ , and uses separate dead times,  $dt_n$  and  $dt_p$ , for the falling and rising edges of the rectangular output voltage.<sup>2</sup> The durations of both dead times,  $dt_n$  and  $dt_p$ , are programmable in order to enable the operating-point dependent optimization of the switching losses. Further details related to the operation of the CMOS ANPC HB are presented in [27].

Fig. 7 shows the simplified schematics of the open-loop circuitry that is used to generate  $ck_{\mathrm{TP}\{1,...4\}}$  and  $ck_{\mathrm{TN}\{1,...4\}}$  for all four converter phases. The combination of four-bit counter, four-bit comparator, and RS latch is used to generate a PWM signal with a frequency equal to  $f_{\mathrm{ck}}/16$  and a programmable duty cycle that can be adjusted with a resolution of  $\Delta T = 1/f_{\mathrm{ck}}$ . Three shift registers further process the PWM signal in order to generate gate signals that are phase shifted by 90°, 180°, and 270°; from this, a configurable phase angle selector block redirects selected PWM signals, with or without phase shift, to the dead time generation units of the four converter phases. Finally, phase-enabling circuits allow for a proper deactivation of all transistors of a selected output stage, which enables the implementation of phase-shedding to achieve increased part-load efficiency.

TABLE II Accuracies of DAU34970 (voltage) and N6781A (current).

| Equipment | Measurement error |                       |  |  |  |

|-----------|-------------------|-----------------------|--|--|--|

|           | δ                 | $\epsilon$            |  |  |  |

| DAU34970  | $\pm 0.0035 \%$   | $\pm 50\mu\mathrm{V}$ |  |  |  |

| N6781A    | $\pm 0.03 \%$     | $\pm 250 \mu A$       |  |  |  |

### III. CHARACTERIZATION OF THE BUCK CONVERTER

The employed procedure to characterize the converter losses takes calculated and simulated results as well as experimental results from electrical and thermal measurements into account, to accurately identify the different loss components of the investigated converter. The procedure comprises of the steps listed below.

- Numerical estimation of the dc resistances of the power transistors' channels, the metal layers, the converter interconnections, and the PDN using numerical software tools (Cadence post-layout simulation, FastHenry).

- Electrical measurement of the converter's dc resistances and comparison to the numerical estimations in order to clarify whether all important contributions to the dc losses are considered.

- 3) Use of the chip-internal configurable resistive load to characterize the temperature rise of the chip with respect to on-chip power dissipation, which enables a separation of the converter's ac and dc losses.

- 4) Experimental evaluation at different operating points, using an external electronic load (chip-internal load is disabled): electrical measurements of input and output power levels and thermal measurement of the chip temperature. This enables a separation of on-chip and offchip losses of the IVR.

Steps 1 and 2 are further detailed in Section III-A, step 3 in Section III-B, and step 4 in Section III-C.

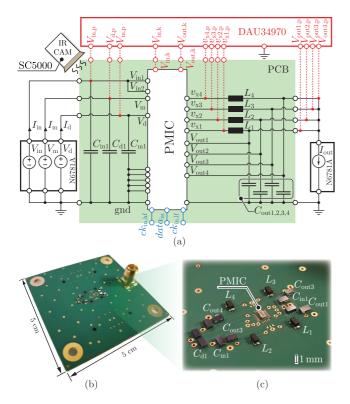

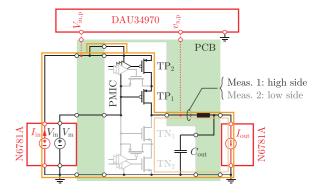

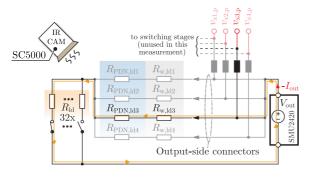

Fig. 8 depicts the employed experimental setup with a schematic overview in Fig. 8(a), the realization of the hybrid PCB-based four-phase IVR in Fig. 8(b), and a magnified view of the IVR in Fig. 8(c). The investigated IVR utilizes the PMIC of Fig. 4. High Temperature Silicon Capacitors (HTSC) with low series equivalent inductance (manufactured by IPDiA) realize the dc capacitors,  $C_{\rm in1}=43\,{\rm nF},~C_{\rm d1}=10\,{\rm nF},~C_{\rm m1}=10\,{\rm nF},~{\rm and}~C_{\rm out\{1,2,3,4\}}=10\,{\rm nF}.$  Solenoidal inductors with magnetic cores (PFL1005-36NMR, manufactured by Coilcraft) with  $L_{\{1,2,3,4\}}=36\,{\rm nH}$  form the output inductors. All measurements are conducted with the high-accuracy equipment listed below.

- *N6781A:* two-quadrant source/measure unit, provides the supply voltages and the load current.

- *DAU34970:* data acquisition unit resistances of the PMIC arising used for all voltage measurements.

- *SC5000:* thermal camera to monitor the temperature distribution on the chip. The camera is equipped with the microscopic zoom lens L0808X5 (1.9 × 1.4 mm).

Table II lists the specified relative and absolute measurement uncertainties,  $\delta$  and  $\epsilon$ , that apply for a certain value, X,

<sup>&</sup>lt;sup>2</sup>Please note that TP<sub>1</sub>, TP<sub>2</sub>, and TP<sub>3</sub> are p-type transistors, e.g.,  $vg_{\text{TP},\text{L}} = 0$  turns TP<sub>3</sub> on and  $vg_{\text{TP},\text{L}} = V_{\text{in}}/2$  turns TP<sub>3</sub> off. Accordingly, the gate drivers ensure that TN<sub>2</sub>, TP<sub>2</sub>, TN<sub>3</sub>, and TP<sub>3</sub> are turned off during both dead times.

FIG. 7. Simplified schematics of the open-loop circuitry used to generate the gate signals of the converter HBs. This circuit generates the 16 required signals to operate the 4 CMOS ANPC HBs of the PMIC of Fig. 4(a).

FIG. 8. (a) Measurement setup used to for the loss characterization and the efficiency measurements. Aluminum bond wires are used to connect the PMIC to the PCB substrate; SMA connectors with coaxial cables provide the connections between PCB, measurement devices, and power supplies. (b) Picture of the corresponding assembled PCB-based IVR. (c) Magnified view of the center of the IVR with the PMIC in the middle.

for a corresponding measured value,  $X_{\text{meas}}$ ,

$$X \in [X_{\text{meas}}(1-\delta) - \epsilon, X_{\text{meas}}(1+\delta) + \epsilon]. \tag{1}$$

For all experiments,  $V_{\text{in,k}} = 1.6 \text{ V}$  and  $V_{\text{m}} = 0.8 \text{ V}$  apply.

### A. DC RESISTANCES

The dc losses substantially contribute to the total converter losses, which is partly due to the MOSFETs' on-state resistances. However, also the PDN is prone to increased losses in

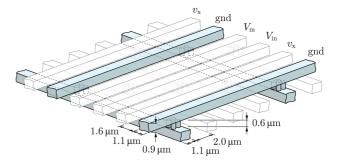

FIG. 9. The Power Distribution Network (PDN) consists of horizontal and vertical conductors; four vias connect the conductors at each crossing. The PDN alternately provides connections for  $V_{\rm in}$ ,  $V_{\rm m}$ , gnd, and  $v_{\rm x}$ , where  $v_{\rm x}$  denotes the switched voltage of the connected converter phase, e.g.,  $v_{\rm x}=v_{\rm x1}$  applies in case of the PDN for converter phase 1. A detailed description of the PDN is provided in [28].

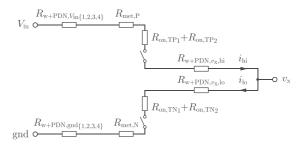

FIG. 10. Internal resistances of the PMIC arising from bond wires and PDN  $(R_{w+PDN,V_{in}[1,2,3,4]}, R_{w+PDN,D_{in}[1,2,3,4]}, R_{w+PDN,D_{in},L_i,hi}, R_{w+PDN,D_{in},L_i,hi})$ , metal layers stack and vias  $(R_{met,P}, R_{met,N})$ , and MOSFET channels  $(R_{on,TP_{[1,2]}}, R_{on,TN_{[1,2]}})$ .

the 14 nm CMOS technology, due to very thin layers of metallization, and needs to be taken into account. Fig. 9 illustrates the layout of the PDN, which realizes an interleaved structure of the required power conductors (e.g.,  $V_{\rm in}$ ,  $V_{\rm m}$ , gnd, and, in case of converter phase 1,  $v_{\rm x1}$ ). It consists of horizontal conductors on a first layer, vertical the required power conductors on a second layer, and vias at the crossings to connect the two layers to each other [28].

Fig. 10 depicts the network of the internal resistances of the PMIC, which arise from bond wires and

TABLE III Computed Values of the Resistances shown in Fig. 10.

| Parameters                                                         | Symbol                                          | Value (mΩ)               |  |  |  |  |

|--------------------------------------------------------------------|-------------------------------------------------|--------------------------|--|--|--|--|

| Values obtained from Cadence simulations                           |                                                 |                          |  |  |  |  |

| PMOS channel at $T_{\rm j} = 85^{\circ}{\rm C}$                    | $R_{\mathrm{on,TP}_{\{1,2\}}}$                  | 115/2                    |  |  |  |  |

| PMOS, metal layers stack                                           | $R_{met,P}$                                     | 18                       |  |  |  |  |

| NMOS channel at $T_{\rm j} = 85^{\circ}{\rm C}$                    | $R_{\text{on,TN}_{\{1,2\}}}$                    | 103/2                    |  |  |  |  |

| NMOS, metal layers stack                                           | $R_{ m met,N}$                                  | 25                       |  |  |  |  |

| Values obtained from FastHenry computations                        |                                                 |                          |  |  |  |  |

| Bond wires + PDN of $V_{\text{in}}$ (converter phases 1 to 4)      | $R_{\text{w+PDN},V_{\text{in}\{1,2,3,4\}}}$     | {145, 185,<br>145, 182}  |  |  |  |  |

| Bond wires + PDN of $v_x$ , high-<br>side on (same for all phases) | $R_{\mathrm{w+PDN},v_{\mathrm{x}},\mathrm{hi}}$ | 139                      |  |  |  |  |

| Bond wires + PDN of $v_x$ , low-<br>side on (same for all phases)  | $R_{\text{w+PDN},v_{\text{x}},\text{lo}}$       | 100                      |  |  |  |  |

| Bond wires + PDN of gnd<br>(converter phases 1 to 4)               | $R_{\text{w+PDN,gnd}}{}_{\{1,2,3,4\}}$          | $\{159, 197, 155, 155\}$ |  |  |  |  |

PDN  $(R_{w+PDN}, V_{in,\{1,2,3,4\}}, R_{w+PDN}, v_{x,hi}, R_{w+PDN}, v_{x,lo}, and$  $R_{\text{w+PDN,gnd}_{\{1,2,3,4\}}}$ ), metal layers stack and vias  $(R_{\text{met,P}})$  and  $R_{\text{met,N}}$ ), and MOSFET channels  $(R_{\text{on,TP}_{\{1,2\}}})$  and  $R_{\text{on,TN}_{\{1,2\}}})$ , metal layers stack and vias ( $R_{\text{met,P}}$  and  $R_{\text{met,N}}$ ), and MOS-FET channels ( $R_{\text{on,TP}_{\{1,2\}}}$  and  $R_{\text{on,TN}_{\{1,2\}}}$ ). FastHenry has been used to compute the resistances of the PDN and Cadence post-layout simulations to determine the resistances of metal layers stack, vias, and MOSFETs; Table III lists the respective results. According to this result, the resistances of the metal layers stacks are comparably small, however, the effective resistances of the PDN are more than twice of the on-state resistances of two series-connected MOSFETs, e.g., in case of the high-side conduction path of phase 1,  $R_{\text{W+PDN},V_{\text{in}\{1,2,3,4\}}}$  +  $R_{\text{w+PDN},v_x,\text{hi}} = 284 \text{ m}\Omega \text{ and } R_{\text{on,TP}_1} + R_{\text{on,TP}_2} = 115 \text{ m}\Omega \text{ ap-}$ ply, even though, the maximum conductor density possible with the given design rules has been utilized. Table III also reveals that  $R_{\text{W+PDN},V_{\text{in}\{2,4\}}}$  are substantially larger than  $R_{\text{w+PDN},V_{\text{in}\{1,3\}}}$ , which is due to longer conduction paths, since the supply pads,  $V_{\text{in}1}$  and  $V_{\text{in}2}$  in Fig. 4, are located close to phases 1 and 3. Similarly, the increased resistance of  $R_{\text{w+PDN,gnd}_2}$ , as compared to  $R_{\text{w+PDN,gnd}_{\{1,3,4\}}}$ , can be explained based on the arrangement of the ground pads, because, due to layout-specific restrictions, the top-side pad sequence is  $V_{\rm m}-dat$  – gnd instead of  $V_{\rm m}$  – gnd – dat, which causes a disturbance of the symmetry.

The subsequent measurement of the dc resistances is conducted with the setup shown in Fig. 11, which allows for an experimental characterization of the high-side and low-side conduction paths, depending on whether  $TP_{\{1,2\}}$  or  $TN_{\{1,2\}}$  conduct. Accordingly,

$$R_{\text{dc,hi,\{1,2,3,4\}}} \in \left\lceil \frac{\min(V_{\text{in,p}} - v_{x\{1,2,3,4\}})}{\max(I_{\text{out}})} \right\rceil \text{ and } (2)$$

$$R_{\text{dc,lo,}\{1,2,3,4\}} \in \left[ \frac{\min \left( v_{x\{1,2,3,4\}} \right)}{\max \left( -I_{\text{out}} \right)} \right]$$

(3)

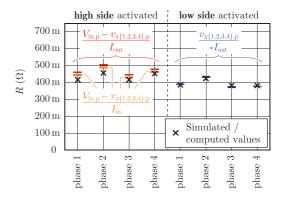

result for the high-side and low-side conduction paths, respectively. Fig. 12 depicts calculated and measured dc resistances (measured at an output current of 200 mA). Due to chipinternal leakage currents, which cause losses between 10 mW

FIG. 11. Setup used to measure the dc resistances of high side and low side of a single converter phase;  $v_{x,p}$  is the switching node of the measured phase, e.g.,  $v_{x1,p}$  in case of phase 1.

FIG. 12. Calculated and measured dc resistances of the four converter phases (measured at  $I_{\rm out} = 200$  mA and  $T_{\rm amb} = 20^{\circ}$ C); left: high-side resistances according to Fig. 11(a), right: low-side resistances according to Fig. 11(b). The high-side resistances are determined for input and output currents, revealing minor differences due to chip-internal leakage currents.

and 11 mW, slightly different dc resistances of the high-side conduction paths result, depending on whether the input or the output currents are used for the calculation. Calculated and measured resistances match well, which confirms the significant contribution of the PDN identified above.

### **B. THERMAL CHARACTERIZATION**

The relatively large resistance values of the chip-internal load enable an accurate electrical measurement of the losses. Therefore, this load is utilized for the experimental characterization of the dependency of the chip temperature on the losses dissipated in the chip, using the measurement setup depicted in Fig. 13. During the thermal characterization, the transistors of the PMIC are turned off. All four loads have been utilized separately (not simultaneously).

Main measurement uncertainties are related to measurement accuracy and losses in the bond wires, because it is unclear, to what extent the losses in the bond wires contribute to heating up the chip. Accordingly, the respective power is within

$$P_{\text{heat}} \in \left[ P_{\text{total}} - I_{\text{out}}^2 R_{\text{bw,eff}}, P_{\text{total}} \right],$$

(4)

FIG. 13. Simplified equivalent circuit of the measurement setup used to identify the characteristic of power dissipation versus chip temperature for the example of a measurement at the load assigned to converter phase 3. The voltage at the switching node of the corresponding converter phase, i.e.,  $v_{x3}$  in the depicted example, reveals the voltage that is present just outside the chip (similar to a Kelvin measurement).

since only the current to the load,  $I_{\rm out}$ , generates substantial losses in the bond wires; the implications of the losses in the bond wires due to the other currents, e.g., input and supply currents, are negligible. The total power includes the power levels at all ports (input, mid-point, output, supply of chipinternal digital components) and is determined with

$$P_{\text{total}} = V_{\text{in,p}}I_{\text{in}} + V_{\text{m,p}}I_{\text{m}} + V_{\text{d,p}}I_{\text{d}} + v_{\text{x,p}}I_{\text{out}},$$

(5)

where  $v_{x,p}$  denotes the voltage at the output node of the converter phase that corresponds to the tested internal load (e.g.,  $v_{x1,p}$  if load 1 is currently under test), since this node yields the most accurate measurement of the load voltage close to the PMIC (similar to a Kelvin pad). Aluminum wires with a length of 500  $\mu$ m and a diameter of 20  $\mu$ m realize the bond wires leading to a resistance of 42 m $\Omega$ . The input to every internal load is connected to the PCB via a single bond wire. The ground connection uses seven bond wires in parallel, however, due to the large resistance of the PDN, only a single bond wire may carry most of the return current through ground. Accordingly, based on a worst case assumption, the effective bond wire resistance may be up to

$$R_{\text{bw,eff}} = 2 \times 42 \,\text{m}\Omega = 84 \,\text{m}\Omega.$$

(6)

Still, the uncertainty remains small, e.g.,  $\pm 2.6\,\text{mW}$  at a dissipated power of 170 mW and a load current of 250 mA.

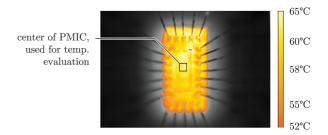

With regard to the thermal measurements, the chip has been painted with high-emissivity black paint to achieve accurate results. In steady-state, the distributions of the surface temperatures are found to be similar for all considered excitations. Fig. 14 presents a thermal image of the chip that results if the load dissipates a power of 180 mW. The observed local areas of increased or reduced temperatures are linked to the layouts of top layer and PDN, e.g., reduced temperatures result at the pads. Further temperature gradients are found close to the edges of the chip, which, however, are far from the investigated chip-internal converter parts. The obtained result is different to what is found for chips used in high-power modules, where large temperature gradients may occur on the

FIG. 14. Example of a thermal measurement of the load at a dissipated power of 178 mW. The temperature used for chip characterization is the mean value of the temperatures of  $3 \times 3$  pixels in the center of the PMIC.

FIG. 15. Identified power dissipation characteristic with respect to chip temperature.

surface, e.g. in IGBTs as presented in [29], and is due to the comparably small chip volume and the placement of the chip on the PCB, providing thermal insulation. Due to these reasons and because the control circuitry, which generates only negligible losses, resides at the center of the chip, it is assumed that the losses in the on-chip load resistors and the converter phases have similar implications on the chip temperature at the center. Thus, the average temperature of  $3 \times 3$  pixels in the middle of the chip is used as chip surface temperature,  $T_c$ , cf. Fig. 14. In the considered temperature range, the employed thermal camera, SC5000 (Flir), has an absolute accuracy of ±1°C. However, the presented setup uses the same camera and the same setup to identify the dependency of the chip temperature on the losses in a first step and to estimate the on-chip losses based on the chip temperature in a second setup that is conducted shortly after. Therefore, systematic errors are removed and only noise remains as a source of uncertainty for which an uncertainty equal to the standard deviation of ±0.3°C, typically found in the measurements, has been considered.

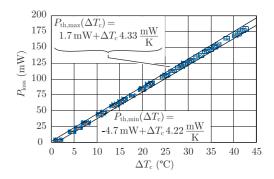

Fig. 15 depicts the experimental results for the power dissipation with respect to the difference between chip surface temperature and ambient temperature,

$$\Delta T_{\rm c} = T_{\rm c} - T_{\rm amb},\tag{7}$$

where the ambient temperature has been measured at the center of the chip prior to the load measurements and with no supply voltages being provided to the PMIC. The shown

results have been obtained for different voltages at the load, ranging from 0.5 V to 0.85 V, and for each of the four load phases; the result reveals same temperature characteristics for all phases. With the known uncertainties of thermal and electrical measurements, the characteristics of upper and lower boundaries of the on-chip losses, which are found to be almost linear with respect to temperature, can be estimated using the bottom-right and the top-left corners of the uncertainty ranges of each measurement result. In this regard, a subsequent least mean square optimization yields

$$P_{\text{th,min}} = 4.22 \frac{\text{mW}}{\text{K}} \Delta T_{\text{c}} - 4.7 \,\text{mW},$$

(8)

$$P_{\text{th,max}} = 4.33 \frac{\text{mW}}{\text{K}} \Delta T_{\text{c}} + 1.7 \,\text{mW}.$$

(9)

# C. EFFICIENCY MEASUREMENTS AND LOSS BREAKDOWN

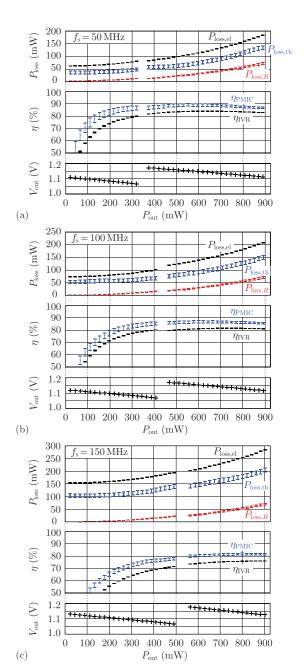

With all four phases being operated, the IVR yields the losses and efficiencies presented in Fig. 16 for a voltage conversion ratio of

$$M = \frac{V_{\text{out,k}}}{V_{\text{in,k}}} = \frac{V_{\text{out,k}}}{1.6 \,\text{V}} \approx 0.7 \tag{10}$$

and for three switching frequencies (50 MHz, 100 MHz, and 150 MHz). The total efficiency and the total losses,

$$\eta_{\text{IVR}} = \frac{P_{\text{out}}}{P_{\text{in}}}, \qquad P_{\text{loss,el}} = P_{\text{in}} - P_{\text{out}}, \qquad (11)$$

are directly determined from the input and output power levels of the IVR measured with the setup of Fig. 8,

$$P_{\rm in} = V_{\rm in,p}I_{\rm in}, \qquad P_{\rm out} = V_{\rm out,k}I_{\rm out}.$$

(12)

At the gaps observed in Fig. 16, e.g., at  $P_{\text{out}} \approx 350 \,\text{mW}$  in Fig. 16(a), the duty cycle is changed from 75 % (= 12/16) to 81 % (= 13/16) such that M remains close to 0.7.

The PMIC itself generates only a part of the total losses, which is determined from the chip temperature using (8), (9), cf. Fig. 15. Similar to Section III-B, the uncertainty of the temperature measurement is set equal to the standard deviation found for the thermal measurements, which is  $\pm 0.3$ °C,

$$P_{\text{loss,th}} \in [P_{\text{th,min}}(T_{\text{c}} - 0.3^{\circ}\text{C}), P_{\text{th,max}}(T_{\text{c}} + 0.3^{\circ}\text{C})].$$

(13)

The depicted efficiency of the PMIC itself is calculated with

$$\eta_{\text{PMIC}} = \frac{P_{\text{out}}}{P_{\text{out}} + P_{\text{loss,th}}}.$$

(14)

The on-chip losses,  $P_{\text{loss,th}}$ , can be further separated into a resistive loss component,  $P_{\text{loss,R}}$ , and an additional loss component,  $P_{\text{loss,add}}$ , using the resistor network of Fig. 10 and the previously identified resistance values, cf. Section III-A,

$$P_{\text{loss,th}} = P_{\text{loss,R}} + P_{\text{loss,add}}, \tag{15}$$

where  $P_{loss,R}$  is calculated with the dc resistances, (2) and (3), and the currents through the high-side and low-side paths for

**FIG. 16.** Losses and efficiencies for M=0.7 and two different switching frequencies: (a)  $f_s=50$  MHz, (b)  $f_s=100$  MHz, and (c)  $f_s=150$  MHz;  $P_{loss,el}$  and  $P_{loss,th}$  denote the losses determined with electrical and thermal measurements,  $P_{loss,R}$  refers to the resistive on-chip losses determined for the measured resistances of the PMIC's high-side and low-side current paths. The shown gap results due to a step of the duty cycle, which is needed to maintain  $V_{out}$  close to  $0.7 \times 1.6 V = 1.12 V$ .

all enabled converter phases, N (e.g., N = 4 applies in Fig. 16 and Fig. 17),

$$P_{\text{loss},R} = \sum_{n=1}^{N} \left( R_{\text{dc,hi},n} I_{\text{hi,rms}}^2 + R_{\text{dc,lo},n} I_{\text{lo,rms}}^2 \right); \qquad (16)$$

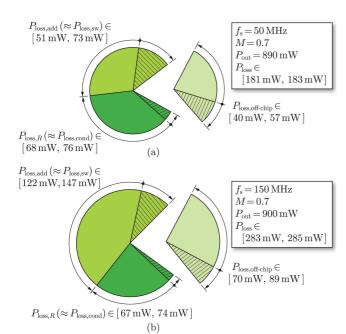

FIG. 17. Breakdown of the losses of the IVR for two different switching frequencies based on the data shown in Fig. 16, for an output power of 0.9 W, and two different switching frequencies: (a)  $f_s = 50 \, \mathrm{MHz}$ , (b)  $f_s = 150 \, \mathrm{MHz}$ ;  $P_{\mathrm{loss,ac}} = P_{\mathrm{loss,th}} - P_{\mathrm{loss,dc}}$  and  $P_{\mathrm{loss,off-chip}} = P_{\mathrm{loss,el}} - P_{\mathrm{loss,th}}$  apply. The result reveals that an increase of the switching frequency leads to increased ac losses on the chip (switching losses, ac conduction losses) and increased off-chip losses (e.g., in the inductor).

$I_{\text{hi,rms}}$  and  $I_{\text{lo,rms}}$  are determined based on inductor rms current,  $I_{L,\text{rms}}$ , and duty cycle, D,

$$I_{\text{hi,rms}} = I_{L,\text{rms}} \sqrt{D}, \quad I_{\text{lo,rms}} = I_{L,\text{rms}} \sqrt{1 - D}, \quad (17)$$

using

$$I_{L,\text{rms}}^2 = \left(\frac{I_{\text{out}}}{N}\right)^2 + \left(\frac{\Delta I_L}{2\sqrt{3}}\right)^2 \Delta I_L = \frac{V_{\text{out,k}}(1-D)}{f_{\text{s}}L}.$$

(18)

The additional loss component,  $P_{\rm loss,add}$ , is the sum of switching losses, losses due to leakage currents, increased losses due to eddy current effects inside the chip (Skin and Proximity effects), and power dissipation in the digital control circuitry. The calculation of the ac resistances of the PDN with FastHenry gives a negligible increase at the considered switching frequencies, due to the small physical dimensions, the losses due to leakage identified in Section III-A are in the range of  $10\,\mathrm{mW}$ , and the power demand of the control circuitry is approximately  $1\,\mathrm{mW}$ . For these reasons, it can be assumed that the resistive losses and the additional losses mainly resemble the conduction losses and the switching losses, respectively,

$$P_{\text{loss,cond}} \approx P_{\text{loss},R}, \qquad P_{\text{loss,sw}} \approx P_{\text{loss,add}}, \qquad (19)$$

The results reveal that the losses in the PMIC typically contribute to more than two thirds of the total losses of the IVR and that the additional loss component increases if the switching frequency is increased, which confirms (19). In

addition, also the off-chip losses,

$$P_{\text{loss,off-chip}} = P_{\text{loss,el}} - P_{\text{loss,th}}, \tag{20}$$

which contain the losses of inductor and PCB,<sup>3</sup> increase for increasing switching frequencies. At  $f_s = 50 \, \text{MHz}$ , the IVR achieves a maximum efficiency of 84.1 % at  $P_{\text{out}} = 640 \, \text{mW}$ . With respect to the active chip area of the power stages of all four phases (0.0324 mm²), this efficiency is achieved at a chip current density of 17.3 A/mm². At full load,  $P_{\text{out}} = 890 \, \text{mW}$  (corresponding to a chip current density of 24.7 A/mm²), the efficiency is 83.0 %. The maximum efficiency of the PMIC is in the range  $\eta_{\text{PMIC,max}} \in [88 \, \%, \, 90 \, \%]$  at  $f_s = 50 \, \text{MHz}$  and output power levels between 500 mW and 600 mW; the corresponding full-load efficiency of the PMIC is between 86.3 % and 87.6 %. Please note that an increased range of uncertainty results for  $\eta_{\text{PMIC,max}}$ , compared to the electrically measured efficiency, due to the increased uncertainty of the thermal measurement.

Fig. 17 depicts the ranges of conduction losses, switching losses, and off-chip losses for full-load operation with  $P_{\text{out}} = 0.9 \text{ W}$ ,  $M \approx 0.7$ , and two different switching frequencies, i.e.,  $f_s = 50 \text{ MHz}$  in Fig. 17(a) and 150 MHz in Fig. 17(b), in order to provide a more detailed view on the three loss components. The shaded areas denote the uncertainty ranges that result for the available measurement data at the considered operating points, cf. Fig. 16. For  $f_s = 50 \text{ MHz}$ , the range of the resistive losses,  $P_{\text{loss},R} \in [68 \text{ mW}, 76 \text{ mW}]$ , is similar to the range of the additional losses,  $P_{\text{loss},\text{add}} \in [51 \text{ mW}, 73 \text{ mW}]$ . In contrast, for  $f_s = 150 \text{ MHz}$ , the additional losses,  $P_{\text{loss},\text{add}} \in [122 \text{ mW}, 147 \text{ mW}]$ , are approximately twice the resistive losses ( $P_{\text{loss},R} \in 67 \text{ mW}, 74 \text{ mW}]$ ).

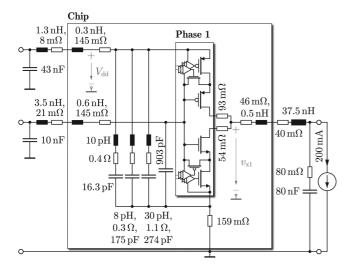

In order to clarify the origin of the additional losses, a detailed simulation has been realized for converter phase 1. This simulation includes the parasitic components of metal layers 1 to 10 and models the parasitics of PDN and PCB with the simplified network depicted in Fig. 18, cf. [28].

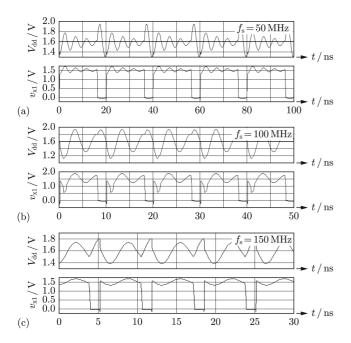

The values of the presented parasitic inductances and resistances of PDN and PCB have been computed with FastHenry. Fig. 19 depicts the waveforms of the chip-internal input voltage of the half bridge of converter phase 1,  $V_{\rm dd}$ , and the voltage at the corresponding chip-internal switching node,  $v_{\rm x1}$ , determined with the detailed simulations and for three different switching frequencies of 50 MHz, 100 MHz, and 150 MHz. According to the obtained results, the additional parasitic components lead to several unwanted effects, e.g., increased turn-on and turn-off times and oscillations superimposed on supply voltages, output voltages, and output currents. Compared to the results of simplified Cadence simulations that do not take the output current ripple and the parasitic components introduced by metal layers, PDN, bond wires, and PCB into account [27], these parasitic components are indeed

<sup>&</sup>lt;sup>3</sup>A separation of the off-chip losses into the losses of inductor and PCB would require a detailed characterization of the high-frequency inductor losses in presence of DC bias; however, this information is currently not available.

FIG. 18. Network used to model the parasitic components of PCB, bond wires, and PDN for the detailed simulation of converter phase 1. The framed block 'Phase 1' refers to a detailed simulation model that takes further parasitic components introduced by metal layers 1 to 10 into account.

FIG. 19. Waveforms of the supply voltage and the voltage at the switching node of converter phase 1,  $V_{\rm dd}$  and  $v_{\rm x1}$ , cf. Fig. 18, obtained from a detailed Cadence simulation and for different switching frequencies: (a)  $f_{\rm s}=50\,{\rm MHz}$ , (b)  $f_{\rm s}=100\,{\rm MHz}$ , (c)  $f_{\rm s}=150\,{\rm MHz}$ .

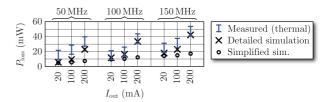

the main reason for the increased losses, in particular at high output currents, cf. Fig. 20. Remaining differences between simulated and measured losses are of relatively low value and may be reproduced by even more detailed simulations, e.g., the measured losses at  $f_{\rm s} = 50\,{\rm MHz}$  are found to be larger than expected, which may originate from additional resonance effects in PCB and PDN.

FIG. 20. Comparison of the losses of converter phase 1, determined with simplified and detailed simulations, to the measured on-chip losses. In contrast to the detailed simulation, cf. Fig. 18, the simplified simulation does not take parasitic components into account (e.g., due to metal layers, PDN, etc.) [27]. The depicted outcome reveals a substantial contribution of these parasitic components on the obtained losses; especially at high output currents, e.g.,  $I_{out} = 200 \, \text{mA}$ , these are mainly responsible for the differences between the results determined with simplified simulations and measurements.

### **IV. CONCLUSION**

This paper presents a detailed characterization of an inductor-based four-phase buck converter featuring CMOS APNC HBs, which is supported by the results of profound simulations and extensive experiments. The investigated converter uses a PMIC assembled in a 14 nm CMOS technology node and allows for operation with switching frequencies between 50 MHz and 150 MHz. Its implemented open-loop circuitry allows for configurable dead times, to optimize switching losses, and realizes output stages that are capable of being deactivated, in order to facilitate phase-shedding, i.e., operation of a reduced number of converter phases, to increase the achieved efficiency at lower output power levels. With a FEOL chip area of only 0.0081 mm<sup>2</sup> for each phase of the four-phase converter, a very compact design has been achieved, consuming only a small amount of valuable chip area.

The process of realizing an optimized chip-integrated IVR is highly challenging, mainly due to the aspects listed below.

- Limited possibility to fabricate several different chips to conduct a redesign as it is commonly done in power electronics, since chip design is bound to high costs and high time requirements.

- 2) Since it is not possible to measure voltages and currents inside the chip, the chip designer needs to fully trust the simulation results, e.g., also in case of switching losses. For the purpose of verification, specific test chips could be planned and realized to investigate a particular effect, which, however, is in contradiction to aspect 1). In this regard, Fig. 21 shows the layout of a more advanced version of the presented PMIC including a high-speed Analog-to-Digital Converter (ADC) to electrically measure the voltage at the v<sub>x3</sub> node on the chip. In the course of a comparison against simulated waveforms, this will allow for further insights with respect to similarities and differences between the simulated and the real processes, e.g., to clarify if the network assumed for the PDN needs to be further refined.

- 3) The design tools for most recent CMOS technologies are of limited extent, i.e., only a certain part of the chip can be simulated; accordingly, important interactions

FIG. 21. Layout image of a more advanced generation of the designed PMIC including ADCs for digital output voltage control and  $v_{x3}$  voltage measurement. The high impedance voltage measurement at the  $v_{x3}$  node will allow for experimental verification of its switching waveform and output power.

between different parts of a complete IVR are not identified.

In order to still gain detailed insights into the investigated IVR, the presented converter characterization consolidates the results of electrical measurements, thermal inspections of the chip surface, and simulations, which enables the separation of the total losses into on-chip and off-chip loss components as well as the allocation of important loss components inside the chip. In summary, the IVR achieves a maximum efficiency of 84.1% at  $P_{\text{out}} = 640 \,\text{mW}$  and  $f_{\text{s}} = 50 \,\text{MHz}$  and a maximum full-load efficiency of 83.0% at  $P_{\text{out}} = 890 \,\text{mW}$ with a corresponding chip current density of 24.7 A/mm<sup>2</sup>. The maximum efficiency of the PMIC itself is between 88% and 90% for  $P_{\text{out}} \in [500 \,\text{mW}, 600 \,\text{mW}]$ . The obtained results reveal that PDN and metal layers cause a considerable increase of the total losses, e.g., a simulation of the PMIC without PDN and metal layers reveals losses of only 30 mW at  $f_s = 100 \,\mathrm{MHz}$  and  $P_{\mathrm{out}} = 0.9 \,\mathrm{W}$ ; however, the corresponding measured losses of the PMIC are in the range between 140 mW and 156 mW, which can be reproduced with detailed simulations. Furthermore, the measured experimental results confirm that the combination of appropriate software tools, e.g., Cadence to conduct detailed post-layout circuit simulations and FastHenry to identify the impedances of PDN and PCB, enables a prediction of the expected losses with reasonable accuracy.

Table IV lists the performance and design values of the realized ANPC IVR and provides a comparison to previously presented results. The achieved maximum current density of the realized PMIC is amongst the highest documented values, however, the peak efficiency of 84.1% is below the maximum documented efficiency of 91.5%. According to Table IV, the efficiency of the IVR can be increased with advanced packaging technologies, e.g., flip-chip bonding the PMIC on an interposer that provides the inductors and the capacitors. In addition, this Table indicates a trend that more mature CMOS technology nodes, e.g., 22 nm, 40 nm, enable the realization of more efficient IVRs. This trend matches to the results of prior realizations with more mature CMOS nodes, where the losses

**TABLE IV** Performance and Design Values of the Investigated ANPC HB IVR in Comparison to Previously Presented Converters.

|                                          | This<br>work  | C.<br>Schaef<br>et al.<br>[11] | H. K.<br>Krish-<br>namurty<br>et al.<br>[8] | H. K.<br>Krish-<br>namurty<br>et al.<br>[9] | E. A.<br>Burton<br>et al.<br>[10] | F. Neveu<br>et al.<br>[13] | N. Stur-<br>cken et<br>al. [15] |

|------------------------------------------|---------------|--------------------------------|---------------------------------------------|---------------------------------------------|-----------------------------------|----------------------------|---------------------------------|

| Techn. node<br>PMIC (nm)                 | 14            | 14                             | 14                                          | 14                                          | 22                                | 40                         | 45                              |

| Peak efficiency (%)                      | 84.1          | 88                             | 84 (for on-die induct.)                     | 80                                          | 90                                | 91.5                       | 75                              |

| Max. curr. density (A/mm <sup>2</sup> )* | 24.7          | 10.7                           | ı                                           | ı                                           | 31                                | 6.3                        | 22.7                            |

| Input voltage (V)                        | 1.6           | 1.6                            | 1.5                                         | 1.2                                         | 1.7                               | 3.3                        | 1.8                             |

| Conv. ratio M at peak efficiency         | 0.7           | 0.75                           | 0.77                                        | 0.77                                        | 0.62                              | 0.73                       | 0.67                            |

| HB topol-<br>ogy                         | ANPC          | stacked<br>transist.           | stacked<br>transist.                        | stacked<br>transist.                        | stacked<br>transist.              | stacked<br>transist.       | single<br>transist.             |

| Switching freq. (MHz)                    | 50            | 70                             | 100                                         | 90                                          | 140                               | 100                        | up to 200                       |

| Inductor value L (nH)                    | 36            | 2.5                            | 1.5 or<br>22**                              | 4.8                                         | _                                 | 60                         | 12.5                            |

| Inductor<br>technology                   | discrete      | on-<br>package                 | on-die<br>or ext.                           | on-die                                      | on-<br>package                    | discrete                   | silicon interp.                 |

| Inductor packaging                       | bond-<br>wire | flip-<br>chip                  | <ul><li>/ on-<br/>probe</li></ul>           | 1                                           | flip-<br>chip                     | flip-<br>chip              | flip-<br>chip                   |

| Number of phases                         | 4             | 1                              | 2                                           | 2                                           | 16                                | 1                          | 8                               |

<sup>\*</sup> Defined as the maximum output current of the IVR divided by the area of the enabled power switches, gate-drivers, and level shifters. This value was calculated using information found in the corresponding publications.

in PDN and metal layers have been relatively low, and the findings of this paper, which reveal substantial losses, there, due to the small values of maximum widths and thicknesses defined by the design rules. Therefore, even higher losses in the PDN and the metal layers would be expected in case of higher-integrated, e.g., 7 nm, CMOS nodes [30]. Accordingly, future research will also focus on alternative solutions that do not require a direct integration of the PMIC on the CPU die, e.g., 3D realizations using chiplets [31], which extends the current design space with respect to system complexity, efficiency, and costs.

### **ACKNOWLEDGMENT**

The authors would like to thank Arvind Sridhar, Dario Kneubühler, Thomas Toifl, Danny Luu, Lukas Kull, Alessandro Cevrero, and Ilter Ozkawa for contributions on the chip design and package implementations. Part of this work was carried out within the European CarrICool Project under the Seventh Framework Program for Research and Technological Development (FP7-ICT-619488).

### **REFERENCES**

C. Berry et al., "Ibm z15: A 12-core 5.2GHz microprocessor," in Proc. IEEE Int. Solid-State Circuits Conf., San Jose, California, USA, Feb. 2020, pp. 54–56.

<sup>\*\*</sup> Two realizations are presented, with on-die and external inductor.

- [2] S. M. Tam et al., "SkyLake-SP: A 14nm 28-core Xeon processor," in Proc. IEEE Int. Solid-State Circuits Conf., San Francisco, CA, USA, Feb. 2018, pp. 34–36.

- [3] Y. F. Shen, "Power integrity challenges of re-designing a mobile SoC with fully integrated voltage regulator to iot applications," in *Proc. IEEE Workshop Signal and Power Integrity*, Brest, France, May 2018, pp. 1–4.

- [4] U. Lopez-Novoa, "Exploring performance and energy consumption differences between recent intel processors," in Proc. IEEE Smart-World, Ubiquitous Intell. & Comput., Adv. & Trusted Comput., Scalable Comput. & Commun., Cloud & Big Data Comput., Internet People and Smart City Innovation, Leicester, United Kingdom, Aug. 2019, pp. 263–267.

- [5] A. Varma et al., "Power management in the intel xeon e5 v3," in Proc. IEEE Int. Symp. Low Power Electron. Des., Rome, Italy, Sep. 2015, pp. 371–376.

- [6] Package Prepares for AI Comput., 2018. [Online]. Available: http://www.vicorpower.com

- [7] H. K. Krishnamurthy et al., "A 500 MHz, 68% efficient, fully on-die digitally controlled buck voltage regulator on 22 nm tri-gate CMOS," in Proc. IEEE Symp. VLSI Circuits, Hsinchu, Taiwan, Apr. 2014, pp. 167–168.

- [8] H. K. Krishnamurthy et al., "A digitally controlled fully integrated voltage regulator with on-die solenoid inductor with planar magnetic core in 14nm tri-gate CMOS," in Proc. IEEE Int. Solid-State Circuits Conf., San Francisco, CA, USA, Feb. 2017, pp. 336–338.

- [9] H. K. Krishnamurthy et al., "A digitally controlled fully integrated voltage regulator with 3-D-TSV-based on-die solenoid inductor with a planar magnetic core for 3-D-stacked die applications in 14-nm tri-gate CMOS," IEEE J. Solid-State Circuits, vol. 53, no. 4, pp. 1038–1048, Apr. 2018.

- [10] E. A. Burton et al., "FIVR fully integrated voltage regulators on 4th generation Intel Core<sup>TM</sup> SoCs," in Proc. IEEE Appl. Power Electron. Conf., Houston, TX, USA, Mar. 2014, pp. 432–439.

- [11] C. Schaef et al., "A fully integrated voltage regulator in 14nm CMOS with package-embedded air-core inductor featuring self-trimmed, digitally controlled variable on-time discontinuous conduction mode operation," in Proc. IEEE Int. Solid-State Circuits Conf., San Francisco, CA, USA, Feb. 2019, pp. 154–156.

- [12] W. J. Lambert, M. J. Hill, K. Radhakrishnan, L. Wojewoda, and A. E. Augustine, "Package inductors for intel fully integrated voltage regulators," *IEEE Trans. Compon., Packag. Manuf. Technol.*, vol. 6, no. 1, pp. 3–11, Jan. 2016.

- [13] F. Neveu, B. Allard, C. Martin, and P. Bevilacqua, "A 100 MHz 91.5% peak efficiency integrated buck converter with a three-MOSFET cascode bridge," *IEEE Trans. Power Electron.*, vol. 31, no. 6, pp. 3985–3988, Jun. 2016.

- [14] T. Brunschwiler et al., "Towards cube-sized compute nodes: Advanced packaging concepts enabling extreme 3D integration," in Proc. IEEE Int. Electron. Devices Meet., San Francisco, CA, USA, Dec. 2017, pp. 3.7.1–3.7.4.

- [15] N. Sturcken et al., "A 2.5D integrated voltage regulator using coupled-magnetic-core inductors on silicon interposer," *IEEE J. Solid-State Circuits*, vol. 48, no. 1, pp. 244–254, Jan. 2013.

[16] H. J. Bergveld et al., "A 65-nm-cmos 100-MHz 87%-efficient dc-

- [16] H. J. Bergveld et al., "A 65-nm-cmos 100-MHz 87%-efficient dede down converter based on dual-die system-in-package integration," in Proc. IEEE Energy Convers. Congr. and Expo., San Jose, USA, Sep. 2009, pp. 3698–3705.

- [17] P. A. M. Bezerra et al., "Modeling and multi-objective optimization of 2.5D inductor-based fully integrated voltage regulators for microprocessor applications," Proc. Brazilian Power Electron. Conf. Southern Power Electron. Conf., pp. 1–6, Nov. 2015.

- [18] S. A. Chickamenahalli, H. Braunisch, S. Srinivasan, J. He, U. Shrivastava, and B. Sankman, "RF packaging and passives: Design, fabrication, measurement, and validation of package embedded inductors," *IEEE Trans. Adv. Packag.*, vol. 28, no. 4, pp. 665–673, Nov. 2005.

- [19] S. Müller, M. L. F. Bellaredj, A. K. Davis, P. A. Kohl, and M. Swaminathan, "Design exploration of package-embedded inductors for high-efficiency integrated voltage regulators," *IEEE Trans. Compon.*, *Packag., Manuf. Technol.*, vol. 9, no. 1, pp. 96–106, Jan. 2019.

- [20] X. Zhang et al., "Heterogeneous 2.5D integration on through silicon interposer," Appl. Physics Rev., vol. 2, no. 2, Jun. 2015.

- [21] T. Song, N. Sturcken, K. Athikulwongse, K. Shepard, and S. K. Lim, "Thermal analysis and optimization of 2.5-D integrated voltage regulator," in *Proc. IEEE Conf. Elect. Perform. Electron. Packag. and Syst.*, Tempe, AZ, USA, Oct. 2012, pp. 25–28.

- [22] S. Mueller et al., "Modeling and design of system-in-package integrated voltage regulator with thermal effects," in Proc. IEEE 25th Conf. Elect. Perform. Of Electron. Packag. And Syst. (EPEPS), San Diego, CA, USA, Oct. 2016, pp. 65–68.

- [23] E. Kursun and C.-Y. Cher, "Variation-aware thermal characterization and management of multi-core architectures," in *Proc. IEEE Int. Conf. Comput. Des.*, Lake Tahoe, CA, USA, Oct. 2008, pp. 280–285.

- [24] A. N. Nowroz, R. Cochran, and S. Reda, "Thermal monitoring of real processors: Techniques for sensor allocation and full characterization," in *Proc. 47th Des. Autom. Conf.*, Anaheim, CA, USA, Jul. 2010, pp. 56–61.

- [25] N. A. Sturcken, "Integrated voltage regulators with thin-film magnetic power inductors," Ph.D. dissertation, Columbia Univ., 2013.

- [26] T. M. Andersen, "On-chip switched capacitor voltage regulators for granular microprocessor power delivery," Ph.D. dissertation, Swiss Federal Inst. Technol. Zurich, 2015.

- [27] P. A. M. Bezerra, R. K. Aljameh, F. Krismer, J. W. Kolar, A. Sridhar, T. Brunschwiler, and T. Toifl, "Analysis and comparative evaluation of stacked transistor half-bridge topologies implemented with 14 nm bulk CMOS technology," in *Proc. IEEE Workshop Control and Model. for Power Electronics*, Stanford, CA, USA, Jul. 2017.

- [28] Q. K. Zhu, Power Distribution Netw. Des. For VLSI. Hoboken, New Jersey: Wiley, 2004.

- [29] R. Schmidt and U. Scheuermann, "Using the chip as a temperature sensor - the influence of steep lateral temperature gradients on the Vce(T)-measurement," in *Proc. Eur. Conf. Power Electron. Appl.*, San Jose, USA, Sep. 2009.

- [30] A. A. Vyas, C. Zhou, and C. Y. Yang, "On-chip interconnect conductor materials for end-of-roadmap technology nodes," *IEEE Trans. Nan-otechnol.*, vol. 17, no. 1, pp. 4–10, 2018.

- [31] P. Vivet et al., "A 220 GOPS 96-core processor with 6 chiplets 3d-stacked on an active interposer offering 0.6 ns/mm latency, 3 Tb/s/mm<sup>2</sup> inter-chiplet interconnects and 156 mW/mm<sup>2</sup> @ 82%-peak-efficiency dc-dc converters," in Proc. IEEE Int. Solid-State Circuits Conf., San Francisco, California, USA, 2020, pp. 46–48.