Received 15 March 2024; revised 15 April 2024 and 23 April 2024; accepted 24 April 2024. Date of publication 1 May 2024; date of current version 16 May 2024. The review of this article was arranged by Associate Editor Liangzong He.

Digital Object Identifier 10.1109/OJPEL.2024.3394529

# Analytical Benchmarking of Direct Hybrid Switched-Capacitor DC-DC Converters

GAËL PILLONNET<sup>1</sup> (Senior Member, IEEE) AND PATRICK P. MERCIER<sup>1</sup> (Senior Member, IEEE)

<sup>1</sup>Univ. Grenoble Alpes, CEA, Leti, F-38000 Grenoble, France <sup>2</sup>Department of Electrical and Computer Engineering, University of California San Diego, San Diego, CA 92093 USA

CORRESPONDING AUTHOR: GAËL PILLONNET (e-mail: gael.pillonnet@cea.fr)

**ABSTRACT** Hybrid switched-capacitor converters (HSCCs) have gained attention due to their promising efficiency and power density compared to traditional inductor- or capacitor-based converters. However, with the recent development of various HSCC topologies, it has become increasingly challenging to choose the most suitable one for a particular application. To address this challenge, this paper proposes a benchmarking framework that enables direct comparison of direct HSCC topologies based on various performance metrics such as passives volume and bandwidth. The proposed approach, which compares all topologies at the same efficiency and output voltage ripple, provides guidelines for topology selection and optimization, ultimately contributing to wider industrial adoption and exploration of new topologies. Downloadable open-access code is also provided to recreate presented results and expand to other topologies not discussed in the paper.

**INDEX TERMS** DC-DC converter, hybrid converter topology, switching converters.

# I. INTRODUCTION

Many non-isolated step-down DC-DC converter applications, such as microprocessor power delivery, USB charging, and automotive systems, require large voltage conversion ratios (VCRs). In such cases, the passive components, typically capacitors and inductors, often dominate the size of the converter. To reduce the volume of these passive components, recent efforts have focused on increasing the switching frequency [1], using resonant topologies [2], introducing inductorless piezoelectric structures [3], [4], [5], using alternative flying components [6], [7], and high density Silicon capacitor components [8], [9]. Among all of these solutions, hybrid switched-capacitor converters (HSCCs) are considered amongst the most promising [10], [11] and have received significant attention over the last decade. Initially, these efforts were driven by a few research groups [12], [13], [14].

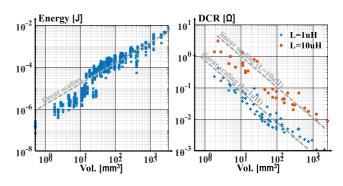

The root reasons for HSCC supremacy are mostly due to technological limitations on: i) passive components, specifically the relative low inductor energy density compared to capacitors [8], [15], and ii) on active devices, namely the negative impact of the blocking voltage on switch performance [16], [17], [18], [19]. HSCCs utilize a switched-capacitor network to block a portion of the input voltage across capacitors, and then an inductor-based stage completes

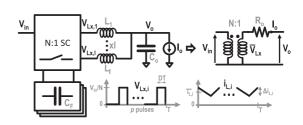

**FIGURE 1.** Overview of the general scheme employed by hybrid switched-capacitor converters (HSCCs).

the conversion, as illustrated in Fig. 1. Since HSCCs do not usually suffer from inherent charge-sharing losses that appear in pure switched-capacitor converters (SCCs) due to inductors soft-charging the flying capacitor networks, performance can be significantly higher than the baseline SCC [20]. For example when operating in a soft-charged mode, the ripple across the flying capacitors can be significantly increased without experiencing the impedance issues typically associated with the slow-switching limit (SSL) observed in pure SCC [19]. Additionally, HSCCs offer a lossless voltage control capability not possible in baseline SCCs [17].

The topological zoology of HSCCs is mainly derived from SCCs, influenced by formalization in the 2000s [19]:

|                       | Unit              | TPEL'22 | TPEL'23   | TPS54A20   | ISSCC'19  | TCAS'22        | JSSC'20   | CICC'20  | JSSCC'22     | ISSCC'17    | JSSC'21       |

|-----------------------|-------------------|---------|-----------|------------|-----------|----------------|-----------|----------|--------------|-------------|---------------|

|                       |                   | [47]    | [48]      | TI Product | [49]      | [50]           | [23]      | [51]     | [52]         | [53]        | [54]          |

| Topology name         | -                 | 3L buck | 3L buck   | DSD        | 4L buck   | Dual-branch SP | SMML      | 5L buck  | Cascaded SC  | 4:1 Dickson | Tri-State DSD |

| Nominal voltage ratio | -                 | 2       | 2         | 2          | 3         | 3              | 3         | 4        | 4            | 4           | 4             |

| # phase               | -                 | 1       | 1         | 2          | 1         | 1              | 1         | 1        | 1            | 1           | 2             |

| Input voltage         | V                 | 3.5-4.5 | 2.7-4.5   | 12         | 3.7-5     | 3.6            | 3-5.0     | 4-5.5    | 4-6.0        | 3-4.5       | 12-24.0       |

| Output voltage        | V                 | 1-3.3   | 0.6-1.3   | 1.2        | 0.8-1.8   | 0.55-1         | 0.3-1.2   | 0.4-1.2  | 0.4-1.2      | 0.3-1       | 1             |

| Peak output current   | А                 | 0.9     | 1.6       | 10         | 10        | 0.5            | 0.43      | 1.4      | 1            | 1.5         | 3             |

| Technology            | nm                | 55      | 65        |            | 22        | 3              | 180       | 180      | 180          | 65          | 180           |

| Die area              | $\rm mm^2$        | 0.8     | 2.07      |            | 6.9       | 65             | 5.5       |          | 7.8          | 4.1         | 6.3           |

| Area (die, passive)   | $\rm mm^2$        |         | 13.3      |            | 75.6      | 1.01           | 7         |          | 11           |             |               |

| Inductor              | μΗ                | 0.33    | 0.47      | 2x0.22     | 10        | 0.1            | 0.22      | 0.24     | 0.24         | 0.18        | 2x0.56        |

| Flying capacitor      | μF                | 1x2.2   | 1x1       | 1x2.2      | 2x13.2    | 4x0.47         | 4x1       | 3x4.7    | 2x4.7 + 1x10 | 3x22        | 2x1           |

| Output capacitor      | μF                | 2.2     | 10        | 2x4.7      | 18        | 0.94           | 1         | 10       | 14.4         | 22          | 10            |

| Switching frequency   | MHz               | 3-3.5   | 2.5       |            | 4.4-11.8  | 5              | 4         |          | 1.4-1.6      | 1           | 0.2-2         |

| Max power density     | W/mm <sup>2</sup> |         | 0.15      |            | 0.95      |                | 0.52      | 0.11     | 0.1          |             |               |

| Peak power density    | W/mm <sup>3</sup> |         | 0.061@3.5 |            | 0.198     |                | 0.52@4.2  |          | 0.18@4.5     | 0.24@4.4    | 0.06@12       |

| Peak Efficiency       | %@- [CR]          | 95@1.3  | 88.6@3.5  |            | 93.8@2.77 | 82@4           | 89.5@4.2  | 92.4@4.6 | 96.9@4.2     | 94.2@4.4    | 91.2@12       |

| Max VCR               | -@% [Eff.]        |         |           | 10@85      | 6.25@85.8 |                | 16.7@74.0 | 8.8@86.5 | 12.5@85.5    |             |               |

TABLE 1. Table of Comparison of Previously Published Non-Resonant Hybrid Converters

Dickson [20], [21], series-parallel [13], Fibonacci [22], ladder [23], multi-level [24] and others [25], [26]. The concept of HSCCs can be expanded to multiple inductors [27], [28] placed at the input [29], [30], output [25], or in the middle [31] of capacitor networks. Moreover, certain proposed topologies such as those in [32], [33], [34], [35], [36], [37] incorporate the concept of dual-current paths, where simultaneous soft-charging and hard-charging operations are implemented primarily to minimize the current flowing into the inductor. Finally, HSCCs topologies can be combined with other well-known topologies such as dual active bridge to create high-performance DC-DC converters [38].

There are two main HSCC subsets divided by the energy transfer mode: resonant [2] or non-resonant [13]. Although resonant operation enables zero current switching, it is worth noting that operating a HSCC above resonance has the advantage of significantly reducing the circulating current. This reduction leads to a decrease in the RMS current through the switches, effectively mitigating switching losses and resulting in improved efficiency [39], [40]. Additionally, non-resonant operation is preferred for its advantages in regulating the output voltage and in less susceptibility to component and timing mismatch [41], [42], [43].

To further diminish the size of the inductor, prior studies have suggested the utilization of coupled inductors, which yield notable enhancements in transient response compared to uncoupled counterparts [44]. The advantages of coupling multiple inductors become particularly pronounced with an increase in the number of phases. However, designing a multiphase coupled inductor configuration that achieves simultaneously small current ripples, rapid transient response, and a compact inductor size poses significant challenges [45]. Due to the distinct inductor sizing procedure [46], our paper concentrates solely on structures utilizing non-coupled inductors.

This paper focuses only on non-resonant "direct" (as defined in [40]) HSCC topologies where the inductors are located at the output. In this configuration, the inductors act as current sources to soft-charge the capacitors located in the first conversion stage, which helps to reduce the capacitors' values compared to their baseline SCC counterparts. Thanks to the first stage introducing a natural N:1 voltage conversion ratio, the second stage can be seen as a traditional buck converter powered by a reduced intermediate power supply,  $V_{in}/N$ , to achive the desired VCR, named M here. Moreover, by interleaving the pulse train, it can have a higher rate than the switching frequency [24], reducing further the inductor voltage-second balance, which is an attractive benefit.

Choosing the right HSCC topology for a given application is crucial, as the topological choice distributes the constraints over the three main converter components (switches, capacitors, and inductors). Table 1 provides experimental data obtained by different research groups who have experimented with non-resonant HSCC using integrated Silicon power stages and inductors at the output with full soft-charging operations [23], [47], [48], [49], [50], [51], [52], [53], [54]. The data suggests that for most cases with MHz switching frequency, the inductor and flying capacitor are in the 100 s of nH and  $\mu$ F range, respectively. However, due to the different input voltage levels and IC choices used in various Silicon technologies, it is difficult to isolate the benefits of the HSCC topology itself, making inference of which topology is best suited for which application difficult. This is the main motivation for this work.

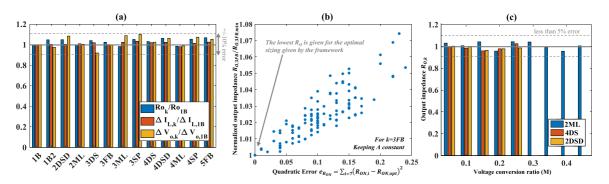

Previous studies have introduced various methods to predict the achievable output resistance [18], [39], [55], largely relying on models developed for SCCs [19], [56]. However, the proposed approach sets itself apart by establishing a direct link between the inherent performance of both passive and active components, leveraging parameters such as switch area and switching frequency across diverse topologies. This methodology allows for a comprehensive comparison of all topologies while ensuring consistent conduction and switching losses, including those from inductor. Additionally, it guarantees uniform inductor current and output voltage ripples, enhancing the fairness and accuracy of the evaluation process.

Our previous work [57] proposed a normalized benchmarking framework for fully soft-charging non-resonant direct HSCC topologies, comparing various topologies to a baseline 2-level buck converter operating at the same power efficiency and output voltage ripple. This paper expands on [57] by presenting a comprehensive analytical framework with tractable equations and offering a broad overview of HSCC performance in various expanded design contexts, including regulated HSCCs where voltage regulation is achieved through duty cycle adjustment. The comparison is dimensionless, which ensures that any conclusions drawn are broadly applicable to various input/output voltage and current levels, as long as current and voltage ripples remain negligible in the calculation of RMS values and not impact the switch voltage rating. Recently, [43] introduces a comprehensive analysis that considers the impact of voltage ripple and introduces metrics to assess switch stress and passive volume for hybrid converters both at and above resonance.

The paper is structured as follows: we begin by presenting the modeling framework, including the assumptions made and the method for determining converter parameters from a small set of topological parameters. Next, we compare our benchmark to previous works. Then, we provide analytical expressions for converter parameters, such as silicon area, switching frequency, and total volume using the aforementioned method. Based on this framework, we offer recommendations for selecting the best topology for various design contexts, such as for a given voltage conversion ratio, and discuss the effect of switch and inductor scaling laws.

### II. MODELING FRAMEWORK

#### A. INITIAL ASSUMPTIONS AND NOTATIONS

The proposed approach has certain limitations and assumptions. It is only valid in continuous mode, in periodic steadystate operation, without core saturation or hysteresis effects, and assumes equally-valued inductors, L, at the outputs for perfect output current sharing between phases [58]. The energy transfer through flying capacitance is considered to be in a fully soft-charging mode, with no charge-sharing loss in any state, and the frequency operation, F, is far above the self-resonance formed by L,  $C_F$  as in [14], [59], [60]. The resonant-based HSCC is not addressed in this paper due to its distinct loss mechanism, which significantly differs from non-resonant approaches [39], [40].

The methodology also assumes that the inductor series resistance (DCR) remains relatively constant within the studied switching frequency range, which is less than ten times in the following. Moreover, for the sake of simplicity, all flying capacitors are assigned an identical value, denoted as  $C_F$ .

The framework remains applicable under the condition of small voltage ripple across capacitors, as it does not consider the impact of voltage ripple on the voltage stress experienced by the switches, as also presumed in [19], [55], [61]. We have also assumed that the RMS current conveyed through all switches is solely due to the DC current. In other words, the contribution of current ripple in the switches conduction loss is neglected in this analysis. However, the effect of current

ripple is included to calculate the conduction loss in the inductor. It's important to note that all these assumptions are uniformly applied to all topologies, potentially mitigating the impact of these assumptions in the later normalized benchmark results.

To enhance clarity, further assumptions, including passive component sizing, are introduced later in the paper. A summary of assumptions introduced later in the paper can be found in Appendix A.

Practical converter designs involve several considerations beyond just sizing of power transistors and passive components. These include factors such as VCR (DC gain) range, number of switches, gate driving, level shifters, capacitor charge balancing [33], [50], [62], voltage stress during the starting phase [52], feedback control [47], [48], [63], PCB routing, input capacitor [64] and EMI. While these considerations may make the low *N* topology an appealing choice, a final decision must take into account all relevant factors with appropriate weighting depending on the application.

To distinguish between dimensionless (x) and dimensional ( $\tilde{x}$ ) values, the paper uses tilde notation ( $\tilde{x}$ ). We also define three main variable types: i) the "input" variables defining the design context (e.g., desired VCR, switch performance), ii) the "topological" variables describing the HSCC, and iii) the "design" variables resulting of the framework (e.g., switching frequency, inductor volumes). Regarding the notation for voltage and volume, this paper names them V and U, respectively.

## B. METHOD FOR SIZING A CONVERTER WITH CONSTANT LOSS AND CONSTANT RIPPLES

The core of the proposed framework involves comparing a HSCC referenced by a topology index, k, to a 2-level singlephase buck converter (1B) at the same power dissipation level and at same inductor current and output voltage ripples. The losses considered are the switch conduction loss,  $P_{cond}$ , the gate driving (i.e., switching) loss,  $P_{drive}$ , the inductor loss,  $P_{ind}$ , from the inductor's DCR, and the loss induced by the current ripple,  $\Delta I_L$ . The total HSCC loss is expressed as:

$$\widetilde{P_{loss,k}} = \widetilde{P_{cond,k}} + \widetilde{P_{drive,k}} + \widetilde{P_{ind,k}}$$

$$= \widetilde{R_{o,k}}\widetilde{I_o^2} + \widetilde{E_{dr,k}}\widetilde{F_k} + \sum_{i}^{\#ind} R_L \frac{\widetilde{I_o^2}}{l_k^2} \left(1 + \frac{\varepsilon}{12}\right) \quad (1)$$

where k is the topology index,  $\widetilde{R}_o$  is the equivalent output impedance,  $\widetilde{I}_o$  is the output current,  $\widetilde{F}_k$  is the switching frequency,  $\widetilde{E}_{dr,k}$  is the total energy consumed by all switches during one cycle to commute,  $\varepsilon$  is the relative inductor current ripple (with respect to  $\widetilde{I}_L$ ),  $l_k$  is the number of inductors, and  $\widetilde{R}_L$  is the series resistance of each inductor (DCR).

For a given set of input parameters (voltage conversion ratio, switch scaling law, etc.), the method involves three steps:

Finding the total switch area, Ã<sub>k</sub>, to achieve the same output impedance as the basedline 1B buck converter (R<sub>o,k</sub> = R<sub>o,1B</sub>), meaning P<sub>cond,k</sub> = P<sub>cond,1B</sub>;

- 2) From  $\widetilde{A}_k$ , deducing the total energy,  $\widetilde{E}_{dr}$ , to commute during one cycle and adjusting the switching frequency  $\widetilde{F}_k$ , to obtain  $\widetilde{P_{drive,k}} = \widetilde{P_{drive,1B}}$ ;

- 3) Adapting the inductor value,  $L_k$ , to equalize inductor ripple, and thus losses:  $\widetilde{P_{ind,k}} = \widetilde{P_{ind,1B}}$ .

The output capacitor,  $C_{o,k}$ , is then adjusted such that the HSCC and the 1B buck converter produce the same amount of output voltage ripple. By ensuring that the inductor current and output voltage ripples are the same for both topologies, the comparison becomes more meaningful, since any differences in performance can be attributed to the topology itself.

The value of the flying capacitors,  $\widetilde{C_{F,k}}$ , is then chosen such that the operating frequency of the HSCC is significantly above the resonance frequencies formed by  $\{\widetilde{L_k}, \widetilde{C_{F,k}}\}$  and  $\{\widetilde{L_k}, \widetilde{C_{o,k}}\}$  tanks compared to the chosen switching frequency,  $\widetilde{F_k}$ . This ensures that the flying capacitors operate in a fully soft-charging mode and ensures that each current is a constant value during each state. Hence, the RMS value is close to the DC value, restricting the framework to small-signal analysis, as in most existing benchmarks [19], [55].

To ensure consistent conduction loss in the inductor  $(P_{\text{ind},k})$  across various topologies, the DC resistance (DCR) of each inductor is chosen to be proportional to the number of inductors, as indicated by the topological parameter *l* defined later in Section II-E. For instance, single-inductor topologies like the baseline or Dickson share the same DCR for their inductor. In the case of topologies with two inductors, such as the double step-down (DSD) [12], the DCR is doubled compared to single-inductor topologies.

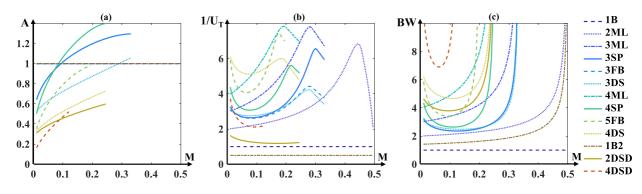

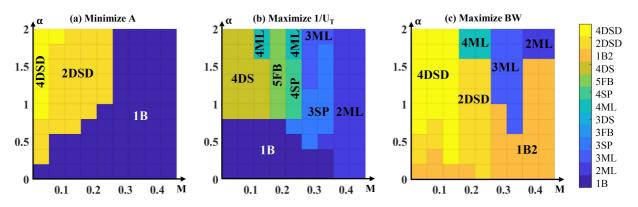

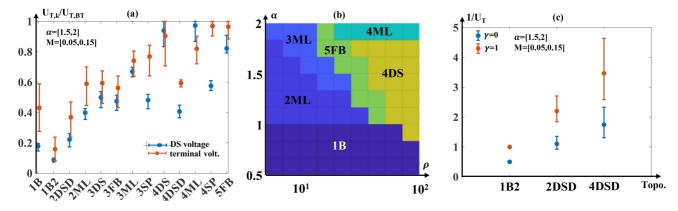

The method provides dimensionless design parameters, which are relative to those of the 1B converter. The output parameters include the switch area  $A_k$ , the switching frequency  $F_k$ , and passive component values  $(L_k, C_{ok}, \text{ and } C_{Fk})$  relative to those of the 1B converter (e.g.,  $\tilde{F}_k = F_k x \tilde{F}_{1B}$ ).

From these parameters, the method can determine the relative gain in switch area, passive component size (inductor and capacitor) and maximal cutoff frequency of the output LC filter *BW* compared to the 1B converter. This allows for a more direct comparison between the HSCC and 1B converter in terms of power density at the same power efficiency and inductor current and output voltage ripples.

## C. COMPARISON TO PREVIOUS BENCHMARKS

The proposed methodology stands apart from prior studies by fully normalizing the design to a reference case and optimizing the triptych parameters  $A_k$ ,  $F_k$ ,  $L_k$  to achieve consistent overall losses, as shown in (1). Additionally, the optimization process encompasses adjustments to  $C_{o,k}$ ,  $C_{F,k}$  to ensure equivalent output ripple and maintain non-resonant operation. In contrast to [19], [65], our approach involves the comprehensive optimization of switch sizing. Each switch is tailored to minimize conduction loss at the targeted voltage conversion ratio, M. Furthermore, M does not necessarily correspond to the inherent Voltage Conversion Ratio (VCR) of the SCC network preceding the inductor (referred to as 1/N). Consequently, our analysis focuses on comparing HSCCs with regulation capability. Our method distinguishes itself from previous approaches by establishing a connection between the intrinsic performance of passive and active components through switch area and switching frequency across different topologies. This facilitates a comparison of all topologies while maintaining consistent conduction and switching losses, including inductor losses. Moreover, it ensures uniform inductor current and output voltage ripples for a fair evaluation.

#### **D. SELECTED TOPOLOGIES**

In this paper, we have constrained our analysis to three flying capacitors to maintain a reasonable number of passive devices. Most of the referenced papers for 12-to-1 V in the IC context use three or fewer flying capacitors. If a higher VCR is targeted, the framework and the open-access code [66] can be easily extended to accommodate a greater number of flying capacitors. As mentioned earlier when discussing assumptions, we only consider HSCC topologies where the inductors are placed at the output, and exclude topologies from [29], [30], [31], as they require more nuanced analysis. Furthermore, we only consider HSCCs that exhibit fully soft-charging operation, which limits the selection of common SCC topologies, as not all of them are compatible with soft-charging. This excludes some topologies from our benchmarking scope, such as those in [32], [33], [34], [35], [36], [37]. While coupled-inductor topologies demonstrate noteworthy enhancements in certain use cases, we have excluded them from our comparison due to differences in the inductor sizing procedure.

For a single inductor at the output, previous work in [65] has already formally revealed configurations that satisfy this requirement without infinite flying capacitor values, namely the series-parallel (SP) and Fibonacci (FB) topologies. Direct deployment of the Dickson SCC topology in a HSCC does not provide soft-charging operation, but it can be modified to be compatible by introducing a splitting state [60], which we refer to as DS. The ladder [23] and doubler topologies are not included in our benchmark, as they are generally not amenable to soft-charging without major modifications. Based on our modeling assumptions, we compare the SP, FB, and DS topologies in the following. Additionally, flying capacitor multilevel converters (ML) are also added to the benchmark as they satisfy the soft-charging constraint [41], [49], [51], [67], [68]. These topologies align with the direct-conversion distinction proposed in [40].

For two inductors at the output, we have considered the well-known two-phase 2-L buck (1B2), the double step-down (2DSD) [12], and the tri-state DSD (2DSD3) [54] topologies, all of which offer full soft-charging operation.

The *N* prefix is used in this paper to indicate the *N*:1 natural SCC voltage conversion ratio for the topology name. The number of flying capacitors is *N*-1, except for 5FB (which follows the Fibonacci series) and 2DSD3. For instance, 3DS refers to the Dickson topology with unregulated 3:1

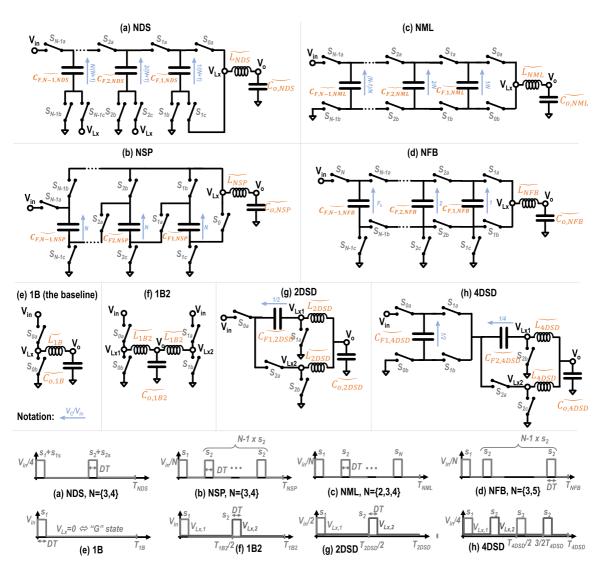

**FIGURE 2.** Selected topologies: Schematic diagrams and V<sub>Lx</sub> waveforms, (a) Dickson, (b) series-parallel, (c) multi-level, (d) Fibanocci, (e) buck (the baseline), (f) 2-phase buck, (g) double-step-down, and (h) tri-state double-step-down.

| Topology | Terminologies found in literature | References                   |

|----------|-----------------------------------|------------------------------|

| 1B       | 1-phase 2-level Buck              | [69]                         |

| 1B2      | 2-phase 2-level Buck              | [69]                         |

| NML      | N:1 Flying-Capacitor Multi-Level  | [24], [47], [49], [51]       |

| NSP      | N:1 Series-Parallel               | [13], [25], [65]             |

| NFB      | N:1 Fibonacci Hybrid Converters   | [22], [65]                   |

| NDS      | N:1 Hybrid Dickson Switched-Cap.  | [20], [21], [25], [60], [65] |

| 2DSD     | Double Step Down                  | [12], [70], [71]             |

| 4DSD     | Tri-State Double Step Down        | [54]                         |

TABLE 2. Terminology for Topologies in This Article

conversion capability. Table 2 aims to provide clarity on the naming conventions.

As we investigate the HSCC for achieving a targeted voltage ratio M that differs from the natural N:1 given by the flying capacitors network, we introduce the ground state (G), where the inductor is demagnetized. The duration of the G state is modulated according to the targeted VCR. Fig. 2 shows the schematics of all the screened topologies in this paper. Table 3 describes the states by giving the normalized current flowing into each switch in each state  $(I_{sw,i}/I_o)$ .

# E. TOPOLOGY DESCRIPTION

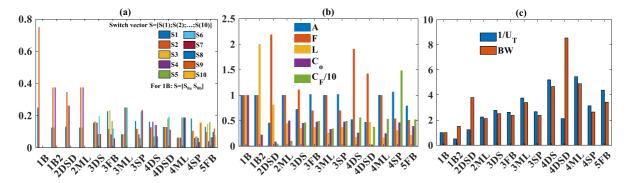

First, topologically defining vectors for each HSCC structure under consideration need to be derived through analysis and deduction. The framework utilizes only nine "topological" parameters (C, S,  $V_s$ ,  $V_c$ , m, d, l, p, s) obtained from circuit inspection as inputs:

- The current multiplication vector, *C*, represents the RMS current flowing through each switch during the entire switching period *T* and is referenced to *I*<sub>0</sub>. This concept is akin to the charge multiplier utilized in [19].

- The switching rate activity is given by the vector *S*, where each entry in the vector represents the number of times each switch in a given topology commutes during time *T*.

#### TABLE 3. Normalized Current Flowing in Each Switch for All States in 13 Selected Topologies

| topo  |   | 1B  |   | 2M | ι    |   | 3 | ML |      |   |   | 4M | 4L |      |   | 35  | P    |   | 4S  | Р    |   | 3FI | 3    |     | 5FB |      |      |      | 3DS  |      |      |     |      | 4DS |      |      |   | 1B | 2    |     | 2DSE | )    |     | 4E  | DSD |      |

|-------|---|-----|---|----|------|---|---|----|------|---|---|----|----|------|---|-----|------|---|-----|------|---|-----|------|-----|-----|------|------|------|------|------|------|-----|------|-----|------|------|---|----|------|-----|------|------|-----|-----|-----|------|

| state | 1 | G   | 1 | 2  | G    | 1 | 2 | 3  | G    | 1 | 2 | 3  | 4  | G    | 1 | 2   | G    | 1 | 2   | G    | 1 | 2   | G    | 1   | 2   | G    | 1    | 1s   | 2    | 28   | G    | 1   | 1s   | 2   | 2s   | G    | 1 | 2  | G    | 1   | 2    | G    | 1   | 2   | 3   | G    |

| T     | D | 1-D | D | D  | 1-2D | D | D | D  | 1-3D | D | D | D  | D  | 1-4E | D | 2D  | 1-3I | D | 3D  | 1-4C | D | 2D  | 1-3D | D   | 4D  | 1-5D | 2/3D | 1/3D | 2/3D | 1/3D | 1-2D | ¾D  | 1/4D | 54D | 1/4D | 1-2D | D | D  | 1-2D | D   | D    | 1-2D | D   | 2D  | D   | 1-4D |

| 0a    | 1 |     | 1 |    |      | 1 |   |    |      | 1 |   |    |    |      | 1 |     | 1    | 1 |     | 1    |   |     |      |     |     |      | 1/2  |      |      | 1    |      | 2/3 |      |     |      |      | 1 |    |      | 1/2 |      |      | 1/2 |     |     |      |

| 0b    |   | 1   |   | 1  | 1    |   | 1 | 1  | 1    |   | 1 | 1  | 1  | 1    |   |     |      |   |     |      |   |     |      |     |     |      |      |      |      |      |      |     |      |     |      |      |   | 1  | 1    |     |      |      |     |     | 1/2 |      |

| la    |   |     |   | 1  |      |   |   | 1  |      |   |   | 1  |    |      | 1 |     |      | 1 |     |      |   | 1/2 | 1    |     | 1/3 | - 1  |      |      | 1    |      |      |     |      | 1/3 | 1    |      |   | 1  |      |     |      |      |     |     | 1/2 |      |

| 1b    |   |     | 1 |    | 1    | 1 | 1 |    | 1    | 1 | 1 |    | 1  | 1    |   | 1/2 |      | Т | 1/3 |      |   | 1   |      |     | 1   |      | 1/2  |      |      | 1    | 1/2  | 1   | 1    |     |      | 1/2  | 1 |    | 1    |     |      |      | 1/2 |     |     |      |

| lc    |   |     |   |    |      |   |   |    |      |   |   |    |    |      |   | 1/2 | 1    |   | 1/3 | - 1  | 1 |     | - 1  | 1   |     | 1    |      |      | 1    |      | 1/2  |     |      | 1   | 1    | 1/2  |   |    |      |     |      |      |     |     |     |      |

| 2a    |   |     |   |    |      |   | 1 |    |      |   |   |    | 1  |      | 1 |     |      | 1 |     |      | 1 |     |      | 1/2 |     |      | 1/2  | 1    |      |      |      | 1/3 | 1    |     |      |      |   |    |      |     | 1/2  |      |     | 1/2 |     |      |

| 2b    |   |     |   |    |      | 1 |   | 1  | 1    | 1 | 1 | 1  |    | 1    |   | 1/2 |      |   | 1/3 |      | 1 |     |      | 1   |     |      |      |      | 1    |      | 1/2  |     |      | 1/3 | 1    | 1/2  |   |    |      |     | 1    | 1/2  |     | 1   |     | 1/2  |

| 2c    |   |     |   |    |      |   |   |    |      |   |   | 1  |    |      |   | 1/2 |      |   | 1/3 |      |   | 1/2 |      |     | 1/3 |      | 1/2  | 1    |      |      | 1/2  | 1/3 | 1    |     |      | 1/2  |   |    |      | 1/2 |      | 1/2  | 1/2 |     | 1/2 | 1/2  |

| 3a    |   |     |   |    |      |   |   |    |      |   | 1 |    |    |      |   |     |      | 1 |     |      |   | 1/2 |      |     | 1/3 |      |      |      |      |      |      |     |      | 2/3 |      |      |   |    |      |     |      |      |     |     |     |      |

| 3b    |   |     |   |    |      |   |   |    |      | 1 |   | 1  | 1  | 1    |   |     |      |   | 1/3 |      |   |     |      |     | 1/3 |      |      |      |      |      |      |     |      |     |      |      |   |    |      |     |      |      |     |     |     |      |

| 3c    |   |     |   |    |      |   |   |    |      |   |   |    |    |      |   |     |      |   | 1/3 |      |   |     |      | 1/2 |     |      |      |      |      |      |      |     |      |     |      |      |   |    |      |     |      |      |     |     |     |      |

| 4a    |   |     |   |    |      |   |   |    |      |   |   | 1  |    |      |   |     |      |   |     |      |   |     |      | 1/2 |     |      |      |      |      |      |      | 1   |      | 1   |      |      |   |    |      |     |      |      |     |     |     |      |

TABLE 4. Topological Parameters of Selected Hybrid Switched-Capacitor Converter Topologies

|      | #ind. | #cap. | #switch | m               | d   | p               | l     | s   | $C^2$                               | S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | $V_s$ (DSV)                              | $V_s$ (TV)                  | $V_c$           |

|------|-------|-------|---------|-----------------|-----|-----------------|-------|-----|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-----------------------------|-----------------|

| Торо |       |       |         | $V_{Lx}/V_{in}$ | D/M | $V_{Lx}$ pulses | #ind. |     | current multiplication vector       | Switch activity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | DS Blocking volt.                        | Term. Blocking volt.        | Cap. volt.      |

|      |       |       |         |                 |     |                 |       |     | $S_{0}$ ;                           | $S_{1a}; S_{1b}; S_{1c}; S_{2a}; S_{2$ | $S_{2b}; S_{2c}; S_{3a}; S_{3b}; S_{3c}$ |                             | $C_1; C_2; C_3$ |

| 1B   | 1     | 0     | 2       | 1               | 1   | 1               | 1     | -   | M,1-M                               | 1;1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1;1                                      | 1;1                         | -               |

| 2ML  |       | 1     | 4       | 1/2             | 1   | 2               | 1     | 1   | M;1-M;M;1-M                         | 1;1;1;1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1/2;1/2;1/2;1/2                          | 1;1/2;1;1/2                 | 1/2             |

| 3ML  |       | 2     | 6       | 1/3             | 1   | 3               | 1     | 2   | M;1-M;M;1-M;M;1-M                   | 1;1;1;1;1;1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1/3;1/3;1/3;1/3;1/3;1/3                  | 2/3;1/3;1;1/3;1;1/3         | 1/3;2/3         |

| 3SP  |       |       | 7       | 1/3             | 1   | 3               | 1     | 2   | 1-2M;M;M/2;1-5/2M;M;M/2;M/2         | 2;1;2;1;1;1;2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1/3;1/3;1/3;1/3;2/3;2/3;2/3              | 1/3;1/3;2/3;1/3;1;1;2/3     | 1/3;1/3         |

| 3FB  |       |       | 7       | 1/3             | 1   | 3               | 1     | 2   | 1-5/2M;2M;1-2M;M;M;M/2;M/2          | 1;2;2;1;1;1;2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1/3;1/3;1/3;1/3;2/3;2/3;1/3              | 1/3;2/3;1/3;1/3;1;2/3;1     | 1/3;2/3         |

| 3DS  |       |       | 7       | 1/3             | 3/2 | 2               | 1     | 2   | 3/4M;M;1/4;1/4+M/4;3/4M;1/4+M/4;1/4 | 2;1;1;2;1;1;1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1/3;2/3;1/3;1/3;1/3;1/3;1/3              | 2/3;1;1/3;1/3;1;1/3;1/3     | 1/3;2/3         |

| 4ML  |       | 3     | 8       | 1/4             | 1   | 4               | 1     | 2   | M;1-M;M;1-M;M;1-M;M;1-M             | 1;1;1;1;1;1;1;1;1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1/4;1/4;1/4;1/4;1/4;1/4;1/4              | 1/2;1/4;3/4;1/4;1;1/4;1;1/4 | 1/4;1/2;3/4     |

| 4SP  |       |       | 10      | 1/4             | 1   | 4               | 1     | 3   | 1-3M;M;M/3;1-11/3M;                 | 3;1;3;1;1;1;3;1;1;3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1/4;1/4;1/4;1/4;1/4;                     | 1/4;1/4;1/2;1/4;1/4;3/4;    | 1/4;1/4;1/4     |

|      |       |       |         |                 |     |                 |       |     | M;M/3;M/3;M/3;M;M/3                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1/2;1/2;3/4;3/4;3/4                      | 1/2;1;1;3/4                 |                 |

| 5FB  |       |       | 10      | 1/5             | 1   | 5               | 1     | 2/3 | 1-14/3M;3M;1-3M;M/2;                | 2;3;3;2;2;3;3;3;2;2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1/5;1/5;1/5;1/5;2/5;                     | 1/5;2/5;1/5;1/5;3/5;2/5;    | 1/5;2/3;3/5     |

|      |       |       |         |                 |     |                 |       |     | 2M;M/3;M/3;M/3;M/2;M/2              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2/5;2/5;3/5;3/5;2/5                      | 2/5;1;3/5;1                 |                 |

| 4DS  |       |       | 8       | 1/4             | 2   | 2               | 1     | 2   | 2/3M;2/3M;1/4+M;1/4+M; 2/3M         | 1;1;1;1;1;1;1;1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1/4;1/2;1/4;1/4;1/2;                     | 1/2;3/4;1/4;1/4;1;1/4;1/4;1 | 1/4;1/2;3/4     |

|      |       |       |         |                 |     |                 |       |     | 1/4-M/3;1/4-M/3;2/3M                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1/4;1/4;1/4                              |                             |                 |

| 1B2  | 2     | 0     | 4       | 1               | 1   | 2               | 2     | -   | M/4;(1-M)/4;M/4;(1-M)/4             | 1;1;1;1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1;1;1;1                                  | 1;1;1;1                     | -               |

| 2DSD |       | 1     | 4       | 1/2             | 2   | 2               | 2     | 1   | M/2;1/4+M;M/2;1/4-M/2               | 1;1;1;1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1/2;1/2;1;1/2                            | 1;1/2;1;1/2                 | 1/2             |

| 4DSD |       | 2     | 7       | 1/4             | 2   | 4               | 2     | 2   | M/2;M/2;M/2;M/2;M;1/4+2M;1/4-M      | 1;1;1;1;2;2;2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1/2;1/2;1/2;1/2;1/2;1/4;1/4              | 1;1/2;1;1/2;1/2;1/4;1/4     | 1/2;1/4         |

- The vector  $V_s$  illustrates the maximal voltage experienced by each switch during all states. The voltage can be defined by referencing drain and source voltages to the bulk (TV), or alternatively the drain-to-source voltage (DSV). All components are normalized with respect to  $\widetilde{V_{in}}$ .

- The voltage handled by each flying capacitor is described in the vector  $V_c$ , where each element is the normalized voltage referenced to  $\widetilde{V_{in}}$ . A unity value means the DC voltage across the capacitor is  $\widetilde{V_{in}}$ .

- The scalar  $m_k$  represents the normalized  $V_{Lx}$  voltage (Fig. 1) by dividing the maximal  $\widetilde{V_{Lx}}$  by  $\widetilde{V_{in}}$ .  $m_k$  is equal to 1/N.

- The relationship between the desired VCR *M* and the duty cycle *D* is illustrated by the normalized duty-cycle  $d_k = \frac{D}{M}$ . *DT* represents the duration of each pulse where  $V_{Lx}$  is not equal to zero, as illustrated in Fig. 1.

- The scalar *l* is equal to the number of inductors.

- The switch rate of  $V_{Lx}$  is given by the scalar *p*. Here, a value of *n* means  $V_{Lx}$  switches *n* times during time *T*.

- The scalar *s* is utilized to ascertain the ratio of the effective capacitor value seen by  $L_k$ . It is used to calculate the out-of-resonance condition and is derived by determining the minimum value of the equivalent flying capacitor network at the  $V_{Lx}$  node throughout all states.

The vector size of *C*, *S* and  $V_s$  is equal to the number of switches. The length of  $V_c$  is determined by the number of flying capacitors. The term "state" pertains to the various switch configurations within one switching period, whereas the term "phase" is employed to signify the interconnection between different power stages that converge at the output node  $V_o$  through inductors. The topological parameters of all screened topologies are given in Table 4.

### F. INPUTS DETERMINATION USING DSD AS AN EXAMPLE

This section describes how to find the topological parameters for a 2:1 HSCC in the DSD configuration (2DSD) using the schematic and state sequence shown in Fig. 2 and Table 3, respectively.

In the 2DSD configuration, featuring two inductors, under steady-state operation with ideal charge balancing, the capacitor network produces a  $V_{LX}$  pulse train oscillating between 0 and  $V_{in}/2$  with a duty cycle of *D*, consequently resulting in m = 1/2. The connection between VCR and the duty cycle is expressed as D = 2M, setting *d* to 2. The total count of pulses observed by the output from both  $V_{Lx}$  is 2, yielding p = 2.

Table 3 gives the normalized current flowing in each state with respect to the output current, which allows us to determine the dimensionless current multiplication vector, C (Table 4). The RMS current flowing can be deduced in each switch during the period using Table 3, and then  $C_i$  can be calculated as:

$$C_{i} = \sqrt{\sum_{j}^{\# state} C_{i,j}^{2} D_{j}} = f(M)$$

(2)

Here,  $D_j$  is the duty cycle of the *j*th state, and  $C_{i,j}$  is the normalized DC current passing through the *i*th switch.

In 2DSD [12], three switches see half of the input voltage, and the third one sees the entire voltage ( $V_{s,j} = 1/2$ ,  $j \in \{1, 2, 4\}$  and  $V_{s,3} = 1$ ). In some contexts, the voltage referenced to the bulk is the limiting factor, and this is given in the  $V_S$  vector in Table 4 (terminal voltage column). For 2DSD,

two switches see the entire voltage, and the others see half of the input voltage. In this case,  $V_s$  is equal to [1,1/2,1,1/2].