Received 16 December 2022; revised 10 January 2023; accepted 15 January 2023. Date of publication 18 January 2023; date of current version 8 February 2023. The review of this article was arranged by Associate Editor Ui-Min Choi.

Digital Object Identifier 10.1109/OJPEL.2023.3237877

# Medium-Voltage Seven-Level Multiplexed Converter for AC Applications

ALESSANDRO LIDOZZI <sup>10</sup> , MARCO DI BENEDETTO <sup>10</sup> (Member, IEEE), THIERRY A. MEYNARD <sup>10</sup> , AND LUCA SOLERO <sup>10</sup> (Senior Member, IEEE)

<sup>1</sup>Engineering, University Roma Tre, 00146 Roma, Italy <sup>2</sup>Laplace, Universite de Toulouse, 31000 Toulouse, France

CORRESPONDING AUTHOR: ALESSANDRO LIDOZZI (e-mail: alessandro.lidozzi@uniroma3.it)

This work was supported by the Regione Lazio of Italy under Grant "Progetti di Gruppi di Ricerca 2020, N. 36774".

ABSTRACT After several decades of technological evolution, power electronics applications have become extremely important for electric/hybrid propulsion systems, smart grids, renewable energy systems, energy saving, and bulk energy storage, besides the typical applications in industrial automation and high-efficiency energy systems. In all these applications, a power conversion system with high efficiency and power density is required without sacrificing the system's power quality. The paper describes the specific characteristics and the scalar modulation strategy of a new multi-level multiplexed inverter topology for medium-voltage AC applications. The proposed power converter configuration is intended for high-power applications aiming to reduce the active device's voltage rating and losses exhibiting a resulting low switching frequency of the power switches. The proposed modulation strategy aims to reduce the computational burden and simplify the implementation process, which are at the basis of any possible industrial adoption. Simulation results and full Hardware-In-the-Loop verification support the analysis. The Hardware-In-the-Loop assessment has enabled the development of a suitable modulation strategy, and the testing of the power converter is a safe environment.

**INDEX TERMS** Multilevel, multiplexed, AC application, three-phase inverter.

#### I. INTRODUCTION

Multilevel and multicell power converters are currently considered one of the most promising industrial topology solutions thanks to the reduction of losses and, consequently, the efficiency improvement without sacrificing the system's power quality [1]. Over the years, several multilevel topologies, from the simplest to the most complex, have been introduced in literature [2], [3]. The fundamental characteristics of the multilevel converters, which determine their usability, such as DC bus neutral point voltage balancing and flying capacitor voltage control, are investigated in [4], [5].

New converter topologies have been introduced [6], presenting specific features for medium voltage applications. A review of Modular Multilevel Converters (MMC) has been presented in [7], where the application to medium voltage electric drives is illustrated in [8]. Concerning the MMC, a flying capacitor architecture has been described in [9]. Charging the floating capacitors is an issue that has been solved by

adopting cost-effective solutions [10], gaining attention to the related converter topologies.

Multilevel based power converter architectures have also been investigated for DC-DC applications as in [11], [12]. It is imperative to choose the proper conversion topology and technology to enhance the characteristics of the multilevel converters, such as efficiency, power density, and quality of the input currents and output voltages. Concerning the choice of the conversion topology, size and weight of the system, its cost, energy efficiency, thermal efficiency, complexity, and electromagnetic interference are all factors that a designer should consider to achieve an optimal design [13], [14]. Naturally, it must be recognized that these factors are interdependent. For instance, a complex topology may exhibit more pronounced electromagnetic interference effects than a simpler one. Beyond the choice of the topology, there is another essential element in the hardware implementation of a power conversion system, such as the progress in new power

devices and/or technologies [15]. Today, for example, many converter designers rely on the use of new power semiconductors based on the Wide Bandgap Semiconductors (WBS), like Silicon Carbide (SiC) or Gallium Nitride (GaN) [1] which support much faster commutations than silicon power devices and can operate at higher temperatures [17]. This paper describes the three-phase 7-level Multiplexed Converter (3Φ7L M<sub>L</sub>M<sub>X</sub>C). The operation principles and the modulation strategy of the proposed converter are discussed, by proposing a carried-based modulation approach (i.e., effective to be implemented on industrial microcontrollers or FPGAs) and describing the commutation paths. The flying capacitor of the proposed converter requires an additional pre-charging circuit during the start-up process and balancing control during steady-state operation. The voltage balancing of flying capacitor at a steady-state can be solved by charging and discharging the capacitors using the redundant states. However, the problem of the unbalancing voltage across the flying capacitors is not addressed in this paper. The analysis is supported by simulation results and full Hardware-In-the-Loop (HIL) verification implementing the proposed modulation scheme on an industrial-grade control board. The Hardware-In-the-Loop assessment has enabled the development and testing of a suitable modulation strategy for the power converter in a safe environment, which is very close to the final usage being the code implemented in an industrial control platform.

This paper is organized as follows. In Section II, the  $3\Phi7L$   $M_LM_XC$  topology is introduced and compared with other 7-level topologies. The carrier-based modulation strategy and the operating principle of the proposed converter are presented in Section III, including a detailed description of the commutation paths. The problem of the flying capacitor voltage balancing is addressed in Section IV. Section V presents the simulation results to verify the converter performance, while Section VI presents the experimental results using the Hardware-In-the-Loop system. A preliminary analysis of the conduction and switching losses of the  $3\Phi7L$   $M_LM_XC$  topology is shown in Section VII. Finally, Section VI outlines the conclusion.

### II. 347L MLMxC TOPOLOGY

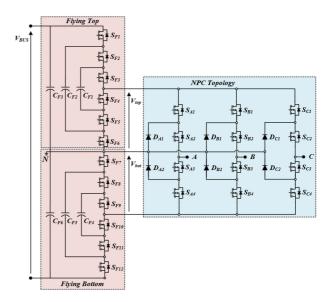

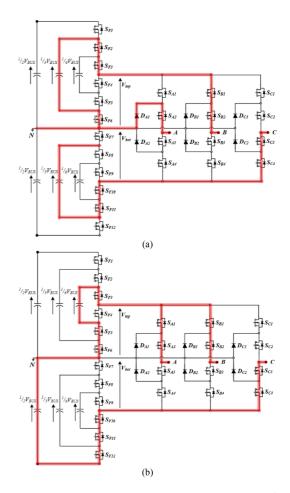

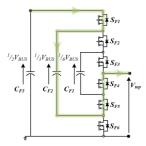

The circuit diagram of the proposed topology is illustrated in Fig. 1. As can be seen, the  $3\Phi 7L$   $M_L M_X C$  is equipped with 24 switches, and it is the combination of two different topologies: the Flying Capacitor (FC) and the NPC (Neutral Point Clamped). The first FC on the top side of the power conversion is responsible for managing the upper DC-bus, while the second FC manages the lower part of the DC-bus.

Thus, the top side and the bottom side FCs work as DC-DC converters, and they play the role of the multiplexer, hence the name multi-level multiplexed converter. Both top and bottom FCs provide four voltage levels  $(0, \frac{1}{2}V_{BUS}, \frac{1}{3}V_{BUS}, \frac{1}{6}V_{BUS},$  top side and  $0, -\frac{1}{2}V_{BUS}, -\frac{1}{3}V_{BUS}, -\frac{1}{6}V_{BUS}$  bottom side). Consequently, the single phase of the NPC topology can provide seven voltage levels,  $0, \pm 1/2V_{BUS}, \pm 1/3V_{BUS}, \pm 1/6V_{BUS}$ . The main advantage of this configuration is that no filter

FIGURE 1. Circuit diagram of 3  $\Phi$ 7L M<sub>L</sub>M<sub>X</sub>C.

elements are used between the flying capacitor and the NPC topologies. Another benefit of the proposed topology is the low voltage stress across the power semiconductors, which enables to use low-cost silicon components or, in the alternative, SiC devices can be used to improve the efficiency and the power density. Several multilevel topologies able to provide 7 voltage levels at the output are proposed in the literature [18], [19], [20], [21], [22], [23], [19], [24], [25], [26], [27], [28], [29]. The comparison of the three-phase 7-level (7L) converter topologies in terms of the number of power semiconductors, including switches and diodes, the number of DC-bus capacitors and flying capacitors, as well as the maximum voltage stress across the components is shown in Table 1. As can be seen, the 7L Active Neutral point Clamped (ANPC) [22], the 7L Flying Capacitor NPC (FC-NPC) [24], and the proposed topology makes fewer power semiconductors compared to the other topologies. The 7L NPC [20], the Hybrid ANPC (H-ANPC) [25], as well as the 7L modular multilevel converter (MMC) [28] require a larger number of power semiconductors. The disadvantages of the  $3\Phi7L\ M_LM_XC$  are the voltage stress across the external flying capacitors  $C_{F3}$ ,  $C_{F6}$  and the voltage across the power semiconductors located in NPC, which is equal to  $^{1}/_{2}V_{BUS}$ . However, the commutation of the power semiconductors placed into NPC of the 3Φ7L M<sub>L</sub>M<sub>X</sub>C can occur at zero current, and thus the switching losses can be drastically reduced.

#### III. MODULATION STRATEGY

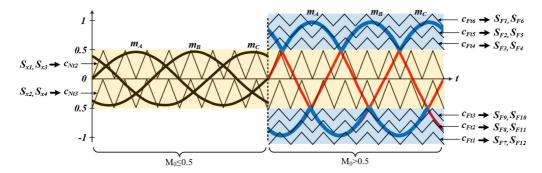

Sinusoidal Pulse Width Modulation (SPWM) has been used to control the power semiconductors of the topology. Fig. 2 shows the implemented modulation scheme for the modulation depth  $M_0$  below and above 0.5. When  $M_0 \le 0.5$ , the top and bottom FCs provide  $\pm 1/3V_{BUS}$  (given that  $S_{F3}$ ,  $S_{F5}$ ,  $S_{F6}$ ,  $S_{F7}$ ,  $S_{F8}$ ,  $S_{F10}$  are in on-state conduction mode) and two carrier signals  $c_{Nt2}$ ,  $c_{Nt3}$  are compared to the modulating signals,

**TABLE 1.** Number of Components in Three-Phase 7-Level Converter Topologies

|                                    | Number of power semiconductors | Number of DC-bus | Number of Flying<br>Capacitors | Maximum<br>Capacitors voltage                       | Maximum power semiconductors | Number of power semiconductor with |

|------------------------------------|--------------------------------|------------------|--------------------------------|-----------------------------------------------------|------------------------------|------------------------------------|

| 7L NPC [20]                        | 66                             | capacitors<br>6  |                                | stress <sup>1</sup> / <sub>6</sub> V <sub>BUS</sub> | voltage stress               | $^{1}/_{6}V_{BUS}$                 |

| t 3                                | 36                             | 2                | 15                             |                                                     |                              | 36                                 |

| 7L FC [21]                         |                                |                  | 13                             | $^{5}/_{6}V_{BUS}$                                  | $^{I}/_{6}V_{BUS}$           |                                    |

| 7L ANPC [22]                       | 30                             | 2                | 6                              | $V_{BUS}$                                           | $^{1}/_{2}V_{BUS}$           | 12                                 |

| 7L HC [23], [24]                   | 36                             | 3                | 6                              | $^{l}/_{3}V_{BUS}$                                  | $^{I}/_{3}V_{BUS}$           | 12                                 |

| 7L FC-NPC [25]                     | 24                             | -                | 12                             | $^{1}/_{2}V_{BUS}$                                  | $^{1}/_{2}V_{BUS}$           | 12                                 |

| 7L H-ANPC [26]                     | 57                             | 2                | 15                             | $^{I}/_{2}V_{BUS}$                                  | $^{1}/_{2}V_{BUS}$           | 6                                  |

| 7L E-Type [27]                     | 36                             | 6                | -                              | $^{l}/_{6}V_{BUS}$                                  | $^2/_3V_{BUS}$               | 12                                 |

| 7L Generalized [28]                | 36                             | 3                | 12                             | $^{I}/_{3}V_{BUS}$                                  | $^{1}/_{3}V_{BUS}$           | 6                                  |

| 7L MMC [29]                        | 72                             | -                | 36                             | $^{1}/_{6}V_{BUS}$                                  | $^{1}/_{6}V_{BUS}$           | 72                                 |

| 7L Cascade [30]                    | 36                             | 6                | -                              | $^{l}/_{6}V_{BUS}$                                  | $^{l}/_{6}V_{BUS}$           | 36                                 |

| 7L M <sub>L</sub> M <sub>X</sub> C | 30                             | -                | 6                              | $^{1}/_{2}V_{BUS}$                                  | $^{1}/_{2}V_{BUS}$           | 12                                 |

FIGURE 2. Carrier-based modulation scheme for the  $3\Phi 7L$  M<sub>L</sub>M<sub>X</sub>C.

providing the control signals of the power semiconductors located in the NPC.

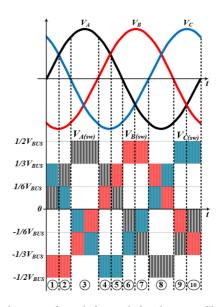

In case  $M_0 > 0.5$ , it is possible to notice that the top and the bottom part of the modulation signals (blue line) are managed by the FCs, as well as the transitions of the modulation signals (red line) are handled by the NPC converter. The control signals of the switches located in the bottom FC are generated by the comparison between the lower modulating signal (highlighted in blue) and three carrier signals,  $c_{Ft1}$ ,  $c_{Ft2}$ , and  $c_{Ft3}$ , while the control signals of the power semiconductors placed into the top FC are provided through the comparison between the higher modulating signal (highlighted in blue) and three carrier signals  $c_{Ft4}$ ,  $c_{Ft5}$ ,  $c_{Ft6}$ . The comparison between the modulating signals highlighted in red and two carrier signals  $c_{Nt2}$  and  $c_{Nt3}$ , generate the power semiconductors' control signals in the NPC. Thus, the voltage provided by the proposed converter shows seven voltage levels in Fig. 3, in which the ten sectors are clearly visible at the bottom side.

## A. FORBIDDEN STATES

The presented configuration exhibits inherent forbidden states, which must be avoided to not occur in catastrophic failure of the power converter. The proposed carrier-based modulation will be able to prevent such conditions thanks also to the FPGA implementation. The PWM modulation strategy has been implemented to stop any potentially dangerous state propagated by comparing the carrier and the modulating signal. The specific operating sector must be distinguished to

FIGURE 3. Voltage waveforms before and after the output filters.

detect the switching pulses that are not allowed. The modulating signals of the particular phase are split into ten different sectors. For instance, considering the phase A, it is possible recognize ten sectors, as shown in Fig. 3. Given that the positive DC-bus and the negative DC-bus are shared between the three phases of the NPC inverter, when the output voltage vector to be synthesized is inside a specific sector, the affected

VOLUME 4, 2023 83

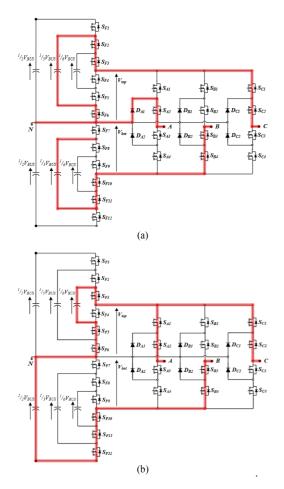

FIGURE 4. Commutation path in the sector 1: (a)  $V_{A(sw)}=0$ ,  $V_{B(sw)}=-^1/_3V_{BUS}$ ,  $V_{C(sw)}=^1/_3V_{BUS}$ , (b)  $V_{A(sw)}=^1/_6V_{BUS}$ ,  $V_{B(sw)}=-^1/_2V_{BUS}$ ,  $V_{C(sw)}=^1/_6V_{BUS}$ .

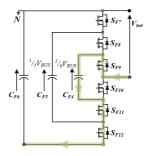

switches are forced to their appropriate state. As seen in Fig. 3, in sector 1 the phase A commutates between 0 and  $^{I}/_{6}V_{BUS}$ , while the phase C and then the phase B commutate between  $^{I}/_{6}V_{BUS}$  and  $^{I}/_{3}V_{BUS}$  in the same sector. Thus, in sector 1, phase A of the NPC is kept to zero through the clamped diode when the top FC provides  $^{I}/_{3}V_{BUS}$ , as illustrated in Fig. 4(a), while in the other state, both phases A and C provide  $^{I}/_{6}V_{BUS}$ , as shown in Fig. 4(b).

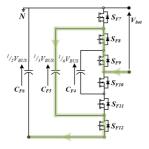

In sector 2, there is the same situation as in sector 1, but with phases A and C reversed. In sector 4, the same situation occurs, but this time, it is phase B instead of phase C to share the positive DC-bus with phase A. Consequently, when the output of phase B provides  $^{1}/_{3}V_{BUS}$ , phase A is kept to zero, as shown in Fig. 5(a), whereas in the other instant, both phases A and B provide  $^{1}/_{3}V_{BUS}$ , as illustrated in Fig. 5(b).

In sector 5, there is the same situation as in sector 4, but with phases, A and B reversed. A similar situation occurs in sectors 6, 7, 9, and 10.

#### **IV. SIMULATION RESULTS**

The operation principle, including the modulation scheme of the  $3\Phi 7LM_LM_XC$ , has been implemented in Matlab/Simulink

FIGURE 5. Commutation path in the sector 5: (a)  $V_{A(sw)}=0$ ,  $V_{B(sw)}=^1/_3V_{BUS}$ ,  $V_{C(sw)}=^1/_5V_{BUS}$ ,  $V_{B(sw)}=^1/_6V_{BUS}$ ,  $V_{B(sw)}=^1/_6V_{BUS}$ ,  $V_{B(sw)}=^1/_2V_{BUS}$ .

TABLE 2. Operating Point of the  $3\Phi7LM_LM_XC$

| DC-bus voltage $V_{BUS}$                                    | 11 kV  |  |

|-------------------------------------------------------------|--------|--|

| Line-to-line RMS voltage $V_{xLL}$ with $x \in \{A, B, C\}$ | 6.6kV  |  |

| switching frequency $f_{sw}$                                | 5 kHz  |  |

| fundamental frequency $f_0$                                 | 50 Hz  |  |

| Output filter capacitance C <sub>0f</sub>                   | 20 μF  |  |

| Output filter inductance L <sub>0f</sub>                    | 200 μΗ |  |

| Resistive load R <sub>Load</sub>                            | 10 Ω   |  |

| Output Power P <sub>0</sub>                                 | 3.8 MW |  |

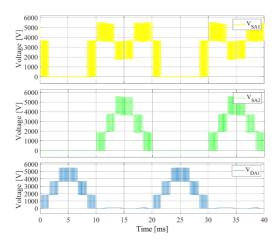

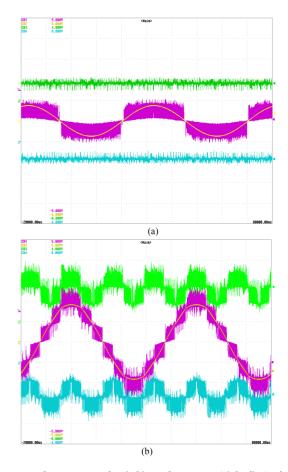

with a fully detailed model, which considers the physical realization of the modulation strategy on the control platform. The characteristic waveforms and the voltage stress of the power semiconductors have been evaluated according to the operating point listed in Table 2. Fig. 6 shows the voltage waveforms at steady-state under resistive load when the modulation depth  $M_0$  is below (a) and above 0.5 (b).

As it can be seen, when  $M_0 = 0.4$ , the phase-to-neutral switching voltages  $V_{xN(sw)}$ , with  $x \in \{A, B, C\}$ , show three-voltage level, as well as the positive and negative DC-bus voltages  $V_{top}$  and  $V_{bot}$  are equal to  $\pm \frac{I}{6}V_{BUS}$ , respectively. When  $M_0 = 0.94$ , the phase-to-neutral switching voltages  $V_{xN(sw)}$  show seven voltage levels, and the output voltages

FIGURE 6. Waveforms at a steady state, from top to bottom: Phase-to-neutral before and after filter  $V_{xN}$ ,  $V_{xN(sw)}$ , three-phase currents  $i_x$  and top and bottom DC-bus voltages  $V_{top(sw)}$  and  $V_{bot(sw)}$ : (a)  $M_0{=}0.4$ , (b)  $M_0{=}0.94$ .

FIGURE 7. Voltage stress across the NPC power semiconductors  $S_{A1},\,S_{A2},\,D_{A1},\,$

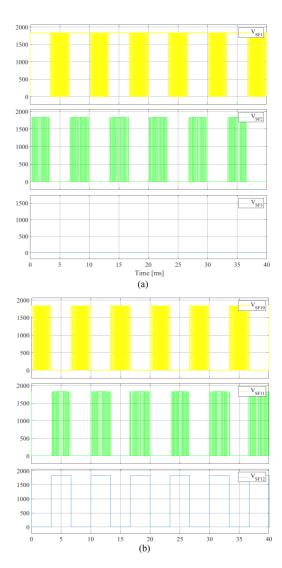

provided by the top and the bottom FCs ( $V_{top}$  and  $V_{bot}$ ) draw three voltage levels. The voltage across the power semiconductors of the top side of the NPC phase leg A  $S_{AI}$ ,  $S_{A2}$ ,  $D_{AI}$  are illustrated in Fig. 7. Fig. 8 shows the power semiconductors' voltage stress in the top FC and bottom FC,  $S_{FI}$ ,  $S_{F2}$ ,

**FIGURE 8.** (a) Voltage stress across the power semiconductors: (a) Located in the top FC  $S_{F1}$ ,  $S_{F2}$ ,  $S_{F3}$ . (b) Located in the bottom FC  $S_{F10}$ ,  $S_{F11}$ ,  $S_{F12}$ .

$S_{F3}$ ,  $S_{F10}$ ,  $S_{F11}$ ,  $S_{F12}$ . From this analysis, it is possible to state that the maximum voltage stresses of power semiconductors placed into NPC and FCs are  $^1/_2V_{BUS}$  and  $^1/_6V_{BUS}$ , respectively.

#### **V. CAPACITORS VOLTAGE BALANCING AND DESIGN**

The flying capacitors can be balanced starting from the proposed modulation control scheme. The external flying capacitors  $C_{F3}$  and  $C_{F6}$  can be balanced by adding the offset in the modulation signals [30]. The control signals are written in (0), where  $m_0$  is the offset of the signals,  $M_0$  is the modulation depth and  $\xi$ =01,2.

$$m_{A,B,C}(t) = m_0 + \frac{1}{2} \left[ 1 + M_0 \sin \left( \omega_0 t - \xi \frac{2\pi}{3} \right) \right]$$

(1)

It can be proven that the average current into the neutral point N depends on the offset  $m_0$ . Thus, by controlling the modulation index offset  $m_0$ , it is possible to achieve an

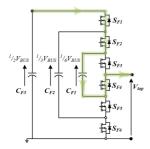

FIGURE 9. Charging path for the flying capacitors C<sub>F1</sub>.

FIGURE 10. Charging path for the flying capacitors  $C_{F2}$ .

FIGURE 11. Charging path for the flying capacitors CF4.

FIGURE 12. Charging path for the flying capacitors  $C_{F5}$ .

equal voltage distribution among the capacitors  $C_{F3}$  and  $C_{F6}$ . Regarding the flying capacitors  $C_{F1}$ ,  $C_{F2}$ ,  $C_{F4}$  and  $C_{F5}$ , the situation is different. The main idea is to exploit some commutation instants to charge the capacitors in each sector, as shown respectively in Fig. 9 for  $C_{F1}$  and in Fig. 10 for  $C_{F2}$ .

When the capacitor  $C_{F1}$  is charged, the top FC provides  $^{1}/_{3}V_{BUS}$ , while the top FC provides  $^{1}/_{6}V_{BUS}$  when the flying capacitor  $C_{F2}$  is charged. The same happens to the flying

capacitors  $C_{F4}$  and  $C_{F5}$ , as shown in Figs. 11 and 12, respectively. If the capacitor  $C_{F5}$  is charged, the bottom FC provides  $-^{1}/_{6}V_{BUS}$ . As can be noticed, the flying capacitor voltages are self-balanced without additional balancing circuits.

Since the load current flow through the flying capacitors, film capacitors must be used. Film capacitors have a much lower ESR than electrolytic capacitors but are bulkier. The minimum required value of the flying capacitors depends on several factors, such as maximum permissible voltage ripple, switching frequency, and current flowing through the flying capacitors. Consequently, the choice of the flying capacitors to be used can be made on two criteria: 1) current stress and 2) minimizing the peak value of the output voltage ripple. In particular, the voltage ripple is related to the current and the capacitor by the relationship in (2), where  $I_{FC}$  is the current flowing in the flying capacitor and  $d_{FC}$  is the duty cycle of the flying capacitor current. The maximum voltage ripple  $\Delta V_{FC\_max}$  occurs in a switching period when  $d_{FC}$   $T_{FC}$  is maximum.

$$\Delta V_{FC_{\text{max}}} = \frac{\max (d_{FC}I_{FC})}{2f_{sw}C_{FC}}$$

(2)

To simplify the design process, for a given power factor, the worst-case scenario for maximum voltage ripple is considered, i.e.,:

$$\Delta V_{FC\_max}\big|_{(worstcase)} = \frac{\max(d_{FC})\max(I_{FC})}{2f_{sw}C_{FC}} \approx \frac{I_{BUS}^{pk}}{2f_{sw}C_{FC}}$$

Consequently, the minimum flying capacitor value can be calculated considering the (4).

$$C_{FC} \ge \frac{I_{BUS}^{pk}}{2f_{sw} \Delta V_{FC\_max}|_{(worstcase)}} \tag{4}$$

To precharge the flying capacitors, resistors can be installed in parallel. There is no specific formula for calculating these resistor values. Still, they should be selected so that when no power semiconductors are switching, and the general circuit behaviour is similar to an RC network, the steady state value of the flying capacitor voltages are within 5% of their nominal value.

### VI. EXPERIMENTAL VERIFICATION

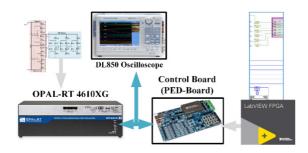

Complete power converter configuration has been real-time emulated by the eHS64 FPGA solver from OPAL-RT. The high-fidelity, high-performance OP4610XG Hardware-In-the-Loop allowed to correctly represent the power converter behavior under the proposed modulation strategy. Inverter switches' commutation patterns are provided by an industrial control platform directly connected to the HIL system. The modulation scheme has been implemented on the PED-Board controller directly on the FPGA taking advantage of the LabVIEW graphical environment. Thanks to the FPGA implementation, the carrier-based approach was possible due

FIGURE 13. Real-time arrangement for testing the  $3\Phi 7L$   $M_L M_X C$  modulation strategy.

FIGURE 14. Block diagram for the suppression of the prohibited switching pulses.

to the possibility of stopping the forbidden states straightforwardly. The experimental set-up used for the final verification is shown in Fig. 13.

#### A. FPGA IMPLEMENTATION FOR THE FORBIDDEN STATES

As previously described, a pure carrier-based PWM modulator generates specific switching configurations that must be avoided to save the converter from dangerous and catastrophic situations. Accordingly, the FPGA checks for every switching pulse when it falls in the forbidden list. Consequently, the prohibited impulses will be inhibited, as shown in Fig. 14. Sector identification is performed continuously with a time resolution of 25 ns. which is the FPGA base clock.

#### B. STEADY-STATE TEST

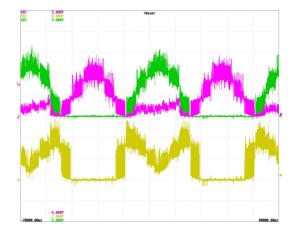

The experimental verification of the  $3\Phi 7 L M_L M_X C$  has been performed according to the operating point of Table 2. Fig. 15 shows the phase-to-neutral switching voltage  $V_{A(sw)}$  (violet line), the phase voltage  $V_A$  (yellow line), the top DC-bus voltage  $V_{top(sw)}$  (green line) and the bottom DC-bus voltage  $V_{bot(sw)}$  (cyan line) for different values of the modulation depth.

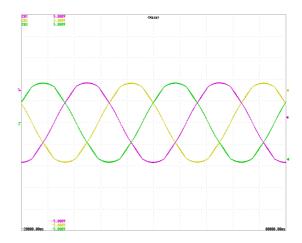

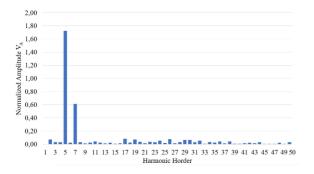

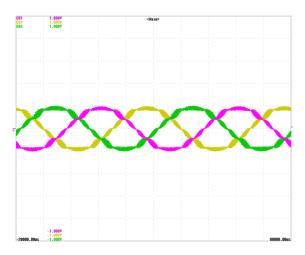

It is easy to recognize the seven voltage levels provided by the phase A. Moreover, as it results in Fig. 6, the voltages  $V_{top(sw)}$  and  $V_{bot(sw)}$  show three voltage levels. The three-phase voltages  $V_A$ ,  $V_B$  and  $V_C$  are illustrated in Fig. 16, whereas the normalized harmonic content of the phase-to-neutral voltage related to the phase A,  $V_A$ , is illustrated in Fig. 17. As can be seen, the 5th and 7th harmonics are dominant at low frequencies.

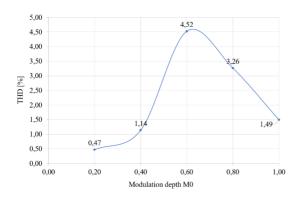

Fig. 18 shows the THD of the phase-to-neutral voltage  $V_A$  as a function of the modulation depth  $M_0$ . As can be seen, the THD exhibits a relatively high value when  $M_0$  is close to 0.6 since the duty cycle of the switches into NPC is

FIGURE 15. Phase-to-neutral switching voltage  $V_{A(sw)}$  (violet line), phase voltage  $V_A$  (yellow line), top DC-bus voltage  $V_{top(sw)}$  (green line) and bottom DC-bus voltage  $V_{bot(sw)}$  (cyan line): (a)  $M_0$ =0.4, (b)  $M_0$ =0.94. 2500 V/div, 4 ms/div.

FIGURE 16. Three-phase voltages waveforms  $V_A$  (violet line),  $V_B$  (yellow line),  $V_C$  (green line) when  $M_0$ =0.94. 2500 V/div, 4 ms/div.

different if the transition happens when the voltage is high or low. The three-phase currents flowing into output inductances are shown in Fig. 19. It can be noticed that the three-phase voltages and currents are perfectly symmetrical and balanced. The Total Harmonic Distortion (THD) estimated up to the  $50^{th}$  harmonic is 1.52%.

VOLUME 4, 2023 87

FIGURE 17. Normalized phase-to-neutral voltage  $V_A$  harmonic content when  $M_0$ =0.94.

FIGURE 18. Total harmonic distortion of the phase-to-neutral voltage  $V_A$  as a function of modulation depth  $M_{\rm o}$ .

FIGURE 19. Three-phase inductor currents waveforms  $I_A$  (violet line),  $I_B$  (yellow line),  $I_C$  (green line)  $M_0$ =0.94. 400 A/div, 4 ms/div.

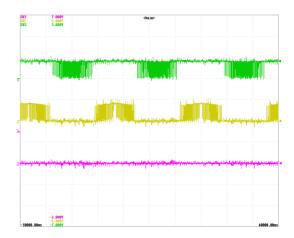

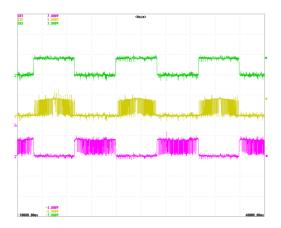

Fig. 20 illustrates the voltage waveforms across the power switches  $S_{A1}$ ,  $S_{A2}$ , and the power diode  $D_{A1}$ . As can be seen, these waveforms are coincident with those of Fig. 7. Finally, Figs. 21 and 22 show the voltage stress of the power semiconductors located in the top FC  $S_{F1}$ ,  $S_{F2}$ ,  $S_{F3}$  and the voltage stress found in the bottom FC  $S_{F10}$ ,  $S_{F11}$ ,  $S_{F12}$ .

FIGURE 20. Voltage stress across the NPC power semiconductors  $S_{A1}$  (yellow line),  $S_{A2}$  (green line),  $D_{A1}$  (violet line). 2500 V/div, 4 ms/div.

FIGURE 21. Voltage stress across the top FC power semiconductors  $S_{F1}$  (green line),  $S_{F2}$  (yellow line),  $S_{F3}$  (violet line). 2500 V/div, 4 ms/div.

# VII. PRELIMINARY ANALYSIS OF THE CONVERTER LOSSES

The power losses are evaluated in the Plexim/Plecs environment, where the thermal model of power semiconductors has been created, producing multi-dimensional lookup tables based on the parameters provided by the manufacturers. In this case, the losses have been evaluated considering the use of the 3300V IGBT module (manufacturer Infineon, part number FZ2400R33HE4) and for the FCs the 2300V IGBT module (manufacturer Infineon, part number FF1800R23IE7P).

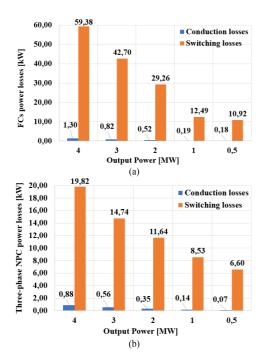

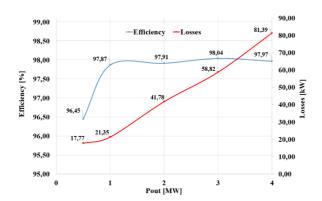

Assuming the DC-bus voltage  $V_{BUS} = 11 \ kV$ , line-to-line RMS voltage  $V_{xLL} = 6.6 \ kV$ , switching frequency  $f_{sw} = 5 \ kHz$ , fundamental frequency  $f_0 = 50 \ Hz$ , modulation depth  $M_0 = 0.94$ , output filter capacitance  $C_{0f} = 20 \ mF$ , output filter inductance  $L_{0f} = 200 \ mH$ , Fig. 23(a) illustrates the conduction and switching losses in both top and bottom FCs as a function of the output power, while Fig. 23(b) shows the conduction and switching losses in the NPC as a function of the output power. As can be seen, the switching losses are higher than the conduction losses since the power switches commutate at high DC-bus voltage. Fig. 24 shows the efficiency and power

FIGURE 22. Voltage stress across the bottom FC power semiconductors  $S_{F10}$  (violet line),  $S_{F11}$  (yellow line),  $S_{F12}$  (green line). 2500 V/div, 4 ms/div.

FIGURE 23. Power losses distribution of the power semiconductors located in: (a) Top and bottom FCs, (b) Three-phase NPC.

FIGURE 24. Estimated power efficiency and losses as a function of the power.

losses distributions as a function of the output power. It can be seen from Fig. 24 that the efficiency is above 97.5% in the power range between 1 and 4 MW.

#### VIII. CONCLUSION

A three-phase multi-level multiplexed converter for medium voltage has been discussed in this paper. The  $3\Phi7L$   $M_LM_XC$  topology, modulation strategy, and operating principle have been explained. The modulation strategy has been implemented in Matlab/Simulink environment to verify the proposed analysis. Experimental waveforms obtained using the high-fidelity Hardware-In-the-Loop real-time emulator have been illustrated to prove the correct operation and performance of the proposed topology. The achieved results show the excellent quality of the converter's output waveforms even in the case of low switching frequency.

#### **REFERENCES**

- T. A. Meynard, H. Foch, P. Thomas, J. Courault, R. Jakob, and M. Nahrstaedt, "Multicell converters: Basic concepts and industry applications," *IEEE Trans. Ind. Electron.*, vol. 49, no. 5, pp. 955–964, Oct. 2002.

- [2] G. F. Gontijo, S. Wang, T. Kerekes, and R. Teodorescu, "Novel converter topology with reduced cost, size and weight for high-power medium-voltage machine drives: 3x3 modular multilevel series converter," *IEEE Access*, vol. 9, pp. 49082–49097, 2021.

- [3] J. Wu and X. Wu, "FoM based optimal frequency and voltage level design for high efficiency high density multilevel PFC with GaN device," in *Proc. IEEE Appl. Power Electron. Conf. Expo.*, 2020, pp. 1911–1915.

- [4] X. Yuan, "Derivation of voltage source multilevel converter topologies," IEEE Trans. Ind. Electron., vol. 64, no. 2, pp. 966–976, Feb. 2017.

- [5] J. Rodriguez, J.-S. Lai, and F. Z. Peng, "Multilevel inverters: A survey of topologies, controls, and applications," *IEEE Trans. Ind. Electron.*, vol. 49, no. 4, pp. 724–738, Aug. 2002.

- [6] P. Sun, Y. Tian, J. Pou, and G. Konstantinou, "Beyond the MMC: Extended modular multilevel converter topologies and applications," *IEEE Open J. Power Electron.*, vol. 3, pp. 317–333, 2022.

- [7] A. Dekka, B. Wu, R. L. Fuentes, M. Perez, and N. R. Zargari, "Evolution of topologies, modeling, control schemes, and applications of modular multilevel converters," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 5, no. 4, pp. 1631–1656, Dec. 2017.

- [8] S. Du, B. Wu, K. Tian, N. Zargari, and Z. Cheng, "An active cross-connected modular multilevel converter (AC-MMC) for mediumvoltage motor drive," *IEEE Trans. Ind. Electron.*, vol. 63, no. 8, pp. 4707–4717, Aug. 2016.

- [9] S. Du, B. Wu, N. R. Zargari, and Z. Cheng, "A flying-capacitor modular multilevel converter for medium-voltage motor drive," *IEEE Trans. Power Electron.*, vol. 32, no. 3, pp. 2081–2089, Mar. 2017.

- [10] K. Tian, B. Wu, S. Du, D. Xu, Z. Cheng, and N. R. Zargari, "A simple and cost-effective precharge method for modular multilevel converters by using a low-voltage DC source," *IEEE Trans. Power Electron.*, vol. 31, no. 7, pp. 5321–5329, Jul. 2016.

- [11] M. V. Soares and Y. R. de Novaes, "MMC based hybrid switched capacitor DC-DC converter," *IEEE Open J. Power Electron.*, vol. 3, pp. 142–152, 2022.

- [12] S. F. Graziani, T. V. Cook, and B. M. Grainger, "Isolated flying capacitor multilevel converters," *IEEE Open J. Power Electron.*, vol. 3, pp. 197–208, 2022.

- [13] J. W. Zapata, G. Postiglione, D. Falchi, G. Borghetti, T. A. Meynard, and G. Gateau, "Multilevel converter for 4.16- and 6.6-kV variable speed drives," *IEEE Trans. Power Electron.*, vol. 36, no. 3, pp. 3172–3180, Mar. 2021.

- [14] K. Odriozola, T. A. Meynard, and A. Lacarnoy, "Full-silicon 98.7% efficient three-phase five-level 3-port UPS architecture with wide voltage range battery based on multiplexed topology," in *Proc. 22nd Eur. Conf. Power Electron. Appl.*, 2020, pp. 1–13.

VOLUME 4, 2023 89

- [15] Z. Liao, Y. Lei, and R. C. N. Pilawa-Podgurski, "Analysis and design of a high-power density flying-capacitor multilevel boost converter for high step-up conversion," *IEEE Trans. Power Electron.*, vol. 34, no. 5, pp. 4087–4099, May 2019.

- [16] S. Belkhode, P. Rao, A. Shukla, and S. Doolla, "Comparative evaluation of silicon and silicon-carbide device-based MMC and NPC converter for medium-voltage applications," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 10, no. 1, pp. 856–867, Feb. 2022.

- [17] X. Ding, Y. Zhou, and J. Cheng, "A review of gallium nitride power device and its applications in motor drive," CES Trans. Elect. Mach. Syst., vol. 3, no. 1, pp. 54–64, Mar. 2019.

- [18] Y. P. Siwakoti, A. Mahajan, D. J. Rogers, and F. Blaabjerg, "A novel seven-level active neutral-point-clamped converter with reduced active switching devices and DC-Link voltage," *IEEE Trans. Power Electron.*, vol. 34, no. 11, pp. 10492–10508, Nov. 2019.

- [19] H. Tian, Y. Li, and Y. W. Li, "A novel seven-level hybrid-clamped (HC) topology for medium-voltage motor drives," *IEEE Trans. Power Electron.*, vol. 33, no. 7, pp. 5543–5547, Jul. 2018.

- [20] I. Md Rabiul, G. Youguang, and J. G. Zhu, Power Converter Topologies for Grid-Integrated Medium-Voltage Applications. Berlin, Germany: Springer, 2014.

- [21] K. Ramani, D. Krishnan, and A. Rathinam, "High performance of sinusoidal pulse width modulation based flying capacitor multilevel inverter fed induction motor drive," *Int. J. Comput. Appl.*, vol. 1, pp. 116–121, Feb. 2010.

- [22] Y. P. Siwakoti, S. Liese, A. Mahajan, A. Palanisamy, D. Rogers, and F. Blaabjerg, "A new seven-level active boost neutral point clamped (7L-ABNPC) Inverter," in *Proc. IEEE Energy Convers. Congr. Expo.*, 2018, pp. 5636–5642.

- [23] H. Tian and Y. W. Li, "An active capacitor voltage balancing method for seven-level hybrid clamped (7L-HC) converter in motor drives," *IEEE Trans. Power Electron.*, vol. 35, no. 3, pp. 2372–2388, Mar. 2020.

- [24] G. Chen, A. Bahrami, and M. Narimani, "A new seven-level topology for high-power medium-voltage application," *IEEE Trans. Ind. Electron.*, vol. 68, no. 1, pp. 37–46, Jan. 2021.

- [25] W. Sheng and Q. Ge, "A novel seven-level ANPC converter topology and its commutating strategies," *IEEE Trans. Power Electron.*, vol. 33, no. 9, pp. 7496–7509, Sep. 2018.

- [26] M. di Benedetto, A. Lidozzi, L. Solero, F. Crescimbini, and P. J. Grbović, "Symmetrical three-phase seven-level E-type inverter for PV systems: Design and operation," *IET Renewable Power Gener.*, vol. 14, pp. 2852–2863, 2020.

- [27] F. Z. Peng, "A generalized multilevel inverter topology with self-voltage balancing," *IEEE Trans. Ind. Appl.*, vol. 37, no. 2, pp. 611–618, Mar./Apr. 2001.

- [28] H. Akagi, "Multilevel converters: Fundamental circuits and systems," Proc. IEEE, vol. 105, no. 11, pp. 2048–2065, Nov. 2017.

- [29] P. Kant and B. Singh, "Multipulse converter fed new 7-level cascaded multilevel inverter based induction motor drive," in *Proc. 2nd Int. Conf. Power, Control Comput. Technol.*, 2022, pp. 1–6.

- [30] S. K. Giri, S. Chakrabarti, S. Banerjee, and C. Chakraborty, "A carrier-based PWM scheme for neutral point voltage balancing in three-level inverter extending to full power factor range," *IEEE Trans. Ind. Electron.*, vol. 64, no. 3, pp. 1873–1883, Mar. 2017.

**ALESSANDRO LIDOZZI** received the Electronic Engineering and Ph.D. degrees from Roma Tre University, Rome, Italy, in 2003 and 2007, respectively.

From 2010 to 2017, he was a Researcher with the Department of Engineering, ROMA TRE University, where he has been an Associate Professor since 2017. His research interests mainly include power converter modeling and control, control of permanent magnet motor drives, control aspects for power electronics in diesel-electric generating

units, four-leg converters, and development of high-performance control platforms based on combined DSP-FPGA systems. He is an Associate Editor for IEEE TRANSACTION ON INDUSTRY APPLICATIONS.

verter topologies.

**MARCO DI BENEDETTO** (Member, IEEE) received the M.Eng. degree in electronic engineering from the University of Roma TOR VERGATA, Rome, Italy, in 2014, and the Ph.D. degree in mechanical and industrial engineering from ROMA TRE University, Rome, in 2018.

Since November 2018, he has been a Research Fellow with the Center of Power Electronics and Drives (C-PED), ROMA TRE University. His research interests mainly include hardware and FPGA control design for multilevel power con-

**THIERRY A. MEYNARD** received the graduation degree from the Ecole Nationale Supérieure d'Electrotechnique, d'Electronique, d'Hydraulique de Toulouse, Toulouse, France, in 1985.

He became a Doctor with the Institut National Polytechnique de Toulouse, Toulouse, France, in 1988, and was an invited Researcher with the Université du Québec à Trois Rivières, Trois-Rivières, QC, Canada, in 1989. In 1990, he joined the Centre National de la Recherche

Scientifique (CNRS)as a Full-Time Researcher, and was the Head of Static Converter Group from 1994 to 2001. From 2010 to 2018, he was the Associate Director of the National Program Three-Dimensional Power Hy-brid Integration. He is currently the Directeur de Recherches CNRS with the LAPLACE, but in parallel he has been also involved in several industry-related activities. He was a Part-Time Consultant with Cirtem from 2000 to 2016. In 2016, he cofounded and became a Scientific Advisor with the Company Power Design Technologies that develops PowerForge, software for design of two-and multilevel power converters, and the consulting company EIRL Thierry Meynard was created to help theoretical knowledge to become industrial products in January 2020. His research interests include series and parallel multicell converters, magnetic components, and development of design tools for power electronics.

Dr. Meynard is a coinventor of several topologies of multilevel converter used by ABB, Alstom, Cirtem, General Electric, Schneider Electric, such as Flying capacitor, Stacked MultiCell, 5LANPC, AC/AC chopper, and xPlexed choppers.

**LUCA SOLERO** (Senior Member, IEEE) received the Electrical Engineering degree from the University of Rome La Sapienza, Italy, in 1994.

Since 1996, he has been with the Department of Engineering, University ROMA TRE where he currently is a Full Professor of charge of teaching courses in the fields of power electronics and industrial electric applications. His research interests include power electronic applications to electric and hybrid vehicles and to distributed power and renewable energy generating units. He has been

the Chair of IEEE-IAS Industrial Power Converters Committee IPCC during 2020–2021. Since 2022, he has been the Vice-Chair the IEEE IAS Industrial Power Conversion Systems Department IPCSD. He is an Associate Editor for IEEE TRANSACTION ON INDUSTRY APPLICATIONS.

Prof. Solero was the recipient of two IEEE IAS IPCC Prize Paper Awards. He is a Member of the IEEE INDUSTRIAL ELECTRONICS, IEEE INDUSTRY APPLICATIONS, and IEEE Power Electronics Societies.

Open Access provided by 'Università degli Studi Roma Tre' within the CRUI CARE Agreement