Received 26 September 2022; revised 27 October 2022; accepted 1 November 2022. Date of publication 4 November 2022; date of current version 18 November 2022. The review of this article was arranged by Associate Editor Thomas I. Strasser.

Digital Object Identifier 10.1109/OJIES.2022.3219607

# A Survey on FEC Techniques for Industrial Wireless Communications

LORENZO FANARI <sup>10</sup> (Graduate Student Member, IEEE), ENEKO IRADIER <sup>10</sup> (Member, IEEE), IÑIGO BILBAO <sup>10</sup> (Graduate Student Member, IEEE),

RUFINO CABRERA <sup>10 1</sup> (Graduate Student Member, IEEE), JON MONTALBAN <sup>10 1, 2</sup> (Senior Member, IEEE), PABLO ANGUEIRA <sup>10 1</sup> (Senior Member, IEEE), OSCAR SEIJO <sup>10 3</sup> (Member, IEEE), AND IÑAKI VAL <sup>10 3</sup> (Senior Member, IEEE)

CORRESPONDING AUTHOR: LORENZO FANARI (e-mail: lorenzo.fanari@ehu.eus).

This work was supported in part by the Basque Government under Grant IT1436-22, in part by the PREDOC under Grant PRE2019\_099407, in part by the Spanish Government through project PHANTOM (MCIU/AEI/FEDER, UE) under Grant RTI2018-099162-B-100 and through project THERESA under Grant PID2021-124706OB-100 funded by MCIN/AEI/10.13039/501100011033 and by ERDF A way of making Europe, and in part by the Basque Government through project VIRTGRID under Grant Elkartek KK-2022/00069.

ABSTRACT Industry 4.0 aims to digitize industrial processes entirely, and wireless technologies represent one of the enablers for scalable and flexible communications. However, the current standards and proprietary solutions do not meet the industry's tight requirements in fundamental use cases such as factory automation (FA). One of the key research challenges toward replacing wired fieldbuses with wireless links is the design of techniques that enable real-time and deterministic behavior when transmitting short packets. Forward error correction (FEC) techniques are critical to this objective, and coding/decoding algorithms must comply with reliability and low latency specifications. This article surveys existing FEC techniques for short packet transmissions. Compared to other survey papers in the field, we propose several FEC candidate techniques specifically suitable for FA wireless systems. We explore four of these techniques, also examining hardware architecture proposals. This article proposes a methodology to evaluate their latency and reliability performance. We finally discuss the lessons learned and challenges for future research.

**INDEX TERMS** Complexity, factory automation (FA), forward error correction (FEC), industrial wireless communications, Industry 4.0, latency, PHY, reliability, short packet transmission, wireless communications.

| <b>ARRKEAIVI</b> | IONS USED IN THIS ARTICLE                       | BPSK     | Binary phase-shift keying.                |

|------------------|-------------------------------------------------|----------|-------------------------------------------|

| 3GPP             | 3rd Generation Partnership Project.             | B-DMC    | Binary-input discrete memoryless channel. |

| 5G NR            | 5G New Radio.                                   | BER      | Bit error rate.                           |

| AR3A             | Accumulate-Repeat-3-Accumulate.                 | BLER     | Block error rate.                         |

| AR4JA            | Accumulate-Repeat-by4-Jagged-Accumulate.        | BCH      | Bose-Chaudhuri-Hocquenghem.               |

| AWGN             | Additive white Gaussian noise.                  | BPM      | Burst position modulation.                |

| ASIC             | Application specific integrated circuit.        | CVA      | Circular Viterbi algorithm.               |

| ASIP             | Application-specific instruction set processor. | CCSDS    | Consultative committee for space data     |

| ATSC             | Advanced Television Systems Committee.          |          | systems.                                  |

| ARQ              | Automatic repeat request.                       | CC       | Convolutional codes.                      |

| BM               | Base matrix.                                    | CA-Polar | CRC-aided polar.                          |

| BP               | Belief propagation.                             | CRC      | Cyclic redundancy check.                  |

|                  |                                                 |          |                                           |

Department of Communications Engineering, University of the Basque Country (UPV/EHU), 48012 Bilbao, Spain

Department of Electronic Technology, University of the Basque Country (UPV/EHU), 48012 Bilbao, Spain

Ikerlan Technology Research Centre, Basque Research and Technology Alliance (BRTA), 20500 Arrasate, Spain

DVB-S2 Digital Video Broadcasting - Satellite - Second

Generation.

DVB-T2 Digital Video Broadcasting - Second Genera-

tion Terrestrial.

DSSS Direct sequence spread spectrum.

E2E End-to-end latency. FA Factory automation.

FPGA Field programmable gate arrays.

FEC Forward error correction.

GPU Graphics processing unit.

HART Highway addressable remote transducer proto-

col.

HARQ Hybrid automatic repeat request.

HAR2D-FI Hybrid channel Access with redundancy for re-

liable and deterministic Wi-Fi.

IEC International Electrotechnical Commission.

ISM Industrial Medical Scientific Band. ISA International Society of Automation.

LDPC Low density parity check. LLR Logarithmic likelihood ratio.

LTE Long-term evolution.

LT Luby transform.

MAP Maximum *a posteriori*.

MediaFLO Media forward link only.

MAC Medium access control layer.

MBMS Multimedia broadcast multicast services.

NASA National Aeronautics and Space Administra-

tion.

OMNET++ Objective Modular Network Testbed in C++.

OSI Open systems interconnection model.

OSD Ordered statistics decoding.

OFDMA Orthogonal frequency-division multiple access.

OFDM Orthogonal-frequency division multiplexing.

PER Packet error rate.

PLR Packet loss rate.

PCCC Parallel concatenated convolutional codes.

H Parity check matrix. PHY Physical layer.

PPDU Physical layer protocol data unit.

PAC Polarization-adjusted convolutional codes.

PEG Power edge growth.

PA Process automation.

QPSK Quadrature phase-shift keying.

QC Quasi-cyclic.

RAN Radio access network.

RS Reed–Solomon.

SCCC Serial concatenated convolutional codes.

SNR Signal-to-noise ratio.

SDR Software-defined radio.

SVC Sparse vector code.

SCE Suggestive gangellation

SCF Successive cancellation flip. SCL Successive cancellation list.

SHARP Synchronous and hybrid architecture for real-

time performance.

TBCC Tailbiting convolutional codes.

TDMA Time-division multiple access.

TPC Turbo product codes.

URLLC Ultrareliable low latency communications.

UWB Ultrawideband.

UMTS Universal mobile telecommunications system.

USRP Universal software radio peripherals.

WirelessHP Wireless high-performance.

WIA-FA Wireless networks for industrial automation-

dactory automation.

WPAN Wireless personal area network.

WiMAX Worldwide interoperability for microwave ac-

cess.

WAVA Wrap-around Viterbi algorithm.

ZTBCC Zero tailbiting convolutional codes.

### I. INTRODUCTION

The fourth industrial revolution, also referred to as Industry 4.0, is one of the most promising fields where research on information technologies is under development. Its principal goal is to digitalize the entire industrial process. The transition requires the inclusion of the latest communication technologies: wireless networks, tactile internet, Internet of Things, and in general, the optimization of the so-called cyber-physical systems. Wireless communications bring significant advantages to this scenario while posing relevant technological challenges [1].

Regarding the wireless transition, numerous actors from both the industrial world [2], [3], [4], [5], as well as from the standardization committees [6], [7], [8] have established several guidelines for successful wired to wireless transition in a variety of scenarios [4]. Indeed, the industrial world encompasses diverse environments, which differ in applications and environmental properties. Some examples are factory production processes or factory automation (FA), surveillance systems, electricity production assets, transport infrastructure, oil production, chemical material handling, etc. FA is among the most challenging use cases for ad hoc wireless system design and deployment. Contrary to the traditional requirements of generic wireless communications, which entail the transmission of large-size data, FA wireless communications involve the transmission of short data packets with high reliability and reduced latency.

### A. FIELDS OF APPLICATION FOR FA

FA comprises different fields of application that are necessary for the operations of monitoring and controlling in the industrial environment. These processes are distinguishable among critical and noncritical processes. Based on the criticality level of the processes, several layers of the Open Systems Interconnection model (OSI model) have to be adapted [9].

Numerous players from the industrial world [2], [3], [4], [5] and from standardization committees [6], [7], [8] have suggested their use case vision for FA, and defining the desired performance at the MAC layer. However, such guidelines are challenging to accomplish in the case of highly critical or safety communications. Few proposals offer partial solutions

**TABLE 1. Proposed Fields of Application**

| Use case                   | Reliability | Latency         | Payload         |

|----------------------------|-------------|-----------------|-----------------|

|                            | [PER]       | $[\mu s]$       | [B]             |

| Safety<br>communications   | $10^{-9}$   | 0.25-4          | From 6<br>to 24 |

| Critical communications    | $10^{-9}$   | 0.5-20          | From 8 to 1024  |

| Noncritical communications | $10^{-7}$   | Not<br>relevant | Up to 33k       |

that, nevertheless, do not entirely fulfill the required performance range [10]. Table 1 presents a classification of the fields of application for the industrial wireless systems as a function of the link-level requirements. The definition of requirements follows the guidelines of [4], [7]. We have considered three key parameters: payload length, reliability, and latency. Reliability and latency are defined as packet error rate (PER) and end-to-end (E2E) latency. The PER evaluates the correct interpretation of the message, while the E2E latency estimates the time interval between the data generation and its future reception at the MAC layer.

Based on the presented parameters, three prominent fields of application are recognized: Non-critical communications, which include, for example, monitoring operations and involve less stringent requirements. Existing wireless technologies are currently applied in such scenarios. Critical communications demand communication systems designed to protect people, machines, and production processes. Such scenarios denote strict reliability and latency requirements. Finally, the case of safety communications covers all the risk reduction operations associated with personnel and equipment damage prevention and protection. In this case, the communications require extremely low latency data transfer.

### B. WHY FEC?

Optimizing all ISO/OSI layers towards real-time communications [9] is necessary for the demanded performance for FA fields of application. Focusing on the PHY layer, two strategies can be considered [11]. First, the automatic repeat request (ARQ) techniques introduce some check-bits in the transmitted packet for retransmitting the erroneous messages. However, on the other hand, retransmissions introduce undesirable delay during the packet transmission [12]. The other strategy is the FEC. These techniques include some redundancy bits within the packet during transmission. At the receiver, this redundancy allows the detection and error correction of the received message, avoiding the delay effect discussed in the previous case. Consequently, including FEC techniques within the industrial wireless systems has potential benefits for achieving the desired performance in terms of reliability and latency. The requirements have been briefly introduced in Section I-A.

#### C. RELATED WORKS AND CONTRIBUTIONS

### 1) RELATED WORKS

Despite a large body of surveys on FEC for short packet transmissions, only [20] attempts to address some issues related to FA. The majority of the encountered surveys focus on URLLC, which requires different performances related to latency and reliability. However, their results are essential for the development of this topic.

Sybis et al. [13] compare different FEC candidates for 5G URLLC communications, previously identified by 3GPP. Analysis for both reliability and complexity are proposed, considering different decoding algorithms. Liva et al. [14] present a survey of modern codes for short packet transmission. Iscan et al. [15] compare different FEC schemes for 5G URLLC communications. Moreover, different decoding algorithms are included in the study. Wu et al. [27], for short packet communications made with SDR, analyzes different FEC candidates. Tzimpragos et al. [17] review different FEC schemes for 100-Gb/s optical networks. Also, an analysis of the published results is included. Shirvanimoghaddam et al. [18] review the state of the art of the FEC techniques for URLLC. Moreover, a comparison of reliability and decoding complexity analyzes different decoding algorithms. The results are obtained from MATLAB simulations. Qiao et al. [19] compare the performance of numerous FEC within a flexible ASIP decoder. Zhan et al. [20] analyzes FEC candidates for WirelessHP. This work also offers future directions for designing FEC schemes for industrial control applications. Hajiyat et al. [21] compare different candidates for 5G machine-type communications. Shao et al. [22] analyze the published results of the ASIC implementations of different 3GPP FEC techniques. Ahmed et al. [23] in their survey focused on addressing the design for future ARQ schemes, reviews suitable FEC techniques. In [24], Habib et al. study different decoding algorithms for LDPC un the context of Reinforce Learning. Lian et al. compare different decoding algorithms for TBCC and Polar in terms of reliability and complexity [25]. Ferraz et al. [26] analyze and compare numerous decoding algorithms for LDPC addressing issues associated with high-throughput and low energy consumption.

Table 2 outlines the existing survey articles and justifies how these publications differ from this survey article. Nowadays, no surveys in the literature simultaneously review numerous FEC techniques for short packet transmission and address the architectural and design problems of the FEC techniques for FA fields of Application.

### 2) CONTRIBUTIONS

The surveys available in the literature do not address the specific challenges of FA communications. An exception is given by [20], whose main contribution consists of surveying a set of candidate codes, and then, suggesting an *ad hoc* set of architectures. However, this work lacks the analysis of decoding algorithms. To the best of our knowledge, there is no comprehensive survey in the literature about FEC

**TABLE 2.** Related Works

| Author                 | Year | Proposed<br>scenario                        | FEC<br>survey | Decoding<br>survey | Hardware<br>analysis | Reliability comparisons | Decoding<br>latency<br>comparisons | Future<br>challenges<br>for FEC | Future<br>challenges<br>for<br>decoding | Ref  |

|------------------------|------|---------------------------------------------|---------------|--------------------|----------------------|-------------------------|------------------------------------|---------------------------------|-----------------------------------------|------|

| Sybis                  | 2016 | URLLC                                       | Yes           | Yes                | No                   | Yes                     | No                                 | No                              | No                                      | [13] |

| Liva                   | 2016 | Theoretical                                 | Yes           | No                 | No                   | Yes                     | No                                 | No                              | No                                      | [14] |

| Iscan                  | 2016 | Theoretical                                 | Yes           | Yes                | No                   | Yes                     | No                                 | No                              | No                                      | [15] |

| Wu                     | 2016 | High-Throughput<br>Communications           | Yes           | Yes                | Yes                  | Yes                     | No                                 | No                              | No                                      | [16] |

| Tzimpragos             | 2016 | Optical<br>Networks                         | Yes           | No                 | No                   | Yes                     | No                                 | Yes                             | No                                      | [17] |

| Shirvani-<br>moghaddam | 2018 | URLLC                                       | Yes           | Yes                | No                   | No                      | No                                 | Yes                             | Yes                                     | [18] |

| Qiao                   | 2018 | High-Throughput<br>Communications           | Yes           | Yes                | Yes                  | Yes                     | No                                 | No                              | No                                      | [19] |

| Zhan                   | 2018 | High-Throughput<br>Communications<br>for FA | Yes           | Yes                | No                   | Yes                     | No                                 | Yes                             | No                                      | [20] |

| Hajyiat                | 2019 | Machine-type communications                 | Yes           | Yes                | No                   | Yes                     | No                                 | No                              | No                                      | [21] |

| Shao                   | 2019 | Broadband<br>Communications                 | Yes           | Yes                | Yes                  | No                      | No                                 | No                              | Yes                                     | [22] |

| Ahmed                  | 2021 | URLLC                                       | Yes           | No                 | No                   | No                      | No                                 | No                              | No                                      | [23] |

| Habib                  | 2021 | Reinforce<br>Learning                       | No            | Yes                | No                   | Yes                     | No                                 | No                              | No                                      | [24] |

| Lian                   | 2021 | Theoretical                                 | No            | Yes                | No                   | Yes                     | No                                 | No                              | No                                      | [25] |

| Ferraz                 | 2021 | High-<br>Throughput<br>Communica-<br>tions  | Yes           | Yes                | Yes                  | Yes                     | No                                 | No                              | Yes                                     | [26] |

| This article           | 2022 | FA                                          | Yes           | Yes                | Yes                  | Yes                     | Yes                                | Yes                             | Yes                                     |      |

techniques for FA wireless systems that address at the same time reliability and latency aspect. Moreover, existing surveys neither consider theoretical nor hardware implementation results.

The main contributions of this article are summarized as follows.

- A comprehensive taxonomy of several FEC techniques developed for short packet communications. These techniques are classified into block and memory codes, and their features are collected and compared in a table. The features are associated with the requirements of the FA use cases. The best-performing FEC techniques are considered as candidates.

- 2) For each candidate, several decoding architecture proposals are compiled and analyzed. The gathered results have been found from the information-theoretic and technique-oriented literature. Moreover, we compare those contributions by using reliability and latency metrics. Some examples are BLER and the number of required clock cycles.

- 3) As the results of the previous contributions, the authors provide some metrics for evaluating the FEC performance within FA wireless systems. Finally, the suggested metrics are used to benchmark the candidates.

- 4) Some lessons learned and future challenges are outlined.

### D. ARTICLE OUTLINE

The rest of this article is organized as follows. Section II describes the research method adopted for the proposed literature review. Section III briefly describes FEC and defines the metrics analyzed in this survey. Section IV offers state-of-the-art of several FEC techniques suitable for short packet communications focusing on FA. Section V reviews the industrial wireless systems proposed, analyzing their FEC. This Section also includes the candidates detected by the authors in Section IV. Section VI collects the performance of several candidate hardware implementations and compares them. Section VII offers reliability and latency comparisons based

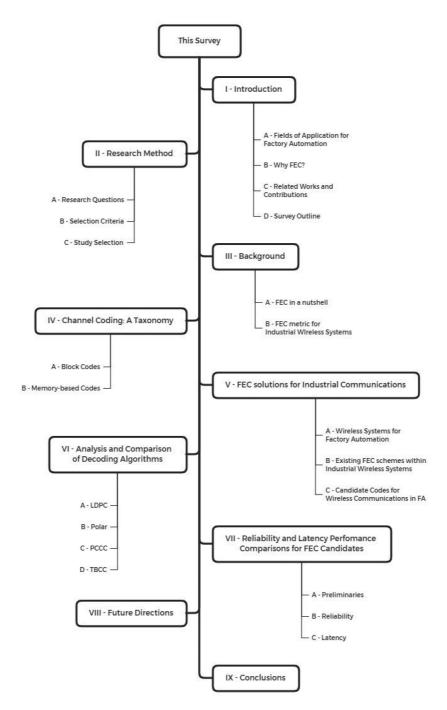

FIGURE 1. Survey structure.

on simulations and published results for the detected candidates. Section VIII contains the future challenges detected by this study. Finally, Section IX concludes this article. Fig. 1 offers an outline of the survey content.

### **II. RESEARCH METHOD**

This study proposes a systematic literature review approach for reviewing the articles encountered in the considered databases. PRISMA is the guideline followed [28]. This

methodology comprises four main steps: issue detection and preliminary studies, collection of articles and reports, data extraction, and data inclusion. The first step aims to identify research questions, and therefore, the objectives. More in detail, this is the stage where the selection procedure of the article, keywords formulation for research and search queries, and the quality assessment criteria of extracted studies are defined. The subsequent step consists of using the keywords for the queries in the databases. The results are then collected

### **TABLE 3.** Research Question for This Survey

| # | Research Question                                                  |

|---|--------------------------------------------------------------------|

| 1 | Which are the main goals in the design of wireless systems for FA? |

- Which are the traditional and modern FEC techniques for short packet communications proposed by the literature?

- What are the application areas in wireless communications for short-packet communications?

- 4 What are the various metrics for evaluating the FEC for industrial communications, particularly for FA?

- 5 Which FEC techniques are commonly used in industrial communications?

- 6 Which decoding algorithms are to consider for fulfilling the FA requirements?

**TABLE 4.** Selected Keywords for This Survey

| Group 1: FA-and URLLC related keywords       | FA OR URLLC OR Reliability OR Latency OR Decoding Complexity OR Industry4.0 OR Industrial Communications |

|----------------------------------------------|----------------------------------------------------------------------------------------------------------|

| Group 2: FEC related keywords                | Block Codes OR Convolutional Codes OR Non Linear Block Codes OR LDPC OR                                  |

| Of our 2. The related key words              | Polar OR Turbo OR Sparse Vector Codes OR TBCC OR QC LDPC                                                 |

| Group 3: Decoding algorithm related keywords | Belief Propagation OR Successive Cancellation List OR Viterbi OR Sphere OR                               |

| Group 3. Decoding argorithm related keywords | OSD OR Full Parallelism OR Parallelism OR MINSUM OR FPGA OR ASIC                                         |

| Group 4: Wireless Systems related keywords   | IEEE 802.11 OR IEEE 802.15.4 OR 5G New Radio                                                             |

| Search Query                                 | (Group 1) AND (Group 2) AND (Group 3)                                                                    |

| Scarcii Query                                | OR (Group 1) AND (Group 2) OR (Group 1) AND (Group 4)                                                    |

in Zotero©, a software for managing bibliographic data and generally research materials encountered in databases or manually added.

### A. RESEARCH QUESTIONS

This study suggests FEC techniques for wireless systems for industrial environments like FA. Moreover, several guidelines are provided to the audience for designing *ad hoc* PHY layers for future industrial wireless systems proposals. For this aim, six research questions have been considered (see Table 3).

### **B. SELECTION CRITERIA**

After defining the objectives for this work, the databases are selected for the subsequent analysis. For this aim, the following databases have been considered IEEE Xplore, Google Scholar, and the 3gpp-database. This last collects many technical reports associated with FEC implementation for URLLC scenarios, which show similarities with FA.

Then, a list of keywords for the queries is generated as shown in Table 4. These are organized into four groups. The first contains the FA-related keywords, and the second includes FEC-related keywords. In contrast, the decoding algorithm-related keywords are grouped in the third group. Finally, Group 4 collects the keywords associated with industrial wireless systems.

Moreover, the articles selected are published in English and indicate a minimum of one citation. The result is a collection of documents published in English that covers more than 60 years of contributions associated with "FEC for short-packet communications."

### C. STUDY SELECTION

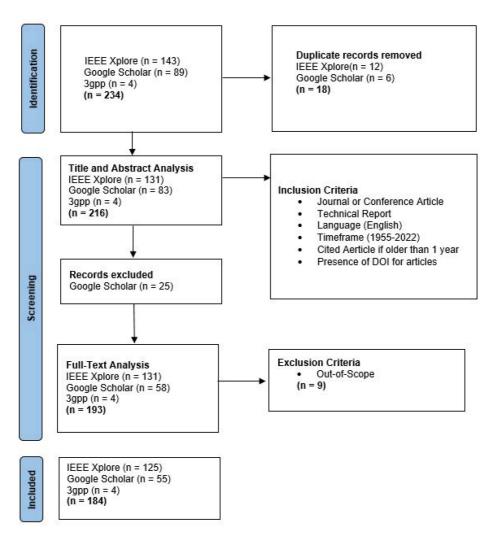

Fig. 2 resumes the decision steps for including the articles in this work.

Initially, the research shows a total of 234 articles and technical reports to be analyzed. Among these, 18 were excluded as copies. Therefore, the amount passes to 216.

Then, the study passes to the screening phase, which consists of an initial examination of the title and abstract, followed by a full-text analysis. During the first step, the number of articles was reduced to 192, and subsequently, they passed to 184. The excluded manuscripts did not show any element for this scope. In this case, there are no explanations of the methodology proposed or the absence of comparable results. Consequently, this survey considers a total of 184 documents divided into academic articles and technical reports.

### III. BACKGROUND

This section presents a brief definition of FEC and the PHY-layer metrics proposed for analyzing the different FEC techniques presented in this work. According to the authors, this section aims to familiarize the general reader with the content proposed in this article.

### A. FEC IN A NUTSHELL

In 1948, Shannon [29] proved that the error-free transmission of data is achievable in communication channels affected by noise. He demonstrated that the reliability is achievable in these scenarios by transmitting the data with a code rate R lower than the channel capacity, also known as Shannon limit.

The FEC techniques are one of the common approaches to this problem. It consists of applying some redundancy to the

FIGURE 2. Selection criteria based on PRISMA.

data, which will be transmitted through the communication channel, with a determined code rate R. R is the ratio between the original data size of K bits and transmitted data of size N, where N > K. This redundancy helps the receiver detect and correct some corrupted bits within the transmitted data.

Ideally, the Shannon limit tends to infinity, and consequently, it is much easier to analyze the performance of FECs in the case of large packets [30]. Consequently, more assumptions are needed to evaluate FECs in short packet communications. In [31] a solid theoretical bound is proposed for the evaluation of FEC within short packet communications.

### B. FEC METRICS FOR INDUSTRIAL WIRELESS SYSTEMS

### 1) RELIABILITY

Industrial wireless systems require high reliability during the transmission of short data. A transmission failure could affect critical aspects of the manufacturing processes associated with safety, equipment, and machinery integrity. The error rate is a metric strictly related to the probability of transmission failure. Its measurement in these particular environments is

defined at PHY or MAC layers and offers the rate of successfully delivered bits or packets.

The error rate metrics described in this section are used to evaluate the industrial wireless systems performance, where the desired performances are achievable using FEC and retransmission techniques. Some examples are bit error rate (BER), block error rate (BLER), packet error rate (PER), packet loss rate (PLR), and connection error rate (CER). The terms BLER, PER, and PLR are interchangeable in these scenarios. Commonly, BLER is associated with 5G NR, while PER for IEEE 802 standards for both PHY and MAC layer. PLR only refers to MAC-layer performances. CER evaluates the reliability performance in the presence of multiple connections among devices, and thus, is not included in this study.

Three main metrics have been detected and defined. BER is commonly used to evaluate the decoding performance at the PHY layer, indicating the probability of an erroneous bit transmission. BLER is defined exclusively at the PHY layer and represents the ratio between the erroneous packets received and the totality of transmitted packets. Finally, PLR considers

the erroneous transmission in the case of contiguous packets, evaluating the reliability at the MAC layer.

In [20], the authors compare the BER/BLER of different FEC candidates for high-throughput communications within factories, resulting from previous studies. While in [32], BER is used as a threshold for testing the WirelessHP PHY layer with different low-order modulations at different communications distances. A BLER threshold is defined in [33] to compare different FEC candidates' performance with the IEEE 802.11be PHY layer, assuming different industrial channel models. In [34], [35], and [36], BLER and PLR are an upper bound for testing the IEEE 802.11 PHY layer performance assuming deterministic protocols.

Generally, in industrial communications and FA, a system is considered reliable if it provides only one communication failure during thousand years [7]. This assumption is based on the recommendation IEC 61784, where the communication failure should compose at most 1% of the Mean time to failure, in this case of thousand years [37].

A communication failure is caused when the receiver lacks the correct packet reception, and this depends on one of the three following events.

- 1) The receiver does not receive the packet.

- 2) The received packet contains erroneous bits.

- 3) The packet is received outside the latency requirement.

Among the different metrics used for the reliability estimation, PER and BLER provide error rate values assuming the communication failure. Nevertheless, only BLER is focused on evaluating the performance at the PHY layer, and thus, is recommendable for evaluating the FEC techniques. For fair comparisons between different BLER results shown in different publications, additional elements such as SNR, channel typology, and channel properties must be included in the analysis.

### 2) LATENCY: DECODING LATENCY

In industrial communications, latency is generally expressed as cycle time [4], [7], [36]. This metric expresses the latency between the data transmission and its reception. Three main processes affect this metric. The first one is the transmitter latency, which expresses the time elapsed between the data available at the MAC layer and its subsequent transmission by the PHY layer. Coding and modulation processes are parts of this period. Second, propagation latency represents the associated delay of the channel. Finally, the receiver latency considers the required time for demodulation and decoding. Moreover, for the criticality of the processes involved within the industrial environment, cycle time is commonly bounded by a maximum value  $T_{\rm max}$ , which is half of the update rate period of the sensors and actuators included in the network [7].

An accurate estimation of the impact of the FEC on the latency performance of the wireless system is a complex measurement. Different and uncorrelated factors must be considered, such as the decoder architecture, the programming language, the interpretation of the algorithm's pseudocode,

and the hardware performance. In consequence, the comparison among different proposals is not straightforward.

FEC contributes notably to the receiver decoding latency [22]. In many works, it is described as the ratio between the clock cycles required by the decoding latency and the clock frequency of the hardware used for the implementation [33], [38], [39]

Decoding Latency =

$$\frac{\text{Required Clock Cycles}}{\text{Decoder Clock Frequency}}.$$

(1)

#### IV. CHANNEL CODING: A TAXONOMY

The literature includes many examples of FEC techniques suitable for short packet communication scenarios, and such choices have risen over the years. FEC can be addressed as memory-based and memoryless FEC (or Block Codes). This section aims to provide a state-of-the-art of them, moreover suggesting some FEC candidates for FA wireless systems.

#### A. BLOCK CODES

Block codes are a class of FEC in which the data stream turns into a block of K bits; subsequently, by using a generating matrix, further N-K bits, known as redundancy bits, have been included. The code rate  $R=\frac{K}{N}$  specifies the number of these bits.

A primary classification proposed for these techniques consists of distinguishing between linear and nonlinear techniques. Linear block codes are less complex than nonlinear ones and offer commonly good decoding performances. The nonlinear block codes are characterized by a very high complexity that does not allow their consideration in low latency communications nowadays [40]. On the contrary, the respective counterpart shows many applicative examples in numerous standards.

The linear block codes can be classified as a function of the generating matrixes and attainable performance. On this basis, the linear block codes are grouped as follows: LDPC, algebraic, fountain, and compressive sensing based. Table 5 compares the block code techniques using reliability in short packet regime and parallel decoding capability. Parallel decoding is a crucial parameter for achieving the stringent latency requirements for FA.

LDPC codes were discovered by Gallager in the 60s [41], and rediscovered in the late 90s by Mackay and Davey [42]. The remarkable decoding performance of this family have fostered their use in many standards since the first decade of XXI century. Some examples are IEEE 802.11 [43], WiMax [44], 5G NR [45], ATSC3.0 [46], 10GBase-T [47], WiGig [48], DVB-T2 [49], [50], DVB-S2 [51], and Consultative Committee for Space Data Systems (CCSDS) [52]. Generally the LDPC are classifiable into three main subfamilies: Random LDPC [41], Quasi-Cyclic (QC) LDPC [53], and Cyclic LDPC [54], among these QC-LDPC are suitable for communications in FA scenarios; indeed, the possibility of a full parallelization secures low latencies. Nevertheless, QC-LDPC shows error floors in BLER-based

**TABLE 5.** Block Codes and FEC Comparison

| Typology   | Family                          | Subfamily             | Parallel decoding | High reliability in short packet transmission | Ref                   |

|------------|---------------------------------|-----------------------|-------------------|-----------------------------------------------|-----------------------|

| Linear     | LDPC                            | Cyclic                |                   | X                                             | [54]                  |

| Linear     | LDPC                            | Quasi-<br>Cyclic      | X                 | X                                             | [53]                  |

| Linear     | LDPC                            | Random                |                   | X                                             | [41]                  |

| Linear     | Algebraic                       | Hamming               | X                 |                                               | [63]                  |

| Linear     | Algebraic                       | Golay                 | X                 |                                               | [64]                  |

| Linear     | Algebraic                       | Reed<br>Muller        | X                 |                                               | [68]                  |

| Linear     | Algebraic                       | ВСН                   | X                 |                                               | [65]–[67], [69], [70] |

| Linear     | Algebraic                       | 5G-NR                 | X                 | X                                             | [71]                  |

| Linear     | Fountain                        | LT                    | X                 |                                               | [80]                  |

| Linear     | Fountain                        | Raptor                | X                 |                                               | [81]                  |

| Linear     | Fountain                        | Tornado               | X                 |                                               | [82], [83]            |

| Linear     | Compressive<br>Sensing<br>Based | SVC                   |                   | X                                             | [88]–[92]             |

| Non Linear |                                 | Preparata             |                   | X                                             | [94]                  |

| Non Linear |                                 | Kerdock               |                   | X                                             | [95]                  |

| Non Linear |                                 | Delsarte-<br>Goethais |                   | X                                             | [96]                  |

analysis [20] in short packet transmissions. This problem can be partially solved by the combination with CRC [55], [56].

Algebraic codes include a wide set of FEC techniques that, due to their mathematical properties, exhibit two main advantages: easy implementation and generally high decoding performance [20]. WPAN [57], DVB-T [58], DVB-T2 [50], IEEE 802.11ad [59], CCSDS [60], [61], MediaFLO [62], and 5G NR [45] are examples of standards that employ this FEC family. Among the several FEC grouped as algebraic, the authors of this article have identified four main subfamilies: the Hamming codes [63], Golay codes [64], the BCH codes [65], [66], [67], and the Reed–Muller codes [68]. Among the most well-known Algebraic techniques, there are Reed-Solomon (RS) [69], and Gabidulin [70] that belong to BCH, whereas the Reed-Muller subfamily includes the recently developed Polar codes [71]. Regarding the algebraic codes in the short packet regime, on the one hand, their decoding performance worsens [20]. On the other hand, the use of parallel decoding is possible [20]. However, a few exceptions, suitable for short packet transmissions, have been introduced recently in the literature, as the cases of Polar codes [72], [73], [74], and BCH codes with OSD decoding [75]. A negative aspect concerned OSD decoding is the increased decoding latency [75].

Fountain codes were introduced in the late 90s by Bayers et al. [76] to propose an efficient solution in multicast communications, in particular, to enhance the efficiency of ARQ [77]. Indeed standards employed in multicast and broadcast communications, such as 3GPP MBMS [78], and ATSC3.0 [79] use these FECs. The large number of Fountain techniques developed over the years can be categorized into three main subfamilies: the LT codes [80], the Raptor codes [81], and the Tornado codes [82], [83]. Fountain codes present a high complexity [84] which prevents their use in URLLC and especially for FA [20]. However, recent versions of Fountain have been proposed for URLLC scenarios, such as in [85] and [86], where the transmission scheme is significantly simplified. The proposed scheme in [86] does not offer error floors for BLER values below  $10^{-7}$ .

Sparse vector codes (SVC) are a novelty within the world of FEC techniques. Based on compressive sensing [87], their studies started around 2017. The first results are promising for ultrasmall values of *K*. In particular, for *K* below 100 bits, they show comparable performance with Polar codes [88], [89],

**TABLE 6.** Memory Codes and FEC Comparison

| Family        | Subfamily     | Parallel decoding | High reliability<br>in short packet<br>transmission | Ref          |

|---------------|---------------|-------------------|-----------------------------------------------------|--------------|

| Turbo         | SCCC          |                   | X                                                   | [103], [104] |

| Turbo         | PCCC          | X                 | X                                                   | [103], [104] |

| Turbo         | TPC           |                   | X                                                   | [105]        |

| Convolutional | No Tailbiting | X                 |                                                     | [97]         |

| Convolutional | ZTBCC         | X                 |                                                     | [101]        |

| Convolutional | TBCC          | X                 | X                                                   | [102]        |

[90]. However, the properties related to their generation matrix show worsened decoding performance at high Code Rates  $(R \le \frac{1}{4})$ . Furthermore, the required representation of data into sparse vector form limited the use of SVC exclusively to ultrasmall K values [88]. Recently, the literature proposed some implementations related to these new techniques: [91] where also is estimated computational complexity, and [92] where are given reliability and decoding latency performance.

Finally, the non-linear block codes provide excellent decoding performance in decoding, but at the cost of a complex hardware implementation [93]. Among the best-known non-linear codes, there are the Preparata codes [94], the Kerdock codes [95], and the Delsarte–Goethals codes [96].

Nevertheless, the recent binarization for Preparata and the Kerdock codes proposed in [40] opens new frontiers for their application within low latency communications.

### B. MEMORY-BASED FEC CODES

Since the 1960s, memory-based codes have been applied in numerous systems. The behavior of these techniques is comparable to a state machine, where the data stream passes through different states. Each state is associated with the value of a memory register of the FEC module. A generator polynomial defines the connection between the registers and the relative operations. The encoding process finishes when the last bit of the data stream passes through. It is possible to distinguish two families among the different techniques: convolutional codes (CC) and turbo codes. Table 6 shows a comparison between these techniques by taking into account the reliability performance in short packet regime and the possibility of parallel decoding.

CC codes were introduced by Elias [97] in 1955. CC consists of the convolution operation between bitstreams containing the data and a bit sequence, resulting from the passage of such data in dedicated shift registers. These later constitute a finite-state machine. Unlike block codes, CC allows faster decoding since the encoding/decoding is enabled after the detection of a bitstream, whereas, in block codes, encoding/decoding requires the entire block bit sequence. Nevertheless, block codes give better decoding performance. Principally for its simplicity, CC has achieved wide success from the sixties; indeed, several standards, such as

IEEE 802.11 [43], DVB-T [58], UMTS [98], LTE [99], CCSDS [61], and the Mars Reconnaissance Orbiter NASA Mission [100] utilize CC techniques. There are two main subfamilies of CC: without padding and with padding. CC without padding requires simpler architectures than the counterpart, and as a consequence, this technique is faster. However, the absence of a padding sequence impacts the decoding performance. Indeed, these techniques provide poor decoding performance during the passage of the first bits of the stream caused by the absence of correlation between the initial and the final state. CC with padding improves the decoding performance by including a known sequence for these states, and consequently, a correlation is provided since the first transmissions. CC with padding can be grouped into zero tailbiting convolutional codes (ZTBCC) and tailbiting convolutional codes (TBCC) [101]. ZTBCC has padding composed of zero bits, which on the one hand, improves the performance. However, this option affects the effective code rate [102]. In TBCC, the initial and final states of the encoder are identical. However, this strategy increases the decoding performance in short packet regimes at the expense of complexity.

Berrou et al. [103] proposed Turbo codes in 1993, one of the best performing codes up to date. They have been incorporated into many standards since 1990s. Examples are LTE [99], WiMAX [44], MediaFLO [62], and the Mars Reconnaissance Orbiter NASA Mission [100]. Generally, the Turbo codes can be grouped into parallel concatenated convolutional codes (PCCC), serial concatenated convolutional codes (SCCC) [103], [104], and turbo product codes (TPC) [105]. PCCC and SCCC present similar performance in terms of complexity and reliability. Comparisons between these two architectures are encountered in both [106] and [107]. The authors in [106] shows the better decoding performance of SCCC for BLER below  $10^{-6}$ . In more detail, SCCC achieves the mentioned performance at 7 dB, assuming the AWGN channel model. On the contrary, [107] suggests the use of PCCC over SCCC analyzing the results of complexity and reliability, assuming a BLER of  $10^{-2}$ , also in this study, under the AWGN channel. Analyzing the Turbo subfamilies, TPC is considered as the most promising from a theoretical analysis standpoint [20]. However, nowadays, no hardware

**TABLE 7.** Wireless Systems for FA

| Year | System            | PHY techniques                     | MAC techniques | FEC              | System p     | erformance  | — Ref.                    |

|------|-------------------|------------------------------------|----------------|------------------|--------------|-------------|---------------------------|

| Icai | System            | 1111 techniques                    | MAC techniques | TEC              | E2E          | PER         | — Kci.                    |

|      |                   |                                    |                |                  | Latency [ms] | TER         |                           |

| 2004 | IEEE<br>802.15.4a | UWB+FEC,<br>PSSS+FEC,<br>DSSS+FEC  | Deterministic  | CC, RS+CC        | < 3          | $10^{-7}$   | [119]                     |

| 2015 | WIA-FA            | DSSS+FEC,<br>PHSS+FEC,<br>OFDM+FEC | TDMA           | CC, LDPC         | 8            |             | [4], [20]                 |

| 2017 | 5G New<br>Radio   | OFDM+FEC                           | TDMA, OFDMA    | LDPC,<br>POLAR   | 2            | $10^{-5}$   | [45], [124], [127], [128] |

| 2017 | WirelessHP        | OFDM+FEC                           | TDMA           | RS+CC, RS,<br>CC | 0.44         | $10^{-6}$   | [4], [32], [125]          |

| 2018 | SHARP             | OFDM+FEC,<br>OFDMA+FEC             | TDMA, OFDMA    | CC               | < 30         | $10^{-7}$   | [10], [36], [118]         |

| 2019 | IEEE<br>802.11ax  | OFDM+FEC,<br>OFDMA+FEC             | OFDMA          | CC, LDPC         | 10-100       | $10^{-5}$   | [112]                     |

| 2020 | IEEE<br>802.15.4z | UWB+FEC                            | Deterministic  | CC               | < 3          | $< 10^{-7}$ | [123]                     |

| TBA  | IEEE<br>802.11be  | OFDMA+FEC                          | OFDMA          | LDPC             | < 1          | $< 10^{-5}$ | [111]                     |

implementations are found in the literature, despite the presence of parallel decoding scheme proposals [108]. Among the three subfamilies, only PCCC has several hardware implementations with parallel decoding architectures, such as [109] and [110].

### V. FEC SOLUTIONS FOR INDUSTRIAL WIRELESS SYSTEMS A. WIRELESS SYSTEMS FOR FA

The literature on wireless communication schemes in FA covers systems based on IEEE 802.11, IEEE 802.15.4, 5G NR, or stand-alone proprietary proposals. Nevertheless, these proposals partially meet the FA requirements as gathered in Table 7.

### 1) IEEE 802 FAMILIES

IEEE 802.11 is a family of standards for WLAN communications initially designed to operate in the 5-GHz Industrial Scientific and Medical (ISM) band, specifically with the IEEE 802.11a release. The 2.4-GHz band was included in the IEEE 802.11b/g. The introduction of IEEE 802.11n incorporates the opportunity of switching between these two options. Finally, the recent release of IEEE 802.11ax, facilitates the operation in the 6-GHz band also [111]. One of the main characteristics of the IEEE 802.11 standard family is the lack of determinism in packet arrival times. This aspect prevents their use for real-time communications, and consequently, does not guarantee a controlled latency required in FA use cases. Another negative aspect regards reliability performance. Existing systems are distant from securing PER values below  $10^{-7}$ .

Regarding the PHY layer design, almost all standard releases use orthogonal frequency-division multiplexing

(OFDM) and FEC techniques. OFDM is related to the waveform structure, and it changes with the typology of application. For example, IEEE 802.11 g proposes OFDM spectra in 20-MHz channels composed of 64 subcarriers (52 data carriers). In turn, IEEE 802.11ax has 256 subcarriers available within the same channel width (234 data carriers).

The first IEEE 802.11 standards had FEC modules based on CCs, while more sophisticated algorithms such as LDPC were introduced as an option in the IEEE 802.11n [112]. LDPC has become mandatory for the first time in the standard IEEE 802.11ax. IEEE 802.11ax introduced additional novelties, such as multiuser communications based on OFDMA and a new PPDU design. The new PPDU design introduced in IEEE 802.11ax is nowadays a candidate for the standardization of the upcoming IEEE 802.11be [113]. This standard, also known as extremely high throughput, apart from focusing on high data rate profiles, also targets ultralow latency communications and is, therefore, a good candidate for industrial environments [113].

The worldwide success of the IEEE 802.11 standards has supported various modifications and deterministic MAC approaches over the last decade. These proposals attempt to provide time-aware scheduling by the use of time-division multiple access (TDMA) techniques at the MAC layer, such as RT-WiFi [114], IsoMAC [115], Priority MAC [116], or the recent HAR2D-Fi [117]. Another proposal for FA is SHARP, which attempts to optimize also the PHY of the IEEE 802.11 releases. It proposes the optimization of the PHY of IEEE 802.11 g, while at the MAC layer, it proposes a TDMA frame [36], [118]. Recent updates of SHARP are proposed in [10], where OFDMA is introduced to improve the latency performance further.

Another IEEE 802 family considered for industrial environments is the IEEE 802.15.4 standard, which focuses on high-density networks and very short-distance communication ranges. IEEE 802.15.4 was initially sketched for operating in the 2.4 GHz, and 868/916 MHz ISM [119] bands. On the contrary to IEEE 802.11 standards, the IEEE 802.15.4 support deterministic communications. The PHY of 802.15.4 includes direct spread spectrum (DSSS), and ultrawideband (UWB) techniques [120], [121]. UWB combines two modulations known as burst position modulation (BPM) and binary phase-shift keying (BPSK). Concerning FEC, IEEE 802.15.4a introduced both CC and RS+CC [122], whereas, in the newest standard IEEE 802.15.4z, only CC [123] has been adopted. Several FA and PA communication systems such as Zig-Bee, WirelessHART, ISA100.11a, and WIA-FA rely on IEEE 802.15.4 PHY.

### 2) 5G NEW RADIO (5G NR)

5G NR is the RAN standard for the 5G mobile network (including the PHY layer), developed by 3GPP for the 5G mobile network, and it was introduced in 2017 in Rel-15 [45]. 5G NR is the first 3GPP standard targeted for several communication scenarios. Indeed, the previous 3GPP standards only have been developed for broadband communications. One of the covered verticals, the URLLC, was designed to cover verticals requiring real-time applications. Among these, FA is considered one of the most demanding scenarios [124]. 5G NR for covering such verticals includes two operative frequency ranges for short and large-distance communications. The first one, known as FR1, includes 410 MHz–7.125 GHz, while the second, the FR2, incorporates the frequencies from 24.250 to 52.600 GHz.

The 5G NR PHY layer design partially meets the FA requirements for many applications. Some current limitations are the subframe length, which duration currently spans to 1 ms. However, this new standard improves previous releases' robustness with a combination of OFDMA/TDMA MAC techniques and FEC techniques, i.e., LDPC and POLAR. Regarding latency improvement, some new approaches have been recently proposed. For example, in [26], simulations have demonstrated that FDMA provides latency of 1 ms, while in [27], 2–3 ms is achieved.

### 3) WIRELESSHP

WirelessHP is a standalone standard proposal for FA applications based on IEEE 802.11 PHY [32], [125]. Initially, the system only operated in the 5-GHz frequency range [32], while for future work, millimeter wave is also being considered, in particular, the 60-GHz license-free band [4]. Regarding the system design, MAC techniques allow for WirelessHP time-aware scheduling, and hence, the achievement of very low latencies, around 0.5 ms. Nevertheless, considering the reliability, such performance has currently been reached up to PER of 10<sup>-7</sup> [126]. The adopted FEC are RS, CC, and RS+CC.

### B. EXISTING FEC SCHEMES WITHIN INDUSTRIAL WIRELESS SYSTEMS

In industrial wireless communications, the use of *ad hoc* FEC is necessary for providing highly reliable communications with reduced latencies. Currently, the most popular schemes applied in these environments are based on RS, CC, LDPC, and Polar. Information about their structure and related published research is provided here.

### 1) WIRELESSHP RS+CC

Several FEC candidates have been considered for the WirelessHP [20]. Among the alternatives, the RS+CC based on [129] and [130] has been adopted for the first laboratory trials focused on the PHY layer [11]. RS is the outer code, while CC is the inner code. There are two main reasons. First, the RS achieves high decoding performance. Second, the concatenation between RS and CC allows high throughput transmission at reduced decoding latencies, considering the Viterbi decoding algorithm.

The FEC has been evaluated considering different configurations. For RS has been proposed two different code lengths, which are 15 and 31 B. The first has been applied for coding data sizes between 9 and 13 B, whereas the other has a range between 19 and 29 B. Three different code rates have been used for the outer code (CC) and are the following: 5/6, 3/4, 2/3.

In [11], these configurations have been adopted for the data transmission between two nodes implemented with two Universal Software Radio Peripherals (USRP), considering a bandwidth of 5 MHz. The better performances have been obtained considering CC (2/3), where low values of PER (below  $10^{-7}$ ) were obtained assuming periods for the packet transmissions less than  $100~\mu s$ .

### 2) IEEE 802.11 CC

The IEEE 802.11 CC is ZTBCC and is based on [131]. A tail bit sequence of 6 bits set at zero is included in the data block before the encoder and is used to improve the decoding performance. The convolutional encoder is designed for offering a default code rate of 1/2. For offering multiple code rate choices, puncturing is applied after the encoding. Two different puncturing modes are included. The first allows 1/2 < R < 5/6, while the other is used for R = 5/6. The use of the Viterbi decoding algorithm allows extremely reduced decoding latencies.

The authors in [36] show the results of SHARP obtained by OMNET++ simulations. These results show that, without the use of retransmissions, IEEE 802.11 CC helps in obtaining PER values less than  $10^{-6}$  for latencies close to  $500 \,\mu s$ .

### 3) 5G NR CA-POLAR

5G NR CA-Polar are used within the 5G NR control channel due to the high decoding performance for short packets. Such performances are improved for coupling the CRC sequence with the information block at the PHY layer. This approach is

twofold. First, they are used for improving the error detection performance. Second, their combination with the SCL decoding algorithm also allows error correction [132].

Multiple data size and code rates are available with 5G NR Polar. Data range from 30 to a maximum of 1024 bits. At the same time, the code rate could vary from 1/5 to 5/6 due to the use of the following rate matching operations: puncturing, shortening, or repetition.

In [33], it is shown that CA-Polar outperforms the IEEE 802.11 CC for data with reduced sizes (in the order of 100 b). Moreover, many SCL decoding proposals based on semiparallelism offer reduced decoding latencies [22].

### 4) 5G NR LDPC

5G NR QC LDPC codes are used for the data transmission and are designed to be applied for many scenarios. Among these, also FA is included. Many advantages are associated with this technique. First, the error floors are detectable for PER values below  $10^{-5}$  for a large set of code rates. Second, reduced decoding latencies due to the high degree of parallelism. The reliability performance is improved for using CRC as outer code, while the block segmentation before the encoding allows significantly reduced latency performances [132].

5G NR QC LDPC offers many data sizes, which vary from less than 100 to 8448 bit. Two base matrices (BMs) are proposed. BM1 is usually applied with large data, while on the contrary is used BM2. Puncturing and shortening are applied to achieve code rate flexibility, varying from 19/20 to 1/5.

In [38], it is shown that due to the parallel decoding, 5G NR QC LDPC could achieve decoding latencies below 1  $\mu$ s for achieving PER values below than  $10^{-5}$ .

### C. CANDIDATE CODES FOR WIRELESS COMMUNICATIONS IN FA

This section proposes FEC candidates for FA scenarios. The choice is based on the techniques proposed in Tables 5 and 6. Among all the analyzed techniques, the choice falls on QC-LDPC, Polar, PCCC, and TBCC, due to their high reliability in short packet regime and the opportunity to implement parallel decoding.

### 1) QC-LDPC

QC-LDPC is a subfamily of LDPC. The linear relationships between the information block with K bits and the one encoded with N bits are defined using a parity check matrix (H). H has dimension  $N \times N - K$ , and it is composed only by elements with one or zero as values. Its principal property is sparsity, which means that most of the matrix element values corresponding to zero, allowing, as a consequence, its representation using the Tanner graph. This graph comprises N nodes, the variable nodes, and further N - K nodes, the check nodes. Comparing QC-LDPC with the other subfamilies, its N presents the quasi-cyclic property, enabling full parallel decoding. Indeed, such property derives from the high sparsity

of the matrix, allowing to divide H into several submatrices. The literature offers two methods for generating H in the case of QC-LDPC. By probabilistic approach such as the Photograph method [53], or based on the power edge growth (PEG) method [133], which is an iterative algorithm used for the graph generation.

The Photograph method consists of repetition techniques applied to a base matrix [134]. The main benefits are high reliability for variable lengths of both *K* and code rate, as demonstrated by the version implemented in 5G NR [135]. The only disadvantage related to the short packet transmissions is the presence of error floors at higher SNR levels. Nevertheless, this problem can be solved by concatenation with CRC [55], [56]. Among the obtained FEC by the Photograph method, there are the *accumulate-repeat-3-accumulate* (AR3A) and *accumulate-repeat-by4-jagged-accumulate* (AR4JA) proposed by the Jet Propulsion Laboratory [136], [137].

The second proposal, the PEG method, is an iterative form for generating H, which aims to establish connections between the Tanner Graph nodes. These iterations produce girth maximization, which allows high-decoding performance in short packet communications. The term girth defines the largest cycle in the Tanner Graph. For more details about the algorithm, see [77]. However, their performance tends to deteriorate as the size of the information increases. The QC-PEG-LDPC have been considered as potential candidates in 5G NR for URLLC [13] assuming K of 40 and 200 bits. The results recognize benefits by using this method in the 40-bit case. In [135], the authors recommend the use of the PEG within the QC-LDPC structure adopted in 5G NR for ensuring a better performance in the short packet regime. Table 8 summarizes the main features of the proposed methodologies. Among them, this article recommended the use of the photograph within FA wireless systems. Indeed, high-reliability performance occurs for a wider variety of data sizes, and code rates respect the PEG method.

### 2) POLAR

Polar codes were designed in the late 2000s by Arikan [138], providing for the first time a FEC technique able to achieve the channel capacity. The main feature of Polar is the use of binary-input discrete memoryless channels (B-DMC) W, where a method known as channel polarization is applied. Channel polarization splits W into a perfect channel and a noisy channel, allowing the transmission of the K information through the perfect channels. At the same time, the redundant N-K bits pass along the noisy channels. The noisy channel bits are known as Frozen bits. Such sequence is also known to the receiver. Then, a generator matrix G encodes the generated data vector.

Early Polar results did not provide the expected performance [143], in particular in the short packet regime [72]. This problem was solved by the use of concatenation techniques. There are currently two proposals, one consists of

**TABLE 8.** Encoding Methodologies

| Candidate | Method             | General advantages                                       | General disadvantages                                    | Ref.      |

|-----------|--------------------|----------------------------------------------------------|----------------------------------------------------------|-----------|

| QC-LDPC   | PEG                | High reliability for reduced payload size                | Reduced reliability from payload sizes>200 b             | [133]     |

| QC-LDPC   | Photograph         | High reliability for every payload size                  | CRC concatenation is required in Short Packet Regime     | [53]      |

| Polar     | Arikan's Polar     | High Decoding Performance for large packets              | Poor decoding performance for short packet transmissions | [138]     |

| Polar     | CA-POLAR           | High decoding Performance for short packet transmissions | More latency than Arikan's Polar                         | [72]–[74] |

| Polar     | PAC POLAR          | High decoding Performance for short packet transmissions | Actually no hardware implementations are published       | [139]     |

| PCCC      | Narayan's<br>Model | Reduced Complexity                                       | Poor decoding performance,<br>High latency               | [140]     |

| PCCC      | Souza's Model      | Reduced Complexity                                       | Poor decoding performance                                | [141]     |

| PCCC      | LTE Encoder        | High decoding performance                                | High complexity                                          | [142]     |

| CC        | TBCC               | High Decoding Performance                                | High Complexity                                          | [102]     |

| CC        | ZTBCC              | High decoding performance,<br>Reduced Complexity         | Reduced Code Rate                                        | [102]     |

concatenation with CRC, known as CRC-aided Polar (CA-POLAR) [72], [73], [74], while the other proposes CC and is known as PAC [139]. Recently, in [144] and [145], an optimal Polar code design for industrial environments is presented.

The high performance achievable by CA-POLAR codes allows its consideration within the design of wireless systems for FA communications. As observable in Table 8, such techniques offer, on the one hand, high reliability in short packet regime, and there are hardware implementations with encouraging results.

### 3) PCCC

PCCC codes are a subfamily of Turbo codes [103]. The encoder is designed to connect two convolutional encoders, which produces the parity bits. In addition, a puncturing block ensures the encoding for several code rates. The PCCC encoder includes one or more interleaving blocks to improve the decoding performance. In a survey on Turbo Coding for HARQ, Chen et al. [146] identifies three main Turbo Encoders: Narayanan model [140], Souza model [141], and LTE Turbo encoder [142], which differ in the number and placement of interleaves.

The Narayan model foresees the use of two interleavers: one placed before the encoders and the other before the second encoder. The Souza model involves using a single interleaved set before the second encoder. However, these models do not show successful decoding during the first frames transmission [146]. In the LTE Turbo model, four interleavers solve this issue, the first one placed between the two parallel encoders and the others in correspondence with the systematic bit sequence and the obtained parity bits. Moreover, LTE Turbo presents a circular buffer that solves the decoding problems encountered in the other models.

Table 8 summarizes the main features of the encoder models for PCCC. Among the proposals, LTE turbo shows better

decoding performances compared with its counterparts, and for this reason, the authors propose this model as a candidate.

### 4) PADDED CC

CC with padding reduces the typical high decoding probability that occurs during the first data stream transmitted [102]. Two main padding strategies permit the distinction of this subfamily into TBCC and ZTBCC. TBCC requires that encoder and decoder structures have the same initial and final states. Consequently, the padding sequence is included in the encoded block, showing benefits in the decoding performance, particularly for short packet transmissions, moreover avoiding the code rate loss, defined as follows:

$$R = \frac{K}{N + \text{padding bit}}.$$

(2)

In ZTBCC, the padding is an additional element of the encoded stream. The decoded block is composed of stream and padding bits in this case. This structure affects the code rate described as follows:

$$R = \frac{K}{N}. (3)$$

Table 8 summarizes the main features of the models of CC with padding. Among these models, the authors recommend using the TBCC codes for their high decoding performance in the short packet regime and the absence of code rate loss.

## VI. ANALYSIS AND COMPARISON OF DECODING ALGORITHMS

As highlighted in previous sections, the integration of FEC techniques can be a crucial element for guaranteeing the performance of wireless systems in FA use cases. One reason is associated with the properties of the propagation channels in industrial environments. The high time coherence of industrial

propagation channels makes the use of some MAC layer techniques useless, such as time retransmission techniques [34]. The usage of robust FEC techniques could improve the MAClayer performance [144], [145]. The FECs are techniques that detect and correct the erroneous bit included in the received data. Many propagation effects correlated to the channel models cause these errors during the data transmission, such as noise, interference, and fading. Among these, fading is particularly critical within industrial environments. More specifically, the encoder located in the transmitter converts a block of K information bits into a longer block of N bits, which contains N-K redundant bits. Such redundancy helps the decoding architecture, located in the receiver, detect and correct the erroneous bits. After these corrections, the original K information is ultimately reconstructed. The literature offers numerous decoding architecture proposals to obtain specific reliability, latency, or energy consumption goals. For example, faster decoding is typically allowed by a low complex structure despite the expense of reliability. Commonly, many industrial scenarios, such as process automation, adopt low-complex decoding architectures. In these cases, high density node networks are required to control and monitor the processes, where the nodes must communicate fast and at the same time, maintain a reduced energy consumption. On the contrary, the FA processes demand complex decoding architectures to meet the strict requirements of the use cases. High reliability and low latencies are achievable with decoding architectures that include a high level of parallelism and sophisticated decoding algorithms [20]. To further improve the reliability, typically, the demodulated N bits are estimated by using the logarithmic likelihood ratio (LLR) method [147].

Tables 9 and 10 show a comparison of the decoding algorithms developed for short packet transmissions over the years. The comparison considers both the algorithmic complexity and the reliability. In contrast, the latency is not included in the analysis because the hardware performance advances in recent years, not allowing a fair comparison.

In this work, the definition of Algorithmic complexity refers to the number of required clock cycles during the decoding. The presence of parallel decoding reduces the number of cycles needed. In the analyzed literature, parallel decoding can be semiparallel or fully parallel. Among the reviewed works, in [148], the case of full parallel decoding is defined as available. Moreover, if the algorithms are iterative, another parameter is the number of iterations.

The clock cycle complexity allows the estimation of decoding latency in short packet transmissions, and thus, in FA, as highlighted in [14], [22], and [149]. In this survey, the complexity is related to the parameters N, P, L, R, K, and finally, m. N defines the block length and R is the code rate, whereas K = NR. P defines the number of updated nodes in the decoder. Considering full parallel decoding, N = P. The parameters L and m define the number of lists used in the SCL algorithm and the memory length in WAVA. Finally, the reliability analysis consists of both BLER and BER. BLER values differ from BER ones for the presence of the symbol\*. The

presence of blanks defines the absence of information in the literature regarding the specific parameters. Most decoding algorithms are evaluated with the AWGN channel, whereas in [150], is included a Rayleigh channel.

### A. LOW DENSITY PARITY CHECK (LDPC)

In LDPC codes, the literature suggests using iterative decoding algorithms. Such algorithms allow the message passing between variable nodes and check nodes. The message passing can also be defined as message exchange. Min-Sum and belief propagation (BP) are the algorithms adopted in QC-LDPC. Both algorithms have a complexity tending to  $\frac{N}{P}$  per iteration due to the full parallel decoding. Broulim et al. [151] and Balatsouka-Stimming and Dollas [152] offer an implementation of MIN-SUM with full parallel decoding. In the case of BP, full parallel decoding is proposed in [153], [154], and [155]. Other MIN-SUM implementations in which semiparallel decoding is proposed are [156], [157], and [158], while for the BP case, there is the proposal of [159]. In terms of reliability, BER of  $10^{-6}$  at SNR values close to 4 dB are achieved in [152] and [158] via FPGA implementation. Nevertheless, [153] offers a BER of  $10^{-9}$  at equal SNR. BP-based algorithms offer higher reliability than MIN-SUM-based algorithms due to the higher number of required operations [160]. However, the number of operations does not affect the number of clocks required per iteration, as shown in Table 9. In conclusion, BP, and in particular, the model [153] are optimal, from the complexity point of view, offers full parallel decoding. In contrast, in terms of reliability, [153] is the best performing model among the proposals analyzed.

#### **B. POLAR**

Polar implementations for short packet communications scenarios use algorithms based on the concept of erasure, i.e., the message decoding consists of erasing the interference affecting the received K LLRs and the iterative reconstruction of the message. Cancellation-based algorithms include successive cancellation (SC), successive cancellation list (SCL), and successive cancellation flip (SCP), while the iterative algorithms proposed by the lettering are BP, OSD, and Sphere. The proposals with SC show semiparallel decoding, moreover, the clock complexity varies from a value tending to  $2\log_2(N/P)$ , as in the case of Kam [161] and Ercan's 2017 [162] models, up to a maximum tending to N/P, as in the case of Leroux's model [163], Yuan's 2014 [164], and Giard's [165]. Regarding reliability, the 2017 Ercan model is the best result up to date, offering a BLER of  $10^{-5}$  at SNR of 4 dB (FPGA implementation). Even in the case of SCL have been proposed semiparallel decoding architectures. These models show complexities ranging from  $N/2 + (N/P)\log_2(N/4P)$  clock cycles, as in the case of Yuan's 2015 model [166], up to a complexity tending to  $2N + (N/P)\log_2 N$ . In this last case, the models of Balatsoukas-Stimming [167], Xiong [168], Lin [169], and Fan [170] have been included. Concerning reliability, Balatsoukas-Stimming and Lin offer the best performance for a block length of 1024 bits. Both of them are implemented

**TABLE 9.** Hardware Implementation Part I

| Author                            | FEC   | Decoding<br>algorithm | Block<br>length<br>[Bit] | Code<br>Rate | Hardware<br>implemen-<br>tation | Parallel<br>decod-<br>ing | Number<br>of iter-<br>ations<br>(MAX) | Required<br>clock<br>cycles     | BER/<br>BLER*         | SNR<br>[dB] | Ref   |

|-----------------------------------|-------|-----------------------|--------------------------|--------------|---------------------------------|---------------------------|---------------------------------------|---------------------------------|-----------------------|-------------|-------|

| Park et al                        | LDPC  | MIN-SUM               | 672                      | 0.5          | ASIC                            | Semi-<br>Parallel         | 10                                    | $\frac{5N}{P}$                  | $10^{-7}$             | 4           | [156] |

| Xiang et al                       | LDPC  | MIN-SUM               | 2304                     | 0.5          | ASIC                            | Semi-<br>Parallel         | 10                                    | $\frac{N}{P}$                   | $10^{-6}$             | 3           | [157] |

| Broulim et al                     | LDPC  | MIN-SUM               | 64                       | 0.5          | FPGA                            | Full                      |                                       |                                 | $10^{-7}$             | 6.75        | [151] |

| Broulim et al                     | LDPC  | MIN-SUM               | 128                      | 0.5          | FPGA                            | Full                      |                                       |                                 | $10^{-7}$             | 6           | [151] |