Received 1 December 2020; revised 31 December 2020 and 16 January 2021; accepted 18 January 2021. Date of publication 26 January 2021; date of current version 19 February 2021. The review of this paper was arranged by Associate Editor Dr. Chunhua Liu.

Digital Object Identifier 10.1109/OJIES.2021.3054666

# Review on Single-DC-Source Multilevel Inverters: Topologies, Challenges, Industrial Applications, and Recommendations

MOHAMED TRABELSI <sup>10</sup> (Senior Member, IEEE), HANI VAHEDI <sup>10</sup> (Senior Member, IEEE), AND HAITHAM ABU-RUB <sup>10</sup> (Fellow, IEEE)

<sup>1</sup>Electronic and Communications Engineering Department, Kuwait College of Science and Technology, 27235, Kuwait

<sup>2</sup>Ossiaco Inc., Montreal H3C 2G9, Canada

<sup>3</sup>Electrical and Computer Engineering Program, Texas A&M University at Qatar, Doha 23874, Qatar

CORRESPONDING AUTHOR: MOHAMED TRABELSI (e-mail: m.trabelsi@kcst.edu.kw).

ABSTRACT Having a reduced number of switches and isolated DC sources yet generating a higher number of voltage levels has been always the challenge when selecting the appropriate Multilevel Inverter (MLI) topology. Nowadays, Single-DC-Source Multilevel Inverter (SDCS-MLI) topologies are being considered as more suitable for many power system applications such as Renewable Energy (RE) conversion systems and electrified transportations compared to the Multiple-DC-Source MLIs (MDCS-MLIs). Moreover, increasing the power rating and minimizing the switching frequency while maintaining reasonable power quality using a SDCS-MLI is an important requirement and a persistent challenge for the industry. Thus, this paper presents a general review on the available SDCS-MLI topologies and future trends. Existing solutions are discussed and analyzed based on their topologies, number of output voltage levels, number of active/passive components, advantages/limitations, maturity, and industrial applications. Furthermore, recommendations for future research and development are suggested in this paper.

**INDEX TERMS** Single DC-source, multilevel inverters, MLI, SDCS-MLI, 5-level, reduced components count, industrial applications.

# I. INTRODUCTION

Based on the recent energy statistics, additional power generation is required from renewable energies (REs) in order to decrease the bad environmental impacts of traditional generation [1]. However, the raw outputs of REs need to go through buck/boosting and conversion stages in order to ensure a high-quality AC power injection to the grid. This requires the deployment of high-efficiency, and in many cases high-power inverters (usually connected to medium-voltage grids).

The output of the traditional 2-level inverter contains a lot of harmonics, which makes the use of large filters mandatory. Moreover, in many high-power applications, the capabilities of the 2-level inverter semiconductors are limited by the existing technology to tolerate the high voltage/current ratings [2].

Thus, Multilevel Inverters (MLIs) have been introduced, where the first investigations were mainly based on reducing

the voltage rating of switches for high-power medium-voltage applications where the technology was limited in the market. Nowadays, MLIs are developed to have high number of levels in order to reduce the harmonic pollution and filtering efforts [3], [4].

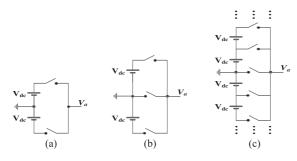

An MLI employs a combination of switches and DC sources/capacitors to generate several voltage levels and have the individual switches carrying less voltage than 2-level inverters. The employed switches are turned on/off according to a selected switching pattern (low voltage block requirement since the switches are not carrying the totality of the DC voltage) in order to produce various voltage levels at the output even at lower switching frequency. Such multilevel voltage waveform leads to better voltage/current quality, hence a reduced output filter size. Fig. 1 shows the basic concept of an MLI operation. Fig. 1(a) shows a conventional 2-level inverter (+Vdc or -Vdc at the output voltage terminals), while a

FIGURE 1. One leg of (a) 2-level, (b) 3-level and (c) n-levels inverter.

FIGURE 2. Real examples of isolated DC sources.

three-level output voltage (+ Vdc, 0 and -Vdc) is produced by the inverter shown in Fig. 1(b). The multilevel configuration represented in Fig. 1(c) generates an n-level output voltage. As it can be noticed from the figure, the power switches carry a maximum voltage rating of Vdc, while the output voltage level maybe higher than Vdc. This MLI feature helps to reach higher power levels without switches derating. Nowadays, the usage of such inverters has been reported in up to 13.8 kV and 100 MW applications [5], [6].

The MLI technology has been initiated by the concept of multilevel step wave in Cascaded H-Bridge (CHB) and Flying Capacitors (FC) inverters in the late 1960s [7]. In 1970, the Diode Clamped Converter (DCC) was introduced but these topologies were proposed for low power applications [8]. For medium-voltage applications, the Neutral Point Clamped (NPC) and then the CHB have been proposed in the 1980s [9], [10]. The FC Inverter (FCI) has been evolved to be employed in medium-voltage and high-power industries in 1990 [11].

MDCS-MLIs require the employment of multiple isolated DC supplies [12], [13]. Such isolated DC power supplies are made up from PV panels, batteries, or AC sources connected to a transformer and rectifier (Fig. 2). Such structure is of big size and high cost in case of MDCS-MLIs. One of the mostly used MDCS-MLIs in high-power motor drive applications is the CHB inverter due to its high modularity and identical voltage rating of the employed switches in case of using identical DC sources. Many other MDCS-MLI have been limitedly used in industry because of the unequal voltage rating of DC supplies and switches. A fair comparison, considering an identical voltage rating, between CHB MLIs and other MDCS-MLIs proves that the CHB MLI is characterized by the employment of optimum number of components and higher modularity [15]. However, the major concern of the MDCS-MLIs is the possibility of unbalanced power sharing among feeders (different voltage levels among the isolated DC sources), which leads to undesirable power losses and malfunctioning [14], [15].

Thus, the use of SDCS-MLIs is generally preferred due to the fact that the employed auxiliary capacitors could be controlled through a proper selection of switching states without adding extra complexity to the system by using linear/nonlinear controllers. SDCS-MLIs can be entirely deployed in power system applications where the 2-level ones are already operational without alterations on the DC side (input) and AC side (output). Moreover, no/few adjustments are incorporated in the controller design since only one DC-link voltage should be regulated and the error signal is used to generate the reference current. Yet, a multilevel switching technique with integrated voltage balancing procedure (taking advantage of the redundant switching states) should be employed to replace the conventional modulation block.

Accordingly, the objectives of this paper are listed as follows.

- 1) To review the available SDCS-MLIs.

- To discuss the merits and limitations of each SDCS-MLI

- 3) To presents potential industrial applications for each topology.

- 4) To give recommendations for further research and development.

#### II. SINGLE DC-SOURCE MULTILEVEL INVERTERS

## A. PRELIMINARIES

NPC, FC, and Modular Multilevel Converter (MMC) have been considered as the most attractive SDCS-MLI families in which FCs (auxiliary capacitors) are used to produce more voltage levels at the output terminals. Recently, the Packed U-Cells (PUC) inverter, considered as an asymmetrical FCI, has emerged as an interesting SDCS-MLI topology that facilitates the implementation of existing controllers for various applications.

#### **B. TOPOLOGIES**

## 1) FCI FAMILY

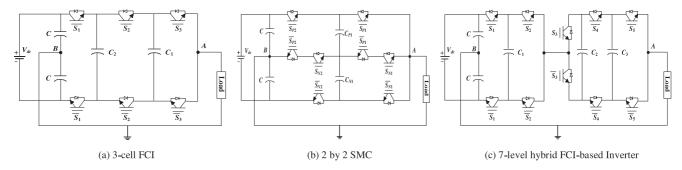

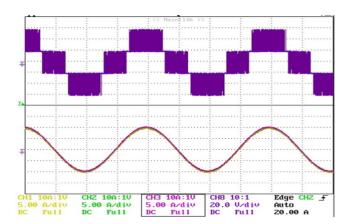

The FCI has been considered as one of the most interesting MLI topologies in industrial application and research fields during the last decades due to its several advantages such as transformer-less operation and equal distribution of switching stress [16]. In FCI topologies, switching power cells composed of 2 low/medium-voltage switching devices controlled in a complementary manner [17] and one DC capacitor, are connected in series to form the converter phase leg and achieve higher voltage/power ranges. The main control task in FCIs is to balance the capacitors' voltages while controlling the output current. For a stable operation of an n-cell FCI, these voltages should be controlled at  $V_{dc}/n$  and  $2V_{dc}/n$  and (n+1) voltage levels are generated. For instance, a 3-cell (n=1) FCI (Fig. 3(a)) generates 4 voltage levels (n+1) at the output terminals (Fig. 4) when the capacitors voltages are controlled

FIGURE 3. Common FCI-based topologies.

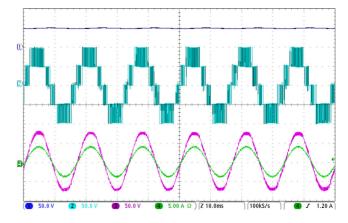

FIGURE 4. Experimental results of a grid-connected 3-cell FCI. Upper: output voltage VAB; Bottom: output current.

**TABLE 1.** Switching Patterns of a 3-Cell FCI

| State | $S_3$ | $S_2$ | $S_1$ | $C_1$      | $C_2$      | $V_{AB}$            |

|-------|-------|-------|-------|------------|------------|---------------------|

| 1     | 0     | 0     | 0     | Bypassed   | Bypassed   | $-V_{dc}/2$         |

| 2     | 0     | 0     | 1     | Discharged | Bypassed   | -V <sub>dc</sub> /6 |

| 3     | 0     | 1     | 0     | Charged    | Discharged | -V <sub>dc</sub> /6 |

| 4     | 0     | 1     | 1     | Bypassed   | Discharged | $V_{dc}/6$          |

| 5     | 1     | 0     | 0     | Bypassed   | Charged    | -V <sub>dc</sub> /6 |

| 6     | 1     | 0     | 1     | Discharged | Charged    | $V_{dc}/6$          |

| 7     | 1     | 1     | 0     | Charged    | Bypassed   | $V_{dc}/6$          |

| 8     | 1     | 1     | 1     | Bypassed   | Bypassed   | $V_{dc}/2$          |

at  $V_{dc}/3$  and  $2V_{dc}/3$ . The corresponding switching patterns are shown in Table 1.

Many other SDCS-MLIs are derived from the FCI structure such as: Stacked Multicell Converter (SMC) [19], [21] and cascaded connection of the modified FCI [22]. Combination of conventional FC, NPC, and 2-level inverter topologies have been also used for 3-phase open-end induction motor drives using only a single DC source as reported in [23].

The SMC can be seen as a combination of two FCI stacked together [24]–[26]. It consists of a hybrid association of commutation cells making possible to share the voltage constraint

on several switches, and also to improve the output waveforms of the converter in terms of number of levels and switching frequency. These benefits lead to a decrease in the cost and size of the SMC in comparison with the conventional FCI for the same output voltage especially for high-power applications. For instance, a 4-cell (2n with n=2) SM converter is composed of 8 (2n) high-frequency switches forming 4 (n) commutation cells, 2 (n-2) clamping capacitors with the same capacitance and different DC voltage ratings equal to  $V_{dc}/2$  and  $V_{dc}$  (Fig. 3(b)). The corresponding output voltage has 5-levels (2n+1).

Another FCI based 7-level hybrid topology was proposed in [27], where each phase of the inverter is realized by cascading two three-level FCIs with a half-bridge module in between (Fig. 3(c)). The main advantage of this topology is the extension capability of the linear modulation range by allowing reduced common-mode voltage (CMV). With the aim of mitigating the leakage current, a similar common-ground 5-level PV inverter topology was proposed in [28] by employing a flying capacitor leg and a half-bridge module. The proposed topology is characterized by its reduced output harmonic content and reactive power injection capability.

An alternative version of the conventional FCI was proposed in [29] as a modular sub-multilevel module. The main advantage of the modified FCI, in comparison with the conventional one, is that the number and voltage rating of the required dc voltage sources are halved for the same number of generated voltage levels, making it more practical and efficient in the medium-voltage high-power applications. This enhancement is attained by adding four switching devices to the conventional FCI topology without any further amendment.

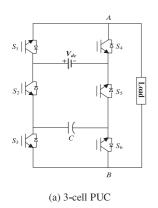

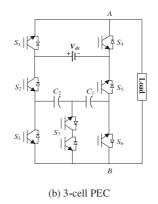

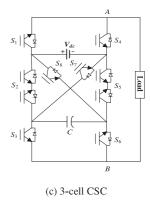

# 2) PUC FAMILY

The PUC inverter, considered as an asymmetrical/double FCI where only two low frequency switches are added to the conventional FCI topology, has been getting an increased interest as a SDCS-MLI topology due to its multiple features compared to the other MLI topologies [30]–[33]. The main benefits of this topology are the flexibility in expanding to higher output levels while employing a SDCS, enhancement of the filter bandwidth taking advantage of the switching states redundancy, high reliability and cost reduction due to the employment of a reduced number of active components, and high

FIGURE 5. Common PUC-based topologies.

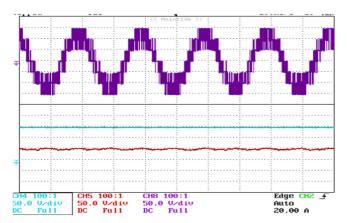

**FIGURE 6.** Experimental results of a grid-connected PUC7 inverter. Upper: output voltage  $V_{AB}$ ; Bottom: Input voltage  $V_1$  (in blue) and capacitor voltage  $V_C$  (in red).

ride-through capability assured by the auxiliary capacitors. Each cell of the PUC topology consists of one capacitor and two power switches. For an n cells topology, 2n switches (the switches of each cell are complimentarily controlled leading to  $2^n$  combinations) and n-2 capacitors are employed. For instance, a 3-cell PUC inverter (Fig. 5(a)) has only 6 active switches, 1 DC source, and 1 auxiliary capacitor ( $C_2$ ). If the capacitor voltage  $V_2$  is controlled at 1/3 of  $V_{dc}$ , then a 7-level voltage waveform (PUC7 configuration) is generated at the output terminals ( $\pm V_{dc}$ ,  $\pm 2/3V_{dc}$ ,  $\pm V_{dc}/3$ , 0) (Fig. 6) [34]–[38]. In PUC7, there is no redundant states (apart from the zero state as shown in Table 2) and utilizing control system to set the voltage on the flying capacitor is inevitable.

If the capacitor voltage is regulated at the reference value  $V_2^*=V_{dc}/2$ , and taking advantage of the switching redundancy, an optimized output performance could be achieved by the generation of 5 equidistant voltage levels (PUC5) at the output terminals (Fig. 7) resulting in a better flexibility in voltage levels generation (Table 3) and easier balancing of the capacitor voltage compared to the PUC7 configuration [39]–[45]. By adding a capacitor to the PUC5 inverter, a new topology called ZPUC5 was proposed in [46], where the output voltage waveform is unipolar.

**TABLE 2.** Switching Table of a PUC7 Inverter

| State | $S_1$ | $S_2$ | $S_3$ | С          | $V_{AB}$             |

|-------|-------|-------|-------|------------|----------------------|

| 1     | 1     | 0     | 0     | Bypassed   | $V_{dc}$             |

| 2     | 1     | 0     | 1     | Charged    | $2/3V_{dc}$          |

| 3     | 1     | 1     | 0     | Discharged | $V_{do}/3$           |

| 4     | 1     | 1     | 1     | Bypassed   | 0                    |

| 5     | 0     | 0     | 0     | Bypassed   | 0                    |

| 6     | 0     | 0     | 1     | Charged    | - V <sub>dc</sub> /3 |

| 7     | 0     | 1     | 0     | Discharged | $-2/3 V_{dc}$        |

| 8     | 0     | 1     | 1     | Bypassed   | - V <sub>dc</sub>    |

FIGURE 7. Experimental results of a grid-connected PUC5 inverter. Upper: capacitor voltage  $V_C$ ; Middle: output voltage  $V_{AB}$ ; Bottom: grid voltage  $V_{grid}$  (in magenta) and output current  $i_{grid}$  (in green).

However, decreasing the voltage levels may affect the power quality (THD increase) [43]. Thus, an extended version, called PUC9, was investigated by adding 1 power cell (two switches and one capacitor) leading to the generation of 9 voltage levels (reduced THD) [47]–[48]. The PUC9 inverter is considered as a low-cost inverter due to the reduced number of devices and simple voltage controller. Higher-level PUC topologies were investigated in the literature for better power quality [49]–[52].

FIGURE 8. Common NPC-based topologies.

**TABLE 3.** Switching Table of a PUC5 Inverter

| State | $S_1$ | $S_2$ | $S_3$ | С          | $V_{AB}$            |

|-------|-------|-------|-------|------------|---------------------|

| 1     | 1     | 0     | 0     | Bypassed   | $V_{dc}$            |

| 2     | 1     | 0     | 1     | Charged    | $V_{do}/2$          |

| 3     | 1     | 1     | 0     | Discharged | $V_{do}/2$          |

| 4     | 1     | 1     | 1     | Bypassed   | 0                   |

| 5     | 0     | 0     | 0     | Bypassed   | 0                   |

| 6     | 0     | 0     | 1     | Charged    | -V <sub>de</sub> ∕2 |

| 7     | 0     | 1     | 0     | Discharged | -V <sub>d</sub> √2  |

| 8     | 0     | 1     | 1     | Bypassed   | - V <sub>dc</sub>   |

A cascade connection of PUC inverters, seen as multilevel modules, was proposed in [53] to decrease the voltage diversity of the PUC inverter. This enhancement helps to increase the modularity of the PUC-based MLIs. Another connection of high-voltage/low-frequency and low-voltage/high-frequency PUC sub-modules was proposed in [54] to form a 23-level Hybrid Packed U-Cell (H-PUC) converter characterized by reduced power losses and higher efficiency.

Recently, a novel 9-level Packed E-Cell (PEC9), with a comparable component count and self-balancing capability of the capacitors' voltages, was proposed in [55], [56]. The PEC9 is composed of 7 power switches and 2 auxiliary capacitors shunted by a four-quadrant switch (Fig. 5(b)). The shunting of the DC capacitors allows their charging/discharging making use of the redundant switching states and their voltages are self-balanced to 1/4 of the DC-link voltage.

By adding two bidirectional switches to the 3-cell PUC topology, 9 voltage levels could be generated by a Crossover Switches Cell (CSC) inverter where the peak output voltage value is greater than the value of the DC source voltage (boost capability) (Fig. 5(c)) [57].

## 3) NPC FAMILY

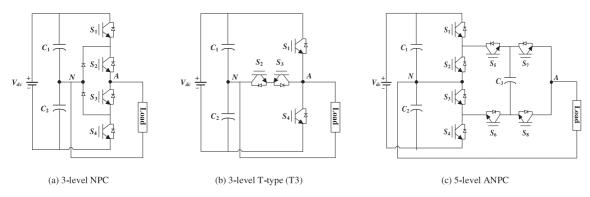

The 3-level NPC (Fig. 8(a)) has been the mostly employed SDCS-MLI [10] in medium voltage drive, marine, and mining applications owing to its high performance compared to the

2-level structure. However, for higher number of levels operation, the 3-level NPC topology suffers from the substantial increase in the number of employed clamping diodes as well as the dc-link capacitor voltage balancing issue.

By cascading 2 NPC modules, a new power converter called series-connected multilevel converter (SCMC) was proposed for medium-voltage high-power applications in [58]. The five-level operation of SCMC (5L-SCMC) is performed by using three-level NPC converter modules in each phase. Compared to the 5-level CHB topology, the required number of secondary windings (needed for isolated DC sources) is considerably reduced in the 5L-SCMC, which leads to the reduction of the complexity and cost of the overall system.

A modified version of the NPC called T3 (Fig. 8(b)) was proposed in [59]. Indeed, the clamping diodes of the NPC are replaced by bidirectional switches in T3. Due to the low conduction and switching losses of the T3 inverter, the efficiency is very high especially for medium switching frequencies (8–24 kHz) often used in industry. Basically, the T3 inverter regroups the merits of the 2-level inverter (simple operation, reduced component count, and low conduction losses) and the 3-level inverter (increased output voltage quality with low switching losses). Thus, T3 has been considered as a good alternative to 2-level inverters in low-voltage with high switching frequency applications. A 9-level modified T-type MLI (MT-MLI) with reduced number of switches was proposed in [60]. By integrating T3 cells into Nested NPC (NNPC) [61], higher levels of output voltage could be achieved. For instance, a 5-level T-type Nested Neutral-Point-Clamped (T-NNPC) converter was proposed in [62], which is considered as an attractive topology for medium-voltage applications as it can work in a wide range of voltages with fewer components. Other NPC-based 5-level topologies have been proposed in the literature. Some of these topologies have been investigated by researchers such as Bidirectional NPC (BNPC) [63] and Pinned Mid-Points (PMP) MLI [64], while others have been commercialized by manufacturers such as 5-level Hbridge NPC (HNPC) [65] and 5-level active NPC (ANPC) (Fig. 8(c)) [66]. Recently, modified ANPC topologies have been proposed, such as new 5-L ANPC [67], 6-Switch and 7-Switch 5L-ANPC [68]–[69], improved ANPC (I-ANPC) [70], and 5-Level Common-Ground Boost-Type Active

FIGURE 9. Common CHB-based topologies.

Neutral-Point-Clamped (5L-CGBT-ANPC) inverter [71]. The latter topology is characterized by its voltage-boosting capability, high-frequency Common Mode Voltage (CMV) mitigation, and enhancement of the DC-link voltage utilization taking advantage of the common ground.

Also, 5-level and N-level hybrid-clamped MLI topologies comprising active (switches) and passive (diodes and capacitors) clamping devices were presented in [72]–[74]. The proposed topologies do not require the use of additional circuitry to balance DC-link capacitor voltages compared to the diode-clamped MLIs. Like the FCI, where the floating capacitors contribute the voltage synthesis, the redundant switching states are used to balance the capacitor voltages.

For RE applications, a single-stage extended T-type boost inverter was proposed in [75]. It consists of switched capacitors and T-type inverter that can step-up the output voltage without inductors. In addition, the number of the switched capacitors corresponds to the maximum boost ratio. Similarly, a transformer-less step-up MLI was proposed in [76] based on cascaded connection of bipolar T-type 5-level modules. Nevertheless, the NPC-based topologies have been suffering from the requirement of capacitive divider bridge to deal with the midpoint balancing (large voltage ripples). Thus, software/hardware solutions, such as space vector modulation, advanced controllers, and the employment of external circuits for capacitors' voltages balancing are needed.

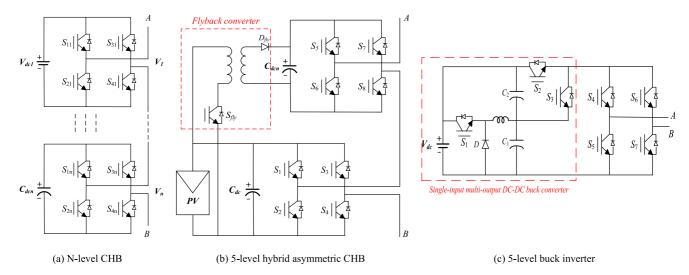

# 4) CHB FAMILY

The CHB inverter is one of the mostly used MLI topologies in the industry due to its high efficiency and modularity. However, the main drawback of the conventional CHB is the use of more than one isolated DC source (Fig. 9(a)) that each one means, to the industry, a transformer and a rectifier. As a remedy, a single DC source CHB MLI has been reported in the literature as single-phase [77] and 3-phase configurations [78]. The main drawback of this configuration is its dependency to the modulation index and load impedance to regulate

the capacitor voltage. Thus, advanced modulation techniques have been proposed in [79], [80] to overcome the limitation of controlling the capacitor voltage for all ranges of modulation index.

A switched-capacitor based CHB (SC-CHB) MLI was proposed in [81]. The suggested topology has remarkable features, such as self-balancing capability and its ability to offer a boosted staircase AC voltage. Consequently, the proposed topology can be a versatile converter in the industrial applications. For instance, by eliminating the leakage current and boosting the input voltage, it can make the transformer needless in grid-tied PV applications.

A hybrid asymmetric 2-cell CHB inverter was proposed in [82], where a flyback converter is used to provide the input DC voltage to the low-voltage H-bridge cell (Fig. 9(b)). Thus, the two H-bridge cells operate with different voltage levels and under different switching frequencies. Another hybrid topology was proposed in [83] by combining 1 leg of H-bridge and 1 leg of NPC and 1 additional bidirectional switch. Moreover, the proposed topology consists of a capacitor in each cell whose voltage is balanced by appropriate switching strategy even under fault conditions. The proposed topology has a capability of producing five-level output. These levels can be extended by using cascading structure similar to CHB inverter. A higher-level Symmetrical Hybrid CHB (SH-CHB) topology (9-level) was proposed in [84] by integrating a 5-level dc/dc converter cell with an H-bridge module.

Another single-stage 3-cell CHB (7-level) inverter with boosting (triple voltage gain), self-balancing of the capacitors' voltages, and low voltage stress capabilities was proposed in [85], [86]. Two bidirectional voltage blocking switches were used to interconnect the H-bridge cells and enable the integration of two switched-capacitors.

Another 5-level CHB-based SDCS-MLI with self-balancing capability of the capacitors' voltages was proposed in [87] for isolated grid-tied systems. The proposed converter requires 12 power switches (a leg with four switches

FIGURE 10. Common MMC topologies with different submodule type: (a) half-bridge, (b) full-bridge, (c) NPC.

connected to the inputs of 2 H-bridge inverters) and two dc-link capacitors.

By using a small high-frequency link, operating the auxiliary bridges as active filters while the main bridges commutate at fundamental frequency, an improved asymmetrical CHB (ACHB) inverter was proposed in [88] to generate any number of levels.

In [89], the connection of a single-input multiple-output buck converter to an H-bridge inverter (Fig. 9(c)) is used to generate a 5-level output voltage. It is worth noting that the proposed topology is characterized by its reduced cost due to the use of a partial-scale buck converter.

Moreover, [90] presents an effective circuit configuration MLI which can increase the number of output voltage levels compared with the conventional CHB MLI. The proposed topology consists of a DC input source with a series of capacitors, diodes, active switches for synthesizing output voltage levels, and an H-bridge inverter. To generate a 7-level output voltage, the proposed topology needs 7 switches, where the traditional CHB inverter needs 12 switches.

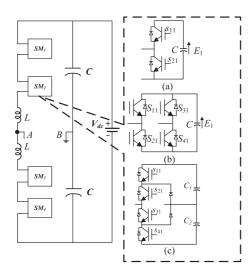

# 5) MMC FAMILY

Modular multilevel converter (MMC) topologies are becoming attractive in both industrial applications and academic research. The MMC is a very promising and attractive MLI used especially in high-power and high-voltage single and 3-phase applications [91]. For a higher number of submodules, this structure is characterized by its high fault-tolerance taking advantage of the state redundancies (degree of freedom in generating voltage levels). Building blocks (sub-modules) can be easily added in series in order to handle considerably higher voltages. Fig. 10(a) shows a typical single-phase circuit topology, where  $SM_{i\{1-4\}}$  denotes the cascaded connection of multiple submodules (half-bridge modules) in each arm and leg [93]. Note that, in each leg, there are two arms connected

FIGURE 11. Experimental results of a 3-level MMC output voltage.

in series via two equal inductors. The switches need to provide bidirectional current flowing and unidirectional voltage blocking. This submodule can be operated in two quadrants and can generate only two voltage levels  $(0, + V_{dc}/2)$  at the output. By parallel connection of two identical H-bridge modules, a full-bridge module (Fig. 10(b)) can be created and both positive and negative cell DC voltages can be obtained  $(0, \pm V_{dc}/2)$  at the output terminals (Fig. 11). Combination (series connection) of half and full-bridge submodules leads to achieving both unipolar and bipolar cell benefits by generating an asymmetric four-level voltage waveform ( $V_{dc}$ , 0,  $\pm V_{dc}/2$ ). The submodules could be connected in series or in parallel in other configurations, such as asymmetrical double, clampeddouble, FC, and NPC commutated cells (Fig. 10(c)), in order to meet the requirements for a specific application [94]. It is generally desired to achieve a cell structure having a higher voltage blocking capability, symmetrical voltage levels, and a bipolar operation at a minimum cost (related to the number of devices and losses).

For distributed PV systems, a new circuit topology of MMC was proposed in [95]. In that topology, the inductors (placed in conventional MMC to limit the circulating current) are replaced by a transformer. The proposed circuit gives a 50% reduction in the voltage rating of the power devices and the capacitor size in comparison with the basic MMC topology. The required DC-link voltage that is directly fed by PV panels is also reduced by half. In addition, the transformer helps to limit the fault current in the DC bus.

# 6) OTHER FAMILIES

Other MLI topologies have been proposed in the literature to generate different voltage levels for several applications, while using a SDCS. For instance, 9-level topologies with boosting and capacitor's voltage self-balancing capabilities were proposed in [96]–[98]. Moreover, many switched-capacitors based MLI topologies have been proposed [99]–[104].

A single-phase 9-level switched-capacitor MLI (9L-SCMLI) has been proposed in [99]. The SCMLI is characterized by its appropriate boosting property and higher efficiency

compared to the classical SDCS-MLI topologies. A switched-capacitor (SC) cell is built by employing two equal capacitors paralleled to a single dc source to boost the input voltage. A modified version called single-stage switched-capacitor module (S³CM) was proposed in [100]. The main advantage of the S³CM topology is to minimize the blocking voltage across the switches, but the switch count is high. To overcome the drawbacks of the S³CM, a compact switched capacitor multilevel inverter (CSCMLI) topology was proposed in [101], offering a boost and self-voltage balancing capabilities while employing a reduced switches count. The capacitors voltages balancing is ensured by selecting an appropriate switching sequence. The capacitors are integrated to keep the equal average voltage during the switching operation.

Using 2 SCs and 9 switching devices, a transformerless dual-mode five-level common-grounded type (5L-DM-CGT) inverter was proposed in [104]. The proposed topology can operate in buck and boost modes while eliminating the leakage current. Some common-grounded SDCS-MLIs are using inductors at their inputs to make a boost stage and increase the DC voltage, which usually requires a separate PWM or controller for the DC-DC stage [105]–[106].

On the other hand, some topologies use coupled inductors to increase the number of output voltage levels without adding more switches to the configuration [107], [118]. The main practical concern about using inductors is their size and losses at higher current.

# C. CONTROL STRATEGIES

Usually, the control techniques applied to power converters consist of cascaded current and voltage loops. In PV applications, the voltage error is also injected into the current reference to control the dc link voltage. However, the injection of voltage errors into a single current reference cannot ensure a proper share of the active power among the dc links to keep the capacitors voltages balanced. For example, in single-phase applications, external controllers should be employed to regulate the two DC capacitors' voltages in NPC and T3 inverters (redundant switching states could be considered for 3-phase applications). The same applies to ANPC and FCI topologies except their auxiliary capacitors.

Thus, the main challenge for most of the SDCS-MLI topologies is to regulate the voltages across the auxiliary capacitors while best tracking the output current reference. It is also worth noting that the controlled variables are interrelated in most of the topologies (FCI, PUC, and MMC) and any change in one of them may affect the others. Usually, additional circuits or external controllers are used to balance the voltages across the auxiliary capacitors. Also, most conveniently, redundant switching states are used to perform this task in some topologies. For example, a Phase Disposition Pulse Width Modulation (PD-PWM)-based strategy was proposed in [108], [109] to balance the capacitors voltages in FCIs. Similarly, the capacitors voltages of a 7-level 3x2 SMC were balanced in [110] using the same technique. An optimal switching-based voltage balancing technique (only optimal

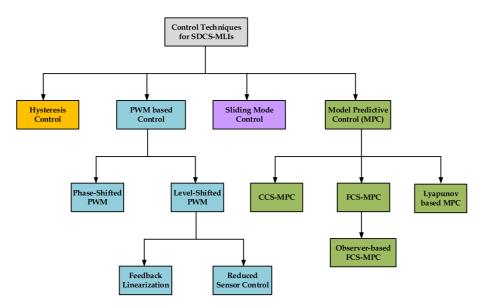

transitions between consecutive voltage levels are considered) was proposed by authors in [111] for a similar SMC structure. Owing to their fast dynamic response and ability to include constraints with different natures, several Model Predictive Control (MPC)-based strategies have been also extensively applied as an alternative to the standard PI controllers to control FCIs [112]- [114], PUC [36]- [38], and MMCs [91], [92] The most common control techniques applied to SDCS-MLIs are summarized in Fig. 12.

## III. SDCS-MLI TOPOLOGIES COMPARISON

A realistic comparison of MLIs should cover the commercialization factors such as size, cost, and efficiency which are the most important keys for industries to make products out of them. These factors can be turned into the engineering or research words like the number of components, voltage/current rating of components, size of passive filters, switching frequency, etc. The number of components, voltage/current rating, and switching frequency has a direct effect on the cost and size. The more components, the higher losses, and consequently the lower efficiency. As well, larger filters force the overall size of the inverter to be higher.

Most of the performed comparisons in the literature only include the number of components such as DC sources, active switches, diodes, and capacitors without considering the number of voltage levels or equal voltage rating of the switches. Such efforts may be interesting for research but impractical in real applications. Industries look for cheap but effective solutions. For instance, the CHB is appealing for industry because of modularity. Although it requires isolated DC sources for each cell, installation/commissioning/maintenance is reasonable as well as full-bridge switch modules are manufactured at low prices by many sources.

To have a fair engineering comparison, the number of switches and voltage levels should be listed all together. As well, since this work is devoted to SDCS-MLIs, the number of voltage-controlled capacitors should be included in the comparison. It is also better to compare MLIs with the same number of output voltage levels as the performance changes per number of levels obviously. In this study, in order to calculate the total voltage withstanding (Table IV-Table VI), it has been assumed that a 600 V peak voltage level is required at the output of each topology. Therefore, according to the boosting feature of the topology, the appropriate voltage amplitudes of the DC-links have been calculated and then, the voltage rating of each device has been obtained. Finally, the voltage ratings of all parts in every topology have been added together to achieve the total withstanding voltage. Separate comparison tables have been prepared for 5-level, 7-level and 9-level topologies (Table 4–Table 6).

Eventually, a comparison has been performed on 3-phase SDCS-MLI topologies and results are listed in Table 7.

According to such comparisons, it can be concluded that a higher number of capacitors are needed for a higher number of levels. Consequently, more complex voltage balancing

FIGURE 12. Most common control techniques applied to SDCS-MLIs.

**TABLE 4** 5-Level SDCS-MLI Topologies

| Topology                  | Switches<br>Count | Diodes<br>Count | Capacitors<br>Count | Inductors<br>Count | Total<br>Components<br>Count | Switching<br>Frequency<br>(Hz) | Boosting<br>Feature | Voltage<br>Rating<br>(V) | Reference |

|---------------------------|-------------------|-----------------|---------------------|--------------------|------------------------------|--------------------------------|---------------------|--------------------------|-----------|

| PUC5                      | 6                 | 0               | 1                   | 0                  | 7                            | 2000                           | no                  | 2400                     | [39]      |

| Hybrid NPC-<br>CHB        | 12                | 0               | 2                   | 0                  | 14                           | 10000                          | no                  | 3600                     | [87]      |

| SCMLI                     | 9                 | 0               | 2                   | 0                  | 10                           | 10000                          | no                  | 3600                     | [115]     |

| SCMC                      | 8                 | 4               | 4                   | 0                  | 16                           | 60                             | no                  | 3600                     | [58]      |

| Fault Tolerant            | 8                 | 2               | 1                   | 0                  | 11                           | 5000                           | No                  | 6000                     | [83]      |

| Common<br>Ground          | 7                 | 0               | 2                   | 0                  | 9                            | 12000                          | No                  | 3000                     | [116]     |

| 6S-5L-ANPC                | 6                 | 2               | 1                   | 0                  | 9                            | 15000                          | no                  | 2100                     | [117]     |

| Coupled<br>Inductors      | 6                 | 0               | 0                   | 1                  | 7                            | 4000                           | no                  | 3600                     | [118]     |

| B5LI                      | 10                | 0               | 2                   | 2                  | 14                           | 5000                           | yes                 | 3000                     | [105]     |

| SBD2T5L-TL                | 10                | 0               | 2                   | 1                  | 13                           | 20000                          | yes                 | 3900                     | [106]     |

| 4-switch coupled inductor | 4                 | 2               | 2                   | 1                  | 9                            | 10000                          | no                  | 3000                     | [107]     |

**TABLE 5** 7-Level SDCS-MLI Topologies

| Topology                  | Switches<br>Count | Diodes<br>Count | Capacitors<br>Count | Inductors<br>Count | Total<br>Components<br>Count | Switching<br>Frequency<br>(Hz) | Boosting<br>Feature | Voltage<br>Rating<br>(V) | Reference   |

|---------------------------|-------------------|-----------------|---------------------|--------------------|------------------------------|--------------------------------|---------------------|--------------------------|-------------|

| Modified CHB              | 16                | 0               | 2                   | 0                  | 18                           | 1667                           | yes                 | 2800                     | [86]        |

| SDCS-CHB                  | 8                 | 0               | 1                   | 0                  | 9                            | 2000                           | no                  | 3200                     | [77], [119] |

| PUC                       | 6                 | 0               | 1                   | 0                  | 7                            | 1000                           | no                  | 2400                     | [33]        |

| BMSC                      | 12                | 0               | 4                   | 0                  | 16                           | 15000                          | yes                 | 4500                     | [120]       |

| BSC7LI                    | 10                | 0               | 4                   | 0                  | 14                           | 5000                           | yes                 | 2200                     | [121]       |

| 7L self-voltage balancing | 10                | 0               | 3                   | 0                  | 13                           | 10000                          | yes                 | 2800                     | [122]       |

| 7-Level T-<br>Type        | 7                 | 2               | 3                   | 0                  | 12                           | 10000                          | no                  | 4200                     | [123]       |

**TABLE 6 9-Level SDCS-MLI Topologies**

| Topology                    | Switches<br>Count | Diodes<br>Count | Capacitors<br>Count | Inductors<br>Count | Total<br>Components<br>Count | Switching<br>Frequency<br>(Hz) | Boosting<br>Feature | Voltage<br>Rating (V) | Reference |

|-----------------------------|-------------------|-----------------|---------------------|--------------------|------------------------------|--------------------------------|---------------------|-----------------------|-----------|

| PUC                         | 8                 | 0               | 2                   | 0                  | 10                           | 4000                           | No                  | 2400                  | [47]      |

| PEC                         | 8                 | 0               | 2                   | 0                  | 10                           | 1500                           | No                  | 2550                  | [55]      |

| CSC                         | 10                | 0               | 1                   | 0                  | 11                           | 1200                           | Yes                 | 2400                  | [57]      |

| MT-MLI                      | 10                | 0               | 3                   | 0                  | 13                           | 2000                           | Yes                 | 2700                  | [60]      |

| SC-CHB                      | 17                | 5               | 4                   | 1                  | 27                           | 5000                           | Yes                 | 3300                  | [81]      |

| SH-CHB                      | 12                | 0               | 4                   | 0                  | 16                           | 10000                          | No                  | 3600                  | [84]      |

| Step-Up MLI                 | 12                | 8               | 8                   | 0                  | 28                           | 4000                           | Yes                 | 3300                  | [96]      |

| Quadruple<br>Boost Inverter | 8                 | 3               | 3                   | 0                  | 14                           | 4000                           | Yes                 | 3600                  | [97]      |

| Hybrid Boost<br>Inverter    | 8                 | 2               | 3                   | 0                  | 13                           | 2000                           | Yes                 | 3000                  | [98]      |

| SCMLI                       | 10                | 1               | 2                   | 0                  | 13                           | 550                            | Yes                 | 3450                  | [99]      |

| S <sup>3</sup> CM           | 12                | 0               | 2                   | 0                  | 14                           | 2800                           | Yes                 | 3300                  | [100]     |

| CSCMLI                      | 11                | 0               | 2                   | 0                  | 13                           | 2500                           | Yes                 | 3000                  | [101]     |

| SC-Boost<br>Inverter        | 13                | 0               | 2                   | 0                  | 15                           | 2500                           | Yes                 | 2850                  | [102]     |

| SC-Step-Up<br>Inverter      | 19                | 3               | 3                   | 0                  | 25                           | 2000                           | Yes                 | 2850                  | [103]     |

**TABLE 7 3-Phase SDCS-MLI Topologies**

| Topology                                   | Number<br>of<br>Levels | Switches<br>Count | Diodes<br>Count | Capacitors<br>Count | Inductors<br>Count | Reference |

|--------------------------------------------|------------------------|-------------------|-----------------|---------------------|--------------------|-----------|

| NPC                                        | 5                      | 12                | 6               | 2                   | 0                  | [10]      |

| Cascaded<br>FCI + HB                       | 5                      | 24                | 0               | 3                   | 0                  | [22]      |

| Reduced<br>FCs and<br>Switches<br>Inverter | 5                      | 18                | 0               | 4                   | 0                  | [23]      |

| T-Type                                     | 3                      | 12                | 0               | 2                   | 0                  | [59]      |

| NNPC                                       | 5                      | 24                | 6               | 8                   | 0                  | [61]      |

| T-NNPC                                     | 5                      | 18                | 0               | 6                   | 0                  | [62]      |

| Hybrid<br>MLI                              | 7                      | 18                | 0               | 3                   | 0                  | [78]      |

techniques are required to keep the voltages of the capacitors at desired levels.

# **IV. INDUSTRIAL APPLICATIONS**

Till now, the mostly used MLIs in the industry are NPC, T3, and CHB. All these topologies have been used due to the industrial demand for high-power delivery and market limit on voltage/current rating of switches. The main advantage of those topologies is the reduced voltage rating of switches that help using them in high-power and ultra-high-power, medium, or high voltage applications such as large motor drives and wind energy conversion systems [6]. To reduce the voltage rating in those configurations, it was necessary to split the DC link. The positive side effect of split DC links in MLIs is the generation of multilevel output voltage waveform. Such

waveform is more similar to a sine wave with lower harmonic contents than a 2-level one inherently. For instance, a 3-level waveform has 50% lower THD than a 2-level one. Therefore, it is clear that the size of output filters will be reduced significantly by adding more levels to the output voltage waveform. Increasing the number of levels needs more isolated DC sources or voltage-controlled capacitors which is not cost and size-effective. In this regard, CHB can generate a high number of voltage levels by adding more cells thanks to its modularity. However, it requires isolated DC sources that increase the size and cost dramatically and reduces the applicability for a vast range of power. It is justifiable only for high-power applications like hundreds of kilowatts or megawatts where there are no available components for such ratings. Currently, many companies like Infineon, Semikron, Vincotech, and Fuji Electric are developing and manufacturing switch modules for NPC, ANPC and T3 (Table 8). They have integrated multi IGBT switches and diodes in one package to reduce the size and increase the efficiency. Vincotech has also developed other modules like FC and H6.5 for various applications such as PV inverters and motor drives.

Such modules are used by well-known companies to build high power UPS or pumps. For instance, ABB is manufacturing 3-level NPC and 5-level ANPC for industrial drives and frequency converters. Schneider Electric uses 3-level NPC for motor drives and 4-level FC for UPS products. Toshiba also uses 3-level NPC with 3-level and 5-level PWM for their high-power drives. All those converters are mostly used for high power applications like pumps, fans, conveyors, traction systems, etc.

Nowadays, industries are more interested in using MLIs for low and medium power ratings (like more than 1 kW) as a

**TABLE 8** Common Industrial MLI Switch Modules

| Company          | Module<br>Topology | Voltage<br>Rating  | Current<br>Rating  | Applications                                                                      | Reference |

|------------------|--------------------|--------------------|--------------------|-----------------------------------------------------------------------------------|-----------|

| Vincotech        | NPC                | 1200 &<br>1500V    | 30 to<br>1800A     | • Drives • Solar Inverters • UPS                                                  | [124]     |

| Vincotech        | Т3                 | 650 &<br>1200V     | 25 to<br>1800A     | • Drives • Solar Inverters • UPS                                                  | [125]     |

| Vincotech        | ANPC               | 1200 &<br>1500V    | 150, 300<br>& 600A | • Solar<br>Inverters                                                              | [126]     |

| Vincotech        | FC                 | 1200V              | 200A               | • Drives<br>• Solar                                                               | [127]     |

|                  |                    |                    |                    | Inverters • UPS                                                                   |           |

| Fuji<br>Electric | Т3                 | 600,900 &<br>1200V | 50 to<br>600A      | • Drives • Power Conditioners • UPS                                               | [128]     |

| Semikron         | NPC                | 650 &<br>1200V     | 20 to<br>600A      | • Wind Turbine<br>Converters<br>• Solar<br>Inverters<br>• UPS                     | [129]     |

| Semikron         | Т3                 | 650 &<br>1200V     | 50 to<br>600A      | <ul><li>Wind Turbine<br/>Converters</li><li>Solar inverters</li><li>UPS</li></ul> | [129]     |

| Infineon         | NPC                | 650 &<br>1200V     | 30 to<br>400A      | <ul><li>High Speed<br/>Drives</li><li>Solar inverters</li><li>UPS</li></ul>       | [130]     |

| Infineon         | Т3                 | 650 &<br>1200V     | 15 to<br>600A      | <ul><li>High speed<br/>Drives</li><li>Solar<br/>Inverters</li><li>UPS</li></ul>   | [130]     |

result of low prices of the active switches. This range is mainly related to residential and small-scale industrial applications. Moreover, it also belongs to single-phase applications such as residential PV inverters, water pumps, home generator sets, low/medium power backup UPS, etc. As shown in previous sections, it is almost impractical and uneconomical to use topologies with isolated DC sources for low and medium power ratings. Therefore, SDCS-MLIs are getting more attention for that power rating and industries are developing them for market products. Although a high number of levels is always interesting for researchers, it is very bulky and costly to increase the number of components like switches and capacitors for such power ranges for market players. Considering the size, cost, voltage balancing issues, efficiency, manufacturing, etc, there would be a trade-off for MLIs to find their way to the market.

A 3-level Full-Bridge (FB) can be built using the same hardware of 2-level FB but changing the software to have a unidirectional PWM and generate a 3-level waveform with 50% lower THD. Although it needs extra gate drivers, it manages to reduce the output filters significantly. Going beyond, as reviewed in this paper, some SDCS-MLIs are generating

FIGURE 13. Applications of SDCS-MLIs.

a high number of voltage levels like 9-level and more but looking to the industry, it is revealed that 5-level topologies are at the highest attention at the moment. The 5-level MLIs need between 6-10 switches and 1-3 auxiliary capacitors. The well-known topologies are 2-leg NPC/T3/FC and PUC5. Fig. 13 shows the possible applications of Single-DC-Source MLIs.

Imperix builds 3-level NPC legs to be used in single-phase and 3-phase applications. Vincotech also manufactures different types of converters for renewable energy systems such as H-Bridge, FC, H6.5, NPC, T3 and ANPC. Huawei, SolarEdge and Ossiaco are developing their products around 5-level core inverters Huawei has announced the use of 5-level technology for their data centers. SolarEdge is developing HD Wave with a 5-level MLI for PV energy conversion system. Ossiaco is developing its EV Charger/PV Inverter based on the PUC5 topology.

According to these exploration outcomes, it is clear that although high power multilevel converters are widely used in the industries, many companies started developing and manufacturing multilevel converters for single-phase low/medium power applications such as EV chargers, V2G, V2H, PV inverters and residential UPS. Moreover, industries tend to use SDCS-MLIs due to being practical and affordable in terms of size and cost for all type of power electronics applications (Fig. 14).

# V. COMMERCIALIZATION AND DEVELOPMENT CHALLENGES

As industrial applications have shown, it is obvious that low-harmonic multilevel waveforms could attract the attention of industries to commercialize the most reliable and cost-effective topologies. However, it should be noted that adding more switches and auxiliary capacitors to the inverter structure is always costly for manufacturing. Moreover, it will bring further complication to the control circuit to add extra gate drivers, voltage balancing techniques, and switching algorithms. Therefore, there should be some gains on the topology such as reduced size of the passive components, reduced switching frequency and switching losses, increased reliability, and efficiency, to be selected by a company to commercialize. Industries are always looking for a trade-off between the number of levels and complexity of the design

(b) Solaredge HD Wave

(c) Ossiaco DCBEL

FIGURE 14. SDCS-MLI industrial products.

and operation. Some drawbacks of the existing SDCS-MLIs can be mentioned as below:

- 1) Using high number of switches while generating low number of voltage levels

- Having multiple stages (DC-DC and DC-AC) to increase the number of DC links and voltage levels

- 3) Using numerous capacitors as auxiliary DC links

- 4) Using large capacitors as auxiliary DC links

- Difficult voltage balancing procedure of auxiliary DC links

- 6) Complex control circuits with extra gate drivers and voltage/current sensors

- 7) Complicated switching algorithm.

Currently, 5-level SDCS-MLIs are matured and widely developed/manufactured by companies for various applications such as EV chargers, motor drives and PV inverters as a solution to above-mentioned trade-off and drawbacks. Topologies such as CHB, T3, NPC, ANPC and PUC5 could prove their ability to be commercialized by industry due to low-complexity voltage balancing, acceptable performance by available standard controllers (cascaded PI controllers), design consideration and suitable reliability and efficiency. Thus, it is seen that industries are interested in simplicity and high-performance for their next generation of power electronic converters. Based on the review study performed in this paper, the future research and development challenges can be listed as follows:

- Extending the use of SDCS-MLI topologies from high-power to medium/low-power applications such as aerospace and aircrafts, power supplies, residential products, electrified transportation, solid state transformers, etc.

- Developing higher-level SDCS-MLI topologies (more than 5-level). One suggestion is to replace the isolated DC sources by voltage-controlled capacitors in MDCS-MLIs.

- Applying new voltage balancing techniques or external circuits to reduce the size of auxiliary capacitors and voltage ripples in single-DC-source topologies.

- 4) Designing new switching techniques with integrated voltage balancing algorithms to reduce the complexity of the controllers.

- 5) Reducing losses and increasing the efficiency

- Developing modular/fault-tolerant SDCS-MLI topologies

- 7) Designing resonant converters based on SDCS-MLIs.

# VI. CONCLUSION

This paper proposed an extensive review on Single-DC-Source Multilevel Inverters (SDCS-MLIs). Different existing MLI families, such as Flying Capacitors Inverter (FCI), Packed U-Cell (PUC), Neutral Point Clamped (NPC), Cascaded H-Bridge (CHB), Modular Multilevel Converter (MMC), have been reviewed and analyzed based on their structure, number of output voltage levels, number of active/passive components, boosting capability, voltage rating, advantages/limitations, and industrial applications. Based on the proposed review study, it has been shown that 5-level SDCS-MLIs present a good trade-off between low-harmonic multilevel waveform (high-performance), cost-effectiveness, and structure simplicity. Thus, they have been considered as matured and widely developed/manufactured by companies for various applications such as EV chargers, motor drives and PV inverters. Furthermore, recommendations on topologies such as CHB, T3, NPC, ANPC and PUC5 are given based on their proven ability to be commercialized due to low-complexity voltage balancing, acceptable performance by available standard controllers, design consideration and suitable reliability and efficiency.

Finally, future research and development challenges such as extending the use of SDCS-MLI topologies to medium and low-power applications, applying new voltage balancing techniques to reduce the size of auxiliary capacitors and voltage ripples, developing modular and fault-tolerant topologies, have been defined.

#### **ACKNOWLEDGMENT**

Open Access funding provided by the Qatar National Library.

#### **REFERENCES**

- Enerdata. Global Energy Statistical Yearbook. 2015 [Online]. Available: http://yearbook.enerdata.net/

- [2] Wikipedia. Power Semiconductor Device. 2012. [Online]. Available: http://en.wikipedia.org/wiki/Power\_semiconductor\_device

- [3] M. Vijeh, M. Rezanejad, E. Samadaei, and K. Bertilsson, "A general review of multilevel inverters based on main submodules: Structural point of view," *IEEE Trans. Power Electron.*, vol. 34, no. 10, pp. 9479–9502, Oct. 2019.

- [4] H. P. Vemuganti, S. Dharmavarapu, S. K. Ganjikunta, H. M. Suryawanshi, and H. Abu Rub, "A survey on reduced switch count multilevel inverters," *IEEE Open J. Ind. Electron. Soc.*, Early Access, pp. 1–1, 2020.

- [5] J. Rodríguez, S. Bernet, B. Wu, J. O. Pontt, and S. Kouro, "Multilevel voltage-source-converter topologies for industrial medium-voltage drives," *IEEE Trans. Ind. Electron.*, vol. 54, no. 6, pp. 2930–2945, Dec. 2007.

- [6] H. Abu-Rub, J. Holtz, J. Rodriguez, and G. Baoming, "Medium-Voltage multilevel converters—State of the art, challenges, and requirements in industrial applications," in *IEEE Trans. Ind. Electron.*, vol. 57, no. 8, pp. 2581–2596, Aug. 2010.

- [7] W. McMurray, "Fast response stepped-wave switching power converter circuit," US Patent 3581212, 1971.

- [8] R. H. Baker, "High-voltage converter circuit," US Patent 4203151, 1980.

- [9] R. H. Baker, "Bridge converter circuit," US Patent 4270163, 1981.

- [10] A. Nabae, I. Takahashi, and H. Akagi, "A new neutral-point-clamped PWM inverter," *IEEE Trans. Ind. Appl.*, vol. IA-17, no. 5, pp. 518–523, Sep. 1981.

- [11] T. Meynard and H. Foch, "Dispositif électronique de conversion d'énergie électrique," France Patent WO1993002501A1, 1991.

- [12] Y. Hinago and H. Koizumi, "A single-phase multilevel inverter using switched series/parallel dc voltage sources," *IEEE Trans. Ind. Elec*tron., vol. 57, no. 8, pp. 2643–2650, Aug. 2010.

- [13] K. K. Gupta and S. Jain, "A novel multilevel inverter based on switched DC sources," *IEEE Trans. Ind. Electron.*, vol. 61, no. 7, pp. 3269–3278, Jul. 2014.

- [14] E. Samadaei, S. A. Gholamian, A. Sheikholeslami, and J. Adabi, "An envelope type (E-Type) module: Asymmetric multilevel inverters with reduced components," *IEEE Trans. Ind. Electron.*, vol. 63, no. 11, pp. 7148–7156, Nov. 2016.

- [15] M. Malinowski, K. Gopakumar, J. Rodriguez, and M. A. Perez, "A survey on cascaded multilevel inverters," *IEEE Trans. Ind. Electron.*, vol. 57, no. 7, pp. 2197–2206, Jul. 2010.

- [16] M. F. Escalante, J. C. Vannier, and A. Arzandé, "Flying capacitor multilevel inverters and DTC motor drive applications," *IEEE Trans. Ind. Electron.*, vol. 49, no. 4, pp. 809–815, Aug. 2002.

- [17] M. Trabelsi, L. Ben-Brahim, and K. A. Ghazi, "An improved real-time digital feedback control for grid-tie multilevel inverter," in *Proc. IECON-39th Annu. Conf. IEEE Ind. Electron. Soc.*, 2013, pp. 5776–5781.

- [18] M. Trabelsi, J. M. Retif, X. Lin-Shi, X. Brun, F. Morel, and P. Bevilacqua, "Hybrid control of a three-cell converter associated to an inductive load," in *Proc. IEEE Power Electron. Specialists Conf.*, 2008, pp. 3519–3525.

- [19] M. Ben Smida and F. Ben Ammar, "Modeling and DBC-PSC-PWM control of a three-phase flying-capacitor stacked multilevel voltage source inverter," *IEEE Trans. Ind. Electron.*, vol. 57, no. 7, pp. 2231–2239, Jul. 2010.

- [20] A. K. Sadigh, V. Dargahi, M. A. Pahlavani, and A. Shoulaie, "Elimination of one dc voltage source in stacked multicell converters," *IET Power Electron*, vol. 5, no. 6, pp. 644–658, 2012.

- [21] G. Gateau, T. A. Meynard, and H. Foch, "Stacked multicell converter (SMC):Properties and design," in *Proc. IEEE 32nd Annu. Power Electron. Specialists Conf.*, 2001, pp. 1583–1588.

- [22] P. Roshankumar, P. P. Rajeevan, K. Mathew, K. Gopakumar, J. I. Leon, and L. G. Franquelo, "A five-level inverter topology with single-DC supply by cascading a flying capacitor inverter and an H-Bridge," in *IEEE Trans. Power Electron.*, vol. 27, no. 8, pp. 3505–3512, Aug. 2012.

- [23] M. G. Majumder, A. K. Yadav, K. Gopakumar, K. R. Raj, U. Loganathan, and L. G. Franquelo, "A 5-level inverter scheme using single DC link with reduced number of floating capacitors and switches for open-end IM drives," in *IEEE Trans. Ind. Electron.*, vol. 67, no. 2, pp. 960–968, Feb. 2020.

- [24] M. Ben Smida and F. Ben Ammar, "Modeling and DBC-PSC-PWM control of a three-phase flying-capacitor stacked multilevel voltage source inverter," *IEEE Trans. Ind. Electron.*, vol. 57, no. 7, pp. 2231–2239, Jul. 2010.

- [25] A. K. Sadigh, V. Dargahi, M. A. Pahlavani, and A. Shoulaie, "Elimination of one dc voltage source in stacked multicell converters," *IET Power Electron*, vol. 5, no. 6, pp. 644–658, 2012.

- [26] G. Gateau, T. A. Meynard, and H. Foch, "Stacked multicell converter (SMC): Properties and design," in *Proc. IEEE 32nd Annu. Power Electron. Specialists Conf.*, 2001, vol. 3, pp. 1583–1588.

- [27] A. Rahul Sanjeevan, R. S. Kaarthik, K. Gopakumar, P. P. Rajeevan, J. I. Leon, and L. G. Franquelo, "Reduced common-mode voltage operation of a new seven-level hybrid multilevel inverter topology with a single DC voltage source," in *IET Power Electron.*, vol. 9, no. 3, pp. 519–528, 2016.

- [28] F. B. Grigoletto, "Five-level transformerless inverter for single-phase solar photovoltaic applications," in *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 8, no. 4, pp. 3411–3422, Dec. 2020.

- [29] V. Dargahi, A. K. Sadigh, M. Abarzadeh, S. Eskandari, and K. A. Corzine, "A new family of modular multilevel converter based on modified flying-capacitor multicell converters," in *IEEE Trans. Power Electron.*, vol. 30, no. 1, pp. 138–147, Jan. 2015.

- [30] A. K. Sadigh, S. H. Hosseini, M. Sabahi, and G. B. Gharehpetian, "Double flying capacitor multicell converter based on modifed phase-shifted pulsewidth modulation," *IEEE Trans. Power Electron.*, vol. 25, no. 6, pp. 1517–1526, Jun. 2010.

- [31] A. S. Hemasilvia Vinothini and B. P. M. Dhanasekaran, "Nine level double flying capacitor multicell converter based on modulation technique," in *Proc. IEEE-Int. Conf. Adv. Eng., Sci. Manage.*, 2012, pp. 320–325.

- 32] H. Vahedi and M. Trabelsi, Single-DC-Source Multilevel Inverters. Switzerland: Springer 2019

- [33] Y. Ounejjar, K. Al-Haddad, and L.-A. Gregoire, "Packed U cells multilevel converter topology: Theoretical study and experimental validation," *IEEE Trans. Ind. Electron.*, vol. 58, no. 4, pp. 1294–1306, Apr. 2011.

- [34] H. Makhamreh, M. Trabelsi, O. Kükrer, and H. Abu-Rub, "An effective sliding mode control design for a grid-connected PUC7 multilevel inverter," *IEEE Trans. Ind. Electron.*, vol. 67, no. 5, pp. 3717–3725, May 2020.

- [35] H. Makhamreh, M. Trabelsi, O. Kükrer, and H. Abu-Rub, "A simple sliding mode controller for PUC7 grid-connected inverter using a lookup table," in *Proc. 45th Annu. Conf. IEEE Ind. Electron. Soc.*, 2019, pp. 3325–3330.

- [36] M. Trabelsi, S. Bayhan, K. A. Ghazi, H. Abu-Rub, and L. Ben-Brahim, "Finite-Control-Set model predictive control for grid-connected packed-u-cells multilevel inverter," in *IEEE Trans. Ind. Electron.*, vol. 63, no. 11, pp. 7286–7295, Nov. 2016.

- [37] S. Xiao, M. Metry, M. Trabelsi, R. S. Balog, and H. Abu-Rub, "A model predictive control technique for utility-scale grid connected battery systems using packed u cells multilevel inverter," in *Proc. 42nd Annu. IEEE Conf. Ind. Electron. Soc.*, 2016, pp. 5953–5958.

- [38] M. Trabelsi, S. Bayhan, M. Metry, H. Abu-Rub, L. Ben-Brahim, and R. Balog, "An effective model predictive control for grid connected packed u cells multilevel inverter," in *Proc. IEEE Power Energy Conf.* at Illinois (PECI), 2016, pp. 1–6.

- [39] H. Vahedi, P. A. Labbé, and K. Al-Haddad, "Sensor-less five-level packed U-Cell (PUC5) inverter operating in stand-alone and gridconnected modes," *IEEE Trans. Ind. Informat.*, vol. 12, no. 1, pp. 361–370, Feb. 2016.

- [40] H. Makhamreh, M. Trabelsi, O. Kükrer, and H. Abu-Rub, "Model predictive control for a PUC5 based dual output active rectifier," in *Proc. IEEE 13th Int. Conf. Compat., Power Electron. Power Eng.*, 2019, pp. 1–6.

- [41] M. Abarzadeh, H. Vahedi, and K. Al-Haddad, "Fast sensor-less voltage balancing and capacitor size reduction in PUC5 converter using novel modulation method," *IEEE Trans. Ind. Informat.*, vol. 15, no. 8, pp. 4394–4406, Aug. 2019.

- [42] H. Vahedi, M. Sharifzadeh, and K. Al-Haddad, "Topology and control analysis of single-DC-source five-level packed U-cell inverter (PUC5)," in *Proc. 43rd Annu. Conf. IEEE Ind. Electron. Soc.*, 2017, pp. 8691–8696.

- [43] S. Arazm, H. Vahedi, and K. Al-Haddad, "Phase-shift modulation technique for 5-level packed U-cell (PUC5) inverter," in *Proc. IEEE 12th Int. Conf. Compat., Power Electron. Power Eng.*, 2018, pp. 1–6.

- [44] S. Arazm, H. Vahedi, and K. Al-Haddad, "Space vector modulation technique on single phase sensor-less PUC5 inverter and voltage balancing at flying capacitor," in *Proc. 44th Annu. Conf. IEEE Ind. Elec*tron. Soc., 2018, pp. 4504–4509.

- [45] M. Trabelsi, H. Vahedi, H. Komurcugil, H. Abu-Rub, and K. Al-Haddad, "Low complexity model predictive control of PUC5 based dynamic voltage restorer," in *Proc. IEEE 27th Int. Symp. Ind. Electron.*, 2018, pp. 240–245.

- [46] S. Arazm and K. Al-Haddad, "ZPUC: A new configuration of single DC source for modular multilevel converter applications," in *IEEE Open J. Ind. Electron. Soc.*, vol. 1, pp. 97–113, May 2020.

- [47] S. Arazm, H. Vahedi, and K. Al-Haddad, "Nine-Level packed U-Cell (PUC9) inverter topology with single-dc-source and effective voltage balancing of auxiliary capacitors," in *Proc. IEEE 28th Int. Symp. Ind. Electron. (ISIE)*, 2019, pp. 944–949.

- [48] K. Abdelbasset, S. S. Refaat, and M. Trabelsi, "Model predictive control of a 9-Level Packed U-Cells based grid-connected PV system," in *Proc. 2nd Int. Conf. Smart Grid Renewable Energy (SGRE)*, 2019, pp. 1–6.

- [49] M. Trabelsi, S. Bayhan, S. S. Refaat, H. Abu-Rub, and L. Ben-Brahim, "Multi-objective model predictive control for grid-tied 15-level packed U cells inverter," in *Proc. 18th Eur. Conf. Power Electron. Appl.*, 2016, pp. 1–7.

- [50] M. Trabelsi, M. Ghanes, S. Bayhan, and H. Abu-Rub, "High performance voltage-sensorless model predictive control for grid integration of packed U ceils based PV system," in *Proc. 19th Eur. Conf. Power Electron. Appl.*, 2017, pp. P.1–P.8.

- [51] Y. Ounejjar and K. Al-Haddad, "Fourteen-band hysteresis controller of the fifteen-level packed u cells converter," in *Proc. IECON 36th Annu. Conf. IEEE Ind. Electron. Soc.*, 2010, pp. 475–480.

- [52] Y. Ounejjar and K. Al-Haddad, "A novel 31-level packed u cells converter," in *Proc. Int. Conf. Power Eng., Energy Elect. Drives*, 2011, pp. 1–6.

- [53] A. K. Sadigh, V. Dargahi, and K. A. Corzine, "New multilevel converter based on cascade connection of double flying capacitor multicell converters and its improved modulation technique," *IEEE Trans. Power Electron.*, vol. 30, no. 12, pp. 6568–6580, Dec. 2015.

- [54] K. Sorto-Ventura, M. Abarzadeh, K. Al-Haddad, and L. A. Dessaint, "23-level Single DC source hybrid PUC (H-PUC) converter topology with reduced number of components: Real-time implementation with model predictive control," *IEEE Open J. Ind. Electron. Soc.*, vol. 1, pp. 127–137, Jul. 2020.

- [55] M. Sharifzadeh and K. Al-Haddad, "Packed E-Cell (PEC) converter topology operation and experimental validation," *IEEE Access*, vol. 7, pp. 93049–93061, 2019.

- [56] R. M. Sekar, D. N. Jayakumar, K. Mylsamy, U. Subramaniam, and S. Padmanaban, "Single phase nine level inverter using single DC source supported by capacitor voltage balancing algorithm," *IET Power Electron.*, vol. 11, no. 14, pp. 2319–2329, 2018.

- [57] H. Vahedi, K. Al-Haddad, Y. Ounejjar, and K. Addoweesh, "Crossover switches cell (CSC): A new multilevel inverter topology with maximum voltage levels and minimum DC sources," in *Proc. 39th Annu. Conf. IEEE Ind. Electron. Soc.*, 2013, pp. 54–59.

- [58] A. Dekka, B. Wu, and M. Narimani, "A series-connected multilevel converter: Topology, modeling, and control," *IEEE Trans. Ind. Electron.*, vol. 66, no. 8, pp. 5850–5861, Aug. 2019.

- [59] M. Schweizer and J. W. Kolar, "High efficiency drive system with 3-level T-type inverter," in *Proc.14th Eur. Conf. Power Electron. Appl.*, 2011, pp. 1–10.

- [60] B. S. Naik, Y. Suresh, J. Venkataramanaiah, and A. K. Panda, "Design and implementation of a novel nine-level MT-MLI with a self-voltagebalancing switching technique," *IET Power Electron.*, vol. 12, no. 15, pp. 3953–3963, Sep. 2019.

- [61] M. Narimani, B. Wu, and N. R. Zargari, "A new five-level nested neutral point clamped (NNPC) voltage source converter," in *Proc. IEEE Appl. Power Electron. Conf. Expo.*, 2017, pp. 2554–2558.

- [62] A. Bahrami and M. Narimani, "A new five-level T-Type nested neutral point clamped (T-NNPC) converter," *IEEE Trans. Power Electron.*, vol. 34, no. 11, pp. 10534–10545, Nov. 2019.

- [63] S. S. Shekhawat, P. J. Dhyanchand, and P. Thollot, "Bi-directional switch for neutral point clamped PWM inverter," EP0258428A4, European Patent Office, Feb. 24, 1987.

- [64] H. Vahedi, S. Rahmani, and K. Al-Haddad, "Pinned mid-points multilevel inverter (PMP): Three-phase topology with high voltage levels and one bidirectional switch," in *Proc. IECON 39th Annu. Conf. IEEE Ind. Electron. Soc.*, 2013, pp. 102–107.

- [65] C. M. Wu, W. H. Lau, and H. Chung, "A five-level neutral-point clamped H-bridge PWM inverter with superior harmonics suppression: A theoretical analysis," in *Proc. IEEE Int. Symp. Circuits Syst.*, May 30–Jun. 2, 1999, vol. 5, pp. 198–201.

[66] G. Tan, Q. Deng, and Z. Liu, "An optimized SVPWM strategy for five-

- [66] G. Tan, Q. Deng, and Z. Liu, "An optimized SVPWM strategy for five-level active NPC (5L-ANPC) converter," *IEEE Trans. Power Electron.*, vol. 29, no. 1, pp. 386–395, Jan. 2014.

- [67] E. Burguete, J. Lopez, and M. Zabaleta, "A new five-level active neutral-point-clamped converter," *IEEE Trans. Indus. Appl.*, vol. 51, no. 1, pp. 7175–7183, Jan./Feb. 2015.

- [68] H. Wang, L. Kou, Y. Liu, and P. C. Sen, "A seven-switch five-level active-neutral-point-clamped converter and its optimal modulation strategy," *IEEE Trans. Power Electron*, vol. 32, no. 7, pp. 5146–5161, Jul. 2017.

- [69] L. Kou, H. Wang, Y. Liu, P. C. Sen, and Y. Zhang, "Modulation method for single-phase six-switch five-level ANPC inverter," in *Proc. IEEE Energy Convers. Congr. Expo.*, 2016, pp. 1–8.

- [70] V. Dargahi, K. A. Corzine, J. H. Enslin, J. Rodríguez, and F. Blaabjerg, "Improved active-neutral-point-clamped (I-ANPC) multilevel converter: Fundamental circuit topology, innovative modulation technique, and experimental validation," in *Proc. IEEE Power Energy Conf. Illinois*, 2018, pp. 1–8.

- [71] S. S. Lee, Y. Yang, and Y. Siwakoti, "A novel single-stage five-level common-ground-boost-type active neutral-point-clamped (5L-CGBT-ANPC) inverter," *IEEE Trans. Power Electron.*, to be published, 2020, doi: 10.1109/TPEL.2020.3037720.

- [72] A. Chen and X. He, "Res. Hybrid-clamped multilevel-inverter topol," IEEE Trans. Ind. Electron., vol. 53, no. 6, pp. 1898–1907, Dec. 2006.

- [73] B.-S. Suh and D.-S. Hyun, "A new n-level high voltage inversion system," *IEEE Trans. Ind. Electron.*, vol. 44, no. 1, pp. 107–115, Feb. 1997.

- [74] F. Z. Peng, "A generalized multilevel inverter topology with self voltage balancing," *IEEE Trans. Ind. Appl.*, vol. 37, no. 2, pp. 611–618, Mar./Apr. 2001.

- [75] T. Sugimoto, T. Nozaki, and T. Murakami, "Extended T-type boost inverter using switched capacitors," in *Proc. 2019 - 45th Annu. Conf. IEEE Ind. Electron. Soc.*, 2019, pp. 1756–1761.

- [76] A. Khodaparast, J. Adabi, and M. Rezanejad, "A step-up switched-capacitor multilevel inverter based on 5-level T-type modules," *IET Power Electron.*, vol. 12, no. 3, pp. 483–491, 2019.

- [77] Z. Du, L. M. Tolbert, J. N. Chiasson, and B. Ozpineci, "A cascade multilevel inverter using a single DC source," in *Proc. 21st Annu. IEEE Appl. Power Electron. Conf. Expo.*, 2006, pp. 426–430.

- [78] H. Liu, L. M. Tolbert, B. Ozpineci, and Z. Du, "Hybrid multilevel inverter with single DC source," in *Proc. 51st Midwest Symp. Circuits Syst.*, 2008, pp. 538–541.

- [79] F. Khoucha, A. Ales, A. Khoudiri, K. Marouani, M. E. H. Benbouzid, and A. Kheloui, "A 7-level single DC source cascaded H-bridge multilevel inverters control using hybrid modulation," in *Proc. 19th Int. Conf. Elect. Machines*, 2010, pp. 1–5.

- [80] H. Vahedi, M. Sharifzadeh, K. Al-Haddad, and B. M. Wilamowski, "Single-DC-source 7-level CHB inverter with multicarrier levelshifted PWM," in *Proc. 41st Annu. Conf. IEEE Ind. Electron. Soc.*, 2015, pp. 4328–4333.

- [81] H. Khoun Jahan, M. Abapour, and K. Zare, "Switched-Capacitor-Based single-source cascaded H-Bridge multilevel inverter featuring boosting ability," *IEEE Trans. Power Electron.*, vol. 34, no. 2, pp. 1113–1124, Feb. 2019.

- [82] M. S. Manoharan, A. Ahmed, H. Kim, and J. Park, "A single-source photovoltaic power conditioning system using asymmetric cascaded multilevel inverter," *Proc.* 2015 9th Int. Conf. Power Electron. ECCE Asia, 2015, pp. 21–26.

- [83] S. P. Gautam, L. Kumar, S. Gupta, and N. Agrawal, "A single-phase five-level inverter topology with switch fault-tolerance capabilities," *IEEE Trans. Ind. Electron.*, vol. 64, no. 3, pp. 2004–2014, Mar. 2017.

- IEEE Trans. Ind. Electron., vol. 64, no. 3, pp. 2004–2014, Mar. 2017.

K. Wang, Z. Zheng, D. Wei, B. Fan, and Y. Li, "Topology and capacitor voltage balancing control of a symmetrical hybrid nine-level inverter for high-speed motor drives," IEEE Trans. Ind. Appl., vol. 53, no. 6, pp. 5563–5572, Nov./Dec. 2017.

- [85] S. S. Lee, "A single-phase single-source 7-Level inverter with triple voltage boosting gain," *IEEE Access*, vol. 6, pp. 30005–30011, 2018.

- [86] X. Sun, B. Wang, Y. Zhou, W. Wang, H. Du, and Z. Lu, "A single DC source cascaded seven-level inverter integrating switched-capacitor techniques," *IEEE Trans. Ind. Electron.*, vol. 63, no. 11, pp. 7184–7194, Nov. 2016.

- [87] B. S. Naik, L. Umanand, K. Gopakumar, and B. S. Reddy, "A two-phase five-level converter with least number of power switches requiring only a single DC source," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 6, no. 4, pp. 1942–1952, Dec. 2018.

- [88] J. Pereda and J. Dixon, "23-level inverter for electric vehicles using a single battery pack and series active filters," *IEEE Trans. Veh. Technol.*, vol. 61, no. 3, pp. 1043–1051, Mar. 2012.

- [89] M. Farhadi-Kangarlu and M. G. Marangalu, "Five-level single-dc source inverter with adjustable DC-Link voltage," in *Proc. Elect. Eng.* (ICEE), Iranian Conf., 2018, pp. 1017–1021.

- [90] J. Choi and F. Kang, "Modification of cascaded H-bridge multilevel inverter to increase output voltage level with a single DC voltage source," in *Proc. 2014 IEEE Energy Convers. Congr. Expo.*, 2014, pp. 5757–5760.

- [91] L. Ben-Brahim, A. Gastli, M. Trabelsi, K. A. Ghazi, M. Houchati, and H. Abu-Rub, "Modular multilevel converter circulating current reduction using model predictive control," *IEEE Trans. Ind. Electron.*, vol. 63, no. 6, pp. 3857–3866, Jun. 2016.

- [92] M. Trabelsi, L. Ben-Brahim, A. Gastli, and K. A. Ghazi, "An improved predictive control approach for multilevel inverters," in *Proc. IEEE Int.* Symp. Sensorless Control for Elect. Drives Predictive Control Elect. Drives Power Electron., 2013, pp. 1–7.

- [93] M. Trabelsi, M. Ghanes, O. Ellabban, H. Abu-Rub, and L. Ben-Brahim, "An interconnected observer for modular multilevel converter," in *Proc. IEEE Energy Convers. Congr. Expo.*, 2016, pp. 1–7.