# MMC-MTDC Transmission System with Partially Hybrid Branches

Yongyang Chen, Student Member, IEEE, Shangzhi Pan, Senior Member, IEEE, Meng Huang, Member, IEEE, Zili Zhu, Yushuang Liu, Student Member, IEEE, and Xiaoming Zha, Member, IEEE

Abstract—This paper proposes a hybrid submodule modular multilevel converter (MMC) topology which is suitable for multi terminal direct current (MTDC) transmission systems. Each arm of the proposed MMC topology consists of a half-bridge submodule (HBSM) branch and two parallel full-bridge submodule (FBSM) branches. Comparing with the conventional MTDC transmission system, the proposed topology can selectively block the DC fault current and isolate the corresponding fault line without expensive DC circuit breakers (DCCBs). Thus, the influence range of the DC fault can be reduced and the reliability of the power supply can be improved as well. The corresponding modulation and voltage balancing strategies are developed for the proposed hybrid MMC topology. The feasibility of the proposed topology and control strategy is verified in the MATLAB/ Simulink simulation.

*Index Terms*—Hybrid modular multilevel converter, multi terminal networks, high voltage dc (HVDC) transmission.

### I. INTRODUCTION

**N**OWADAYS, HVDC transmission systems are widely adopted in the island-grid power connection, the non-synchronous grids interconnection, and distributed energy generation systems [1][2]. The growing demand for large-scale renewable energy delivery expands the transmission capacity and distance of MMC-MTDC systems [3][4].

At present, cables and overhead lines are two options for DC transmission lines in MTDC projects[5]. The cost of the DC transmission cable is higher and the cables are difficult to lay in some scenes [6]. Compared with cables, the failure rate of overhead lines is higher [7]. Thus, the DC fault detection and protection scheme of MMC-MTDC systems is of concern [8][9]. The DC fault detection methods are widely studied such as impedance calculations, rate of change of voltages and

Manuscript received August 10 2020; revised October 04 2020 and December 07 2020; accepted January 26, 2021. date of publication June 25, 2021; date of current version June 18, 2021.

This work was supported in part by the National Natural Science Foundation of China under Grant 51637007 and in part by the Science and Technology Projects of State Grid Corporation of China under project SG-TYHT/16-JS-198. (*Corresponding author: M. Huang*)

Y. Chen, M. Huang, S. Pan, Y. Liu and X. Zha are with the School of Electrical Engineering and Automation, Wuhan University, Wuhan, China. (e-mail: meng.huang@whu.edu.cn).

Z. Zhu is with the College of Electrical Engineering, Zhejiang University, Hangzhou, China. (e-mail: zhuzl@zju.edu.cn).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.30941/CESTEMS.2021.00016

currents[10], overcurrent detection[11].

The DC fault blocking capability is necessary for the MTDC system to protect converters [12]. Many topologies and methods are dealing with the DC fault protection capabilities of the MTDC system, such as the HBSM-MMC with DCCBs [13][14], FBSM-MMC [3][15], and the hybrid MMC with HBSM and FBSM [2][16].

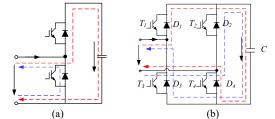

Setting a DCCB at each terminal of the MTDC system is one of the most common and effective DC grid protection strategies [14]. The fault current can be quickly isolated by DCCBs. However, this is at the expense of high economic investment and additional operational losses [17]. These obstacles limit its application to MTDC systems. Another DC fault blocking method is to equip submodules with fault clearance capabilities, such as FBSM, clamp-double submodule (CDSM), and so on [18]. As shown in Fig. 1, the fault current path of HBSM is different from that of FBSM, the fault current still flows through the diode after the HBSM is blocked. However, the current flows through the FBSM capacitor and charge it so that the diode is subjected to reverse voltage to cut off the fault current. Although the FBSM has the capability of dc fault clearance, it also increases module cost and switching losses [19]. Therefore, the hybrid MMC with HBSM and FBSM is proposed.

The hybrid MMC consists of FBSM and HBSM. By appropriately designing the ratio of FBSM and HBSM, the hybrid MMC maintains the DC fault blocking capacity while reducing the cost and power loss[20]. Since the hybrid MMC has the above advantages, there is much research on the hybrid MMC, such as the voltage balancing control[20][22], the fault ride-through process[21], and the reliability analysis[18].

However, the above researches focus on the hybrid MMC itself and did not pay attention to its application in the MTDC system. In the MTDC system, the main drawback of the hybrid MMC is that it cannot isolate the fault line, which often expands the impact range of the DC fault. In [23], a continuous operation strategy under DC fault was mentioned. However,

Fig. 1. SM fault current path after blocking. (a) HBSM. (b) FBSM

124

2096-3564 © 2021 CES

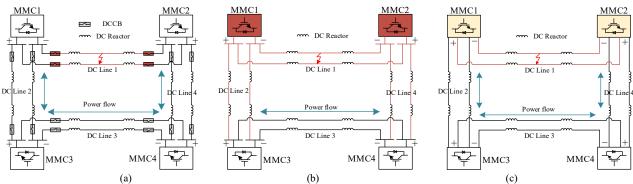

Fig. 2. DC fault protection schemes for the MTDC system. (a) HBSM MMC and DCCBs; (b) FBSM MMC; (c) Proposed MMC topology.

this strategy still relies on DCCBs and the circuit breakers at the nodes present a challenge for protection control.

In order to overcome the above obstacles, this paper proposes a hybrid MMC topology that can reduce the influence range of line faults and improve the power supply reliability of MTDC transmission systems. As shown in Fig.2, if a pole-to-pole fault occurs on the DC line, the MTDC system will feed current to the fault point. When the overcurrent is detected, the fault protection of the MTDC system is activated. As shown in Fig. 2(a), for the MTDC system equipped with DCCBs, the fault current is blocked by DCCBs and the fault line is also isolated by DCCBs. Because of the aforementioned drawbacks of DCCBs, the MMC topology with fault blocking capability is also an alternative in the MTDC system. As shown in Fig. 2(b), the DC fault current can be interrupted after the FBSM-MMCs are blocked. Because MMC 1 and MMC 2 are blocked, the DC line 2 and DC line 4 cannot transmit power and the influence range of the DC line fault is expanded. With the proposed MMC topology, the fault on the DC line 1 can be blocked and isolated selectively. Comparing Fig. 2(b) and Fig. 2(c), we can see that the influence range of the DC fault can be reduced and the reliability of the power supply can be improved with the proposed MMC topology.

The rest of this paper is organized as follows: Section II presents the MMC topology with partially hybrid branches. In section III, the corresponding MMC station control strategy for the proposed hybrid MMC is presented. In Section IV, the

| TABLE I                           |

|-----------------------------------|

| THE PROPOSED HYBRID MMC PARAMETER |

| Parameters                       | Symbols                             |

|----------------------------------|-------------------------------------|

| AC rated voltage amplitude       | $V_g$                               |

| DC line rated voltage            | V <sub>dc1</sub> , V <sub>dc2</sub> |

| Rated active power of DC lines   | $P_{ref1}, P_{ref2}$                |

| Rated reactive power of DC lines | $Q_{ref1}, Q_{ref2}$                |

| SM number of a HB branch         | $N_H$                               |

| SM number of FB branches         | $N_{F1}$ , $N_{F2}$                 |

| HBSM capacitance                 | $C_{smh}$                           |

| FBSM capacitance                 | $C_{smf1}, C_{smf2}$                |

| HBSM rated voltage               | $U_{smh}$                           |

| FBSM rated voltage               | $U_{smf1}$ , $U_{smf2}$             |

| Arm inductance                   | $L_0$                               |

| DC line reactor                  | $L_d$                               |

| Capacitor voltage ripple rate    | ξ                                   |

proposed topology and control strategies are validated by simulation results. Section V presents the topology comparison result of different MTDC protection schemes. Finally, the concluding remarks are provided in Section VI.

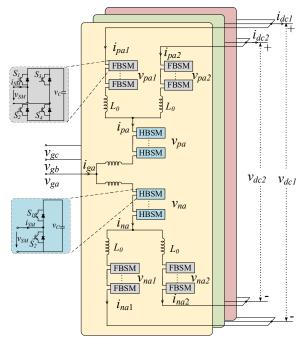

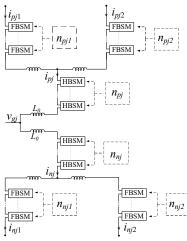

### II. PROPOSED HYBRID MMC TOPOLOGY

The proposed hybrid MMC topology is shown in Fig. 3. The parallel FBSM branches are connected to the DC line 1 and the DC line 2. The components of the FBSM branch 1 are indicated by subscript 1 and the components of the FBSM branch 2 are indicated by subscript 2. The parameters and variables of the proposed MMC topology are shown in Table I. The resistance of the arm is not considered in the analysis and the arm inductance is recorded as  $L_0$ .  $v_{pj}$  is the sum of the inserted HBSM voltages on the upper arm of phase *j* and  $v_{nj}$  is the sum of the inserted HBSM voltages on the lower arm of phase *j*, where *j* denotes the AC phase and  $j \in \{a, b, c\}$ . The voltage of the FBSM branch 1 is expressed as  $v_{pj2}$  or  $v_{nj2}$ . The current flowing through each branch is similarly marked.

As shown in Fig. 3, the relationship of the FBSM branch 1 variables can be derived as follows.

Fig. 3. The MMC topology with partially hybrid branches.

$$L_0 \frac{di_{pj}}{dt} + L_0 \frac{di_{pj1}}{dt} = \frac{1}{2} v_{dc1} - v_{gj} - v_{pj} - v_{pj1}$$

(1)

$$L_0 \frac{di_{nj}}{dt} + L_0 \frac{di_{nj1}}{dt} = \frac{1}{2} v_{dc1} + v_{gj} - v_{nj} - v_{nj1}$$

(2)

The equations of the FBSM branch 2 can be obtained similarly. The AC current is composed of the current flowing through the FBSM branch 1 and the current flowing through the FBSM branch 2.

$$i_{gj} = i_{gj1} + i_{gj2}$$

Where,

$$i_{gj1} = i_{nj1} - i_{pj1} \tag{4}$$

(3)

$$i_{gj2} = i_{nj2} - i_{pj2} \tag{5}$$

The rated capacitor voltage of the FBSM branch 1 and that of the FBSM branch 2 are  $U_{smf1}$  and  $U_{smf2}$  respectively. The SM number of the FBSM branch 1 and that of the FBSM branch 2 are  $N_{F1}$  and  $N_{F2}$  respectively.

Under normal operating conditions, the rated voltages of the DC lines 1 and DC line 2 can be expressed as follows.

$$V_{dc1} = N_H U_{smh} + N_{F1} U_{smf1}$$

(6)

$$V_{dc2} = N_H U_{smh} + N_{F2} U_{smf2}$$

(7)

For each phase, the sum of the inserted HBSM is always  $N_H$  and the sum of the inserted FBSM is  $N_{FI}$  and  $N_{F2}$  respectively. In the normal operation condition, the SM capacitor voltage should be equal. If the rated voltages of HBSM and FBSM are all equal, the number of SMs invested in each branch has the following relationship.

$$\frac{N_{F1} + N_H}{N_{F2} + N_H} = \frac{V_{dc1}}{V_{dc2}}$$

(8)

When a pole to pole short-circuit fault occurs on the DC line 1, FBSMs connected to the DC line 1 are blocked. The HBSM and the parallel FBSM branches to which the DC line 2 is connected remain in operation. Due to the fault current blocking effect of FBSMs, the AC system cannot feed current to the fault point and the fault current on DC line1 is quickly blocked. Meantime, as the parallel FBSM branches are still working, the power transmission of DC line 2 is not affected.

According to [24], for a hybrid MMC with DC fault riding

through ability, the FBSM proportion should satisfy the following inequality.

$$\left\{N_{F1}, N_{F2}\right\} \ge N_H \tag{9}$$

The DC voltage level of the MTDC system is always uniform, the FBSM number  $N_{F1}$  and  $N_{F2}$  should also be the same. If the rated voltages of the DC line 1 and that of the DC line 2 are different, the FBSM number  $N_{F1}$  and  $N_{F2}$  can be calculated according to (8) and (9). Unless otherwise stated, the number of SMs in a FBSM branch is always equal to the number of SMs in a HBSM branch in the following analysis.

The sub-module capacitance is designed to limit the ripple of the capacitor voltage. According to [25], the capacitance of the FBSM branch 1 can be calculated as follows.

$$C_{smf1} = \frac{P_{ref1}}{3\xi U_{smf}V_{dc1}\omega m} \left[1 - \left(\frac{m\cos\varphi}{2}\right)^2\right]^{1.5}$$

(10)

where,  $\omega$  is the angular velocity corresponding to the grid frequency,  $\cos\varphi$  is the power factor, and *m* is the MMC modulation ratio.

In this paper, the grid frequency is 50Hz. The modulation ratio *m* and the power factor  $\cos\varphi$  are both set to 1. In (10), if the other parameters are all set, the sub-module capacitance is linear with the rated power. The capacitance of the FBSM branch 2 can be similarly designed according to the rated power of DC line 2. Furthermore, the power flowing through the HBSM branch is the sum of the two FBSM branches, and the HBSM capacitance is designed as follows.

$$C_{smh} = C_{smf1} + C_{smf2} \tag{11}$$

The topology shown in Fig. 3 can handle the case where the single-terminal grid supplies power to the other two terminals. Furthermore, the proposed topology can be extended to N-terminals DC grids with N parallel FBSM branches.

#### **III. CONTROL STRATEGIES**

As for the MTDC system in Fig. 2 (c), MMC 1 is connected to two MMCs (MMC 2 and MMC 3) via the DC line 1 and DC line 2. The parameters of the two DC lines and the MMC stations are usually different and the control modes of the two

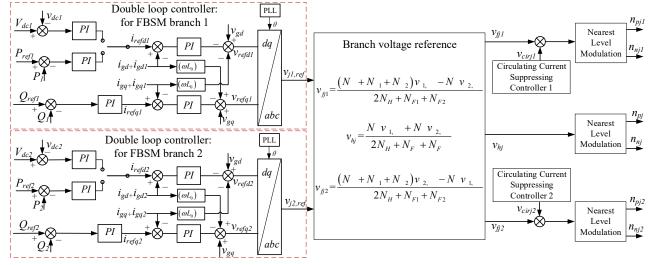

Fig. 4. The proposed MMC station control strategy.

DC outputs may be different. The conventional MMC control strategies are no longer applicable in the proposed MMC topology. Therefore, this paper proposes a corresponding MMC station control strategy for the proposed hybrid MMC topology.

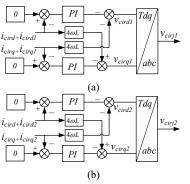

The proposed MMC station control strategy includes: branch voltage controller, circulating current suppression controller (CCSC), and nearest level modulation (NLM). The proposed MMC station control strategy is shown as Fig. 4 and the design of each controller is described in detail in this section.

# A. Branch Voltage Controller

In order to realize the function of the proposed topology, the corresponding branch voltage controller is designed according to the circuit relationship.

First, the AC output voltage of each branch can be defined as follows.

$$v_{hj} = \frac{v_{nj} - v_{pj}}{2}$$

(12)

$$v_{jj1} = \frac{v_{nj1} - v_{pj1}}{2} \tag{13}$$

$$v_{jj2} = \frac{v_{nj2} - v_{pj2}}{2} \tag{14}$$

According to (1) and (2), the relationship of the AC output voltages in the three-phase coordinate system is as follows.

$$L_0 \frac{di_{gj}}{dt} + L_0 \frac{di_{gj1}}{dt} = 2v_{gj} - 2v_{hj} - 2v_{fj1}$$

(15)

$$L_0 \frac{di_{gj}}{dt} + L_0 \frac{di_{gj2}}{dt} = 2v_{gj} - 2v_{hj} - 2v_{jj2}$$

(16)

In the synchronous rotating coordinate system, (15) and (16) can be rewritten as follows.

$$v_{hd} + v_{fd1} = v_{gd} - \frac{L_0}{2} \frac{d(i_{gd} + i_{gd1})}{dt} - \frac{\omega L_0}{2} (i_{gq} + i_{gq1})$$

(17)

$$v_{hq} + v_{fq1} = v_{gq} - \frac{L_0}{2} \frac{d(i_{gq} + i_{gq1})}{dt} + \frac{\omega L_0}{2} (i_{gd} + i_{gd1})$$

(18)

According to (17) and (18), the double loop controller of the FBSM branch 1 can been designed and the output voltage reference of the double loop controller is denoted as  $v_{j1,ref}$ . The double loop controller of the FBSM branch 2 can been designed in a similar way, and the output voltage reference of this controller is denoted as  $v_{j2,ref}$ . The double loop controllers are shown in Fig. 4.

The AC output voltage of the HBSM branch is defined as  $v_{hj}$ and the AC output voltages of the two FBSM branches are defined as  $v_{fjl}$  and  $v_{fj2}$  respectively. The double loop controller voltage reference is composed of the voltage of the HBSM branch and that of the FBSM branch.

$$v_{i1,ref} = v_{hi} + v_{fi1}$$

(19)

$$v_{j2,ref} = v_{hj} + v_{fj2}$$

(20)

According to (6) and (7), the branch reference voltages in (19) and (20) have a certain ratio. The results of the branch reference voltage can be calculated as follows.

$$v_{hj} = \frac{N_H v_{j1,ref} + N_H v_{j2,ref}}{2N_H + N_{F1} + N_{F2}}$$

(21)

Fig. 5. Circulating Current Suppressing Controller. (a) CCSC1; (b) CCSC2.

$$v_{jj1} = \frac{\left(N_H + N_{F1} + N_{F2}\right)v_{j1,ref} - N_H v_{j2,ref}}{2N_H + N_{F1} + N_{F2}}$$

(22)

$$v_{jj2} = \frac{\left(N_H + N_{F1} + N_{F2}\right)v_{j2,ref} - N_H v_{j1,ref}}{2N_H + N_{F1} + N_{F2}}$$

(23)

If CCSC is not considered, the output of the branch voltage controller can be directly used for NLM. Thus, the branch reference voltage of the upper and lower arms of each phase can be calculated according to (12) (13) and (14).

# B. Circulating Current Suppressing Controller

As for the proposed hybrid MMC topology, the circulating current is also different from the conventional MMC. So the CCSC should be redesigned. The circulating current of the conventional MMC is defined as follows.

$$i_{cirj} = \frac{1}{2} (i_{nj} + i_{pj})$$

(24)

Similarly, the FBSM branch circulating currents of the proposed hybrid MMC topology can be defined as follows.

$$i_{cirj1} = \frac{1}{2} \left( i_{nj1} + i_{pj1} \right)$$

(25)

$$i_{cirj1} = \frac{1}{2} \left( i_{nj1} + i_{pj1} \right)$$

(26)

According to (1) and (2), the circulating currents of the proposed hybrid MMC topology have the following relationship.

$$L_0 \frac{di_{cirj}}{dt} + L_0 \frac{di_{cirj1}}{dt} = \frac{1}{2} v_{dc1} - \frac{1}{2} \left( v_{pj} + v_{nj} \right) - \frac{1}{2} \left( v_{pj1} + v_{nj1} \right) \quad (27)$$

$$L_0 \frac{di_{cirj}}{dt} + L_0 \frac{di_{cirj2}}{dt} = \frac{1}{2} v_{dc2} - \frac{1}{2} \left( v_{pj} + v_{nj} \right) - \frac{1}{2} \left( v_{pj2} + v_{nj2} \right)$$

(28)

It can be seen from (27) and (28) that the circulating current of the FBSM branch 1 and that of the FBSM branch 2 do not affect each other. The circulating currents can be controlled separately. In the double frequency negative sequence rotating coordinate system, the structure of the CCSC are shown in Fig. 5.

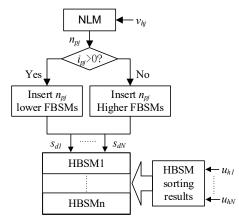

#### C. Nearest Level Modulation

The equalization and stability of SM voltage is the basis for stable operation of MMC. For the NLM Strategy, the SM capacitor voltage balancing is affected by the modulation reference, the current direction and the SM capacitor voltage sorting result. The proposed hybrid MMC topology contains two parallel FBSM branches and a HBSM branch each arm. Because the current flowing through each branch is inconsistent and the power loss of the FBSM is not the same as

Fig. 6. The modulation outputs of each branch.

the HBSM, it is difficult for the SM capacitor voltages of different branches to maintain a balance.

Therefore, in the control process, the reference voltages of different branches are separated. As long as the SM capacitor voltage in each branch is balanced and each branch follows the branch reference voltage, the proposed topology can operate stably. The modulation output results corresponding to each branch are shown in Fig. 6. On the basis of branch modulation, the SM capacitor voltage balance control of each branch can be realized

Taking the HBSM branch as an example, the SM capacitor voltage balancing control strategy is shown in Fig. 7. The input voltage of the NLM is  $v_{hj}$  and the number of inserting SMs  $n_{pj}$  of the HBSM branch can be obtained. When the current flowing through the HBSM branch is positive,  $n_{pj}$  submodules with the lower capacitor voltage are inserted. When the current flowing through the HBSM branch is negative,  $n_{pj}$  submodules with the higher capacitor voltage are inserted.

Through the above modulation and voltage balancing strategy, the SM capacitor voltages of each branch can be balanced. The sum of the inserting SM capacitor voltages follows its voltage reference. Thus, the SM capacitor voltages of the entire arm can achieve balancing.

# IV. VERIFICATION

In MATLAB/Simulink, the simulation model is constructed to verify the feasibility of the proposed MMC topology and

Fig. 7. Voltage balancing control strategy of the HBSM branch.

| TABLE II<br>Control Case |         |                                     |                 |  |  |

|--------------------------|---------|-------------------------------------|-----------------|--|--|

| Symbol                   | Value   | Symbol                              | Value           |  |  |

| $V_{g}$                  | 23 kV   | V <sub>dc1</sub> , V <sub>dc2</sub> | 50 kV           |  |  |

| $Q_{ref1}, Q_{ref2}$     | 0 Mvar  | $P_{refl}$                          | 50 MW           |  |  |

| $P_{2ef2}$               | 62.5 MW | $N_H$                               | 10              |  |  |

| $N_{Fl}$ , $N_{F2}$      | 10      | $C_{smh}$                           | 13.2 mF         |  |  |

| $C_{smf1}, C_{smf2}$     | 6.6 mF  | $U_{smh}$                           | 2.5 kV          |  |  |

| $U_{smf1}$ , $U_{smf2}$  | 2.5kV   | $L_0$                               | 9 mH            |  |  |

| $L_d$                    | 120 mH  | ξ                                   | $\pm \ 10 \ \%$ |  |  |

control strategies. The HVDC transmission system adopts bipolar transmission mode, and MMC 1 adopts the proposed hybrid MMC topology shown in Fig. 3. The preset fault is a bipolar short circuit fault on the DC line 1. The system parameters of the simulation model are shown in Table II. The DC voltage level of the MTDC system is uniform and the transmission power of each line is often different. In this case, the DC line 1 and DC line 2 have the same parameters except for active power, and the circuit parameters of FBSM branch 1 are consistent with that of FBSM branch 2. Both FBSM branch 1 and FBSM branch 2 adopt DC voltage and reactive power control modes.

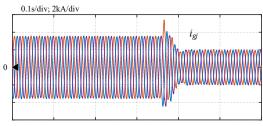

In the case, the DC line 1 has a DC bipolar short-circuit, and the FBSM branches connected to the DC line 1 are completely blocked after 5 milliseconds. The control loop 1 fails at the same time and the reference value of the control loop 1  $v_{j1,ref}$  is consistent with  $v_{j2,ref}$ . The HBSM branch and the FBSM branch 2 connected to the DC line 2 remain in normal operation and the DC line 2 still maintains power transmission. The results in this section are the internal variables of MMC1 or the system connected to MMC1.

Fig. 8 (a) shows the current of the DC line 1 and that of the DC line 2. Before the fault occurs, the current of the DC line 1 is stable at 1 kA and that of the DC line 2 is 1.25 kA. After the fault occurs, the DC current rises rapidly until the FBSM branches connected to the DC line 1 are blocked. Due to the presence of the DC limiting inductor, the current of the DC line 1  $i_{dc1}$  will be limited in a secure range. As the DC bipolar short-circuit fault occurs, the current of the DC line 2  $i_{dc2}$  has a

Fig. 8. The operation of the DC line. (a) DC current; (b) DC voltage.

Fig. 9. The AC grid current of MMC 1.

small fluctuation and quickly returns to its normal value.

Fig. 8 (b) shows the voltage of the DC line 1 and that of the DC line 2. Before the fault occurs, the two DC lines both operate in the normal condition and the rated voltage is 50 kV. The voltage of the DC line 1  $v_{dcl}$  decreases as soon as the fault occurs. This is due to DC fault and FBSM blocking will make the DC voltage drop to 0. Similar to the current, the voltage of the DC line 2 quickly returns to stability after a short period of fluctuation. After applying the proposed topology, the DC fault of the DC line 1 has little effect on the DC line 2 and the DC fault is isolated. The above simulation results illustrate the effectiveness of the proposed topology and control strategies.

Fig. 9 shows the AC grid current of MMC 1. It can be seen that the grid current will rise before the fault current is blocked. After the FBSMs connected to the DC line 1 are blocked, the transmission power of the AC grid falls from  $(P_1+P_2)$  to  $P_2$  and the peak of the grid current also falls. With the proposed hybrid MMC topology, the DC fault line is isolated and the AC grid can continue to transmit power to the fault-free DC lines.

Fig. 10(a) shows the upper arm currents which flow through the three-phase HBSM branches. Similar to the grid current, the currents flowing through the HBSM branches also rise before the fault current is blocked. The currents flowing through the FBSM branches are shown in Fig. 10(b) and Fig 10(c). As the FBSMs connected to the DC line 1 are blocked, the currents flowing through those branches decrease to 0. And the currents flowing through the remained FBSMs can return to normal operation after a period of fluctuation. It can be seen from Fig. 10 that the DC bipolar fault will have an impact on the system. However, by blocking the corresponding FBSMs, the fault current can be blocked, and the fault-free line can still operate normally.

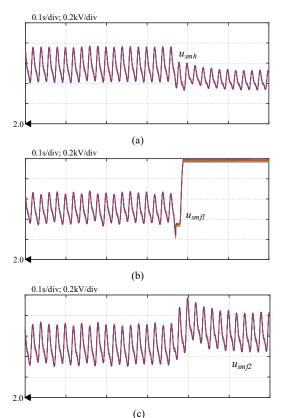

Take the upper arm of phase A as an example, the simulation results of the SM capacitor voltages are shown in Fig. 11. The SM capacitance was designed according to (10) and (11). After the fault occurs, the capacitor voltages of the HBSM branch are still at the rated value. However, the current flowing through the HBSM branch is reduced, so its capacitor voltage ripple will also decrease as shown in Fig. 11 (a). It can be seen from Fig. 11 (b) that the SM capacitor voltages of the FBSM branch 1 will rise as the FBSMs are blocked. This is because the fault current will charge the FBSM capacitor until the fault current is completely blocked. As shown in Fig. 11 (c), the capacitor voltages of the FBSM branch 2 can return to the rated voltage after a small increase.

As long as the fault is cleared, the MTDC system can return to normal operation. For permanent faults, the entire MMC can be restarted after the fault is cleared. In this case, the energy stored in capacitors will be consumed by the bypass resistors. For

The simulation results show that the proposed topology and control strategies can quickly block the fault current and isolate

Fig. 10. The upper arm current of each phase. (a) HBSM branch; (b) FBSM branch 1; (c) FBSM branch 2.

Fig. 11. The SM capacitor voltages of phase A upper arm. (a) HBSM branch;(b) FBSM branch 1; (c) FBSM branch 2.

temporary faults, the corresponding controller is initialized first, and then the blocked FBSMs are restored. In this case, the energy stored in capacitors will be transmitted to the load. The fault line under the DC bipolar short-circuit fault. The feasibility and effectiveness of the proposed topology have been verified.

#### V. TOPOLOGY COMPARISON

The DC fault protection schemes of the MMC-MTDC system are shown in Fig. 2. First, the HBSM-MMC cannot interrupt the DC fault current and DCCBs are necessary to protect the converter under DC short-circuit faults. Secondly, the hybrid MMC can use FBSMs to block DC fault current. Finally, the proposed MMC topology can block the DC fault current and isolate the fault line as shown in Fig. 2 (c). The device number and power loss of different topologies are listed in Table III.

According to (9), the number of FBSMs in the hybrid MMC cannot be less than the number of HBSMs. For the hybrid MMC in Table 3, the number of FBSMs is equal to the number of HBSMs. If the ratio of FBSM increases, the cost and loss of the hybrid MMC will further increase. A simplified MMC loss model is adopted to calculate the power loss of the topologies [26]. The parameters used in the power loss calculation are derived from the datasheet of the Infineon insulated gate bipolar transistor (IGBT) module FZI500R33HL3.

As shown in Table III, the HBSM-MMC has the lowest power loss and the least number of semiconductor devices. However, DCCBs are expensive and bulky [27][28]. Compared with the proposed MMC topology, the hybrid MMC requires fewer semiconductor devices, but its loss is higher and there is no fault isolation capability. Although the proposed MMC topology requires the most semiconductor devices, the current flowing through the FBSM branch is only half of the HBSM current. The smaller current stress can reduce the devices' cost and power loss. The proposed MMC topology has two FBSM branches, which increases the system complexity and cost, but it also has the aforementioned advantages compared to other topologies. It is a beneficial choice for the MTDC system.

|                            | TABLE III |                     |            |  |  |  |

|----------------------------|-----------|---------------------|------------|--|--|--|

| TOPOLOGY COMPARISON        |           |                     |            |  |  |  |

| Item                       | Proposed  | Hybrid MMC          | HB MMC +   |  |  |  |

| Item                       | topology  | $(N_{\rm H} = N/2)$ | DC breaker |  |  |  |

| MMC rated power            | 110MW     | 110MW               | 110MW      |  |  |  |

| DC voltage                 | 50kV      | 50kV                | 50kV       |  |  |  |

| No. of HBSMs per arm       | 10        | 10                  | 20         |  |  |  |

| No. of FBSMs per arm       | 2×10      | 10                  | 0          |  |  |  |

| SM capacitor voltage       | 2.5kV     | 2.5kV               | 2.5kV      |  |  |  |

| Power capacity per<br>HBSM | 1.83 MW   | 1.83 MW             | 1.83 MW    |  |  |  |

| Power capacity per FBSM    | 0.92 MW   | 1.83 MW             | 0          |  |  |  |

| No. of IGBTs per arm       | 100       | 60                  | 40         |  |  |  |

| No. of DC breakers         | 0         | 0                   | 16         |  |  |  |

| Conduction Loss            | 881.29kW  | 1307.90kW           | 880.29kW   |  |  |  |

| Switching Loss             | 168.45kW  | 96.99kW             | 64.78kW    |  |  |  |

| Total Loss                 | 1049.74kW | 1404.89kW           | 945.07kW   |  |  |  |

| Total loss ratio           | 0.95%     | 1.28%               | 0.86%      |  |  |  |

| DC fault blocking          | yes       | yes                 | yes        |  |  |  |

| DC fault isolation         | yes       | no                  | yes        |  |  |  |

### VI. CONCLUSION

In this paper, a MMC topology with partially hybrid branches is proposed. The proposed MMC topology is suitable for the MTDC system, as it can reduce the influence range of the DC fault and improve the reliability of the power supply. In order to selectively block the fault current and isolate the fault line, corresponding control strategies are also proposed. With the branch reference calculation and group voltage balancing method, the parallel FBSM branches can operate in different conditions. The power flow of the proposed topology can be flexibly controlled, which improves the availability of the proposed topology. The proposed topology and control strategies are verified by simulation results.

#### **REFERENCES:**

- N. Flourentzou, V. G. Agelidis and G. D. Demetriades, "VSC-based HVDC power transmission systems: an overview," *IEEE Trans. Power Electron.*, vol. 24, no. 3, pp. 592–602, Mar. 2009.

- [2] J.-H. Lee, J.-J. Jung, and S.-K. Sul, "Balancing of submodule capacitor voltage of hybrid modular multilevel converter under DC-Bus voltage variation of HVDC system," *IEEE Trans. Power Electron.*, vol. 34, no. 11, pp. 10458–10470, Nov. 2019.

- [3] G. Guo, Q. Song, B. Zhao, H. Rao, S. Xu, Z. Zhu and W. Liu, "Series-connected-based offshore wind farms with full-bridge modular multilevel converter as grid- and generator-side converters," *IEEE Trans. Ind. Electron.*, vol. 67, no. 4, pp. 2798–2809, Apr. 2020.

- [4] P. Denholm, R. Margolis, T. Mai, G. Brinkman, E. Drury, M. Hand, and M. Mowers, "Bright future: Solar power as a major contributor to the U.S. grid," *IEEE Power Energy Mag.*, vol. 11, no. 2, pp. 22–32, Mar./Apr. 2013.

- [5] H. Pang and X. Wei, "Research on key technology and equipment for zhangbei 500kV DC grid," in *International Power Electronics Conference*, *Niigata*, 2018, pp. 2343–2351.

- [6] Y. Wang, B. Zhang and X. Fan, "The overhead transmission line protection scheme for the voltage-source converter-based HVDC grids," *The Journal of Engineering*, vol. 2019, no. 16, pp. 674–679, Mar. 2019.

- [7] X. Li, Q. Song, W. Liu, H. Rao, S. Xu and L. Li, "Protection of nonpermanent faults on DC overhead lines in MMC-based HVDC systems," IEEE Trans. Power Del., vol. 28, no. 1, pp. 483–490, Jan. 2013.

- [8] Y. Xue and Z. Xu, "On the bipolar MMC-HVDC topology suitable for bulk power overhead line transmission: configuration, control, and DC fault analysis," *IEEE Trans. Power Del.*, vol. 29, no. 6, pp. 2420–2429, Dec. 2014.

- [9] L. Tang and B.T. Ooi, "Locating and isolating DC faults in multi-terminal DC systems," *IEEE Trans. Power Del.* vol. 22, no. 3, pp. 1877–1884, Jul. 2007.

- [10] J. Sneath and A. D. Rajapakse, "Fault detection and interruption in an earthed hvdc grid using rocov and hybrid dc breakers," *IEEE Trans. on Power Del.*, vol. 31, no. 3, pp. 973–981, June 2016.

- [11] R. E. Torres-Olguin and H. K. Hoidalen, "Inverse time overcurrent protection scheme for fault location in multi-terminal HVDC," in *IEEE Eindhoven PowerTech*. IEEE, June 2015.

- [12] L. Lin, Y. Lin, C. Xu, and Y. Chen, "Comprehensive analysis of capacitor voltage fluctuation and capacitance design for submodules in hybrid modular multilevel converter with boosted modulation index," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 7, no. 4, pp. 2369–2383, Dec. 2019.

- [13] H. Xiao, Z. Xu, L. Xiao, C. Gan, F. Xu, and L. Dai, "Components sharing based integrated HVDC circuit breaker for meshed HVDC grids," *IEEE Trans. Power Del.*, vol. 35, no. 4, pp. 1856–1866, Aug. 2020.

- [14] G. Liu, F. Xu, Z. Xu, Z. Zhang and G. Tang, "Assembly HVDC breaker for HVDC grids with modular multilevel converters," *IEEE Trans. Power Electron.*,vol. 32, no. 2, pp. 931–941, Feb. 2017.

- [15] W. Liu, G. Li, J. Liang, C. E. Ugalde-Loo, C. Li, and X. Guillaud, "Protection of single-phase fault at the transformer valve side of

FB-MMC-based bipolar HVdc systems," *IEEE Trans. Ind. Electron.*, vol. 67, no. 10, pp. 8416–8427, Oct. 2020.

- [16] S. Xu et al., "Dynamic model of the dc fault clearing process of a hybrid modular multilevel converter considering commutations of the fault current," *IEEE Trans. Power Electron.*, vol. 35, no. 7, pp. 6668–6672, Jul. 2020.

- [17] D. Keshavarzi, E. Farjah and T. Ghanbari, "Hybrid DC circuit breaker and fault current limiter with optional interruption capability," *IEEE Trans. on Power Electron.*, vol. 33, no. 3, pp. 2330–2338, Mar. 2018.

- [18] J. Xu, P. Zhao and C. Zhao, "Reliability analysis and redundancy configuration of MMC with hybrid submodule topologies," *IEEE Trans. Power Electron.*, vol. 31, no. 4, pp. 2720–2729, Apr. 2016.

- [19] R. Zeng, L. Xu, L. Yao and B. W. Williams, "Design and operation of a hybrid modular multilevel converter," *IEEE Trans. Power Electron.*, vol. 30, no. 3, pp. 1137–1146, Mar. 2015.

- [20] Y. Dong, J. Tang, H. Yang, W. Li, and X. He, "Capacitor voltage balance control of hybrid modular multilevel converters with second- order circulating current injection," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 7, no. 1, pp. 157–167, Mar. 2019.

- [21] R. Zeng, L. Xu, L. Yao, and D. J. Morrow, "Precharging and DC fault ride-through of hybrid MMC-based HVDC systems," *IEEE Trans. Power Del.*, vol. 30, no. 3, pp. 1298–1306, Jun. 2015.

- [22] M. Lu, J. Hu, R. Zeng, W. Li and L. Lin, "Imbalance mechanism and balanced control of capacitor voltage for a hybrid modular multilevel converter," *IEEE Trans. Power Electron.*, vol. 33, no. 7, pp. 5686–5696, July 2018.

- [23] R. Li, L. Xu, D. Holliday, F. Page, S. J. Finney and B. W. Williams, "Continuous operation of radial multiterminal HVDC systems under DC fault," *IEEE Trans. Power Del.*, vol. 31, no. 1, pp. 351–361, Feb. 2016.

- [24] J. Sheng et al., "Active thermal control for hybrid modular multilevel converter under overmodulation operation," *IEEE Trans. Power Electron.*, vol. 35, no. 4, pp. 4242–4255, Apr. 2020.

- [25] J. Hu, M. Xiang, L. Lin, M. Lu, J. Zhu, and Z. He, "Improved design and control of fbsm mmc with boosted ac voltage and reduced dc capacitance," *IEEE Trans. Ind. Electron.*, vol. 65, no. 3, pp. 1919–1930, Mar. 2018.

- [26] L. Yang, Y. Li, Z. Li, P. Wang, F. Gao and F. Xu, "A simplified loss model of modular multilevel converter," in *IEEE PES Asia-Pacific Power* and Energy Engineering Conference, 2016, pp. 661–665.

- [27] R. Majumder, S. Auddy, B. Berggren, G. Velotto, P. Barupati, and T. U. Jonsson, "An alternative method to build DC switchyard with hybrid DC breaker for DC grid," *IEEE Trans. Power Del.*, vol. 32, no. 2, pp. 713–722, Apr. 2017.

- [28] S. Zhang, G. Zou, X. Wei and C. Sun, "Diode-bridge multiport hybrid DC circuit breaker for multiterminal DC grids," *IEEE Trans. Ind. Electron.*, vol. 68, no. 1, pp. 270-281, Jan. 2021.

**Yongyang Chen** (S'19) was born in Hefei, Anhui Province, China, in 1996. He received B.Eng. Degree in electrical engineering from Wuhan University, Wuhan, China, in 2017, where he is currently working toward the Ph.D. degree. His main research interests include the modular multilevel converter and dynamic

analysis of power converters.

Shangzhi Pan (M'08-SM'14) received his B.Sc. and M.Sc. in Electrical Engineering from Zhejiang University, China, in 1998 and 2001, respectively, and the Ph.D. from Queen's University in 2008. He joined the College of Electrical Engineering, Wuhan University, China in 2018, where he currently is a professor. He is also an adjunct faculty at Queen's Center of Energy and Power Electronics Applied Research Laboratory (ePOWER) since 2014. Previously he worked as the VP of research and development at SPARQ systems, a Queen's Spun-off photovoltaic microinverter company since 2010. He was a senior research engineer at Queen's University from 2008 to 2013. His research interests include digital control techniques for power converters, grid-connected inverters, voltage regulators for computing systems, power converters for renewable energy sources, and power converters for electric vehicles.

**Meng Huang** (S'11–M'13) received the BEng. And MEng. degrees from the Huazhong University of Science and Technology, Wuhan, China, in 2006 and 2008, respectively, and the Ph.D. degree from the Hong Kong Polytechnic University, Hong Kong, in 2013. He is currently an Associate Professor of the School of Electrical Engineering and Diversity Wuhan China

Automation, Wuhan University, Wuhan, China.

His research interests include nonlinear analysis of power converters and power electronics reliability. He received the best paper award of the IEEE Transactions on Power Electronics in 2016. He serves as the Guest Associate Editor of IEEE Journal of Emerging and Selected Topics of Power Electronics, IEEE Journal of Emerging and Selected Topics of Circuits and Systems, and the Associate Editor of IEEE Access.

Zili Zhu was born in Huangshi, Hubei, China in 1997. He received the B.S. degrees in electronic engineering from the Wuhan University, Wuhan, in 2019 and is currently pursuing Ph.D. degree in electronic engineering from Zhejiang University, Hangzhou, Zhejiang, in 2019.

Yushuang Liu (S'18) received her B.Eng. degree in Electrical Engineering in 2016 from Wuhan University, Wuhan, China, where she is currently working toward her Ph.D. degree. From Oct. 2019 to Oct. 2020, she was a visiting Ph.D. student with the Department of Electrical, Electronic and Computer Engineering, the University of Western Australia, Western Australia,

Australia. Her main research interests include the modeling and stability analysis of power converters.

Xiaoming Zha (M'02) was born in Huaining, Anhui Province, China, in 1967. He received B.S., M.S., and Ph.D. degrees in electrical engineering from Wuhan University, Wuhan, China, in 1989, 1992, and 2001, respectively. He was a Postdoctoral Fellow at the University of Alberta, Canada from 2001 to 2003. He has been a Faculty Member of Wuhan University since 1992, and became a Professor in 2003. He is currently the Deputy Dean in the school of electrical engineering, Wuhan University, Wuhan, China. His research interests include power electronic converter, the application of power electronics in smart grid and renewable energy generation, the analysis and control of microgrid, the analysis and control of power quality, and frequency control of high-voltage high-power electric motors.