# Arm Voltage Balancing Control of Modular Multilevel Resonant Converter

Jianjia Zhang, Shuai Shao, Member, IEEE, Yucen Li, Junming Zhang, Senior Member, IEEE, and Kuang Sheng, Senior Member, IEEE,

Abstract—Modular multilevel resonant converter is an promising candidate for high voltage applications since it has advantageous features, such as high efficiency, high voltage capability and easy fault-tolerant operation. However, the inequality of arm inductance in practice will lead to imbalance between the upper and lower arm voltages, which will induce large ripples in the circulating current and a dc bias on the voltage generated by modular circuits. To compensate for the voltage imbalance, effects of arm duty cycle changes on arm voltages are discussed. An arm voltage balancing control method is proposed: adjust arm duty cycle according to arm voltage deviation in every switching cycle. Simulation and experimental results are presented to validate the theoretical analysis and the proposed control method.

*Index Terms*— modular multilevel resonant (MMR) converter, arm voltage balancing, duty cycle.

## I. INTRODUCTION

**D**<sup>C</sup> Transformers (DCTs) have gained lot of attention with the rapid development of DC distribution systems. They are crucial components in dc grids to interconnect different voltage levels and achieve the necessary isolation. Therefore, high power converters with high voltage capability, high efficiency and smaller volume and weight are desired for DC transformers [1] [2].

At the present time, the voltage and power ratings of commercial semiconductor devices are far below the requirements of high voltage applications. So converters are supposed to be designed carefully to meet the demand. Various efforts have been made to provide DC transformer topologies. With advantages such as modularity, high reliability and high power rating, the modular multilevel converter (MMC) is one of the widely employed high-voltage techniques [3]-[5]. Combining MMC with the dual active bridge (DAB) converter is a solution to construct an isolated DC transformer [6]. To reduce the transformer size, quasi-two-level modulation can be implemented for the converter, where the fundamental ac

Manuscript received August 18, 2020; Revised September 17, 2020; Accepted November 19, 2020. Date of publication December 25, 2020; Date of current version December 18, 2020.

This work is supported by the National Key Research and Development Program of China (No. 2016YFB0100603) and National Natural Science Foundation of China (No. 51877193). (Corresponding Author: Shuai Shao)

The authors are with the College of Electrical Engineering, Zhejiang University, Hangzhou 310027, Zhejiang Province, China (e-mail: jianjia@zju.edu.cn; shaos@zju.edu.cn; yucenlee@zju.edu.cn; zhangjm@zju.edu.cn; shengk@zju.edu.cn).

Digital Object Identifier 10.30941/CESTEMS.2020.00037

frequency is the same as the switching frequency [7]. The converter operates similar to the traditional DAB, hence zero voltage switching (ZVS) of power devices cannot be achieved in the whole operation region, which means considerable switching loss [8]. In addition, the reactive current in the converter is high which increases the conduction loss of power devices. To avoid the drawbacks, LLC resonant converter can be used. Based on this idea, a modular multilevel resonant (MMR) dc-dc converter with wide voltage regulation range was proposed in [9].

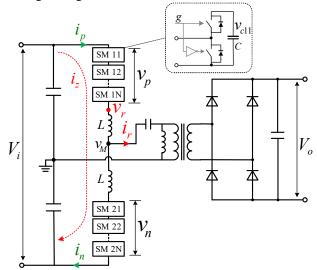

As shown in Fig. 1, the primary-side single power transistor in LLC resonant converter is replaced by modular structure and the square voltage generated by the modular circuits is applied to a resonant circuit. The switching frequency of submodule power transistors is equal to the fundamental ac frequency which is similar to conventional LLC converter, hence the power transistors can achieve ZVS-on. Besides, compared with conventional resonant converters, the MMR converter can operate in a wide input voltage range by inserting certain number of submodules according to the input voltage level. To limit the circulating current in the modular circuits, two inductors ( $L_1$  and  $L_2$ ) are inserted into the arms and they also operate as the resonant inductor. However, in practice, the arm inductance deviation is inevitable, which will lead to imbalance between the upper and lower arm voltages. As a result, the generated square voltage is not symmetrical which will induce negative effects on the converter. Therefore, arm voltage balancing is a significant issue for the MMR converter.

Fig. 1. Topology of MMR dc-dc converter.

Various arm voltage-balancing strategies have been proposed to compensate for the arm voltage imbalance in MMCs. In [10], the operation of MMCs is studied under asymmetry of the upper and lower arm impedance. Then a controller based on the instantaneous power theory and proportional-resonant scheme is designed. In [11], decoupled control model of MMC under asymmetric parameter conditions is established, and an optimized control method of arm capacitor voltage balancing is proposed. Similar control strategies for arm voltage balancing are also presented in [12]-[14]. However, these control strategies are not suitable for a MMR converter because it operates at medium-frequency which makes the accurate sampling of arm currents difficult. To avoid current sampling, an arm voltage balancing control method based on inter-arm phase-shift modulation scheme is presented in [15], which needs to combine the scheme with inter-submodule phase-shift modulation scheme and increases the complexity of control system.

To achieve arm voltage balancing in MMR converter, the generating mechanism and effects of arm voltage imbalance are studied in this paper. Meanwhile, the effects of arm duty cycle changes on arm voltage are discussed. On this basis, a control method to balance arm voltages in MMR converter is proposed: adjust arm duty cycle according to the arm voltage deviation in every switching cycle. Simulation and experimental results demonstrate the capability of the proposed method in arm voltage balancing.

# II. MECHANISM AND EFFECTS OF THE ARM VOLTAGE IMBALANCE

Similar to MMC, the arm current in MMR is composed of a dc component and an ac component. Hence, the arm currents  $i_p$  and  $i_n$  can be expressed as:

$$\begin{cases} i_{p} = i_{z} + \frac{1}{2}i_{r} \\ i_{n} = i_{z} - \frac{1}{2}i_{r} \end{cases}$$

(1)

where  $i_z$  is the circulating current,  $i_r$  is the resonant current.

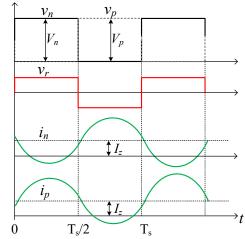

Ignoring the small phase-shift between submodules, the theoretical waveforms of arm voltages  $(v_p \text{ and } v_n)$  and currents  $(i_p \text{ and } i_n)$  are shown in Fig. 2. Assume  $i_r = I_r \sin(\omega t - \theta)$ , then the equivalent current flowing through the submodule capacitors during a switching cycle can be obtained as:

$$i_{eq} = \frac{1}{T_s} \int_0^{T_s/2} (i_z - \frac{1}{2}i_r) dt = \frac{1}{T_s} \int_{T_s/2}^{T_s} (i_z + \frac{1}{2}i_r) dt$$

$$= \frac{I_z}{2} - \frac{I_r \cos\theta}{2\pi}$$

(2)

where  $\theta$  is phase shift between the arm output voltage  $v_r$  and the resonant current  $i_r$ ,  $T_s$  is the switching period;  $I_z$  is the amplitude of  $i_z$ . Considering  $\Delta Q = C\Delta V = i\Delta t$ , the sign of  $i_{eq}$ determines the charge/discharge of submodule capacitors. Hence, (2) reveals that, in every switching cycle, the circulating current  $i_z$  charges the submodule capacitors, whereas the ac current discharges them since  $\theta$  is much smaller than 90 degree. In steady state,  $i_{eq}$  must be equal to 0, otherwise the capacitor voltage will keep increasing or decreasing, therefore

$$I_z = \frac{I_r \cos \theta}{\pi} \tag{3}$$

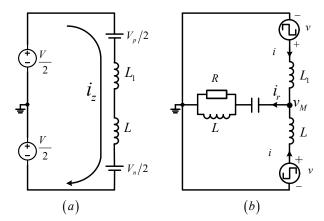

The arm voltages  $v_p$  and  $v_n$  can also be considered as composed of a dc component  $(V_p/2, V_n/2)$  and an ac component  $(v_{pa}, v_{na})$ . The equivalent circuits of dc current path and ac current path are illustrated in Fig. 3. The ac voltage and current directions have been redefined in Fig. 3 (b) for convenience. According to Kirchhoff's voltage and current law, the following equations can be obtained:

$$\begin{cases} i_{pa}(t) + i_{na}(t) = i_{r}(t) \\ v_{pa}(t) = v_{M}(t) + L_{1} \frac{di_{pa}(t)}{dt} \\ v_{na}(t) = v_{M}(t) + L_{2} \frac{di_{na}(t)}{dt} \end{cases}$$

(4)

where  $i_{pa}$  and  $i_{na}$  are the ac components of  $i_p$  and  $i_n$  respectively, L<sub>1</sub> and L<sub>2</sub> is the arm inductance.

Fig. 2. Theoretical waveforms of voltages and currents in MMR.

Fig. 3. Equivalent circuits of (a) dc current path and (b) ac current path

According to (4), when the arm voltages are balanced ( $v_{pa} = v_{na}$ ), if L<sub>1</sub>=L<sub>2</sub>, we will have  $i_{pa} = i_{na} = 0.5i_r$  which is consistent with (1). However, the component variation is inevitable in practice. Take L<sub>1</sub> < L<sub>2</sub> for example, assume the upper and lower arm voltages are initially balanced ( $v_{pa} = v_{na}$ ),

then  $i_{pa}$  will be larger than  $i_{na}$  according to (4) while the dc current  $i_z$  in the upper and lower arms is equal. As a result, the capacitors in the upper arm are discharged more than the capacitors in the lower arm, as (2) reveals. Hence, the upper arm voltage  $v_p$  will be lower than the lower arm voltage  $v_n$  during the next switching cycle. Referring back to (4), as  $v_p$  decreases,  $i_{pa}$  will become smaller. Similarly,  $i_{na}$  will become larger as  $v_n$ increases. Therefore, this is a negative feedback process, which ends when  $i_{pa}$  and  $i_{na}$  become equal again. Therefore, the converter will enter into another steady state with a constant deviation between the upper and lower arm voltages.

In Fig. 1, according to the Kirchhoff's voltage law, the voltage across the arm inductors can be obtained as

$$u_L = V_i - v_p - v_n \tag{5}$$

where  $V_i$  is the input voltage. In the steady state, when the lower arm is inserted,  $u_L$  is equal to  $V_i - V_n$ . When the upper arm is inserted,  $u_L$  is equal to  $V_i - V_p$ . If the arm voltages are balanced,  $V_p = V_n$ , then  $u_L$  will be 0 in every switching cycle. Otherwise, a square-wave voltage  $(u_L)$  will be applied across the arm inductors, which will induce large ripples in circulating current  $i_z$  and may saturate the arm inductors.

Similarly, the voltage generated by the modular circuit ( $v_r$ ) is written as

$$\begin{cases} v_r = V_n - \frac{V_i}{2}, & 0 \sim \frac{T_s}{2} \\ v_r = \frac{V_i}{2} - V_p, & \frac{T_s}{2} \sim T_s \end{cases}$$

(6)

which reveals that the imbalance of arm voltages will lead to a dc bias on the arm output voltage  $v_r$  and increases voltage stress of the resonant capacitor.

### III. ARM VOLTAGE BALANCING CONTROL METHOD

In order to compensate voltage imbalance caused by the inequality of arm inductance, a control method is proposed in this section. The basic idea is to adjust the arm duty cycle according to the arm voltage deviation.

Add a small disturbance to the duty cycle of the upper arm ( $\Delta d$ ), according to (2), the equivalent current flowing through the submodule capacitors in upper arm during a switching cycle is calculated as:

$$I_{eq} + \Delta i_{eq} = \frac{1}{T_s} \int_{(\frac{1}{2} - \Delta d)T_s}^{T_s} (I_z + \frac{1}{2}I_r \sin(\omega t - \theta))dt$$

= $(\frac{1}{2} + \Delta d)I_z - \frac{I_r}{4\pi} [\cos\theta + \cos(2\pi \cdot \Delta d + \theta)]$  (7)

Substitute (3) into (7), then the variation of  $i_{eq}$  caused by duty cycle change  $\Delta d$  can be derived as:

$$\Delta i_{eq} = \Delta d \cdot I_z - \frac{I_r}{4\pi} \left[ \cos(2\pi \cdot \Delta d + \theta) - \cos\theta \right]$$

=  $I_z (\Delta d + \frac{1}{4} - \frac{1}{4} \cos(2\pi \cdot \Delta d)) + \frac{I_r}{4\pi} \sin(2\pi \cdot \Delta d) \sin\theta$  (8)

Considering  $\Delta d$  and  $\theta$  are very small,  $\Delta i_{eq}$  can be simplified as:

$$\Delta i_{eq} \approx I_z \Delta d \tag{9}$$

which reveals that the equivalent current flowing through the submodule capacitors will increase as the arm duty cycle increases. In other words, the arm voltages can be balanced by adjusting the arm duty cycle: increase the duty cycle of the arm with lower voltage (decrease the duty cycle of the arm with higher voltage).

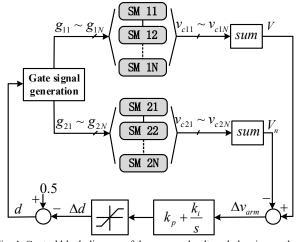

Fig. 4 shows the block diagram of the proposed arm voltage balancing method. Considering a MMR converter with N submodules in each arm,  $v_{c11} \sim v_{c1N}$  and  $v_{c21} \sim v_{c2N}$  are the sampling voltages of submodule capacitors in the upper and lower arms, respectively. The upper and lower arm voltages are obtained as the sum of their submodule capacitor voltages. Then the difference between the arm voltages is calculated:  $\Delta v_{arm} = V_p - V_n$ .  $\Delta v_{arm}$  is the input of a PI controller whose output is the duty cycle variation  $\Delta d$  and is limited by a saturation. Finally, the duty cycle d of the upper arm for the next switching cycle (while the duty cycle of the lower arm is 1 - d) is calculated by 0.5 minus  $\Delta d$  and sent to the gate signal generation unit.

The proposed arm voltage balancing method does not rely on accurate current sampling, and the voltage sampling of submodule capacitors is also necessary for inter-submodule voltage balancing [17]. In addition, the control algorithm is not complicated to implement. Hence, the proposed method will not increase the complexity of control system and is also suitable for other converters with MMC structure.

Fig. 4. Control block diagram of the proposed voltage balancing method.

## IV. SIMULATION RESULTS

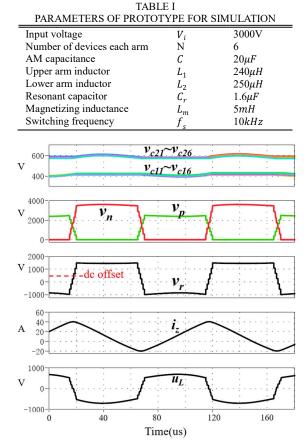

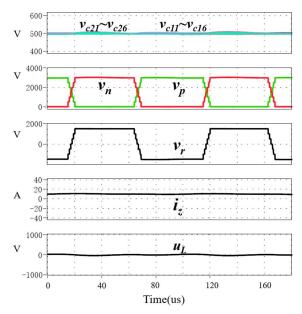

To verify the above theoretical analysis and the proposed method, simulations with parameters listed in Table I, are conducted in PLECS. The lower arm inductance is 4% larger than the upper arm inductance. Fig. 5 shows simulation results without the proposed arm voltage balancing method. Voltage of the upper arm  $v_p$  is lower than that of the lower arm  $v_n$ obviously, which is consistent with the analysis in Section II. In addition, the voltage across arm inductors is a square-wave voltage and induces large ripples in the circulating current. With the proposed method, as shown in Fig. 6, the upper and lower arm voltages are well balanced, and the dc bias in arm

Fig. 5. Simulation results without arm voltage balancing method when 4% difference in arm inductance is considered.

Fig. 6. Simulation results with the proposed balancing method when 4% difference in arm inductance is considered. output voltage  $v_r$  and the large ripples in the circulating current  $i_z$  are both eliminated.

## V. EXPERIMENTAL RESULTS

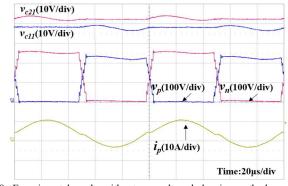

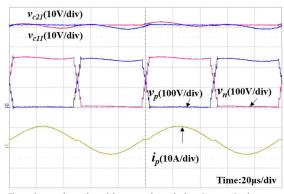

To validate the presented analysis and simulations, downscaled experiments are conducted on a MMR prototype with parameters listed in Table II. Photographs of the prototype hardware is shown in Fig. 7. The proposed control method is implemented by a hierarchical control system in the prototype, similar to the inter-submodule voltage balancing method in [17]. The core controller is implemented with FPGA where the sampling voltages are processed and gate signals are generated. Experimental results without and with the proposed arm voltage balancing method are shown in Fig. 8 and Fig. 9, respectively.  $v_{c11}$  and  $v_{c21}$  are the submodule capacitor voltages from the upper and lower arms. As illustrate in Fig. 8, parameter even though the nominal value of two inductors are both 240uH. The variations are inevitable which results in the obvious deviation of arm voltages without the proposed method. The results in Fig. 9 demonstrate that the arm voltages are well balanced when the proposed method is implemented.

| TABLE II                                |         |            |

|-----------------------------------------|---------|------------|

| PARAMETERS OF PROTOTYPE FOR EXPERIMENTS |         |            |

| Input voltage                           | $V_i$   | 250V       |

| Number of devices each arm              | Ň       | 6          |

| AM capacitance                          | С       | $20\mu F$  |

| Upper arm inductor                      | $L_1$   | 240µH      |

| Lower arm inductor                      | $L_2$   | 240µH      |

| Resonant capacitor                      | $C_r$   | $1.6\mu F$ |

| Magnetizing inductance                  | $L_m$   | 5mH        |

| Switching frequency                     | $f_{s}$ | 10kHz      |

| Transformer ratio                       | n       | 2:1        |

Fig. 7. Photographs of the prototype hardware.

Fig. 8. Experimental results without arm voltage balancing method.

Fig. 9. Experimental results with arm voltage balancing method.

#### VI. CONCLUSION

This paper analyzes the mechanism of arm voltage imbalance caused by inequality of arm inductance in MMR converter. Then an arm voltage balancing method by adjusting the arm duty cycle is proposed. Simulation and experimental results demonstrate that, with the proposed method, arm voltages are well balanced. The ripples of the circulating current and the dc bias in resonant voltage caused by the arm voltage imbalance are suppressed. The proposed method does not rely on arm current sampling and can be combined with the intersubmodule voltage balancing method, which is easy to be implemented.

#### REFERENCES

- X. She, A. Q. Huang and R. Burgos, "Review of Solid-State Transformer Technologies and Their Application in Power Distribution Systems," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 1, no. 3, pp. 186-198, Sept. 2013.

- [2] S. Cui, N. Soltau and R. W. De Doncker, "A High Step-Up Ratio Soft-Switching DC–DC Converter for Interconnection of MVDC and HVDC Grids," *IEEE Transactions on Power Electronics*, vol. 33, no. 4, pp. 2986-3001, April 2018.

- [3] A. A. Jamshidi Far, M. Hajian, D. Jovcic and Y. Audichya, "High-power modular multilevel converter optimal design for DC/DC converter applications," *IET Power Electronics*, vol. 9, no. 2, pp. 247-255, 10 2 2016.

- [4] I. A. Gowaid, G. P. Adam, S. Ahmed, D. Holliday and B. W. Williams, "Analysis and Design of a Modular Multilevel Converter With Trapezoidal Modulation for Medium and High Voltage DC-DC Transformers," *IEEE Transactions on Power Electronics*, vol. 30, no. 10, pp. 5439-5457, Oct. 2015.

- [5] S. Kenzelmann, A. Rufer, D. Dujic, F. Canales and Y. R. de Novaes, "Isolated DC/DC Structure Based on Modular Multilevel Converter," *IEEE Transactions on Power Electronics*, vol. 30, no. 1, pp. 89-98, Jan. 2015.

- [6] T. Lüth, M. M. C. Merlin, T. C. Green, F. Hassan and C. D. Barker, "High-Frequency Operation of a DC/AC/DC System for HVDC Applications," *IEEE Transactions on Power Electronics*, vol. 29, no. 8, pp. 4107-4115, Aug. 2014.

- [7] I. A. Gowaid, G. P. Adam, A. M. Massoud, S. Ahmed, D. Holliday and B. W. Williams, "Quasi Two-Level Operation of Modular Multilevel Converter for Use in a High-Power DC Transformer With DC Fault Isolation Capability," *IEEE Transactions on Power Electronics*, vol. 30, no. 1, pp. 108-123, Jan. 2015.

- [8] S. Shao, M. Jiang, W. Ye, Y. Li, J. Zhang and K. Sheng, "Optimal Phase-Shift Control to Minimize Reactive Power for a Dual Active Bridge DC– DC Converter," *IEEE Transactions on Power Electronics*, vol. 34, no. 10, pp. 10193-10205, Oct. 2019.

- [9] S. Shao et al., "A Modular Multilevel Resonant DC–DC Converter," *IEEE Transactions on Power Electronics*, vol. 35, no. 8, pp. 7921-7932, Aug.

2020.

- [10] Y. Zhou, D. Jiang, J. Guo, P. Hu and Y. Liang, "Analysis and Control of Modular Multilevel Converters Under Unbalanced Conditions," *IEEE Transactions on Power Delivery*, vol. 28, no. 4, pp. 1986-1995, Oct. 2013.

- [11] C. Sun, J. Zhang, X. Cai and G. Shi, "Analysis and Arm Voltage Control of Isolated Modular Multilevel DC–DC Converter with Asymmetric Branch Impedance," *IEEE Transactions on Power Electronics*, vol. 32, no. 8, pp. 5978-5990, Aug. 2017.

- [12] Xiaoming Yuan, W. Merk, H. Stemmler and J. Allmeling, "Stationaryframe generalized integrators for current control of active power filters with zero steady-state error for current harmonics of concern under unbalanced and distorted operating conditions," *IEEE Transactions on Industry Applications*, vol. 38, no. 2, pp. 523-532, March-April 2002.

- [13] R. Lizana, M. A. Perez, S. Bernet, J. R. Espinoza and J. Rodriguez, "Control of Arm Capacitor Voltages in Modular Multilevel Converters," *IEEE Transactions on Power Electronics*, vol. 31, no. 2, pp. 1774-1784, Feb. 2016.

- [14] F. Deng, Y. Tian, R. Zhu and Z. Chen, "Fault-Tolerant Approach for Modular Multilevel Converters Under Submodule Faults," *IEEE Transactions on Industrial Electronics*, vol. 63, no. 11, pp. 7253-7263, Nov. 2016.

- [15] R. Zeng, L. Xu, L. Yao and S. J. Finney, "Analysis and Control of Modular Multilevel Converters under Asymmetric Arm Impedance Conditions," *IEEE Transactions on Industrial Electronics*, vol. 63, no. 1, pp. 71-81, Jan. 2016.

- [16] B. Li, S. Shi, B. Wang, G. Wang, W. Wang and D. Xu, "Fault Diagnosis and Tolerant Control of Single IGBT Open-Circuit Failure in Modular Multilevel Converters," *IEEE Transactions on Power Electronics*, vol. 31, no. 4, pp. 3165-3176, April 2016.

- [17] S. Shao, M. Jiang, J. Zhang and X. Wu, "A Capacitor Voltage Balancing Method for a Modular Multilevel DC Transformer for DC Distribution System," *IEEE Transactions on Power Electronics*, vol. 33, no. 4, pp. 3002-3011, April 2018.

Jianjia Zhang was born in Henan, China, in 1996. He received the B.S. degree in electrical engineering, in 2018, from Zhejiang University, Hangzhou, China, where he is currently working toward the M.S. degree with the College of Electrical Engineering.

His current research focuses on highefficiency dc/dc converters.

**Shuai Shao** (M'17) received the B.S. degree from Zhejiang University, China, in 2010, and the Ph.D. degree in electrical and electronic engineering from the University of Nottingham, U.K., in 2015. In 2015, he joined the College of Electrical Engineering, Zhejiang University, as a Lecturer. In Jan. 2020, he was promoted as an associate professor.

His research interests include solid-state transformers, bidirectional dc-dc converters, and fault detection in power converters. He has published more than 40 peer-reviewed technical papers.

He serves as a Guest Associated Editor of Journal of Emerging and Selected Topics in Power Electronics.

**Yucen Li** was born in Hubei, China, in 1995. He received the B.S. and the M.S. degrees from Zhejiang University, Hangzhou, China, in 2017 and 2020, respectively, all in electrical engineering.

His current research focuses on highefficiency dc/dc converters. Computer Engineering, Michigan State University, East Lansing, MI, USA. His research interests include power electronics system integrations, power management, and highefficiency converters.

Dr. Zhang is an Associate Editor for the IEEE TRANSACTIONS ON INDUSTRY APPLICATIONS and CPSS Transactions Power Electronics and Application.

Junming Zhang (Senior, Member) received the B.S., M.S., and Ph.D. degrees from Zhejiang University, Hangzhou, China, in 1996, 2000, and 2004, respectively, all in electrical engineering. He is currently a Professor with the College of Electrical Engineering, Zhejiang University. From 2010 to 2011,

he was a Visiting Scholar with the Department of Electrical and

Kuang Sheng (Senior Member, IEEE) received the B.Sc. degree from Zhejiang University, Hangzhou, China, in 1995, and the Ph.D. degree from HeriotWatt University, Edinburgh, U.K., in 1999. He is currently a Professor with Zhejiang University. His current research interests

include all aspects of power semiconductor devices, and ICs on SiC and Si.