# Failure Analysis of Power Electronic Devices and Their Applications under Extreme Conditions

Yifei Luo, Fei Xiao\*, Bo Wang, and Binli Liu

(National Key Laboratory of Science and Technology on Vessel Integrated Power System,

Naval University of Engineering, Wuhan, 430033, China)

Abstract: Power electronic devices are the core components of modern power converters, not only for normal applications, but also for extreme conditions. Current design of power electronic devices require large redundancies for reliability. This results in huge volume and weight for a large-capacity power converter, especially for some extreme applications. Therefore, to optimize the power density, the reliability of power devices needs to be investigated first in order to obtain the accurate operational margin of a power device. Although much research on device failure analysis has been reported, there still lacks efficient failure evaluation methods. This paper first summarizes the current failure research. Then, a three-step failure analysis method of power electronic devices is proposed as: failure information collection, failure identification and mechanism, and failure evaluation. The physics-based modeling method is emphasized since it has a strong relationship with the device fundamentals. After that, power electronic device applications under extreme conditions are introduced and a design method of device under extreme conditions is proposed based on the thermal equilibrium idea. Finally, the challenges and prospects to improve the power device reliability under extreme conditions are concluded.

**Keywords:** Power electronic device, failure mechanism, failure evaluation, physics-based modeling, extreme conditions, thermal equilibrium

#### 1 Introduction

Power electronic devices are the core components of modern power converters, not only for normal applications such as energy saving, electrical traction, intelligent grid etc, but also for extreme applications such as high-voltage short-circuit breaking, three deeps (deep space, deep sea, deep earth), three poles, etc.[1-4]. Current applications of power electronic devices require large redundancies for device reliability issues. However, this brings huge weight and volume to the power converters, and difficulties to the device control strategy because of the large amount of serial/parallel connected devices. To optimize the device power density, the safety margin of power devices needs to be clarified accurately, especially for extreme applications. Therefore, failure analysis of power electronic devices becomes the fundamental aspect of extreme applications because it explains why the device fails and more importantly, it helps define the safety margin of the device operation.

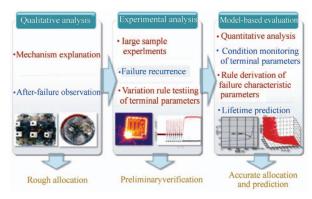

In the past few years, many research papers on power device failures have been published<sup>[5-39]</sup>. From the perspective of analyzing methods, previous research can be classified into three categories as shown in Fig.1: 1) qualitative analysis; 2) experimental analysis; 3) model-based evaluation. The first one gives rough allocations of the device

failures since it lacks enough quantitative analysis and is mainly based on after-failure observations. For example, the reconstruction of the aluminum metallization in IGBT multichip modules has been first reported in [5, 6], adhesion failures of AlN ceramic substrates due to the peeling of the copper metallization have been reported in [7], thermal mechanisms on IGBT modules are reported in [8-11], and failure modes and mechanisms at different stages of short-circuit have been analyzed in [12-15]. The second category gives preliminary failure verification because it uses large sample of experiments to make failures reoccur and therefore obtains the variation rules of terminal parameters of power devices. For example, the bonding wires on device lifetime have been investigated with simulation and experimental results in [16-18], temperature influence on IGBT failure has been analyzed through simulation and experiments in [19-21], and failure precursor parameter varying rules of IGBTs have been identified through

Fig.1 Current failure research categories

<sup>\*</sup> Corresponding Author, E-mail: xfeyninger@qq.com.

Supported by the key program of National Natural Science Foundation of China under Grant 51490681, National Key Basic Research Program of China (973 Program) under Grant 2015CB251004 and National Natural Science Foundation of China under Grant 51507185.

experiments in [22-24]. The third category includes quantitative analysis and model-based failure prediction, therefore achieving the most accurate allocation and evaluation of device failures and is currently the most popular research field of device failure. For example, mathematical statistics lifetime prediction methods based on Coffin-Manson or Arrhenius model have been published in [25-28], device model-based lifetime prediction method have been published in [29-34], mission profile based model has been investigated in [35-36], and condition monitoring methods based on terminal parameters have also been published in [37-39]. However, model-based evaluation is of course the most difficult of the three categories because it requires the knowledge of not only the device physics, the failure mechanisms, but also the mathematical statistics. Therefore, there are still limited efficient ways to achieve accurate evaluations of device failures, especially when power devices are operating under extreme conditions which have stringent requirements for weight and volume and demand a more critical approach to failure analysis.

The purpose of this paper is to give a general view of current failure analysis of power electronic devices based on the proposed research and to present a design method for power devices under extreme conditions. The rest is organized as follows: Section 2 introduces the proposed failure analysis method, including failure information collection, failure identification and mechanism, and failure evaluation. Several proposed techniques are illustrated in detail as proof of the proposed failure analysis method. Then, section 3 introduces the extreme applications of power electronic devices based on the failure analysis and a design method under extreme conditions is proposed. Finally, section 4 concludes this paper with future research challenges and prospects.

# 2 Failure analysis

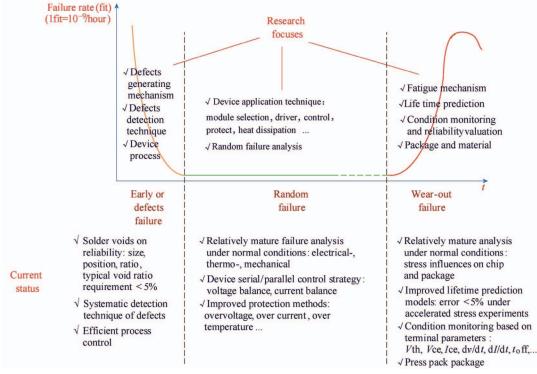

From the perspective of research focus, current device failure analysis can be classified into three groups based on the typical device lifetime tube curve as shown in Fig.2: early failure, random failure and wear-out failure.

Early failure analysis includes device defects generating mechanism, defects detection technique and device process<sup>[16,17,38]</sup>. Current research focuses on the solder voids and process control<sup>[40-42]</sup>.

Random failure analysis mainly includes device random failure mechanism and device reliable application techniques. It is widely investigated by researchers from electrical-, thermo- and mechanical induced aspects<sup>[12-15, 18-20, 43-47]</sup>. In addition, efficient device serial/parallel control strategies and improved protection methods have been published recently<sup>[48-50]</sup>.

Wear-out failure includes device fatigue and aging<sup>[5-11]</sup>. Lifetime prediction <sup>[21, 25-31, 35, 36]</sup> is always a research focus in this group and currently the condition monitoring techniques has become another popular research focus<sup>[22-24, 32-34,37,39]</sup>.

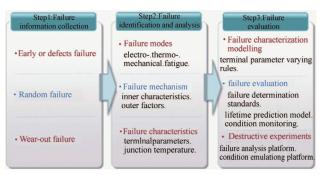

Although much research on device failures has been carried out, failures still occur frequently. One of the most important reasons is lack of effective characterizations of device dynamics and accurate descriptions of device operation under extreme conditions. This has brought out three critical techniques: Failure mechanisms, multi-fields coupling model of devices, and evaluation model of device reliability. Therefore, this paper proposed a systematic failure analysis method of power devices as three steps: failure information collection, failure identification and mechanism, and failure evaluation, as shown in Fig.3.

Fig.2 Current failure analysis and research focuses

Fig.3 The proposed failure analysis procedure

### 2.1 Failure information collection

This is the precondition of the proposed device failure analysis method. It determines which failure mode the failure belongs to. The required information mainly includes the states of physical surfaces of power devices and the operational conditions before the device fails. The former can be achieved by different kinds of testing instruments such as X-ray, SEM, SAM, etc. The latter is difficult because it needs real-time monitoring and recording of the device terminal parameters during operation, especially right when the failure happens.

However, in large-capacity power converters which consist of lots of devices, it may require lots of monitoring resources and thus bring another challenge to the topology design. Therefore, monitoring the most critical devices may be a practical solution.

#### 2.2 Failure identification and mechanism

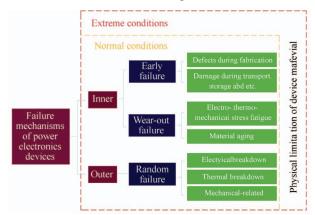

This is the basis of the proposed failure analysis method. It focuses on the failure mechanisms of power

devices. As mentioned previously, failure mechanisms can be classified into two categories: the device inner factors and outer factors as shown in Fig.4. Inner factors are related with the device process and materials. Outer factors are related with the operational conditions. For extreme conditions, physical limitation of device material such as melting point needs to be specifically investigated.

#### 2.2.1 Inner factors

Inner factors of device failures include early and wear-out failures. Defects are mainly caused by the fabrication process and packaging process. Fatigue and aging is mainly caused by device material characterristics under certain stresses. Therefore, they are inherent factors after the device is fabricated.

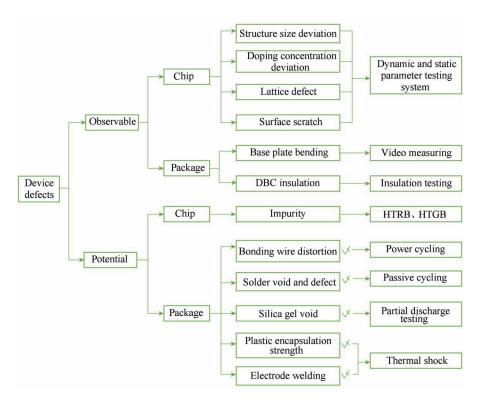

According to current publications about device defects, a systematic defects categorization and detection method is concluded in Fig.5.

Fig.4 Failure mechanisms of power electronic devices

Fig.5 Device defects category and analysis methods

It is classified into observable defects and potential ones which need certain stress conditions to make them occur. In each category, they are divided into chip-related and package-related. Special testing instruments are required to assist the device defects analysis. "V" means the defects need certain stresses to occur.

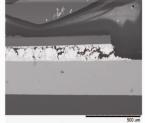

The fatigue and aging mechanisms of power devices can be divided into chip-related and package-related failures according to the failure sources. The former mainly comes from the interface fatigue based on the physical structure of the device and the Si fatigue as shown in Fig.6; the latter mainly comes from the solder fatigue and the bonding wire fatigue as shown in Fig.7.

#### 2.2.2 Outer factors

Outer factors of power device failures need acquisition of both after-failure physical states and pre-failure operation conditions of devices. The root reason for these failures could be electrical-, thermoand mechanical induced ones:

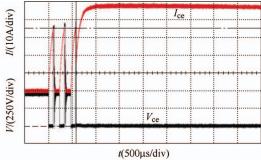

#### 2.2.3 Electrical breakdown

This is mainly caused by the avalanche breakdown either at one high energy avalanche or after accumulated energy during several breakdowns as shown in Fig. 8.

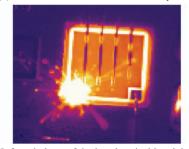

#### 2.2.4 Thermal breakdown

This is mainly caused by large energy by large current, and finally goes to local or partial burnouts as shown in Fig.9.

# 2.2.5 Mechanical-related failure

This is an important factor especially for press pack modules because it induces unequal thermal resistance distribution to the module package, leading to high local temperature and finally causing device burnout if operation current is large. As shown in Fig.10, the surface flatness of a GCT after power cycles with unequal mounting forces may become severe compared

Fig.6 SEM photos of device surface before and after fatigue

Fig. 7 Bonding wire lift-off and solder fracture [17] after fatigue

(a) Avalanche breakdown after three cycles

(b) Infrared photo of device electrical breakdown Fig.8 Device electrical breakdown

Fig.9 Thermal breakdown under high energy

(a) New device surface flatness :  $\Delta h < 15 \mu m$

(b) Used device surface flatness:  $\Delta h > 1 \text{ mm}$

(c) Local burnout under unequal mounting force Fig.10 Failure of a GCT under unequal mounting forces

with the new one, therefore generating unequal thermal resistance and finally leading to device local burnout.

According to the above descriptions, failure mechanism analysis of power electronic devices is therefore a very complicated process requiring consideration of various factors.

#### 2.3 Failure evaluation

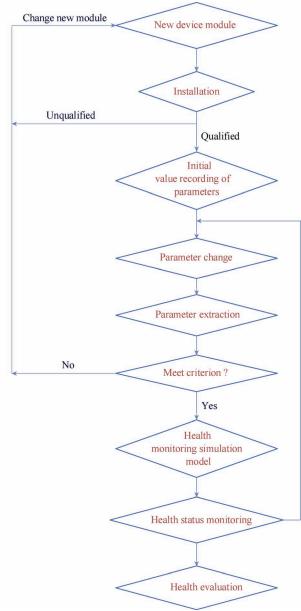

This is the ultimate goal of the proposed failure analysis method. Failure evaluation achieves the quantitative characterization of a failure. It requires the acquisition of both failure mechanisms and device models. Fig.11 shows the proposed method of device health monitoring. The main procedures are to first set the initial states of devices, then monitor the states of devices after some power cycles and finally compare with the failure evaluation model simulation results to see whether the device is still in its healthy status. Therefore, device failure evaluation model is the most critical part in failure evaluation procedure.

Fig.11 The proposed failure evaluation process

Currently, there are two types of failure evaluation models: 1) mathematical statistical model; 2) physics-based model.

#### 2.3.1 Mathematical statistical model

The mathematical statistical model has been studied for a long time such as Coffin Manson model in 1953, LESIT model in 1997, CIPS model in 2008 and etc.

Several improved lifetime prediction models have been published recently. One improved lifetime prediction model is presented with high accuracy as shown in Eq. (1) and Fig.12<sup>[28]</sup>.

$$N_f = A(\Delta T_j)^{\alpha} \left(\frac{273 + T_{j \max}}{T_m}\right)^N \left(\frac{i_{st}}{i}\right)^M \exp\frac{Q}{RT_m}$$

(1)

In addition, other kinds of methods have been published recently based on the new ideas such as neural network based model, weighted network model and etc.

#### 2.3.2 Physics-based failure evaluation model

The physics-based failure evaluation model has been studied recently, for example, the mission profile based model in [35-36]. It shows a new branch of failure evaluation methods and seems more attractive because it is based on the device physics and can characterize a power device more accurately.

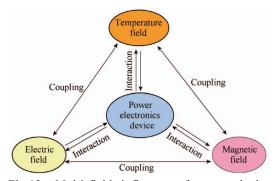

To obtain the physics-based failure evaluation model, the device physics-based models need to be constructed. However, power devices always work under a highly coupled multi-fields condition as shown in Fig.13. A full model including influences of all coupled fields is still too complicated to be effectively constructed until now. Therefore, analysis under separate fields has been carried out by many researchers recently.

Fig.12 Simulation results of the lifetime prediction model

Fig.13 Multi-fields influences of a power device

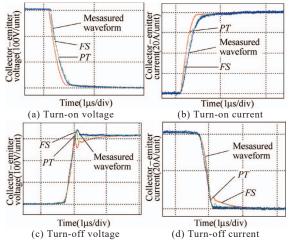

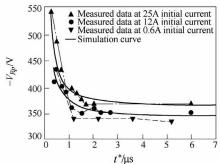

The Trench-FS model is derived as Eq. (2) and shows good consistence with the measurements as shown in Fig.14<sup>[51]</sup>. Correct voltage peak can be simulated with the proposed improved physics model.

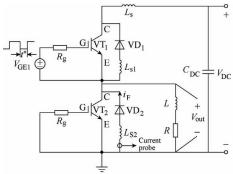

The reverse recovery model of PIN diodes at freewheeling especially at short-time freewheeling is built as Eq.(3), and verified as shown in Fig.15<sup>[52]</sup>. It shows good correlation of voltage peak between simulation and measurements.

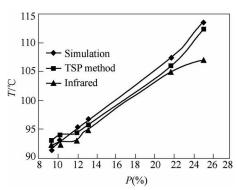

In addition, different thermal models of power devices are proposed by many researchers and show valuable instructions for junction temperature evaluation as mentioned above. An improved thermal model is also shown in [53] with more accurate thermal resistance.

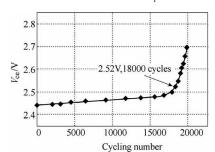

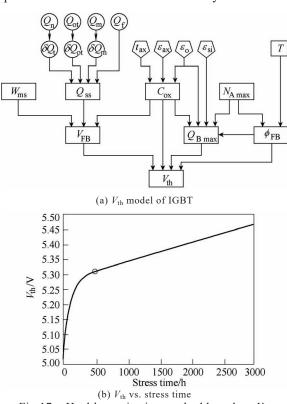

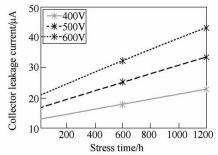

Based on the device physical model and material physics, condition monitoring methods through different parameters can be obtained. For example,  $V_{\rm ce}$  based health monitoring model as shown in Fig.16,  $V_{\rm th}$ -

Fig.14 Comparison of the model simulation with measurements of an FS IGBT module FF200R06KE3 at 300V

(a) Test circuit of PIN diode under short-time freewheeling

(b) Comparison of simulation with measurement Fig.15 Experiment results at different initial off-current of  $VT_1$

Fig. 16  $V_{ce}$  based failure evaluation

$$\frac{dV_{AC}(t)}{dt} = \frac{\left[1 - \frac{1}{1 + b_L} \left(1 + \frac{\tau_{Hb}}{\tau_L}\right) \frac{W_L^2}{W_{\text{eff}}^2}\right] I_T - \frac{1}{\tau_{Ab}} \frac{W_L^2}{W_{\text{eff}}^2} Q_T - I_{\text{mos}} + \frac{C_{\text{GD}}}{C_{\text{GS}} + C_{\text{GD}}} I_{\text{G}}}{C_{\text{GS}} + C_{\text{GD}}} + \frac{C_{\text{GS}}C_{\text{GD}}}{V_{\text{eff}}^2} + \frac{W_L^2}{W_{\text{eff}}^2} \frac{Q_T}{3Q_B} C_{BCJ}} dU_{\text{GS}} + \frac{dQ(t)}{dt} = I_{\text{mos}} + (C_{\text{DSJ}} + C_{\text{GD}}) \frac{dV_{\text{ds}}}{dt} - C_{\text{GD}} \frac{dV_{\text{GS}}}{dt} - \frac{Q_{\text{b}}(t)}{\tau_L} - \frac{Q_{\text{H}}(t)}{\tau_H} - \frac{4Q^2(t)I_{\text{sne}}}{W^2(t)A^2q^2n_i^2} dU_{\text{GS}} + \frac{dI_T(t)}{dt} = \frac{1}{L} \left[V_{\text{bus}} - RI_T(t) - V_{\text{A}}(t)\right]$$

(2)

$$V_{Rp} = -V_{DC} - L_{s2} \left( \frac{1}{\tau_{\rm r}^2} - \frac{1}{\tau_{\rm r}} \right) \left( \left( Q_{\rm T} - \left( Q_0 + I_{\rm F} \left( 1 + \frac{\tau}{t_0} \right) \tau \right) \left( 1 - \exp \left( -\frac{t^*}{\tau^*} \right) \right) \right) \exp \left( -\frac{t_0 + t_1}{\tau} \right) + I_{\rm F} \left( 1 - \exp \left( -\frac{t^*}{\tau^*} \right) \right) \left( \tau - t_1 \right) \frac{\tau}{t_0} \right)$$

$$(3)$$

$$I_{\text{leak}} = \begin{cases} \frac{Aqn_{i}^{2}\sqrt{D_{p}}}{N_{\text{B}}\sqrt{\tau_{p}}} + \frac{Aqn_{i}W}{\tau_{\text{sc}}} + I_{\text{leak}(em)} & V_{\text{g}} \leq V_{\text{FB}} \\ \frac{Aqn_{i}^{2}\sqrt{D_{p}}}{N_{\text{B}}\sqrt{\tau_{p}}} + \frac{Aqn_{i}W}{\tau_{\text{sc}}} + I_{\text{mos}} + \Delta I_{\text{mos}} + I_{\text{leak}(em)} & V_{\text{FB}} < V_{\text{g}} \leq V_{\text{th}} \\ \frac{1}{2\alpha} \frac{z}{l} \frac{\mu_{\text{eff}} C_{\text{ox}}}{1 - \alpha_{\text{pnp}}} (V_{\text{g}} - V_{\text{th}})^{2} & V_{\text{th}} < V_{\text{g}} < V_{\text{GE}} \end{cases}$$

$$(4)$$

based health monitoring model as shown in Fig.17 and leakage current based health monitoring model as shown in Fig.18 can be used to evaluate the device health status through the degradation of device parameters<sup>[54]</sup>.

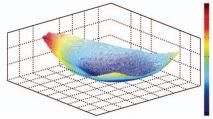

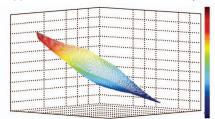

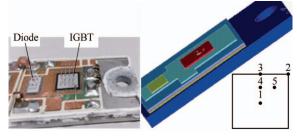

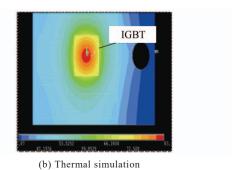

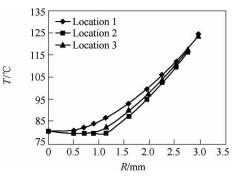

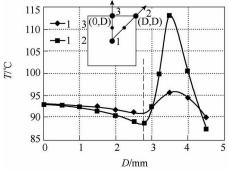

In addition, the influence of solder voids on junction temperature is also modeled from the perspective of void size, position, and ratio, as shown in Fig.19 and Fig.20<sup>[42]</sup>. This is also helpful for condition monitoring of a power device from the aspect of package.

# 3 Power electronic device applications under extreme conditions

#### 3.1 Extreme conditions

As mentioned in the beginning, single devices need to be operated beyond its rated margin to increase the power density under extreme conditions such as high-voltage short-circuit breaker, three deeps and other applications which demand a restraint on instrument weight and volume. This brings more critical requirements to the device reliability. Besides the

Fig.17 Health monitoring method based on  $V_{\rm th}$

Fig.18 IGBT leakage current vs. stress time

(a) Ansys modeling

Fig.19 Ansys modeling of IGBT module

(a) Void size vs. junction temperature

(b) Void location vs. junction temperature

(c) Void ratio vs. junction temperature

Fig.20 Void influences on junction temperature

Fig.21 Proposed design process of devices under extreme conditions

Fig.22 Thermal equilibrium design method under extreme conditions

failure analysis, power devices working under extreme conditions are more condition-related and the safety margin of device operation needs to be considered very accurately.

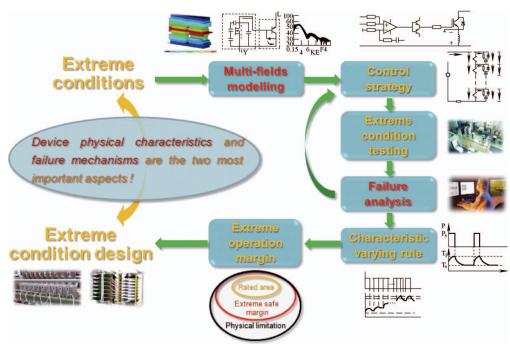

# 3.2 Design method

Power device design under extreme applications could follow the following process as shown in Fig.21. First, multi-fields model of power devices is built. Second, the control strategy needs to be specified especially when there are serial/parallel connections of many devices. Then, testing is carried out and the failure analysis in section 2 is applied to adjust the model and control strategies. After that, the characteristic varying rules of power devices are investigated and the safety margin of devices under extreme conditions is obtained. Therefore, device modeling and failure analysis are the two most important aspects in this process.

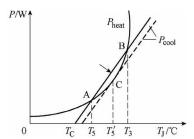

For failure analysis in extreme conditions, thermal equilibrium needs to be considered based on the above failure analysis as shown in Fig.22<sup>[55]</sup>. There exists the heat dissipation (power dissipation) curve and heat generation (power generation) curve of a power device under a certain condition. The relative position of these two curves can then determine the safety margin of the specific condition. If the two curves cross

over, there exists point B which is the safety point margin since the generated power is less than the dissipated power below point B, if they are tangent at C, then C is the critical margin point. In addition, the limitation of device material characteristics such as the melting point should also be considered under extreme conditions.

However, this is not an easy way in practical applications. First, the accurate heat generation curve needs accurate device physics model as mentioned in section 2.3.2; second, the accurate heat dissipation curve requires an accurate model of heat sink; third, the models are multi-fields coupled. Therefore, applications of power electronic devices under extreme conditions are very difficult and complicated.

#### 4 Conclusion

In this paper, a general view of failure mechanism research is introduced first. A proposed failure analysis method of power electronic devices is then provided. It consists of three steps: failure information collection, failure identification and mechanism, and failure evaluation. The first step is the precondition, the second step is the basic and the final step is the most difficult because of the complicated modeling. Failure evaluation is therefore emphasized by describing the physical modeling of power devices in details. Design method of devices under extreme conditions was also proposed based on thermal equilibrium. The analysis shows that the failure of a power device is a complicated process and needs to consider various coupled factors. Finally, the challenges and prospects for failure analysis research of power electronic and their applications under extreme conditions are addressed.

#### 4.1 Challenges

Effective characterization of device dynamics

- under multi-fields.

- Accurate descriptions of device operation under extreme conditions.

#### 4.2 Prospects

- Device dynamics and simulation model of multifields coupling under electrical-magnetic-thermomechanical fields.

- Model-based device failure characterization and reliability evaluation under actions of both power stream and information stream.

- Reliability margin of power electronic devices under extreme conditions.

#### References

- [1] Z. Chen, J. M. Guerrero, and F. Blaabjerg, "A review of the state of the art of power electronics for wind turbines," *IEEE Trans. Power Electron.*, vol. 24, no. 8, pp. 1859-1875, Aug. 2009.

- [2] Y. L. Xiong, X. Cheng, and Z. J. Shen, "Prognostic and warning system for power-electronic modules in electric, hybrid electric, and fuel-cell vehicles," *IEEE Trans. Ind. Electron.*, vol. 55, no. 6, pp. 2268-2276, Jun. 2008.

- [3] H. Wang, M. Liserre, and F. Blaabjerg, "Toward reliable power electronics - challenges, design tools and opportunities," *IEEE Industrial Electronics Magazine*, vol. 7, no. 2, pp. 17-26, Jun. 2013.

- [4] A. D. Touboul, L. Foro, and F. Wrobel, "On the reliability assessment of trench fieldstop IGBT under atmospheric neutron spectrum," *Microelectronics Reliability*, vol. 52, pp. 124-129, 2012.

- [5] M. Ciappa, and P. Malberti, "Plastic-strain of aluminum interconnections during pulsed operation of IGBT multichip modules," *Int. Qual. Reliab. Eng.* 1996, 12, pp. 297-303.

- [6] P. Malberti, M. Ciappa, and R. Cattomio, "A power-cycling induced failure mechanism of IGBT multichip modules," *Int. Symp. Testing Failure Anal.* 1995, 21, pp. 163-168.

- [7] G. Mitic, R. Beinert, P. Klofac, "Reliability of AlN substrates and their solder joints in IGBT power modules," *Microelectron. Reliab.* vol. 39, pp. 1159-1164, 1999.

- [8] M. Bouarroud, Z. Khatir, J. P. Ousten, and S. Lefebvre, "Temperaturelevel effect on solder lifetime during thermal cycling of power modules," *IEEE Trans. Device Mater. Rel.*, vol. 8, no. 3, pp. 471-477, Sep. 2008.

- [9] Z. Khatir, J. P. Ousten, F. Badel, "Degradation behavior of 600V-200A IGBT modules under power cycling and high temperature environment conditions," *Microelectron. Reliab.*, vol. 47, no. 9-11, pp. 1719-1724, 2007.

- [10] B. Czerny, M. Lederer, B. Nagl, "Thermo-mechanical analysis of bonding wires in IGBT modules under operating conditions," *Microelectron. Reliab.* vol. 52, pp. 2353-2357, 2012.

- [11] J. A. Sayago, T. Brückner, and S. Bernet, "How to select the system voltage of MV drives-A comparison of semiconductor expenses," *IEEE Trans. Ind. Electron.*, vol. 55, no. 9, pp. 3381-3390, Sep. 2008.

- [12] L. Takata, "Destruction mechanism of PT and NPT-IGBTs in the short circuit operation--an estimation from the quasistationary simulations," *International symposium on power* semiconductor devices conference, 4-7 June, 2001, pp. 327-330

- [13] M. Trivedi, "Failure mechanisms of IGBTs under short-circuit and clamped inductive switching stress," *IEEE Trans. on Power Electron.* vol. 14, no. 1, pp. 108–116, 1999.

- [14] M. Ishiko, "Investigation of IGBT turn-on failure under high applied voltage operation," *Microelectron. Reliab.* vol.44, no. 9-11, pp. 1431-1436, 2004.

- [15] A. Benmansour, "Failure mechanism of trench IGBT under shortcircuit after turn-off," *Microelectron. Reliab.* vol. 46, no. 9-11, pp. 1778-1783, 2006.

- [16] W. S. Loh, "Wire bond reliability for power electronic modules - effect of bonding temperature, thermal, mechanical and multi-physics simulation experiments," *Microelectronics*

- and Micro-Systems, EuroSime 2007.

- [17] M. Ishiko, "Design concept for wire-bonding reliability improvement by optimizing position in power devices," *Microelectron. J.* vol. 37, pp. 262-268, 2006.

- [18] H. Medjahed, P. Vidal, and B. Nogarede, "Thermo-mechanical stress of bonded wires used in high power modules with alternating and direct current modes," *Microelectron. Reliab*. vol. 52, pp. 1099-1104, 2012.

- [19] A. Benmansour, S. Azzopardi, J. C. Martin, and E. Woirgard, "Trench IGBT failure mechanisms evolution with temperature and gate resistance under various short-circuit conditions," *Microelectron. Reliab.* vol. 47, pp. 1730-1734, 2007.

- [20] M. Ishiko, "Investigation of IGBT turn-on failure under high applied voltage operation," *Microelectron. Reliab.* vol. 44, no. 9-11, pp. 1431-1436, 2004.

- [21] V. Smet, F. Forest, J. Huselstein, "Ageing and failure modes of IGBT modules in high-temperature power cycling," *IEEE Trans. on Ind. Electron.* vol. 58, no. 10, pp. 4931-4941, 2011.

- [22] A. Marco, C. Abraham, T. Didier, "A failure-detection strategy for IGBT based on gate-voltage behavior applied to a motor drive system," *IEEE Trans. on Ind. Electron.* vol. 58, no. 5, pp. 1625-1633, 2011.

- [23] V. Smet, F. Forest, J. Huselstein, "Evaluation of vce monitoring as a real-time method to estimate aging of bond wire-ight modules stressed by power cycling," *IEEE Trans.* on Ind. Electron., vol. 60, no. 7, pp. 2760-2770, Jul. 2013.

- [24] N. Patil, D. Das, and M. Pecht, "A prognostic approach for non-punch through and field stop IGBTs," *Microelectron. Reliab.*, vol. 52, pp. 482-488, Mar. 2012.

- [25] R. Bayerer, T. Licht, T. Herrmann, "Model for power cycling lifetime of IGBT modules-Various factors influencing lifetime," The 5th International Conference on Integrated Power System, 2008, pp. 1-6.

- [26] L. Yang, P. A. Agyakwa, and C. M. Johnson, "Physics-of-failure lifetime prediction models for wire bond interconnects in power electronic modules," *IEEE Trans. Device Mater. Rel.*, vol. 13, no. 1, pp. 9-17, Mar. 2013.

- [27] U. Scheuermann, and R. Schmidt, "A new lifetime model for advanced power modules with sintered chips and optimized Al wire bonds," *Proc. PCIM*, 2013, pp. 810-817.

- [28] B. Liu, D. Liu, Y. Tang, "The investigation on the lifetime prediction model of IGBT module," *Energy Procedia*, 2011 vol. 12, pp. 394-402.

- [29] A. T. Bryant, P. A. Mawby, P. R. Palmer, et al. "Exploration of power device reliability using compact device models and fast electro-thermal simulation," *IEEE Trans. on Ind. Applications*, vol. 44, no. 3, pp. 894-903, 2008.

- [30] A. Testa, S. De Caro, and S. Russo, "A reliability model for power MOSFETs working in avalanche mode based on an experimental temperature distribution analysis," *IEEE Trans. Power Electron.*, vol. 27, no. 6, pp. 3093-3100, Jun. 2012.

- [31] A. Bryant, S. Y. Yang, P. Mawby, et al., "Investigation into IGBT dV/dt during turn-off and its temperature dependence," *IEEE Trans. Power Electron.*, vol. 26, no. 10, pp. 3019-3031, Oct. 2011.

- [32] R. Wu, F. Iannuzzo, H. Wang, and F. Blaabjerg, "Electrothermal modeling of high power IGBT module short circuits with experimental validation," *Proceedings of the 2015 Annual Reliability and Maintainability Symposium (RAMS)*, 2015, pp. 1-7.

- [33] M. Jason, Anderson, and W. C. Robert, "On-line condition monitoring for MOSFET and IGBT switches in digitally controlled drives," *Energy Conversion Congress & Exposition*, pp. 3920-3927, 2011.

- [34] K. B. Pedersen, and K. Pedersen, "Dynamic modeling method of electro-thermo-mechanical degradation in IGBT modules," *IEEE Trans. on Power Electron.*, vol. 31, no. 2, pp. 975-986, Jun. 2016.

- [35] P. Ghimire, K. B. Pedersen, B.Rannestad, "Real mission profile oriented IGBT module wear out test and physics of failure analysis," *IEEE Trans. on Power Electron.*, early access article, 2016.

- [36] K. Ma, M. Liserre, F. Blaabjerg, "Thermal loading and lifetime estimation for power device considering mission profiles in wind power converter," *IEEE Trans. on Power Electron.*, vol. 30, no. 2, pp. 590-602, 2015.

- [37] N. Baker, S. Munk Nielsen, F. Iannuzzo, and M. Liserre, "Online junction temperature measurement using peak gate current," *IEEE Applied Power Electronics Conference and Exposition (APEC)*, March 2015, pp. 1270-1275.

- [38] S. Zhou, L. Zhou, and P. Sun, "Monitoring potential defects in an IGBT module based on dynamic changes of the gate current," *IEEE Trans on Power Electron.*, vol. 28, no. 3, pp. 1479-1487, 2013.

- [39] K. Ma, F. Blaabjerg, and M. Liserre, "Electro-thermal model of power semiconductors dedicated for both case and junction temperature estimation," *Proc. PCIM*, 2013, pp. 1042-1046.

- [40] A. S. Flelschera, L. B. C. Chang, and Johnson, "The effect of die attach voiding on the thermal resistance of chip level packages," *Microelectronics Reliability*, vol. 46, no. 6, pp. 794-804, 2006.

- [41] R. S. Otiabke, R. E. Bhatti, "Thermal effect of die- attach voids location and style on performance of chip level package," 3rd IEEE International Conference on Adaptive Science and Technology (ICAST), 2011, pp. 231-236.

- [42] Y. Xia, Y. Luo, B. Wang, "Effects of voids in solder layer on the temperature distribution," *Marine Electric and Electronic Engineering*, vol. 35, no. 12, pp. 1-5, 2015.

- [43] P. Lefranc, D. Planson, H. Morel, "Analysis of the dynamic avalanche of punch through insulated gate bipolar transistor (PT-IGBT)," Solid-State Electronics, vol. 53, pp. 944-954, 2009.

- [44] I. Masayasu, H. Koji, K. Sachiko, "Investigation of IGBT turn-on failure under high voltage operation," *Microelectronics Reliability*, vol. 44, pp. 1431-1436, 2004.

- [45] J. M. Domeij, J. Lutz, and D. Silber, "On the destruction limit of Si power diodes during reverse recovery with dynamic avalanche," *IEEE Transactions on Electron Devices*, vol. 50, no. 2, pp. 486-493, 2003.

- [46] S. Milady, D. Silber, F. Pfirsch, et al. "Simulation studies and modeling short circuit current oscillations in IGBTs," *Proceeding* of ISPSD, 2009, pp. 37-40.

- [47] S. Hu, Y. Zhu, and Y. Duan, "An impact analysis of gate resistance on static and dynamic dissipation of IGBT modules," *Proceeding of ICECC*, 2011, pp. 715-718.

- modules," *Proceeding of ICECC*, 2011, pp. 715-718.

[48] I. Bararia, J. Barrena, G. Abad, "An experimentally verified active gate control method for the series connection of IGBT/diodes," *IEEE trans. on Power electron.* vol. 27, no. 2, 1025-1038, 2012.

- [49] Z. Wang, X. Shi, L. M. Tolbert, "A di/dt feedback- based active gate driver for smart switching and fast overcurrent protection of IGBT modules," *IEEE Trans. Power Electron.*, vol. 29, no. 7, pp. 3720-3732, Jul. 2014.

- [50] W. S. Im, J. M. Kim, D. C. Lee, and K. B. Lee, "Diagnosis and fault tolerant control of 3-phase AC-DC PWM converter systems," *IEEE Trans. Ind. Appl.*, vol. 49, no. 4, pp. 1539-1547, 2013.

- [51] Y. Tang, B. Wang, M. Chen, "Simulation model and parameter extraction of Field-Stop(FS) IGBT," *Microelectronics Reliability*, vol. 52, no. 12, pp. 2920-2931, 2012.

- [52] Y. Luo, F. Xiao, B. Wang, "A voltage model of PIN diodes at reverse recovery under short-time freewheeling," *IEEE Trans. Power Electron*, early access article, 2016.

- Power Electron., early access article, 2016.

[53] M. Chen, B. Wang, and Y. Tang, "Test of IGBT transient thermal impedance and modeling research on thermal model,"

Advanced Materials Research, vol. 148-149, no. 1, pp. 429-433, 2011.

- [54] B. Liu, "Study on fatigue failure mechanism and health condition monitoring methods for IGBT," Ph.D. dissertation. Dept. Electr. Eng., Naval University of Engineering, China, 2014.

[55] B. Wang, Y. Luo, S. Zhang, et al. "Analysis of Limiting Power Loss and Thermal Failure Mechanism," *Transactions of China Electrotechnical Society*, vol. 31, no. 12, pp. 135-141, 2016.

Yifei Luo received the B.S. and M.S. degrees in electrical engineering from Huazhong University of Science and Technology, Wuhan, China, in 2002 and 2005, respectively, and the Ph.D. degree in electrical engineering from University of New Hampshire, NH, U.S., in 2010. From 2010 to 2011, he was a Senior Engineer in LSI Corporation in U.S. In 2011, he was a Lecturer in Naval

University of Engineering, where he was an Associate Professor in 2014. His research interests include power semiconductor device modelling, power electronic device reliability and power converter reliability.

Fei Xiao received the B.S. and M.S degrees in electrical engineering from Naval University of Engineering, Wuhan, China, in 1999 and 2001, respectively. From 2004 to 2012, he worked toward the Ph.D. degree in electrical engineering in Zhejiang University. In 2003, he was a Lecturer in Naval University of Engineering, where he was an Associate Professor in 2009 and a Full Professor in 2012.

He is currently the committee member of Department of Energy and Transportation in China Ministry of Science and Technology. His research interests include renewable energy generation, modeling and control of power electronic system, and high-voltage large-power electronic equipment.

Bo Wang received the B.S. and M.S. degrees in electrical engineering from Air Force Radar Academy, Wuhan, China, in 2002 and 2008, respectively, and the Ph.D. degree from Naval University of Engineering, Wuhan, China, in 2012. In 2012, he was a Lecturer in Naval University of Engineering. His research interests include power semiconductor device modelling and power electronic device reliability.

Binli Liu received the B.S. and M.S. degrees in electrical engineering from Naval Submarine Academy, Qingdao, China, in 2008 and 2010, respectively, and the Ph.D. degree from Naval University of Engineering, Wuhan, China, in 2014. In 2015, he was a Lecturer in Naval University of Engineering. His research interests include power semiconductor device modeling and power electronic device reliability.