# Investigating Surface Loss Effects in Superconducting Transmon Qubits

Jay M. Gambetta, *Member, IEEE*, Conal E. Murray, Y.-K.-K. Fung, Douglas T. McClure, Oliver Dial, *Member, IEEE*, William Shanks, Jeffrey W. Sleight, *Senior Member, IEEE*, and Matthias Steffen, *Senior Member, IEEE*

Abstract—Superconducting qubits are sensitive to a variety of loss mechanisms including dielectric loss from interfaces. By changing the physical footprint of the qubit, it is possible to modulate sensitivity to surface loss. Here, we show a systematic study of planar superconducting transmons of differing physical footprints to optimize the qubit design for maximum coherence. We find that qubits with small footprints are limited by surface loss and that qubits with large footprints are limited by other loss mechanisms, which are currently not understood.

Index Terms—Dielectric loss, quantum noise, superconducting qubits.

### I. INTRODUCTION

MPROVING coherence times (or quality factors) of superconducting qubits is necessary in order to implement meaningful tests of quantum information processing in such systems. It has been known for many years that dielectric loss can play a potentially limiting role for qubit coherence [1]. While other loss mechanisms such as quasi-particle loss [2], [3], limitations due to infrared (IR) radiation [4], [5], losses related to the qubit readout [6], or electromagnetic radiation [7] can play dominant roles, a picture has been emerging recently that dielectric loss at surfaces also plays a key role [8]–[11]. In particular, it has been observed that quality factors tend to increase when the physical footprint of the devices increases for resonators [9], [10], two-dimensional (2-D) transmon qubits [12], and 3-D qubits [13], [14]. This points to surface loss as a detractor of qubit coherence, suggesting that qubits can be optimized for coherence by increasing the physical footprint. However, simply continuing to increase physical size is not a guarantee for further improvements in coherence times as other loss mechanisms can become dominant. It is therefore important to design qubits that are sensitive to specific loss mechanisms and perform a systematic study to optimize qubit coherence times.

Inspired by similar work for 3-D qubits [14], we here implement a study for the 2-D transmon qubits [15] fabricated

Manuscript received May 27, 2016; revised August 11, 2016; accepted September 5, 2016. Date of publication November 16, 2016; date of current version January 5, 2017. The paper was recommended by Associate Editor O. Mukhanov.

The authors are with the International Business Machines, IBM TJ Watson Research Center, Yorktown Heights, NY 10598 USA (e-mail: jay.gambetta@us.ibm.com; conal@us.ibm.com; yfung@us.ibm.com; dtm-cclur@us.ibm.com; odial@us.ibm.com; willshanks@us.ibm.com; sleight@us.ibm.com; msteffe@us.ibm.com).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TASC.2016.2629670

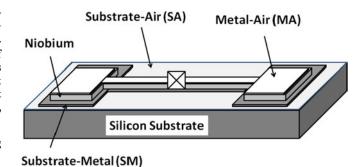

Fig. 1. Schematic of a superconducting qubit fabricated on top of a silicon substrate. Surface loss can arise due to the contributions from the SA interface, the SM interface, and the MA interface.

on high-resistivity silicon. Anticipating energy dissipation from surface loss, we tested several styles of transmon qubits. From these studies, we find that the qubits with physically small shunting capacitors (i.e., a small physical footprint) show a characteristic  $T_1$  decay that is likely limited by losses associated with one or more surfaces (see Fig. 1) though the present data are not sufficient to pinpoint which surface dominates. Meanwhile qubits with physically large footprints show a characteristic  $T_1$  that appears to be limited by contributions of currently unknown origin and saturates near  $T_1 \sim 50~\mu \rm s$ , corresponding to a quality factor  $Q = T_1 2\pi f \sim 1.5~\rm M$ , where  $f \sim 4$ –5 GHz is the qubit frequency.

All presented  $T_1$  times are typically averaged over several hours and in most cases fluctuations on the order of  $\pm 20\%$  have been observed, although fluctuations by as much as a factor of  $2\text{--}4\times$  have been noticed in some of the rare cases. We believe these are real  $T_1$  fluctuations because the uncertainty from each fit is typically less than the measured  $T_1$  variations with time. Since  $T_1$  itself appears to be fluctuating, the values that are shown should be interpreted with a sizable error bar. We believe that in the long term it is useful to introduce metrics to quantify these fluctuations so that experiments or improvements can be more readily compared. Despite these fluctuations, meaningful information can be extracted from our experiments described below.

## II. DESIGN AND SIMULATION

A systematic study of coherence times as a function of qubit geometry has been done for the 3-D transmon qubits on sapphire [14], and we adopt similar strategies here. The experimental goal

1051-8223 © 2016 IEEE. Translations and content mining are permitted for academic research only. Personal use is also permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

TABLE I

SUMMARY OF SIMULATED SURFACE PARTICIPATION TO QUBIT LOSS FOR THE

FIVE DIFFERENT QUBIT DESIGNS WITH A SUBSTRATE TRENCH

DEPTH OF 50 NM

|    | MOD A                | MOD B              | MOD C              | MOD D              | MOD E                |

|----|----------------------|--------------------|--------------------|--------------------|----------------------|

| SM | $3.68 \times 10^{6}$ | $1.10 \times 10^6$ | $3.46 \times 10^5$ | $2.15 \times 10^5$ | $1.20 \times 10^{5}$ |

| SA | $1.24 \times 10^{6}$ | $3.32 \times 10^5$ | $9.10 \times 10^4$ | $5.04 \times 10^4$ | $2.38 \times 10^{4}$ |

| MA | $7.20 \times 10^{4}$ | $1.62 \times 10^4$ | $3.80 \times 10^3$ | $1.80 \times 10^3$ | $6.0 \times 10^{2}$  |

Of particular interest is the significant change in SA participation between MOD A and B. It is also interesting to note that the MA participation is simulated to be very small.

is to design, fabricate, and test transmon qubits with identical anharmonicities of approximately  $E_c \sim 350$  MHz but substantially different physical sizes for the shunting capacitor to test how  $T_1$  times vary and compare the results to theory.

A total of five qubit styles were designed and simulated using Ansys HFSS and Q3D software, and shown in Figs. 4-8. We refer to these different designs as MOD A through MOD E. Participation factors were determined by calculating the corresponding energy based on the electric fields present at particular surfaces and interfaces within the build. Hypothetical layers possessing a dielectric constant of  $\epsilon_r = 5$  [14] were placed between the substrate and overlying metallization (SM), which includes the capacitors, groundplane, and adjacent readout resonator, the top surface of the substrate exposed to air (SA), and the metallization surfaces exposed to air (MA). Continuous layers of uniform thickness were assumed, but because the thickness of these layers was not known a priori, the units of the calculated surface participation factors in Table I are m<sup>-1</sup>. For a given layer, multiplying the participation factor by the thickness and  $tan(\delta)$  gives the reciprocal of the qubit quality factor Q assuming no other sources of loss.

Because the thicknesses of these contamination layers are presumed to be much thinner (<10 nm) than the dimensions of the constitutive elements of the qubit metallization, the constraints on the domain discretization necessary to produce a credible numerical solution made conventional simulation impractical. Instead we adopted a strategy of calculating the effective electric field strength at a specific interface by first assuming no contamination layer and extrapolating the solution to a different dielectric constant than those on either side of the original interface [14]. The effective fields were calculated by matching the appropriate components of the electric fields as prescribed by the boundary conditions between two dielectric layers

$$\vec{E}_{||}^{(1)} = \vec{E}_{||}^{(2)}$$

(1)

$$\epsilon_1 \vec{E}_{\perp}^{(1)} = \epsilon_2 \vec{E}_{\perp}^{(2)} \tag{2}$$

where  $\vec{E}_{||} = -(\vec{E} \times \vec{n}) \times \vec{n}$  is the component of the field parallel to the interface,  $\vec{E}_{\perp} = \vec{n}(\vec{E} \cdot \vec{n})$  is that normal to the interface, superscript 1 refers to the hypothetical contamination layer, and 2 the actual dielectric material present in the simulation (e.g., silicon for the substrate surfaces or vacuum for the free surfaces). Combining (1) and (2), we arrive at the effective electric

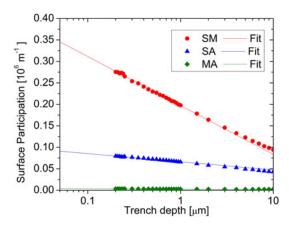

Fig. 2. Calculated surface participation factors for the SM, SA, and MA interfaces as a function of qubit pocket trench depth for the MOD C qubit design. The participation factors obey a logarithmic dependence for small trench depths (< 1  $\mu$ m), which is predicted by the  $r^{-\frac{1}{2}}$  electric field dependence near the metallization edges. Below trench depths of 300 nm, surface participation factors were extrapolated using the logarithmic fits (solid lines) due to the simulation convergence issues arising from the singular behavior of the electric fields.

field in the contamination layer with dielectric constant  $\epsilon_1$

$$\vec{E}^{(1)} = \frac{\epsilon_2}{\epsilon_1} \vec{n} (\vec{E}^{(2)} \cdot \vec{n}) - (\vec{E}^{(2)} \times \vec{n}) \times \vec{n}. \tag{3}$$

Calculations of the surface participation factors  $p_i/t_i$  were then conducted by assuming a uniform electric field strength throughout the layer thickness  $t_i$  and integrating over the corresponding surface S

$$\frac{p_i}{t_i} \approx \frac{\int_S \vec{E}^{(1)} \cdot \epsilon_1 \vec{E}^{*(1)} dS}{U_{\text{tot}}} \tag{4}$$

where  $\vec{E}^*$  is the conjugate of  $\vec{E}$  and  $U_{\rm tot}$  is the total energy of the system.

Additional complications are that the electric field diverges near corners, and that the etching procedures used in the fabrication of the 2-D transmon qubits result in some degree of recess of the substrate surface in the qubit pocket. It is thus important to incorporate the effects of trenching in the surface participation calculations. HFSS models were generated that included both 200-nm-thick niobium (Nb) metallization and a variation in the pocket trench depth. Identical qubit junctions, treated as lumped elements, were used for all of the MOD's under investigation. Because the singular nature of the electric fields near the edges of the Nb metallization can lead to convergence issues in the simulations of trench depths less than  $\sim$ 200–300 nm, we restricted the modeling to trenches greater than this thickness and extrapolated participation factors of the various interfaces according to a logarithmic fit with respect to the trench depth. Because the electric field strength obeys a  $r^{-\frac{1}{2}}$  dependence for a thin metallic sheet [16], where r is the distance from the sheet edge, the integrand in (4) should scale as  $r^{-1}$  for small r and a corresponding log(r) scaling of the surface participation. Although simulations based on the finite element method may be susceptible to errors due to the presence of these singularities, the logarithmic dependence in surface participation observed in Fig. 2 suggests that their contributions to the electric field energy are being sufficiently captured. Table I contains the extrapolated participation factors to a trench depth of 50 nm for all of the designs, demonstrating that the substrate—metal (SM) interface participation varies by a factor of  $30\times$  over the different designs, the substrate—air (SA) interface participation varies about a factor of  $50\times$ , and while the metal—air (MA) interface participation varies over two orders of magnitude, its participation is substantially less than that of the SM and SA interfaces and is likely not contributing to the loss.

Substrate participation was simulated using HFSS in a similar manner as that used for the surface participation factors. The substrate participation asymptotes to a constant value in the limit that the trench depth approaches zero. In this limit, in which the magnitude of the electric fields present in the dielectric substrate and in vacuum ( $\epsilon_r=1$ ) are equal, the substrate participation approaches  $\frac{\epsilon_{\rm sub}}{\epsilon_{\rm sub}+1}=0.92$  for all of the MOD's. Here and in all simulations, we have assumed the dielectric constant of the substrate as  $\epsilon_{\rm sub}=11.45$ .

Chip sizes were  $4 \times 7$  and  $4 \times 8$  mm<sup>2</sup>, small enough that the fundamental chip mode was located above 10 GHz. Each chip consists of a single 50  $\Omega$  feedline, out of which four  $\lambda/2$  coplanar waveguide (CPW) resonators (also 50  $\Omega$ ) are each terminated by a transmon qubit of identical design. The resonator frequencies are staggered at 6.75, 7.0, 7.25, 7.5 GHz with a coupling quality factor of 10 000-40 000. Given qubit-resonator coupling strengths in the range of  $g = 10-50 \,\mathrm{MHz}$ , we calculate the Purcell loss [17] to be negligible in all our experiments with qubit frequencies targeted in the f = 4-5 GHz range. The qubit chip is back mounted to a printed circuit (PC) board and placed in a light tight enclosure to minimize the exposure to IR radiation [4], [5]. Most  $T_1$  measurements were done using the high-power readout [6]. To ensure no residual effects from the readout are present [3], we varied the repetition time or employed standard low-power quantum non-demolition (QND) measurements for many samples (but not all) and observed no noticeable differences. The input attenuation and filtering to the sample varied slightly between experiments to test thermal dephasing [18], but these variations were found to have little impact, if any, on  $T_1$  times. However, because  $T_2$  times are typically near  $T_1$ , there is still room for improvement for future experiments. The output lines included PAMTECH 3-12 GHz isolators (model CWJ0312KI) and a 4K HEMT amplifier by CalTech.

#### III. FABRICATION, TESTING, AND RESULTS

The qubits were fabricated on high-resistivity ( $\rho \sim 1~k\Omega {\rm cm}$ ) silicon, which received a hydrogen fluoride (HF) clean just prior to the metallization. Approximately 200 nm of Nb was physical vapor deposited at a rate of 1.7 nm/s. The junctions were fabricated using a cold develop and acetone lift off at room temperature. Each wafer received a Huang clean (also known as an radio corporation of america (RCA) clean [19]) to remove organic and inorganic contaminants from the wafer surface. Within 30 min prior to the 200-nm Nb deposition, each wafer received a 2 min 100:1 HF clean to remove the surface SiOx. After the HF treatment, each wafer received a 5 min water rinse. After the water rinse and dry, a thin SiOx layer remained

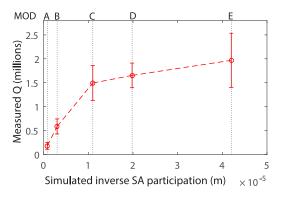

Fig. 3. Qubit quality factor as a function of the inverse SA surface participation. Markers indicate the average, and error bars indicate  $\pm$  the standard deviation divided by the square root of the number of measured qubits. The data indicate that low MOD qubits are consistent with surface loss due to linear scaling with the simulation. Coherence of high-MOD qubits appears to be much less sensitive to surface loss, seemingly limited by another loss mechanism.

on the surface. Next, a chlorine-based reactive ion etch (RIE) etch was performed, which slightly overetches the silicon, etching approximately 50–100 nm into the silicon. The aluminum–aluminum oxide–aluminum Josephson junction was fabricated using a Dolan bridge [20] employing polymethyl methacrylate / methyl methacrylate (PMMA/MMA) processing steps. The aluminum makes contact to the Nb after applying a gentle low-power ion mill clean prior to the aluminum deposition. We have tested additional qubits (data not shown) with slight modifications to the precleans prior to the Nb deposition, but found no deviations from the data reported here, and similarly a junction liftoff in microposit remover 1165 at 80 °C was also found not to affect coherence times.

The measured  $T_1$  times are translated into quality factors in order to remove effects from frequency variations of the qubits; within the range of qubit frequencies measured, no frequency dependence of the quality factor was found. The results are summarized in Fig. 3, where the measured quality factors are plotted against the inverse of simulated SA surface loss participation values. If coherence times were limited by SA loss, we would expect Q to linearly scale with the inverse of the participation values. Each data point represents the mean quality factor of eight qubits, and the error bar is the standard deviation divided by the square root of the number of measured qubits. Each  $T_1$  is obtained by averaging typically on the order of a few hours to account for known fluctuations. We observe a dramatic improvement in Q between MOD A and MOD B qubits, consistent with predictions based on the surface loss. When plotted against SM or MA inverse surface participation values (not shown), the results look very similar, which leads us to the conclusion that at present, the data are not sufficient to ascertain which of the interfaces dominates. High-MOD qubits appear to saturate near  $Q \sim 1.5$ –2 M indicating a loss contribution of unknown origin, which could potentially include substrate loss, loss due to quasiparticles [3], residual coupling to resistive metallic components housing the qubits, or other mechanisms. Nonetheless, it is possible to place an upper bound on the bulk loss of the silicon

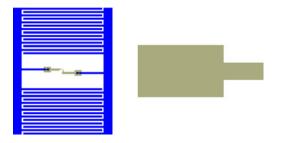

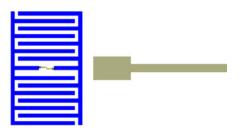

Fig. 4. Schematic of the MOD A design featuring an interdigitated capacitor with a finger linewidth and finger-to-finger spacing of 1  $\mu$ m. The rectangle to the right is the coupling capacitor to the CPW readout resonator of sufficient size such that g=8 MHz.

Fig. 5. Schematic of the MOD B design featuring an interdigitated capacitor with a finger linewidth and finger-to-finger spacing of 5  $\mu$ m. The rectangle to the right is the coupling capacitor to the CPW readout resonator of sufficient size such that g=20 MHz.

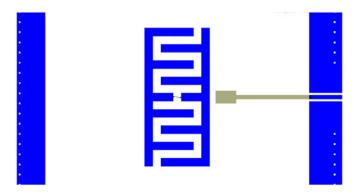

Fig. 6. Schematic of the MOD C design featuring an interdigitated capacitor with a finger linewidth and finger-to-finger spacing of 20  $\mu$ m. The rectangle to the right is the coupling capacitor to the CPW readout resonator of sufficient size such that g=45 MHz.

of  $\tan(\delta) \sim 5 \times 10^{-7}$ , though we believe the actual number is likely less.

# IV. PICTURES OF THE QUBIT DESIGNS

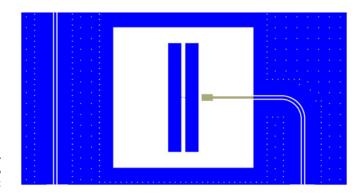

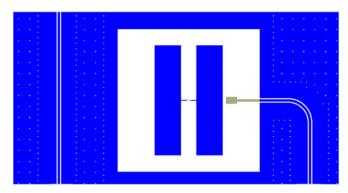

Figs. 4–8 depict each of the five MOD designs in detail. Note that all qubits are placed inside a grounding box of dimension  $650 \times 650 \ \mu \text{m}^2$ . This box is only fully visible for MODs D and E. MODs A and B were also tested with a larger coupling capacitor to increase the signal-to-noise ratio. The data indicate no appreciable effect on  $T_1$ , which is not surprising given that the calculated Purcell limit is much larger than the observed coherence times.

Fig. 7. Schematic of the MOD D design featuring two capacitor pads of dimension  $500 \times 60~\mu\text{m}^2$  separated by  $20~\mu\text{m}$ . The rectangle to the right is the coupling capacitor to the CPW readout resonator of sufficient size such that g=52~MHz.

Fig. 8. Schematic of the MOD E design featuring two capacitor pads of dimension  $500 \times 120~\mu\text{m}^2$  separated by 70  $\mu\text{m}$ . The rectangle to the right is the coupling capacitor to the CPW readout resonator of sufficient size such that q=53~MHz.

## V. CONCLUSION

In conclusion, we present a systematic study of quality factors in qubits with widely varying degrees of surface participation. Results indicate that depending on the design, qubits can be either limited by surface loss (low-MOD qubits) or an additional loss mechanism (high-MOD qubits) that is currently not well understood. The experimental results are not sufficient for us to make any claims on which surface dominates surface loss. We believe the methods applied here should allow for optimal design of qubits for long coherence to enable relevant multiqubit implementations. The results also motivate the development of cleaning methods to potentially enable smaller footprint qubits with good coherence in the future, as well as the development of additional strategies to understand new loss mechanisms for high-MOD qubits.

#### ACKNOWLEDGMENT

The authors would like to thank the useful discussions and contributions from M. B. Rothwell, G. Keefe, and C. Cabral.

## REFERENCES

[1] J. M. Martinis *et al.*, "Decoherence in Josephson qubits from dielectric loss," *Phys. Rev. Lett.*, vol. 95, no. 21, Nov. 2005, Art. no. 210503.

- [2] L. Sun et al., "Measurements of quasiparticle tunneling dynamics in a band-gap-engineered transmon qubit," Phys. Rev. Lett., vol. 108, 2012, Art. no. 230509.

- [3] C. Wang et al., "Measurement and control of quasiparticle dynamics in a superconducting qubit," *Nature Commun.*, vol. 5, 2014, Art. no. 5836.

- [4] R. Barends et al., "Minimizing quasiparticle generation from stray infrared light in superconducting quantum circuits," Appl. Phys. Lett., vol. 99, 2011, Art. no. 113507.

- [5] A. D. Corcoles et al., "Protecting superconducting qubits from radiation," Appl. Phys. Lett., vol. 99, 2011, Art. no. 181906.

- [6] M. D. Reed et al., "High fidelity readout in circuit quantum electrodynamics using the Jaynes-Cummings nonlinearity," Phys. Rev. Lett., vol. 105, 2010, Art. no. 173601.

- [7] M. Sandberg, M. R. Vissers, T. A. Ohki, J. Gao, J. Aumentado, M. Weides, and D. P. Pappas, "Radiation-suppressed superconducting quantum bit in a planar geometry," *Appl. Phys. Lett.*, vol. 102, 2013, Art. no. 072601.

- [8] J. Wenner et al., "Surface loss simulations of superconducting coplanar waveguide resonators," Appl. Phys. Lett., vol. 99, 2011, Art. no. 113513.

- [9] K. Geerlings, S. Shankar, E. Edwards, L. Frunzio, R. Schoelkopf, and M. H. Devoret, "Improving the quality factor of microwave compact resonators by optimizing their geometrical parameters," *Appl. Phys. Lett.*, vol. 100, 2012, Art. no. 192601.

- [10] A. Megrant et al., "Planar superconducting resonators with internal quality factors above one million," Appl. Phys. Lett., vol. 100, 2012, Art. no. 113510.

- [11] C. M. Quintana et al., "Characterization and reduction of microfabricationinduced decoherence in superconducting quantum circuits," Appl. Phys. Lett., vol. 105, 2014, Art. no. 062601.

- [12] R. Barends et al., "Coherent Josephson qubit suitable for scalable quantum integrated circuits," Phys. Rev. Lett., vol. 111, 2013, Art. no. 080502.

- [13] C. Wang et al., "Surface participation and dielectric loss in superconducting qubits," Appl. Phys. Lett., vol. 107, 2015, Art. no. 162601.

- [14] O. Dial et al., "Bulk and surface loss in superconducting transmon qubits," Superconductor Sci. Technol., vol. 29, no. 4, 2016, Art. no. 044001.

- [15] J. Koch et al., "Charge-insensitive qubit design derived from the cooper pair box," Phys. Rev. A, vol. 76, no. 4, Oct. 2007, Art. no. 042319.

- [16] J. Jackson, Classical Electrodynamics, 2nd ed. Hoboken, NJ, USA: Wiley, pp. 77–78, 1975.

- [17] A. Houck et al., "Controlling the spontaneous emission of a superconducting transmon qubit," Phys. Rev. Lett., vol. 101, 2008, Art. pp. 080502

- [18] C. Rigetti et al., "Superconducting qubit in a waveguide cavity with a coherence time approaching 0.1 ms," Phys. Rev. B, vol. 86, 2012, Art. no. 100506

- [19] W. Kern, "The evolution of silicon wafer cleaning technology," J. Electrochem. Soc., vol. 137, no. 6, pp. 1887–1892, 1990.

- [20] G. J. Dolan, "Offset masks for lift-off processing," Appl. Phys. Lett., vol. 31, pp. 337–339, 1977.

**Jay M. Gambetta** (M'13) received the Doctorate degree (First Class Hons.) in physics from Griffith University, Logan, QLD, Australia, in 2004.

He is currently the Manager of the Theory of Quantum Computing and Information Group, IBM, Yorktown Heights, NY, USA. He joined IBM in 2011 to work on quantum information science. Prior to IBM, he held positions in the Institute for Quantum Computing in Canada (2007–2011) and in Yale University (2004–2007). He has authored or coauthored more than 80 peer-review articles in the field of quantum computing.

Dr. Gambetta was named a Fellow of the American Physical Society in 2014.

Conal E. Murray received the Sc.B. degree in mechanical engineering from Harvard University, Cambridge, MA, USA, in 1992, the M.S. degree in mechanical engineering from Boston University, Boston, MA, USA, in 1994, and the Ph.D. degree in materials science and engineering from Northwestern University, Evanston, IL, USA, in 2000.

Since 2000, he has been a Research Staff Member in the IBM T.J. Watson Research Center, Yorktown Heights, NY, USA. He has authored or coauthored more than 100 publications, 3 book chapters, and holds more than 60 patents. His research interests include modeling of quantum computing structures, soft error rate in CMOS devices, and the micromechanics of semiconductor features.

Y.-K.-K. Fung received the B.S. and M.S. degrees both in electrical engineering from Northwestern University, Evanston, IL, USA in 2005, and Columbia University, New York, NY, USA, in 2007 respectively.

He started as a Contractor in IBM's Quantum Computing Group after graduation and later officially joined the team in Yorktown Heights, where he continues to provide support in measurements, layouts, wirebonding, and design.

**Douglas T. McClure** received the A.B. degree in physics and the Ph.D. degree in physics from Harvard University, Cambridge, MA, USA, in 2006 and 2012, respectively. His graduate studies focused on semiconductor-based systems with potential applications to topological quantum computing.

He joined the Quantum Computing Group at IBM Research, Yorktown Heights, NY, USA, as a Postdoctoral Researcher in 2012 and became a Research Staff Member in 2013. His research interests include experimental studies of coherence and readout in superconducting transmon qubits.

Oliver Dial (M'16) received the B.S. degree in physics from the California Institute of Technology, Pasadena, CA, USA, in 1999 and the Ph.D. degree in physics from the Massachusetts Institute of Technology, Cambridge, MA, USA, in 2007. His graduate studies focused on tunneling spectroscopy and the quantum Hall effect. He then moved to Harvard in 2010 where he studied semiconductor quantum dot qubits and their application to quantum computing.

In 2012, he joined IBM Research, Yorktown Heights, NY, USA. His research interests include experimental studies of coherence and quantum control in superconducting transmon qubits.

William Shanks received the B.A. degree in physics and mathematics from Harvard University, Cambridge, MA, USA, in 2005, and the Ph.D. degree in physics from Yale University, New Haven, CT, USA, in 2011.

From 2011 to 2013, he was a Postdoctoral Researcher in the Department of Electrical Engineering, Princeton University, Princeton, NJ, USA, where he studied quantum computing and simulation with superconducting circuits. In 2013, he became a Research Staff Member in the Quantum Computing Group, IBM Research, Yorktown Heights, NY, USA.

**Jeffrey W. Sleight** (SM'01) received the B.A. degree in physics from Vassar College, Poughkeepsie, NY, USA, in 1988. He received a Fulbright scholarship in 1989 to study at the University of Helsinki's X-Ray Laboratory, Helsinki, Finland. He received the Ph.D. degree in applied physics from Yale University, New Haven, CT, USA, in 1995. His Ph.D. thesis dealt with the physics and fabrication of sub-micron semiconductor structures that exhibit quantum size and charging effects.

In 1995, he joined the Device and Interconnect Physics Group, Digital Semiconductor, Hudson, MA, USA, where he worked primarily in the area of silicon on insulator (SOI) device development and modeling. In 1998, he joined IBM, Yorktown Heights, NY, USA, where he has worked in both semiconductor development and research across many areas, ranging from advanced SOI FET scaling, circuit and technology interactions, highly scaled SRAM, and gate all around silicon nanowire FETs. He has authored and coauthored more than 90 papers in the areas of semiconductor device physics, fabrication, and modeling and holds more than 100 U.S. patents.

**Matthias Steffen** (SM'15) received the B.S. degree in physics from Emory University, Atlanta, GA, USA in 1998, and the M.S. and Ph.D. degrees in electrical engineering from Stanford University, Stanford, CA, USA in 2003. His Ph.D. thesis focused on testing small prototype quantum computers using nuclear spins in liquid solution.

He has worked in the field of quantum computing since 1998 and focused on a variety of approaches toward building a quantum computer. His postdoctoral work and work at IBM focused on advancing superconducting quantum bits. He has had several jobs roles within the Quantum Computing Group, IBM T. J. Watson Research Center, Yorktown Heights, NY, USA, where he is currently a Distinguished Research Staff Member. He has authored or coauthored more than 40 peer-review articles in the field of quantum computing.