# A 3–10 GHz IR-UWB CMOS Pulse Generator With 6 mW Peak Power Dissipation Using A Slow-Charge Fast-Discharge Technique

Ming Shen, Member, IEEE, Ying-Zheng Yin, Hao Jiang, Tong Tian, and Jan H. Mikkelsen, Member, IEEE

Abstract—This letter proposes a UWB pulse generator topology featuring low peak power dissipation for applications with stringent instantaneous power requirements. This is accomplished by employing a new slow-charge fast-discharge approach to extend the time duration of the generator's peak current so that the peak value of the current is significantly reduced, while maintaining the waveform of the generated UWB pulse signal. A prototype pulse generator has been implemented using the UMC 0.18  $\mu m$  CMOS process for validation. The pulse generator offers a 3–10 GHz bandwidth, a maximum pulse repetitive rate of 1 Gpps, a minimum peak power consumption of 6 mW, and a low energy consumption of 5 pJ/pulse. The fabricated pulse generator measures 0.16 mm².

Index Terms—Charge, discharge, IR-UWB, peak power dissipation, pulse generator.

### I. INTRODUCTION

MPULSE radio ultra wideband (IR-UWB) has been considered a promising technology for short range applications with stringent power consumption requirements, such as battery-less wireless sensor networks (WSN) based on energy harvesting [1], [2]. In an IR-UWB system the pulse generator is the key component in generating short pulses for low duty cycle operation and low power consumption. Thus it has attracted considerable research attention in recent years [3]–[7]. According to FCC's regulation, a UWB signal should have a minimum bandwidth of 500 MHz or a minimum fractional bandwidth of 20% [8]. Therefore the time duration of a UWB pulse signal is usually at the order of 1–2 ns or less. Existing UWB pulse generators based on CMOS circuits can easily achieve pulse widths of a few hundreds ps due to the fast switching capability of CMOS transistors [3]-[7]. However, CMOS circuits mainly dissipate power during switching. This results in a high peak power dissipation typically at the order of tens of mW or higher (90 mW in [4]). For devices powered by energy harvesters, which usually only can provide an output power at the order of a few mW or less [2], the peak power dissipation in existing designs

Manuscript received January 27, 2014; revised April 17, 2014; accepted June 12, 2014. Date of publication July 09, 2014; date of current version September 01, 2014. This work was supported by the Danish Research Council for Technology and Production Sciences (FTP).

M. Shen and J. H. Mikkelsen are with the Department of Electronic Systems, Aalborg University, Aalborg 9220, Denmark (e-mail: mish@es.aau.dk).

Y.-Z. Yin is with Xidian University, Shaanxi, China.

H. Jiang is with San Francisco State University, San Francisco, CA 94132 USA.

T. Tian is with the Shanghai Institute of Microsystem and Information Technology, Shanghai 200050, China.

Digital Object Identifier 10.1109/LMWC.2014.2332057

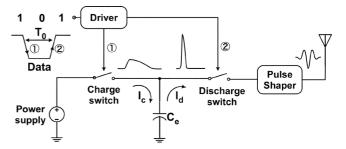

Fig. 1. The proposed IR-UWB pulse generator topology.

is too high. As a consequence, high performance power management circuits, big energy storage capacitors and long energy storage time are required (250  $\mu \rm F$  and charging time of 13 s in [1]), which lead to high cost and low feasibility. To enable low cost implementation of battery-less WSN nodes based on energy harvesting, UWB pulse generators with not only low average power consumption but also low peak power consumption are highly desired. This letter proposes a circuit topology for the implementation of UWB pulse generators aiming at both low instantaneous power dissipation and low energy consumption per pulse. A slow-charge fast-discharge approach is used to reduce the peak of the power supply current, while the energy consumption per pulse is minimized as well.

# II. THE PROPOSED UWB PULSE GENERATOR

The proposed IR-UWB pulse generator topology is shown in Fig. 1. It consists of an energy storage capacitor,  $C_e$ , two switches, a driver stage and a pulse shaper. This topology is suitable for on-off keying (OOK) with return-to-zero coding. At every falling edge of the input data, the charge switch is turned on and starts charging  $C_e$  during the period of  $T_0$  (stage 1) 'in Fig. 1) while the discharge switch is off. And at every rising edge of the input the discharge switch is turned on to discharge the stored energy (stage ②) with a short time discharge current  $I_d$ .  $I_d$  is then fed to a pulse shaper and subsequently the antenna. The pulse shaper is a high pass filter that reduces the low frequency spectrum components of the generated UWB pulse signal to fulfill FCC's mask. It should be noted that the starting time of charging and discharging are separated with a time interval of  $T_0$ . Therefore the charging can be done slowly during the whole period of  $T_0$ , resulting in a low peak value of the current. Different from existing duty cycled systems, where the energy is stored for a burst of data, the proposed approach stores energy only for one pulse generation. Therefore, the value of  $C_e$ is significantly smaller than the capacitors in existing methods and the required charging time is much shorter.

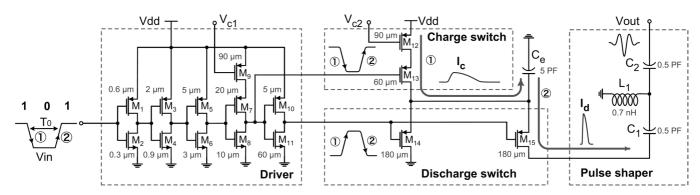

Fig. 2. CMOS implementation of the proposed IR-UWB pulse generator topology in Fig. 1.

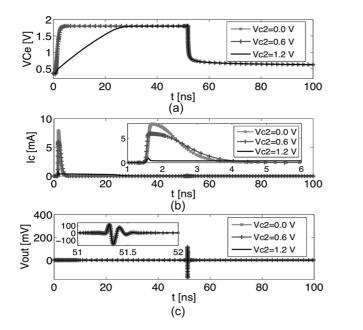

Fig. 3. Simulated (a) voltage on  $C_e$ , (b) charging current and (c) the generated UWB pulse waveform ( $V_{c1}=0$ ,  $T_0=50~\rm{ns}$ ).

The design implemented in the UMC 0.18  $\mu m$  CMOS process is shown in Fig. 2. The value of  $C_e$  is designed to 5 pF to achieve a storage capability of 8 pJ when charged to 1.8 V. The driver is implemented using a five-stage inverter chain  $(M_1 - M_{11})$ .  $V_{c1}$  is used to control the falling slope of the signal driving  $M_{14}$  and  $M_{15}$  for tunable pulse width. The charging switch is implemented using two cascaded PMOS transistors ( $M_{12}$  and  $M_{13}$ ). The gate of  $M_{12}$  is controlled by  $V_{c2}$  so that the amplitude of the charging current  $I_c$  can be adjusted. The discharging is done by  $M_{14}$  and  $M_{15}$ . The discharging current flowing throw M<sub>15</sub> is used for the generation of the pulse signal. To guarantee a short time duration of  $I_d$ and consequently a wide bandwidth of the generated UWB pulse signal, a relatively big size of  $M_{15}$  (180  $\mu m$ ) was chosen.  $M_{14}$  directly discharges part of the energy on  $C_e$  to ground. This is necessary to keep the discharging speed high, since the pulse shaper and the load antenna (50  $\Omega$ ) present a high discharging impedance. Including  $V_{c1}$  and  $V_{c2}$  in the design enables tuning capability of the UWB pulse generator under different operation scenarios [9]

The simulated voltages on  $C_e$ , charging currents and UWB pulse waveforms with a pulse repetitive rate (PRR) of 10 MHz are shown in Fig. 3. The input data signal falls at 0 ns , and rises at 50 ns. By using relatively small transistors ( $M_{12}$  and  $M_{13}$ ) the

Fig. 4. Simulated (a) voltage on  $C_e$ , (b) total current and (c) the generated UWB pulse waveform ( $V_{c2}=1.2,\,T_0=50~\mathrm{ns}$ ).

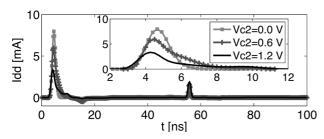

amplitude of the charging current is only 8 mA when both  $V_{c1}$ and  $V_{c2}$  are equal to 0 V. By increasing  $V_{c2}$  from 0 to 1.2 V the peak of  $I_c$  can be reduced to less than 1 mA. It should be noted that the energy stored on  $C_e$  is the same since  $C_e$  is charged to the same voltage value  $V_{dd}$  even though the charging currents are different [Fig. 3(a)]. Thus the generated UWB pulse signals are maintained identical [Fig. 3(c)]. The simulated total current consumption  $I_{dd}$ , including both  $I_c$  and the current consumption in the driver, is shown in Fig. 4. In this simulation,  $V_{c2} = 1.2 \text{ V}$ and  $V_{c1}$  varies from 0 V to 1.0 V. Similarly, by increasing the value of  $V_{c1}$  the peak value of  $I_{dd}$  at the time of discharging (mainly contributed by  $M_7$  and  $M_9$ ) can be reduced. In addition, the width of the generated UWB pulse signal is extended as  $V_{c1}$ increases. This is because  $V_{c1}$  changes the falling slope of the input to the discharge switch and hence changes the discharge speed. In the frequency domain, the PSD of the generated pulse can be shifted by applying different values of  $V_{c1}[9]$ .

# III. EXPERIMENTAL VALIDATION

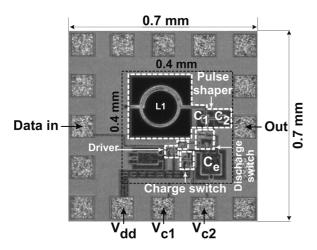

The fabricated prototype chip is shown in Fig. 5. The size of the design without measurement pads is  $0.4 \times 0.4~\mathrm{mm^2}$ . The total current of the generator was measured from the voltage across a  $10~\Omega$  series resistor connected between the power supply and the  $V_{dd}$  node of the generator (Fig. 6). The peak

Fig. 5. Microphotograph of the fabricated prototype chip.

Fig. 6. Measured total current of the UWB pulse generator at a PRR of 10 Mpps  $(V_{c1} = 1.0 \text{ V})$ .

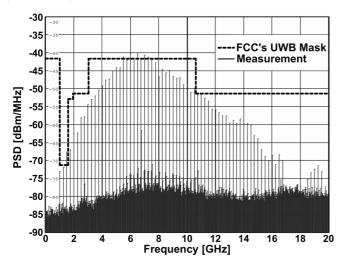

Fig. 7. Measured PSD of the UWB pulse signal with a PRR of 250 Mpps ( $V_{c1}=0.9~{\rm V}~V_{c2}=1.0~{\rm V}$ ). The resolution bandwidth is 1 MHz.

TABLE I COMPARISON OF MEASURED PERFORMANCE

| Ref       | CMOS<br>[μm] | PRR<br>[Mpps]     | EP<br>pJ/pulse     | BW<br>[GHz]        | PP<br>[mW]           | Area<br>[mm <sup>2</sup> ] |

|-----------|--------------|-------------------|--------------------|--------------------|----------------------|----------------------------|

| [3]       | 0.18         | 250               | 20                 | 3-5                | N/A                  | 0.08                       |

| [4]       | 0.13         | 100               | 9                  | 6.8                | 90                   | 0.54                       |

| [5]       | 0.18         | 100               | 18                 | 0.53               | N/A                  | 0.4                        |

| [6]       | 0.13         | 50                | 48                 | 3.1-4.8            | N/A                  | 0.11                       |

| [7]       | 0.09         | 400               | 65                 | 5.5                | N/A                  | 1.9                        |

| This work | 0.18         | 10<br>250<br>1000 | 18<br>14.6<br>5.0* | 7.5<br>6.75<br>6.0 | 6.0<br>10.0<br>10.4* | 0.16                       |

<sup>\*:</sup> Simulation

current of the pulse generator is only 3.3 mA while  $V_{c1} = 1.0 \text{ V}$ and  $V_{c2} = 1.2 \text{ V}$ , corresponding to a peak power dissipation of 6 mW and an energy consumption of 18 pJ/pulse with the power supply of 1.8 V. Fig. 7 shows the measured PSD of the generated UWB pulse signal at a PRR of 250 MHz. It can be seen that the PSD has a -10 dB bandwidth (BW) of 6.75 GHz (3.75-10.5 GHz) with a maximum magnitude of −40 dBm/MHz, which fulfills FCC's UWB mask. An added benefit of the pulse generator is that as the PRR increases, the time slot  $T_0$  available for charging  $C_e$  is reduced, and so is the energy stored on  $C_e$ . Therefore the pulse generator can operate with a high PRR up to 1 Gpps  $(V_{c1} = 1.0 \text{ V}, V_{c2} = 1.0 \text{ V})$ without violating FCC's radiation limit. The performance of the proposed UWB pulse generator is summarized in Table I and compared with previously published designs. It is clear that the proposed UWB pulse generator features low peak power dissipation (PP), broad bandwidth, low energy consumption (EP), and compact chip size compared to previous work.

# IV. CONCLUSION

A UWB pulse generator topology is presented in this letter. A slow-charge fast discharge approach is proposed to achieve low peak power dissipation as well as low energy consumption per pulse. The proposed design has been validated by a prototype UWB pulse generator fabricated using the UMC 0.18  $\mu$ m CMOS process. The fabricated UWB pulse generator offers a 3–10 GHz full bandwidth coverage with a minimum peak power dissipation of 6 mW (PRR = 10 Mpps). The energy consumption is 5 pJ/pulse at 1 Gpps, and the size of the core circuit is only 0.16 mm<sup>2</sup>. The proposed UWB pulse generator is suitable for short-rang applications with tight instantaneous power constrain such as battery-less self-sustainable wireless sensor networks based on energy harvesting.

### REFERENCES

- [1] J. Jang, D. Berdy, J. Lee, D. Peroulis, and B. Jung, "A wireless condition monitoring system powered by a sub-100 μW Vibration Energy Harvester," *IEEE Trans. Circuits Syst. I: Reg. Papers*, vol. 60, no. 4, pp. 1082–1093, Apr. 2013.

- [2] R. Vullers, R. Schaijk, H. Visser, J. Penders, and C. Hoof, "Energy harvesting for autonomous wireless sensor networks," *IEEE Solid State Circuits Mag.*, vol. 2, no. 2, pp. 29–38, Jun. 2010.

- [3] M. J. Zhao, B. Li, and Z. H. Wu, "20-pJ/pulse 250 Mbps low-complexity CMOS UWB transmitter for 3–5 GHz applications," *IEEE Mi*crow. Wireless Compon. Lett., vol. 23, no. 3, pp. 158–160, Mar. 2013.

- [4] S. Bourdel, Y. Bachelet, J. Gaubert, R. Vauche, O. Fourquin, N. Dehaese, and H. Barthelemy, "A 9-pJ/pulse 1.42-Vpp OOK CMOS UWB pulse generator for the 3.1–10.6-GHz FCC band," *IEEE Trans. Microw. Theory Tech.*, vol. 58, no. 1, pp. 65–73, Jan. 2010.

- [5] T.-A. Phan, J. Lee, V. Krizhanovskii, S.-K. Han, and S.-G. Lee, "A 18-pJ/pulse OOK CMOS transmitter for multiband UWB impulse radio," *IEEE Microw. Wireless Compon. Lett.*, vol. 17, no. 9, pp. 688–690, Sep. 2007.

- [6] Y. Choi, Y. Kim, H. Hoang, and F. Bien, "A 3.1–4.8-GHz IR-UWB all-digital pulse generator with variable channel selection in 0.13-CMOS technology," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 59, no. 5, pp. 282–286, May 2012.

- [7] H. Hedayati and K. Entesari, "A 90-nm CMOS UWB impulse radio transmitter with 30-dB in-band notch at IEEE 802.11a system," *IEEE Trans. Microw. Theory Tech.*, vol. 61, no. 12, pp. 4220–4232, Dec. 2013.

- [8] "Revision of part 15 of the commissions rules regarding ultra-wideband transmission system," in FCC, Tech. Rep. Et-docket, Feb. 14, 2002, pp. 98–153.

- [9] M. Miao and C. Nguyen, "On the development of an integrated CMOS-based UWB tunable-pulse transmit module," *IEEE Trans. Microw. Theory Tech.*, vol. 54, no. 10, pp. 3681–3687, Oct. 2006.