Received 24 June 2018; revised 9 August 2018, 4 September 2018, and 21 September 2018; accepted 4 October 2018.

Date of publication 8 October 2018; date of current version 9 November 2018.

Digital Object Identifier 10.1109/JXCDC.2018.2874805

# Performance Characterization and Majority Gate Design for MESO-Based Circuits

ZHAOXIN LIANG<sup>®</sup>, MEGHNA G. MANKALALE<sup>®</sup>, JIAXI HU<sup>®</sup>, ZHENGYANG ZHAO<sup>®</sup>, JIAN-PING WANG (Fellow, IEEE), AND SACHIN S. SAPATNEKAR<sup>®</sup> (Fellow, IEEE)

Department of Electrical and Computer Engineering, University of Minnesota, Minneapolis, MN 55455 USA CORRESPONDING AUTHOR: Z. Liang (zxliang@umn.edu)

This work was supported in part by C-SPIN, one of six centers of STARnet, a Semiconductor Research Corporation program, sponsored by MARCO and DARPA.

This paper has supplementary downloadable material available at http://ieeexplore.ieee.org, provided by the author. This consists of a PDF file containing additional material not included in the paper itself. This material is 75 KB in size.

ABSTRACT Magnetoelectric spin-orbit (MESO) logic is a promising spin-based post-CMOS logic computation paradigm. This paper explores the application of the basic MESO device concept to more complex logic structures. A simulation framework is first developed to facilitate the performance evaluation of MESO-based circuits. Based on the analysis, it is seen that inadvertent logic errors may potentially be introduced in cascaded MESO stages due to sneak paths, and solutions for overcoming this problem with a short pulse and two-phase evaluation are discussed. Next, the generalization of the MESO inverter structure to majority logic gates is shown. Two implementations, based on different physical mechanisms, are presented and a relative analysis of their speed and power characteristics is provided.

**INDEX TERMS** Inverse spin-orbit coupling (ISOC), magnetoelectric (ME) coupling, majority gate, simulation, spintronics.

#### I. INTRODUCTION

As CMOS-based designs reach their limits, there is an increasing interest in developing novel device technologies. Spin-based computing shows promise as it embraces emerging physical mechanisms and new materials to enable better device performance and enriched design functionality. Through mechanisms that allow material and feature scaling, spintronics provides a pathway for designing future electronic systems [1].

Magnetoelectric spin-orbit (MESO) logic [2] is a recently proposed spintronic logic device concept that achieves high energy efficiency by combining the ME coupling effect [3]–[5] with the inverse spin-orbit coupling (ISOC) effect [6]-[8]. Low-energy magnetic state switching is enabled by the ME coupling effect and realized with the presence of multiferroic materials or heterostructures [9], [10]. The ISOC effect provides efficient spin-to-charge conversion and facilitates the use of charge-based signal propagation between stages of logic. Unlike technologies such as all-spin logic [11], [12] that use spin current to propagate signals, the use of charge current avoids the large overhead of repeater insertion [13]. Together, the ME and ISOC effects realize energy-efficient transduction between the charge and magnetic state variables, and either could implement majority logic.

In this paper, we first develop a simulation framework to determine the energy and delay of a single MESO device as well as cascaded stages of MESO structures. We introduce our method for estimating the delay and energy of the MESO device based on our modified circuit model with conventional elements as well as the ferroelectric (FE) capacitor model based on Landau–Khalatnikov (LKh) equation. The simulation method and the performance measurement are described in Section II. Next, we examine issues related to cascading MESO logic stages in Section III, with particular attention to the potential for sneak paths that may disrupt correct operation. In Section IV, we propose and evaluate two approaches for implementing MESO majority gates based on the two different physical mechanisms in the MESO device, and conclude with Section V.

#### **II. MODELING A MESO INVERTER**

#### A. STRUCTURE OF A BASIC MESO INVERTER

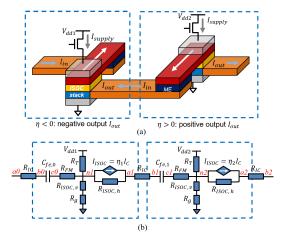

A basic MESO inverter [2] consists of several major components, as shown in Fig. 1: an *input unit* that uses ME coupling to transduce incoming charge current to a magnetic state variable in the in-plane ferromagnet (FM); an *output unit* that generates positive or negative charge current using the ISOC effect, depending on the magnetization in the FM; and a *metallic channel* that conducts charge current from an

FIGURE 1. Structure of a basic MESO inverter [2].

FIGURE 2. Cascaded MESO inverters and their circuit model [2].

output unit of the previous stage to an input unit of the current stage.

Fig. 2(a) shows a pair of cascaded MESO inverters, each associated with a different state, as indicated by the magnetization direction of the FM in each stage. The presence of two states is characterized by the sign of a parameter,  $\eta$ , defined as the conversion ratio between the supply current from the transistor and the current generated by the ISOC unit. The sign of  $\eta$  indicates whether the ISOC charge current injected by the output unit goes into ( $\eta$  < 0) or out of ( $\eta$  > 0) the metallic channel: this sign is determined by the direction of magnetization in the FM layer in the output unit. More details about  $\eta$  will be elaborated in Section II-B2. The operation of a single MESO inverter proceeds as follows.

- 1) The charge current from the output of the previous stage is injected into the FE material in the input unit of the current stage. The FE material is modeled as a capacitor for which the behavior is governed by the LKh equation [14], and the input current generates a voltage that switches its polarization.

- 2) The FE capacitor voltage induces a magnetic field on the FM due to the ME effect, flipping its magnetization.

- 3) The output unit has a transistor above the ISOC material stack and a ground contact beneath it. A charge current, injected through the transistor, is polarized to positive or negative spin currents, depending on the magnetization in the FM [15]. This spin current flows into the ISOC conversion stack beneath the FM,

which performs spin-to-charge conversion based on the inverse spin-Hall effect (ISHE) and the inverse Rashba–Edelstein effect (IREE) [6]–[8]. Depending on the spin current polarity, either positive or negative charge current flows into the metallic interconnect that drives the next logic gate.

#### B. CIRCUIT MODEL FOR A MESO INVERTER

In this section, we will introduce a circuit model of a MESO inverter and elaborate upon the ISOC current conversion model as well as the response of the FE capacitor polarization. We will then show how a MESO stage can be analyzed using numerical circuit simulation to extract its delay and energy.

#### 1) CIRCUIT MODEL

A circuit model for the MESO inverter was proposed in [2]. We extend this model to show the model for cascaded pair of MESO inverters in Fig. 2(b), which shows the interactions between the successive stages. Our interest is in modeling the time required by this structure to charge the FE capacitor in the output unit, and accordingly we isolate the subcircuit that contributes to driving this capacitor and illustrate it in Fig. 3. This differs slightly from the model in [2], where node c was connected directly to ground; in contrast, we show that this path goes through a few resistors.

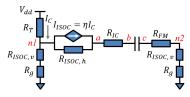

FIGURE 3. Circuit model for a single MESO inverter [2].

The transistor is connected to a supply voltage,  $V_{\rm dd}$ , and is modeled as an effective resistance  $R_{\rm T}$ . This is valid given that the gate capacitance is small enough compared to the effective capacitance of the FE capacitor, and thus a gate transition does not induce a coupled voltage spike at the source that moves the transistor out of the linear region. Under the assumption that the transistor driving each stage is clocked during the transition, only  $R_{\rm T}$  for the current stage must be considered. The FM and ISOC material stacks are modeled as a vertical resistance  $R_{\rm ISOC,v}$ , and are connected to the ground lead resistance,  $R_g$ . The generation of charge current from spin current is modeled as a current-controlled current source (CCCS), with a horizontal resistance  $R_{\rm ISOC,h}$ representing the internal ISOC source resistance. The interconnect resistance  $R_{\rm IC}$  associated with the metallic channels leads to one plane of the FE capacitor. The other plane of the FE capacitor is connected to a resistance  $R_{\text{FM}}$  representing the entire horizontal resistance of FM. The FM is then connected to the vertical ISOC unit and the ground lead of the next MESO inverter, represented by  $R_{\rm ISOC,v}$  and  $R_{\rm g}$  from the next stage.

TABLE 1. Simulation parameters for the MESO circuit.

| Parameter                                          | Value                          |

|----------------------------------------------------|--------------------------------|

| $V_{dd}$ (source voltage)                          | 100mV                          |

| $\eta$ (conversion ratio)                          | 1.0                            |

| A (ferroelectric capacitor area)                   | $10 \times 10$ nm <sup>2</sup> |

| T (multiferroic layer thickness)                   | 5.0nm                          |

| $R_T$ (equivalent resistance of transistor)        | $23 \mathrm{k}\Omega$          |

| $R_g$ (ground lead resistance)                     | $500\Omega$                    |

| $R_{ISOC,v}$ (vertical resistance of ISOC stack)   | $1.5 \mathrm{k}\Omega$         |

| $R_{ISOC,h}$ (horizontal resistance of ISOC stack) | $10 \mathrm{k}\Omega$          |

| $R_{IC}$ (resistance of interconnect)              | $1k\Omega$                     |

| $R_{FM}$ (resistance of FM)                        | $1k\Omega$                     |

| $C_g$ (gate capacitance, per inverter)             | 0.2aF                          |

| $V_g$ (gate voltage)                               | 0.73V                          |

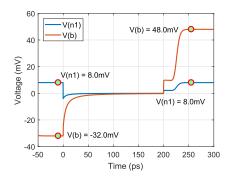

FIGURE 4. Voltage at nodes n1 and b for a single MESO inverter, with negative  $\eta$  before 0 ps and positive  $\eta$  after 200 ps.

#### 2) MODEL FOR THE ISOC UNIT

The spin-to-charge conversion occurs in the ISOC stack based on the ISHE and IREE effects. The conversion between the spin current  $I_s$  and the generated charge current  $I_{ISOC}$  can be written in the following form [2]:

$$I_{\rm ISOC} = \frac{1}{w} \left[ \lambda_{\rm IREE} + \Theta_{\rm SHE} \lambda_{\rm sf} \tanh \left( \frac{t}{2\lambda_{\rm sf}} \right) \right] \cdot I_{\rm s}$$

(1)

where w is the width of the ISOC conversion unit and  $\lambda_{\rm IREE}$  represents the IREE length [16]. The bulk ISHE is indicated by the spin-Hall angle  $\Theta_{\rm SHE}$ , the spin diffusion length  $\lambda_{\rm sf}$ , and the thickness t. The spin current,  $I_{\rm s}$ , injected into this stack is polarized by the FM from the charge current  $I_{\rm c}$ , that is,

$$I_{\rm S} = \pm P \cdot I_{\rm C} \tag{2}$$

where P is the spin polarization. Therefore, the conversion ratio  $\eta = I_{\rm ISOC}/I_{\rm c}$  for the CCCS can be written as

$$\eta = \pm \frac{P}{w} [\lambda_{\text{IREE}} + \Theta_{\text{SHE}} \lambda_{\text{sf}} \tanh(t/2\lambda_{\text{sf}})]. \tag{3}$$

Using simulation parameters that will be detailed in Table I, the transient waveform for switching the voltage at node n1 and node b is shown in Fig. 4 when the sign of  $\eta$  changes from negative (before 0 ps) to positive (after 200 ps). It can be seen that the steady-state voltages for b are asymmetric about zero. To understand this, consider the steady state, where the FE capacitor can be treated as an open circuit, and no current flows through  $R_{\rm IC}$ . Thus, the

voltage drop on the FE capacitor equals the voltage drop at node b, i.e., the voltage across  $R_{\rm ISOC,h}$  plus the voltage of node n1. The plot shows that the voltage at node n1 settles to 8.0 mV in the steady state. Since no current flows into  $R_{\rm IC}$ , the charge current  $I_{\rm ISOC}$  must flow to ground through  $R_{\rm ISOC,h}$ . From (3), the magnitude of  $\eta$  is identical for either FM polarization, but the sign depends on the Polarization; as a result, in this case, the voltage drop from node b to node n1 is  $\pm 40$  mV. This results in asymmetric steady-state voltage levels of 8-40 mV=-32.0 mV and 8+40 mV=+48.0 mV, as shown in Fig. 4.

#### 3) MODEL FOR THE FE CAPACITOR

The LKh equation [14], [17], [18] governs the temporal response of the electric polarization P in the FE capacitor to the electric field E

$$\gamma \frac{dP}{dt} = \frac{1}{2}\beta E - g_2 P - g_4 P^3 - g_6 P^5 \tag{4}$$

where  $\gamma$  is a parameter indicating the switching speed, and  $\beta$ ,  $g_2$ ,  $g_4$ , and  $g_6$  are obtained as fitting parameters that match experimental data to this theoretic model [18]. In the Supplementary Material, we demonstrate a hysteresis loop obtained based on (4) and the related remnant polarization.

#### C. CIRCUIT SIMULATION

The components associated with the MESO circuits in Figs. 2(b) and 3 can be classified into elements defined by linear algebraic equations (resistors, supply voltage source, and CCCS), and by nonlinear differential equations (FE capacitor). We analyze this structure by discretizing the differential equations in time, and at each time step, using Newton–Raphson linearizations to obtain affine representations of circuit elements that are solved by modified nodal analysis (MNA).

We focus on the FE capacitor that is represented by the LKh equation, which is a nonlinear differential equation. We show in the following how the FE capacitor can be represented using an I-V relationship, eliminating the polarization variable P.

We begin with the equation  $Q = A(\epsilon_0 E + P) = A(\epsilon_0 V/T + P)$  that describes the free charge Q as a function of voltage V and polarization P on a capacitor with area A and a distance T between plates; here, T is the thickness of the FE capacitor. Based on the above-mentioned equation, we obtain the following linear relation between P, I, and V in the (i+1)th time step:

$$P = \left\lceil \frac{h}{A} \right\rceil I - \left\lceil \frac{\epsilon_0}{T} \right\rceil V + \left\lceil P_i + \frac{\epsilon_0 V_i}{T} \right\rceil \tag{5}$$

where  $V_i$  and  $V_i$  are the values of V and P, respectively, in the ith time step, and h is the simulation time step. A derivation of (5) is provided in the Supplementary Material.

Next, we revisit (4) and replace electric field E = V/T

$$\gamma \frac{dP}{dt} = \frac{\beta V}{2T} - f(P)$$

where  $f(P) = g_2 P + g_4 P^3 + g_6 P^5$ . (6)

To eliminate P and create an I-V relationship for the FE capacitor, we combine (14), (5), and (6) to obtain the non-linear I-V relation at the (i+1)th time step

$$g(I, V) = \left[\frac{\gamma}{A}\right]I - \left[\frac{\gamma\epsilon_0}{Th} + \frac{\beta}{2T}\right]V + \frac{\gamma\epsilon_0}{Th}V_i + f\left(\left[\frac{h}{A}\right]I - \left[\frac{\epsilon_0}{T}\right]V + \left[P_i + \frac{\epsilon_0}{T}V_i\right]\right) = 0 \quad (7)$$

where g is a polynomial in I and V. Using standard circuit simulation approaches, we now create an affine approximation to this function about a guess,  $(I^k, V^k)$ , where the superscript k represents the Newton-Raphson iteration number

$$g(I^{k}, V^{k}) + \frac{dg}{dI} \left|_{I^{k}, V^{k}} (I - I^{k}) + \frac{dg}{dV} \right|_{I^{k}, V^{k}} (V - V^{k}) = 0.$$

(8)

This provides a stamp [19] for the FE capacitor element, which when combined with the stamps for the resistors and CCCS, yields the MNA equations for each Newton–Raphson iteration.

#### Algorithm 1 Simulation Method for a MESO Gate

**Input:** Circuit netlist, initial polarization  $P_0$  and voltage  $V_0$ ; **Output:** Polarization P of the FE capacitor, voltage V and current I of every node in the circuit over the simulation period.

- 1:  $t_i \leftarrow 0, i \leftarrow 0, P_i \leftarrow P_0, V_i \leftarrow V_0$ .  $\triangleright$  Initialization for time zero

- 2: repeat

- 3:  $t_{i+1} \leftarrow t_i + h, i \leftarrow i + 1.$   $\triangleright$  Time-stepping to the next simulation time

- next simulation time

4:  $k \leftarrow 1, V^0 \leftarrow V_i$  and  $I^0 \leftarrow I_i$ .  $\triangleright$  Newton–Raphson initializations

- repeat ▷ Newton–Raphson iterations at time step i

Calculate dg/dI and dg/dV at I<sup>k</sup>, V<sup>k</sup>, based on g(I, V) in (7).

- 7: Construct the affine relation between *V* and *I* based on (8).

- 8: Construct the MNA equations and solve them for *V* and *I*.

- 9:  $k \leftarrow k + 1$ .

- until V and I converge to the solution at time step i.

- 11: Use V and I to calculate P at time step i based on (5).

- 12: until End of simulation time.

The simulation method is summarized in Algorithm 1. After initialization (line 1), the entire simulation contains two nested loops: the outer loop (lines 2–12) performs time-stepping, setting up the computations for V, I, and P at each time step, while the inner loop (lines 5–10) performs Newton–Raphson iterations to solve the nonlinear equations at each time step. The Newton–Raphson iterations develop the affine form in (8) based on the partial derivatives of g(I, V), (7), which is used to create and solve the MNA equations (line 8).

## D. CALCULATION OF DELAY AND ENERGY FOR THE MESO INVERTER

1) CALCULATION OF THE MESO INVERTER DELAY

The delay of a single MESO inverter includes two parts: the delay of switching the FE capacitor polarization, and the delay of switching the magnetization in the FM layer.

Delay of Switching FE Capacitor Polarization: As mentioned in Section II-B2, the incoming charge current from previous MESO inverter is injected into the ME unit, creating a voltage drop across the FE capacitor and switching its polarization. The switching response of the FE capacitor polarization is governed by the LKh equation and simulated numerically. As a baseline example, we perform the simulation to measure the inverter delay based on the parameters in Table I. The resistances related to ISOC stack are estimated based on the information from [20], with the rest of the parameters from [2]. For the FE capacitor, the parameters in (4) are set to  $\beta = 500$ ,  $\gamma = 3.5 \times 10^{-4}$ ,  $g_2 = -2.0 \times 10^3$  Jm/C<sup>2</sup>,  $g_4 = -2.4 \times 10^9$  Jm<sup>5</sup>/C<sup>4</sup>, and  $g_6 = 4.2 \times 10^{10}$  Jm<sup>9</sup>/C<sup>6</sup> [18].

As elaborated in Section S.4 of the Supplementary Material, the rise time  $t_r$ , defined as the time required for the signal to transition from its 10% point to its 90% point, is 28.9 ps. The fall time is analogously defined and obtained as 46.8 ps. The average switching delay is  $t = (t_r + t_f)/2 = 37.9$  ps.

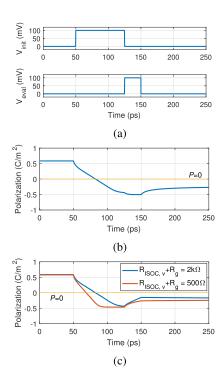

As mentioned in Section II-B2, the voltage drop across FE capacitor (between node b and c) has a higher absolute value when  $\eta$  is positive (48 mV) compared to the case when  $\eta$  is negative (32 mV), leading to the asymmetry in the rising and falling transition as  $t_r < t_f$ . This symmetry is inevitable due to the circuit structure, but could be alleviated if the resistance to ground from n1, ( $R_{\rm ISOC,v} + R_{\rm g}$ ), could be reduced and/or if the conversion rate,  $\eta$ , could be increased. Both correspond to materials-related advances. For example, reducing ( $R_{\rm ISOC,v} + R_{\rm g}$ ) from  $2k\Omega$  to  $500\Omega$  at the same  $\eta$  would change the steady-stage voltages to 44.7 mV for  $\eta > 0$  and -40.4 mV for  $\eta < 0$ , with  $t_r = 26.6$  ps and  $t_f = 30.2$  ps, and a smaller average delay of t = 28.4 ps.

Delay of Switching FM Magnetization: After the polarization of the FE capacitor is switched, the FM magnetization will be switched due to the ME effect. This delay is added directly to the switching delay of the FE capacitor to obtain the inverter delay. As in [2], the switching delay of the FM is treated as a fixed time, which is determined by the in-plane FM material parameters and the FE material properties. When the sign of electric polarization P in the FE capacitor changes, this constant latency representing the switching of FM follows, after which the sign of  $\eta$  in the next MESO inverter becomes opposite to the sign of P in current MESO inverter.

#### 2) CALCULATION OF MESO INVERTER ENERGY

The MESO device energy per transition consists of two parts: 1) the energy dissipated by the MESO inverter comes from the supply source through the transistor, i.e., the product of the source voltage  $V_{\rm dd}$ , the current through the transistor resistance  $I_{\rm supply}$ , and the delay of the MESO inverter t and

2) the energy for charging the gate capacitor,  $C_g$ . The total energy is given by

$$E = V_{\rm dd} \cdot I_{\rm supply} \cdot t + C_{\rm g} \cdot V_{\rm g}^2. \tag{9}$$

Note that the energy related to the ME coupling effect enabled FM switching is the charging energy of the FE capacitor. The charging process completes during the pulse t and is part of the first term in (9). For circuits with multiple MESO gates, if each gate i is pulsed for time  $t_i$  during its transition, the first term is altered to  $V_{\rm dd} \cdot I_{\rm supply} \cdot \sum t_i$ . Using the parameters in Table I, the rise and fall switching energies are 13.4 and 19.2 aJ, respectively, where  $C_{\rm g}V_{\rm g}^2=1.1$  aJ in each case.

#### **III. SNEAK PATHS IN CASCADED MESO INVERTERS**

As stated in Section II-B2, since the FE capacitor acts as an open circuit at steady state, the voltage drop across an FE capacitor (between node b and c as shown in Fig. 3) in a single MESO inverter model is determined by the voltage drop across  $R_{\rm ISOC,h}$  (between node n1 and a), plus the node voltage at n1. In this figure, the voltage for one plate of the FE capacitor, at node c, is zero since no current flows through the resistors between c and ground in steady state; the same is true of the simpler model in [2], where c is directly connected to the ground.

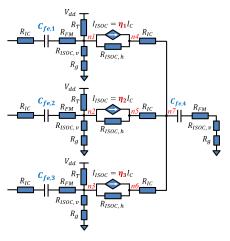

However, the simplifications of considering a single stage must be reexamined for the case where inverters are cascaded. The circuit model for this case is shown in Fig. 2(b). Assuming that each stage is clocked while it is switching, the transistor for the first gate is turned off after  $C_{\text{fe},1}$  is charged, and the transistor for the second gate is turned on. In other words,  $R_{\rm T}$  for the second gate was an open circuit while  $C_{\text{fe},1}$  was being switched, but enters the circuit after the FE capacitor is charged. This creates two sneak paths. 1) A discharging path from b to ground through  $R_{\rm ISOC,h}$  and  $R_{\rm g}$  (the CCCS goes to zero since  $I_{\rm s}=0$  when the transistor is off), which sets the voltage of b to zero in the steady state. 2) An additional charging path to c through n2 that could corrupt the stored value on  $C_{\text{fe},1}$ . If only the former path was present, this would not be a cause for concern, since the polarization would move to its nonzero remnant polarization value when the voltage across the capacitor decays to zero. In this section, we show that the latter sneak path, when coupled with the former, may change the voltage drop across the FE capacitor, and thus inadvertently switch its polarization under some clocking scenarios. This can be avoided, but imposes additional overheads and delay constraints in the design of MESO gates. We now consider the following two clocking scenarios.

- 1) *Pulsed Clocking*: Each MESO inverter in a cascade is turned on by a single pulse for a certain period of time.

- Always-On: Every MESO inverter in a cascade is turned on for the entire period of operation of the circuit.

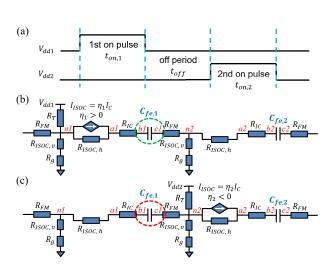

FIGURE 5. (a) Pulsed clocking waveform. (b) and (c) Equivalent circuit representations during successive clock pulses.

#### A. SNEAK PATHS UNDER PULSED CLOCKING

Fig. 5 shows the voltage waveform that clocks the transistors for two successive stages in a cascaded MESO inverter chain, and the circuit models during these two pulses. The operation of the circuit can be divided into several steps.

- 1) As shown in Fig. 5(b), when the first pulse  $t_{\text{on},1}$  turns on the supply current, the generated ISOC current will start to charge the FE capacitor in the first stage. For illustration, we consider the case where  $\eta > 0$  (the  $\eta < 0$  case is analogous); here, the voltage drop across  $C_{\text{fe},1}$  will be positive (V(b) > V(c)) and the polarization will switch to its positive saturation value.

- 2) Next, in the OFF period  $t_{\rm off}$ , the polarization in  $C_{\rm fe,1}$  drops toward its remnant value, and the magnetization in the adjacent FM is switched by the ME effect.

- 3) The second pulse, t<sub>on,2</sub> in Fig. 5(a) corresponds to the circuit shown in Fig. 5(c), and serves to charge node b<sub>2</sub>, setting C<sub>fe,2</sub> to a negative polarization. However, this pulse will also pull up the voltage at node c<sub>1</sub> through the path V<sub>dd2</sub> → n2 → c2, while the sneak path b<sub>1</sub> → a<sub>1</sub> → n<sub>1</sub> → ground will discharge the plate of C<sub>fe,1</sub> on the node b<sub>1</sub> side. Thus, a negative voltage between nodes b<sub>1</sub> and c<sub>1</sub> may be created. This voltage sets up a transient that can change the polarization of C<sub>fe,1</sub> from positive to negative, which may cause an inadvertent error.

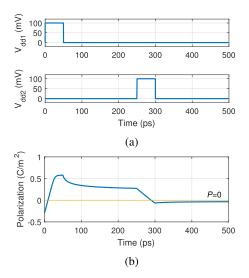

For the case when  $t_{\rm on,1} = t_{\rm on,2} = 50$  ps and  $t_{\rm off} = 200$  ps, as shown in Fig. 6(a), under the technology parameters in Table I, we show the transient behavior of the polarization in the FE capacitor,  $C_{\rm fe,1}$ , in Fig. 6(b). The choices for the on pulsewidth are based on our simulation results for single-inverter transition time as in Section II-D1. The polarization should have remained positive after 50 ps, but it can be seen an inadvertent error caused as  $C_{\rm fe,1}$  is switched to a negative polarization during  $t_{\rm on,2}$  due to the sneak path.

This inadvertent error may be avoided by optimizing the operation periods. For example, in Fig. 7, when we alter

FIGURE 6. (a) Waveform for two successive on pulses (50-ps pulsewidth, 200-ps off time) for two cascaded MESO inverters, resulting in (b) inadvertent polarization error in  $C_{\rm fe,1}$ .

FIGURE 7. (a) Modified waveform with 25-ps pulsewidth, 200-ps OFF time. (b)  $C_{\rm fe,1}$  functions correctly, retaining P>0.

$t_{\text{on},1} = t_{\text{on},2} = 25$  ps, the polarization remains positive even after the second pulse, even in the presence of a sneak path.

### B. SNEAK PATH EFFECTS UNDER ALWAYS-ON CLOCKING

The always-on clocking model negates the effect of sneak paths completely. Under this model, all transistors are on for the entire duration, and the circuit model is identical to that shown in Fig. 2(b). In this mode, the two nodes b1 and c1 on the two sides of the two plates for  $C_{\rm fe,1}$  are both connected to supply current paths, and there is no sneak path discharging the FE capacitor. However, the energy consumption here is high as the  $V_{\rm dd}$  supply constantly provides current to the system.

In summary, the pulse time matters in several respects. As explained in Section II-D2, smaller pulse time is preferred for lower energy consumption. Nonetheless, enough pulsewidth is still required to guarantee successful switching. Pulse time is also important in the occurrence of sneak path effects as discussed in Figs. 6 and 7. Choosing a proper pulse time (25 ps in Fig. 7) could prevent the electric polarization from going to the undesired negative region (as shown in Fig. 6(b) at 300 ps) due to the sneak path, while the FE capacitor still have enough time to complete a successful switching.

#### IV. MESO-BASED MAJORITY GATE DESIGN

We now discuss how to construct a majority gate based on two approaches for switching the FE capacitor polarization at the next stage. We use the gate inputs to either: 1) generate competing domain walls (DWs) that switch the magnetization at the FM output; or 2) generate competing charge currents. These gates calculate the minority amongst the three inputs. Instead of using the term "minority gate" or "majority complementary gate," we use the term "majority gate" as in [21].

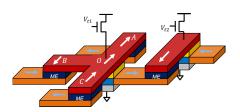

#### A. MAJORITY GATE USING COMPETING DWs IN THE FM

A three-input majority gate could be formed by feeding each input to a structure similar to a MESO inverter, and connecting their FMs together into a single merged structure driving an output ISOC unit, as illustrated in Fig. 8. Each input ME unit switches the magnetization of the partial FM region above it, and propagates a DW that transmits the magnetization from three input branches to the junction. The majority of magnetization will propagate to the output branch O in a properly designed FM [22] with a switching time of 200 ps. Next, as in the case of the MESO inverter, the magnetization at the output O determines the direction of the charge current generated out of the ISOC unit in the output stack, switching the polarization of the input FE capacitor of the next gate.

FIGURE 8. Majority gate with competing DWs.

In computing the energy for a gate, we count the energy required to switch O and to switch the input FE capacitor of the next gate. Therefore, the energy for switching the polarization in the FE capacitors in each input ME unit of the current gate is counted toward the energy consumption of the previous MESO gates. Based on this approach, the energy for this majority gate is identical to a single MESO inverter, as given in (9), and consists of the energy required to drive the load FE capacitance and the energy required to switch

the transistor above *O*. Similarly, the delay corresponding to switching the polarization of the load FE capacitor is the same as that for a single MESO inverter delay, and as before, the delay of propagating the signal through the FM is treated as a constant. Therefore, the delay and energy consumption of this majority gate is the same as that in Section II-D1.

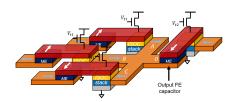

#### **B. MAJORITY GATE USING CHARGE CURRENTS**

Alternatively, majority gates can be implemented using the charge current, as shown in Fig. 9. Here, the three metallic channels A, B, and C going out of each ISOC unit merge together and connect to a common FE capacitor through the output branch O. The majority direction of the charge current in the three metallic channels determines whether the voltage drop on the output FE capacitor is positive or negative, which realizes the majority function. We show that the current to the load is not the algebraic sum of the  $I_{\rm ISOC}$  values in each of the three branches, and other circuit elements also play a part.

FIGURE 9. Majority gate based on competing charge currents.

FIGURE 10. Circuit model for the charge-based majority gate.

#### 1) OUTPUT VOLTAGE OF THE MAJORITY GATE

The operation of the gate is captured by the circuit model in Fig. 10. The polarization of each FE capacitor  $C_{\text{fe},k}$  (k=1,2,3) determines the magnetization in the adjacent magnets through the ME effect, and consequently the sign of  $\eta$  for each ISOC unit. The sign of each  $\eta$  indicates not only the direction of charge current in the three channels but also the voltage level at nodes n4, n5, and n6: a positive  $\eta$  results in V(ni) > 0 (i=4,5,6) in the corresponding branch; otherwise V(ni) < 0.

Since an FE capacitor is an open circuit in the steady state, the voltage drop across  $C_{\text{fe},4}$  is determined by V(n7) with the opposite plate at ground. The voltage at node n7 is a result of voltage division between V(ni) (i=4,5,6) through the channels: a branch with  $\eta>0$  induces a higher voltage and will inject current into the branch with  $\eta<0$ , so that

$$\min_{i \in \{4,5,6\}} V(ni) \le V(n7) \le \max_{i \in \{4,5,6\}} V(ni). \tag{10}$$

Therefore, if the inputs with positive  $\eta$  are in the majority [minority], V(n7) will stabilize at a positive [negative] value.

TABLE 2. Steady-state voltages in a charge current-based MESO majority gate for different input combinations.

| Sign of $\eta$ | Node voltages |          |          |          |  |

|----------------|---------------|----------|----------|----------|--|

| on the inputs  | V(n4)         | V(n5)    | V(n6)    | V(n7)    |  |

| +++            | 48.0mV        | 48.0mV   | 48.0mV   | 48.0mV   |  |

| + + -          | 25.5mV        | 25.5mV   | 19.4mV   | 23.5mV   |  |

| +              | 1.2mV         | -5.2mV   | -5.2mV   | -3.1mV   |  |

|                | -32.0 mV      | -32.0 mV | -32.0 mV | -32.0 mV |  |

From Table II, the cases with three or zero positive  $\eta$  values show no voltage difference between V(ni) (j=4,5,6), and thus V(n7) equals each V(ni) since no current flows through the metallic channel. In the other two cases, the positive  $\eta$  branch(es) inject(s) current into the negative  $\eta$  branch(es), even in the steady state. This creates a voltage divider that determines the voltage at the intermediate node, n7.

The voltage values are not symmetric, e.g., the case where all inputs have  $\eta>0$  has a larger output voltage than the case where all inputs have  $\eta<0$ . The root cause of this is similar to the asymmetry seen in the voltage drop on the FE capacitor in a MESO inverter under negative and positive  $\eta$ , as discussed in Section II-B2. For cases where all three  $\eta$  values do not have the same sign, the magnitude of V(n7) is even lower, although for these parameter values, the majority gate operates correctly, i.e., the sign of the voltage at n7 matches the majority sign of the  $\eta$  values at the gate inputs.

However, this may not always be true, and V(n7) depends on the voltage divider action. In fact, if the value of  $(R_{\rm ISOC,h}+R_{\rm g})$  is too high, the voltage for the +- case may not go below zero, and the output FE capacitor may incorrectly carry a positive P. This effectively places an upper bound on  $(R_{\rm ISOC,h}+R_{\rm g})$ . Keeping all other simulation parameters unchanged, if this total resistance is increased from 2 to 3 K $\Omega$ , then the polarization will not be switched to a negative value. In this case, the values of V(n4), V(n5), and V(n6), are 4.2, -1.9, and -1.9 mV, respectively. The voltage divider action then sets V(n7)=0.13 mV, which incorrectly results in P>0 at the output FE capacitor.

Practically, switching at small voltages such as 3.1 mV is challenging under current technologies and may even fail since it is smaller than the coercive field of typical candidate materials. Increasing the value of  $\eta$  or  $R_{\rm ISOC,h}$  and decreasing  $R_{\rm g}$  or  $R_{\rm ISOC,v}$  in new technologies can help in raising the voltage to a higher value. For example, reducing  $R_{\rm g} + R_{\rm ISOC,v}$  from 2 to 1 k $\Omega$  and increasing  $\eta$  from 1.0 to 2.0 would raise the voltage from 3.1 to 17.8 mV.

TABLE 3. Transition times for the output FE capacitor polarization in a charge current-based MESO majority gate.

|      | Before       | transition | After transition |          | Delay | Energy |

|------|--------------|------------|------------------|----------|-------|--------|

|      | Input $\eta$ | V(n7)      | Input $\eta$     | V(n7)    | (ps)  | (aJ)   |

| Rise |              | -32.0 mV   | +++              | 48.0mV   | 13.5  | 18.5   |

|      |              | -32.0 mV   | + + -            | 23.5mV   | 26.0  | 34.1   |

|      | +            | -3.1mV     | +++              | 48.0mV   | 11.7  | 16.4   |

|      | +            | -3.1mV     | + + -            | 23.5mV   | 22.4  | 30.6   |

| Fall | +++          | 48.0mV     |                  | -32.0 mV | 21.3  | 26.5   |

|      | +++          | 48.0mV     | +                | -3.1mV   | 155.4 | 188.4  |

|      | + + -        | 23.5mV     |                  | -32.0 mV | 20.4  | 25.9   |

|      | + + -        | 23.5mV     | +                | -3.1mV   | 154.1 | 189.0  |

#### 2) ENERGY AND DELAY OF THE MAJORITY GATE

Table III provides a summary of the rise and fall transition time under various input combinations. The overall delay of the majority gate is the transition time listed, added to the 200-ps delay of the FM. A rise transition goes from a case where the majority of  $\eta$  values is negative to one where the majority is positive. From Table II, the negative and positive majorities each correspond to two cases, and therefore, four cases must be considered. The same is true of the fall transition.

The table shows a large range of delay values for the 90% switching time of the output FE capacitor polarization, depending on the initial and final input states. This can be ascribed largely to the voltage drop on the FE capacitor after the transition: larger steady-state values of V(n7) correspond to smaller delays. There are two cases in the fall transition time that are significantly larger than others, when inputs transition to +- from different input states. Here, the final steady-state voltage at n7 has the smallest magnitude. This causes a small electric field across the FE capacitor, resulting in a slow transition. Considering the worst case transition, for a three-input majority gate based on charge current, we have  $t_r = 26.0$  ps,  $t_f = 155.4$  ps, and the average delay t = 90.7 ps.

The last column in Table III shows the energy dissipation of the charge current-based majority gate implementation. Similar to the single MESO inverter case, the energy of the majority gate is the summation of energy from the  $V_{\rm dd}$ source at each branch within the transition time. Long transition times naturally involve large energy dissipation, e.g., the energy for the fall transition of  $t_f = 155.4$  ps is 188.4 aJ, much higher compared to most of the other cases. Note that there is another case with a delay of  $t_f = 154.1$  ps but a slightly higher energy of 189.0 aJ. These two cases both share the same input states after the transition, but the input state for the latter case before the transition is composed of two positive  $\eta$  and one negative  $\eta$ , meaning that there are currents flowing between node n4, n5 and n6 at the beginning of the transition. Therefore, the averaged current during the transition is slightly higher and incurs a larger energy in the latter case. These values are much higher than the DW-based majority gate.

## 3) IMPROVING THE WORST CASE DELAY USING STEM For cases where the difference between the best and worst case delays is large, the work in [23] had proposed STEM,

a two-phase majority gate scheme for faster operation. We now show how STEM can be applied here to reduce the energy and delay.

In the first phase, STEM uses an initialization pulse to preset the polarization at the output with only one input branch activated. Immediately after this initialization phase ends, a short evaluation pulse is applied to the other two branches. If  $\eta$  for these two branches have opposite signs, then the majority value corresponds to the initial value. In this case, under the short pulse, V(n7) will be close to zero (even under asymmetric voltage levels), and the short pulse will not be applied for long enough to switch the polarization, and the majority function is correctly evaluated. On the other hand, if the two branches in the later phase have the same sign of  $\eta$ s, they will induce a large voltage magnitude at n7, which will cause the polarization at the output to be switched very fast.

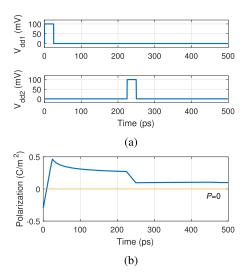

FIGURE 11. (a) Two-phase STEM pulse. (b) Fall transition with inputs going from three positive  $\eta$  to three negative  $\eta$ . (c) Two fall transitions with inputs going from three positive  $\eta$  to two negative  $\eta$  and one positive  $\eta$ , for different values of  $R_{\rm ISOC,V}+R_{\rm g}$ . The initialization phase activates one of input branches with  $\eta < 0$ .

The two-phase STEM switching process is illustrated under an initialization pulse of 75 ps and an evaluation pulse of 25 ps, as shown in Fig. 11(a). We first consider the scenario where the input switches from  $\eta$  values of + + + to - - in Fig. 11(b). During the 75-ps initialization phase, the output switching to one of the incoming inputs, corresponding to a negative polarization. In the second phase, this polarization is reinforced by two negative inputs, resulting in a net negative polarization at the end of the second pulse. The FE capacitor then returns to its remnant polarization, as seen in the figure.

Next, in Fig. 11(c), we show the fall transitions when the input switches from + + + to + - -. If the initialization activates a branch of negative  $\eta$ , the first pulse results in an identical waveform as the previous case. The second pulse causes a small increase in the polarization: this is caused by a positive V(n7) due to asymmetry, when one branch with negative  $\eta$  and one branch with positive  $\eta$  are activated at the same time, and is a result of the voltage divider that determines V(n7). As stated earlier, this is influenced by  $(R_{\rm ISOC,v} + R_{\rm g})$ : in the same figure, we show another curve that considers a smaller value of  $(R_{\rm ISOC,v} + R_{\rm g})$ ; here, the polarization at the end of the second pulse is more negative. The smaller value demonstrates better switching and takes the polarization to saturation faster and suggests that the widths of the first pulse used in the two-phase scenario can be further reduced.

This STEM scheme reduces the worst case delay from 155.4 to 100 ps, the sum of the two pulse widths, and results in an average energy of 42.5 aJ, significantly better than the 188.4 aJ associated with the worst case and the 66.2 aJ average over all cases in Table III. The energy of charging the gate capacitor per transistor under STEM is also 1.1 aJ, the same as that for charging a single MESO inverter. The two-phase scenario may incur slightly more overhead for clock distribution, which is not included in our energy estimate.

#### V. CONCLUSION

This paper has introduced a method to simulate the performance of the MESO device, incorporating the LKh equation for FE capacitor polarization switching into traditional MNA-based circuit simulation to compute the energy/delay under realistic parameters. This paper has also presented the potential sneak path issue that may induce inadvertent logic errors in the cascaded MESO inverter chain. Two different majority gate implementations are proposed and analyzed based on the two computation mechanisms in the MESO device. For the charge-based majority gate, some input scenarios may be unable to reach the coercive field of the material, which results in switching failure: this is avoided by the STEM-based scheme.

#### **ACKNOWLEDGMENT**

The authors would like to thank the anonymous reviewer for feedback regarding coercivity.

#### **REFERENCES**

- J.-P. Wang et al., "A pathway to enable exponential scaling for the beyond-CMOS era," in Proc. ACM/ESDA/IEEE Design Autom. Conf., 2017, Art. no. 16.

- [2] S. Manipatruni, D. E. Nikonov, R. Ramesh, H. Li, and I. A. Young. (2017). "Spin-orbit logic with magnetoelectric nodes: A scalable charge mediated nonvolatile spintronic logic." [Online]. Available: https://arxiv.org/abs/1512.05428v2

- [3] N. A. Spaldin and M. Fiebig, "The renaissance of magnetoelectric multiferroics," *Science*, vol. 309, no. 5733, pp. 391–392, 2005.

- [4] J. T. Heron *et al.*, "Deterministic switching of ferromagnetism at room temperature using an electric field," *Nature*, vol. 516, no. 7531, pp. 370–373, Dec. 2014.

- [5] X. He *et al.*, "Robust isothermal electric control of exchange bias at room temperature," *Nature Mater.*, vol. 9, pp. 579–585, Jun. 2010.

- [6] E. Saitoh et al., "Conversion of spin current into charge current at room temperature: Inverse spin-Hall effect," Appl. Phys. Lett., vol. 88, no. 18, p. 182 509–1–182 509–3, 2006.

- [7] J.-C. Rojas-Sánchez et al., "Spin-to-charge conversion using Rashba coupling at the interface between non-magnetic materials," *Nature Commun.*, vol. 4, Dec. 2013, Art. no. 2944.

- [8] Y. Shiomi et al., "Spin-electricity conversion induced by spin injection into topological insulators," Phys. Rev. Lett., vol. 113, no. 19, 2014, Art. no. 196601.

- [9] G. Radaelli et al., "Electric control of magnetism at the Fe/BaTiO<sub>3</sub> interface," *Nature Commun.*, vol. 5, Mar. 2014, Art. no. 3404.

- [10] Y.-H. Chu et al., "Electric-field control of local ferromagnetism using a magnetoelectric multiferroic," *Nature Mater.*, vol. 7, pp. 478–482, Apr. 2008.

- [11] B. Behin-Aein, D. Datta, S. Salahuddin, and S. Datta, "Proposal for an all-spin logic device with built-in memory," *Nature Nanotechnol.*, vol. 5, no. 4, pp. 266–270, Apr. 2010.

- [12] J. Hu, N. Haratipour, and S. J. Koester, "The effect of output-input isolation on the scaling and energy consumption of all-spin logic devices," *J. Appl. Phys.*, vol. 117, Apr. 2015, Art. no. 17B524.

- [13] Z. Liang and S. S. Sapatnekar, "Energy/delay tradeoffs in all-spin logic circuits," *IEEE J. Explor. Solid-State Computat. Devices Circuits*, vol. 2, pp. 10–19, Dec. 2016.

- [14] E.-K. Tan, J. Osman, and D. R. Tilley, "Theory of switching in bulk first-order ferroelectric materials," *Phys. Status Solidi B*, vol. 228, no. 3, pp. 765–776, 2001.

- [15] V. M. Edelstein, "Spin polarization of conduction electrons induced by electric current in two-dimensional asymmetric electron systems," *Solid State Commun.*, vol. 73, no. 3, pp. 233–235, 1990.

- [16] J.-C. Rojas-Sánchez et al., "Spin to charge conversion at room temperature by spin pumping into a new type of topological insulator: α-Sn films," Phys. Rev. Lett., vol. 116, no. 9, 2016, Art. no. 096602.

- [17] D. Ricinschi, C. Harnagea, C. Papusoi, L. Mitoseriu, V. Tura, and M. Okuyama, "Analysis of ferroelectric switching in finite media as a Landau-type phase transition," *J. Phys. Condens. Matter*, vol. 10, no. 2, pp. 477–492, 1998.

- [18] T. K. Song, "Landau-Khalatnikov simulations for ferroelectric switching in ferroelectric random access memory application," *J. Korean Phys. Soc.*, vol. 46, no. 1, pp. 5–9, 2005.

- [19] S. Sapatnekar, Timing. Boston, MA, USA: Kluwer, 2004.

- [20] A. R. Mellnik et al., "Spin-transfer torque generated by a topological insulator," *Nature*, vol. 511, pp. 449–451, Jul. 2014.

- [21] M. Zabihi, Z. Chowdhury, Z. Zhao, U. R. Karpuzcu, J. Wang, and S. Sapatnekar, "In-memory processing on the spintronic CRAM: From hardware design to application mapping," *IEEE Trans. Comput.*, 2018. [Online]. Available: https://ieeexplore.ieee.org/abstract/document/8416761

- [22] D. E. Nikonov, G. I. Bourianoff, and T. Ghani, "Proposal of a spin torque majority gate logic," *IEEE Electron Device Lett.*, vol. 32, no. 8, pp. 1128–1130, Aug. 2011.

- [23] M. G. Mankalale, Z. Liang, and S. S. Sapatnekar, "STEM: A scheme for two-phase evaluation of majority logic," *IEEE Trans. Nanotechnol.*, vol. 16, no. 4, pp. 606–615, Jul. 2017.

Authors' photographs and biographies not available at the time of publication.