# A General Method to Study Multiple Discontinuous Conduction Modes in DC–DC Converters With One Transistor and Its Application to the Versatile Buck–Boost Converter

Duberney Murillo-Yarce, Carlos Restrepo, Diego G. Lamar, Senior Member, IEEE, and Javier Sebastián, Senior Member, IEEE

Abstract—The discontinuous conduction mode (DCM) is usually studied in single-diode and single-inductor converters, where only one DCM exists. However, multiple DCMs can appear in multidiode and multi-inductor topologies and the methodology to identify and characterize these multiple modes is not evident. In this article, a general method to study multiple DCMs is presented. The first step of the method consists in finding out the number n, which is the number of diodes conducting current passing exclusively through inductors when the transistor turns OFF. For a given n value,  $2^n$  possible conduction modes are expected: 1 continuous mode and  $2^n-1$  DCMs. The second step is to create an n-dimensional space called "k-space." In the k-space, the converter operation describes a straight line when the load changes. This straight line called "converter trajectory" passes through different n-dimensional enclosures. Each one of these enclosures represents a different conduction mode. The third step is to determine the borders between conduction modes which are subspaces of (n-1) dimensions. This method must be followed for both control strategies (i.e., open- and closed-loop controls). The proposed method is applied to the versatile buck-boost converter. Experimental results verify the theoretical analysis for all the identified conduction modes.

Manuscript received 12 February 2022; revised 16 May 2022; accepted 26 June 2022. Date of publication 4 July 2022; date of current version 26 July 2022. This work was supported in part by the Agencia Nacional de Investigación y Desarrollo (ANID) under Grant ANID/FONDECYT/1191680, in part by the Millenium Institute on Green Ammonia as Energy Vector MIGA under Grant ANID/Millennium Science Initiative Program/ICN2021\_023, in part by SERC Chile under Grant ANID/FONDAP/15110019, in part by ANID/PFECHA/Doctorado-Nacional/2019-21191663, in part by the Ministerio de Ciencia, Innovación y Universidades de España under Research Projects MCI-20-PID2019-110483RB-I00 and MCI-21-PDC2021-121242-I00, in part by the Principado de Asturias Government under Project SV-PA-21-AYUD/2021/51931, and in part by the FEDER funding. Recommended for publication by Associate Editor D. Maksimovic. (Corresponding author: Carlos Restrepo.)

Duberney Murillo-Yarce is with the Engineering Systems Doctoral Program, Faculty of Engineering, Universidad de Talca, Curicó 3340000, Chile (e-mail: duberney.murillo@utalca.cl).

Carlos Restrepo is with the Department of Electrical Engineering, Faculty of Engineering, Universidad de Talca, Curicó 3340000, Chile (e-mail: crestrepo@utalca.cl).

Diego G. Lamar is with the Department of Electrical Engineering, Universidad de Oviedo, 33204 Gijón, Spain (e-mail: diegoglamar@ieee.org).

Javier Sebastián is with the Ingeniería Eléctrica, Electrónica, de Computadores y Sistemas, Universidad de Oviedo, 33204 Gijón, Spain (e-mail: se-bas@uniovi.es).

This article has supplementary material provided by the authors and color versions of one or more figures available at https://doi.org/10.1109/TPEL.2022.3187963.

Digital Object Identifier 10.1109/TPEL.2022.3187963

*Index Terms*—Conduction modes study, dc-dc converters, multidiode topologies, multiple discontinuous conduction modes (DCMs), versatile buck-boost (VBB) converter.

#### I. INTRODUCTION

It Is well known that the characteristics of a dc-dc converter strongly depend on its conduction mode [1]. In continuous conduction mode (CCM), classical dc-dc converters (buck, boost, or buck-boost converters) exhibit low open-loop output impedance. This means that, in this conduction mode, the output voltage remains theoretically constant when the load changes. The converter conversion ratio only depends on the converter duty cycle while the converter remains operating in this conduction mode, whatever the value of the switching frequency, the inductor inductance, and the load resistance.

On the other hand, when any of the classical dc–dc converters are operating in discontinuous conduction mode (DCM), they become a high open-loop output impedance converter, which means that the output voltage changes when the load changes. In this case, the converter conversion ratio depends not only on the converter duty cycle but also on the switching frequency, the inductor inductance, and the load resistance, as well. Therefore, closed-loop operation strongly depends on the operation mode: The actual value of the duty cycle changes slightly with the load variations if the converter is operating in CCM, but it changes markedly under the same circumstances if the converter is operating in DCM.

Although behavior with low open-loop output impedance is more desirable than with high open-loop output impedance in most applications, there are exceptions to this general rule. One example is the use of these converters for power factor correction (PFC) in single-phase ac-dc conversion [2]-[6]. In this case, the use of a high open-loop output impedance converter after a four-diode bridge rectifier allows a very simple control strategy to achieve sinusoidal [3]-[6] (or quasi-sinusoidal [2]) line current and output voltage control at the same time, thus carrying out the so-called voltage follower control.

The conduction mode also influences the converter losses and, therefore, the converter efficiency. Operation in DCM is prone to increase the conduction losses and the transistor turn-OFFlosses, whereas the transistor turn-ON losses decrease considerably due to the zero current switching of the converter diode [7]–[10]. Regarding the value and the size of the converter inductor, the design of a converter to operate in DCM over the full operation range leads to a lower value of this device, but its total size does not decrease similarly due to the increase in the inductor peak current [11]–[13].

Another important difference between the two conduction modes can be seen when analyzing the converter transfer function that relates the variations of output voltage and duty cycle [1]. Operation in CCM yields second-order transfer functions (even with a right half-plane zero in the case of the boost and buck-boost converters). By contrast, operation in DCM leads to simple first-order transfer functions in basic converters. Therefore, the knowledge of the conduction mode is important in determining the control transfer function of a specific converter and, consequently, the type of compensator that must be implemented in the control feedback-loop. Therefore, the study of the converter conduction mode is important for evaluating both its static and dynamic behaviors.

Many converters are usually designed to operate in CCM under heavy load conditions. However, DCM can be reached during light load conditions. If needed, this situation can be avoided by applying design criteria derived from the knowledge of the CCM-DCM borders. In this case, knowing these borders becomes of primary concern.

Due to the above-mentioned reasons, the analysis of the conduction modes must be performed whenever a rigorous study of a converter is required. The study of the conduction modes is addressed in power electronics books by the most well-known authors, and in application notes from the most significant converter manufacturers. Regarding converters on the market, some of them operate in DCM or on the border between both conduction modes [14]. For example, some PFC stages used in LED drivers rated between 50 and 150 W are based on a boost converter that operates in the above-mentioned border between conduction modes (sometimes called "critical mode"), thus achieving the highest efficiency possible for the current technology of low-cost semiconductors [15]. Another proof of the importance of the operation in DCM is the existence of commercial chips designed to control low-power converters in this conduction mode [16], [17].

A limited analysis of the conduction modes in multidiode topologies was addressed in [18], where a modified single-ended primary-inductor converter (SEPIC) was studied. In that work, a diode is added in series with the SEPIC input inductor, thus obtaining a topology with two diodes. This additional diode represents the effect of the bridge rectifier diodes placed at the input of the SEPIC converter when it is used in PFC applications. The inclusion of this diode avoids negative current circulating through the input inductor, clearly defining an additional DCM. The main contribution of [18] is the generalization of the averaged state—space method (proposed in [19]) to obtain small-signal model is derived for only one of the possible DCMs. The study of other possible DCMs is omitted, and, therefore, the

determination of the borders between conduction modes and the determination of the sequence of conduction modes when the load changes (either in open- or closed-loop operation) was not addressed.

The complexity of the analysis of the possible conduction modes in a given dc-dc converter depends on its number of inductors and diodes. If there are n diodes conducting inductive current when the converter transistor turns OFF, then 1 CCM and  $2^n - 1$  possible DCMs are expected. This article introduces a general method to determine the conduction modes of a given dc-dc converter, the borders between these modes, and the sequence of modes that it follows when its load changes. Afterwards, the proposed method is applied to the versatile buck-boost (VBB) converter. This converter can be implemented either in a bidirectional power-flow version (with four transistors) or in an unidirectional power-flow version (with two transistors and two diodes). In the unidirectional power-flow version, the converter can operate either like a boost (step-up) converter, with one transistor and only one diode switching each period, or like a buck (step-down) converter, with one transistor and two diodes switching each period. In this last case, the VBB presents three DCMs, which has not been identified so far.

This article is organized as follows. The description of the proposed methodology is presented in Section II, and a brief description of the VBB converter is shown in Section III. The possible conduction modes of the VBB converter in boost and buck modes are presented in Sections IV and V, respectively, while the features of all the conduction modes in buck operation mode are presented in Section VI. Experimental results in both open- and closed-loop operations are shown in Section VII. Finally, Section VIII concludes this article.

# II. GENERAL METHOD TO STUDY MULTIPLE DISCONTINUOUS CONDUCTION MODES IN DC-DC CONVERTERS

The method proposed in this article to analyze the conduction modes of a dc–dc converter is based on the steps analyzed below.

#### A. Finding Out the n value

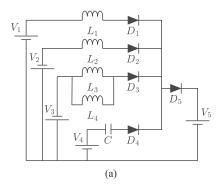

The determination of the number n is of primary concern in this study. This number is defined as the number of nonredundant diodes that are conducting current passing exclusively through inductors (one inductor or several inductors in parallel) when the transistor turns OFF. This number is calculated after eliminating redundant diodes in the aforementioned state. As an example to explain the determination of n, Fig. 1(a) shows a general equivalent circuit of a dc-dc converter when the transistor is OFF. Four branches with one diode appear in this figure. It is assumed that voltage sources or capacitors with no voltage ripple are connected at the end of each branch, including the common one [voltage sources  $V_1 - V_5$  in Fig. 1(a)], which is the normal situation in standard pulsewidth modulated (PWM) dc-dc converters. Some of the diodes and voltage sources could have the opposite polarity to the one shown in this figure. However, the voltage across any of the inductors when all the diodes are conducting must provoke the decreasing of the current passing through them, because the transistor OFF-state corresponds to the

Fig. 1. Examples of equivalent circuits corresponding to the transistor OFF-state in conventional PWM dc-dc converters. (a) Case with a redundant diode. (b) Case with no redundant diodes.

demagnetizing period for all the inductors in single-transistor PWM dc-dc converters. Thus, in the particular case of Fig. 1(a),  $V_5 - V_4 > 0$ ,  $V_5 + V_2 > 0$ , and  $V_5 + V_3 > 0$ . Moreover, some of the voltage sources could be short circuits. The first branch of the circuit shown in Fig. 1(a) contains diode  $D_1$ , which conducts the current passing through inductor  $L_1$ . Similarly, diode  $D_2$ exclusively conducts the current passing through inductor  $L_2$ . The next branch contains diode  $D_3$ , which conducts the current passing through inductors  $L_3$  and  $L_4$ . Diodes  $D_4$  and  $D_5$  are not placed in inductive branches. Thus,  $D_4$  only conducts the current passing through capacitor C and, therefore, must not be taken into account when computing number n. Finally, even in the case of a circuit without the aforementioned branch, diode  $D_5$  must not be taken into account when computing number n because it is redundant with the rest of diodes. As there are only three nonredundant diodes  $(D_1, D_2, \text{ and } D_3)$ conducting inductive currents when the transistor is OFF, then n=3. Another example is shown in Fig. 1(b). In this case, the branch made up of  $V_3$  and  $L_3$  does not have any diodes, which means that the current passing through it can flow in both directions. Due to this,  $D_3$  is not redundant and must be taken into account when computing number n and, therefore, n=3.

### B. Computing the Number of Conduction Modes

The number of conduction modes is directly determined by the number n. We can built an n-dimensional vector D = $(D_1, D_2, \dots, D_n)$  with the conduction state of each diode at the end of the switching period. It should be noted that only the diodes taken into account when computing n must be considered in vector D. As a diode that has stopped conducting remains OFF the rest of the switching period, the value of D characterizes the conduction state of the converter diodes and, therefore, it corresponds to a single conduction mode. As only two conduction states (ON and OFF) are possible for each diode, there are  $2^n$  possible values for the vector, and, therefore, there are  $2^n$ possible conduction modes. Let us consider the ON-state of each diode as logic level 1 and the OFF-state of the same diode as logic level 0. The conduction mode corresponding to all diodes in ON-state at the end of the switching period, i.e., D = (1, 1, ... 1), is the CCM. The remaining  $2^n - 1$  cases correspond to DCMs.

### C. Representing the Converter Trajectories in the k-Space

The evolution of the converter conduction modes is determined by the load changes in two different control situations: open-loop operation (i.e., at constant input voltage and duty cycle) and closed-loop operation (i.e., at constant input voltage and constant conversion ratio). In both cases, the succession of operating points is called "trajectory" in this article. Each point of a given trajectory will belong to a specific conduction mode. To determine this conduction mode, the proposed method uses the concept of "k-space," which is going to be presented in this section.

The next step of the proposed method is to define n conduction parameters  $k_x$ , as follows:

$$k_x = \frac{2L_x}{R_T T} \tag{1}$$

where  $1 \leqslant x \leqslant n$ ,  $R_L$  is the converter load, T is the switching period, and  $L_x$  is the inductance corresponding to the inductor (or the parallel connection of inductors) whose current cannot reverse due to diode  $D_x$ . The set of possible values of the n parameters  $k_x$  determine an n-dimensional space, called "k-space" in this article. In the k-space, each conduction mode is represented by an n-dimensional enclosure. The borders between two adjacent enclosures are subspaces of (n-1) dimensions. Two different types of n-dimensional enclosures can be defined in the k-space, one for the converter operating in open loop and the other for the converter operating in closed loop. In both control situations and for any value of the load  $R_L$ , the values of  $k_x$  are related to the following set of n-1 linear equations [obtained from (1)]:

$$(n-1) \text{ linear equations } \begin{cases} k_n &= \frac{L_n}{L_{n-1}} k_{n-1} \\ k_{n-1} &= \frac{L_{n-1}}{L_{n-2}} k_{n-2} \\ \vdots \\ k_2 &= \frac{L_2}{L_1} k_1 \end{cases}$$

(2)

Each one of these n-1 linear equations represent a hyperplane of n-1 dimensions in the k-space. The intersection of this equation set determines a straight line in the k-space. The changes of the load  $R_L$  cause a synchronous change of all the  $k_x$  values and, therefore, a change of operating point position on the straight line. Therefore, this straight line is the

above-mentioned converter trajectory that the converter follows when  $R_L$  changes. Whatever the dimension of the k-space is, the converter trajectory in the k-space is always a straight line. The converter trajectory passes through different n-dimensional enclosures and always passes through the origin (that corresponds to  $R_L \to \infty$ ). The slope of the trajectory in the k-space is defined by the inductances ratios,  $L_n/L_{n-1}, L_{n-1}/L_{n-2}, \ldots$ ,  $L_2/L_1$ , which are constant values for a given design. Changing these inductances ratios, the trajectory also changes, but the new trajectories thus obtained always pass through the origin. Once the converter has been designed, it has a given trajectory in the k-space. This trajectory is independent from the converter duty cycle and from the converter conversion ratio. However, the n-dimensional enclosures that the trajectory passes through depend on the converter control situation (either open loop or closed loop) and on the particular value of the duty cycle (in open-loop operation) or of the conversion ratio (in closed-loop operation). Once the converter inductors and the control situation have been selected, both the trajectory and the enclosures that the trajectory passes through in the k-space are completely defined. In these conditions, the position on the trajectory and, therefore, the conduction mode only depends on the value of  $R_L$ .

#### D. Computing the Borders Between Enclosures

The third step in this method is to determine the borders between the n-dimensional enclosures. For this purpose, we will start computing the converter conversion ratios corresponding to the different conduction modes, i.e., the converter conversion ratios inside the  $2^n$  different n-dimensional enclosures. Once all the conversion ratios have been computed, the border between two adjacent n-dimensional enclosures can be easily calculated by equaling the expressions of the converter conversion ratios corresponding to them. Sometimes, this border can be easily computed by equaling the average value of the current passing through an inductor and its zero-peak ripple value. The borders thus obtained are subspaces of (n-1) dimensions. This process can be extended to the common border between adjacent n-dimensional enclosures, equaling the expressions corresponding to the conversion ratios.

The process of obtaining the borders between the  $2^n$  n-dimensional enclosures must be carried out for the two converter control situations that have been mentioned, i.e., open- and closed-loop controls. Moreover, the borders between enclosures not only change with the control strategy but also with the duty cycle when the converter is operating in open loop and with the conversion ratio when it is operating in closed loop.

In summary, the selection of the converter inductors determine the converter trajectory in the k-space. This trajectory is independent from the converter duty cycle and conversion ratio, and, therefore, it is independent from the converter control strategy. It is also independent from the load, but it determines the point of the trajectory where the converter is operating. For a given duty cycle and conversion ratio, an operating point belongs to a specific conduction mode, which means that it is inside of a specific n-dimensional enclosure in the k-space. Once the converter trajectory and the borders between enclosures

$\begin{array}{c} {\rm TABLE\ I} \\ {\rm Conduction\ Modes\ for\ } n=2 \end{array}$

| Vector D |       | Conduction mode | Region name |

|----------|-------|-----------------|-------------|

| $D_1$    | $D_2$ |                 |             |

| 1        | 1     | CCM             | CCM         |

| 1        | 0     | DCM             | DCM1        |

| 0        | 1     | DCM             | DCM2        |

| 0        | 0     | DCM             | DCM3        |

for a given control strategy are known, the conduction mode corresponding to each possible value of the load is completely determined. Either the conversion ratio (open-loop) or the duty cycle (closed-loop) corresponding to this operating point can be easily computed by using the corresponding equations.

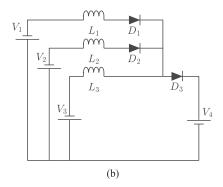

### E. Applying the Proposed Method to Low-Order Cases

Some examples of the study of the conduction modes using trajectories in the k-space are shown in Figs. 2 and 3. For n=1, which is the classic case, vector D only has two values, i.e., D=(1), which is the CCM, and D=(0), which is the unique DCM. Consequently, there is a single parameter k. The k-space is a straight line (see Fig. 2), where both conduction modes are located, separated by a point defined as border, as shown in Fig. 2. As parameter k is always positive, only the positive part of the straight line is considered. The conversion ratio in CCM will be called N and verifies

$$N = \left[\frac{V_o}{V_q}\right]_{\text{CCM}} = f_{\text{CCM}}(d_1) \tag{3}$$

where  $d_1$  is the transistor duty cycle. When the converter operates in the unique DCM, the conversion ratio will be called M and verifies

$$M = \left[\frac{V_o}{V_a}\right]_{\text{DCM}} = f_{\text{DCM}}(d_1, k) \tag{4}$$

where k is defined according to (1). The border between modes can be easily calculated equaling (3) and (4). The value of k thus obtained is the "critical" value of k and is called  $k_{\rm crit}$ . This value can be expressed either as a function of the duty cycle  $d_1$  [for open-loop control, Fig. 2(a)] or as a function of the conversion ratio M [for closed-loop control, Fig. 2(b)], as follows:

$$k_{\text{crit OL}} = f_{\text{crit OL}}(d_1)$$

(5)

$$k_{\text{crit CL}} = f_{\text{crit CL}}(M).$$

(6)

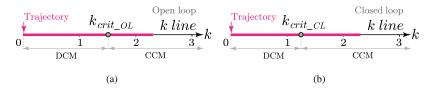

In the case n=2, vector D has four possible values, as shown in Table I. There are two types of k parameters,  $k_1$  and  $k_2$ , that define a plane, as shown in Fig. 3(a). As parameters  $k_1$  and  $k_2$  are always positive, only the positive part of the plane is considered. The converter trajectory is a straight line in the  $k_1k_2$  plane, as also shown in Fig. 3(a), where the inductance ratio is  $L_2/L_1=1.5$ . The conversion ratio in CCM will be expressed as in (3). On the other hand, the conversion ratios in the different DCMs can be expressed in the following general form:

$$M_x = \left[\frac{V_o}{V_g}\right]_{\text{DCM}_x} = f_{\text{DCM}_x}(d_1, k_1, k_2) \tag{7}$$

Fig. 2. k-space when n=1. (a) Trajectory in the k line when the converter operates in open loop with  $k_{\text{crit\_OL}}=1.5$ . (b) Trajectory in the k line when the converter operates in closed loop with  $k_{\text{crit\_CL}}=1.25$ .

Fig. 3. k-space when n = 2. (a) Trajectory in the  $k_1k_2$  plane when  $L_2/L_1 = 1.5$ . (b) Map of regions when the converter operates in open loop at a given duty cycle. (c) Map of regions when the converter operates in open loop at a duty cycle different from the previous one. (d) Map of regions when the converter operates in closed loop at a given conversion ratio.

where  $1 \leqslant x \leqslant 3$ . The 2-D enclosures corresponding to any of the four conduction modes are "regions" of the plane. Each point in the  $k_1k_2$  plane belongs to one of the four possible regions, whose names are given in Table I. However, the region where a given point is placed depends on the control strategy used and either on the duty cycle (in open-loop control) or on the conversion ratio (in closed-loop control). The borders between adjacent regions are, in general, curves, although it could be points in some specific cases. The equations of these curves can be obtained by equaling conversion ratio equations corresponding to adjacent modes. For example, if DCM2 and DCM3 are adjacent [as shown in Fig. 3(b)], the border curve will be obtained equaling the respective conversion ratios given by (7). The result can be expressed in open and closed loop, as follows:

$$k_{2 \text{ crit } 2-3 \text{ OL}} = f_{\text{crit } 2-3 \text{ OL}}(d_1, k_1)$$

(8)

$$k_2 \text{ crit } 2-3 \text{ CL} = f_{\text{crit } 2-3 \text{ CL}}(M, k_1).$$

(9)

The curves given in (8) and (9) determine the border between adjacent Modes DCM2 and DCM3 in the  $k_1k_2$  plane for both control situations. As mentioned before, this border can be sometimes easily computed by equaling the average value of the current passing through an inductor and its zero peak ripple value. The curves given in (8) and (9) appear in Fig. 3(b) and (c) for open-loop operation at different duty cycle, and in Fig. 3(d) for closed-loop operation at a given conversion ratio. We can call these figures "maps." The converter trajectory in the  $k_1k_2$ plane is only determined by the value of the ratio  $L_2/L_1$ , but the regions the trajectory passes through depend on the map of regions. In turn, the map of regions depends on the control strategy and on the value of the control parameter that remains constant for each type of control (either the duty cycle or the conversion ratio). If the process of equaling conversion ratios given by either (7) or (3) and (7) does not give a solution, then the regions corresponding to these conversion ratios will not be adjacent in the map of regions. If this process gives constant

values for  $k_2$  and  $k_1$ , then the border between regions is a point. Moreover, the border between three or more adjacent regions is always a point, whose value can be obtained by equaling the respective conversion ratios given by either (7) or (3) and (7). This is the situation shown in Fig. 3(b)–(d), where  $P_c$  is that common point for the four regions in the three maps represented in these figures.

As Fig. 3(b)–(d) shows, a given trajectory can pass through different regions, depending on the map that the control strategy determines. Looking at these figures, three classes of trajectories can be identified. The first class [see Fig. 3(b)] corresponds to the sequence of vector D values (i.e., the sequence of conduction states) given by (1,1), (1,0). The sequence of vector D values corresponding to the second class [see Fig. 3(c)] is (1,1), (0,1), (0,0), (1,0). Finally, the third class [see Fig. 3(d)] corresponds to the sequence of vector D values given by (1,1), (0,1), (0,0).

In the case n=3, vector D has eight possible values. There are three types of k parameters,  $k_1$ ,  $k_2$ , and  $k_3$ , that define a volume. The converter trajectory is a straight line in the  $k_1k_2k_3$  volume. As parameters  $k_1$ ,  $k_2$ , and  $k_3$  are always positive, only the positive part of the volume is considered. The conversion ratio in CCM will be expressed as in (3). On the other hand, the conversion ratios in DCM can be expressed in the following general form:

$$M_x = \left[\frac{V_o}{V_g}\right]_{\text{DCM}_x} = f_{\text{DCM}_x}(d_1, k_1, k_2, k_3)$$

(10)

where  $1 \le x \le 7$ . The 3-D enclosures corresponding to any of the eight conduction modes are "bodies" of the volume. Each point in the  $k_1k_2k_3$  volume belongs to one of the eight possible bodies. However, the body where a given point is placed depends on the control strategy used and on the value of the control parameter that remains constant for each type of control. The border between two adjacent bodies is a surface, whereas the border between three adjacent bodies is a curve, both in the  $k_1k_2k_3$  volume. The equations of the surfaces can be obtained by equaling two conversion ratio equations corresponding to adjacent modes. For example, if DCM5 and DCM6 are adjacent, the border surface will be obtained by equaling the respective conversion ratios given by (10). If this process does not give a solution, then the bodies corresponding to these conduction modes will not be adjacent in the  $k_1k_2k_3$  volume. Otherwise, the result can be expressed in open and closed loop, as follows:

$$k_{3\_crit\_5-6\_OL} = f_{crit\_5-6\_OL}(d_1, k_1, k_2)$$

(11)

$$k_{3 \text{ crit } 5-6 \text{ CL}} = f_{\text{crit } 5-6 \text{ CL}}(M, k_1, k_2).$$

(12)

The surfaces given by (11) and (12) determine the border between adjacent bodies DCM5 and DCM6 in the  $k_1k_2k_3$  volume for both control situations. If body DCM4 is adjacent to bodies DCM5 and DCM6, a new pair of equations can be obtained by equaling the respective conversion ratios given by (10), now corresponding to DCM4 and either DCM5 or DCM6. For example, equaling the conversion ratios corresponding to DCM4 and DCM5, we obtain

$$k_{3\_crit\_4-5\_OL} = f_{crit\_4-5\_OL}(d_1, k_1, k_2)$$

(13)

$$k_{3\text{\_crit\_}4-5\text{\_CL}} = f_{\text{crit\_}4-5\text{\_CL}}(M, k_1, k_2).$$

(14)

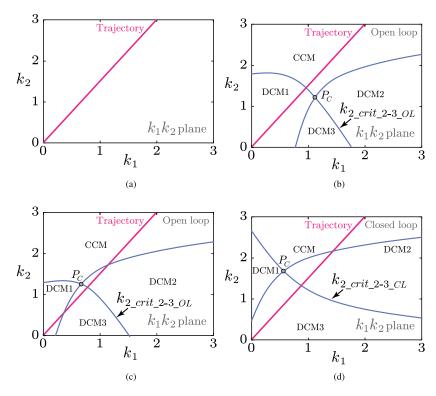

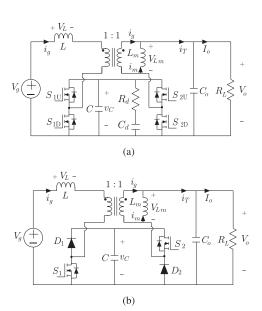

Fig. 4. Versions of the versatile buck–boost (VBB) converter. (a) Bidirectional power flow. (b) Unidirectional power flow.

The set of (11) and (13) determines a curve in the  $k_1k_2k_3$  volume. This curve is the border between adjacent bodies DCM4, DCM5, and DCM6 in the case of open-loop operation and at a given  $d_1$  value. Similarly, the set of (12) and (14) determines the border curve between adjacent bodies DCM4, DCM5, and DCM6 in the case of closed-loop operation at a given M value. Obviously, this process can also be extended to the case of four or more adjacent bodies, increasing the number of equations used. The result will be a point in the  $k_1k_2k_3$  volume. Just on the other hand, if the set of equations obtained equaling several of the conversion ratios given by either (10) or (3) and (10) does not have a solution, then the bodies are not adjacent.

### III. REVIEW OF THE VBB CONVERTER

The VBB converter was first introduced in [20]. This converter exhibits a noninverting step-up and step-down characteristic and nonpulsating currents in the input and output ports, making it useful for many power processing applications. It is composed of a buck-boost cell, a pair of coupled inductors, an intermediate capacitor, and a damping network, as shown in Fig. 4(a). The damping network and the coupled inductors solve the drawback of zeros in the right half-plane when the converter operates in boost mode. This feature increases the converter bandwidth and makes the controller design easier. The converter can operate either as a boost converter with an output filter or as a buck converter with an input filter, with lower voltage stress in the switches compared to other buck-boost topologies. This converter also exhibits some other interesting features. Thus, it can control either the input or output current with low ripple values [see Fig. 4(a)]. Moreover, it is capable of rapidly and seamlessly interchanging the port whose current is being controlled [21]. The effects of the dead zone in the transition between buck and boost operating modes can be mitigated using the method proposed in [22]. In addition, the adaptability of the VBB converter to many situations was successfully verified when it was used as

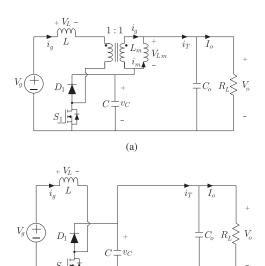

Fig. 5. Boost mode operation of the circuit shown in Fig. 4(b). (a) Circuit obtained when switch  $S_2$  is permanently in on-state. (b) Equivalent circuit when the voltage ripple across capacitor C is negligible.

(b)

a part of a fuel-cell hybrid power system [23]–[25]. In this case, the VBB operation was tested in three different configurations and with different control objectives.

The VBB converter can be implemented in a bidirectional power flow version [see Fig. 4(a)], but also in a unidirectional power flow version, when some of the transistors are replaced with diodes, as shown in Fig. 4(b). This version of the VBB converter has been chosen for the analysis of conduction modes presented in this article because it has two diodes and, therefore, multiple DCMs are possible. For the analysis carried out in the article, the damping network has not been taken into account, since it does not affect the converter operation in steady state.

# IV. CONDUCTION MODES OF THE VBB CONVERTER IN BOOST OPERATION MODE

The conduction modes of the VBB converter depend strongly on the converter operation mode (either buck or boost). This section makes a detailed analysis of the conduction modes appearing when the converter operates in boost mode. In this mode, the transistor  $S_2$  in Fig. 4(b) is permanently ON, which forces the diode  $D_2$  to be permanently blocking. Under these conditions, the circuit in Fig. 4(b) reduces to the one given in Fig. 5(a). From this equivalent circuit, one obtains

$$v_{L_m} = v_o - v_c. (15)$$

The capacitor values C and  $C_o$  are conveniently chosen to ensure no appreciable ripple; then, voltage  $v_{L_m}$  must be a constant value. This constant value must be zero because the average voltage across any inductor is always zero in a steady state. Therefore, in steady state, the circuit in Fig. 5(a) becomes the one given in Fig. 5(b), where short circuits have replaced the magnetizing inductance  $L_m$  and the ideal transformer. This latter circuit corresponds to a conventional boost converter but

Fig. 6. Circuit obtained when switch  $S_1$  in Fig. 4(b) is permanently in OFF-state (buck mode operation).

with two parallel capacitors at its output. It is important to note that in this equivalent circuit, there is only one diode (diode  $D_1$ ), so that only two conduction modes are expected.

- 1) CCM: Diode  $D_1$  always conducts current when transistor  $S_1$  does not conduct.

- 2) DCM: Diode  $D_1$  does not continuously conduct current when transistor  $S_1$  does not conduct.

This situation is the same as the one of a conventional boost converter; so the conduction mode will depend on the dimensionless parameter k, defined as in (1)

$$k = \frac{2L}{R_L T}. (16)$$

The border between the CCM and DCM is established by comparing k with  $k_{\rm crit}$ . The value of  $k_{\rm crit}$  for the boost converter is

$$k_{\text{crit}} = d_1 (1 - d_1)^2.$$

(17)

Therefore, the converter works in CCM if  $k > k_{\rm crit}$ , in DCM if  $k < k_{\rm crit}$ , and on the border between the two modes (CCM and DCM) if  $k = k_{\rm crit}$ .

# V. CONDUCTION MODES OF THE VBB CONVERTER IN BUCK OPERATION MODE

### A. General Considerations

In buck mode operation, the transistor  $S_1$  in Fig. 4(b) is permanently blocking; so the circuit from Fig. 4(b) becomes the circuit in Fig. 6, where only transistor  $S_2$  is working in switching mode. During the OFF-state of transistor  $S_2$ , two branches conducting inductive current can be easily identified. Therefore, n=2 in buck operation mode, and, therefore, four conduction modes are expected. As will be commented in another section, a subdivision of the CCM may even be considered.

In steady state, the average values of the currents  $i_g$ ,  $i_m$ , and  $i_T$  are defined as  $I_g$ ,  $I_m$ , and  $I_T$ , respectively. Verifying the steady-state converter power balance, we obtain

$$I_q = I_T M (18)$$

$$I_m = I_T(1 - M) \tag{19}$$

$$I_T = \frac{v_o}{R_L} \tag{20}$$

where M is the converter conversion ratio defined as

$$M = \frac{v_o}{v_g}. (21)$$

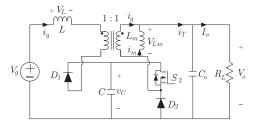

Fig. 7. Transformations of the circuit from Fig. 6 are valid only in conduction modes in which diode  $D_1$  always conducts. (a) Circuit obtained considering  $V_C = V_g$ . (b) Redrawing the previous circuit, moving inductor L to the transformer secondary side.

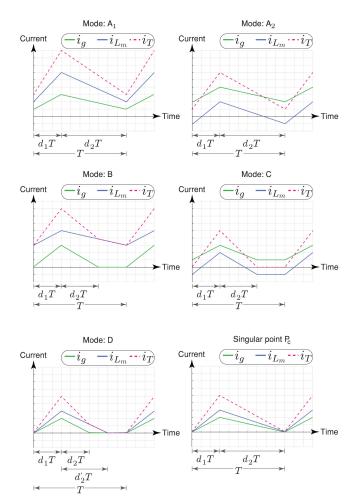

Fig. 8. Main waveforms in each conduction mode (A1, A2, B, C, and D) and the operation at the singular point  $P_c$ .

On the other hand, the conduction of  $S_2$  produces an increase in the inductor current  $i_g$  ( $\Delta i_g$ ). This increase can be easily calculated by applying Faraday's law to the circuit of Fig. 6 and considering that  $D_1$  conducts while  $S_2$  conducts, leading to

$$\Delta i_g = \frac{v_g - v_o}{L} d_1 T. \tag{22}$$

Equations (18)–(22) are valid in any case of buck mode operation of the VBB converter, regardless of the conduction state of diodes  $D_1$  and  $D_2$  during the OFF-state of transistor  $S_2$ . In conduction modes in which diode  $D_1$  conducts during the OFF-state of transistor  $S_2$ , the circuit in Fig. 6 can be notably simplified, as explained in the following subsection.

# B. Simplifications in Operation Modes in Which $D_1$ Does Not Stop the Current Conduction

As mentioned before, diodes conduct  $D_1$  and  $D_2$  are placed in inductive branches during the OFF-state of transistor  $S_2$ , which means that both diodes are conducting current passing through an inductor (the case of diode  $D_1$  and inductor L) or the sum of the currents circulating through two inductors (the case of diode  $D_2$  and inductors L and  $L_m$ ). In the case of current  $i_g$ , if the following condition is verified:

$$\Delta i_q < 2 I_q \tag{23}$$

the current through diode  $D_1$  will not reach zero, and its conduction will not be interrupted during the transistor OFF-state. If this condition is not met, it will produce a condition that will generate a specific conduction mode.

Unlike  $D_2$ ,  $D_1$  conducts during the conduction interval of  $S_2$ . If it also conducts the entire blocking interval of  $S_2$ , then it always conducts so that it can be replaced by a short circuit in Fig. 6. Under these conditions

$$v_L + v_{L_m} = V_g - V_c. (24)$$

Taking into account that  $V_g$  and  $V_c$  are constant voltages in steady state and that the mean values of  $v_L$  and  $v_{L_m}$  have to be zero under the same conditions, it follows that

$$V_c = V_q. (25)$$

Therefore, the circuit from Fig. 6 can now be redrawn as shown in Fig. 7(a). Finally, moving the inductor L to the secondary side of the ideal transformer with a 1:1 ratio gives the circuit in Fig. 7(b). This equivalent circuit is especially useful for performing calculations in conduction modes in which diode  $D_1$  always conducts. Thus, under these conditions, it can be stated that the  $D_2$  conduction during the blocking interval of  $S_2$  will not be interrupted if the following condition is verified:

$$\Delta I_T < 2 I_T \tag{26}$$

where the  $\Delta I_T$  value can be calculated by applying Faraday's law during the conduction interval of  $S_2$ , resulting in

$$\Delta I_T = \frac{V_g - V_o}{L_{\rm eq}} d_1 T \tag{27}$$

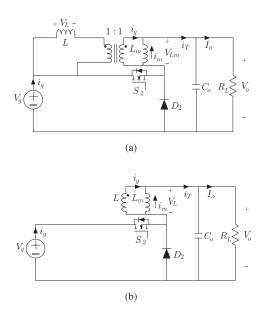

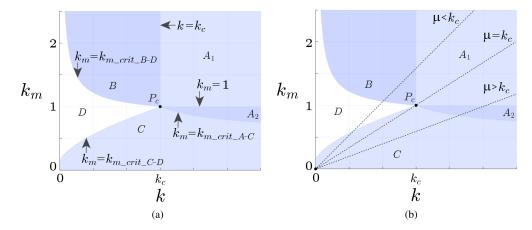

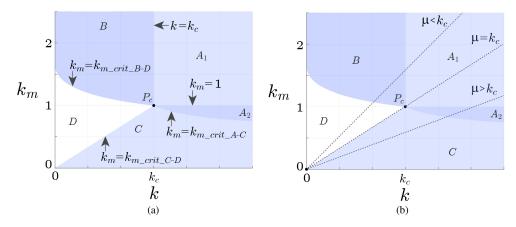

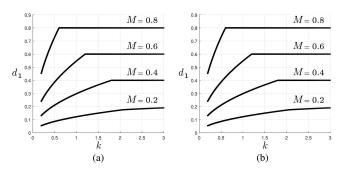

Fig. 9. (a) Map of conduction regions corresponding to operate at constant  $d_1$  (open loop). The value of  $k_c$ , and therefore the abscissa of the singular point  $P_c$ , changes in each map. (b) Possible open-loop trajectories.

Fig. 10. (a) Map of conduction regions corresponding to operate at constant M (closed loop). The value of  $k_c$ , and therefore the abscissa of the singular point  $P_c$ , changes in each map. (b) Possible open-loop trajectories.

where  $L_{\rm eq}$  is the equivalent inductor of the parallel between L and  $L_m$ . This equivalent inductor can be calculated as

$$L_{\rm eq} = \frac{L L_m}{L + L_m}. (28)$$

### C. VBB Converter Conduction Mode Waveforms

This subsection examines the different conduction modes that arise from analyzing the four possible operation alternatives of diodes  $D_1$  and  $D_2$  during the blocking interval of  $S_2$ .

1) Mode A: This is the CCM. In this mode,  $D_1$  and  $D_2$  conduct while  $S_2$  is blocking the current flow, i.e., vector D verifies D = (1,1). As long as  $D_1$  is conducting, the considerations derived from the previous subsection are valid. Inequalities (23) and (26) define this operation mode. However, the condition expressed by (26) can be satisfied in two different ways:

$$\Delta i_m < 2I_m \tag{29}$$

$$\Delta i_m > 2I_m. \tag{30}$$

Verification of inequalities (23), (26), and (29) produces a submode, called Mode A1, while verification of inequalities (23), (26), and (30) produces another submodule, called Mode A2. The waveforms corresponding to these situations are shown in Fig. 8 (see Modes A1 and A2).

2) Mode B: This is one of the DCMs. The waveforms for this mode are shown in Fig. 8 (see Mode B). In this mode,  $D_1$  does not always conduct while  $S_2$  is blocking and  $D_2$  is conducting, i.e., vector D verifies D = (0, 1). In this case, inequality (29) is satisfied together with

$$\Delta i_q > 2 I_q. \tag{31}$$

3) Mode C: This is another DCM. In this mode,  $D_1$  always conducts while  $D_2$  does not always conduct when  $S_2$  is blocking, i.e., vector D verifies D = (1,0). The waveforms for this mode are shown in Fig. 8 (see Mode C), and this mode is defined by inequality (23) together with

$$\Delta i_T > 2 I_T \tag{32}$$

with (25), (27), and (28) being valid since this is a case in which  $D_1$  always conducts.

4) Mode D: This is the last DCM. In this mode, there is an interval in which neither  $S_2$ , nor  $D_1$ , nor  $D_2$  conduct, as shown

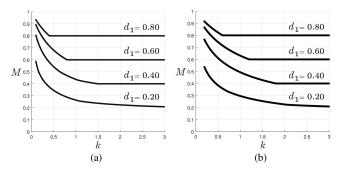

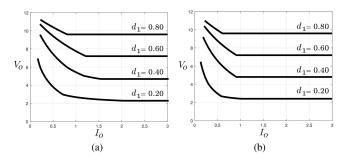

Fig. 11. Family of characteristic curves of the converter operation in open loop with constant duty cycles. (a)  $\mu = 1$ . (b)  $\mu = 2$ .

Fig. 12. Example of the family of characteristic curves  $V_o$  vs.  $I_o$  in open-loop control. In this case,  $L=23.7~\mu\text{H},~T=10~\mu\text{s},$  and  $V_g=12~\text{V}.$  (a)  $\mu=1.$  (b)  $\mu=2.$

Fig. 13. Family of characteristic curves of the converter operation in closed loop with constant conversion ratios. (a)  $\mu=1$ . (b)  $\mu=2$ .

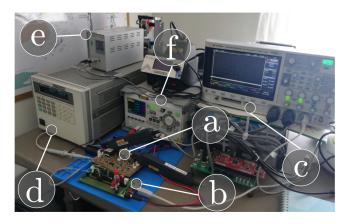

Fig. 14. Experimental configuration. (a) VBB converter. (b) Digital signal controller. (c) Oscilloscope (Keysight MSOX-2014 A). (d) DC electronic load. (e) Power supply for current probe. (f) Input dc power supply.

in Fig. 8 (see Mode D). Therefore, vector D verifies D = (0,0) in this mode. The inequalities that define it are (30) and (31).

## D. Conversion Ratios in the Different Modes

1) Mode A: In both A1 and A2 submodes, diode  $D_1$  always conducts; so the circuit in Fig. 7(b) is used to analyze this mode. As it is a conventional buck converter and when (26) is verified, the following equation is satisfied:

$$M = d_1. (33)$$

2) *Mode B:* Examining the circuit in Fig. 6 and applying Faraday's law during the decreasing interval of  $i_q$  produces

$$\Delta i_g = \frac{V_o + V_c - V_g}{L} \, d_2 \, T. \tag{34}$$

From (22) and (34), it can be seen that

$$d_2 = \frac{V_g - V_o}{V_o + V_c - V_g} d_1. {35}$$

The volt-second balance in  $L_m$  (see Fig. 6) leads to

$$V_o = V_c d_1. (36)$$

Averaging the  $i_g$  value in Fig. 8 (see Mode B) and using (22) and (34)–(36),  $I_q$  can be calculated as

$$I_g = \frac{(V_g - V_o)V_o}{2L(V_o - (V_q - V_o)d_1)} d_1^2 T.$$

(37)

Performing a power balance between input and output in the converter, and using the definitions of k and M in (16) and (21), the following relation is derived:

$$k = \frac{1 - M}{M(M - (1 - M)d_1)} d_1^2 \tag{38}$$

where M can be calculated as

$$M = \frac{\left(1 - \frac{d_1}{k}\right) + \sqrt{\left(\frac{d_1}{k} + 1\right)^2 + \frac{4}{k}}}{2(d_1 + 1)} d_1.$$

(39)

*3) Mode C:* Similar to Mode A, the circuit from Fig. 7(b) is used to analyze this mode. Its behavior is as a conventional buck converter working in DCM and created with an equivalent inductor defined in (28). Therefore, the conversion ratio value will be

$$M = \frac{2}{1 + \sqrt{1 + \frac{4 k k_m}{(k + k_m) d_1^2}}} \tag{40}$$

where  $k_m$  is calculated as

$$k_m = \frac{2L_m}{R_L T}. (41)$$

4) Mode D: Equations (34) and (35) remain valid in this mode. From these equations, it is easy to obtain the  $I_g$  value [note that (36) and (37) are not valid in this mode] as

$$I_g = \frac{(V_g - V_o)V_c}{2L(V_o - V_q + V_c)} d_1^2 T.$$

(42)

The  $V_c$  value can be calculated using (18), (20), (21), and (42), obtaining the expression

$$V_c = \frac{(1-M)M}{M^2 - \frac{d_1^2}{k}(1-M)} V_o.$$

(43)

On the other hand, the increase in  $i_m$  in this mode can be calculated both in the conduction interval of  $S_2$  and  $D_2$ , producing

$$\Delta i_m = \frac{V_c - V_o}{L_m} d_1 T \tag{44}$$

$$\Delta i_m = \frac{V_o}{L_m} d_2' T. \tag{45}$$

From these two equations, the  $I_m$  value is obtained

$$I_m = \frac{(V_c - V_o)V_c}{2 L_m V_o} d_1^2 T.$$

(46)

Using (19)–(21), (43), and (46), the following expression is finally obtained to determine the conversion ratio M in Mode D:

$$\frac{d_1^2 M}{k_m} \left( M - 2 M^2 + \frac{d_1^2 (1 - M)}{k} \right) = \left( M^2 - \frac{d_1^2 (1 - M)}{k} \right)^2. \tag{47}$$

# VI. DETERMINING THE MAPS OF CONDUCTION REGIONS IN THE $kk_m$ Plane for the VBB Converter Operating in Buck Mode

The next step in this study is to obtain the maps of conduction regions in the  $kk_m$  plane. It should be noted that parameters k and  $k_m$  are always positive, and, therefore, only the positive part of the plane must be considered. As mentioned before, these maps can be structured in two different ways.

- 1) Keeping  $d_1$  constant in the map. These maps correspond to operating the converter at a constant duty cycle by letting the conversion ratio change as the load changes. In other words, it corresponds to the converter in open-loop control. There will be one map for each  $d_1$  value.

- 2) Keeping M constant in the map. The curves correspond to operate the converter at a constant conversion ratio by letting a feedback system change the  $d_1$  value. In other words, it corresponds to the converter in closed-loop control. There will be one map for each M value.

# A. Open-Loop Control Conduction Maps

1) Mode A Region: This region can be subdivided into Mode A1 Region, in which the inequality (29) is verified, and Mode A2 Region, in which the inequality (30) is satisfied. The value of  $\Delta i_m$  can be calculated by applying Faraday's law to the circuit in Fig. 7(b) during the conduction interval of  $S_2$  yielding

$$\Delta i_m = \frac{V_g - V_o}{L_m} d_1 T. \tag{48}$$

Substituting (48) in (29) and using (16), (19), (20), and (33), the conditions for operation in Mode A1 can be determined as

$$k_m > k_{m \text{ crit } A1-A2} = 1.$$

(49)

For the case that  $k_m < k_{m\_crit\_A1-A2}$ , the converter operates in Mode A2. Therefore, the border between regions corresponding to Modes A1 and A2 is defined by the equality in (49). Furthermore, in the regions corresponding to Modes A1 and A2, the inequalities (23) and (26) are satisfied. The inequalities (23) and (26) are transformed into (50) and (51) using (16), (18), (20), (21), (27), and (28), as follows:

$$k > k_c = \frac{1 - d_1}{d_1} \tag{50}$$

$$k_m > k_{m\_crit\_A-C} = \frac{(1-d_1) k}{k - (1-d_1)}.$$

(51)

Since the opposite inequality to (23) is (31) and this corresponds to Mode B region, then the inequality in (50) defines operation in Mode A region in the vicinity of Mode B region. The border between the regions corresponding to Modes A and B is determined by the inequality in (50). Similarly, since the opposite inequality to (26) is (32), and this corresponds to Mode C region, then the inequality in (51) defines operation in Mode A region in the vicinity of Mode C region. The border between these regions is determined by the inequality in (51).

2) Mode B Region: In addition to the border already defined with Mode A region, Mode B region has a border with Mode D region. This border is defined by inequality (29) and by the conduction of diode  $D_2$ . The  $\Delta i_m$  value can now be calculated by applying Faraday's law to  $L_m$  in the circuit of Fig. 6 during the conduction interval of  $S_2$ , resulting in (44). The inequality (29) becomes the inequality (52), considering that (36) is satisfied in Mode B and using (16), (19)–(21), (39), and (41)

$$k_m > k_{m\_crit\_B-D} = \frac{2 (1 - d_1^2) k}{2k + d_1(k + d_1) - d_1 \sqrt{(k + d_1)^2 + 4 k}}.$$

(52)

The border between the regions corresponding to Modes B and D is defined by the equality in (52).

3) Mode C Region: In addition to the already-defined border with Mode A region (51), Mode C region has a border with Mode D region. This border is determined by inequality (23) and by the fact that the current  $i_m$  is negative at the beginning of the switching period. In the case that  $i_m$  was zero at the beginning of the switching period, as in Mode D, then the mean value of  $i_m$  could be easily calculated from the circuit in Fig. 7(b) using (25), (35), and (48). The final result is

$$I_{m\_{crit\_C-D}} = \frac{V_g - V_o}{2 L_m V_o} V_g d_1^2 T.$$

(53)

When starting  $i_m$  at a negative value, the following should be checked:

$$I_m < I_{m \text{ crit } C-D}. \tag{54}$$

Considering (19)–(21), (40), and (16 7), inequality (54) becomes

$$k_m^3 < d_1^2 (k_m + k)^2. (55)$$

Using Cardano's formula, this inequality becomes

$$k_m < k_{m\_crit\_C-D} = A(k) + B(k) + \frac{d_1^2}{3}$$

(56)

with

$$A(k) = \sqrt[3]{\frac{d_1^6}{27} + \frac{d_1^4}{3}k + \frac{d_1^2}{2}k^2 + d_1^2k\sqrt{\frac{d_1^2}{27}k + \frac{k^2}{4}}}$$

(57)

$$B(k) = \sqrt[3]{\frac{d_1^6}{27} + \frac{d_1^4}{3}k + \frac{d_1^2}{2}k^2 - d_1^2k\sqrt{\frac{d_1^2}{27}k + \frac{k^2}{4}}}.$$

(58)

The border between regions corresponding to Modes C and D is defined by the equality in (56).

- 4) Mode D Region: This region has the already-defined borders with regions corresponding to Modes B and C.

- 5) Singular Point  $P_c$ : All of the regions converge in one operation point whose waveforms are shown in Fig. 8 (see singular point  $P_c$ ). In the situation described in this figure, the following are satisfied:

$$\Delta i_q = 2 I_q \tag{59}$$

$$\Delta i_m = 2 I_m. \tag{60}$$

From these equations and taking into account (18)–(22), (33), and (48) yields:

$$k = k_c = \frac{1 - d_1}{d_1} \tag{61}$$

$$k_m = k_{m\_{crit\_}A1-A2} = 1.$$

(62)

Therefore, the point defined by  $P_c = (k_c, 1)$  is the point of convergence of all the regions and, therefore, of all the operation modes.

6) Trajectories in the Conduction Maps: As previously mentioned, the converter trajectories in the  $kk_m$  plane are straight lines that always pass through the origin. The slope of these trajectories only depend on the converter inductors ratio. Thus, if the dimensionless parameter  $\mu$  is defined as

$$\mu = \frac{L}{L_{m}} = \frac{k}{k_{m}} \tag{63}$$

then the trajectory slope is  $1/\mu$ . When the  $R_L$  value increases or the switching frequency decreases (lower values of k and  $k_m$  in both cases), the operation point approaches the origin. Otherwise, the operation point moves away from the origin.

Three classes of trajectories can be defined in the map of regions, as shown in Fig. 9(b).

1) Class I ( $\mu < k_c$ ): The trajectory that a converter designed to work at full load in Mode A would follow when increasing the  $R_L$  value would be

Region A1  $\rightarrow$  Region B  $\rightarrow$  Region D  $\rightarrow$  Region C.

2) Class II ( $\mu > k_c$ ): The trajectory, under the same conditions as in the previous case, would be

Region A1

$$\rightarrow$$

Region A2  $\rightarrow$  Region C.

3) Singular class  $\mu=k_c$ : This trajectory, with only theoretical interest, would have the following trajectory:

Region A1

$$\rightarrow$$

Region C.

# B. Closed-Loop Control Conduction Maps

The inequalities (49)–(52) and (56) delimit the open-loop working modes. In the process of obtaining them, some variables from various mathematical expressions have been eliminated in the initial analysis (including M), producing mathematical expressions in the form  $k_m = f_1(k, d_1)$ . Similarly, the starting equations can be manipulated so that  $d_1$  is eliminated instead of M, giving mathematical expressions in the form  $k_m = f_2(k, M)$ . Thus, the following borders have been obtained.

1) Mode A Region: The border between the regions corresponding to Modes A1 and A2 is still defined by inequality (49). The borders with the regions corresponding to Mode B and Mode C become

$$k > k_c = \frac{1 - M}{M} \tag{64}$$

$$k_m > k_{m\_crit\_A-C} = \frac{(1-M) k}{k - (1-M)}.$$

(65)

2) *Mode B Region:* Besides the border with Mode A region defined by (64), this mode has the following border with Mode D region:

$$k_m > k_{m\_crit\_B-D}$$

$$= \frac{(2+Mk)(1-M)-M\sqrt{(M-1)^2 k^2 + 4k(1-M)}}{2(1-M)^2}.$$

(66)

3) Mode C Region: In addition to the already-defined border with Mode A region (65), its border with Mode D region is

$$k_m < k_{m\_crit\_C-D} = \frac{M}{1 - M} k.$$

(67)

- *4) Mode D Region:* This region has the already-defined borders with regions corresponding to Modes B and C.

- 5) Singular Point  $P_c$ : Its coordinates in the  $kk_m$  plane are defined by (62) and by the equality in (64).

- 6) Trajectories in the Conduction Maps: Fig. 10(a) shows a conduction map for closed-loop control. As already mentioned, there is a specific plane for each M value. The classes of possible trajectories are shown in Fig. 10(b). These classes of trajectories are as follows.

- 1) Class I ( $\mu < k_c$ ):

Region A1

$$\rightarrow$$

Region B  $\rightarrow$  Region D.

2) Class II  $(\mu > k_c)$ :

Region A1

$$\rightarrow$$

Region A2  $\rightarrow$  Region C.

3) Singular Class  $\mu=k_c$ : which is a trajectory with only theoretical interest:

Region A1

$$\rightarrow$$

C  $-$  D border.

## C. Characteristic Curves

Once the value of  $\mu$  has been selected (and, therefore, the converter trajectory) in a given design, a set of curves that characterize the converter operation in buck mode in both open-

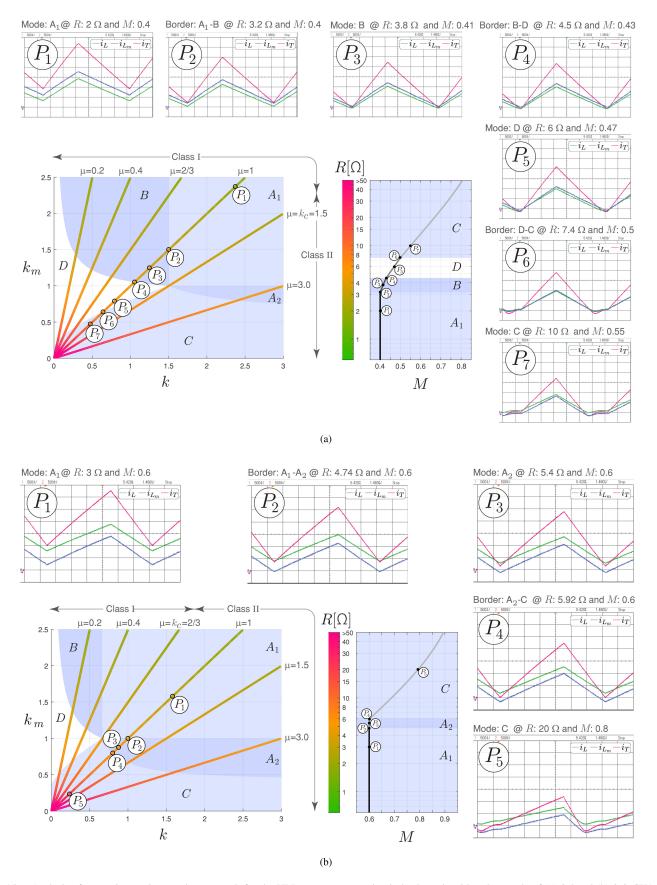

Fig. 15. Analysis of one trajectory in open-loop control, for the VBB converter operating in buck mode with a duty cycle of (a) 0.4 and (b) 0.6. CH1:  $i_L$  (500 mA/div), CH2:  $i_T$  (500 mA/div), Math Channel:  $i_{L_m}=i_T(CH1)-i_L(CH2)$  (500 mA/div), and time base of 1.48  $\mu$ s.

Fig. 16. Analysis of one trajectory in closed-loop control, for the VBB converter operating in buck mode with a conversion ratio of (a) 0.4 and (b) 0.6. CH1:  $i_L$  (600 mA/div), CH2:  $i_T$  (600 mA/div), Math Channel:  $i_{L_m} = i_T(CH1) - i_L(CH2)$  (600 mA/div), CH3:  $V_g$  (15 V/div), CH4:  $V_{C_o}$  (15 V/div), and time base of 1.48  $\mu$ s.

and closed-loop operations can be obtained. This set of curves is presented in this section.

1) Open-Loop Curves: Open-loop control with constant duty cycle and increases in the  $R_L$  value can be plotted in the  $MR_L$  plane. Using (16),  $R_L$  can be expressed in terms of k to graph

the operation in the Mk plane. The set of curves obtained for different  $d_1$  values forms a family of curves whose common characteristic is the value of parameter  $\mu$ . In Fig. 11, two families of open-loop characteristic curves are shown for values of  $\mu=1$  [see Fig. 11(a)] and  $\mu=2$  [see Fig. 11(b)].

Each of these curves describes the operation point locus for one of the previously explained open-loop trajectories. The corresponding class of trajectory can be deduced from (61) and (62). The results are as follows:

1) Class I: if

$$d_1 < \frac{1}{1+\mu}$$

;

2) Class II: if  $d_1 > \frac{1}{1+\mu}$ .

2) Class II: if

$$d_1 > \frac{1}{1+\mu}$$

.

The converter goes through modes according to the type of trajectory. The following equations are useful for finding the operation borders for the curves plotted in the Mk plane:

$$k_{\text{crit\_}A-C} = (1 - d_1)(1 + \mu)$$

(68)

$$k_{\text{crit\_}A-B} = k_c = \frac{1 - d_1}{d_1}$$

(69)

$k_{\text{crit }B-D} =$

$$\frac{\mu(1-d_1)(2+d_1) + d\sqrt{\mu(1-d_1)(\mu(1-d_1)+4)}}{2}$$

(70)

$$k_{\text{crit}\_D-C} = d_1^2 \mu (1+\mu)^2.$$

(71)

These equations can be easily obtained from the equalities in (51), (52), and (56), taking into account (63). On the other hand, the conversion ratio of each region is a mathematical expression of the form  $M_i = f(k, \mu, d_1)$ . The conversion ratios for each region were presented in (33), (39), (40), and (47).

An important characteristic studying the converter is the output impedance behavior. From the curves plotted in Fig. 11, a family of curves  $V_o$  vs.  $I_o$  with constant duty cycles can be obtained as shown in Fig. 12.  $V_o$  is calculated by substituting M and  $V_g$  in (21), while  $I_o$  can be obtained substituting  $R_L$ using Ohm's law in (16) and solving. The evaluation of the sign-changed slope at each operation point determines the output impedance. Note that the impedance in CCM remains zero, while in DCMs, the impedance is variable and increases as  $I_o$ decreases.

2) Closed-Loop Curves: The description is similar to openloop control. In this case, operation curves with constant conversion ratio are plotted on the  $d_1$  k plane. The set of curves obtained for different values of M (with  $\mu$  constant) represent another family of characteristic curves (see Fig. 13). Each curve in the plane  $d_1 k$  shows the converter evolution along with one of the classes of trajectories. The criteria to define the corresponding class are as follows:

1) Class I: if

$$M < \frac{1}{1+\mu}$$

;

2) Class II: if

$$M > \frac{1}{1+\mu}$$

.

In the plotted curves, the borders between modes are obtained by evaluating (72)–(75)

$$k_{\text{crit}\_A-C} = (1-M)(1+\mu)$$

(72)

$$k_{\text{crit\_}A-B} = k_c = \frac{1-M}{M} \tag{73}$$

$$k_{\text{crit\_}B-D} = \frac{-b - \sqrt{b^2 - 4ac}}{2a} \tag{74}$$

$$a = (1 - M)^{2} [1 - M(1 + \mu)]$$

$$b = -\mu [2(1 - M)^{2} + \mu M(2M - 1)]$$

$$c = \mu^{2} (1 - M).$$

(75)

On the other hand, the mathematical expressions of the form  $d_{1-i} = f(k, \mu, M)$ , given in (76)–(80), allow us to obtain the duty cycle required to achieve operation with M constant in mode i.

$$d_{1-A} = M (76)$$

$$d_{1-B} = M \frac{k(1-M) + \sqrt{k(1-M)(k-Mk+4)}}{2(M-1)}$$

(77)

$$d_{1-C} = M\sqrt{\frac{k}{(\mu+1)(1-M)}}\tag{78}$$

$$d_{1-D} = M\sqrt{\frac{k[\mu X + k(2(M-1) + \mu(2M-1))]}{2k(1-M)[M(\mu+1) - 1]}}$$

(79)

where

$$X = \sqrt{k[k + 4kM(M-1) + 4\frac{k}{\mu}(M-1)^2]}.$$

(80)

### VII. EXPERIMENTAL RESULTS

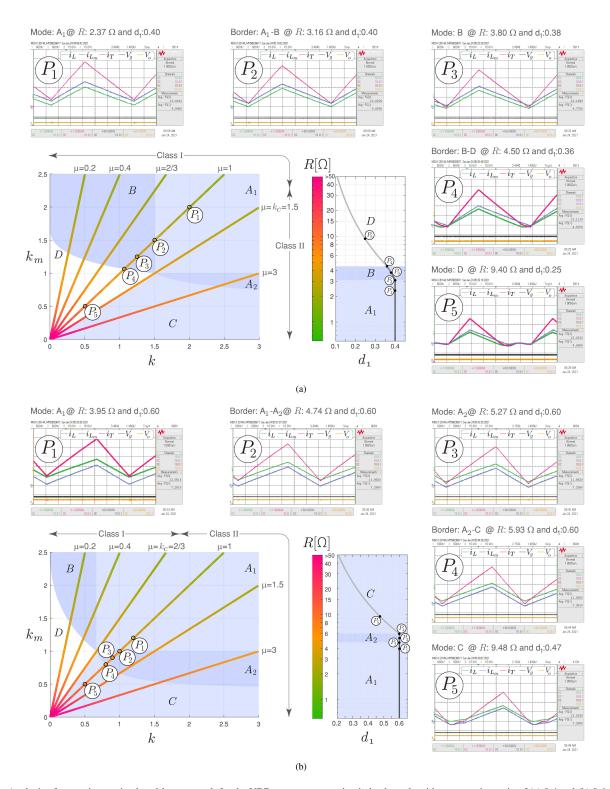

The VBB converter prototype described in [24] was used to obtain the experimental results. The inductor values were  $L=L_m=23.7\,\mu\mathrm{H}$ , which means  $\mu=1$  in this design. The experimental configuration of the power circuit is shown in Fig. 14. A Texas instruments TMS320F28335 digital signal controller was used to generate the switching signals for openand closed-loop operations. Open-loop results for duty cycles of 0.4 and 0.6 are shown in Fig. 15(a) and (b). In both cases, current waveforms are depicted for different operation points that belong to the trajectory  $\mu = 1$ , which are also plotted in the  $kk_m$  plane, where all of the operation modes and borders are shown. These operation points exhaustively describe all the regions and borders that the converter can reach with  $\mu=1$  as the  $R_L$  value increases. Several trajectories with a color scale were included to show the evolution of the operation modes. Note that  $\mu = 1$  is Class I for a duty cycle of 0.4 and Class II for a duty cycle of 0.6. Closed-loop experimental results for 0.4 and 0.6 conversion ratios are shown in Fig. 16(a) and (b). These figures show current and voltage waveforms for different operation points that belong to the closed-loop regions and borders of the trajectory  $\mu = 1$ , which are also plotted in the  $kk_m$  plane. Experimental results in both open- and closed-loop operations validated all of the VBB converter conduction modes (CCM and DCMs) demonstrating agreement with the theoretical analysis in both trajectories. The waveforms mentioned above show the agreement with the expected waveforms generically plotted in Fig. 8.

### VIII. CONCLUSION

A general method to determine the conduction modes of dc-dc converters with only one transistor has been presented in this article. The first step of the method consists in determining the number n, which corresponds to the diodes conducting current passing exclusively through inductors when the transistor turns OFF. Afterwards, one dimensionless parameter k is defined for each of these n diodes. The set of these parameters defines the k-space. In the k-space, the converter operation describes a straight line when the load changes. This straight line is called "converter trajectory." The converter trajectory is independent from the converter duty cycle and from the converter conversion ratio, and it only depends on the ratio of inductors. The converter trajectory passes through different n-dimensional enclosures in the k-space. The total number of possible enclosures is  $2^n$ . Each one of these n-dimensional enclosures represents a different conduction mode. The borders between enclosures depend on the converter control strategy. If the converter is operating in open loop, then there will be a specific set of borders between adjacent enclosures for each duty cycle. On the other hand, if the converter is operating in closed loop, then there will be another specific set of borders for each conversion ratio. In the particular case of n=2, the k-space is a plane and there are four regions corresponding to one CCM and three DCMs. The borders between adjacent regions are curves. The set of regions and their borders configure a "map." As mentioned before, these borders (curves) depend on the control strategy, thus existing two families of maps, one family for open-loop, and another family for closed-loop. As a study case of the method proposed in this article, the conduction modes of the unidirectional version of the VBB converter working in the boost and buck modes have been presented. The analysis shows that there are only two conduction modes (one CCM and one DCM) in boost mode, which fit the behavior of a classic boost. In contrast, VBB converter operation in buck mode has two diodes in inductive branches, which means that n=2, and, therefore, there are two k parameters (k and  $k_m$ ) and four conduction modes, of which one is the CCM (subdivided into Modes A1 and A2) and three are DCMs (Modes B, C, and D). Consequently, four regions can be delimited in the  $kk_m$ plane. These four regions have a common point, called "singular point." Besides this singular point, the borders between adjacent regions are curves in the  $kk_m$  plane, whose equations have been calculated in the article for both converter control strategies (i.e., open- and closed-loop). Thus, two families of maps can be established in the  $kk_m$  plane. In each map, two classes of trajectories can be established. Moreover, in each conduction mode, the conversion ratio corresponding to a given duty cycle (useful for calculations in open loop) and the duty cycle corresponding to a given conversion ratio (useful for calculations in closed loop) has been computed in the article. Once the map and the trajectory is known, the converter operation is completely defined, because a specific load means a specific point in the trajectory, which is placed in a specific region in the map. Either the conversion ratio (open-loop) or the duty cycle (closed-loop) corresponding to this operating point can be easily computed by using the

already determined corresponding equations. Using these proper equations, the completed behavior of the converter when the load changes is completely determined for both control strategies. As expected, the open-loop output impedance is zero in the CCM and increases when the load increases in all the DCMs. Finally, all the theoretical predictions around the different conduction modes have been verified in a converter prototype.

#### ACKNOWLEDGMENT

The authors would like to thank Janeth Alpala from Artificial Intelligence for Electrical Engineering Research Program, SDAS Research Group<sup>1</sup>, for her mathematical support.

#### REFERENCES

- R. W. Erickson and D. Maksimovic, Fundamentals of Power Electronics. New York, NY, USA: Springer Science & Business Media, 2007.

- [2] K. Liu and Y. Lin, "Current waveform distortion in power factor correction circuits employing discontinuous-mode boost converters," in *Proc. 20th Annu. IEEE Power Electron. Specialists Conf.*, vol. 2, 1989, pp. 825–829.

- [3] R. Erickson, M. Madigan, and S. Singer, "Design of a simple high-power-factor rectifier based on the flyback converter," in *Proc. 5th Annu. Appl. Power Electron. Conf. Expo.*, 1990, pp. 792–801.

- [4] J. Sebastian, J. Uceda, J. A. Cobos, J. Arau, and F. Aldana, "Improving power factor correction in distributed power supply systems using PWM and ZCS-QR SEPIC topologies," in *Proc. Rec. 22nd Annu. IEEE Power Electron. Specialists Conf.*, 1991, pp. 780–791.

- [5] M. Brkovic and S. Cuk, "Input current shaper using CUK converter," in Proc. 14th Int. Telecommun. Energy Conf., 1992, pp. 532–539.

- [6] D. S. L. Simonetti, J. Sebastian, and J. Uceda, "The discontinuous conduction mode SEPIC and CUK power factor preregulators: Analysis and design," *IEEE Trans. Ind. Electron.*, vol. 44, no. 5, pp. 630–637, Oct. 1997.

- [7] X. Ren, Z. Guo, Y. Wu, Z. Zhang, and Q. Chen, "Adaptive LUT-based variable on-time control for CRM boost PFC converters," *IEEE Trans. Power Electron.*, vol. 33, no. 9, pp. 8123–8136, Sep. 2018.

- [8] K. Yao, X. Zhou, F. Yang, S. Yang, C. Cao, and C. Mao, "Optimum third current harmonic during nondead zone and its control implementation to improve PF for DCM buck PFC converter," *IEEE Trans. Power Electron.*, vol. 32, no. 12, pp. 9238–9248, Dec. 2017.

- [9] M. Lee and J.-S. Lai, "Unified voltage balancing feedforward for three-level boost PFC converter in discontinuous and critical conduction modes," *IEEE Trans. Circuits Syst. II: Exp. Briefs*, vol. 68, no. 1, pp. 441–445, Jan 2021

- [10] V. Pogaku and P. Sensarma, "Super buck converter for high step-down DC-DC conversion," in *Proc. 45th Annu. Conf. IEEE Ind. Electron. Soc.*, vol. 1, 2019, pp. 2038–2043.

- [11] F.-Z. Chen and D. Maksimović, "Digital control for improved efficiency and reduced harmonic distortion over wide load range in boost PFC rectifiers," *IEEE Trans. Power Electron.*, vol. 25, no. 10, pp. 2683–2692, Oct. 2010.

- [12] J.-Y. Lee and H.-J. Chae, "6.6-kw onboard charger design using DCM PFC converter with harmonic modulation technique and two-stage DC/DC converter," *IEEE Trans. Ind. Electron.*, vol. 61, no. 3, pp. 1243–1252, Mar. 2014.

- [13] L. Li, Q. Zhang, R. Min, K. Liu, Q. Tong, and D. Lyu, "A current reshaping strategy to reduce parasitics-induced current distortion in discontinuous conduction mode boost power factor correction converter," *IEEE Trans. Ind. Electron.*, vol. 68, no. 3, pp. 2215–2224, Mar. 2021.

- [14] R. Min et al., "Superposed compensation strategy to optimize load/line transient response and reference tracking for discontinuous conduction mode boost converter," *IEEE Trans. Ind. Inform.*, vol. 15, no. 5, pp. 2512–2522, May 2019.

- [15] Y.-L. Chen and Y.-M. Chen, "Line current distortion compensation for DCM/CRM boost PFC converters," *IEEE Trans. Power Electron.*, vol. 31, no. 3, pp. 2026–2038, Mar. 2016.

<sup>&</sup>lt;sup>1</sup>[Online]. Available: www.sdas-group.com

- [16] H. Dong, X. Xie, F. Mao, L. Zhang, and Y. He, "A novel primary-side regulation control scheme for CCM and DCM LLC LED driver based on "magnetizing current cancellation method"," *IEEE Trans. Power Electron.*, vol. 35, no. 11, pp. 12223–12237, Nov. 2020.

- [17] X. Ren, Y. Zhou, Z. Guo, Y. Wu, Z. Zhang, and Q. Chen, "Simple analog-based accurate variable on-time control for critical conduction mode boost power factor correction converters," *IEEE Trans. Emerg. Sel. Topics Power Electron.*, vol. 8, no. 4, pp. 4025–4036, Dec. 2020.

- [18] K. Schenk and S. Cuk, "Small signal analysis of converters with multiple discontinuous conduction modes," in *Proc. 29th Annu. IEEE Power Electron. Specialists Conf.*, vol. 1, 1998, pp. 623–629.

- [19] S. Cuk and R. D. Middlebrook, "A general unified approach to modelling switching DC-to-DC converters in discontinuous conduction mode," in *Proc. IEEE Power Electron. Specialists Conf.*, 1977, pp. 36–57.

- [20] C. Restrepo, J. Calvente, A. Cid-Pastor, A. E. Aroudi, and R. Giral, "A noninverting buck-boost DC-DC switching converter with high efficiency and wide bandwidth," *IEEE Trans. Power Electron.*, vol. 26, no. 9, pp. 2490–2503, Sep. 2011.

- [21] C. Restrepo, T. Konjedic, J. Calvente, M. Milanovic, and R. Giral, "Fast transitions between current control loops of the coupled-inductor buckboost DC-DC switching converter," *IEEE Trans. Power Electron.*, vol. 28, no. 8, pp. 3648–3652, Aug. 2013.

- [22] C. Restrepo, T. Konjedic, J. Calvente, and R. Giral, "Hysteretic transition method for avoiding the dead-zone effect and subharmonics in a noninverting buck-boost converter," *IEEE Trans. Power Electron.*, vol. 30, no. 6, pp. 3418–3430, Jun. 2015.

- [23] H. Ramírez-Murillo, C. Restrepo, J. Calvente, A. Romero, and R. Giral, "Energy management DC system based on current-controlled buck-boost modules," *IEEE Trans. Smart Grid*, vol. 5, no. 5, pp. 2644–2653, Sep. 2014

- [24] H. Ramírez-Murillo, C. Restrepo, J. Calvente, A. Romero, and R. Giral, "Energy management of a fuel-cell serial-parallel hybrid system," *IEEE Trans. Ind. Electron.*, vol. 62, no. 8, pp. 5227–5235, Aug. 2015.

- [25] C. Restrepo, T. Konjedic, F. Flores-Bahamonde, E. Vidal-Idiarte, J. Calvente, and R. Giral, "Multisampled digital average current controls of the versatile buck-boost converter," *IEEE Trans. Emerg. Sel. Topics Power Electron.*, vol. 7, no. 2, pp. 879–890, Jun. 2019.

**Duberney Murillo-Yarce** received the bachelor's and master's degrees in electrical engineering from Universidad Tecnológica de Pereira (UTP), Pereira, Colombia, in 2004 and 2010, respectively. He is currently working toward the Ph.D. degree in power electronics with the Engineering Systems Doctoral Program, Universidad de Talca, Curicó, Chile.

From 2006 to 2018, he was a Professor in Electrical and Electronic Engineering programs with the Faculty of Engineering, UTP. In addition, he is a Researcher with the Laboratory of Applications, Smart

Grids Research Group (LARI in Spanish). His research interests include modeling and controlling power electronic converters, renewable energies, and model predictive control.

Carlos Restrepo received the bachelor's (Hons.) and master's degrees in electrical engineering from the Universidad Tecnológica de Pereira, Pereira, Colombia, in 2006 and 2007, respectively, and the master's and Ph.D. (Hons.) degrees in electronic engineering from the Universitat Rovira i Virgili de Tarragona, Tarragona, Spain, in 2008 and 2012, respectively.

He was a Visiting Scholar with the Faculty of Electrical Engineering and Computer Science, University of Maribor, Maribor, Slovenia, in 2011. During 2013 and 2014, he was a Postdoctoral Researcher with the

Electrical Power Processing Group, Delft University of Technology, Delft, The Netherlands. From 2014 to 2016, he was a Professor with the Departamento de Ingeniería Eléctrica, Universidad Técnica Federico Santa María, Santiago de Chile, Chile. He is currently a Professor with the Departamento de Ingeniería Eléctrica, Universidad de Talca, Curicó, Chile. His main research interests include modeling and emulator design for fuel cells, design and digital control of switched converters, and energy management of hybrid electric vehicles. He is the Director of the Laboratory of Applications in Smart Grids (LARI in Spanish) research group.

**Diego G. Lamar** (Senior Member, IEEE) was born in Zaragoza, Spain, in 1974. He received the M.Sc. and Ph.D. degrees in electrical engineering from the University of Oviedo, Oviedo, Spain, in 2003 and 2008, respectively.

In 2003, 2005, and 2011, he was a Research Engineer, Assistant Professor, and Associate Professor, respectively, with the University of Oviedo. Since 2022, he has been a Full Professor with the University of Oviedo. Since 2003, he has been involved in Power Electronics, participating in more than 40

research and development projects. He has authored or coauthored more than 140 technical papers in IEEE transactions and IEEE conferences. His main research interests include converter modeling, power factor correction, LED drivers, dc–dc converters for visible light communication applications, and wide bandgap semiconductors in power converters.

Javier Sebastián (Senior Member, IEEE) was born in Madrid, Spain, in 1958. He received the M.Sc. degree from the Technical University of Madrid (UPM), Madrid, Spain, in 1981, and the Ph.D. degree from the University of Oviedo, Oviedo, Spain, in 1984, both in industrial engineering.

He was an Assistant Professor and an Associate Professor with both the UPM and the University of Oviedo. Since 1992, he has been with the University of Oviedo, where he is currently a Professor. His research interests include switching-mode power sup-

plies, modeling of dc-to-dc converters, single-phase high power factor rectifiers, LED drivers, dc-to-dc converters for envelope tracking techniques and for visible light communication, and the use of wide bandgap semiconductors in power supplies.