#

Ioannis Nikiforidis , Juan M. Arteaga , *Member, IEEE*, Christopher H. Kwan, Nunzio Pucci , *Student Member, IEEE*, David C. Yates, *Member, IEEE*, and Paul D. Mitcheson , *Senior Member, IEEE*

Abstract—The additional complexity of Class EF and Class Φ inverters compared with their Class E counterparts, combined with parasitic effects becoming more prevalent as frequency and power levels increase, results in poor accuracy from traditional design methods, and usually additional iterations of manual retuning are required. Furthermore, after making these additional iterations, it is practically impossible to ensure that all the desired design conditions are met in hardware, due to the number of degrees of freedom in these circuits. In this work, we propose an approach to simulating and tuning Class EF/ $\Phi$  inverters, with various levels of accuracy depending on the level of knowledge of the system parasitics. Our method is composed of a combination of analytic and numerical solving methods, thus providing both insight on the progression of the algorithm and computational robustness. The aim of our algorithm formulation is to enable solutions to be found in an automated and fast way. The novelty in our work lies in the design method's concurrent capability to provide a generalized set of design inputs (e.g., dc to ac current gain, arbitrary drain voltage slope at turn ON, Φ-branch resonance, etc.), inclusion of board and device nonlinear parasitics, and the ability to design within the set of preferred component values. An example is shown for the design of a 50-W, 13.56-MHz inverter where the experimental setup approaches the theoretical efficiency of 97%, whilst maintaining all of the other design requirements. The algorithm changes the

Manuscript received November 3, 2021; revised January 31, 2022 and April 4, 2022; accepted May 8, 2022. Date of publication May 20, 2022; date of current version June 24, 2022. This work was supported in part by the European Union's Horizon 2020 Research and Innovation Programme under Marie Skłodowska-Curie Grant 722496, in part by EPSRC Quietening ultralow-loss SiC & GaN waveforms, under Grant EP/R029504/1, in part by the Department of Electrical and Electronic Engineering, Imperial College, London, in part by EPSRC Impact Acceleration Account–Imperial College London 2020 under Grant EP/R511547/1, and in part by SitS NSF-UKRI: Wireless In-Situ 801 Sensing Network for Future Sustainable Agriculture under Grant NE/T011467/1. Recommended for publication by Associate Editor D. Mark Xu. (Corresponding author: Ioannis Nikiforidis.)

Ioannis Nikiforidis is with the Wireless Power Lab, Control and Power Group, Electrical and Electronic Engineering Department, Imperial College London, SW7 2AZ London, U.K., and also with Bumblebee Power Ltd, Battersea SW8 3NS London, U.K. (e-mail: i.nikiforidis@imperial.ac.uk).

Juan M. Arteaga, Nunzio Pucci, and Paul D. Mitcheson are with the Wireless Power Lab, Control and Power Group, Electrical and Electronic Engineering Department, Imperial College London, SW7 2AZ London, U.K. (e-mail: j.arteaga-saenz15@imperial.ac.uk; nunzio.pucci15@imperial.ac.uk; paul.mitcheson@imperial.ac.uk).

Christopher H. Kwan and David C. Yates are with Bumblebee Power Ltd, Battersea SW8 3NS London, U.K. (e-mail: chris@bumblebeepower.com; david@bumblebeepower.com).

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TPEL.2022.3176391.

Digital Object Identifier 10.1109/TPEL.2022.3176391

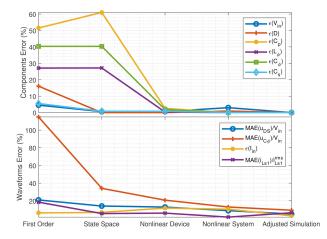

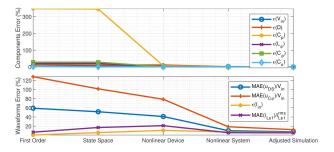

values of the components over 5%–50% and improves the simulated waveform accuracy by 2–12 times compared with the design method based on first-order approximations.

Index Terms—Circuit simulation, Class  $\Phi$ , Class EF, high frequency (HF), inverter design, resonant power converter, wireless power transfer (WPT).

#### I. INTRODUCTION

RANSMITTING power using a high-frequency (HF) induction offers numerous benefits for wireless power transfer (WPT) systems as the link can be realized with miniaturized and lightweight air core coils with high-quality factors (Q) that can transmit power efficiently over low coupling [1]–[3]. Advances in wide-bandgap devices make the realization of HF inductive power transfer (IPT) systems operating in MHz frequency range more attractive, where the Class E-type single-switch resonant converter circuits demonstrate benefits over the Class D-type drivers [4]–[6].

The properties of the basic Class E inverter can be enriched and the design possibilities can be expanded by adding resonant networks in parallel and in series with the series load network [7]-[11]. These topologies have been given different names in the literature based on the resonant frequency of those additional networks and the degree that the input choke is contributing to the rest of the resonant circuit of the inverter. In this work, we use the term "Class EF<sub>n</sub>" when referring to a design with an infinite choke and "Class  $\Phi_n$ " when the finite input choke is contributing to the resonant behavior of the inverter, where "n" is the ratio of the resonance frequency of the single parallel resonant branch ( $\phi$ -branch) over the switching frequency. The two additional degrees of freedom for defining the behavior of the inverter that the  $\phi$ -branch provides enable the Class EF/ $\Phi$ inverters to achieve better device power capability utilization by shaping the drain voltage and to decrease total harmonic distortion (THD) by filtering the output current, compared to the typical Class E converters. These additional degrees of freedom also expand the number of circuit operating properties that can be set independently, beyond what can be achieved with Class E inverters. For example, load-independent operation can be achieved with a Class E converter using a finite dc feed inductor [10], [12], [13], but Class EF can do the same with a infinite choke [10], which can be preferable in cases where a low ripple input current is required.

Because of the high number of design variables combined with the low component value tolerances of these resonant circuits, it is typical that additional manual retuning is required, which is an iterative procedure based on trial and error [10], [14]–[16]. This process is not trivial and requires high level of insight and experience [14], [16], [17], especially at high operating frequency and power level. Most importantly though, after such alterations to the original design, it is not guaranteed that the final experimental setup will still remain true to the initial design requirements [18].

The main motivation leading to this work is to eliminate the need of manual retuning of Class EF/ $\Phi$  inverters, by developing a robust and reproducible design method, which can be fully automated and produces reliable results with high accuracy. In addition, our method is able to cater for designs based on specification of several different properties of the converter circuit, such as the dc to ac current gain, and the slope of the drain voltage at turn ON while maintaining zero-voltage switching (ZVS) at the specified  $\phi$ -branch resonance frequency. The scope of this work is to explain the details of the proposed design algorithm rather than propose specific inverter designs.

Our proposed algorithm provides different levels of precision, depending on the amount of information that is available about the system. Different complexities of models from ideal first-order (FO) approximations to state-space (SS) models with a nonlinear switching device are used. Furthermore, in order to take full advantage of the design degrees of freedom that the Class EF/ $\Phi$  inverter provides, this algorithm regularly ensures during its progression that the required properties of the circuit are maintained until the end, with no external supervision form the user being needed.

#### II. OVERVIEW

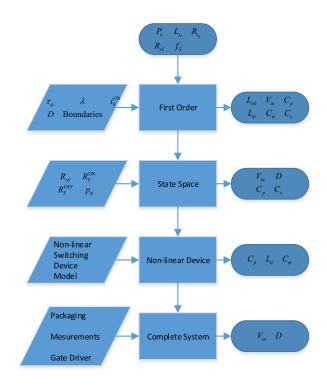

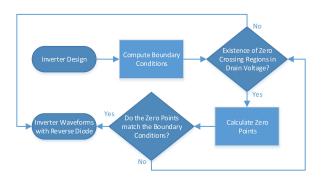

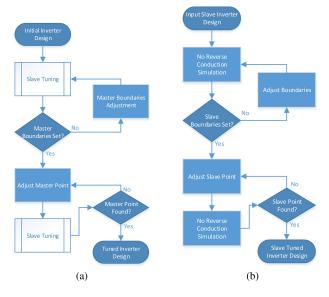

The inverter design process flow chart is illustrated in Fig. 1. It consists of four main, interdependent steps executed in sequence, which are further explained in the corresponding sections. Depending on the desired accuracy of simulation to experimental matching requirements, the tuning process can be terminated at the end of any of the specified steps of the procedure.

The first step of the design algorithm (Section III) is based on FO analysis of the circuit. It is the least accurate part of the proposed tuning process. However, it is the only one that uses analytic expressions, and its main contribution is that it provides a good starting point for the iterative methods that follow, ensuring speed and convergence. Typically, the component values that this part of the design algorithm produces are not very accurate, mainly due to its inherit simplification, as explained in Section III-A. The accuracy of the outputs can be evaluated by an LTspice simulation, which will determine whether the subsequent steps of the algorithm need to be applied.

The second tuning part, analyzed in Section IV, is based on SS representation of the circuit and resolves any approximation and simplification errors caused by the first part. The accuracy of the outcome of this algorithm step should be practically enough

Fig. 1. Class  $EF/\Phi$  inverter design flowchart diagram.

when the switching frequency is low enough so that the shunt capacitor value (circuit diagram details given in Section III-A) is substantially higher than the effective output capacitance of the device (for a given power level). This is due to the fact that the values of the energy storing components are related to the operating frequency. Usually, when this is the case, the effect of the rest of the parasitic capacitances of the device along with the stray package inductances and gate driver imperfections is negligible, too. If any of the two first steps of the algorithm fail to converge or produce a realistic result, it is an indication that the operation requirements cannot be met with the given input conditions.

The third part introduces a more representative nonlinear model of the switching device and compensates for the changes caused by the parasitics of the device, and is discussed in Section V. Proceeding to this part of the algorithm is required at higher switching frequencies, as the theoretical speed threshold of the converter is approached. If this part does not converge, it means that the parasitics of the transistor of choice cannot be absorbed in the circuit.

The fourth part includes the effects caused by the unavoidable mismatch between the theoretical optimal component values and their actual experimental measurements and is given in Section VI. This stage is essential when this mismatch becomes substantial, mostly due to limitations of off-the-shelf passive component values. The last two parts also include the effects of the packaging of the device and gate drive signal-shaping resistances. Convergence failure during the last part of our algorithm shows that the circuit design cannot be realized with preferred values.

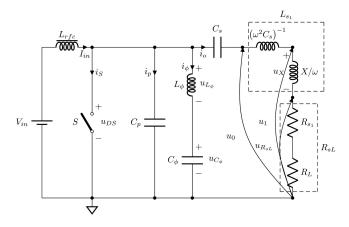

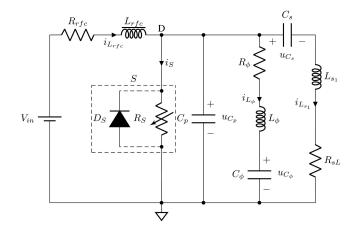

Fig. 2. Circuit diagram of Class  $EF/\Phi$  inverter using the first-order formulation.

The description of the experimental setup and circuit examples used for the verification of the performance of our proposed method are given in Section VII and in the Appendix. Measurements are taken across a variety of operating conditions and the evaluation of the accuracy and contribution of each tuning step is performed.

#### III. FIRST-ORDER APPROXIMATION

The first section of the proposed tuning algorithm uses a FO approximation. The derivation of the design equations and the corresponding assumptions they are based on have been extensively described in [5], [18]–[21] for infinite choke Class E, in [22], [23] for the finite choke Class E, in [7], [24], [25] for the Class  $\Phi$ , and in [10], [26] for the Class EF inverter. Second-order approximations for the simulation of Class E inverters have been applied in [27]. In this work, we formulate the problem using a combination of the analytic methods mentioned above in a way that provides both control and insight to the user about the tuning of the resulting circuit. This part of the design algorithm is the only one that is based on analytical synthesis; the rest use iterative optimization. As stated previously, the design algorithm uses the FO approach as an initial point for the iterative procedures that follow in the next steps, for faster and more controlled convergence.

#### A. Design and Simulation Equations

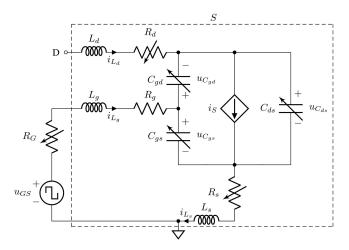

The circuit diagram of an ideal Class EF/ $\Phi$  inverter is shown in Fig. 2. In this work, we implement the Class EF/ $\Phi$  inverter as a primary coil driver in WPT applications. In the diagram of Fig. 2,  $L_{s_1}$  is the transmitter (Tx) coil inductance and  $R_{sL}$  is the series combination of the primary coil resistance  $(R_{s_1})$  with the equivalent resistance of the secondary reflected to the primary  $(R_L = R_{sL} - R_{s_1})$ , with zero reflected reactance [5]. The final component of the series load network is the  $C_s$  capacitor. The input choke inductance  $(L_{rfc})$  can be regarded as either finite (Class  $\Phi$ ) or infinite (Class EF).  $C_p$  is the shunt capacitor to the switching device (S) and  $L_{\phi}$  in series with  $C_{\phi}$  form the added

resonant  $\phi$ -branch network parallel to the load network, which is absent in the Class E inverter.

As shown in Fig. 1, the FO design process of the inverter begins by determining the requirements of the IPT system, namely the output power  $P_o$  and switching frequency  $f_S$ . Then, we define the desired characteristics of the circuit, i.e., the frequency of the  $\phi$ -branch normalized to  $f_S$  ( $\tau_\phi$ ), the duty cycle (D), the ratio  $\lambda$  of the peak output current ( $I_m$ ) to the input current ( $I_{in}$ ) (which represents the dc to ac current gain), and the current through S at turn-ON ( $i_S^{\rm ON}$ ).  $R_{sL}$  is defined according to the inductive link properties and the corresponding choice of  $L_{s_1}$ , while  $R_{s_1}$  is an intrinsic property of  $L_{s_1}$ .

We assume that the load network Q is high enough, i.e.,  $\omega L_{s_1}/R_{sL}>15$  [5], so that the current through the coil can be approximated as sinusoidal [19]:  $i_o(\theta)/I_{\rm in}=\lambda\sin(\theta+\phi)$ , where  $\phi$  is the output current phase relative to the gate signal of the switching device [20], and  $\theta=\omega t$  is the angular time in radians, with  $\omega=2\pi f_S$  being the angular switching frequency and t being the time. The input current is  $I_{\rm in}=I_m/\lambda$ , where  $I_m=\sqrt{2P_o/R_L}$ . Since the only losses incorporated in the circuit are in the Tx coil,  $V_{\rm in}=\lambda I_m R_{sL}/2$ . If it is preferable to design with the input voltage set as condition, then the last equation needs to be solved for  $\lambda$  instead.

Since S is modeled as an ideal switch, there is no voltage drop across it when turned ON and no current flows through it during turn-OFF. Also, the current through  $C_p$  during turn-ON is considered to be zero. By applying Kirchhoff's voltage (KVL) and current law (KCL) to the  $\phi$ -branch and solving the resulting differential equation for the  $\phi$ -branch current using the Laplace transform, we get

$$\frac{i_{\phi}(\theta)}{I_{\text{in}}}\Big|_{\theta_{\text{ON}}^{+} \leq \theta \leq \theta_{\text{OFF}}^{-}} = A_{1}\left(i_{\phi}\left(\theta_{\text{ON}}^{+}\right)\right)\cos\left(\tau_{\phi}\theta\right) \\

+ B_{1}\left(u_{C_{\phi}}\left(\theta_{\text{ON}}^{+}\right)\right)\sin\left(\tau_{\phi}\theta\right) \quad (1)$$

$$\frac{i_{\phi}(\theta)}{I_{\text{in}}}\Big|_{\theta_{\text{OFF}}^{+} \leq \theta \leq \theta_{\text{ON}}^{-}} = A_{2}\left(i_{\phi}\left(\theta_{\text{OFF}}^{+}\right)\right)\cos\left(\tau_{2}\theta\right) \\

+ B_{2}\left(u_{C_{\phi}}\left(\theta_{\text{OFF}}^{+}\right)\right)\sin\left(\tau_{2}\theta\right) \\

- P_{1}\sin\left(\theta + \phi\right) + K_{1} \quad (2)$$

where  $\theta_{\rm ON}^+=0$ ,  $\theta_{\rm ON}^-=2\pi$ , and  $\theta_{\rm OFF}=\theta_{\rm ON}^-D$  are the boundary angles at turn-ON and turn-OFF, respectively;  $A_{1,2}$  and  $B_{1,2}$  are boundary conditions-dependent coefficients;  $u_{C_\phi}$  is the voltage across  $C_\phi$ ;  $K_1=p/\lambda$ ;  $\tau_2=\tau_\phi/\sqrt{K_2}$  and  $K_2=1-K_1$ ; and  $P_1=p\tau_2^2/(\tau_2^2-1)$ .

By definition, the voltage across  $L_\phi$   $(u_{L_\phi})$  and  $u_{C_\phi}$  can be directly calculated from  $i_\phi$

$$\frac{u_{L_{\phi}}(\theta)}{V_{\text{in}}} = \frac{\omega B_{C} L_{\phi}}{a} \cdot \begin{cases}

\tau_{\phi} \left[ B_{1} \cos \left( \tau_{\phi} \theta \right) - A_{1} \sin \left( \tau_{\phi} \theta \right) \right], \\

\theta_{\text{ON}}^{+} \leq \theta \leq \theta_{\text{OFF}}^{-} \\

\tau_{2} \left[ B_{2} \cos \left( \tau_{2} \theta \right) - A_{2} \sin \left( \tau_{2} \theta \right) \right] - P_{1} \\

\cdot \cos \left( \theta + \phi \right), \ \theta_{\text{OFF}}^{+} \leq \theta \leq \theta_{\text{ON}}^{-}

\end{cases} (3)$$

$$\frac{u_{C_{\phi}}(\theta)}{V_{\text{in}}} = \frac{k}{a} \begin{cases}

\frac{A_1}{\tau_{\phi}} \sin(\tau_{\phi}\theta) - \frac{B_1}{\tau_{\phi}} \sin(\tau_{\phi}\theta) \\

\theta_{\text{ON}}^+ \le \theta \le \theta_{\text{OFF}}^- \\

\frac{A_2}{\tau_2} \sin(\tau_2\theta) - \frac{B_2}{\tau_2} \sin(\tau_2\theta) \\

+ P_1 \cos(\theta + \phi) + K_1\theta + E \\

\theta_{\text{OFF}}^+ \le \theta \le \theta_{\text{ON}}^-

\end{cases} \tag{4}$$

where  $B_C = \omega C_p$ ,  $k = C_p/C_\phi$ , and

$$\theta_{\text{ON}}^{-}a = K_2 \left(\theta_{\text{OFF}} - \theta_{\text{ON}}^{-}\right)^2 + P_2 \left[\sin\left(\theta_{\text{OFF}} + \phi\right) + \left(\theta_{\text{ON}}^{-} - \theta_{\text{OFF}}\right) \cos\left(\theta_{\text{OFF}} + \phi\right) - \sin\phi\right] + \frac{A_2}{\tau_2} \left[\frac{1}{\tau_2}\right] \cdot \left(\cos\left(\tau_2\theta_{\text{ON}}^{-}\right) - \cos\left(\tau_2\theta_{\text{OFF}}\right)\right) + \left(\theta_{\text{ON}}^{-} - \theta_{\text{OFF}}\right) \cdot \sin\left(\tau_2\theta_{\text{OFF}}\right)\right] + \frac{B_2}{\tau_2} \left\{\frac{1}{\tau_2} \left[\sin\left(\tau_2\theta_{\text{ON}}^{-}\right)\right] - \sin\left(\tau_2\theta_{\text{OFF}}\right)\right] - \left(\theta_{\text{ON}}^{-} - \theta_{\text{OFF}}\right) \cos\left(\tau_2\theta_{\text{OFF}}\right)\right\}$$

(5)

$$E = P_1 \left[\frac{\cos\phi}{K_2\tau_2} - \cos\left(\theta_{\text{OFF}} + \phi\right)\right] - K_1\theta_{\text{OFF}} + \frac{B_2}{\tau_2} \left[\cos\left(\tau_2\theta_{\text{OFF}}\right) - \frac{1}{K_2}\right] - \frac{A_2}{\tau_2} \sin\left(\tau_2\theta_{\text{OFF}}\right).$$

If we were to derive the exact waveform expressions of the inverter in Fig. 2, we should be solving a sixth-degree differential equation (which is the approach we follow in the second part of this proposed design algorithm). However, doing so results in overly complicated analytical expressions of very limited practical use. Even the approximation of infinite  $L_{\rm rfc}$  and high Q output network still requires solving a third-order differential equation with two boundary conditions (device turned OFF and ON). For comparison, the Class E inverter requires solving just one FO differential equation [19].

To overcome this, we made one more simplification, which despite introducing another source of error, results in a more manageable expression with a good trade-off of accuracy to complexity: We treat the  $\phi$ -branch independently of the shunt capacitor network during turn-OFF. This is also obvious from the formulation of the current through the  $\phi$ -branch equations that follows, which incorporates only four boundary-dependent parameters  $(A_{1,2},B_{1,2})$  instead of six, which effectively reduces the degree of the differential equation from three to two. This results in simpler and more compact analytic waveform expressions. The choice of the  $\phi$ -branch specifically is also based on

the fact that during turn-ON, it is already independent of the shunt capacitor, since the device is shorting it. It should be mentioned that this approach is fairly typical in the existing literature [10], [26]. The additional source of error introduced by this approach is eliminated by the more accuracy-based iterative tuning process of the subsequent algorithmic stage in Section IV, which simulates the circuit using the full sixth-degree SS differential equation solution.

Given the above reasoning, the ON–OFF boundary conditions of the  $\phi$ -branch-shunt network can involve any combination of two signals among the drain voltage  $(u_{\rm DS})$ ,  $i_{\phi}$  and  $u_{C_{\phi}}$ . Different combinations of boundary conditions will provide different inverter designs, for the same inputs. The designer can choose the preferred boundaries based on the component values that they provide and the focus of the modeling accuracy of the FO approximation, since the parts off the circuit that the boundaries are applied will be simulated with more precision. As an example, we provide the exact equations satisfying the switching continuity conditions for the  $i_{\phi}$  and  $u_{C_{\phi}}$  boundaries. By using (1), (2), and (4) to satisfy the boundary continuity conditions, we get  $[A_1, B_1, A_2, B_2]^T = \mathbf{B}^{-1}\mathbf{a}$ , where (7) shown at the bottom of this page.

$$\mathbf{a} = \begin{bmatrix} K_1 - P_1 \sin \left(\theta_{\text{OFF}} + \phi\right) \\ K_1 - P_1 \sin \phi \\ \frac{P_1 \cos \phi}{\sqrt{K_2}} \\ P_1 \left[ \cos \left(\theta_{\text{OFF}} + \phi\right) - \left(1 + \frac{1}{\tau_2 K_2}\right) \cos \phi \right] \\ + \left(\theta_{\text{ON}}^- - \theta_{\text{OFF}}\right) K_1 \end{bmatrix}$$

(8)

By applying KCL while the device is not conducting and incorporating  $i_o$  and (2), the normalized current through  $C_p$  is given by

$$\frac{i_p(\theta)}{I_{\text{in}}}\bigg|_{\theta_{\text{OFF}}^+ \le \theta \le \theta_{\text{ON}}^-} = K_2 + P_2 \sin(\theta + \phi)

- A_2 \cos(\tau_2 \theta) - B_2 \sin(\tau_2 \theta). \quad (9)$$

The voltage across the device during the OFF time is directly derived from integrating (9)

$$a \left. \frac{u_{\rm DS} \left( \theta \right)}{V_{\rm in}} \right|_{\theta_{\rm OFF}^{+} \le \theta \le \theta_{\rm ON}^{-}} = K_{2} \theta - P_{2} \cos \left( \theta + \phi \right)$$

$$- \frac{A_{2}}{\tau_{\phi}} \sin \left( \tau_{\phi} \theta \right) + \frac{B_{2}}{\tau_{\phi}} \cos \left( \tau_{\phi} \theta \right) + C \tag{10}$$

$$\mathbf{B} = \begin{bmatrix} \cos\left(\tau_{\phi}\theta_{\mathrm{OFF}}\right) & \sin\left(\tau_{\phi}\theta_{\mathrm{OFF}}\right) & -\cos\left(\tau_{2}\theta_{\mathrm{OFF}}\right) & -\sin\left(\tau_{2}\theta_{\mathrm{OFF}}\right) \\ 1 & 0 & -\cos\left(\tau_{2}\theta_{\mathrm{ON}}\right) & -\sin\left(\tau_{2}\theta_{\mathrm{ON}}\right) \\ \sin\left(\tau_{\phi}\theta_{\mathrm{OFF}}\right) & -\cos\left(\tau_{\phi}\theta_{\mathrm{OFF}}\right) & 0 & \frac{1}{\sqrt{K_{2}}} \\ 0 & \frac{1}{\tau_{\phi}} & \frac{\sin\left(\tau_{2}\theta_{\mathrm{ON}}\right) - \sin\left(\tau_{2}\theta_{\mathrm{OFF}}\right)}{\tau_{2}} & \frac{\cos\left(\tau_{2}\theta_{\mathrm{OFF}}\right) - \cos\left(\tau_{2}\theta_{\mathrm{ON}}\right) - \frac{1}{K_{2}}}{\tau_{2}} \end{bmatrix}$$

(7)

(6)

where

$$C = \frac{A_2}{\tau_2} \sin(\tau_2 \theta_{\text{OFF}}) - \frac{B_2}{\tau_2} \cos(\tau_2 \theta_{\text{OFF}}) - K_2 \theta_{\text{OFF}}$$

$$+ P_2 \cos(\theta_{\text{OFF}} + \phi). \tag{11}$$

Applying KCL while the switching device is conducting, by combining (1) and  $i_o$ , gives the normalized current through the device

$$\frac{i_S(\theta)}{I_{\text{in}}} \bigg|_{\theta_{\text{ON}}^+ \le \theta \le \theta_{\text{OFF}}^-} = 1 - A_1 \cos(\tau_{\phi} \theta)

- B_1 \sin(\tau_{\phi} \theta) - \lambda \sin(\theta + \phi).$$

(12)

Applying the ZVS condition through (10) results in the following equation:

$$C(p,\phi) = P_2(p,\phi)\cos\phi + \frac{A_2(p,\phi)}{\tau_2(p)}\sin\left(\theta_{\text{ON}}^-\tau_2(p)\right)$$

$$-\theta_{\text{ON}}^-K_2(p) - \frac{B_2(p,\phi)}{\tau_2(p)}\cos\left(\theta_{\text{ON}}^-\tau_2(p)\right). \tag{13}$$

The drain current is equal to  $i_p$  at turn-ON, because of the discharge of the shunt capacitor. Hence, we can apply the condition of the drain current at turn-ON by using (9)

$$\frac{i_{S}^{ON}}{I_{in}} = K_{2}(p) + P_{2}(p)\sin\phi - A_{2}(p,\phi)$$

$$\cdot \cos\left(\theta_{ON}^{-}\tau_{2}(p)\right) - B_{2}(p,\phi)$$

$$\times \sin\left(\theta_{ON}^{-}\tau_{2}(p)\right) \tag{14}$$

where  $i_S^{\rm ON}$  is the drain current at turn-ON. Since the boundary-dependent parameters  $A, B_{1,2}(p,\phi)$  are interconnected, in this work, we solve the combined system of  $A, B_{1,2}$ , (13), and (14) using the trust-region-dogleg algorithm described in [28], [29].

The input voltage is equal to the mean of the drain voltage, hence  $C_p = \omega V_{\rm in}/(aI_{\rm in})$ . Using the definition of the loading parameter [30], we get  $C_\phi = pC_p/(\lambda-p)$ . The  $\phi$ -branch inductor is calculated from the resonance frequency,  $L_\phi = (\omega \tau_\phi)^{-2} C_\phi^{-1}$ .

Following the convention proposed in [19], we define  $u_X$  as the fictitious voltage across the residual series reactance  $X=\omega L_{s_1}-(\omega C_s)^{-1}$  of the load network at  $f_S$  (X is assumed to be infinite at any other frequency), since  $C_s$  and  $L_{s_1}$  are not exactly at resonance. We also define the voltage  $u_1$  as the combined effect of voltage across  $R_{sL}$  ( $u_{R_{sL}}$ ) and  $u_X$ . The magnitude of  $u_1$  is equal to the Fourier component of  $u_{DS}$  at  $f_S$ , which results in the relation

$$\pi B_C \lambda R_{sL} \sqrt{1 + \tan^2 \psi} = K_2 f_1(\psi) + P_2 f_2(\psi) + \frac{A_2}{2\tau_2} f_3(\psi) + \frac{B_2}{2\tau_2} f_4(\psi) \quad (15)$$

where  $\psi$  is the phase difference between  $i_o$  and  $u_1$ , and

$$f_1(\psi) = \sin(\phi + \psi) - (\theta_{\text{ON}}^- - \theta_{\text{OFF}}) \cos(\phi + \psi) - \sin(\theta_{\text{OFF}} + \phi + \psi)$$

(16)

$$f_2(\psi) = \frac{\cos(2\phi + \psi)}{4} - \pi (1 - D)\sin\psi$$

$$+ \frac{\cos(2\theta_{\text{OFF}} + 2\phi + \psi)}{4} - \frac{\cos(\theta_{\text{OFF}} - \psi)}{2} \\

+ \frac{\cos\psi}{2} - \frac{\cos(\theta_{\text{OFF}} + 2\phi + \psi)}{2} \tag{17}$$

$$f_3(\psi) = \frac{\sin((\tau_2 + 1)\theta_{\text{ON}}^- + \phi + \psi)}{\tau_2 + 1} \\

+ \frac{\tau_2 \sin((\tau_2 + 1)\theta_{\text{OFF}} + \phi + \psi)}{\tau_2 + 1} \\

+ \frac{\tau_2 \sin((\tau_2 - 1)\theta_{\text{OFF}} - \phi - \psi)}{\tau_2 - 1} \\

- \frac{\sin((\tau_2 - 1)\theta_{\text{ON}}^- + \phi + \psi)}{\tau_2 - 1} \\

- \sin(\tau_2\theta_{\text{OFF}} + \phi + \psi) - \sin(\tau_2\theta_{\text{OFF}} - \phi - \psi) \tag{18}$$

$$f_4(\psi) = \frac{\tau_2 \cos((1 - \tau_2)\theta_{\text{ON}} + \phi + \psi)}{1 - \tau_2} \\

- \frac{\cos((1 - \tau_2)\theta_{\text{ON}}^- + \phi + \psi)}{1 - \tau_2} \\

- \frac{\tau_2 \cos((\tau_2 + 1)\theta_{\text{ON}}^- + \phi + \psi)}{\tau_2 + 1} \\

- \frac{\cos((\tau_2 + 1)\theta_{\text{ON}}^- + \phi + \psi)}{\tau_2 + 1} \\

- \cos(\tau_2\theta_{\text{OFF}} - \phi - \psi) + \cos(\tau_2\theta_{\text{OFF}} + \phi + \psi). \tag{19}$$

The series load capacitance is derived from X,  $C_s = (\omega L_{s_1} - R_{sL} \tan \psi)^{-1} \omega^{-1}$ , where  $\psi$  is calculated by solving (15) using a combination of bisection, secant, and inverse quadratic interpolation methods described in [31], [32].

The normalized voltage across the Tx coil is

$$\frac{u_o(\theta)}{V_{\text{in}}} = \frac{B_C \lambda}{a} \left( \omega L_{s_1} \cos \left( \theta + \phi \right) + R_{sL} \sin \left( \theta + \phi \right) \right). \tag{20}$$

The minimum impedance value of the input choke must be substantially higher than the input resistance of the inverter [21],  $L_{\rm rfc}\gg R_{\rm in}/\omega$ , where  $R_{\rm in}=\lambda^2 R_{sL}/2$ . For the special case of the inverter with a finite dc-feed inductance and  $50\,\%$  duty cycle, the input inductance value can be calculated using the expression proposed in [33] combined with  $R_{\rm in}$ .

### B. Measurements and Numerical Example

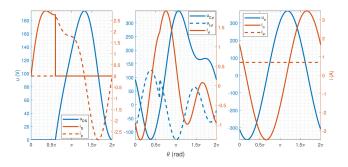

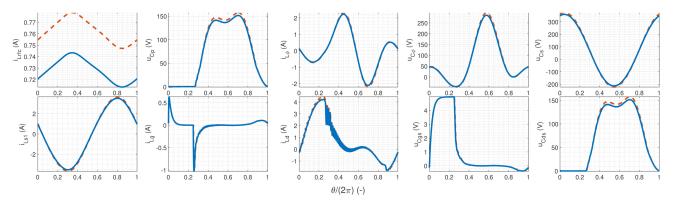

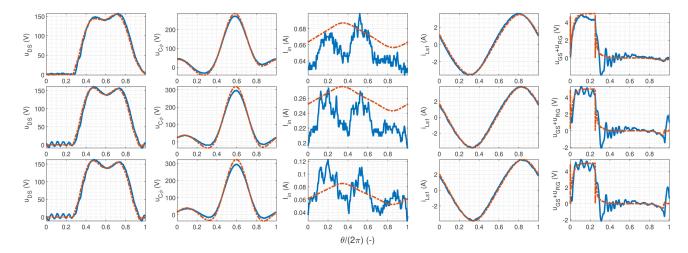

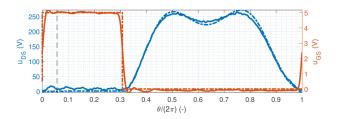

The application of the FO tuning equations is presented in the numerical example below. This example is further developed and improved in the following sections of this article. The inputs that were chosen to define the circuit properties are given in Table I, along with the corresponding outputs of the algorithm. The waveforms across various parts of the circuit shown in Fig. 2 are given in Fig. 3.

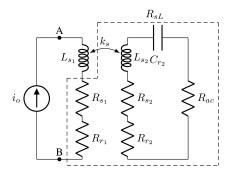

The complete WPT system of the experimental setup is shown Fig. 4 [34]. The inverter is represented as a current source connected to the Tx coil and the Receiver (Rx) coil ( $L_{s_2}$ ) is

|         | Quantity                                                 | Value                                   | Unit               |

|---------|----------------------------------------------------------|-----------------------------------------|--------------------|

|         | _ ` '                                                    | 50                                      | W                  |

|         | $P_o$                                                    |                                         | VV                 |

|         | $	au_{\phi}$                                             | 2                                       | _                  |

|         | $\lambda$                                                | 5                                       | _                  |

|         | $i_S^{ m ON}$                                            | 0                                       | A                  |

| Inputs  | $R_{sL}$                                                 | 8.6                                     | Ω                  |

| inputs  | $R_{s_1}$                                                | 346                                     | $\mathrm{m}\Omega$ |

|         | $L_{s_1}$                                                | 1.24                                    | $\mu H$            |

|         | $f_S$                                                    | 13.56                                   | MHz                |

|         | D                                                        | 30                                      | %                  |

|         | Boundaries                                               | $\left\{ i_{\phi},u_{C_{\phi}}\right\}$ | _                  |

| Outputs | $V_{in}$                                                 | 78.835                                  | V                  |

|         | $C_p$                                                    | 228.971                                 | pF                 |

|         | $egin{array}{c} C_p \ L_\phi \ C_\phi \ C_s \end{array}$ | 536.941                                 | $_{ m nH}$         |

|         | $C_{\phi}$                                               | 64.141                                  | pF                 |

|         | $C_{\circ}$                                              | 150.317                                 | pF                 |

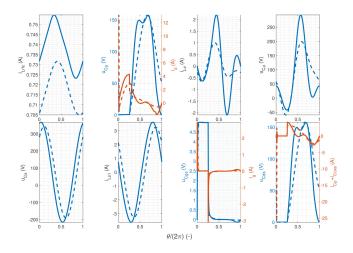

Fig. 3. Inverter waveforms of the numerical example given in Table I. The voltages are shown in blue on the left-hand-side vertical axes of the graphs and the currents in orange on the right-hand side. The parts of the circuit each individual waveform corresponds to are given in Fig. 2. The graph on the left shows the shunt network waveforms, the middle graph represents the  $\phi$ -branch, and the graph on the right has the input–output waveforms.

Fig. 4. WPT link with a current source as inverter, series secondary tuning capacitor, and ac load.

connected to an ac load  $(R_{\rm ac})$  via a series tuning capacitor  $(C_{s_2})$ ,  $k_s$  is the coupling factor and  $R_{r_{1/2}}$  is the radiation resistance of the Tx and Rx, respectively.

$R_{\rm ac}$  consists of 12 LTO100F100R0JTE3 AC resistors in parallel. Because of the relatively low value of  $R_{\rm ac}$  we opt for a series-tuned secondary [5], where the theoretical value of the tuning capacitor is  $C_{s_2}=(\omega^2L_{s_1})^{-1}$  since the two coupled coils are identical in our setup, whereas the generalized computation

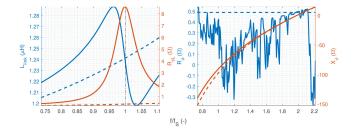

Fig. 5. Inductance and series resistance measurement of the fully loaded (solid line) and unloaded (dashed line) IPT link (left), and total series resistance and reactance measurements (solid line) and fitting curves (dashed line) of the  $\phi$ -branch with impedance analyzer, where  $X_\phi^{\rm fit}(f)=(2\pi f L_\phi C_\phi-1)/2\pi f C_\phi.$

of the tuning capacitors is given in [35]. The WPT coils consist of two planar spiral turns made of FR-4 printed circuit board (PCB) with maximum outer radius  $r_o=10.5\,\mathrm{cm}$ , minimum inner radius  $r_i=6.75\,\mathrm{cm}$ , track width of 1 cm, across distance  $d_s=12\,\mathrm{cm}$  with zero lateral misalignment and angle. An estimation of the order of magnitude of the radiation resistances of the coils based on the size and geometry mentioned above, based on [36], gives  $R_{r_{1/2}}\approx 1.137\,\mathrm{m}\Omega$ .

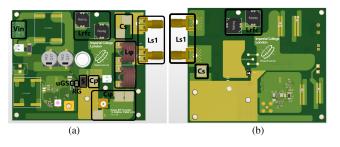

The impedance measurements of the fully loaded ( $k_S = k_S^{\text{max}}$ ) and unloaded ( $k_S = 0$ ) IPT link taken with an impedance analyzer (E4990 A Impedance Analyzer from Keysight Technologies) across the points A and B in Fig. 4 are provided in Fig. 5. The value of  $C_{s_2}$  was manually adjusted using the tuning method described in [37] starting from the theoretical value. The measurements were taken from the empty inverter board with only the Tx coil soldered in place. This way, the adjustment of  $C_{s_2}$ , which in our setup are  $3 \,\mathrm{kV}$  COG capacitors, naturally incorporates the stray inductances and capacitances of the PCB and the rest of the passive components, and the measurements represent the effective values of the circuit components. If a parasitic extraction tool is available, the incorporation of their effect can be done a posteriori in the calculations with the individual component values; however, the abovementioned method of measurements gave the most accurate results when compared to the theoretical predictions.

The numerical values of the equivalent series resistances in the measurements of Fig. 5 and Table I are several orders of magnitude larger than  $R_{\tau_{1,2}}$ , and thus their effect can be considered negligible. An analytical approximation of the Tx inductance can be derived by [38],  $L_{s_1}\approx 1.062\,\mu\mathrm{H}$ . This estimation agrees with the measurements of Fig. 5, if we take into consideration and add the effects of the stray inductances of the SMA connectors. The coupling factor is calculated using the formula in [37] and the experimental measurements as inputs,  $k_s^{\mathrm{max}}\approx 8.011\,\%$ . It must be noted at this point that the link was neither optimized for radiation [36], nor gain [39].

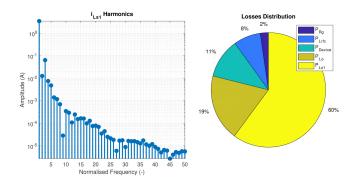

The aim of this inverter circuit example is to achieve maximum efficiency at the lower ISM bands. In order to be able to measure ac current accurately, we limit the output power within the capabilities of the current probe at these frequencies, namely Keysight N2783B. We set the  $\phi$ -branch to resonate at double the switching frequency to reduce THD [5], [40]. We minimize the ohmic losses by reducing the currents and increasing the

(23)

voltages in the circuit through a high  $\lambda$  value. Additionally, we minimize the switching device losses by applying zero derivative switching (ZDS), despite that this condition will result in nonload-independent operation, as defined in [10]. The duty cycle was chosen based on [10]. The output power capability and distribution of device stress are mainly determined by  $\lambda$  and D; high  $\lambda$  and low D increase the current demands and decrease the voltage requirements and vice versa. The boundaries were selected according to the signals that we want to simulate more accurately.

By comparing the input requirements in Table I with the waveforms in Fig. 3, we can verify that all the desired properties of inverter are met. The limitation of the applied boundary conditions is revealed through the discontinuity during switching of  $u_{L_{\phi}}$ .

#### IV. STATE-SPACE TUNING

Analytical expressions for designing Class E inverters at any load network Q have been derived in [41], [42]. An alternative approach of deriving design equations based on fitting datasets is presented in [14]. Search optimization algorithms based on the more accurate linear SS simulation of the circuit have also been used for defining the passive component values of the inverter [8], [30], [43], with the downside that such numerical approaches provide limited insights and control of the tuning process to the user, do not provide such a broad range of design input parameters, are relying on random initial parameters to run, and are usually computationally demanding and provide no guarantee of a practically realizable design output. An extension to traditional FO design methods is proposed in [44] using higher order analysis but some of the design component values need to be set initially, which may be problematic.

The second tuning step of the proposed algorithm uses a piece-wise SS representation for the formulation of the problem. However, instead of using a predefined optimization tool for the design process, we develop a custom Newton-based iterative method, starting from the solution of the previous step. The SS simulation resolves the approximation errors of the FO analysis and the aim of the numerical optimization is to fine-tune the inverter while maintaining the required design properties. The advantages in modeling accuracy of the SS approach compared to FO approximations in Class E converters are demonstrated in [45], [46].

#### A. Simulation Equations

At this part of the algorithm, we replace the infinite choke with its actual measured value, and we model the switching device as a variable resistance  $R_S^{\rm ON/OFF}$ . Also, as shown in Fig. 6, we incorporate the series resistance  $R_{\rm rfc}$  of the input choke, and Q factor of the  $\phi$ -branch through the parameter  $p_{\phi} \equiv$  $au_{\phi}\omega/Q_{L_{\phi}}(f)|_{f= au_{\phi}f_{S}}$ , since  $R_{\phi}=p_{\phi}L_{\phi}$  is proportionate to the windings  $L_{\phi}$ .

The sixth-order system of linear SS differential equations of the inverter is solved separately for the ON/OFF periods, in a

Fig. 6. Circuit diagram of Class EF/Φ inverter using the state-space formulation.

piece-wise linear manner, and its solution is given by

$$\mathbf{q}(\theta)|_{\theta_{\text{ON/OFF}}^{+} \leq \theta \leq \theta_{\text{OFF/ON}}^{-}}$$

$$= e^{\left(\theta - \theta_{\text{ON/OFF}}^{+}\right)\mathbf{A}_{\text{ON/OFF}}} \cdot \mathbf{q}\left(\theta_{\text{ON/OFF}}\right) + \mathbf{A}_{\text{ON/OFF}}^{-1}$$

$$\cdot \left(e^{\left(\theta - \theta_{\text{ON/OFF}}^{+}\right)\mathbf{A}_{\text{ON/OFF}}} - \mathbf{I}\right)\mathbf{b}$$

(21)

where I is the identity matrix,  $\mathbf{b} = V_{\text{in}}(\omega L_{\text{rfc}})^{-1}\mathbf{e}_1$  with  $\mathbf{e}_i$  being the single-entry column vector whose ith element is one and the rest are zero, and the state matrix and vector are defined as follows:

$$\mathbf{A}_{\text{ON/OFF}} = \frac{1}{\omega} \text{diag}^{-1} \left( L_{\text{rfc}}, C_p, L_{\phi}, C_{\phi}, C_s, L_{s_1} \right)$$

$$\begin{bmatrix} -R_{\text{rfc}} & -1 & 0 & 0 & 0 & 0 \\ 1 & \frac{-1}{R_S^{\text{ON/OFF}}} & -1 & 0 & 0 & -1 \\ 0 & 1 & -R_{\phi} & -1 & 0 & 0 \\ 0 & 0 & 1 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 & 1 \\ 0 & 1 & 0 & 0 & -1 & -R_{sL} \end{bmatrix}$$

$$\mathbf{q}(\theta) = \begin{bmatrix} i_{L_{\text{rfc}}}(\theta) \ u_{C_p}(\theta) \ i_{L_{\phi}}(\theta) \ u_{C_{\phi}}(\theta) \\ u_{C_s}(\theta) \ i_{L_{C_s}}(\theta) \end{bmatrix}^T.$$

(22)

The boundary continuation conditions when the switching device is turning ON and OFF during one period are calculated by applying the Schur complement [47]:  $[\mathbf{q}(\theta_{\text{ON}}), \mathbf{q}(\theta_{\text{OFF}})]^T =$  $\mathbf{C}^{-1}\mathbf{E}$ , where

$$\mathbf{E} = \begin{bmatrix} \mathbf{A}_{\text{OFF}}^{-1} \left( e^{\left(\theta_{\text{ON}}^{-}-\theta_{\text{OFF}}\right) \mathbf{A}_{\text{OFF}}} - \mathbf{I} \right) \mathbf{b} \\ \mathbf{A}_{\text{ON}}^{-1} \left( e^{\theta_{\text{OFF}} \mathbf{A}_{\text{ON}}} - \mathbf{I} \right) \mathbf{b} \end{bmatrix}$$

$$\mathbf{C}^{-1} = \begin{bmatrix} \left[ \mathbf{I} - e^{\left(\theta_{\text{ON}}^{-}-\theta_{\text{OFF}}\right) \mathbf{A}_{\text{OFF}}} e^{\theta_{\text{OFF}} \mathbf{A}_{\text{ON}}} \right]^{-1} \\ \mathbf{0} \end{bmatrix}$$

(24)

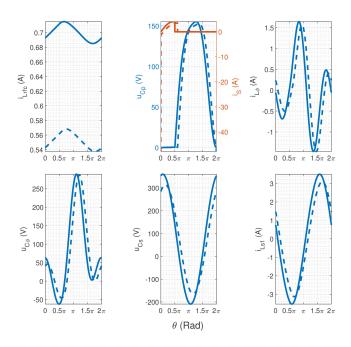

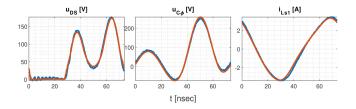

Fig. 7. Simulation of the Class  $EF_2$  inverter waveforms using state-space formulation. The dashed line is used to represent the design that occurs from the FO tuning method and the solid line shows the state-space tuned inverter.

$$\times \begin{bmatrix} \mathbf{0} \\ \mathbf{I} - e^{\theta_{\text{OFF}}} \mathbf{A}_{\text{OFF}} e^{\left(\theta_{\text{ON}}^{-} - \theta_{\text{OFF}}\right)} \mathbf{A}_{\text{OFF}} \end{bmatrix}^{-1}$$

$$\cdot \begin{bmatrix} \mathbf{I} \\ e^{\theta_{\text{OFF}}} \mathbf{A}_{\text{ON}} \end{bmatrix}$$

$$(25)$$

and 0 is the zero matrix. The current through the switching device is given by the relation

$$i_S(\theta)|_{\theta_{\text{ON/OFF}}^{+/-} \le \theta \le \theta_{\text{OFF/ON}}^{+/-}} = \frac{u_{C_p}(\theta)}{R_S^{\text{ON/OFF}}}.$$

(26)

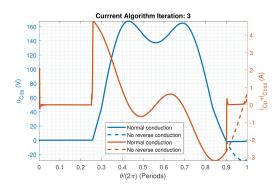

Simulating the inverter with (21) gives a more accurate and realistic representation of the operation of the circuit (Fig. 7) compared to the FO formulation, since the assumptions and simplifications that are incorporated in the FO equations are no longer present in the SS approach. By comparing the waveforms in Fig. 3 with the equivalent part of Fig. 7, neither the required design properties of Table I nor the soft switching conditions are met, and further tuning is required.

The additional input parameters needed for the SS simulation in Fig. 7, along with the ones in Table I, are given in Table II.  $I_m$  is calculated in the previous tuning step, as described in Section III-A, and the rest of the input values are based on the component selection of the experimental setup, which are more thoroughly presented and justified in Section IV-C. Specifically for the input choke, the impedance value chosen in Table II is around 57 times higher than the FO input resistance of the inverter, which practically acts as an infinite choke. The input component values for this stage of the algorithm are not limited only to the ones produced by our proposed first tuning step, but can be derived by any arbitrary design algorithm for Class EF inverters that

TABLE II INPUTS AND OUTPUTS OF STATE-SPACE CLASS  $\mathrm{EF}_2$  TUNING EXAMPLE

|                 | Quantity                    | Value           | Unit                    |

|-----------------|-----------------------------|-----------------|-------------------------|

|                 | $I_m$                       | 3.481           | A                       |

|                 | $L_{rfc}$                   | 72              | $\mu H$                 |

| Inputs*         | $R_{rfc}$                   | 500             | ${ m m}\Omega$          |

| inputs          | $R_{rfc}$ $R_S^{ m ON}$     | 100             | ${ m m}\Omega$          |

|                 | $R_S^{ m OFF}$              | 650             | $M\Omega$               |

|                 | $p_{\phi}$                  | $1 \times 10^6$ | $\Omega\mathrm{H}^{-1}$ |

|                 | $V_{in}$                    | 75.7            | V                       |

| Outputs         | D                           | 25.169          | %                       |

| Outputs         | $C_p$                       | 284.559         | $_{ m pF}$              |

|                 | $C_s$                       | 143.166         | pF                      |

|                 | $\delta\left(V_{in}\right)$ | -3.977          | %                       |

| Relative change | $\delta(D)$                 | -16.103         | %                       |

| Kelative change | $\delta\left(C_{p}\right)$  | 21.277          | %                       |

|                 | $\delta(C_s)$               | -4.757          | %                       |

<sup>\*</sup>The inputs given in this table are in addition to the data of Table I.

needs additional correction, as long as the formulation of input conditions matches, such as the special cases discussed in [10].

#### B. Iterative Tuning Process

In this section, we introduce a tuning method using the SS representation in order to correct the inaccuracies caused by the FO formulation. We choose to keep the  $\phi$ -branch unaltered and adjust the rest of the control parameters accordingly to reassure that the circuit is operating as defined by the input parameters in Table I. This corresponds to readjusting  $P_o, \lambda, u_{C_p}(\theta_{\rm ON}^-)$ , and  $i_S^{\rm ON}$  at their desired values by optimizing for  $V_{\rm in}, D, C_p$ , and  $C_s$ .

The input voltage determines the output current and hence power.  $C_s$  sets the load network impedance, which primarily defines  $\lambda$  but also shapes the drain voltage waveform.  $C_p$  and D also shape the drain voltage, with the first one mainly contributing to the value at turn-ON and the latter mostly affecting the derivative. Changing the combination of  $L_\phi$ - $C_\phi$  while keeping  $\tau_\phi$  constant also affects the drain voltage shape, however including them as independent variables in the iterative scheme impacts the convergence negatively and makes it uncontrollable.

The state vector formulation in (21) is defined in terms of matrix exponentials, which is not a convenient form for dealing with the output current characteristics. By approximating the output current waveform using the sine wave fit algorithm proposed in [48], we can solve for peak output current as well as minimize the THD. The sine coefficients of the fitted waveforms are  $y_n = z_1 \cos \theta_n + z_2 \cos \theta_n + z_3$ , where n = 1, 2, ..., N, N is the waveform discretization number,  $\mathbf{z} = [\mathbf{D}^T \mathbf{D}]^{-1} \mathbf{D}^T \mathbf{y}$ ,  $\mathbf{y} = [i_{L_{s_1}}(\theta_1), ..., i_{L_{s_1}}(\theta_N]^T, \theta_n = (n-1)2\pi/(N-1)$ , and

$$\mathbf{D} = \begin{bmatrix} \cos \theta_1 & \sin \theta_1 & 1 \\ \cos \theta_2 & \sin \theta_2 & 1 \\ \vdots & \vdots & \vdots \\ \cos \theta_n & \sin \theta_n & 1 \end{bmatrix}. \tag{27}$$

We define the following system of nonlinear equations in the form of a vector function:

$$\mathbf{f}(\mathbf{x}) = \left[ u_{C_p} \left( \theta_{\text{ON}}; \mathbf{x} \right) \ i_{C_p} \left( \theta_{\text{ON}}^-; \mathbf{x} \right) - i_S^{\text{ON}} \right]$$

$$\sqrt{z_1^2(\mathbf{x}) + z_2^2(\mathbf{x})} - I_m \ z_3(\mathbf{x})$$

$$\frac{\max_{\theta} \left| i_{L_{s_1}} \left( \theta; \mathbf{x} \right) \right|}{I_{L_{\text{rfc}}}(\mathbf{x})} - \lambda \right]^T$$

(28)

where  $\mathbf{x} = [C_p,\ D,\ V_{\rm in},\ C_s]^T$ ; and  $I_{L_{\rm rfc}}$  is the dc component of  $i_{L_{\rm rfc}}$ , which can be obtained either arithmetically, e.g., through the trapezoidal rule [49], or by analytically integrating (21). The peak output current in the fifth element of (28) can be calculated by setting the derivative of (21) to zero. The circuit design resulting from the solution of (28) corresponds to the required conditions for ideal tuned operation of the Class  $\mathrm{EF}/\Phi$  inverter, based on the inputs in Table I. More specifically, the first component of (28) is the ZVS condition, the second one sets the slope of the drain voltage at turn-ON to the desired value, the third condition sets the output current amplitude according to  $P_o$ , and the fifth component controls  $\lambda$ . The fourth component of (28) is the dc part of  $i_{L_{s_1}}$  and combined with the third component result in reducing THD, when satisfied.

We solve (28) using the combined gradient-descent and Newton's method iterative algorithm mentioned in [50]

$$\mathbf{x}^{(m+1)} = \mathbf{x}^{(m)} - \left\{ \gamma \left( a_N \left[ \mathbf{J}_{\mathbf{f}}^T \mathbf{J}_{\mathbf{f}} \left( \mathbf{x}^{(m)} \right) \right]^{-1} - a_{GD} \mathbf{I} \right) + a_{GD} \mathbf{I} \right\} \mathbf{J}_{\mathbf{f}}^T \left( \mathbf{x}^{(m)} \right) \mathbf{f} \left( \mathbf{x}^{(m)} \right)$$

(29)

where m denotes the iteration index,  $\gamma$  is the mixing parameter of Newton's and gradient-descent methods,  $a_N$  and  $a_{GD}$  are the respective converging coefficients and  $\mathbf{J_f}$  is the Jacobian matrix of  $\mathbf{f}$  with respect to  $\mathbf{x}$ . The condition that needs to be satisfied for the termination of the iterative process in (29) is  $\|\mathbf{x}^{(m} - \mathbf{x}^{(m-1)}\|_{\infty}/\|\mathbf{x}^{(m)}\|_{2} < \epsilon$ , where  $\epsilon$  is the error tolerance.

The partial derivatives of the Jacobian components that cannot be directly computed, i.e., the exponential derivatives with respect to  $C_p$  and  $C_s$ , can be calculated by any combination of the methods described in [51], [52]. The method described in [51] uses the complex step derivative approach and is simpler to implement as well as less computationally demanding compared to the one in [52]. However, the approach of [52], which is based on matrix diagonalization, provides a better insight on the actual analytic equation of the derivative. We provide below the exact equations of these terms for both approaches, where the subscripts "CS" and "MD" denote the complex step and the matrix diagonalization derivatives, respectively

$$\frac{\partial_{\mathrm{CS}} \mathrm{e}^{\left(\theta - \theta_{\mathrm{ON}/\mathrm{OFF}}^{+}(\mathbf{x})\right) \mathbf{A}_{\mathrm{ON}/\mathrm{OFF}}(\mathbf{x})}}{\partial C_{p/s}} \bigg|_{\mathbf{x} = \mathbf{x}^{(m)}}$$

$$= \frac{\operatorname{Im}\left(e^{\left(\theta - \theta_{\text{ON/OFF}}^{+}\left(\mathbf{x}^{(k)}\right)\right)\mathbf{A}_{\text{ON/OFF}}\left(\mathbf{x}^{(m)} + jh\mathbf{e}_{1/4}\right)}\right)}{h}$$

$$\frac{\partial_{\text{MD}}e^{\left(\theta - \theta_{\text{ON/OFF}}^{+}\left(\mathbf{x}\right)\right)\mathbf{A}_{\text{ON/OFF}}\left(\mathbf{x}\right)}}{\partial C_{p/s}} = \mathbf{X}_{\text{ON/OFF}}\left(\mathbf{x}\right)$$

$$\cdot \mathbf{V}_{p/s}^{\text{ON/OFF}}\left(\mathbf{x};\theta\right)\mathbf{X}_{\text{ON/OFF}}^{-1}\left(\mathbf{x}\right)$$

(31)

where j is the imaginary unit and h is an infinitesimal positive number [51].  $\mathbf{X}_{\mathrm{ON/OFF}}$  is the matrix whose ith column is a right eigenvector corresponding to the eigenvalue  $d_i^{\mathrm{ON/OFF}}$  of  $\mathbf{A}_{\mathrm{ON/OFF}}$ :  $\mathbf{A}_{\mathrm{ON/OFF}} = \mathbf{X}_{\mathrm{ON/OFF}} \mathbf{D}_{\mathbf{A}}^{\mathrm{ON/OFF}} \mathbf{X}_{\mathrm{ON/OFF}}$ , where  $\mathbf{X}_{\mathrm{ON/OFF}}$  and  $\mathbf{D}_{\mathbf{A}}^{\mathrm{ON/FF}} = \mathrm{diag}(d_1^{\mathrm{ON/OFF}}, \ldots, d_6^{\mathrm{ON/OFF}})$  can be calculated using the QZ decomposition method [53]. The individual entries of  $\mathbf{V}_{p/s}^{\mathrm{ON/OFF}}$  are given by

$$V_{p/s}^{\text{ON/OFF}}[i,j](\mathbf{x};\theta) = \begin{cases} G_{p/s}^{\text{ON/OFF}}[i,j](\mathbf{x}) \left( e^{\left(\theta - \theta_{\text{ON/OFF}}^{+}(\mathbf{x})\right)} d_{i}^{\text{ON/OFF}}(\mathbf{x}) \right) \\ -e^{\left(\theta - \theta_{\text{ON/OFF}}^{+}(\mathbf{x})\right)} d_{j}^{\text{ON/OFF}}(\mathbf{x}) \end{pmatrix} / \left( d_{i}^{\text{ON/OFF}}(\mathbf{x}) \right) \\ -d_{j}^{\text{ON/OFF}}(\mathbf{x}) , i \neq j \\ G_{p/s}^{\text{ON/OFF}}[i,i](\mathbf{x}) \left( \theta - \theta_{\text{ON/OFF}}^{+}(\mathbf{x}) \right) \\ \cdot e^{\left(\theta - \theta_{\text{ON/OFF}}^{+}(\mathbf{x})\right)} d_{i}^{\text{ON/OFF}}(\mathbf{x}) , i = j \end{cases}$$

(32)

where

$$\mathbf{G}_{p/s}^{\text{ON/OFF}}(\mathbf{x}) = \mathbf{X}_{\text{ON/OFF}}^{-1}(\mathbf{x}) \frac{\partial \mathbf{A}_{\text{ON/OFF}}(\mathbf{x})}{\partial C_{p/s}}$$

$$\cdot \mathbf{X}_{\text{ON/OFF}}(\mathbf{x}). \tag{33}$$

### C. Class EF<sub>2</sub> Inverter Tuning Example

In this subsection, we further improve the numerical example of the Class EF<sub>2</sub> inverter presented in Section III-B of this work by using the SS formulation. The additional inputs needed for the computational process, to the ones given in Table I, as well as the resulting adjusted component values with their relative change to the previous tuning step, are given in Table II. The inductance of the choke was measured using the method described in Section III-B at  $f_S$  and its series resistance was measured with a multimeter (Keysight 34465 A Digital Multimeter), since the input current is mostly dc. Based on the peak of the drain voltage and current waveforms in Fig. 3 as well as the switching frequency requirements, the switching device of choice is the GS66504B from GaN Systems, which is where the ON and OFF resistances in Table II were derived. The value of  $p_{\phi}$  was based on the properties of the air-core inductors at  $\tau_{\phi}f_{S}$  used in the  $\phi$ -branch [3]. The waveforms of the improved design are shown in Fig. 7 displayed in solid line, compared to the ones from the FO tuning method, shown with dashed lines.

In this example, we calculated  $I_{L_{\rm rfc}}$  numerically and used the pure Newton version of (29). For the Jacobian computation, we

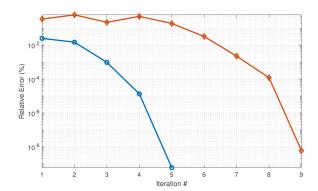

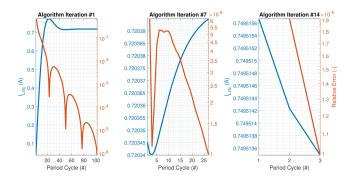

Fig. 8. Convergence progression of the termination condition. The blue circles correspond to the Class  $EF_2$  and the orange diamonds to the Class  $\phi_2$  inverter examples presented in this article.

TABLE III INPUTS AND OUTPUTS OF STATE-SPACE CLASS  $\Phi_2$  Tuning Example

|                 | Quantity                    | Value   | Unit |

|-----------------|-----------------------------|---------|------|

| Inputs*         | $L_{rfc}$                   | 600     | nΗ   |

|                 | $V_{in}$                    | 77.068  | V    |

| Outputo         | D                           | 20.817  | %    |

| Outputs         | $C_p$                       | 515.532 | pF   |

|                 | $C_p$ $C_s$                 | 142.641 | pF   |

|                 | $\delta\left(V_{in}\right)$ | -2.368  | %    |

| Relative change | $\delta(D)$                 | -30.61  | %    |

| Relative change | $\delta\left(C_{p}\right)$  | 125.152 | %    |

|                 | $\delta\left(C_{s}\right)$  | -5.107  | %    |

<sup>\*</sup>The inputs given in this table are in addition to the data of Tables I and II.

implemented the approach in (30). The iterative progression of the solution convergence of (28) is shown in Fig. 8. Apart from  $I_m$ , which was calculated in the previous tuning step, the choice of the component values in Table II is based on their experimental measurements and datasheets.

#### *D.* Class $\Phi_2$ Inverter Tuning Example

As mentioned in Section I, in this section, we show the design of a Class  $\Phi_2$  inverter in order to demonstrate the versatility and the design possibilities that the proposed SS tuning method can provide. In the numerical example in Section IV-C, the inductance of the input choke is large enough so that it can be regarded as infinite. However, by reducing the value of the choke inductance, relative to the inverter input resistance, we get closer to the Class  $\Phi_2$  operation.

The inputs and outputs for the Class  $\Phi_2$  inverter design example are given in Table III, in addition to the component values required from Tables I and II. Here, the impedance of the input choke is half of the input resistance and the condition for infinite input choke operation does not apply. The progress of the convergence procedure is shown in Fig. 8. The FO inverter design that is used as an initial point for the iterative process is again the one mentioned in Section III-B. The waveforms of the SS variables in Fig. 6 before and after the application of the SS tuning method are shown in Fig. 9.

Fig. 9. Simulation of the Class  $\Phi_2$  inverter waveforms using state-space formulation. The dashed line is used to represent the design that occurs from the FO tuning method, the dashed-dotted line shows the FO design with an antiparallel diode incorporated into the device, and the solid line shows the state-space tuned inverter. The negative limit of the  $i_S$  overshoot in the graph is not shown to its full amplitude for improved readability and scaling, since it does not provide any meaningful information.

As expected, the FO method is even more inaccurate when using a finite input choke, since it is based on an infinite input choke assumption. This limitation is reflected in the difference of the waveforms shapes before and after tuning in Fig. 9 as well as the mismatch of the corresponding parts of Figs. 3 and 9. Also, the tuning process was slower compared to the Class  $EF_2$ , as shown in Fig. 8, mostly because the FO initial point of the iterative method is by definition less suitable for the Class  $\Phi$  inverter design. However, the algorithm still manages to produce an inverter design that complies with (28).

#### E. Simulation of the Device Anti-Parallel Diode

As shown in Figs. 7 and 9, simulating the circuit in Fig. 6 using (21) with the switching boundaries does not incorporate the effect of the reverse conducting diode, which is an intrinsic property of power MOSFETS [54] and high-electron-mobility transistor (HEMTs), since the device is blocking both positive and negative current when turned OFF. The impact of the antiparallel diode to the behavior of the circuit can be included by adding to the a priori known switching boundary conditions the points in time where  $u_{C_p}$  changes polarity during turn-OFF. However, the process of figuring out the parts of the period during which the reverse diode is conducting is not straightforward and requires a dynamic calculation approach. In this subsection, we propose

Fig. 10. Flowchart of the algorithm proposed in Section IV-E for simulating the effect of the intrinsic reverse conducting diode of the switching device to the waveforms of the Class  $EF/\Phi$  inverter using the state-space formulation.

an iterative scheme, which is broken down in the flowchart in Fig. 10, for the calculation of the time points within a period where the reverse diode turns ON and OFF.

The algorithm begins by setting the inverter design with the corresponding component values and computing the state vector waveforms, as described in Section IV-A. The next step involves figuring out whether and when the drain voltage during turn-OFF changes polarity. Solving for the zeros of  $u_{C_p}$  is achieved first by splitting the waveform in a predefined number of equal pieces and checking forward in time if the boundaries of a part have opposing signs. If a waveform part crosses zero, we solve for that point using the two-point Newton method in [55], starting the iteration from the edge points. If, however, no such point exists in the entirety of the drain voltage during turn-OFF, the reverse diode is not conducting and the simulation process is terminated. Once we have solved for all the potential zero crossing points with the current boundary conditions, we readjust the boundary conditions accordingly for the next iteration. At every boundary condition, the conducting state of the device is switched.

The iterative process has converged once the boundary conditions have reached a steady equilibrium, which is applied using the normwise backward error for linear equations [56]

$$\frac{\|\mathbf{d} - \mathbf{A}_{n-1}\mathbf{c}\|_{\infty}}{\|\mathbf{A}_{n-1}\|_{\infty} \|\mathbf{c}\|_{1} + \|\mathbf{d}\|_{\infty}} < \epsilon$$

(34)

where

$$\mathbf{c} = \mathbf{q}(\theta_1) - e^{(\theta_n - \theta_{n-1})\mathbf{A}_{n-1}}\mathbf{q}(\theta_{n-1})$$

and  $\mathbf{d} = (e^{(\theta_n - \theta_{n-1})\mathbf{A}_{n-1}} - \mathbf{I})\mathbf{b}$ .

As an example for the demonstration of the algorithm in Fig. 10, we use the FO design with finite choke of Section IV-D, since the diode conduction part of the period is substantially larger compared to the corresponding Class  $EF_2$  design. The termination tolerance is  $10^{-6}$ . The resulting waveforms are shown in Fig. 9 and it took 4 iterations for the scheme in Fig. 10 to converge. The need for the iterative scheme in order to determine the reverse diode conducting regions becomes clear from Fig. 9, since the actual point in time that the antiparallel diode of the device begins to conduct does not match exactly the zero-crossing point of the nondiode drain waveform.

#### V. TUNING WITH A NONLINEAR DEVICE

Sections III and IV simulate the device behavior as an ideal switch and a variable resistor, respectively. However, power

MOSFETs have nonlinear parasitic capacitances [54], which not only introduce delays but also, specifically  $C_{\rm oss}$  for the cases of Class E [57] and Class EF inverters [58], are part of the shunt network and their effect should be taken into account in the tuning calculations in order to get accurate results. As we have already shown in Section IV, the FO approach is not suitable for Class EF/ $\Phi$  inverter designs, which means that the method proposed in [57] is not ideal for this case, and [58] is based on manual tuning and fitting of the waveforms along with experimental measurements. A numerical design procedure for Class E inverters at 50% duty cycle is presented in [13]; however, it is not directly applicable to Class EF inverters. If a detailed and extensive model of the parasitics of the device is not available, the iterative tuning method in our previous work [59] is a powerful option. However it does not incorporate the gate drive signal in the calculations and focuses only on maintaining ZVS, while the other properties of the circuit may be altered during the tuning process.

In this section, we propose an iterative tuning method, that will further adjust the design produced in Section IV so that it absorbs the unwanted effects of the device parasitics and the nonideal gate drive signal, while maintaining all the required input design properties. The circuit model of the device as well as the simulation equations derived in this section are generally applicable to any transistor. The same applies to the tuning methodology proposed, which is universal. However, since we are dealing with nonlinear effects uniquely defined by the specific semiconductor device used, the exact functions of the parasitics behavior need to be defined accordingly for each individual transistor model.

#### A. System Modeling

The circuit diagram of the Class EF inverter topology that is used for simulation in this section is, for the most part, the one shown in Fig. 6 with a different, more thorough and realistic, transistor model. The switching device is modeled as a nonlinear voltage-dependent current source along with a network of nonlinear voltage-dependent capacitances [60], [61] and temperature-dependent resistors, as shown in Fig. 11. The stray inductances caused by the packaging of the device are incorporated in the computations as inductors at the pins of the device.

Since the three capacitors in Fig. 11 form a delta network, only the voltages across two of them are considered independent SS variables. In this work, we choose  $u_{C_{gd}}$  to be the dependent one, which is related to the other two device capacitor voltages by the relation  $u_{C_{gd}}(\theta) = u_{C_{gs}}(\theta) - u_{C_{ds}}(\theta)$ . The same principle applies for the currents through the package inductances, which form a star network connected at a hypernode. The dependent variable of choice is  $i_{L_s}$ , which is given by the relation  $i_{L_s}(\theta) = i_{L_g}(\theta) + i_{L_d}(\theta)$ .

Applying KVL and KCL to the inverter with the nonlinear device model in Fig. 11 leads to the nonlinear 10th-order differential equation of the system given below

$$\omega \mathbf{M} (\mathbf{v}) \frac{\mathrm{d} \mathbf{v} (\theta)}{\mathrm{d} \theta} = \mathbf{U} (\mathbf{v}, u_{GS}, T) \mathbf{v} (\theta) + \mathbf{e}_1 V_{\mathrm{in}} + \mathbf{n} u_{GS} (\theta) + \mathbf{m} (\mathbf{v}) i_S (\mathbf{v}, T)$$

(35)

Fig. 11. Circuit diagram of a nonlinear model of the switching device in the Class  $EF/\Phi$  inverter, including parasitic capacitances and resistances, stray package inductances and input gate signal with ON/OFF resistors.

where T is the temperature of the device, (36) shown at the bottom of this page

$$\mathbf{M}(\mathbf{v}) = \operatorname{diag}(L_{\text{rfc}}, C_{p}, L_{\phi}, C_{\phi}, C_{s}, L_{s_{1}}, L_{gds}, L_{gds}, C_{gds}(\mathbf{v}), C_{gds}(\mathbf{v}))$$

(37)

$$\mathbf{v} = \begin{bmatrix} i_{L_{\text{rfc}}} & u_{C_{p}} & i_{L_{\phi}} & u_{C_{\phi}} & u_{C_{s}} & i_{L_{s_{1}}} \\ & \times i_{L_{g}} i_{L_{d}} & u_{C_{gs}} & u_{C_{ds}} \end{bmatrix}^{T}$$

(38)

$$\mathbf{n} = \begin{bmatrix} 0 & 0 & 0 & 0 & 0 & 0 & n_{ds} + 1 & -1 & 0 & 0 \end{bmatrix}^{T}$$

(39)

$$\mathbf{m}(\mathbf{v}) = \begin{bmatrix} 0 & 0 & 0 & 0 & 0 & 0 & 0 & m_{dg}(\mathbf{v}) - m_{gs}(\mathbf{v}) \end{bmatrix}^{T}$$

(40)

$$C_{gds}\left(\mathbf{v}\right) = m_{gs}\left(\mathbf{v}\right) \frac{\partial Q_{C_{ds}}\left(\mathbf{v}\right)}{\partial u_{C_{ds}}} + \frac{\partial Q_{C_{gs}}\left(\mathbf{v}\right)}{\partial u_{C_{gs}}} + \frac{\partial Q_{C_{gs}}\left(\mathbf{v}\right)}{\partial u_{C_{ds}}}$$

(41)

$$m_{ds}\left(\mathbf{v}\right) = \frac{\partial_{u_{C_{ds}}} Q_{C_{ds}}\left(\mathbf{v}\right)}{\partial_{u_{C_{gd}}} Q_{C_{gd}}\left(\mathbf{v}\right)} + 1 \tag{42}$$

$$m_{dg}\left(\mathbf{v}\right) = \frac{\partial_{u_{C_{ds}}} Q_{C_{gs}}\left(\mathbf{v}\right)}{\partial_{u_{C_{ad}}} Q_{C_{gd}}\left(\mathbf{v}\right)} - 1 \tag{43}$$

$$m_{gs}\left(\mathbf{v}\right) = \frac{\partial_{u_{C_{gs}}} Q_{C_{gs}}\left(\mathbf{v}\right)}{\partial_{u_{C_{gd}}} Q_{C_{gd}}\left(\mathbf{v}\right)} + 1 \tag{44}$$

where  $L_{gds}=(n_{ds}+1)L_g+L_d$ ,  $n_{gs}=L_g/L_s$ ,  $n_{ds}=L_d/L_s$ ,  $R_{\rm gate}(u_{GS})=R_G(u_{GS})+R_g$ ,  $Q_{C_{gs}}$ , and  $Q_{C_{ds}}$  and  $Q_{C_{gd}}$  are the electrical charges in of the corresponding capacitors of the circuit in Fig. 11, and  $R_G$  is the resistance for shaping the rise and fall of the gate signal of the switching device.

The input gate signal is determined by the characteristics of gate driver circuit used in the experimental setup, which in our case is the LMG1020, and is modeled as an ideal pulse wave

$$u_{GS}(\theta) = \{5 \text{ V}, 0 \le \theta < \theta_{OFF} 0 \text{ V}, \theta_{OFF} \le \theta < \theta_{ON}^{-}\}.$$

(45)

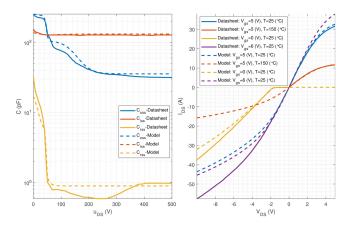

The effect of the temperature on the device operation was emulated by the internal drain and source temperature-dependent resistances  $R_{d/s}(T,T_n)$ , where  $T_n$  is the reference temperature, which are modeled using the linear FO approximation [62]. The equations of the capacitances and the current source in Fig. 11 are defined based on the small signal and dc MOSFET models described in [63]. The fitting of the drain and source resistances, the drain current, and the internal capacitors of the device on the datasheet curves is performed using the Levemberg–Marquardt damped least-squares method, described in [64] combined with information from reverse engineering the LTspice model provided by the manufacturer.

A demonstration of the visual fitting and comparison between some specially selected data from the datasheet measurements of the device and the abovementioned internal device component models is given in Fig 12. The chosen data curves are the ones quantitatively closest to our case study. A more detailed investigation of  $C_{\rm oss}$  losses in a device-level approach is presented in [65], [66].

Since (35) is a nonlinear system of differential equations, it cannot be solved analytically as in Section IV-A. For this reason, we approximate the solution of (35) using the numerical approach described in [67]. We define the application of the implicit Crank–Nicolson discretization formula via an arithmetic mean to (38):  $\mathbf{v}_{n+1/2}(\mathbf{v}_{n+1}) := (\mathbf{v}_{n+1} + \mathbf{v}_n)/2$ , where  $\mathbf{v}_n \equiv \mathbf{v}(\theta_n)$ . Substituting (38) with  $\mathbf{v}_{n+1/2}$  in (35), approximating the derivative with the FO terms of the Taylor series, and rearranging the terms appropriately result in  $\mathbf{g}(\mathbf{v}_{n+1}) =$

Fig. 12. Visual comparison of the dependence of the internal nonlinear capacitances (left) and the drain current (right) on the drain voltage between the datasheet and the fitted model curves. For the case of the drain current, the choice of gate bias and temperature were chosen so that they reflect as closely as possible the numerical example of our experimental setup operation. For the top graph, we set  $u_{\rm GS}=0~{\rm V}$  and  $T_n=27~{\rm ^{\circ}C}$  for the bottom one.

$$\mathbf{H}(\mathbf{v}_{n+1})\mathbf{v}_{n+1} - \mathbf{h}(\mathbf{v}_{n+1})$$

, where

$$\mathbf{H}\left(\mathbf{v}_{n+1}\right) = \frac{\omega}{\Delta_{n}\theta}\mathbf{M}\left(\mathbf{v}_{n+\frac{1}{2}}\right) - \frac{1}{2}\cdot\mathbf{U}\left(\mathbf{v}_{n+\frac{1}{2}}, u_{GS}\left(\theta_{n+1}\right)\right)$$

(46)

$$\mathbf{h}\left(\mathbf{v}_{n+1}\right) = \left(\frac{1}{2}\mathbf{U}\left(\mathbf{v}_{n+\frac{1}{2}}, u_{GS}\left(\theta_{n+1}\right)\right) + \frac{\omega}{\Delta_{n}\theta} \cdot \mathbf{M}\left(\mathbf{v}_{n+\frac{1}{2}}\right)\right) \mathbf{v}_{n} + \mathbf{e}_{1}V_{\text{in}} + \mathbf{n}u_{GS}\left(\theta_{n+1}\right) + \mathbf{m}\left(\mathbf{v}_{n+\frac{1}{2}}\right) i_{S}\left(\mathbf{v}_{n+\frac{1}{2}}\right)$$

(47)

and  $\Delta_n \theta = \theta_{n+1} - \theta_n$ . The converged value of  $\mathbf{v}_{n+1}$  is produced by the following iterative scheme:

$$\mathbf{v}_{n+1}^{(m+1)} = \mathbf{v}_{n+1}^{(m)} - r\mathbf{J}_{\mathbf{g}}^{-1} \left(\mathbf{v}_{n+1}^{(m)}\right) \mathbf{g} \left(\mathbf{v}_{n+1}^{(m)}\right)$$

(48)

where r is the relaxation parameter.

The individual entries of the Jacobian matrix in (48) are defined as

$$J_{\mathbf{g}}\left[i,j\right]\left(\mathbf{v}_{n+1}\right)$$

$$= H_{i,j}\left(\mathbf{v}_{n+1}\right) + \gamma \left(\sum_{l=1}^{N_{\mathbf{v}}} \frac{\partial H_{i,l}\left(\mathbf{v}_{n+1}\right)}{\partial v_{n+1}[j]} v_{n+1}[l] - \frac{\partial h_{i}\left(\mathbf{v}_{n+1}\right)}{\partial v_{n+1}[j]}\right)$$

(49)

where  $N_{\bf v}$  is the size of the state vector. The mixing parameter in (49) refers to the Newton ( $\gamma=1$ ) and Picard ( $\gamma=0$ ) iterations. The inverse of  ${\bf J_g}$  can be calculated either directly or by

applying the bad Broyden method [68]

$$\mathbf{J}_{\mathbf{g}}^{-1} \left( \mathbf{v}_{n+1}^{(m)} \right) = \mathbf{J}_{\mathbf{g}}^{-1} \left( \mathbf{v}_{n+1}^{(m-1)} \right) + \frac{\Delta_{m} \mathbf{v}_{n+1} - \mathbf{J}_{\mathbf{g}}^{-1} \left( \mathbf{v}_{n+1}^{(m-1)} \right) \Delta_{m} \mathbf{g}_{n+1}}{\|\Delta_{m} \mathbf{g}_{n+1}\|_{2}^{2}} \times \Delta_{m} \mathbf{g}_{n+1}^{T}$$

$$(50)$$

where  $\Delta_m \mathbf{v}/\mathbf{g}_{n+1} = \mathbf{v}/\mathbf{g}_{n+1}^{(m)} - \mathbf{v}/\mathbf{g}_{n+1}^{(m-1)}$ . However, even when using (50), there is still the need for either an explicit computation or an approximation of the inverse of (49) for the initial iteration, since every subsequent calculation depends on the value of the previous iteration.

The termination condition used in (48) is the equivalent of the one used in Section IV-A adjusted to  $v_{n+1}$ :  $\|\Delta_m \mathbf{v}_{n+1}\|_{\infty}/\|\mathbf{v}_{n+1}^{(m)}\|_2 < \epsilon_{\mathbf{v}}$ , where  $\epsilon_{\mathbf{v}}$  is the relative error tolerance for the state vector approximation. The initial boundary conditions of (35) mainly affect the convergence speed of the differential equation solution until it reaches steady state, and in this work, we propose three different ways. The first and simpler possible approach is to start off with a zero state vector and let it evolve until convergence. Another approach, which is by default used in LTspice transient simulations, is to treat the inductors as short-circuits and the capacitors as open-circuits. Then, the currents through the inductors and the voltages across the capacitors are determined by the independent current and voltage sources in the circuit topology, accordingly. The third suggested approach for defining the initial conditions of the differential equation is to use the state vector values from the previous tuning step, i.e., the linear SS model. The simulation is considered to have reached steady state when the state vector behavior over a period is not evolving anymore and the process has converged. The condition that we use to determine the termination of the computations is based on the relative error of the dc component of the inverter input current between the last two periods:  $|I_{L_{\rm rfc}}^{(m_T)} - I_{L_{\rm rfc}}^{(m_T-1)}|/I_{L_{\rm rfc}}^{(m_T)} < \epsilon_T$ , where  $I_{L_{\rm rfc}}$  is calculated using the trapezoidal method for numerical integration [49],  $m_T$  is the iteration index of complete periods computations, and  $\epsilon_T$  is the corresponding error tolerance.

#### B. Tuning Method

A tuning algorithm for adjusting the drain voltage and slope at turn-ON using the shunt and series load capacitors for the Class E inverter is proposed in [69]. However, changes in the value of  $C_s$  result in changes in the output power of the inverter, and further tuning of the input voltage, Tx coil inductance and load is required to maintain the desired circuit properties. The higher dimension of degrees of freedom in the Class EF/ $\Phi$  inverter, compared to the Class E counterpart, enables the absorption of the unwanted effects of the switching device on the shape of the drain waveform using the combination of the shunt and the  $\phi$ -branch capacitors, which introduce minimum effects on the output power of the circuit. Instead of the  $\phi$ -branch capacitor, we could also adjust the duty cycle to control the drain voltage

Fig. 13. Simulation of the Class EF<sub>2</sub> inverter using the numerical simulation with the nonlinear switching device model. The dashed waveforms correspond to the linear state-space design and the solid ones represent the tuned version.

Fig. 14. High level flowchart diagrams of the "master" and "slave" tuning processes for adjusting the drain voltage characteristics of the nonlinear switching device in a given Class EF inverter design. The subprocess of the "slave" tuning algorithm in (a) is explained in more detail in (b). (a) Master Tuning. (b) Slave Tuning.

slope at turn-ON; however, this would result in changes in  $\lambda$ , which corresponds in deviation of the inverter behavior from the input design requirements.

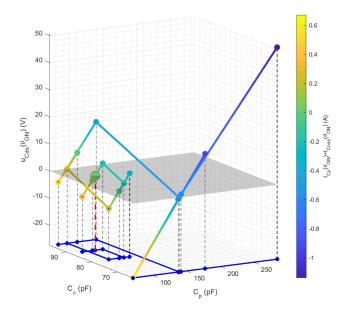

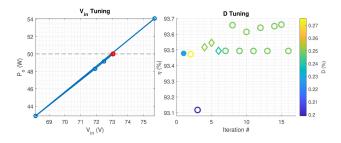

The proposed tuning process is explained in the flowcharts shown in Fig. 14. It is composed of two parts, the "master" and the "slave" tuning methods. The master tuning method [Fig. 14(a)] dictates the results of the slave tuning method [Fig. 14(b)] and the algorithm terminates when the conditions of both processes are satisfied. Both methods are based on the same principle: First set appropriate boundaries in such way that a solution exists within the resulting range, and then search for the solution in it.

The goal of this algorithm is to set the value of the drain voltage to zero, by adjusting the value of  $C_p$ , as well as the

drain current to  $i_S^{\rm ON}$  at turn-ON, using  $C_\phi$ . Any adjustments to  $C_{\phi}$  are followed by the corresponding alterations of  $L_{\phi}$ according to  $\tau_{\phi}$ , and  $R_{\phi}$ , so that the resonant frequency of the  $\phi$ -branch filter remains constant. The order in which the two tuning requirements, the drain voltage, and current values will be assigned to the master and slave iterative schemes is up to the designer to choose and affects primarily the convergence but could also lead to different results. For example, the EF2 example that we use in this work uses the  $C_\phi$  tuning as the master scheme and the  $C_p$  as the slave, as it is discussed in the following subsection. However, tuning the inverter example in the Appendix with this method requires the implementation of the opposite master-slave assignment order, compared to the example mentioned above, in order to achieve convergence. The requirement for the tuning process to be repeated iteratively originates from the fact that the effects of  $C_p$  and  $C_{\phi}$  are interconnected and not independent and their adjustments must be treated simultaneously. Instead of the actual drain voltage, we track the  $u_{C_{ds}}(\theta_{\mathrm{ON}}^{-})$  state variable, since it is the internal signal of the device that controls  $i_S$ . As for the drain current, we use the combination of the shunt capacitor current and the output capacitor current of the device

$$i_{C_p}\left(\theta_{\text{ON}}^-\right) + i_{C_{oss}}^*\left(\theta_{\text{ON}}^-\right) = i_{L_{\text{rfc}}}\left(\theta_{\text{ON}}\right) - i_{L_{\phi}}\left(\theta_{\text{ON}}\right) - i_{L_{\phi}}\left(\theta_{\text{ON}}\right) - i_{S}^*\left(\theta_{\text{ON}}^-\right) \quad (51)$$

where  $i_S^*$  is the current of the dependent source in Fig. 11 without reverse conduction during turn-OFF.

The "Initial inverter design" in Fig. 14(a) can be defined with one of the ways proposed in Section V-A. The "Input slave inverter design" in Fig. 14(b) is always set to the state vector of the previous iteration, since this approach achieves convergence faster as the iterations advance.