# General Control Scheme for a Dual-Input Three-Level Inverter

Cheng Yan<sup>(D)</sup>, Dehong Xu<sup>(D)</sup>, *Fellow*, *IEEE*, and Wenjie Chen

*Abstract*—This paper proposes a general control scheme for the dual-input three-level inverter, which comes from a neutral point clamped three-level inverter. It can be used for photovoltaic (PV) systems or battery storage systems with two dc sources. The dual-input three-level inverter can be connected with two PV arrays, which are able to realize maximum power point tracking independently. First, the dynamic model of the dual-input three-level inverter is established, which describes the relationship between the dual-input voltages and the duty cycle. After discussing the control theory of the dual-input voltages, a typical control scheme is proposed. The design of a control loop is introduced in details. Afterward, modulation and restriction of the proposed method are discussed. Finally, experiment on a 125 kW dual-input three-level PV inverter is implemented to verify the validity and feasibility of the proposed method.

*Index Terms*—Inverters, power control, pulsewidth modulation (PWM), voltage control.

## I. INTRODUCTION

**C** URRENTLY, three-level inverters have been widely used for PV generations [1]. With regards to a PV inverter, if the PV array can be divided into two subarrays, which are connected to the upper and lower dc bus of the three-level inverter, then each subarrays can be controlled independently and work at its maximum power point (MMP). Therefore, independent control of the upper and lower dc bus of the three-level inverter is able to increase solar energy harvesting. This concept can be extended to a battery energy storage system. In these cases, decoupling control of dual-input of the three-level inverter is needed.

Since the voltages of upper and lower half dc bus in the threelevel inverter can be controlled independently, it is called the dual-input three-level inverter in this paper. There have already been important developments with respect to control of dualinput three-level inverters.

Front-end dc–dc converter stages are added between the PV array and the three-level inverter [2]. The dc–dc converters are

Digital Object Identifier 10.1109/TPEL.2018.2829903

used to regulate the terminal voltage of two PV strings independently. Thus, independent maximum power point tracking (MPPT) control is realized even for both PV strings with different output characteristics. Similarly, an auxiliary converter is used to the dual-input three-level inverter in [3]–[5]. Compared to a full-power capacity front-end dc–dc converter method, the auxiliary converter only needs to deal with the power deviation between the two inputs. Although both methods mentioned above can realize independent MPPT control of two PV strings, extra hardware is needed. It not only increases circuit complexity but also results in extra power conversion loss in the added dc–dc conversion stage. Therefore, dual-input voltage control methods without extra power stages are preferred.

Voltage control methods without extra additional power stages have been extensively investigated in the literature [6]– [29]. Though most of them are concentrated on neutral point (NP) voltage balance for the three-level inverter, it shares the similar control concepts for the dual-input three-level inverter. These methods can be classified according to the pulsewidth modulation (PWM) methods.

For dual-input three-level inverter control methods based on carrier-based PWM (CBPWM) schemes, positive or negative zero sequence voltage is injected according to the NP voltage and direction of instantaneous output three-phase current [6]-[8]. If the accurate function between NP current and the added zero sequence voltage is revealed, the active control methods with a linear model can be established. In [9]–[13], the accurate needed zero sequence voltage is derived online according to the deviation of dc-link voltage, the instantaneous current, and the capacitance of dc link. It can completely control the dc-link voltage of the three-level inverter without any low-frequency NP voltage oscillations. Since the exact calculation of added zero sequence voltage in these methods is quite complicated, so the curve fitting is applied in [14] to simplify the calculation. Based on this control concept, an asymmetrical voltage control for dual-input three-level based on CBPWM is proposed in [15]. The NP current is indirectly controlled by the zero sequence voltage. Correlation between NP current and zero-sequence voltage is mathematically analyzed. The performance of all these methods depends on the accurate relationship between the zero sequence voltage and NP current. In [16]–[18], NP voltage control methods based on double-signal PWM (DSPWM) are able to completely remove low-frequency oscillation appearing in NP. The relationship between changed modulation signal and the NP current is easy to be calculated. Besides, this method is suitable for any load over the full range of converter output volt-

0885-8993 © 2018 IEEE. Translations and content mining are permitted for academic research only. Personal use is also permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

Manuscript received October 14, 2017; revised February 27, 2018; accepted April 9, 2018. Date of publication April 26, 2018; date of current version December 7, 2018. This work was supported by the National Natural Science Foundation of China under Grant 51337009. Recommended for publication by Associate Editor Y. Xue. (*Corresponding author: Dehong Xu.*)

C. Yan and D. Xu are with the College of Electrical Engineering, Institute of Power Electronics, Zhejiang University, Hangzhou 310027, China (e-mail: yancheng@zju.edu.cn; xdh@cee.zju.edu.cn).

W. Chen is with Sungrow Power Supply Co., Ltd., Hefei 518057, China (e-mail: wood827@zju.edu.cn).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

age and for all load power. But the switching frequency of the power devices is higher than with the standard CBPWM, and the high-frequency harmonic component of the output voltages increases.

For dual-input three-level inverter control methods based on space vector modulation (SVM) since one pair of redundant small vectors have opposite effect on the NP voltage, thus the NP voltage is controlled by selecting proper small vector or adjusting dwell time of redundant small vectors [19]-[21]. Independent voltage control methods based on SVM are proposed in [22]–[24]. The dwell time of two redundant vectors is rearranged according to instantaneous voltage deviation. Output voltage distortion due to the deviation of two capacitor voltages is taken into consideration. In [24], the influence of all active vectors in a switching sequence is taken into consideration before their activation. Similar control methods based on the discontinuous PWM (DPWM) are realized by selecting small vector properly [25]–[27]. Methods based on the traditional SVM or DPWM are easy to be implemented. But the control performance has not been deeply investigated. Independent voltage control method based on virtue space vector PWM (VSVPWM) is proposed in [28]. This method is similar to DSPWM and can completely remove low-frequency oscillation. However, the switching loss and high-frequency harmonics of output voltage/current will increase.

All these methods mentioned above are all derived from specific PWM or SVM schemes. Up to now, we lack a general model to explicitly describe the relationship between the dualinput voltages and PWM duty cycles for the dual-input threelevel inverter. Analysis of dual-input voltage control restriction has not been deeply investigated yet.

In this paper, we hope to generalize the basic concept of independent control beyond the specific PWM modulation. The control is based on power concept rather than the instantaneous output ac current. An independent control scheme of the dualinput three-level inverter is proposed. The dual-input three-level inverter can be connected with two PV arrays, which are able to realize MPPT independently. The paper is arranged as follows. In Section II, the dynamic model of the dual-input three-level inverter is established. The relationship between the dual-input voltages and the duty cycle is revealed. After discussing the control theory of the dual-input voltages, a typical control scheme is proposed. In Section III, the design of the control loop is implemented in details. In Section IV, modulation and restriction of the proposed method are discussed. The proposed method is verified via experimental results in Section V, and the conclusion is given in Section VI.

## II. MODELING OF THE DUAL-INPUT THREE-LEVEL INVERTER

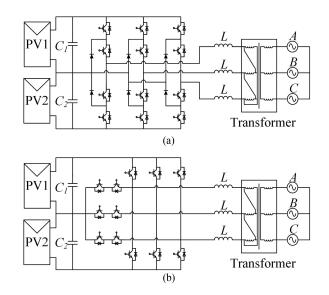

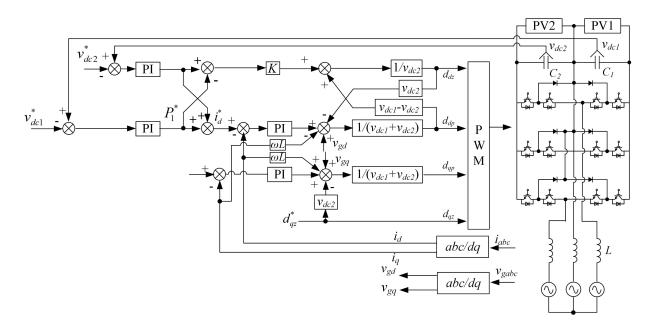

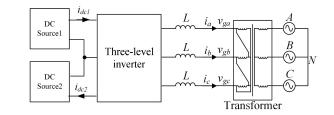

A dual-input three-level inverter connected with two independent PV arrays is shown in Fig. 1. It is mainly composed of a neutral point clamped (NPC) or T-type three-level inverter, which is connected to the grid with L filter and step-up transformer.

It is assumed that power devices in Fig. 1 are ideal switches, and each arm of the bridge has three states (positive, negative, and neutral). So each arm can be simplified by three switches

Fig. 1. Dual-input three-level inverter. (a) NPC. (b) T-type.

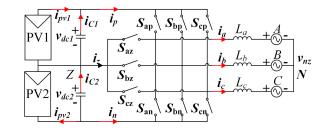

Fig. 2. Equivalent circuit of the dual-input three-level inverter.

(the upper, lower, and neutral switches), shown in Fig. 2. PV1 and PV2 represent two independent PV arrays.  $i_{pv1}$  and  $i_{pv2}$  are the current of PV1 and PV2, respectively.  $i_p$  is the positive bus current between the dc capacitance and the three-phase bridge.  $i_n$  is the negative bus current between the dc capacitance and the three-phase bridge.  $v_{dc1}$  and  $v_{dc2}$  are the voltage of PV1 and PV2, respectively.  $v_{ga}$ ,  $v_{gb}$ ,  $v_{gc}$  are the grid phase voltage and  $i_a$ ,  $i_b$ ,  $i_c$  are the grid current. L is the inductance of the filter, and its parasitic resistance is r.

#### A. Power Control Model

According to the equivalent circuit, a state average model in a three-phase stationary coordinate frame is derived as follows for the ac side:

$$L\frac{d}{dt}\begin{bmatrix}i_{a}\\i_{b}\\i_{c}\end{bmatrix} = \begin{bmatrix}d_{ap}\\d_{bp}\\d_{cp}\end{bmatrix}v_{dc1} - \begin{bmatrix}d_{an}\\d_{bn}\\d_{cn}\end{bmatrix}v_{dc2} - r\begin{bmatrix}i_{a}\\i_{b}\\i_{c}\end{bmatrix} - \begin{bmatrix}v_{ga}\\v_{gb}\\v_{gc}\end{bmatrix} - \begin{bmatrix}v_{nz}\\v_{nz}\\v_{nz}\end{bmatrix}$$

(1)

where  $v_{nz}$  is the voltage from utility neutral point N to neutral point Z of the dc bus in the three-level inverter.  $d_{xp}$ ,  $d_{xn}$ ,  $d_{xz}$  are the switching duty cycles of upper, lower, and neutral switches in phase x, respectively (x can be a, b, or c).

To reveal the relationship between the dc power and ac current, the power of PV1 and PV2 is derived as follows:

$$P_{dc1} = v_{dc1} \cdot i_p = v_{dc1} \cdot (d_{ap}i_a + d_{bp}i_b + d_{cp}i_c)$$

$$P_{dc2} = v_{dc2} \cdot (-i_n) = v_{dc2} \cdot (d_{an}i_a + d_{bn}i_b + d_{cn}i_c). \quad (2)$$

The duty cycles in one phase, duty cycles  $d_{xp}$ ,  $d_{xn}$ ,  $d_{xz}$  need to satisfy the relationship in

$$d_{xp} + d_{xn} + d_{xz} = 1. (3)$$

The model in (1) and (2) under the stationary coordinate frame can be converted into that under a rotating coordinate frame as follows:

$$L\frac{d}{dt}\begin{bmatrix} i_d\\i_q\\i_0\end{bmatrix} = \begin{bmatrix} d_{dp}\\d_{qp}\\d_{0p}\end{bmatrix} v_{dc1} - \begin{bmatrix} d_{dn}\\d_{qn}\\d_{0n}\end{bmatrix} v_{dc2} - \begin{bmatrix} v_{gd}\\v_{gq}\\v_0\end{bmatrix}$$

$$-r\begin{bmatrix} i_d\\i_q\\i_0\end{bmatrix} - \begin{bmatrix} \omega Li_d\\-\omega Li_q\\i_0\end{bmatrix}$$

(4)

$$P_{dc1} = v_{dc1} \cdot (d_{dp}i_d + d_{qp}i_q)$$

$$P_{dc2} = v_{dc2} \cdot (d_{dn}i_d + d_{qn}i_q)$$

(5)

where  $v_{gd}$ ,  $v_{gq}$  are the components of grid voltage in the dq0 frame.  $i_d$ ,  $i_q$  are the components of grid current in the dq0 frame.  $d_{dp}$ ,  $d_{qp}$ ,  $d_{0p}$  are the duty cycles for upper switches in the dq0 frame,  $d_{dn}$ ,  $d_{qn}$ ,  $d_{0n}$  are the duty cycles of lower switches, and  $d_{dz}$ ,  $d_{qz}$ ,  $d_{0z}$  are the switching duty cycles for neutral switches. The relationship between the duty cycles in the dq0 frame and the duty cycles in the stationary coordinate frame is derived as

$$\begin{bmatrix} d_{dp} & d_{dn} & d_{dz} \\ d_{qp} & d_{qn} & d_{qz} \\ d_{0p} & d_{0n} & d_{0z} \end{bmatrix} = T \begin{bmatrix} d_{ap} & d_{an} & d_{az} \\ d_{bp} & d_{bn} & d_{bz} \\ d_{cp} & d_{cn} & d_{cz} \end{bmatrix}$$

(6)

where T is the matrix of park transformation

$$T = \sqrt{\frac{2}{3}} \begin{bmatrix} \cos\omega t & \cos\left(\omega t - \frac{2\pi}{3}\right) & \cos\left(\omega t + \frac{2\pi}{3}\right) \\ -\sin\omega t & -\sin\left(\omega t - \frac{2\pi}{3}\right) & -\sin\left(\omega t + \frac{2\pi}{3}\right) \\ \frac{1}{\sqrt{2}} & \frac{1}{\sqrt{2}} & \frac{1}{\sqrt{2}} \end{bmatrix}.$$

(7)

According to (3) and (6), duty cycles in the dq frame satisfy the relationship

$$d_{dp} + d_{dn} + d_{dz} = 0$$

$$d_{qp} + d_{qn} + d_{qz} = 0.$$

(8)

The factor  $\omega L$  in (4) can be decoupled, so the model in each dq0 frame is composed of three decoupled parts. Among them, the zero-sequence equation can be ignored for a three-phase three-wire system.

*Q*-axis voltage  $v_{gq}$  is regulated to be zero. The three-level PV inverter is controlled with unit power factor, i.e.,  $i_q = 0$ . The power loss of the inverter is ignored, and the grid power is equal

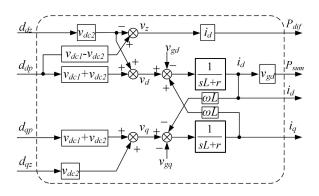

Fig. 3. Power dynamic model of the dual-input three-level inverter.

to the sum of the dual-input power

$$P_{\rm sum} = P_{\rm dc1} + P_{\rm dc2} = v_{gd} \cdot i_d.$$

(9)

Therefore, the total power  $P_{\text{sum}}$  can be controlled by regulating the *d*-axis grid current  $i_d$ . The different power  $P_{\text{dif}}$  of the dual-input  $P_{dc1}$  and  $P_{dc2}$  is derived from (5) and (8)

$$P_{\rm dif} = P_{\rm dc1} - P_{\rm dc2} = v_{\rm dc1} \cdot i_d \cdot d_{dp} + v_{\rm dc2} \cdot i_d \cdot d_{dn}$$

$$= (v_{\rm dc1} - v_{\rm dc2}) \cdot i_d \cdot d_{dp} - v_{\rm dc2} \cdot i_d \cdot d_{dz}.$$

(10)

Diagram of a dual-input three-level inverter model is shown in Fig. 3. The duty cycle in *d*-axis  $d_{dp}$  and  $d_{dz}$  can control the output power of the three-level inverter. The duty cycle  $d_{dz}$ plays a more important role than  $d_{dp}$  in controlling the power deviation  $P_{dif}$  because  $v_{dc1}$  and  $v_{dc2}$  are approximately equal. In other words, the *d*-axis duty cycle of neutral switches  $d_{dz}$ determines the power deviation  $P_{dif}$ . Therefore, the duty cycle  $d_{dp}$  is used to control the *d*-axis current  $i_d$ , i.e., total power. The rest duty cycle in *d*-axis  $d_{dn}$  can be decided by (8). For duty cycle in the *q*-axis,  $d_{qp}$  is used to control *d*-axis current  $i_q$ , i.e., the power factor. There is redundancy in remaining two duty cycles  $d_{qz}$ , and  $d_{qz}$ , which brings freedom in generalizing the PWM scheme.

#### B. Voltage Control Model

In PV application, the dc voltage is the controlled target. It is essentially controlled by the output power of each PV array. As the control relationship between and power and the duty cycle is established, the relationship between the voltage and its output power can be written as

$$C_{1} \frac{dv_{\rm dc1}}{dt} = i_{\rm pv1} - i_{p} = i_{\rm pv1} - \frac{P_{\rm dc1}}{v_{\rm dc1}}$$

$$C_{2} \frac{dv_{\rm dc2}}{dt} = i_{\rm pv2} + i_{n} = i_{\rm pv2} - \frac{P_{\rm dc2}}{v_{\rm dc2}}.$$

(11)

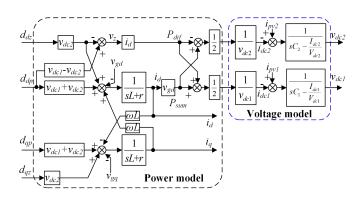

The voltage of each PV array can be controlled by regulating its output power. So the dynamic model of the dual-input threelevel inverter for voltage control is shown in Fig. 4.

#### C. Voltage Control Scheme

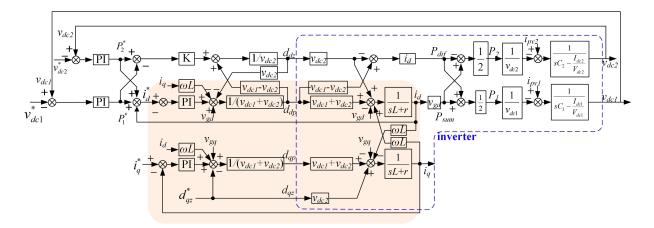

Based on the model mentioned above, the voltage control scheme for the dual-input three-level inverter is shown in Fig. 5.

Fig. 4. Voltage control model of the dual-input three-level inverter.

It is composed of outer dc voltage control loop and inner grid current control loop. Each voltage of the dc bus is controlled by a PI regulator with dc voltage feedback. The output of the voltage regulator is used as the power reference of the inner current loop. And the output of the current regulator is the duty cycle for the three-level inverter.

Besides, necessary decoupling between duty cycles with dc bus voltage is added. The factor  $\omega L$  between current  $i_d$  and  $i_q$  is also decoupled similar to the traditional dq dual controller [30]. The modulation is produced with the demand of certain duty cycle analyzed above.

#### **III. CONTROL LOOP DESIGNED AND ANALYSIS**

From the analysis in the previous section, the power control can be divided into two parts: the total power is control by the *d*-axis current, which is determined by duty cycle  $d_{dp}$ , and the different power is mainly controlled by  $d_{dz}$ , the *d*-axis duty cycle of neutral switches. Replace the dual-input three-level inverter in Fig. 5 with a mathematical module. The fundamental control loop is shown in Fig. 6.

### A. Design of the Current Inner Control Loop

The *d*-axis current  $i_d$  is controlled by the duty cycle  $d_{dp}$ . The *q*-axis current  $i_q$  is controlled by the duty cycle  $d_{qp}$ . There are several coupling factors between  $d_{qz}$  and  $d_{dp}$  in Fig. 6. The coupling is eliminated as (12). Besides, the inductor factor decoupling, dc voltage, and grid voltage feed forward are also implemented here [31], [32]. So the duty cycle reference  $d_{dp}^*$  is designed

$$d_{dp}^{*} = \frac{(i_{d}^{*} - i_{d}) G_{\mathrm{PL}i}(s) + v_{gd} - v_{\mathrm{dc}2} \cdot d_{dz} - \omega L \cdot i_{q}}{v_{\mathrm{dc}1} + v_{\mathrm{dc}2}} \quad (12)$$

where  $G_{PL_i}(s)$  is the PI regulator for the current control loop.

So the inner control loop can be simplified as Fig. 7 without any coupling factors with the other loop.  $e^{-\tau s}$  is the time delay of the control loop. Besides, the disturbance of grid voltage is neglected. The transfer function of the current control loop can

be written as

$$i_d = H_i(s) i_d^*,$$

$$H_i(s) = \frac{G_{\text{PL}i}(s) \cdot e^{-\tau s}}{sL + r + G_{\text{PL}i}(s) \cdot e^{-\tau s}}.$$

(13)

The inner control loop is similar to the traditional current control in the dq0 frame.

#### B. Design of the Voltage Control Loop

Similar to the *d*-axis duty cycle  $d_{dp}$ , the duty cycle reference  $d_{dz}^*$  can be designed as follows:

$$d_{dz}^{*} = \left( (P_{2}^{*} - P_{1}^{*}) \cdot K + (v_{dc1} - v_{dc2}) \cdot d_{dp}^{*} \right) / v_{dc2}$$

(14)

$$\begin{cases} P_1^*(s) = (v_{dc1}(s) - v_{dc1}^*(s)) G_{PL\nu}(s) \\ P_2^*(s) = (v_{dc2}(s) - v_{dc2}^*(s)) G_{PL\nu}(s) \end{cases}$$

(15)

where K is the proportion coefficient.  $P_1^*$  and  $P_2^*$  are the output of the PV1 and PV2 voltage regulators, respectively.  $G_{PLv}(s)$  is the PI regulator for the voltage control loop.

According to Fig. 6, the sum of  $P_1^*$  and  $P_2^*$  is set as reference of *d*-axis current  $i_d^*$ . And the total output power  $P_{\text{sum}}(s)$  and power deviation  $P_{\text{dif}}(s)$  of the inverter can be written as

$$\begin{cases} P_{\text{sum}}(s) = (P_1^*(s) + P_2^*(s)) \cdot H_i(s) \cdot V_{gd} \\ P_{\text{dif}}(s) = (P_2^*(s) - P_1^*(s)) \cdot K \cdot (-i_d). \end{cases}$$

(16)

According to (11), (15), and (16), the voltage of dc1 can be expressed as

$$v_{\rm dc1}(s) = \frac{A \cdot v_{\rm dc1}^*(s) - B(v_{\rm dc2}(s) - v_{\rm dc2}^*(s)) + \frac{1}{sC_1} \cdot i_{\rm pv1}(s)}{A+1}$$

(17)

$$A = \frac{G_{\text{PL}v}(s) (K \cdot i_d + H_i(s) v_{gd}(s))}{2 \cdot sC_1 \cdot V_{\text{dc}1}}$$

$$B = \frac{G_{\text{PL}v}(s) (K \cdot i_d - H_i(s) v_{gd}(s))}{2 \cdot sC_1 \cdot V_{\text{dc}1}}.$$

(18)

The control performance of  $v_{dc1}$  will be affected by  $v_{dc2}$  or  $v_{dc2}^*$  due to the coefficient *B*, which will lead to unexpected disturbance and poor dynamic control performance. In order to control the voltage of dc1 and dc2 independently, the coefficient *B* should be set approximately to be zero. So the coefficient *K* is designed as

$$K = H_i(s) v_{qd}(s) / i_d.$$

<sup>(19)</sup>

As traditional control loop design, the inner loop is much faster than the outer loop [33],  $H_i(s)$  can be regarded as 1 in designing the outer voltage loop.

Then, the voltage control of dc1 is only related to its voltage reference and disturbance of PV current

$$v_{\rm dc1}(s) = \frac{A}{1+A} v_{\rm dc1}^*(s) + \frac{1}{sC_1} \frac{1}{1+A} i_{\rm pv1}(s).$$

(20)

It is similar to voltage control of dc2. As long as K is set as (19), the coupling between the voltage of dc1 and voltage of dc2 can be suppressed. The voltage of dc1 and dc2 can be controlled

Fig. 5. Voltage control scheme for the dual-input three-level inverter.

Fig. 6. Voltage control loop.

Fig. 7. Current inner loop and total power outer loop.

independently. The voltage control of dc2 is only related to its voltage reference and disturbance of PV current

$$v_{\rm dc2}\left(s\right) = \frac{A}{1+A} v_{\rm dc2}^{*}\left(s\right) + \frac{1}{sC_2} \frac{1}{1+A} i_{\rm pv2}\left(s\right).$$

(21)

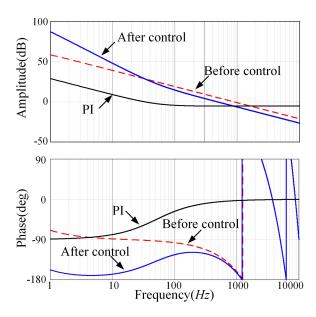

## C. Bode Plot

The current control loop is designed to ensure that the output currents meet the grid code. The bandwidth of the current control loop should be high enough to deal with the dynamic situation such as low voltage ride through. But the control bandwidth is limited by the switching frequency. In this paper, the switching frequency is 5 kHz. The cross-over frequency of the current control loop is designed to 500 Hz, which is much lower than the switching frequency to achieve quite good stability. The bode diagram before and after the PI regulator is shown in Fig. 8. The cross-over frequency before control is 1000 Hz. The zero-point frequency of the PI controller is designed to 50 Hz. The cross-over frequency of the control loop is 500 Hz and the phase margin is 49°.

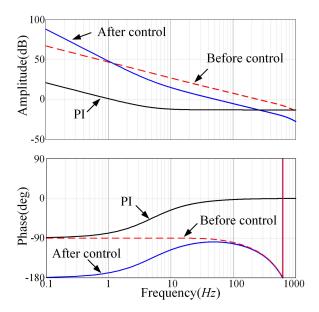

The voltage control loop is designed to control the dc/PV voltage. According to a traditional control loop design, the outer voltage control loop should be much slower than the inner current control loop. On the other hand, the voltage control speed should be faster than the MPPT speed. The MPPT interval in the inverter of this paper is 1 s. So the bandwidth of the voltage control loop is designed to 50 Hz, which is much slower than the MPPT control speed (1 Hz). The bode diagram before and after the PI regulator is shown in Fig. 9. The cross-over frequency before

Fig. 8. Bode diagram of the current control loop.

control is 250 Hz. The zero-point frequency of the PI controller is designed to 5 Hz. The cross-over frequency is 50 Hz and the phase margin is 81°.

Based on the analysis and design aforementioned, the inverter has enough dynamic performance. Meanwhile, the stability of the system is satisfactory.

## IV. MODULATION AND RESTRICTION IN THE DUAL-INPUT THREE-LEVEL INVERTER

According to the analysis aforementioned, the basic control scheme has been established. Some duty cycles in the dq frame  $(d_{dp}, d_{dz}, d_{qp})$  have been determined by the control regulator, and the rest duty cycles bring free degree for a modulation signal. In this section, the final modulation scheme will be discussed and the control restriction of the dual-input three-level inverter will be revealed.

#### A. PWM Modulation Generator

When four duty cycles  $d_{dp}$ ,  $d_{qp} d_{dz}$ ,  $d_{qz}$  are assigned by control scheme, the rest duty cycles in the dq frame  $d_{dn}$ ,  $d_{qn}$  can be derived by (8). The final modulation signal in the stationary frame can be derived from the duty cycles in the dq frame with inverse Park transformation  $T^{-1}$

$$\begin{bmatrix} d_{ap} \\ d_{bp} \\ d_{cp} \end{bmatrix} = \sqrt{\frac{2}{3}} \begin{bmatrix} \cos\theta & -\sin\theta & \frac{1}{\sqrt{2}} \\ \cos\left(\theta - \frac{2}{3}\pi\right) & -\sin\left(\theta - \frac{2}{3}\pi\right) & \frac{1}{\sqrt{2}} \\ \cos\left(\theta + \frac{2}{3}\pi\right) & -\sin\left(\theta + \frac{2}{3}\pi\right) & \frac{1}{\sqrt{2}} \end{bmatrix} \begin{bmatrix} d_{dp} \\ d_{qp} \\ d_{0p} \end{bmatrix}$$

(22)

$$\begin{bmatrix} d_{an} \\ d_{bn} \\ d_{cn} \end{bmatrix} = \sqrt{\frac{2}{3}} \begin{bmatrix} \cos\theta & -\sin\theta & \frac{1}{\sqrt{2}} \\ \cos\left(\theta - \frac{2}{3}\pi\right) & -\sin\left(\theta - \frac{2}{3}\pi\right) & \frac{1}{\sqrt{2}} \\ \cos\left(\theta + \frac{2}{3}\pi\right) & -\sin\left(\theta + \frac{2}{3}\pi\right) & \frac{1}{\sqrt{2}} \end{bmatrix} \begin{bmatrix} d_{dn} \\ d_{qn} \\ d_{0n} \end{bmatrix}.$$

(23)

Fig. 9. Bode diagram of the voltage control loop.

The zero-sequence duty cycles  $d_{0p}$  in (22) and  $d_{0n}$  in (23) represent the common-voltage components produced by the upper and low bus, respectively.

The modulation signal generated by (22) and (23) is called dual-input PWM in this paper. The dual-input PWM is more than a specific modulation scheme. The redundant duty cycles bring a free degree in generating a modulation signal. So there are infinite kinds of modulation signals that can be used in the dual-input three-level inverter. It provides the opportunity to choose the best PWM scheme.

## B. Control Restriction for Power Deviation

Total power control restriction in the dual-input three-level inverter is quite similar to that in a conventional inverter. Modulation index is the basic restriction of the total output power. We should pay more attention to control restriction of power deviation in the dual-input three-level inverter. There must be a boundary for the power deviation of two dc input among all possible PWM modulation signals, which can be derived from the duty cycles of each switch.

First, the duty cycle of upper three switches should be between 0 and 1

$$d_{ap}, d_{bp}, d_{cp} \in [0, 1].$$

(24)

Substituting (22) into (24), the restriction of  $d_{dp}$  and  $d_{qp}$  is

$$\begin{cases} |d_{qp}| \leq \frac{1}{\sqrt{2}} \\ \left| d_{dp} \pm \frac{1}{\sqrt{3}} d_{qp} \right| < \sqrt{\frac{2}{3}}. \end{cases}$$

$$(25)$$

It shows that the vector of  $d_{dp}$  and  $d_{qp}$  is located in a hexagon, which is similar to the traditional SVM space vector hexagon diagram.

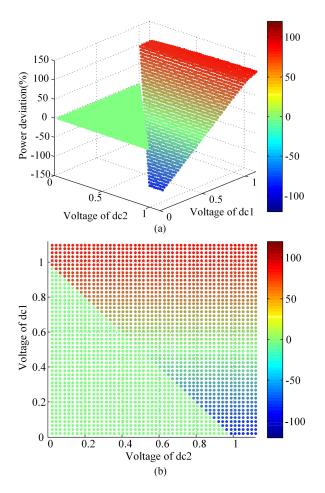

Fig. 10. Maximum limit of the power deviation. (a) 3-D view. (b) X-Y view.

Similarly, the boundary of duty cycles  $d_{dn}$  and  $d_{qn}$  is

$$\begin{cases} |d_{qn}| \le \frac{1}{\sqrt{2}} \\ \left| \frac{\sqrt{3}}{2} d_{dn} \pm \frac{1}{2} d_{qn} \right| < \frac{1}{\sqrt{2}}. \end{cases}$$

(26)

Besides, there is another restriction for the duty cycles, the sum duty cycle of upper and bottom switches for every phase should be between 0 and 1

$$d_{ap} + d_{an}, d_{bp} + d_{bn}, d_{cp} + d_{cn} \in [0, 1].$$

(27)

Equations (25)–(27) are the main restriction for duty cycles; in other words, the power control in the dual-input three-level input is restricted by these equations. According to the boundary of the duty cycle in the dq frame and the power deviation of the dual-input written as (10), the boundary of the power deviation is revealed.

Fig. 10 shows the maximum limit of the power deviation in three-dimensional (3-D) space based on two bus voltages  $(v_{dc1}, v_{dc2})$ , the y-axis is the voltage of the upper dc-bus voltage  $v_{dc1}$ , and the x-axis is the voltage of the lower dc-bus voltage  $v_{dc2}$ . The value of  $v_{dc1}$  and  $v_{dc2}$  in Fig. 10 represents the ratio of dc-bus voltage to output line voltage. In other words,  $v_{dc1}$  is equal to 1 in Fig. 10 meaning that  $v_{dc1}$  is equal to the

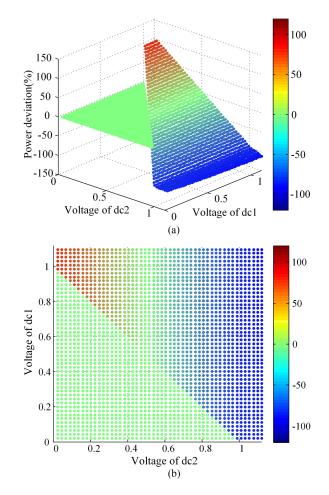

Fig. 11. Minimum limit of the power deviation. (a) 3-D view. (b) X-Y view.

amplitude of output line voltage. As shown in the X-Y view in Fig. 10(b), when the sum of  $v_{dc1}$  and  $v_{dc2}$  is below 1, the inverter cannot output essential grid voltage, so it has no ability to regulate the power deviation. When  $v_{dc2}$  is fixed, the maximum power deviation is approximately proportional to  $v_{dc1}$ . And when  $v_{dc1}$  is fixed,  $v_{dc2}$  has little effect on the maximum power deviation.

Fig. 11 shows the minimum limit of the power deviation in 3-D space based on two bus voltages  $(v_{dc1}, v_{dc2})$ , the y-axis is the voltage of the upper dc-bus voltage  $v_{dc1}$ , and the x-axis is the voltage of the lower dc-bus voltage  $v_{dc2}$ . The value of  $v_{dc1}$  and  $v_{dc2}$  in Fig. 11 represents the ratio of dc-bus voltage to output line voltage. As shown in the X-Y view in Fig. 11(b), when the sum of  $v_{dc1}$  and  $v_{dc2}$  is below 1, the inverter cannot output essential grid voltage, so it has no ability to regulate the power deviation. When  $v_{dc1}$  is fixed, the minimum power deviation is approximately proportional to  $v_{dc2}$ . And when  $v_{dc2}$  is fixed,  $v_{dc1}$  has little effect on the minimum power deviation.

The PWM generator contains all possible PWM signals, including traditional PWM methods such as SPWM and SVM. For comparison, traditional PWM methods are taken into considerations, especially. There is an additional restriction for traditional SPWM or SVM. Only one pair of switches is operating in one switching period. In other words, during every switching period,

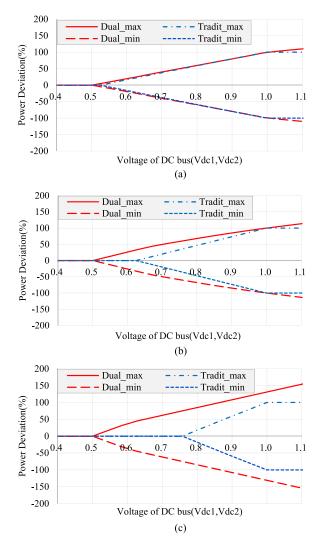

Fig. 12. Power deviation comparison when  $v_{dc1}$  is equal to  $v_{dc2}$ . (a)  $\varphi = 0^{\circ}$ . (b)  $\varphi = 30^{\circ}$ . (c)  $\varphi = 60^{\circ}$ .

there must be

$$d_{ap} \cdot d_{an} = 0$$

$$d_{bp} \cdot d_{bn} = 0$$

$$d_{cp} \cdot d_{cn} = 0.$$

(28)

To prevent complexity in viewing and analysis, Fig. 12 shows the comparison of dual-input PWM and traditional PWM under the situation when  $v_{dc1}$  is equal to  $v_{dc2}$ . The horizontal axis is the voltage of the dc bus. The vertical axis is the power deviation of two inputs. The value of  $v_{dc1}$  and  $v_{dc2}$  represents the ratio of dc-bus voltage to output line voltage.

Fig. 12(a) shows the situation when the power factor is 1, i.e., the power factor angle  $\varphi = 0$ . The red and blue lines represent the maximum power deviation of dual-input PWM and traditional PWM, respectively. And the red and blue dash lines represent the minimum power deviation of dual-input PWM and traditional PWM, respectively. If the voltage of half-bus is below 0.5, all PWM modulations cannot be able to work properly for the three-level inverter. It is the same to the conclusion

from Figs. 10 and 11. With the increase in the dc voltage, the power deviation capability increases proportionally. The relation between the dc voltage and maximum or minimum power deviation is approximately linear.

As shown in Fig. 12(a), the traditional PWM method power deviation capability is slightly weaker than the dual-input PWM method. One difference is that the lowest controllable dc voltage of dual-input PWM is smaller. The other difference is under the situation when dc voltage is high enough, the maximum power deviation of traditional PWM is equal to 100%. While the maximum power deviation of dual-input PWM can be larger than 100%.

Fig. 12(b) shows the power deviation under the situation when the power factor angle  $\varphi$  is 30°. The controllable area of the dual-input PWM method is much larger than that of traditional PWM. The lowest controllable dc voltage  $v_{dc1}$  and  $v_{dc2}$  in dualinput PWM is around 0.5, while the lowest voltage in traditional PWM is around 0.63. With the increase in the dc voltage, the dual-input PWM method always has a wider controllable range.

Fig. 12(c) shows the power deviation under the situation when the power factor angle  $\varphi$  is 60°. The controllable area of the dualinput PWM method is significantly larger than that of traditional PWM. The lowest controllable dc voltage  $v_{dc1}$  and  $v_{dc2}$  in dualinput PWM is around 0.5, while the lowest voltage in traditional PWM is around 0.76. With the increase in the dc voltage, the dual-input PWM method always has a wider controllable range.

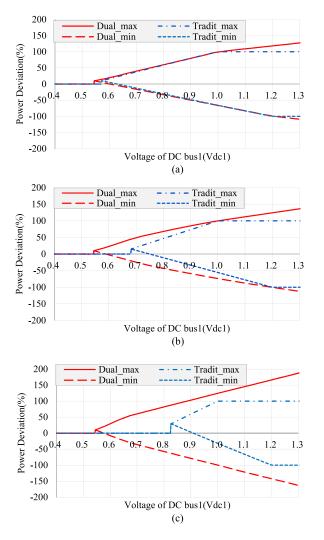

Fig. 13 shows the comparison of dual-input PWM and traditional PWM under a specific situation that  $v_{dc1}$  is 20% larger than  $v_{dc2}$ . The horizontal axis is  $v_{dc1}$ , while  $v_{dc2}$  is 20% less than the voltage of  $v_{dc1}$ . The value of  $v_{dc1}$  and  $v_{dc2}$  represents the ratio of dc-bus voltage to output line voltage.

Fig. 13(a) shows the situation when the power factor is 1, i.e., the power factor angle  $\varphi = 0$ . The red and blue lines represent the maximum power deviation of dual-input PWM and traditional PWM, respectively. And the red and blue dash lines represent the minimum power deviation of dual-input PWM and traditional PWM, respectively. Similar to the situation when  $v_{dc1}$  is equal to  $v_{dc2}$ , if  $v_{dc1}$  (horizontal axis) is below 0.55, all PWM modulation cannot be able to work properly for the three-level inverter. With the increase in the dc voltage, the control capability of power deviation increases proportionally. As  $v_{dc1}$  is larger than  $v_{dc2}$ , the control capability of positive power deviation is stronger than that of negative power deviation. For example, when  $v_{dc1}$  reaches 1, maximum power deviation of traditional PWM is equal to 100%. On the other hand, minimum power deviation of traditional PWM reaches -100% until  $v_{dc1}$  is equal to 1.2 ( $v_{dc2}$  is equal to 1). The relationship between the dc voltage and maximum or minimum power deviation is approximately linear. Besides, control capability of the traditional PWM method power deviation is slightly weaker than that of the dual-input PWM method.

Fig. 13(b) shows the power deviation under the situation when the power factor angle  $\varphi$  is 30°. The controllable area of the dualinput PWM method is much larger than that of traditional PWM. The lowest controllable dc voltages  $v_{dc1}$  and  $v_{dc2}$  in dual-input PWM are around 0.55, while the lowest voltage in traditional PWM is around 0.69. With the increase in the dc voltage, the

Fig. 13. Power deviation comparison when  $v_{dc1}$  is 20% larger than  $v_{dc2}$ . (a)  $\varphi = 0^{\circ}$ . (b)  $\varphi = 30^{\circ}$ . (c)  $\varphi = 60^{\circ}$ .

dual-input PWM method always has a wider controllable range. Besides, as  $v_{dc1}$  is larger than  $v_{dc2}$ , the control capability of positive power deviation is stronger than that of negative power deviation.

Fig. 13(c) shows the power deviation under the situation when the power factor angle  $\varphi$  is 60°. The controllable area of the dualinput PWM method is significantly larger than that of traditional PWM. With the increase in the dc voltage, the dual-input PWM method always has a wider controllable range. Besides, as  $v_{dc1}$ is larger than  $v_{dc2}$ , the control capability of positive power deviation is stronger than that of negative power deviation.

One drawback of the dual-input PWM method is that the number of turn-ON and turn-OFF switching transient may slightly increase in every switching frequency period. But it is quite effective to enhance the control capability of power deviation. So in some extraordinary operation situation, such as PV application, when the PV panels are partially shadowed, large unbalance power deviation of two input arrays appears in dualinput PWM. Though the switching loss may increase, more PV energy can be harvested.

Fig. 14. Experimental system.

TABLE I PARAMETERS OF THE DUAL-INPUT INVERTER

| Parameters                     | Value     |

|--------------------------------|-----------|

| Rated power                    | 125kW     |

| Switching frequency            | 5kHz      |

| Grid voltage                   | 315V/50Hz |

| Filter Inductance              | 0.05mH    |

| Upper and lower DC capacitance | 1260uF    |

TABLE II Parameters of the PV Array

| Parameters            | Value  |  |

|-----------------------|--------|--|

| Open circuit voltage  | 350V   |  |

| Short circuit current | 25A    |  |

| MPP voltage           | 271.6V |  |

| MPP current           | 22.1A  |  |

| MPP power             | 6kW    |  |

For practical application, when the inverter is operating under a normal condition, the three-level inverter can operate with PWM with less switching times, which is similar to SPWM or SVM, and when the required power deviation exceeds its controllable limit, the three-level inverter can transit into dualinput PWM with more switching times to enhance the control capability of power deviation.

#### V. EXPERIMENTAL RESULTS

The implementation is carried out on a 125 kW T-type threelevel PV inverter to verify the proposed control method. Fig. 14 shows the experimental system and its main parameters are listed in Table I.

The dual-input PV arrays of the three-level inverter are produced by two Chroma dc power supply 62150H-1000s. Each one operates as a PV array listed in Table II.

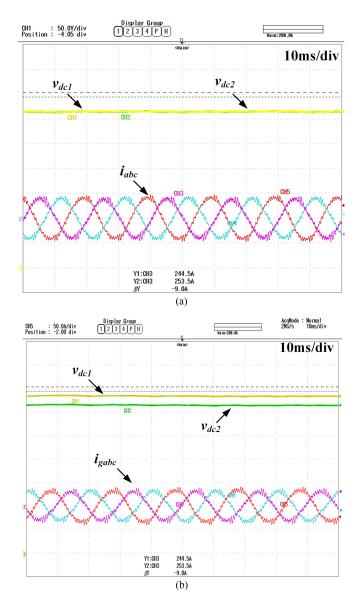

Fig. 15 shows the steady-state waveform with the proposed method at 20 kW. The dc voltages  $v_{dc1}$ ,  $v_{dc2}$  and currents  $i_{dc1}$ ,  $i_{dc2}$  are constant without low-frequency fluctuation, while switching frequency of dc current exists, and  $i_a$ ,  $i_b$ ,  $i_c$  are the grid current with low total harmonic distortion (THD), so the power of DC1 and DC2 is controlled to be constant with high output power quality.

Fig. 15(a) shows the steady waveform when voltages of dc1 and dc2 are the same. Channels 1 and 2 are the voltage of dc1 and dc2, channels 3–5 are the three-phase grid current. The voltages of dc1 and dc2 are both 320 V. The three-phase grid current is symmetrical, and the power quality is as good as that under

Fig. 15. Steady waveform  $[v_{dc1} (50 \text{ V/div}, \text{center } 200 \text{ V}), v_{dc2} (50 \text{ V/div}, \text{center } 200 \text{ V}), i_{dc1} (12 \text{ A/div}, \text{center } 0 \text{ A}), i_{dc2} (12 \text{ A/div}, \text{center } 0 \text{ A}), \text{and } i_{abc} (20 \text{ A/div}, \text{center } -40 \text{ A})].$  (a) With the same dc voltage. (b) With different dc voltages.

traditional control with single PV input. Besides, there is nearly none of the low-frequency oscillation on half bus voltage.

Fig. 15(b) shows the steady waveform when the voltage of dc1 is higher than the voltage of dc2 by 20 V. The three-phase grid current is symmetrical, and the power quality is as good as that under traditional control with single PV input. Besides, there is nearly none of the low-frequency oscillation on single dc1 or dc2 voltage. So the control method will not affect the steady performance of the three-level inverter.

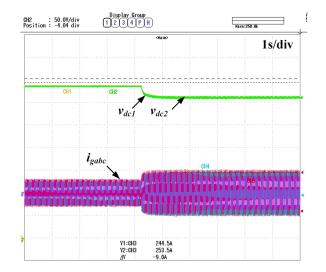

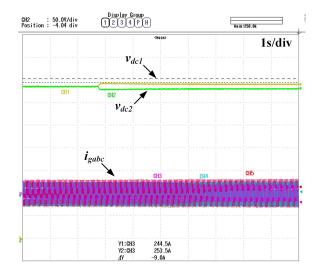

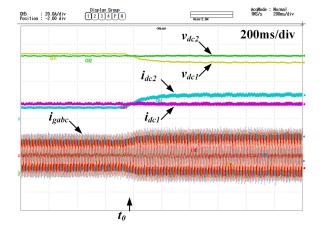

Fig. 16 shows the dynamic voltage control waveform when both voltages of dc1 and dc2 are changed. At time  $t_0$  in Fig. 16, the voltages of dc1 and dc2 are controlled from 340 to 320 V at the same time. It can be seen that the control speed of  $v_{dc1}$ and  $v_{dc2}$  is almost the same. The control time is around 100 ms. When the voltages of dc1 and dc2 are controlled toward MPP, the

Fig. 16. Total voltage control [ $v_{dc1}$  (50 V/div, center 200 V),  $v_{dc2}$  (50 V/div, center 200 V),  $i_{dc1}$  (12 A/div, center 0 A),  $i_{dc2}$  (12 A/div, center 0 A), and  $i_{abc}$  (20 A/div, center - 40 A)].

Fig. 17. Different voltage controls  $[v_{dc1} (50 \text{ V/div}, \text{center } 200 \text{ V}), v_{dc2} (50 \text{ V/div}, \text{center } 200 \text{ V}), i_{dc1} (12 \text{ A/div}, \text{center } 0 \text{ A}), a_{dc2} (12 \text{ A/div}, \text{center } 0 \text{ A}), and i_{abc} (20 \text{ A/div}, \text{center } -40 \text{ A})].$

grid current increases with the decrease in voltage and increase in output power. There is no surge in voltage and current. The total voltage control is implemented.

Fig. 17 shows the dynamic voltage control waveform when the voltage of dc1 increases and dc2 decreases. The control performance is similar to that of total voltage control. The control speed of  $v_{dc1}$  and  $v_{dc2}$  is almost the same. There is no surge on voltage and current. The different voltage controls are implemented.

Fig. 18 shows the performance of single voltage control of PV1. At time  $t_0$ , the voltage of dc1 is reduced by 20 V, while the voltage of dc2 keeps constant. The working point of PV1 alters with the decrease in voltage and the increase in current. Meanwhile, the operation state of dc2 keeps the same. Both current and voltage of PV2 are not changed.

Fig. 18. Voltage control of PV1 [ $v_{dc1}$  (50 V/div, center 150 V),  $v_{dc2}$  (50 V/div, center 150 V),  $i_{pv1}$  (12 A/div, center 0 A),  $i_{pv2}$  (12 A/div, center 0 A), and  $i_{abc}$  (20 A/div, center -40 A)].

Fig. 19. Waveform with the same PV array [ $v_{dc1}$  (50 V/div, center 150 V),  $v_{dc2}$  (50 V/div, center 150 V),  $i_{pv1}$  (12 A/div, center 0 A),  $i_{pv2}$  (12 A/div, center 0 A), and  $i_{abc}$  (20 A/div, center -40 A)].

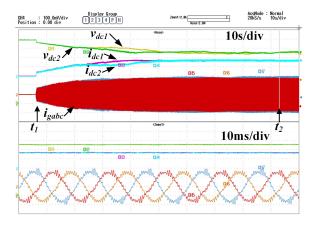

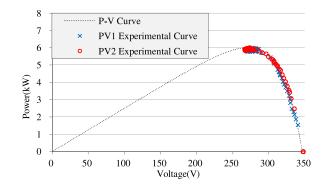

Fig. 19 shows the MPPT waveform of dual PV input. Both PV1 and PV2 are set as Table II. The maximum point power is 6 kW. At time  $t_1$ , the three-level inverter is connected to the grid, and the grid current increases. The voltage controller with MPPT is working properly. Both voltages of DC1 and DC2 can be tracked down to the MPP. At last time  $t_2$  in Fig. 19, each PV array works at its MPP. The bottom of Fig. 19 is the enlarged waveform of time  $t_2$ . The grid current is controlled with good quality.

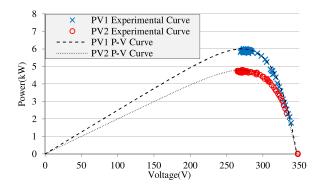

Fig. 20 shows the tacking path of PV1 and PV2 with the same PV array. The blue and red dots are the working state of PV1 and PV2 every 2 s. The slash lines are the P-V curve of PV1 and PV2 in theory. The three-level input can track both of the PV arrays for upper and lower dc side. The power of PV1 and PV2 is 6 kW as expected. The dual-input three-level inverter can work effectively to achieve maximum power from two-series PV array with power deviation.

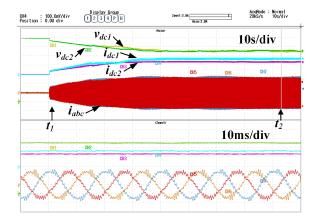

Fig. 21 shows the MPPT waveform of dual PV inputs. PV1 is set as Table II. PV2 is set operating at 80% illumination in Table II. Its maximum power is 4.8 kW. At time  $t_1$ , the three-level inverter is connected to the grid, the voltage controller with

Fig. 20. Comparison of experiment curve and designed P-V curve with the same dual PV array.

Fig. 21. Waveform with the same PV array [ $v_{dc1}$  (50 V/div, center 150 V),  $v_{dc2}$  (50 V/div, center 150 V),  $i_{pv1}$  (12 A/div, center 0 A),  $i_{pv2}$  (12 A/div, center (0 A), and  $i_{abc}$  (20 A/div, center – 40 A)].

Fig. 22. Comparison of experiment curve and designed *P*–*V* curve with different PV arrays.

MPPT is working, and both voltages of DC1 and DC2 can be tracked down to the MPP. At last time  $t_2$  in Fig. 21, each PV array works at its MPP. The bottom of Fig. 21 is the enlarged waveform of time  $t_2$ . The grid current is controlled with good quality.

Fig. 22 shows the tacking path of PV1 and PV2, and the blue and red dots are the working state of PV1 and PV2 every 2 s. The slash lines are the P-V curve of PV1 and PV2 in theory. The three-level input can track both of the PV arrays for upper and lower dc side. The dual-input three-level inverter can work effectively to achieve the maximum power from the two-series PV array with power deviation.

From the experimental results, the voltage of PV1 and PV2 can be controlled separately. Each PV array can reach its MPP when the PV arrays are operating under different circumstances. More power is harvested with good power quality.

## VI. CONCLUSION

This paper proposed a general control scheme for the dualinput three-level inverter. A dynamic model of the dual-input three-level inverter is established, which represents the relationship between the voltage/power and specific duty cycle. With the proposed method, dual-input voltages of the three-level inverter can be controlled independently with good quality of grid current. Each PV array can achieve its maximum power when the PV arrays are operating under different circumstances. It increases energy harvesting for the PV array. Besides, modulation and restriction of the proposed method are discussed. The power deviation control capability of dual-input PWM is much stronger than that of traditional PWM.

#### REFERENCES

- T. Kerekes, M. Liserre, R. Teodorescu, C. Klumpner, and M. Sumner, "Evaluation of three-phase transformerless photovoltaic inverter topologies," *IEEE Trans. Power Electron.*, vol. 24, no. 9, pp. 2202–2211, Sep. 2009.

- [2] S. Kouro, K. Asfaw, R. Goldman, R. Snow, B. Wu, and J. Rodriguez, "NPC multilevel multistring topology for large scale grid connected photovoltaic systems," in *Proc. Int. Symp. Power Electron. Distrib. Gener. Syst.*, 2010, pp. 400–405.

- [3] T. Naik, R. G. Wandhare, and V. Agarwal, "Three-level NPC inverter with novel voltage equalization for PV grid interface suitable for partially shaded conditions," in *Proc. IEEE Power Energy Conf.*, 2013, pp. 186–193.

- [4] R. Krishna, D. E. Soman, S. K. Kottayil, and M. Leijon, "Pulse delay control for capacitor voltage balancing in a three-level boost neutral point clamped inverter," *IET Power Electron.*, vol. 8, no. 2, pp. 268–277, Aug. 2015.

- [5] A. von Jouanne, S. Dai, and H. Zhang, "A multilevel inverter approach providing dc-link balancing, ride-through enhancement, and commonmode voltage elimination," *IEEE Trans. Ind. Electron.*, vol. 49, no. 4, pp. 739–745, Aug. 2002.

- [6] J. Pou, J. Zaragoza, S. Ceballos, M. Saeedifard, and D. Boroyevich, "A carrier-based PWM strategy with zero-sequence voltage injection for a three-level neutral-point-clamped converter," *IEEE Trans. Power Electron.*, vol. 27, no. 2, pp. 642–651, Feb. 2012.

- [7] J. S. Lee and K. B. Lee, "Time-offset injection method for neutral-point ac ripple voltage reduction in a three-level inverter," *IEEE Trans. Power Electron.*, vol. 31, no. 3, pp. 1931–1941, Mar. 2016.

- [8] Y. Zhang, J. Li, X. Li, Y. Cao, M. Sumner, and C. Xia, "A method for the suppression of fluctuations in the neutral-point potential of a three-level NPC inverter with a capacitor-voltage loop," *IEEE Trans. Power Electron.*, vol. 32, no. 1, pp. 825–836, Jan. 2017.

- [9] S. Qiang, L. Wenhua, Y. Qingguang, X. Xiaorong, and W. Zhonghong, "A neutral-point potential balancing algorithm for three-level NPC inverters using analytically injected zero-sequence voltage," in *Proc. IEEE Appl. Power Electron. Conf.*, 2003, pp. 228–233.

- [10] J. Shen, S. Schroder, B. Duro, and R. Roesner, "A neutral-point balancing controller for a three-level inverter with full power-factor range and low distortion," *IEEE Trans. Ind. Appl.*, vol. 49, no. 1, pp. 138–148, Jan./Feb. 2013.

- [11] J. Zaragoza, J. Pou, S. Ceballos, E. Robles, C. Jaen, and M. Corbalan, "Voltage-balance compensator for a carrier-based modulation in the neutral-point-clamped converter," *IEEE Trans. Ind. Electron.*, vol. 56, no. 2, pp. 305–314, Feb. 2009.

- [12] Z. Ye, Y. Xu, X. Wu, G. Tan, X. Deng, and Z. Wang, "A simplified PWM strategy for a neutral-point-clamped (NPC) three-level converter with unbalanced dc links," *IEEE Trans. Power Electron.*, vol. 31, no. 4, pp. 3227–3238, Apr. 2016.

- [13] I. López *et al.*, "Modulation strategy for multiphase neutral-point-clamped converters," *IEEE Trans. Power Electron.*, vol. 31, no. 2, pp. 928–941, Feb. 2016.

- [14] C. Wang and Y. Li, "Analysis and calculation of zero-sequence voltage considering neutral-point potential balancing in three-level NPC converters," *IEEE Trans. Ind. Electron.*, vol. 57, no. 7, pp. 2262–2271, Jul. 2010.

- [15] Y. Park, S. Sul, C. Lim, W. Kim, and S. Lee, "Asymmetric control of dc-link voltages for separate MPPTs in three-level inverters," *IEEE Trans. Power Electron.*, vol. 28, no. 6, pp. 2760–2769, Jun. 2013.

- [16] Z. Weifeng, C. Yanbo, G. Leijiao, and T. Wen, "Study on double modulation wave carrier-based PWM for three-level neutral-point-clamped inverters," in *Proc. 5th Int. Conf. Power Electron. Syst. Appl.*, 2013, pp. 1–5.

- [17] J. Zaragoza, J. Pou, S. Ceballos, E. Robles, P. Ib'a nez, and J. L. Villate, "A comprehensive study of a hybrid modulation technique for the neutralpoint-clamped converter," *IEEE Trans. Ind. Electron.*, vol. 56, no. 2, pp. 294–304, Feb. 2009.

- [18] J. Pou *et al.*, "Fast-processing modulation strategy for the neutral-pointclamped converter with total elimination of the low-frequency voltage oscillations in the neutral point," *IEEE Trans. Ind. Electron.*, vol. 54, no. 4, pp. 2288–2299, Aug. 2007.

- [19] N. Celanovic and D. Boroyevich, "A comprehensive study of neutral-point voltage balancing problem in three-level neutral-point-clamped voltage source PWM inverters," *IEEE Trans. Power Electron.*, vol. 15, no. 2, pp. 242–249, Mar. 2000.

- [20] Y. Lai, Y. Chou, and S. Pai, "Simple PWM technique of capacitor voltage balance for three-level inverter with dc-link voltage sensor only," in *Proc.* 33rd Annu. Conf. IEEE Ind. Electron. Soc., 2007, pp. 1749–1754.

- [21] J. S. Lee, S. Yoo, and K. B. Lee, "Novel discontinuous PWM method of a three-level inverter for neutral-point voltage ripple reduction," *IEEE Trans. Ind. Electron.*, vol. 63, no. 6, pp. 3344–3354, Jun. 2016.

- [22] Z. Zhang, A. Chen, X. Xing, and C. Zhang, "Space vector modulation based control strategy of three-level inverter for separate MPPTs in photovoltaic system," in *Proc. IEEE 8th Int. Power Electron. Motion Control Conf.*, 2016, pp. 2394–2400.

- [23] U. M. Choi, F. Blaabjerg, and K. B. Lee, "Control strategy of two capacitor voltages for separate MPPTs in photovoltaic systems using neutral-pointclamped inverters," *IEEE Trans. Ind. Appl.*, vol. 51, no. 4, pp. 3295–3303, Jul./Aug. 2015.

- [24] A. Lewicki, Z. Krzeminski, and H. Abu-Rub, "Space-vector pulsewidth modulation for three-level NPC converter with the neutral point voltage control," *IEEE Trans. Ind. Electron.*, vol. 58, no. 11, pp. 5076–5086, Nov. 2011.

- [25] A. R. Beig, S. Kanukollu, K. A. Hosani, and A. Dekka, "Space-vectorbased synchronized three-level discontinuous PWM for medium voltage high-power VSI," *IEEE Trans. Ind. Electron.*, vol. 61, no. 8, pp. 3891– 3901, Aug. 2014.

- [26] U. M. Choi, H. H. Lee, and K. B. Lee, "Simple neutral-point voltage control for three-level inverters using a discontinuous pulse width modulation," *IEEE Trans. Energy Convers.*, vol. 28, no. 2, pp. 434–443, Feb. 2013.

- [27] C. Xia, G. Zhang, Y. Yan, X. Gu, T. Shi, and X. He, "Discontinuous space vector PWM strategy of neutral-point-clamped three-level inverters for output current ripple reduction," *IEEE Trans. Power Electron.*, vol. 32, no. 7, pp. 5109–5121, Jul. 2017.

- [28] X. Wu, G. Tan, Z. Ye, G. Yao, Z. Liu, and G. Liu, "Virtual-space-vector PWM for a three-level neutral-point-clamped inverter with unbalanced dc-links," *IEEE Trans. Power Electron.*, vol. 33, no. 3, pp. 2630–2642, Mar. 2018.

- [29] J. Chen, Y. He, S. U. Hasan, and J. Liu, "A comprehensive study on equivalent modulation waveforms of the SVM sequence for three-level inverters," *IEEE Trans. Power Electron.*, vol. 30, no. 12, pp. 7149–7158, Dec. 2015.

- [30] H. Song and K. Nam, "Dual current control scheme for PWM converter under unbalanced input voltage conditions," *IEEE Trans. Ind. Electron.*, vol. 46, no. 5, pp. 953–959, Oct. 1999.

- [31] J. Lee and Y. Sun, "Novel sinusoidal pulsewidth modulation schemes for voltage-source inverters with fluctuating input voltage," *IEEE Trans. Ind. Electron.*, vol. 35, no. 2, pp. 284–294, May 1988.

- [32] A. Yazdani and P. P. Dash, "A control methodology and characterization of dynamics for a photovoltaic system interfaced with a distribution network," *IEEE Trans. Power Del.*, vol. 24, no. 3, pp. 1538–1551, Jul. 2009.

- [33] J. Espinoza, G. Joos, M. Perez, and L. Moran, "Stability issues in three-phase PWM current/voltage source rectifiers in the regeneration mode," in *Proc. IEEE Int. Symp. Ind. Electron.*, 2000, vol. 2, pp. 453–458.

- [34] C. Yan, S. Zou, and D. Xu, "Power control for dual-input dc/ac inverter," in Proc. IEEE 6th Int. Symp. Power Electron. Distrib. Gener. Syst., Aachen, Germany, Jun. 2015, pp. 1–8.

**Dehong Xu** (M'94–SM'09–F'13) received the B.S., M.S., and Ph.D. degrees in power electronics from Zhejiang University, Hangzhou, China, in 1983, 1986, and 1989, respectively.

He was a Visiting Scholar with the University of Tokyo, Tokyo, Japan, from June 1995 to May 1996. From June to December 2000, he was a Visiting Professor with the Center for Power Electronics Systems, Virginia Tech, Blacksburg, VA, USA. From February 2006 to April 2006, he was a Visiting Professor with ETH, Zurich, Switzerland. Since 1996, he has been

with the College of Electrical Engineering, Zhejiang University, as a Full Professor. He has authored or coauthored six books and more than 200 IEEE journal or conference papers. He owns more than 40 Chinese patents and three U.S. patents. His current research interests include power electronics topology and control, and applications for energy saving and renewable energy.

Dr. Xu is an At-Large Adcom Member of the IEEE Power Electronics Society from 2017 to 2019 and from 2006 to 2008. He is an Associate Editor for the IEEE TRANSACTIONS ON POWER ELECTRONICS. He was the IEEE PELS Distinguish Lecturer in 2015–2017. He was a recipient of four IEEE journal or conference paper awards. In 2016, he received the IEEE PELS R. D. Middlebrook Achievement Award. He has been the President of the China Power Supply Society since 2013.

**Cheng Yan** was born in China, in 1987. He received the B.S. degree in electronic and information engineering in 2010 from the College of Electrical Engineering, Zhejiang University, Hangzhou, China, where he is currently working toward the Ph.D. degree in electrical engineering.

His research interests include power conversion, control, and optimization for PV power generation systems.

**Wenjie Chen** received the B.S. degree in electrical and information engineering from Zhejiang University, Hangzhou, China, in 2009, and the Ph.D. degree in power electronics from the College of Electrical Engineering, Zhejiang University, in 2015.

He worked with Aalborg University as a visiting Ph.D. student in 2013. Currently, he is a Senior Engineer working with SUNGROW POWER SUPPLY Co., Ltd., Hefei, China.