# Multiobjective Design Optimization of IGBT Power Modules Considering Power Cycling and Thermal Cycling

Bing Ji, Member, IEEE, Xueguan Song, Member, IEEE, Edward Sciberras, Wenping Cao, Senior Member, IEEE, Yihua Hu, Member, IEEE, and Volker Pickert, Member, IEEE

Abstract—Insulated-gate bipolar transistor (IGBT) power modules find widespread use in numerous power conversion applications where their reliability is of significant concern. Standard IGBT modules are fabricated for general-purpose applications while little has been designed for bespoke applications. However, conventional design of IGBTs can be improved by the multiobjective optimization technique. This paper proposes a novel design method to consider die-attachment solder failures induced by short power cycling and baseplate solder fatigue induced by the thermal cycling which are among major failure mechanisms of IGBTs. Thermal resistance is calculated analytically and the plastic work design is obtained with a high-fidelity finite-element model, which has been validated experimentally. The objective of minimizing the plastic work and constrain functions is formulated by the surrogate model. The nondominated sorting genetic algorithm-II is used to search for the Pareto-optimal solutions and the best design. The result of this combination generates an effective approach to optimize the physical structure of power electronic modules, taking account of historical environmental and operational conditions in the field.

Index Terms—Aging, fatigue, finite-element (FE) methods, insulated-gate bipolar transistors (IGBTs), multiobjective, optimization methods, power cycling (PC), reliability, thermal cycling (TC).

## I. INTRODUCTION

POWER semiconductor devices are an enabling technology to convert energy between different forms. In the last two decades, they are playing an increasingly important role in safety-critical aerospace and automotive applications where stringent reliability constraints are placed on power electronic systems. As a result, there is a pressing need to improve power electronic systems by optimized design, advanced manufacturing and packaging, as well as system integration.

Manuscript received April 1, 2014; revised September 6, 2014; accepted October 12, 2014. Date of publication October 28, 2014; date of current version December 23, 2014. This work was supported by the Engineering and Physical Sciences Research Council (EPSRC) under the Vehicle Electrical Systems Integration (VESI) Project (EP/I038543/1). Recommended for publication by Associate Editor H. Wang.

- B. Ji, E. Sciberras, and V. Pickert are with the School of Electrical and Electronic Engineering, Newcastle University, Newcastle upon Tyne, NE1 7RU, U.K.

- X. Song is with the School of Mechanical Engineering, Dalian University of Technology, Dalian 116024, China (e-mail: sxg@dlut.edu.cn).

- W. Cao is with the School of Electronics, Electrical Engineering and Computer Science, Queen's University Belfast, Belfast, BT9 5BN, U.K.

- Y. Hu is with the Department of Electronic and Electrical Engineering, University of Strathclyde, Glasgow, G1 1XW, U.K.

- Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TPEL.2014.2365531

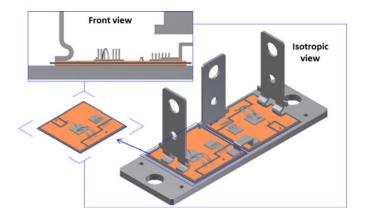

Fig. 1. Typical multilayered IGBT power module.

Insulated-gate bipolar transistor (IGBT) power modules find widespread use in various applications including renewable energy, transport and space, industry, utility and home appliances. They have been manufactured in large quantities and have dominated a large portion of the medium- and high-power conversion market for decades. Field experience shows that power electronic converters were responsible for 37% of the unscheduled maintenance for photovoltaic generation systems [1], 13% for wind turbines [2], and 38% for industrial variable speed ac drives [3]. Their failures determine the system downtime and increase the operational cost [4], [5]. Power semiconductor devices were rated as the most fragile component of a power electronic system from a recent industrial survey, followed by capacitors and gate drives [6]. The device and package-related failures account for 35% of the faults in the power electronics system [7]. The constantly growing need for power semiconductor devices coupled with important roles they have played in the system has led to corresponding reliability and robustness concerns, especially for safety-critical systems that may incur life security risks or enormous additional overall system operating cost (including maintenance, downtime, capital investment, etc).

In general, an IGBT module is comprised of one or more semiconductor chips and its package, which are equally important in providing high performance service. It is constructed with different materials (e.g., silicon, aluminum, copper, ceramics, and plastics), package designs (e.g., layout, geometry, and size) and properties (e.g., electrical, thermal, and mechanical). These components/layers are mostly bonded together by soldering and bond wires (see Fig. 1). The assembly is then covered with an insulating gel and enclosed in a polymer housing from

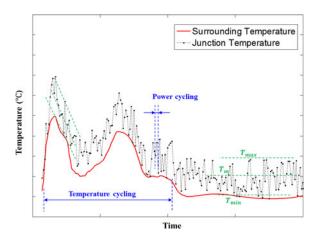

Fig. 2. TC and PC for IGBT module.

which only the metal connectors of the device terminals emerge. The base plate of the assembly is mounted onto a heat sink or other cooling devices with thermal interface material greased between them for improved thermal contact.

Current, voltage, power dissipation, and lifetime are the traditional design specifications, of IGBT power modules. In practice, they undergo harsh operational conditions (i.e., high temperature, frequent temperature cycles, and intensive vibrations) that generate repetitive stresses leading to fatigue and wear-out failures, particularly at the interconnections between different layers. Numerous accelerated aging tests have been conducted by different researchers to evaluate wear-out failures [8]–[10]. The dominant wear-out mechanisms, for example, bond wire lift-off, die–attach solder fatigue and baseplate solder fatigue, are mainly driven by thermomechanical stress that is induced by cyclic temperature swings and exposure to extreme temperatures.

The power dissipation path through the multilayered structure is constructed from different materials, characterized with individual coefficient of thermal expansion (CTE). Thermomechanical stress is generated in service at various layers and their interfaces under cyclic loadings. Power cycling (PC) and thermal cycling (TC) tests, as shown in Fig. 2, are the typical methods to evaluate the robustness and reliability [8]–[11]. The PC is exerted by the heat dissipation of power semiconductor devices when they are actively controlled. As the power loss requires finite time to conduct due to the thermal capacitance, each layer will be subject to different temperature swings dependent on the length of the dissipated power. PC can be further discriminated as short and long PC. Short power cycles are caused by the heat dissipation in relatively short intervals (e.g., a few seconds) that allow semiconductors and their direct vicinity undergoing frequent temperature changes with sizable amplitudes. However, the temperature variation in the distant baseplate solder layer is sufficiently alleviated by the large thermal capacities of substrate and baseplate. Short PC is mainly carried out to evaluate the lifetime of the bond wires and the die-attach solder layer [11]. Long power cycles normally indicate power pulses with long enough intervals (e.g., exceeding 10 s) to cause effective temperature swings and stresses in the baseplate solder layer. TC normally indicates the device temperature changes passively accompanying the ambient temperature variations. The focus of short PCT is normally the bond wire connections and the die attach solder while the baseplate solder fatigue is considered to be a dominant wear-out mechanism during long PC and TCT [11]. The device junction temperature was also factored in, showing accelerated wear-out with the raised temperature [8]. Moreover, the maximum junction temperature specified by the manufacturer (e.g., 150 or 175 °C for silicon devices) must not be exceeded under any conditions, since it may result in sudden failures such as hot spots and latch-up.

In order to achieve a robust design, numerous solutions to reduce the cyclic thermomechanical stress and junction temperature have been developed from all aspects, from design to in-field operation and from the system all the way down to the power semiconductor modules [12]–[17]. On the one hand, the thermal cycles are relieved with advanced structure design and optimized thermal management. The copper baseplate is replaced by AlSiC in some power modules to reduce the CTE mismatch between substrate and baseplate [18]. Active cooling methods were presented using coolant temperature as a feedback for flow control to reduce the temperature variation [19]. Generally, the temperature of the heat sink (either air or liquid cooled) can only be slowly regulated compared to the dynamic power loss variations from power modules due to its large thermal time constant. A thermal management technique is proposed to regulate the power losses with advanced gate control and PWM control algorithm [20]. On the other hand, methods to solve the junction temperature limitation have also been developed which fall into three categories—semiconductor, packaging and assembly, and thermal management algorithm. Semiconductor technological advancement has been observed over the past two decades thanks to the novel materials [21]-[23], improved fabrication technology [24], and optimized structures [25] that are able to sustain higher junction temperature. Advanced packaging and cooling designs have also been developed [26]–[28] to improve the thermal performance of the power assembly. The thermal conductivity of die attachment has been increased by about three times with enhanced electrical conductivity and mechanical properties [26] by replacing the solder alloy with sintered nanosilver paste. The techniques of integrating the cooling system into the power module by removing the base plate [26], or a more ambitious attempt to implement direct chip cooling [25], [27], have been proposed to minimize the thermal resistance as well as the number of interconnections, thus reducing the number of potential sources of failure. The maximum temperature is also reduced with specific modulation strategies to minimize power losses [29].

Although advances in power module techniques have contributed to improved reliability and prolonged lifetime, there is little research on the optimization of IGBT modules [30], [31]. Power modules are generally designed and manufactured to meet their typical operational and lifetime requirements. By following the engineering requirement (i.e., electrical, thermal, mechanical, cost, dimensions, etc.), it is typical to resolve the problem with a single-objective optimization target, i.e., maximizing the lifetime of IGBT modules under only one specific failure mode. In practice, an IGBT module is usually subjected to a combined fatigue loading such as PC, TC and vibration, and the

requirements of the optimal design can be inconsistent or even conflicting with each other. This means that any further lifetime improvement caused by addressing one fatigue mode can worsen the lifetime caused by other modes or increase the manufacturing complexity. For this reason, the multiobjective optimization (MOO) strategy is desirable in the design of IGBT modules. In this paper, the objective is to explain why a MOO strategy is needed for IGBT power module design and to demonstrate the implementation of a MOO considering PC and TC in practice.

#### II. MOO OF IGBT MODULES

A common single-objective optimization problem of a power module is to maximize its lifetime

$$\begin{cases} \text{Max.} : N_f \\ \text{s.t.} : X_L \le X \le X_U \end{cases} \tag{1}$$

where X is the matrix of design variables,  $X_U$  and  $X_L$  are the upper and lower bounds of X, respectively.  $N_f$  is the lifetime of the power module, which may be caused by one of the general failure modes, written in separate form as follows:

$$\begin{cases} \operatorname{Max.}: N_f^d \otimes N_f^t \otimes N_f^p \otimes N_f^v \\ \operatorname{s.t.}: X_L \leq X \leq X_U \end{cases} \tag{2}$$

where  $N_f^d$  is the lifetime of module due to material degradation [32],  $N_f^t$  is the lifetime of module due to the TC fatigue [33],  $N_f^p$  is the lifetime due to the PC fatigue [8], and  $N_f^v$  represents the lifetime due to the vibration fatigue [34]. The improvement of individual lifetime expectancy seems to be advantageous for the overall product lifetime. However, it does not necessarily increase the effective lifetime since different failure mechanisms are responsible for the four lifetime targets and they each play different roles in the aging process of power modules and require elaborated studies.

In terms of the TC fatigue mechanism, attempting to improve  $N_f^t$  requires thicker solder layers, thinner base plate, and thinner ceramics layers to reduce the thermal stress induced by the mismatch of the CTE. And in terms of structural vibration theory, attempting to improve  $N_f^v$  requires all of the layers to be as thick as possible to reduce the static stress during vibration. On the contrary, attempting to improve the  $N_f^d$  and  $N_f^p$  demands most layers to be as thin as possible, since the junction temperature of the module as well as the resultant degradation will be alleviated with reduced total thermal resistance from the die to the base plate, as the failure and degradation are proportional to the junction temperature. Therefore, the lifetime optimization of power module needs considering the failure modes separately, as different failure modes need different treatment methods. In addition, as the price of modern lead-free solder goes up, minimizing the manufacturing cost (especially the material cost) becomes necessary as well. Therefore, the single-objective optimization needs to be transformed to a MOO as follows:

$$\begin{cases}

\operatorname{Max.}: [N_f^d, N_f^t, N_f^p, N_f^v] \\

\operatorname{s.t.}: \begin{cases}

X_L \le X \le X_U \\

N_f^i \ge N_{\min}^i

\end{cases}

\end{cases}$$

(3)

where  $N_{\min}^i$  means the required minimum lifetime of the module due to the ith type of failure (material degradation, TC, powering cycling and vibration). Equation (3) can be solved as a single-objective optimization problem by retaining one objective while changing the other three objectives to constraints or by incorporating all the objectives into a single-objective by the use of arbitrary weighting factors. Such two types of approaches are easy to calculate and can provide quantitative insights into the sole objective, and restrict other constrains to some extent. However, most power module applications are rather sensitive to environmental and operational conditions, and it is thus difficult to select the most appropriate objective, define reasonable constraint levels or choose the most appropriate weighting factors. Consequently, conventional single-objective optimization is subject to a set of constraints which makes it impractical for the design optimization of power modules. As an alternative, introduction and application of a MOO strategy becomes necessary to manage more information.

## III. LIFETIME PREDICTION MODELS

In this paper, only two types of fatigue are taken into account: TC fatigue and PC fatigue.

# A. Lifetime Prediction Model Subjected to PC

For the lifetime analysis due to the PC fatigue, there is a widely used analytical lifetime model, known as the power-law model [8]. The power-law model defines the relationship between the lifetime and the junction temperature of the power module, assuming that a small power cycle has the same effect on the lifetime irrespective of whether it occurred before or after a large temperature cycle, and is given as follows:

$$N_f^p = C_1 \cdot (\Delta T_j)^{C_2} \cdot e^{\frac{Q}{R \cdot T_m}} \tag{4}$$

where  $C_1$  is a curve fitting constant of 640, exponent constant  $C_2$  is approximately equal to -5,  $\Delta T_j$  is the junction temperature,  $T_m$  is the mean temperature, and Q is the activation energy of  $7.8 \times 10^4 \ \mathrm{J/mol}$ , i.e., the smallest energy required to start the reaction, assumed to be independent of the temperature. R is the gas constant  $8.314 \ \mathrm{J/mol} \cdot \mathrm{K}$  [8]. With this model, the lifetime due to the PC can be easily estimated. For a power module used in specific condition,  $\Delta T_j$  and  $T_m$  can be described as

$$T_m = T_{\min} + \frac{1}{2}\Delta T_j \tag{5}$$

$$T_{\min} = T_{\rm amb} + R_{\rm th} \cdot P_{\min} \tag{6}$$

$$\Delta T_i = T_{\text{max}} - T_{\text{min}} = R_{\text{th}} \cdot (P_{\text{max}} - P_{\text{min}}). \tag{7}$$

Therefore, (4) can be transformed to

$$N_f^p = C_1 \cdot \left( (P_{\text{max}} - P_{\text{min}}) \cdot R_{\text{th}} \right)^{C_2}$$

$$\cdot \exp\left(\frac{Q}{R \cdot \left(T_{\rm amb} + \frac{1}{2} \left(P_{\rm max} - P_{\rm min}\right) \cdot R_{\rm th}\right)}\right). \quad (8)$$

For a specific power module under complex conditions,  $P_{\rm max}$  and  $P_{\rm min}$  are difficult to evaluate and thus the lifetime is impossible to predict. However, if the  $P_{\rm max}$  and  $P_{\rm min}$  are assumed to

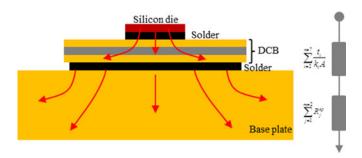

Fig. 3. Conductive and spreading thermal resistance in IGBT module.

be known, for example, for a typical power electronic module with  $R_{\rm th}=0.1\,{\rm K/W}$  and undergoing a recorded temperature difference  $\Delta T_j=30\,^{\circ}{\rm C}$ , the power loss difference  $\Delta P$  is equal to  $\frac{\Delta T_j}{R_{\rm th}}=300\,{\rm W}.$  Therefore, the lifetime will be easily obtained, as  $N_f^p$  is then only related to the total thermal resistance  $R_{\rm th}$ , which can be calculated as

$$R_{\rm th} = \sum_{i=1}^{n=6} \frac{t_i}{k_i A_i} + \sum_{j=1}^{m=2} R_j^{\rm sp}$$

(9)

where  $t_i$ ,  $k_i$ , and  $A_i$  are the thickness, thermal conductivity, and the effective area of the *i*th layer, respectively.  $R_j^{\rm sp}$  is the *j*th spreading thermal resistance, which can be approximately calculated as follows [35]:

$$R_j^{\rm sp} = \frac{\Psi_{\rm max}}{k_j \cdot r_j \cdot \sqrt{\pi}} \tag{10}$$

where  $\Psi_{\rm max}$  is the dimensionless constriction resistance,  $k_j$  is the thermal conductivity of the *j*th layer, and  $r_j$  is the source radius of the *j*th layer. See Fig. 3.

### B. Lifetime Prediction Model Subjected to TC

As the real IGBT module test subjected to TC is very time consuming and costly, finite-element analysis (FEA) is widely accepted in analyzing the failure mechanisms and predicting lifetime of the module especially during the design stage. The finite-element (FE) method provides a valuable insight into evolution characteristics of internal states in the solder joint and low cycle fatigue deformation and failure prediction of the solder [36]. Modeling an IGBT module subjected to TC involves five aspects: the life prediction model, the constitutive model, the material property, the FE model, and the thermal loading. These main steps form the basis of lifetime prediction of IGBT module subjected to TC.

1) Lifetime Prediction Model: Baseplate solder fatigue is the dominant failure mechanism under TC of the IGBT module. There exist many lifetime prediction models for determining the lifetime of solder layer in power modules and other types of electronic packages, in accordance to their own merits [37]. One of the widely accepted failure criteria was introduced by Darveaux for low cycle thermal fatigue life prediction [38]. This model describes the relationship between the volume-averaged inelastic work density increment  $\Delta W$ , and the number of cycles to crack initiation  $N_0$  and the crack propagation rate daldN:

$$N_0 = K_1 \Delta W^{K_2} \tag{11}$$

TABLE I

EMPIRICAL CONSTANTS USED FOR LIFETIME PREDICTION [38]

| Constant | $K_1$                           | $K_2$ | $K_3$                                              | $K_4$ |

|----------|---------------------------------|-------|----------------------------------------------------|-------|

| Value    | 71 000 cycles/psi <sup>K2</sup> | -1.62 | $2.76 \times 10^{-7}$ in./cycles/psi <sup>K4</sup> | 1.05  |

$$\frac{da}{dN} = K_3 \Delta W^{K_4} \tag{12}$$

where  $K_1$ ,  $K_2$ ,  $K_3$ , and  $K_4$  are the empirical constants as shown in Table I and a is the characteristic crack length. So, the characteristic lifetime  $N_f^t$  can be obtained as

$$N_f^t = N_0 + \frac{a}{da/dN}. (13)$$

The parameter defined as

$$\Delta W = \frac{\sum_{i=1}^{n} \Delta W_i \cdot V_n}{\sum_{i=1}^{n} V_n} \tag{14}$$

where  $\Delta W_i$  designates the inelastic work density in the *i*th element in FEA, whose volume is denoted by  $V_n$ .

2) Constitutive Model: To accurately calculate  $\Delta W$  in (14), a high-fidelity FE model with a precise description of the solder behavior is extremely critical. Therefore, the time- and temperature-dependent deformation behavior of the solder is one of the most important properties in the FEA. Among the various time-dependent and temperature-dependent constitutive models for solder in power modules, the viscoplastic constitutive model introduced by Anand is frequently adopted. The Anand model was originally developed for metal forming applications and quickly became popular to applications that involve strain and temperature effect including solder layer and high temperature creep. The model does not require an explicit yield condition and loading /unloading criteria because it assumes that plastic flow occurs at all nonzero stress values [39].

The Anand model consists of two coupled differential equations that relate the inelastic strain rate to the rate of deformation resistance. The strain rate equation is

$$\dot{\varepsilon}_P = A \left[ \sinh \left( \frac{\xi \sigma}{s} \right) \right]^{\frac{1}{m}} e^{-Q/RT} \tag{15}$$

where  $\dot{\varepsilon}_P$  is the inelastic strain rate, A is a constant,  $\xi$  is the stress multiplier,  $\sigma$  is the stress, s is the deformation resistance, R is the gas constant, m is the strain rate sensitivity, Q is the activation energy, and T is absolute temperature. And the rate of deformation resistance equation is

$$\dot{s} = \left\{ h_0 \left( |B| \right)^{\alpha} \frac{B}{|B|} \right\} \dot{\varepsilon}_P \tag{16}$$

where

$$B = 1 - \frac{s}{s^*} \tag{17}$$

$$s^* = \hat{s} \left[ \frac{1}{A} \dot{\varepsilon}_P e^{-Q/RT} \right]^n \tag{18}$$

| TABLE II                                |      |

|-----------------------------------------|------|

| PARAMETERS OF SAC305 IN THE ANAND MODEL | [40] |

| Parameter (unit)      | Description                                                | Values for SAC305<br>$1.0665 \times 10^6$ |  |

|-----------------------|------------------------------------------------------------|-------------------------------------------|--|

| so (MPa)              | Initial value of deformation resistance                    |                                           |  |

| Q/R (1/K)             | (1/K) Activation energy/Boltzmann's                        |                                           |  |

| A (1/s)               | Preexponential factor                                      | $8.265 \times 10^{7}$                     |  |

| $\xi$ (dimensionless) | Stress multiplier                                          | 2.55                                      |  |

| m (dimensionless)     | Strain rate sensitivity of stress                          | 0.141446                                  |  |

| $h_0$ (MPa)           | Hardening/softening constant                               | $5023.9 \times 10^{6}$                    |  |

| $\hat{s}(MPa)$        | Coefficient for saturation value of deformation resistance | $20.2976 \times 10^6$                     |  |

| n (dimensionless)     | Strain rate sensitivity of the saturation value            | $3.2472 \times 10^{-2}$                   |  |

| a (dimensionless)     | Strain rate sensitivity of the<br>hardening/softening      | 1.120371                                  |  |

TABLE III

MATERIAL PROPERTIES OF LAYERS FROM TOP TO BOTTOM

| Layer/material                            | $\rho(\text{kg/m}^3)$ | E (MPa) | v    | CTE<br>(10 <sup>-6</sup> /K) | k(W/<br>(mK)) | σ <sub>allow</sub><br>(MPa) |

|-------------------------------------------|-----------------------|---------|------|------------------------------|---------------|-----------------------------|

| Silicon die                               | 2328                  | 113 000 | 0.28 | 3                            | 90            | 107                         |

| Solder (SAC305)                           | 7400                  | 47      | 0.4  | 20                           | 40            | _                           |

| DCB copper                                | 8900                  | 115 000 | 0.34 | 17                           | 380           | 140                         |

| Ceramic (Al <sub>2</sub> O <sub>3</sub> ) | 3900                  | 370 000 | 0.22 | 6.3                          | 20            | 55                          |

| DCB copper                                | 8900                  | 115 000 | 0.34 | 17                           | 380           | 140                         |

| Solder (SAC305)                           | 7400                  | 47      | 0.4  | 20                           | 40            | _                           |

| Copper of baseplate                       | 8900                  | 115 000 | 0.34 | 17                           | 380           | 140                         |

where  $s^*$  is the saturation value of s,  $\widehat{s}$  is the coefficient for deformation resistance saturation value, and n is the strain rate sensitivity. From the development of the previous equations, there are nine material parameters that need to be defined in the Anand model. Table II shows these parameters for SAC305 alloy used in this work.

- *3) Material Properties:* The IGBT module consists of a total of seven layers of materials. The solder layers are modeled with linear elastic coupled with viscoplastic material properties. The rest including the silicon die, the two copper layers, along with the ceramic layer and the base plate are assumed to be linear elastic in the FEAs. Table III shows the material properties of the seven layers from top to bottom.

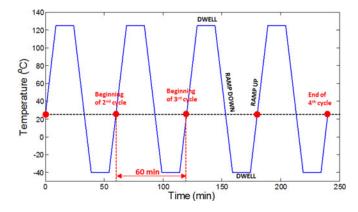

- 4) TC Load: The choice of thermal loads to evaluate the reliability of the IGBT module is important as the relative performance of the solders could change with the thermal load parameters such as maximum temperature and temperature range. This FEA was carried out using a typical thermal cycle as shown in Fig. 4, which includes beginning temperature, reference temperature, maximum temperature of 125 °C, minimum temperature of -40 °C, as well as the duration for ramp-up, ramp down, and dwell at the maximum and minimum temperatures. The beginning temperature as well as the reference temperature is assumed to be 25 °C, since any residual stress in solder will relax due to the creep characteristic of the solder [41] and there is a good agreement between the FEAs and experiments by starting the simulation at reference temperature of 25 °C [42]. Each Dwell takes 15 min, which is the same as the ramp up/down with

Fig. 4. Thermal cycles for fatigue analysis.

Fig. 5. Two-dimensional symmetrical FE model of multilayered IGBT module.

ramp rate of 10 °C/min, so one thermal cycle lasts 60 min. Four thermal cycles in the simulation are usually sufficient to ensure the stability of the hysteresis loop and test semiconductors in automotive applications [43].

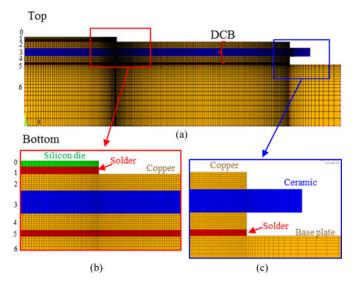

5) FE Model: The FE model in this work was conducted in Ansys 14.5, where the Ansys Parametric Design Language was used to develop a generic model with a robust mesh, despite the variation of various design. To reduce the computational time and resources used, a 2-D symmetrical FE model with one IGBT die was used as shown in Fig. 5 [30], which has been verified to be as accurate as a 3-D FE model for fatigue analysis of solder joints subject to TC [44]. The layers from 0 to 6 in Fig. 5 represent the silicon die, solder, DCB copper, ceramic, DCB copper, solder and baseplate layers, respectively. VISCO106 element type with four nodes was used to model the solder layers because of its highly nonlinear behavior, and Plane 182 element type was used to model other linear elastic layers. Fig. 5(b) and (c) shows the enlarged view of the FE model. It can be seen that fine mesh pattern is maintained in the model especially in the solder layer as the value of  $\Delta W$  is dependent on the thickness s of the elements [45]. In particular,

Fig. 6. Remaining effective solder areas in % observed by the SAM: (a) after 800 cycles and (b) after 1300 cycles.

Fig. 7. C-mode SAM detection of IGBT modules.

the maximum element thickness of the solder layers is 17.5  $\mu$ m which are adequately accurate for the calculation of  $\Delta W$  [38]. In total, 15 405 nodes and 15 040 elements have been generated for the model. Some assumptions are also made in the model, namely all seven layers are assumed homogenous, the process variations along with the manufacturing defect are not taken into account, and the intermetallic growth in the solder layers is ignored.

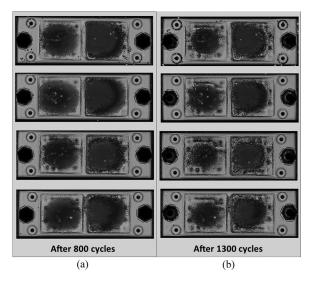

6) Experimental Validation of FE Models: The FE model was validated with TC test results prior to the MOO process. To accelerate the aging process of IGBT modules, a harsh TC profile was applied with the maximum and minimum temperature set to be 160 and  $-50\,^{\circ}$ C, respectively. The ramp up/down time was set to be 2 min with the dwell time set to be 10 min. The TC test was interrupted at 800 and 1300 cycles for inspection. Fig. 6 shows the degradation of the solder layer between the DCB substrate and the base plate with a C-mode scanning acoustic microscope (SAM) from the bottom view as shown in Fig. 7. These figures clearly show that the failure initiates around the solder edges and propagates inwards to the centre.

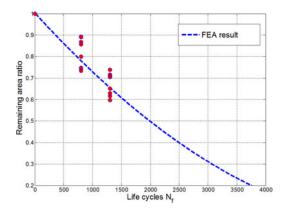

Fig. 8 compares the lifetime versus remaining area ratio between the experiments and the corresponding FEAs. The FEA

Fig. 8. Comparison of life cycles between FEAs and experiments.

results are in a good agreement with experiments, which demonstrates that the developed FE model as well as the lifetime prediction model are adequately accurate for the lifetime prediction of the IGBT module and proper for the subsequent design optimization.

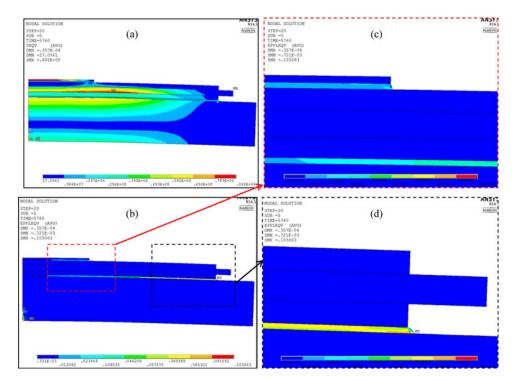

The solder layers deform plastically when subjected to temperature cycling loads. The CTE mismatch of the different bonded materials induces thermomechanical stresses in the module which is critical at the interfaces of the assembled layers. Fig. 9 presents the stress and plastic strain contour of the IGBT module at the end of the fourth thermal cycle. The deformation in Fig. 9 is scaled up by 20 times to better illustrate the bending of each layer. As shown in Fig. 9(a), the maximum elastic stress of 54.07 MPa occurs at the central interface of the ceramic layer and the copper layer, which is attributed to the mismatch in length of different layers. Silicon die and base plate also suffer evident stress of 49.06 and 41.82 MPa, respectively.

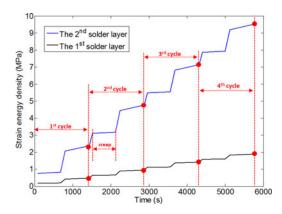

As shown in Fig. 9(b)–(d), the maximum plastic strain is located at the baseplate solder layer near the edge. The plastic strain in the first solder layer is modest compared with that of the baseplate solder layer, which is in agreement with the experimental result. It should be noted that the plastic work is only the output of viscoplastic elements; thus, in the figures, only solder layers are seen with plastic work and the rest corresponds to zero plastic work masked in blue. Fig. 10 plots the change of the strain energy density at the outmost node of the two solder layers over the four thermal cycles. The curve shows that strain energy density increases during the dwell period though the change is relatively small compared with that during the ramp up/down period. This is because the creep phenomenon exists during the dwell period and its effect is included in the plastic strain in Anand model.

# IV. PROBLEM DEFINITION

The objective of this work is to improve the lifetime of the module subject to both PC and TC by varying the thickness of the six layers. Therefore, the objective functions can be expressed as

objective :

$$\begin{cases} \text{Maximize} & N_f^t(\mathbf{t}) \\ \text{Maximize} & N_f^p(\mathbf{t}). \end{cases}$$

(19)

Fig. 9. Distribution of von-Mises stress and plastic strain after the fourth cycle.

Fig. 10. Strain energy density histories of the two solder layers during TC.

As mentioned earlier, for a specific power module used in specific conditions,  $N_f^p$  is a function of total thermal resistance  $R_{\rm th}$ . The smaller the  $R_{\rm th}$ , the larger the  $N_f^p$ . For the lifetime subject to TC  $N_f^t$ , it is beneficial to decrease  $\Delta W$  as much as possible to increase  $N_f^t$ . Therefore, to reduce the equation transform, the objective function can be altered to

objective :

$$\begin{cases} \text{Minimize} & \Delta W_{\text{solder2}} \\ \text{Minimize} & R_{\text{th}}. \end{cases}$$

(20)

Since there are other elastic layers in the module, the reliability of these layers under the repeated thermal loads is mandatory as well. Therefore, five constraints are defined as follows:

s.t.:

$$\begin{cases} \sigma^{i} \leq \sigma_{\text{allow}}^{i} \\ \Delta W_{\text{solder1}} \leq \eta \cdot \Delta W_{\text{solder2}} \end{cases}$$

(21)

where  $\sigma^i$  and  $\sigma^i_{

m allow}$  are the maximum von-Mises stress and the allowed stress of the *i*th elastic layer, respectively.  $\Delta W_{\mathrm{solder}1}$  and  $\Delta W_{\mathrm{solder}2}$  are the inelastic work density in the die-attach and baseplate solder layers, respectively, and  $\eta$  is a constant ensuring less inelastic work density (i.e., longer life) of the former compared to the latter. As the width of the die-attach solder layer and baseplate layer are 9 and 26 mm, resulting in a ratio of  $9/26 \approx 0.35$ ,  $\eta$  is set to be 0.25 in this work to ensure a high reliability. It should be noted that total four layers from the silicon die to the base plate excluding these two solder layers have the elastic stress constraints as shown in Table I. The six design variables are the thickness of the six layers excluding the silicon die which is considered fixed. The layer thicknesses have constraints in terms of upper and lower limits which the variables can take. Specifically, the lower bound in Table IV is defined in terms of a commercially available power module in which the thickness of solder layers is the thinnest thickness the company can manufacture, and the upper bound is specified by the authors to make a reasonable search domain for the optimization.

## V. SURROGATE-BASED MOO (SBMOO)

During the optimization process,  $\Delta W$  and  $R_{\rm th}$  are iteratively calculated in terms of the possible combination of the six design variables. The calculation of  $R_{\rm th}$  is easy and fast because the analytical solution in (11) and (12) is straightforward. However, the calculation of each  $\Delta W$  and  $\sigma^i$  is more difficult and costly, penalizing optimization searches as it requires a costly and lengthy nonlinear FEA. Hence, an efficient optimization method is essential for the optimization using the FE model. In this work, the SBMOO is adopted, whose goal is to reduce computational

TABLE IV DESIGN SPACE FOR THE SIX DESIGN VARIABLES FROM TOP TO BOTTOM (UNIT:  $\operatorname{mm}$ )

|             | $t_1$ | $t_2$ | $t_3$ | $t_4$ | $t_5$ | $t_6$ |

|-------------|-------|-------|-------|-------|-------|-------|

| Upper bound | 0.15  | 0.4   | 0.46  | 0.4   | 0.2   | 4 2   |

| Lower bound | 0.08  | 0.2   | 0.36  | 0.2   | 0.08  |       |

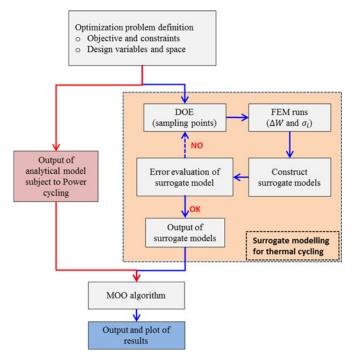

Fig. 11. Structure of the SBMOO algorithm for IGBT module optimization.

iterations while obtaining desirable results. The SBMOO consists of an interpolation function developed based on a design of experiments (DoE) and MOO algorithm for a Pareto-optimal search. The entire workflow is illustrated in Fig. 11 and consists of the following steps:

- 1) define objectives, constraints, design variables and design space for the optimization;

- produce the DoE using the Latin hypercube sampling (LHS) method;

- 3) calculate  $\Delta W$  and  $\sigma^i$  at each design points with the FE model;

- build surrogate model for the objective and constrains (Kriging model);

- 5) minimize errors of the surrogate models;

- 6) output the surrogate models for the TC along with the analytical model for the PC;

- 7) perform MOO using the MOO algorithm [nondominated sorting genetic algorithm-II (NSGA-II)];

- 8) select optimal candidates and plot results.

# A. Kriging Surrogate Model [46], [47]

This work uses a widely used surrogate model, namely a Kriging (KRG) model, to evaluate the approximation models of the objective and constraint functions for the TC. The Kriging

model was originally developed for mining and geostatistical application involving spatially and temporally correlated data.

In general, the Kriging model combines a global model plus a localized departure, and can be formulated as follows:

$$f(x) = \beta + z(x) \tag{22}$$

where f(x) is the unknown function of interest,  $\beta$  denotes a known approximation function (usually polynomial), and z(x) stands for a stochastic component in terms of zero mean and variance  $s^2$  with the Gaussian distribution. Letting  $\hat{f}(\mathbf{x})$  be an approximation function to the true function f(x), by minimizing the mean-squared error (MSE) between f(x) and  $\hat{f}(\mathbf{x})$ ,  $\hat{f}(\mathbf{x})$  can be calculated as

$$\hat{f}(\mathbf{x}) = \hat{\beta} + \mathbf{r}^{\mathbf{T}}(\mathbf{x})\mathbf{R}^{-1}(\mathbf{f} - \hat{\beta}\mathbf{q})$$

(23)

where  $R^{-1}$  is the inverse of correlation matrix R, r is the correlation vector, f is the observed data at  $n_s$  sample points, and  $\mathbf{q}$  is the unity vector with  $n_s$  components. The random variables are correlated to each other using the basis function of

$$R(\mathbf{x}^{j}, \mathbf{x}^{k}) = \operatorname{Exp}\left[-\sum_{i=1}^{m} \theta_{i} \left| x_{i}^{j} - x_{i}^{k} \right|^{2}\right],$$

$$(j = 1, \dots, n_{s} \ k = 1, \dots, n_{s}) \tag{24}$$

where  $\theta_i$  is the *i*th parameter corresponding to the *i*th variable. The Kriging model is built with an assumption that there is no error in f; the likelihood can therefore be expressed in terms of the sampling data as

$$L = \frac{1}{(2\pi s^2)^{n/2} |\mathbf{R}|^{1/2}} \exp\left[-\frac{(\mathbf{f} - \beta \mathbf{q})^{\mathrm{T}} \mathbf{R}^{-1} (\mathbf{f} - \beta \mathbf{q})}{2s^2}\right].$$

(25)

To simplify the maximization of likelihood, (25) can be replaced by (26) by taking a natural logarithmic transformation

$$\ln(L) = -\frac{n}{2}\ln(2\pi) - \frac{n}{2}\ln(s^2) - \frac{1}{2}\ln|\mathbf{R}|$$

$$-\frac{(\mathbf{f} - \beta\mathbf{q})^T\mathbf{R}^{-1}(\mathbf{f} - \beta\mathbf{q})}{2s^2}.$$

(26)

By conducting the derivatives of the ln-likelihood function in (26) with respect to  $\beta$  and s, respectively, and setting them to zero, the maximum likelihood estimators (MLEs) of  $\beta$  and  $s^2$  are determined as follows:

$$\hat{\beta} = (\mathbf{q}^{\mathrm{T}} \mathbf{R}^{-1} \mathbf{q})^{-1} \mathbf{q} \mathbf{R}^{-1} \mathbf{f}$$

(27)

$$\hat{s}^2 = \frac{(\mathbf{f} - \hat{\beta}\mathbf{q})^{\mathrm{T}}\mathbf{R}^{-1}(\mathbf{f} - \hat{\beta}\mathbf{q})}{n_s}.$$

(28)

These MLEs can now be substituted back into (26) by removing the constant terms to give what is known as the concentrated In-likelihood function, and the unknown parameters of  $\theta_i(\theta_i > 0)$  can be calculated by maximizing the formula as follows:

maximize

$$-\frac{n_s}{2}\ln(\hat{s}^2) - \frac{1}{2}\ln|\mathbf{R}|$$

. (29)

In this study, the method of modified feasible direction is utilized to determine the optimum values of parameter  $\theta_i$ . And

the estimated MSE of the predictor is derived as follows:

$$\hat{e}^2 = \hat{s}^2 \left[ 1 - \mathbf{r}^{\mathrm{T}} \mathbf{R}^{-1} \mathbf{r} + \left[ \frac{(1 - \mathbf{q}^{\mathrm{T}} \mathbf{R}^{-1} \mathbf{r})^2}{\mathbf{q}^{\mathrm{T}} \mathbf{R}^{-1} \mathbf{q}} \right] \right].$$

(30)

# B. NSGA-II

Genetic algorithms are a form of search heuristic which takes inspiration from natural evolutionary processes to identify optimal solutions to the problem being addressed. A solution exists in two domains, namely the solution space as well as objective space. In the former domain, a solution is described by its characteristics in terms of the variables, i.e., the various layer thicknesses. This takes this form of a string of code where each element defines the thickness of one layer. In keeping with the biological analogy, this string is termed a chromosome. Each solution is also associated with its value in objective space, i.e., the resultant  $\Delta W$  and  $R_{\rm th}$  for each chromosome. The set of chromosomes is termed a population, and by considering the correlation between a chromosome's location in population space and its location in objective space (fitness), a search can be steered toward locating better solutions.

The optimization process is an iterative one, whereby new chromosomes are created, evaluated in objective space, and in turn used to help identify better solutions to create a new generation. This is done by randomly selecting solutions, ranking according to fitness and mixing elements between chromosomes in order to generate offspring solutions. This process is repeated for a preset number of generations (or until a predetermined accuracy is reached) [48]. The definition of a "better" solution is slightly different in the case of multiple objectives, and is handled by the concept of Pareto-dominance.

A solution is said to Pareto-dominate another, if and only if it is strictly better in all objectives. If a solution is only worse off in one objective, but better in another, then the two solutions form a Pareto-front, giving a set of equally optimum, compromise solutions. The final solution is then chosen from this Pareto-set [49].

A popular genetic algorithm which handles multiple objectives using the concept of Pareto-dominance is the NSGA-II which is able to handle constraints as well as requiring a minimum amount of external parameters [50]. This makes it suited for robustly handling a range of different problems. The pseudocode for the NSGA-II is given next:

- 1) create initial random population of size *N*;

- 2) evaluate  $\Delta W$  and  $R_{\rm th}$  for each solution;

- 3) use binary tournament selection, recombination and mutation operators to create offspring population of *N*;

- 4) sort combined parent and offspring population (of size 2N) into Pareto-ranks using fast nondominated sorting;

- 5) create new generation population by selecting the first *N* population members;

- 6) repeat from step 3.

Constraints are handled in the selection operation, where chromosomes are selected for reproduction based on their Pareto-fitness. If both are in the same rank, a solution which does not violate the constraints is selected, and if both solutions are infeasible, then the one with the least degree of constrain violation is selected. Finally, if both are feasible and do not

$\label{thm:table v} TABLE\ V$  Details of the NSGA-II Parameters Used in This Study

| NSGA-II parameter name   | Value |  |

|--------------------------|-------|--|

| Population size          | 100   |  |

| Number of generations    | 100   |  |

| Probability of crossover | 0.5   |  |

| Mutation probability     | 0.5   |  |

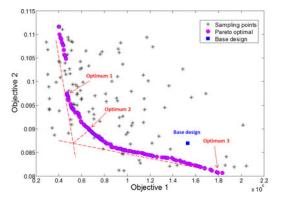

Fig. 12. Pareto-solutions of multiple-objective optimization.

dominate each other, then the solution in the least crowded region of objective space is selected in order to focus the search toward sparser regions [50].

The previous process is repeated for a set number of iterations and finally gives a set of Pareto-optimal solutions. The diversity operator ensures that the solutions are spread out in order to explore all areas of the search space to ensure better location of a global (as opposed to local) optimum.

## VI. TEST RESULTS

To ensure that the surrogate models reach the accuracies required, a total of 124 sampling points (i.e., 124 FEA runs) were generated, where 60 are the initial LHS points and the other 64 are the sequential infill points near the regions or interest. NSGA-II was then used with the parameters as defined in Table V to identify the Pareto-solutions.

Fig. 12 indicates the sampling points and the Pareto-optimal solutions for the two objective functions after 100 generations of the search algorithm. It is observed that many sampling designs are infeasible designs in terms of the constrained condition, though they seem to be better than the Pareto-optimal. For the Pareto-optimal,  $\Delta W$  can be decreased from 2 to 0.4 MPa, while the total thermal resistance  $R_{\rm th}$  can be reduced from 0.11 to 0.09.  $\Delta W$  and  $R_{\rm th}$  are strongly competing with each other and cannot reach an optimum simultaneously. In other words, any further improvement of the lifetime during PC must worsen that during the TC and vice versa. Therefore, it can be suggested from this result that it is better for the designer or engineer of IGBT module to comprehend the practical operational conditions (i.e., cooling ambient conditions and mission profiles).

Optimums 1–3 in Fig. 12 are all feasible solutions and it is difficult to choose the best one without knowing the power/TC information of a specific application. Since the results in Fig. 12 are all equally optimal solutions, it is difficult to choose the best

| TABLE VI                                      |

|-----------------------------------------------|

| OPTIMAL SOLUTIONS AND BASE DESIGN COMPARISONS |

|                         | Base design          | Optimum 1            | Optimum 2            | Optimum 3            |

|-------------------------|----------------------|----------------------|----------------------|----------------------|

| $t_1(mm)$               | 0.090                | 0.0095               | 0.0093               | 0.0080               |

| $t_2  (\mathrm{mm})$    | 0.300                | 0.0315               | 0.0335               | 0.040                |

| $t_3  (\mathrm{mm})$    | 0.400                | 0.0453               | 0.0390               | 0.036                |

| $t_4  (\mathrm{mm})$    | 0.300                | 0.0373               | 0.0339               | 0.0266               |

| $t_5  (\mathrm{mm})$    | 0.090                | 0.0152               | 0.0101               | 0.0080               |

| $t_6  (\mathrm{mm})$    | 3.000                | 0.2200               | 0.2205               | 0.3161               |

| $\Delta W_{ m solder2}$ | 1 530 539            | 470 258              | 665 488              | 1 793 800            |

|                         |                      | -69.28%              | -56.52%              | +17.20%              |

| $R_{ m th}$             | 0.087                | 0.0975               | 0.09                 | 0.0807               |

|                         |                      | +12.07%              | 3.45%                | -7.24%               |

| $N_f^t$                 | $1.29 \times 10^{3}$ | $4.48 \times 10^{3}$ | $4.43 \times 10^{3}$ | $1.09 \times 10^{3}$ |

| ,                       |                      | +247.29%             | +243.41%             | -15.50%              |

| $N_f^p$                 | $5.47 \times 10^{8}$ | $2.67 \times 10^{8}$ | $4.43 \times 10^{8}$ | $8.73 \times 10^{8}$ |

| J                       |                      | -51.19%              | -19.01%              | +59.60%              |

one. Therefore, a process of decision-making for selection of the final optimal solution from the available solutions is needed. One of the classical decision-making processes is performed with the aid of a hypothetical point, named as equilibrium point, i.e., the optimum 2 as shown in Fig. 12, for which both objectives have their optimal values independent of the other objective. The other widely used process is to select a better value for each objective than its initial value from the base design. In terms of these two methods, three optimum solutions are selected among all the possible solutions as shown in Fig. 12 and Table VI. Optimum 1 has the minimum  $\Delta W$  and the longest lifetime during TC; solution 3 has the minimum  $R_{\rm th}$  and the longest lifetime during PC. Solution 2 seems to be a good compromise with respect to the two objectives, i.e., higher reliability during both thermal and PC. With regard to the lifetime, the assumption is that they are put in the same environments and operation conditions with power loss of 300 W in the PC (see Section III-A), temperature variation of 175 °C in the TC (see Section III-B4), and with the failure criteria defined as failure length reaching 10% total length. In terms of the equations derived previously, optimum 1 will have 3.5 times lifetime during TC than the based design; however, its lifetime during PC will decrease to half of the base designs. These are summarized in Table VI, which compares the three optimized solutions with the base design (typical solution), clearly showing the conflicting nature of the optimization objectives.

It is easily understood that the thickness reduction of any layer will decrease the thermal resistance and thus the lifetime during PC. For the TC, it can be concluded that the second solder layer should be designed a little thicker than the first solder layer to prevent the TC failure, as it is the most significant layer to prevent the solder fatigue. The same phenomenon can also be observed in the two copper layers of DCB substrate. Conventional designs make them equal; however, it is shown in this work that different thicknesses will not only help decrease the thermal resistance but also decrease the stress and strain in the layers. Concern of ceramic layer should be addressed more closely, because decreasing this layer will significantly decrease the thermal resistance and help decrease the energy accumulated in the second solder layer; however, the elastic stress will be likely to reach the allowed value as well.

## VII. CONCLUSION

This paper has presented a MOO for multilayered IGBT power modules considering both TC and PC with the thickness of the constituent layers as the optimization targets. Two objectives of maximizing the lifetime under PC and TC are simultaneously considered by minimizing the total thermal resistance and the plastic work accumulated in the solder layer through equation transformation.

Thermal resistance is calculated analytically and the plastic work is obtained with a high-fidelity FE model, which has been experimentally validated. The objective of minimizing the plastic work and constrain functions is formulated by the surrogate model, which reduces computational time and cost. The NSGA-II is used to search for the Pareto-optima in the last step. The results indicate that: 1) the optimization objectives determined by PC and TC are conflicting. This is due to the different failure mechanisms induced by PC and TC, so a MOO considering both effects simultaneously is necessary. 2) During MOO, Pareto-optimal solutions could be identified and selected effectively in accordance to various environmental and operational conditions.

In summary, this work presents a novel and efficient way different from existing ones to optimize the structure of power electronic modules, especially for the power modules under special environmental and operational conditions.

#### ACKNOWLEDGMENT

The authors would like to thank Dr. W. Zhuang and Mr. E. Yao in NanJing SilverMicro Electronics, Ltd., China, and Dr. X. Xue at Newcastle University for their constructive suggestions.

# REFERENCES

- [1] L. M. Moore and H. N. Post, "Five years of operating experience at a large utility-scale photovoltaic generating plant," *Prog. Photovolt.: Res. Appl.*, vol. 16, no. 3, pp. 249–259, 2008.

- [2] Reliawind. (2011). Report on Wind Turbine Reliability Profiles—Field Data Reliability Analysis [Online]. Available: http://www.reliawind.eu/files/fileinline/110502\_Reliawind\_Deliverable\_ D.1.3ReliabilityProfilesResults.pdf

- [3] F. W. Fuchs, "Some diagnosis methods for voltage source inverters in variable speed drives with induction machines—A survey," in *Proc. 29th Annu. Conf. IEEE Ind. Electron. Soc.*, vol. 2, 2003, pp. 1378–1385.

- [4] A. Ristow, M. Begovic, A. Pregelj, and A. Rohatgi, "Development of a methodology for improving photovoltaic inverter reliability," *IEEE Trans. Ind. Electron.*, vol. 55, no. 7, pp. 2581–2592, Jul. 2008.

[5] E. Koutroulis and F. Blaabjerg, "Design optimization of transformerless

- [5] E. Koutroulis and F. Blaabjerg, "Design optimization of transformerless grid-connected PV inverters including reliability," *IEEE Trans. Power Electron.*, vol. 28, no. 1, pp. 325–335, Jan. 2013.

- [6] Y. Shaoyong, A. Bryant, P. Mawby, X. Dawei, R. Li, and P. Tavner, "An industry-based survey of reliability in power electronic converters," *IEEE Trans. Ind. Appl.*, vol. 47, no. 3, pp. 1441–1451, May/Jun. 2011.

- [7] J. Hudgins, "Power electronic devices in the future," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 1, no. 1, pp. 11–17, Mar. 2013.

- [8] M. Held, P. Jacob, G. Nicoletti, P. Scacco, and M. Poech, "Fast power cycling test for IGBT modules in traction application," in *Proc. Power Electron. Drive Syst.*, 1997, pp. 425–430.

- [9] R. Bayerer, T. Herrmann, T. Licht, J. Lutz, and M. Feller, "Model for power cycling lifetime of IGBT modules—Various factors influencing lifetime," in *Proc. 5th Int. Conf. Integr. Power Syst.*, 2008, pp. 37–42.

- [10] U. Scheuermann, "Reliability challenges of automotive power electronics," *Microelectron. Rel.*, vol. 49, no. 9–11, pp. 1319–1325, 2009.

- [11] T. Herrmann, M. Feller, J. Lutz, R. Bayerer, and T. Licht, "Power cycling induced failure mechanisms in solder layers," in *Proc. Eur. Conf. Power Electron. Appl.*, Sep. 2007, pp. 1–7.

- [12] S. Harb and R. S. Balog, "Reliability of candidate photovoltaic module-integrated-inverter (PV-MII) topologies—A usage model approach," *IEEE Trans. Power Electron.*, vol. 28, no. 6, pp. 3019–3027, Jun. 2013.

- [13] S. Yang, D. Xiang, A. Bryant, P. Mawby, R. Li, and P. Tavner, "Condition monitoring for device reliability in power electronic converters: A review," *IEEE Trans. Power Electron.*, vol. 25, no. 11, pp. 2734–2752, Nov. 2010.

- [14] Y. Song and B. Wang, "Survey on reliability of power electronic systems," IEEE Trans. Power Electron., vol. 28, no. 1, pp. 591–604, Jan. 2013.

- [15] H. Wang, M. Liserre, and F. Blaabjerg, "Toward reliable power electronics: Challenges, design tools, and opportunities," *IEEE Trans. Ind. Electron. Mag.*, vol. 7, no. 2, pp. 17–26, Jun. 2013.

- [16] B. Ji, V. Pickert, W. Cao, and B. Zahawi, "In situ diagnostics and prognostics of wire bonding faults in IGBT modules for electric vehicle drives," IEEE Trans. Power Electron., vol. 28, no. 12, pp. 5568–5577, Dec. 2013.

- [17] H. Wang, M. Liserre, F. Blaabjerg, P. Rimmen, J. Jacobsen, T. Kvisgaard, and J. Landkildehus, "Transitioning to physics-of-failure as a reliability driver in power electronics," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 2, no. 1, pp. 97–114, Mar. 2014.

- [18] G. Coquery and R. Lallemand, "Failure criteria for long term accelerated power cycling test linked to electrical turn off SOA on IGBT module. A 4000 hours test on 1200 A–3300 V module with AlSiC base plate," *Microelectron. Rel.*, vol. 40, pp. 1665–1670, Aug.–Oct. 2000.

- [19] X. Wang, A. Castellazzi, and P. Zanchetta, "Temperature control for reduced thermal cycling of power devices," in *Proc. 15th Eur. Conf. Power Electron. Appl.*, Sep. 2013, pp. 1–10.

- [20] Y. Wu, M. Shafi, A. Knight, and R. McMahon, "Comparison of the effects of continuous and discontinuous PWM schemes on power losses of voltage-sourced inverters for induction motor drives," *IEEE Trans. Power Electron.*, vol. 26, no. 1, pp. 182–191, Jan. 2011.

- [21] J. Jordan, V. Esteve, E. Sanchis-Kilders, E. J. Dede, E. Maset, J. B. Ejea, and A. Ferreres, "A comparative performance study of a 1200 V Si and SiC MOSFET intrinsic diode on an induction heating inverter," *IEEE Trans. Power Electron.*, vol. 29, no. 5, pp. 2550–2562, May 2014.

- [22] Z. Xu, M. Li, F. Wang, and Z. Liang, "Investigation of Si IGBT operation at 200 °C for traction applications," *IEEE Trans. Power Electron.*, vol. 28, no. 5, pp. 2604–2615, May 2013.

- [23] H. Zhang, L. Tolbert, and B. Ozpineci, "Impact of SiC devices on hybrid electric and plug-in hybrid electric vehicles," *IEEE Trans. Ind. Appl.*, vol. 47, no. 2, pp. 912–921, Mar./Apr. 2011.

- [24] N. Luther-King, M. Sweet, and E. Madathil Sankara Narayanan, "Clustered insulated gate bipolar transistor in the super junction concept: The SJ-TCIGBT," *IEEE Trans. Power Electron.*, vol. 27, no. 6, pp. 3072–3080, Jun. 2012.

- [25] K. Vladimirova, J. C. Crebier, Y. Avenas, and C. Schaeffer, "Drift region integrated microchannels for direct cooling of power electronic devices: Advantages and limitations," *IEEE Trans. Power Electron.*, vol. 28, no. 5, pp. 2576–2586, May 2013.

- [26] G. Chen, D. Han, Y. Mei, X. Cao, T. Wang, X. Chen, and G. Lu, "Transient thermal performance of IGBT power modules attached by low-temperature sintered nanosilver," *IEEE Trans. Device Mater. Rel.*, vol. 12, no. 1, pp. 124–132, Mar. 2012.

- [27] R. Skuriat and C. Johnson, "Direct substrate cooling of power electronics," in *Proc. 13th Eur. Conf. Power Electron. Appl.*, Sep. 8–10, 2009, pp. 1–10.

- [28] P. Ning, Z. Liang, and F. Wang, "Power module and cooling system thermal performance evaluation for HEV application," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 2, no. 3, pp. 487–495, Sep. 2014.

- [29] A. Trzynadlowski and S. Legowski, "Minimum-loss vector PWM strategy for three-phase inverters," *IEEE Trans. Power Electron.*, vol. 9, no. 1, pp. 26–34, Jan. 1994.

- [30] X. Xue, C. Bailey, H. Lu, and S. Stoyanov, "Integration of analytical techniques in stochastic optimization of microsystem reliability," *Microelectron. Rel.*, vol. 51, no. 5, pp. 936–945, 2011.

- [31] A. Zéanh, O. Dalverny, M. Karama, E. Woirgard, S. Azzopardi, A. Bouzourene, J. Casutt, and M. Mermet-Guyennet, "Proposition of IGBT modules assembling technologies for aeronautical applications," in *Proc. Int. Conf. Integr. Power Electron. Syst.*, Sep. 2008, pp. 1–6.

- [32] C. Mauro, "Selected failure mechanisms of modern power modules," *Microelectron. Rel.*, vol. 42, no. 4, pp. 653–667, 2002.

[33] T. Y. Hung, C. J. Huang, C. C. Lee, C. C. Wang, K. C. Lu, and

- [33] T. Y. Hung, C. J. Huang, C. C. Lee, C. C. Wang, K. C. Lu, and K. N. Chiang, "Investigation of solder crack behavior and fatigue life of the power module on different thermal cycling period," *Microelectron*. *Eng.*, vol. 107, pp. 125–129, 2013.

- [34] K. Sasaki and N. Ohno, "Fatigue life evaluation of aluminum bonding wire in silicone gel under random vibration testing," *Microelectron. Rel.*, vol. 53, no. 9, pp. 1766–1770, 2013.

- [35] R. Simons, "Simple formulas for estimating thermal spreading resistance," Electron. Cooling, May 2004.

- [36] K. C. Otiaba, R. S. Bhatti, N. N. Ekere, S. Mallik, and M. Ekpu, "Finite element analysis of the effect of silver content for Sn–Ag–Cu alloy compositions on thermal cycling reliability of solder die attach," *Eng. Failure Anal.*, vol. 28, pp. 192–207, 2013.

- [37] W. W. Lee, L. T. Nguyen, and G. S. Selvaduray, "Solder joint fatigue models: Review and applicability to chip scale packages," *Microelectron. Rel.*, vol. 40, no. 2, pp. 231–244, 2000.

- [38] R. Darveaux, "Effect of simulation methodology on solder joint crack growth correlation," J. Electron. Packag., vol. 124, no. 3, pp. 147–154, 2002.

- [39] G. Muralidharan, K. Kurumaddali, A. K. Kercher, and S. G. Leslie, "Reliability of Sn-3.5 Ag solder joints in high temperature packaging applications," in *Proc. 60th Electron. Compon. Technol. Conf.*, Jun. 2010, pp. 1823–1829.

- [40] D. Herkommer, J. Punch, and M. Reid, "Life prediction of SAC305 interconnects under temperature cycling conditions using an arbitrary loading fatigue model," in *Proc. ASME InterPACK Conf. Collocated ASME Sum*mer Heat Transf. Conf. ASME 3rd Int. Conf. Energy Sustainability, Jul. 2009, pp. 737–742.

- [41] H. Mavoori, J. Chin, S. Vaynman, B. Moran, L. Keer, and M. Fine, "Creep, stress relaxation, and plastic deformation in Sn-Ag and Sn-Zn eutectic solders," *J. Electron. Mater.*, vol. 26, no. 7, pp. 783–790, 1997.

- [42] A. Guedon-Gracia, E. Woirgard, and C. Zardini, "Reliability of lead-free BGA assembly: Correlation between accelerated ageing tests and FE simulations," *IEEE Trans. Device Mater. Rel.*, vol. 8, no. 3, pp. 449–454, Sep. 2008.

- [43] R. Müller-Fiedler and V. Knoblauch, "Reliability aspects of microsensors and micromechatronic actuators for automotive applications," *Microelectron. Rel.*, vol. 43, no. 7, pp. 1085–1097, 2003.

- [44] F. X. Che and J. H. Pang, "Fatigue reliability analysis of Sn-Ag-Cu solder joints subject to thermal cycling," *IEEE Trans. Device Mater. Rel.*, vol. 13, no. 1, pp. 36–49, Mar. 2013.

- [45] G. Gustafsson, I. Guven, V. Kradinov, and E. Madenci, "Finite element modeling of BGA packages for life prediction," in *Proc. 50th Electron. Compon. Technol. Conf.*, 2000, pp. 1059–1063.

- [46] X. G. Song, J. H. Jung, H. J. Son, J. H. Park, K. H. Lee, and Y. C. Park, "Metamodel-based optimization of a control arm considering strength and durability performance," *Comput. Math. Appl.*, vol. 60, no. 4, pp. 976–980, 2010.

- [47] G. Y. Sun, X. G. Song, S. K. Baek, and Q. Li, "Robust optimization of foam-filled thin-walled structure based on sequential Kriging metamodel," *Struct. Multidisciplinary Optimization*, vol. 49, no. 6, pp. 897–913, 2013.

- [48] D. E. Goldberg, Genetic Algorithms in Search, Optimization, and Machine Learning. Reading, MA, USA: Addison-Wesley, 1989.

- [49] A. Konak, D. W. Coit, and A. E. Smith, "Multi-objective optimization using genetic algorithms: A tutorial," *Rel. Eng. Syst. Safety*, vol. 91, pp. 992–1007, 2006.

- [50] K. Deb, A. Pratap, S. Agarwal, and T. Meyarivan, "A fast and elitist multiobjective genetic algorithm: NSGA-II," *IEEE Trans. Evol. Comput.*, vol. 6, no. 2, pp. 182–197, Apr. 2002.

**Bing Ji** (M<sup>1</sup>13) received the M.Sc. and Ph.D. degrees in electrical and electronic engineering from Newcastle University, Newcastle upon Tyne, U.K., in 2007 and 2012, respectively.

He was a Power Electronics Engineer with a UK low-emission vehicle company from 2012, where he worked on powertrain for electric vehicles and battery management systems. Since 2013, he has been a Postdoctoral Researcher at Newcastle University, where he is involved in accurate power loss measurement and health management for power electronics.

His research interests include reliability of power semiconductor devices, batteries and converters, function integration of gate drivers, electrothermal modeling, thermal management and high power-density converter integration for electric vehicle applications.

Dr. Ji is a Member of the Institution of Engineering and Technology.

**Xueguan Song** (M'13) received the B.S. degree in mechanical engineering from the Dalian University of Technology, Dalian, China, in 2004, and the M.S. and Ph.D. degrees in mechanical engineering from Dong-A University, Busan, South Korea, in 2007 and 2010, respectively.

He is currently a Professor in the School of Mechanical Engineering, Dalian University of Technology. He has published more than 30 peer-reviewed papers, one book and one book chapter in various research fields including engineering optimization,

computational fluid dynamics (CFD) analysis, thermal management and power electronics. His research interest includes multidisciplinary design optimization, electronic packaging design, reliability and modeling, CFD and thermal management.

Dr. Song received the Best Paper Award at LDIA'13 Conference, Best Poster Awards at CSO 2011 and PCO'2010 Conferences, and Honorable Mention Award in the PhD student paper symposium and competition at the 2010 ASME PVP Conference.

Edward Sciberras received the B.Eng. (Hons.) degree in electrical engineering from the University of Malta, Msida, Malta, and the M.Sc. degree in marine electrical power technology from Newcastle University, Newcastle upon Tyne, U.K., where, since July 2011, he has been a Research Associate working toward the Ph.D. degree on the topic of shipboard power systems in the School of Electrical and Electronic Engineering.

Wenping Cao (M'05–SM'11) received the B.Eng. degree in electrical engineering from Beijing Jiaotong University, Beijing, China, in 1991, and the Ph.D. degree in electrical machines and drives from the University of Nottingham, Nottingham, U.K., in 2004.

He is currently a Senior Lecturer at Queen's University Belfast, Belfast, U.K. His research interests are in thermal performance of electric machines, drives and power electronics.

Dr. Cao received the Best Paper Award at the LDIA'13 Conference. He serves as an Associate Ed-

itor for the IEEE TRANSACTIONS ON INDUSTRY APPLICATIONS, IEEE INDUSTRY APPLICATIONS MAGAZINE, *IET Power Electronics*, and nine other International Journals. He is also a Member of the Institution of Engineering and Technology and a Fellow of Higher Education Academy.

**Yihua Hu** (M'13) received the B.S. degree in electrical motor drives and the Ph.D. degree in power electronics and drives, both from the China University of Mining and Technology, Jiangsu, China, in 2003 and 2011, respectively.

Between 2011 and 2013, he was with the College of Electrical Engineering, Zhejiang University, as a Postdoctoral Fellow. Between November 2012 and February 2013, he was an Academic Visiting Scholar with the School of Electrical and Electronic Engineering, Newcastle University, Newcastle upon

Tyne, U.K. He is currently a Research Associate in the Department of Electronic and Electrical Engineering, University of Strathclyde, Glasgow, U.K. He has published more than 20 technical papers in leading journals and conference proceedings. His research interests include photovoltaic generation systems, dc–dc/dc–ac converters, and electrical motor drives.

**Volker Pickert** (M'04) received the Dipl.-Ing. degree in electrical and electronic engineering from the Rheinisch-Westfaelische Technische Hochschule, Aachen, Germany, in 1994, and the Ph.D. degree from Newcastle University, Newcastle upon Tyne, U.K., in 1997.

From 1998 to 1999, he was an Application Engineer with Semikron International, Nuremberg, Germany, and from 1999 to 2003, he was a Group Leader at Volkswagen, Wolfsburg, Germany, and responsible for the development of electric drives for

electric vehicles. In 2003, he was appointed as a Senior Lecturer within the Power Electronics, Drives and Machines Research Group at Newcastle University and in 2011 he became a Professor of power electronics. He has published more than 80 papers in the area of power electronics. His current research includes power electronics for automotive applications, thermal management, fault-tolerant converters and advanced nonlinear control.

Dr. Pickert received the IMarEst Denny Medal for the Best Paper in the *Journal of Marine Engineering and Technology* in 2011. He was Chairman of the Biannual International IET Conference on Power Electronics, Machines and Drives in 2010. He is an Executive Steering Member of the IET PGCU network and a Member of the EPE.