# Decoupling of Fluctuating Power in Single-Phase Systems Through a Symmetrical Half-Bridge Circuit

Yi Tang, *Member, IEEE*, Frede Blaabjerg, *Fellow, IEEE*, Poh Chiang Loh, *Senior Member, IEEE*, Chi Jin, and Peng Wang, *Member, IEEE*

Abstract—Single-phase ac/dc or dc/ac systems are inherently subject to the harmonic disturbance that is caused by the wellknown double-line frequency ripple power. This issue can be eased through the installation of bulky electrolytic capacitors in the dc link. Unfortunately, such passive filtering approach may inevitably lead to low power density and limited system lifetime. An alternative approach is to use active power decoupling so that the ripple power can be diverted into other energy storage devices to gain an improved system performance. Nevertheless, all existing active methods have to introduce extra energy storage elements, either inductors or film capacitors in the system to store the ripple power, and this again leads to increased component costs. In view of this, this paper presents a symmetrical half-bridge circuit which utilizes the dc-link capacitors to absorb the ripple power, and the only additional components are a pair of switches and a small filtering inductor. A design example is presented and the proposed circuit concept is also verified with simulation and experimental results. It shows that at least ten times capacitance reduction can be achieved with the proposed active power decoupling method, and both the input current and output voltage of the converter can be well regulated even when very small dc-link capacitors are employed.

Index Terms—Active power decoupling, capacitance reduction, harmonic compensation, single-phase systems.

## I. INTRODUCTION

Normal Single Phase ac/dc or dc/ac power electronics systems have extremely wide applications in residential and industrial power supplies or conversion systems. Example applications are front-end power factor correction (PFC) converters in consumer power supplies [1]–[3], on-board chargers for plugin hybrid electric vehicles [4]–[6], and 5-kW (or less) grid-connected photovoltaic (PV) inverters for distributed power generation [7]–[9]. A well-known problem with such systems is that their ac-side instantaneous power contains a fluctuating component that changes at twice the fundamental frequency [10]. This fluctuating power is adverse to the system performance because

Manuscript received February 25, 2014; revised April 27, 2014; accepted May 22, 2014. Date of publication May 30, 2014; date of current version November 3, 2014. This work was supported by European Research Council (ERC) under the European Union's Seventh Framework Program (FP/2007-2013)/ERC Grant Agreement [321149-Harmony]. Recommended for publication by Associate Editor B. Lehman.

Y. Tang, F. Blaabjerg, and P. C. Loh are with the Department of Energy Technology, Aalborg University, Aalborg 9220, Denmark (e-mail: yta@et.aau.dk; fbl@et.aau.dk; pcl@et.aau.dk).

C. Jin and P. Wang are with the School of Electrical and Electronic Engineering, Nanyang Technological University, Singapore 639798 (e-mail: jinchi@ntu.edu.sg; epwang@ntu.edu.sg).

Color version of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TPEL.2014.2327134

it may potentially cause distorted input current of PFCs, overheating of batteries [11], and decreased maximum power point tracking (MPPT) efficiency of PV systems [12]. A very straightforward way to mitigate its negative impact is to use bulky electrolytic capacitors in the dc link so that they can act as buffers to the ac-side ripple power. However, those electrolytic capacitors are known to have high equivalent series resistance (ESR) and low ripple current capability, and their lifetime is also relatively short (several thousand hours) when stressed with the nominal voltage and the ripple current. Therefore, they may cause troubles in some applications where 20- or 25-year warranty period is required, e.g., LED drivers and solar inverters [12].

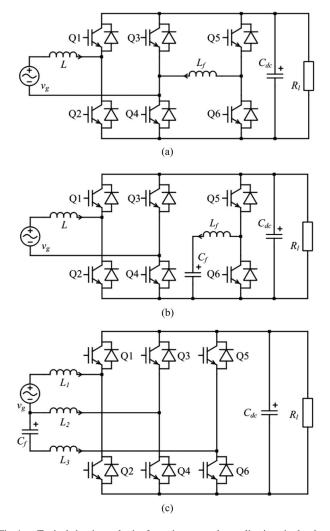

Recently, some active power decoupling methods have been proposed to cope with this problem, and the fundamental principle behind them is to introduce an extra active circuit in the system, so that the ripple power can be shifted away from the dc link and stored by other components with expanded lifetime, e.g., inductors and film capacitors, in a more efficient and effective way. Fig. 1(a) shows an active method which uses an inductor for ripple energy storage [13], and the inductor current is controlled to be sinusoidal which is accomplished through the proper modulation of the added third switching leg. A similar concept is presented in [14], where the lower switch of the third leg is replaced with a diode in order to save one active component, and in this case, the inductor current can be controlled as rectified sinusoidal in order to cancel those ac-side ripple power. Even though inductors are reliable and robust, they are generally of low power density and high power losses when used as energy storage elements for fundamental components, and therefore, the performance improvement could be very limited. In [12], the inductor is replaced by a film capacitor and the ripple power can then be compensated by controlling the voltage of the film capacitor to be rectified sinusoidal as shown in Fig. 1(b). However, such waveforms may contain high-order harmonics which will be difficult to track and control for a highly underdamped second-order system. Using exactly the same circuit configuration, Wang et al. [15] propose to inject a dc offset in the capacitor reference voltage so that the harmonic content may become small and it may facilitate the closed-loop controller design. Nevertheless, since the capacitor voltage does not go down to zero, it will not be fully discharged, which means that the film capacitor is not fully utilized. The similar compensation concept based on capacitive ripple power decoupling has also been discussed in [16]–[18]. A more recently proposed active power decoupling method is discussed in [19] and its circuit diagram is shown in Fig. 1(c). The introduced half-bridge, together with one leg of the full-bridge rectifier, essentially forms another

Fig. 1. Typical circuit topologies for active power decoupling in a single-phase system.

full-bridge circuit, and in this case, the voltage of the film capacitor can be controlled to be sinusoidal and it resolves all the difficulties mentioned previously. Even though being effective in ripple power compensation, this topology is not applicable in some circumstances, e.g., PFCs and unfolding bridge-based inverters, because the power flow is unidirectional. It may also become problematic in H5 inverters, where the full-bridge circuit will be intermittently isolated from the dc link in order to eliminate the leakage current [20]. In [21], a stacked switched capacitor concept is proposed as the energy buffer for singlephase systems. However, the circuit may involve a large number of capacitors and switches if high energy buffering ratio is pursued. It also requires a precharge circuit to distribute the initial voltages for individual capacitors, which may further complicate its circuit implementation. Moreover, this circuit theoretically cannot achieve perfect active power decoupling and small voltage fluctuation may always exist in the dc link.

Instead of using paralleled circuit configurations discussed previously, Wang *et al.* [22] propose a series compensation approach where a controlled voltage source is inserted in be-

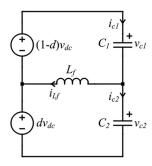

Fig. 2. Proposed symmetrical half-bridge circuit for single-phase active power decoupling.

tween the dc-link capacitor and the load and through this way, low-voltage semiconductors can be used to construct the active power decoupling circuit and to gain an improved system performance. However, the circuit is complicated with four MOSFETs and associated gate drivers, and the dc-link capacitance cannot be too small because it may potentially overmodulate the frontend ac/dc rectifier. Even though the dc-link capacitance can be reduced regardless of the configurations of compensation circuits, a common problem for the existing active power decoupling methods is that, the system ripple power has to be absorbed by additional energy storage elements, either inductors or film capacitors, and this implies that the capacitance reduction is not optimized [23].

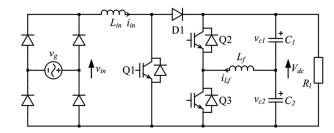

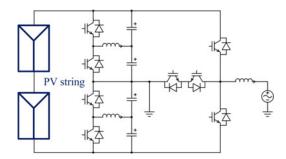

In order to achieve a simple and compact design, and also to break the limitation imposed by the front-end topology in [19], this paper proposes a new topology to realize active power decoupling, and its circuit diagram is shown in Fig. 2. As can be seen, two identical film capacitors are employed and connected in series in the dc link, whose midpoint is then connected to another phase leg through a small filtering inductor. In this way, the dc-link capacitors may not only provide a high-voltage dc bus to support ac/dc or dc/ac conversion, but can also absorb the system ripple power. The added symmetrical half-bridge circuit is also easy to control, because the voltages of the two film capacitors will both be sinusoidal. Moreover, the capacitors can be alternatively discharged to zero in case that high ripple power compensation is required, and the power decoupling can be accomplished without using additional energy storage inductors or capacitors. The power flow involved in this circuit and the relevant controller design are detailed in this paper. Both simulation and experimental results are presented to prove the effectiveness of this concept.

# II. CIRCUIT ANALYSIS AND OPERATING PRINCIPLES

The proposed symmetrical half-bridge circuit is shown in Fig. 2, which is applied to a single-phase PFC converter as an example here. It should be noted that and also as mentioned previously, the proposed active power decoupling method will not be constrained by its front-end topologies, and it can be basically used in any single-phase ac/dc or dc/ac systems, as long as there is a high-voltage dc bus available. In this case, two identical film capacitors, having  $C_1 = C_2 = C_f$ , are connected in series to build up the dc-link voltage  $V_{\rm dc}$ , and  $v_{c1}(t)$  and  $v_{c2}(t)$  are used to denote the voltages of the upper and lower capacitors,

respectively. In order to provide the double-line frequency ripple power, their voltages are then controlled to be sinusoidal with an offset value that equals to half the dc-link voltage  $V_{\rm dc}/2$ , and they can be written as

$$\begin{cases} v_{c1}(t) = \frac{V_{dc}}{2} + V_c \sin(\omega t + \theta) \\ v_{c2}(t) = \frac{V_{dc}}{2} - V_c \sin(\omega t + \theta) \end{cases}$$

(1)

where  $\theta$  is the phase angle between the capacitor voltage  $v_{c1}(t)$  and the input voltage  $v_{\rm in}(t)$ , and  $\omega$  is the fundamental angular frequency.  $V_c$  is the amplitude of the film capacitor voltage having  $V_c \leq V_{\rm dc}/2$ . The capacitor current  $i_{c1}(t)$  and  $i_{c2}(t)$  can then be easily derived as

$$\begin{cases} i_{c1}(t) = I_c \cos(\omega t + \theta) = \omega C_f V_c \cos(\omega t + \theta) \\ i_{c2}(t) = -I_c \cos(\omega t + \theta) = -\omega C_f V_c \cos(\omega t + \theta) \end{cases}$$

(2)

where  $I_c$  is the amplitude of the filtered capacitor current. The instantaneous power  $p_c(t)$  provided by these two capacitors will be

$$p_{c}(t) = v_{c1}(t)i_{c1}(t) + v_{c2}(t)i_{c2}(t)$$

$$= 2V_{c}\sin(\omega t + \theta)\omega C_{f}V_{c}\cos(\omega t + \theta)$$

$$= \omega C_{f}V_{c}^{2}\sin(2\omega t + 2\theta).$$

(3)

In order to achieve accurate power compensation, the instantaneous power  $p_{Lf}(t)$  of the filter inductor  $L_f$  must also be taken into consideration

$$i_{Lf}(t) = i_{c1}(t) - i_{c2}(t)$$

=  $2I_c \cos(\omega t + \theta) = 2\omega C_f V_c \cos(\omega t + \theta)$  (4)

$$p_{Lf}(t) = L_f \frac{di_{Lf}(t)}{dt} i_{Lf}(t)$$

$$= -\omega L_f (2\omega C_f V_c)^2 \sin(\omega t + \theta) \cos(\omega t + \theta)$$

$$= -2\omega L_f (\omega C_f V_c)^2 \sin(2\omega t + 2\theta). \tag{5}$$

Therefore, the total instantaneous power  $p_{hb}(t)$  provided by the symmetrical half-bridge circuit will be

$$p_{hb}(t) = p_c(t) + p_{Lf}(t)$$

=  $[\omega C_f V_c^2 - 2\omega L_f (\omega C_f V_c)^2] \sin(2\omega t + 2\theta)$ . (6)

Equation (6) shows that the filter inductor may reduce the compensation capacity of this circuit and its value should be minimized in the design.

The instantaneous power to the PFC stage  $p_{pfc}(t)$  can be found in a similar manner by defining the input voltage  $v_{\rm in}(t)$  and current  $i_{\rm in}(t)$  to be

$$v_{\rm in}(t) = V_{\rm in} |\sin(\omega t)| \text{ and } i_{\rm in}(t) = I_{\rm in} |\sin(\omega t)|$$

$$p_{\rm PFC}(t) = p_{\rm in}(t) + p_{\rm Lin}(t)$$

$$= v_{\rm in}(t) i_{\rm in}(t) + L_{\rm in} \frac{di_{\rm in}(t)}{dt} i_{\rm in}(t)$$

$$= \frac{V_{\rm in} I_{\rm in}}{2} - \frac{V_{\rm in} I_{\rm in}}{2} \cos(2\omega t) + \frac{\omega L_{\rm in} I_{\rm in}^{2}}{2} \sin(2\omega t)$$

(8)

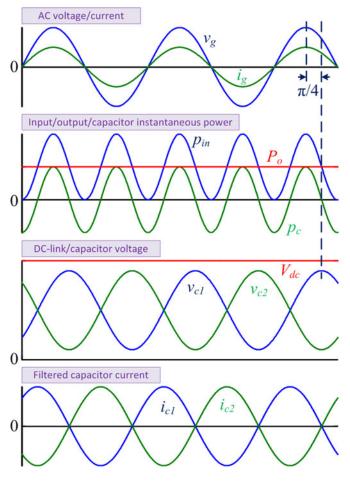

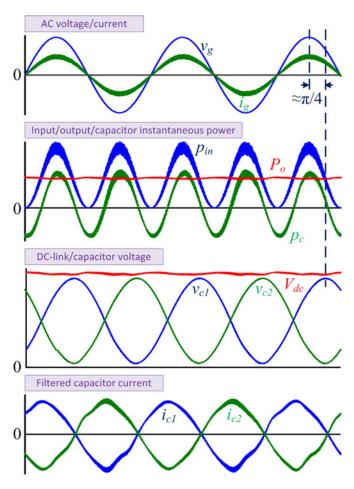

Fig. 3. Idealized operating waveforms for the proposed active power decoupling circuit.

where  $\sin(\omega t) \neq 0$ . By equating the time-varying terms of (8) to (6), it is possible to derive that

$$\theta = \frac{1}{2}\arctan(-\frac{V_{\rm in}I_{\rm in}}{\omega L_{\rm in}I_{\rm in}^2}) = \frac{1}{2}\arctan(-\frac{V_{\rm in}}{\omega L_{\rm in}I_{\rm in}}) \quad (9)$$

$$V_{c} = \sqrt{\frac{\sqrt{\left(\frac{V_{\rm in}I_{\rm in}}{2}\right)^{2} + \left(\frac{\omega L_{\rm in}I_{\rm in}^{2}}{2}\right)^{2}}}{\omega C_{f} - 2\omega L_{f}(\omega C_{f})^{2}}}.$$

(10)

In this case, the voltage references of  $C_1$  and  $C_2$  can be determined by (9) and (10), and through closed-loop control, the system ripple power can be almost cancelled by these two dc-link capacitors and the dc-link voltage will be fairly constant. It should be noted that in practical implementation, there may exist some errors due to parameter tolerance of the components and limited compensation gain, and a closed-loop modification of the voltage references may be required to fine tune the ripple power compensation as discussed in [19].

The idealized operating waveforms of the proposed converter are presented in Fig. 3, where the filter inductance, switching loss, and conduction loss in the circuit are all neglected. It is clear that the two dc-link capacitors can provide the fluctuating power that can be used to cancel those propagated from the ac

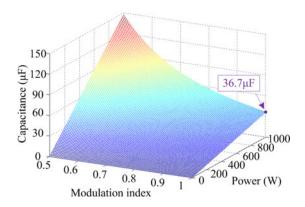

Fig. 4. Required dc-link capacitance as a function of the power rating and the modulation index.

grid side, and the voltage of the upper capacitor has  $\pi/4$  phase shift with the grid voltage.

In order to examine the capacitance reduction achieved by the proposed active power decoupling method, the ripple power across the inductors  $L_{\rm in}$  and  $L_f$  are neglected because they are comparatively much smaller than those capacitive ones. Then, the symmetrical half-bridge circuit can provide the maximum ripple power when  $V_c = V_{\rm dc}/2$  and according to (10)

$$\omega C_f V_c^2 = \frac{V_{\rm in} I_{\rm in}}{2}$$

and  $\frac{\omega C_f V_{\rm dc}^2}{4} = P_{\rm in}$  (11)

$$C_{\rm eq} = \frac{C_f}{2} = \frac{2P_{\rm in}}{\omega V_{\rm dc}^2} \tag{12}$$

where  $P_{\rm in}$  is the amplitude of the input ripple power and  $C_{\rm eq}$  is the equivalent dc-link capacitance. For a typical 60-Hz power system with a dc-link voltage of 380 V, the required capacitance is only 36.7  $\mu$ F/kW according to (12).

In contrast, if there is no active power decoupling and it is desired that the dc-link voltage ripple should be less than 1% of the nominal voltage, the dc-link capacitance would be [15]

$$0.01V_{\rm dc} = \frac{P_{\rm in}}{2\omega C_{\rm dc}V_{\rm dc}}$$

and  $C_{\rm dc} = \frac{50P_{\rm in}}{\omega V_{\rm dc}^2}$ . (13)

Equation (13) clearly shows that the dc-link capacitance can theoretically be reduced by 25 times as compared to that of a conventional passive approach. However, in practice, the improvement may not be so significant because the capacitor voltage  $V_c$  is normally controlled to be slightly less than  $V_{\rm dc}/2$  in order to prevent overmodulation of the symmetrical half-bridge. Fig. 4 shows the dc-link capacitance requirement with respect to the power rating of the converter and the modulation index of the symmetrical half-bridge circuit. The modulation index is normalized to unity when  $V_c = V_{\rm dc}/2$ .

In certain applications, e.g., PFC converters for computer power supplies, there is another requirement for the output capacitors, which is to maintain the output voltage for a short period even if its ac-side input voltage is lost. The required capacitance can then be calculated as

$$C_{\rm dc} \ge \frac{2 \cdot P_{\rm out} \cdot t_{\rm holdup}}{V_{\rm dc}^2 - V_{\rm dc\_min}^2} \tag{14}$$

Fig. 5. Averaged equivalent circuit of the proposed symmetrical half-bridge.

where the common specification for this holdup time  $t_{\rm holdup}$  is 20 ms. If the minimum dc-link voltage  $v_{\rm dc\_min}$  is defined to be 250 V and the power losses of the PFC converter are neglected, the required capacitance is found to be 488.4  $\mu$ F/kW, which is sufficient to provide ripple power compensation even only 0.5 modulation index is applied to the converter according to Fig. 4.

## III. SYSTEM MODELING AND THE CONTROLLER DESIGN

The modeling and controller design of the PFC converter has been extensively discussed in the literature and therefore will not be addressed in this paper. For the introduced symmetrical half-bridge, it simply has two switching states and its corresponding time-averaged model can be derived by averaging the state equations over a switching cycle. The resultant equivalent circuit model is shown in Fig. 5 and based on this model, it is easy to derive the following differential equations:

$$\begin{cases}

L_f \frac{di_{L_f}(t)}{dt} = -v_{c1}(t) + [1 - d(t)] \cdot v_{dc}(t) \\

C_f \frac{dv_{c1}(t)}{dt} = i_{c1}(t)

\end{cases}$$

(15.a)

$$\begin{cases}

L_f \frac{di_{Lf}(t)}{dt} = v_{c2}(t) - d(t) \cdot v_{dc}(t) \\

C_f \frac{dv_{c2}(t)}{dt} = i_{c2}(t)

\end{cases}$$

(15.b)

where d(t) is the duty cycle applied to the upper switch Q2 shown in Fig. 2. Ideally, the compensation network can cancel the acside ripple power and the dynamics of the dc-link voltage and its ripple component can be neglected. In this case, by substituting (2) and (4) into (15.b)

$$\begin{cases}

L_f \frac{di_{L_f}(t)}{dt} = v_{c2}(t) - d(t) \cdot V_{dc} \\

C_f \frac{dv_{c2}(t)}{dt} = -\frac{i_{L_f}(t)}{2}.

\end{cases}$$

(16)

Taking the Laplace transform of (16) and also considering the damping effect of a practical circuit, the control-to-capacitor voltage transfer function  $G_{hb}$  can finally be derived as

$$G_{hb} = \frac{v_{c2}(s)}{d(s)} = \frac{V_{dc}}{2L_f C_f s^2 + K_d C_f s + 1}$$

and  $\omega_{res} = \frac{1}{\sqrt{2L_f C_f}}$  (17)

where  $K_d$  is a parameter that represents the damping effect provided by the ESR of passive components and  $\omega_{res}$  is the LC

TABLE I

CIRCUIT PARAMETERS USED IN ANALYSIS, SIMULATION, AND EXPERIMENT

| Description         | Symbol       | Value        |

|---------------------|--------------|--------------|

| Nominal power       | $P_n$        | 1 kW         |

| Switching frequency | $f_{sw}$     | 19.2 kHz     |

| Line frequency      | $f_n$        | 60 Hz        |

| Grid voltage        | $V_q$        | 156 V        |

| Dc-link voltage     | $V_{ m dc}$  | 380 V        |

| Dc-link capacitor   | $C_1/C_2$    | $90 \mu F$   |

| Boost inductor      | $L_{\rm in}$ | 2 mH         |

| Filter inductor     | $L_f$        | 2 mH         |

| Nominal load        | $\vec{R_l}$  | $150 \Omega$ |

resonant frequency. The ESRs of the capacitors are ignored here because they are of film type and have extremely low value.

It should be noted that in practice, there always exists some control errors and component tolerance, and therefore, the dclink voltage ripple may not be zero and introduce the common mode current in the two decoupling capacitors. In this case,  $i_{c1}(t) = -i_{c2}(t) = i_{Lf}(t)/2$  is no longer valid and in order to get rid of the disturbance from the dc link, the measured capacitor voltage  $v_{c2}(t)$  should be preprocessed before being sent into the voltage controller as follows:

$$v_c(t) = \frac{v_{c2}(t) - v_{c1}(t)}{2} = \frac{2v_{c2}(t) - v_{dc}(t)}{2}.$$

(18)

The above equation in effect indicates that the control variable should be changed to  $v_{c2}(t) - v_{c1}(t)$  rather than  $v_{c2}(t)$ . Combining (15) and (18)

$$\begin{cases}

2L_f \frac{di_{Lf}(t)}{dt} = v_{c2}(t) - v_{c1}(t) + [1 - 2d(t)] \cdot v_{dc}(t) \\

= 2v_c(t) + [1 - 2d(t)] \cdot v_{dc}(t) \\

C_f \frac{d[v_{c2}(t) - v_{c1}(t)]}{dt} = 2C_f \frac{dv_c(t)}{dt} \\

= i_{c2}(t) - i_{c1}(t) = -i_{Lf}(t).

\end{cases}$$

(19)

By introducing perturbation in the state variables

$$\begin{cases}

L_f \frac{d[I_{L_f} + \hat{i}_{L_f}(t)]}{dt} = [V_c + \hat{v}_c(t)] + \left[\frac{1}{2} - D - \hat{d}(t)\right] \\

\cdot [V_{dc} + \hat{v}_{dc}(t)] \\

C_f \frac{d[V_c + \hat{v}_c(t)]}{dt} = -\frac{I_{L_f} + \hat{i}_{L_f}(t)}{2}.

\end{cases}$$

(20)

By equating ac and dc quantities and then proceed only with ac equations (neglect second-order ac quantities)

$$\begin{cases}

L_f \frac{d\hat{i}_{Lf}(t)}{dt} = \hat{v}_c(t) - \hat{d}(t) \cdot V_{dc} + (\frac{1}{2} - D) \cdot \hat{v}_{dc}(t) \\

C_f \frac{d\hat{v}_c(t)}{dt} = -\frac{\hat{i}_{Lf}(t)}{2}.

\end{cases}$$

(21)

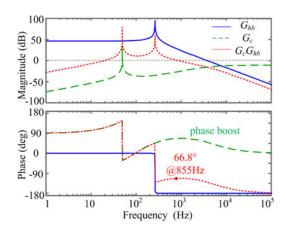

When operated around the quiescent point, the effect of the ripple voltage can be neglected because  $\frac{1}{2}-D$  is comparatively much smaller than  $V_{\rm dc}$ . In this case, the disturbance from the dc link can be eliminated and (21) is simplified to be the same as (16), and therefore, the plant transfer function shown in (17) still holds true. Using the parameters listed in Table I, the openloop gain of this system is plotted as the solid line in Fig. 6, where it is clear that its phase response is nearly  $-180^{\circ}$  after the LC resonant frequency. This paper proposes a modified type III

Fig. 6. Bode diagrams of the plant model, controller, and system open-loop

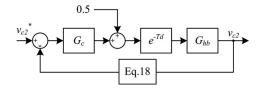

Fig. 7. Control block diagram for the proposed active power decoupling circuit.

compensator to stabilize this system and it is embedded with a resonant controller [24], which ensures zero steady-state tracking error of the voltage control loop, and its transfer function can be written as

$$G_c = K_p \frac{\left(\frac{s}{\omega_{z1}} + 1\right) \left(\frac{s}{\omega_{z2}} + 1\right)}{\left(\frac{s}{\omega_{z}} + 1\right)} \frac{s}{s^2 + \omega^2}$$

(22)

where  $\omega_{z1}$  and  $\omega_{z2}$  are the two zeroes to provide phase boost capability and should be placed around the LC resonance frequency.  $\omega_p$  is the pole to attenuate the system high-order harmonics and is normally chosen to be less than half of the system switching frequency.  $K_p$  is the proportional gain that adjusts the system crossover frequency. Since the ESR of film capacitors is very low, there is no need to add another pole to cancel the ESR zero of capacitors, which in this case is well above the system control frequency. The Bode diagram of the designed controller is then plotted as the dashed line in Fig. 6 and it shows that this controller can provide maximum phase boost of 67.3° at 1040 Hz, and it also has high gain at fundamental frequency to force the voltage tracking error to be zero. The resulting system open-loop gain is plotted as the dotted line in Fig. 6 and it shows that 66.8° phase margin is achieved at 855 Hz, which is sufficient even considering the system delays that are caused by digital computation and pulse-width modulation. In addition to this closed-loop control, a feed-forward path is also implemented which adds a constant 0.5 into the final duty cycle, and in this way, the capacitor voltages will contain  $V_{\rm dc}/2$  offset. The control block diagram is shown in Fig. 7 and it is applied to control the voltage of the lower capacitor in the dc link, and

Fig. 8. Simulation results showing the key operating waveforms of the proposed active power decoupling circuit.

the voltage of the upper capacitor will be naturally determined because the total dc bus voltage is already regulated by the PFC controller, which is usually a very slow control loop.

## IV. SIMULATION AND EXPERIMENTAL RESULTS

#### A. Simulation Results

Simulation was done in MATLAB/Simulink environment and the key circuit parameters are summarized in Table I.

Fig. 8 shows the steady-state simulation results which are comparable to those presented in Fig. 3. Thanks to the smooth dc-link voltage, the input line current can be well regulated by the PFC controller, and it is sinusoidal and in phase with the grid voltage. The two film capacitors can provide the required double-line frequency harmonic power, and the resultant output power can be almost constant. The dc-link voltage has very slight voltage variation, which is around 10 V, and this is caused by the inaccurate calculation of the voltage reference and the errors in the closed-loop control. As mentioned in [19], some closed-loop modifications can be applied to fine tune the voltage reference and to achieve more precise power decoupling. However, this may further complicate the control system, and thus not implemented here. The voltage of the upper capacitor

TABLE II

KEY COMPONENTS USED FOR THE EXPERIMENTAL PROTOTYPE

| Component              | Description                                 |  |  |

|------------------------|---------------------------------------------|--|--|

| Diode rectifier bridge | GBPC2506, 25 A/600 V, MULTICOMP             |  |  |

| Q1Q3/D1                | IKW30N60T, 30 A/600 V, INFINEON             |  |  |

| $L_{in}/L_f$           | 200 turns, 2 × AWG#16, Core DT400-40, DMEGC |  |  |

| $C_1/C_2$              | MKP1847630354Y5, 30 $\mu$ F/350 V, VISHAY   |  |  |

| $C_{dc}$               | EETED2W471LJ, 470 $\mu$ F/450 V, PANASONIC  |  |  |

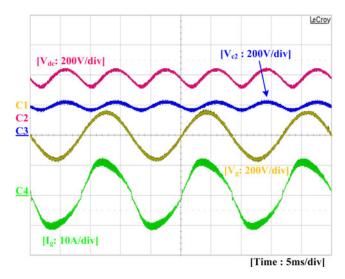

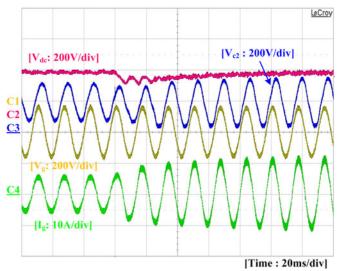

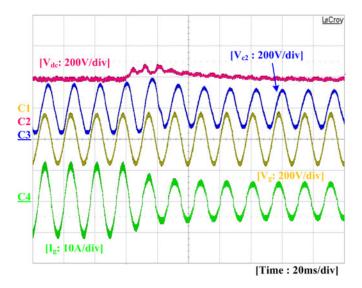

Fig. 9. Steady-state experimental waveforms without ripple power compensation. From top to bottom, dc-link voltage, lower capacitor voltage, grid voltage, and grid current.

is noted to have approximately  $\pi/4$  phase shift with the grid voltage, which matches well with the theoretical analysis.

## B. Experimental Results

A 1-kW prototype was built in the laboratory and the circuit parameters are basically the same as those used in simulation. Two 90- $\mu$ F film capacitors, each of them consisting of three 30- $\mu$ F film capacitors in parallel, are connected in series in the dc link and the equivalent dc-link capacitance is only 45  $\mu$ F, which is much smaller than that of a conventional PFC converter. The key active and passive components used for the tested prototype are summarized in Table II.

Fig. 9 shows the steady-state experimental results when the closed-loop controller is disabled and there is no active power decoupling in the circuit. It is obvious that the dc-link contains high ripple voltage because of the very low capacitance, and this ripple voltage in turn affects the regulation of the input current. Even though a second-order notch filter is implemented in the PFC voltage control loop, it is still not enough to attenuate the voltage harmonic disturbance and it fails to provide a clean reference for the inner current control loop. The grid current is therefore seriously distorted by the third-order harmonic with amplitude of 0.92A. The total harmonic distortion (THD) of grid current, calculated up to 100th harmonics, is found to be 9.1%,

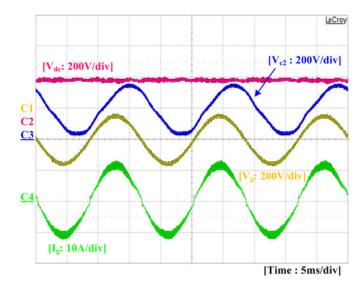

Fig. 10. Steady-state experimental waveforms with ripple power compensation. From top to bottom, dc-link voltage, lower capacitor voltage, grid voltage, and grid current.

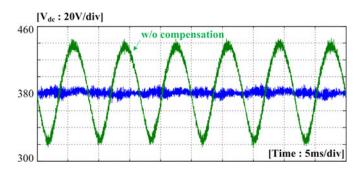

Fig. 11. Zoom-in view of the dc-link voltage under two tests.

and this value may not be able to comply with the standards, like the IEEE 519–1992 harmonic limits.

Fig. 10 shows the steady-state experimental results when the proposed decoupling method is enabled and it is clear that the dc-link voltage ripple can be dramatically reduced. As a consequence, the grid current is also greatly improved and the third-harmonic current is reduced to 0.15A only. In this case, the THD of the grid current is improved to 3.8%. Also as anticipated, the capacitor voltage is sinusoidal with  $V_{\rm dc}/2$  offset, and there is approximately one-eighth cycle phase difference with the grid voltage, which is in good agreement with the theoretical analysis and simulation results presented previously.

Fig. 11 shows the zoom-in view of the dc-link voltage under these two tests. Without compensation, the peak-to-peak dc-link voltage can be up to 120 V, which corresponds to 31.6% of the nominal dc bus voltage, while this ripple voltage can be suppressed to around 10 V, less than 3% of the nominal value if the proposed compensation is implemented.

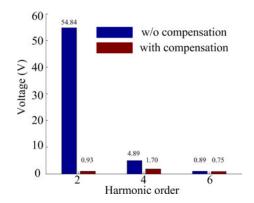

Fig. 12 shows the spectrum of the dc-link voltage and it is clear that there is a dramatic reduction of the second-harmonic voltage after activation of the harmonic compensation. The fourth-and sixth-harmonic voltages are also slightly reduced due to the

Fig. 12. Spectral analysis of the dc-link voltage under two tests.

Fig. 13. Dynamic experimental waveforms showing 50% to 100% step-up load change. From top to bottom, dc-link voltage, lower capacitor voltage, grid voltage, and grid current.

improved grid current. The smooth dc-link voltage indicates that ten times capacitance reduction in single-phase systems is successfully achieved with the proposed active power decoupling circuit.

The prototype was also tested with dynamic loads and the corresponding load step-up and step-down experimental results are presented in Figs. 13 and 14, respectively. As shown, the dc-link voltage dip/swell during load transients can be kept within  $\pm 100$  V. This is acceptable considering the very low equivalent dc-link capacitance used in the circuit. The dc-link voltage can converge to its nominal value within five line cycles and there is no obvious distortion occurred in the grid current and the power factor is clearly always unity regardless of the load disturbances. This again confirms the effectiveness of the proposed circuit and control algorithm.

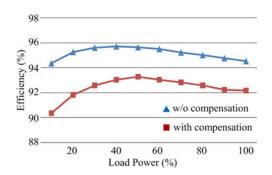

# C. Comparative Study

The proposed single-phase converter is also compared with a conventional boost PFC converter whose dc-link voltage is

Fig. 14. Dynamic experimental waveforms showing 100% to 50% step-down load change. From top to bottom, dc-link voltage, lower capacitor voltage, grid voltage, and grid current.

Fig. 15. Efficiency curve of the proposed single-phase converter compared with that of a conventional boost PFC.

maintained by electrolytic capacitors. In order to obtain a similar level of voltage ripple, the required dc-link capacitance, according to (13) will be 920  $\mu\mathrm{F}$ , which is more than 20 times of the proposed system. In experiment, two 470- $\mu\mathrm{F}/450\text{-V}$  electrolytic capacitors are used in parallel in the dc link. However, the measured dc-link capacitance is only 840  $\mu\mathrm{F}$  because of the tolerance of the capacitors.

The efficiency curves of the two systems are plotted in Fig. 15 and it shows that the proposed system may have 2.3% efficiency drop at full-load operation. This is because the third switching leg may introduce additional switching and conduction losses into the system. It is also clear that the efficiency drop may become more severe at light load as the modulation index of the symmetrical half-bridge is very small during such operating conditions. Efficiency drop is the main drawback of the proposed system and a possible solution could be to use advanced widebandgap power semiconductors with low on-state resistance and low switching losses.

In addition to the system overall efficiency, the power loss inside capacitors is particularly of interest because it may greatly influence the lifetime of the capacitors. The dc-link capacitors used in the proposed circuit are Vishay MKP1847 series and such film capacitors normally have a dissipation factor (DF) or also called the loss angle of 2e - 4 when the frequency is below 100 Hz. Then, its ESR at 60 Hz can be calculated as

$$ESR_{Cf} = \frac{DF}{\omega_n C_f} = \frac{2e - 4}{120\pi \cdot (90e - 6)} \approx 5.9 \text{ m}\Omega.$$

(23)

The total power losses of  $C_1$  and  $C_2$  under full-load operation will be

$$P_{Cf} = 2 \cdot (\omega_n C_f V_{C\_rms})^2 \cdot \text{ESR}_{Cf}$$

=  $2 \cdot [120\pi \cdot (90e - 6) \cdot 121]^2 \cdot (5.9e - 3) \approx 0.20 \,\text{W}.$  (24)

In comparison, the power loss of the electrolytic capacitors in a conventional PFC is also analyzed. The electrolytic capacitors are Panasonic ED series and their DF at 120 Hz (provided in the datasheet) is 0.15. Similarly

$$ESR_{Cdc} = \frac{DF}{2\omega_n C_{dc}} = \frac{0.15}{2 \cdot 120\pi \cdot (840e - 6)} \approx 0.237 \Omega$$

(25)

$$P_{Cdc} = I_{ripple}^2 \cdot ESR_{Cdc}$$

=  $(1000/380/\sqrt{2})^2 \cdot 0.237 \approx 0.82 \text{ W}.$  (26)

It is clear that the capacitors in the proposed system would generate much lower power losses as compared to the conventional case and therefore, the heating effect can be basically neglected.

Table III compares the capacitive energy storage requirement for some common active power decoupling circuits. It should be noted that the  $\omega_n CV_{\mathrm{dc}}^2$  term makes no physical meaning and  $\omega_n$ used here is just a scaling factor for assessing the capacitance requirement, because it is quite intuitive that the higher the fundamental frequency, the lower the capacitance can be used in the dc link to obtain the same level of voltage ripple. The circuit in [19] and the proposed circuit actually exhibit the same capacitive energy storage requirement because for both of them, the ripple power is stored in the decoupling capacitors as pure ac form (the dc offset voltage in the proposed circuit is not for power decoupling purpose). The former one has slightly higher requirement because it is installed with more capacitance in the dc link and therefore, it has relatively longer holdup time in case of ac input lost. The proposed circuit may clearly stand out from the existing active power decoupling methods because the film capacitors used in the system are not only for power decoupling, but also for holding up the dc bus voltage, and therefore, the system will be more cost-effective.

#### V. DISCUSSION

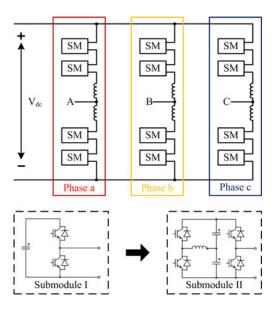

In fact, the proposed symmetrical half-bridge circuit can be regarded as a generic converter cell and it can be used to replace the dc-link capacitors in other advanced converter topologies, e.g., neutral point-clamped (NPC) converters and modular multilevel converters (MMCs), to cope with the system fluctuating power problem.

| Description                                                    | [15]                                                              | [22]                                                                  | [19]                                       | Proposed circuit                            |

|----------------------------------------------------------------|-------------------------------------------------------------------|-----------------------------------------------------------------------|--------------------------------------------|---------------------------------------------|

| Fundamental angular frequency $\omega_n$                       | $2\pi \times 233 \text{ rad/s}$                                   | $2\pi \times 50 \text{ rad/s}$                                        | $2\pi \times 50 \text{ rad/s}$             | $2\pi \times 60 \text{ rad/s}$              |

| Nominal output power $P_n$                                     | 15 kW                                                             | 600 W                                                                 | 4 kW                                       | 1 kW                                        |

| DC-link capacitor<br>Capacitance C/Operating<br>voltage V      | $200~\mu\text{F/}540~\text{V}_{\text{dc}}$                        | 220 $\mu\text{F}/\text{450}V_{\mathrm{dc}}$ (with small ac component) | $120~\mu\text{F}/400~\text{V}_{\text{dc}}$ | 45 $\mu F/380~V_{\rm dc}$                   |

| Decoupling capacitor<br>Capacitance C/<br>Operating voltage V/ | $200~\mu\text{F/}350~\text{V}_{\rm dc}$ (with small ac component) | 1000 $\mu$ F/50 $V_{\rm dc}$                                          | 220 $\mu F/240~V_{\rm rms}$                | $180\mu\text{F}/121~\text{V}_{\text{rm s}}$ |

| $\frac{\sum_{\omega_n CV^2} V^2}{P_n}$                         | 8.08                                                              | 11.36                                                                 | 4.49                                       | 3.45                                        |

TABLE III

CAPACITIVE ENERGY STORAGE REQUIREMENT FOR SOME COMMON ACTIVE POWER DECOUPLING CIRCUITS

Fig. 16. NPC inverter with the proposed symmetrical half-bridge converter cell for the single-phase PV application.

The NPC topology can be found in Conergy IPG S series single-phase PV inverters where a T-type phase leg is used to provide the three-level output voltage. With this configuration, the inverters may have fixed PV terminal-to-ground potentials and feature reduced switching harmonic contents in the output voltage. However, the PV panel voltage can be varying due to the ripple power from the ac side, and this may lead to decreased MPPT efficiency [25]. In order to solve this issue, the proposed converter cell can be embedded into a single-phase T-type NPC inverter as configured in Fig. 16. Through proper control, the film capacitors in the dc link can absorb those ac-side harmonics and give rise to smoother PV voltage, and thus higher solar energy yields.

This concept is equally applicable to the MMC topology shown in Fig. 17. The MMC converter is now one of the most common types of voltage source converters used in high-voltage direct current (HVDC) applications, because it has advantages like modularity, multilevel waveforms, high availability, as well as failure management [26]. However, a known problem of the MMC is that each submodule (SM) converter may need a large and bulky capacitor to hold the dc voltage. As the number of SM increases, the whole system may become very huge in size. The proposed converter cell could be a potential candidate to solve this issue and the voltage of each SM can be kept nearly constant with much reduced capacitance. Nevertheless, the capacitance reduction can only be achieved at the expense of increased number of active components and power losses, and minimum dc-link capacitance is still required in order to safely ride

Fig. 17. MMC with the proposed symmetrical half-bridge converter cell for the HVDC application.

through those steep load changes that occurred in the system. Another design challenge is that, for both NPC and MMC applications, the dc-link voltage may not only contain double-line frequency ripple power but also the fundamental fluctuating power. In this case, the reference voltages of decoupling capacitors may no longer be sinusoidal and instead, they are distorted waveforms and can only be obtained through a closed-loop controller, e.g., another voltage control loop that can regulate the dc-link ripple voltage to be zero. The feasibility of this method will be studied in future research work.

### VI. CONCLUSION

This paper has presented a symmetrical half-bridge circuit to decouple the fluctuating power in single-phase ac/dc and dc/ac systems. The dc-link capacitors in the proposed system may not only provide a high-voltage dc bus to support power conversion, but also absorb the system ripple power originated from the ac side. The resulting system is more cost-effective as compared to other existing active power decoupling methods because it

does not need additional passive components to store the system ripple energy. Experimental results under both steady-state and dynamic operations were obtained from a 1-kW PFC prototype and it shows that at least ten times capacitance reduction can be achieved by the proposed active power decoupling circuit. The ripple voltage in the dc link as well as the THD of the gird current can be significantly reduced, which proves the effectiveness of the proposed solution. The proposed symmetrical half-bridge can also be regarded as a generic converter cell and might be a promising solution for elimination of the fluctuating power and the reduction of dc-link capacitance in other advanced topologies, e.g., NPCs and MMCs.

#### REFERENCES

- O. Garcia, J. A. Cobos, R. Prieto, P. Alou, and J. Uceda, "Single phase power factor correction: A survey," *IEEE Trans. Power Electron.*, vol. 18, no. 3, pp. 749–755, May 2003.

- [2] B. Singh, B. N. Singh, A. Chandra, K. Al-Haddad, A. Pandey, and D. P. Kothari, "A review of single-phase improved power quality AC-DC converters," *IEEE Trans. Ind. Electron.*, vol. 50, no. 5, pp. 962–981, Oct. 2002

- [3] L. Huber, Y. Jang, and M. M. Jovanovic, "Performance evaluation of bridgeless PFC boost rectifiers," *IEEE Trans. Power Electron.*, vol. 23, no. 3, pp. 1381–1390, May 2008.

- [4] F. Musavi, W. Eberle, and W. G. Dunford, "A high-performance single-phase bridgeless interleaved PFC converter for plug-in hybrid electric vehicle battery chargers," *IEEE Trans. Ind. Appl.*, vol. 47, no. 4, pp. 1833–1843, Jul./Aug. 2011.

- [5] F. Musavi, M. Edington, W. Eberle, and W. G. Dunford, "Evaluation and efficiency comparison of front end AC–DC plug-in hybrid charger topologies," *IEEE Trans. Smart Grid*, vol. 3, no. 1, pp. 413–421, Mar. 2012.

- [6] M. Yilmaz and P. T. Krein, "Review of battery charger topologies, charging power levels, and infrastructure for plug-in electric and hybrid vehicles," *IEEE Trans. Power. Electron.*, vol. 28, no. 5, pp. 2151–2169, May 2013.

- [7] Y. Xue, L. Chang, S. B. Kjær, J. Bordonau, and T. Shimizu, "Topologies of single-phase inverters for small distributed power generators: An overview," *IEEE Trans. Power Electron.*, vol. 19, no. 5, pp. 1305–1314, Sep. 2004.

- [8] Q. Li and P.Wolfs, "A review of the single phase photovoltaic module integrated converter topologies with three different DC link configurations," IEEE Trans. Power Electron., vol. 23, no. 3, pp. 1320–1333, May 2008.

- [9] S. B. Kjaer, J. K. Pederson, and F. Blaabjerg, "A review of single-phase grid-connected inverters for photovoltaic modules," *IEEE Trans. Ind. Appl.*, vol. 41, no. 5, pp. 1292–1306, Oct. 2005.

- [10] J. Kolar, U. Drofenik, J. Biela, M. Heldwein, H. Ertl, T. Friedli, and S. Round, "PWM converter power density barriers," *IEEJ Trans. Ind. Appl.*, vol. 128, no. 4, pp. 1–14, 2008.

- [11] T. Shimizu, T. Fujita, G. Kimura, and J. Hirose, "A unity power factor PWM rectifier with DC ripple compensation," *IEEE Trans. Ind. Electron.*, vol. 44, no. 4, pp. 447–455, Aug. 1997.

- [12] P. T. Krein, R. S. Balog, and M. Mirjafari, "Minimum energy and capacitance requirements for single-phase inverters and rectifiers using a ripple port," *IEEE Trans. Power Electron.*, vol. 27, no. 11, pp. 4690– 4698, Nov. 2012.

- [13] T. Shimizu, Y. Jin, and G. Kimura, "DC ripple current reduction on a single-phase PWM voltage-source rectifier," *IEEE Trans. Ind. Appl.*, vol. 36, no. 4, pp. 1419–1429, Sep./Oct. 2000.

- [14] M. Su, X. Long, Y. Sun, and J. Yang, "An active power decoupling method for single-phase AC/DC converters," *IEEE Trans. Ind. Informat.*, vol. 10, no. 1, pp. 461–468, Jan. 2014.

- [15] R. Wang, F. Wang, D. Boroyevich, and P. Ning, "A high power density single-phase PWM rectifier with active ripple energy storage," *IEEE Trans. Power Electron.*, vol. 26, no. 5, pp. 1378–1383, May 2011.

- [16] Y. Ohnuma, and J. Itoh, "A novel single-phase buck PFC AC-DC converter with power decoupling capability using an active buffer," *IEEE Trans. Ind. Appl.*, vol. 50, no. 3, pp. 1905–1914, May–Jun. 2014.

- [17] H. Hu, S. Harb, N. H. Kutkut, Z. J. Shen, and I. Batarseh, "A single-stage microinverter without using electrolytic capacitors," *IEEE Trans. Power Electron.*, vol. 28, no. 6, pp. 2677–2687, Jun. 2013.

- [18] W. Chen and S. Hui, "Elimination of an electrolytic capacitor in ac/dc light emitting diode (LED) driver with high input power factor and constant output current," *IEEE Trans. Power Electron.*, vol. 27, no. 3, pp. 1598– 1607, Mar. 2012.

- [19] H. Li, K. Zhang, H. Zhao, S. Fan, and J. Xiong, "Active power decoupling for high-power single-phase PWM rectifiers," *IEEE Trans. Power Electron.*, vol. 28, no. 3, pp. 1308–1319, Mar. 2013.

- [20] S. V. Araujo, P. Zacharias, and R. Mallwitz, "Highly efficient single-phase transformerless inverters for grid-connected photovoltaic systems," *IEEE Trans. Ind. Electron.*, vol. 57, no. 9, pp. 3118–3128, Sep. 2010.

- [21] M. Chen, K. K. Afridi, and D. J. Perreault, "Stacked switched capacitor energy buffer architecture," *IEEE Trans. Power Electron.*, vol. 28, no. 11, pp. 5183–5195, Nov. 2013.

- [22] H. Wang, H. S. H. Chung, and W. Liu, "Use of a series voltage compensator for reduction of the DC-Link capacitance in a Capacitorsupported system," *IEEE Trans. Power Electron.*, vol. 29, no. 3, pp. 1163– 1175, Mar. 2014.

- [23] H. Hu, S. Harb, N. H. Kutkut, I. Batarseh, and Z. J. Shen, "A review of power decoupling techniques for microinverters with three different decoupling capacitor locations in PV systems," *IEEE Trans. Power Electron.*, vol. 28, no. 6, pp. 2711–2726, Jun. 2013.

- [24] D. N. Zmood and D. G. Holmes, "Stationary frame current regulation of PWM inverters with zero steady-state error," *IEEE Trans. Power Electron.*, vol. 18, no. 3, pp. 814–822, May 2003.

- [25] F. Gao, D. Li, P. C. Loh, Y. Tang, and P. Wang, "Indirect dc-link voltage control of two-stage single-phase PV inverter," in *Proc. IEEE Appl. Power Electron. Conf.*, Sep. 2009, pp. 1166–1172.

- [26] A. Lesnicar and R. Marquardt, "An innovative modular multilevel converter topology suitable for a wide power range," in *Proc. IEEE PowerTech Conf.*, Bologna, Italy, 2003, pp. 1–6.

Yi Tang (S'10–M'14) received the B.Eng. degree in electrical engineering from Wuhan University, Wuhan, China, in 2007, and the M.Sc. and Ph.D. degrees from the School of Electrical and Electronic Engineering, Nanyang Technological University, Singapore, in 2008 and 2011, respectively.

During the summer of 2007, he was a Visiting Scholar with the Institute of Energy Technology, Aalborg University, Aalborg, Denmark, where he worked on the control of grid-interfaced inverters and uninterruptible power supplies. From 2011 to 2013,

he was a Senior Application Engineer with Infineon Technologies Asia Pacific, Singapore. Since 2013, he has been with the Department of Energy Technology, Aalborg University, as a Postdoctoral Research Fellow. He has authored and coauthored more than 20 research papers. He has six U.S. patent applications and one German patent application.

**Frede Blaabjerg** (S'86–M'88–SM'97–F'03) received the Ph.D. degree from Aalborg University, Aalborg, Denmark, in 1992.

He was with ABB-Scandia, Randers, Denmark, from 1987 to 1988. He became an Assistant Professor in 1992, an Associate Professor in 1996, and a Full Professor of power electronics and drives in 1998 at Aalborg University, Aalborg, Denmark. His current research interests include power electronics and its applications such as in wind turbines, PV systems, reliability, harmonics and adjustable speed drives.

Dr. Blaabjerg received 15 IEEE Prize Paper Awards, the IEEE PELS Distinguished Service Award in 2009, the EPE-PEMC Council Award in 2010, the IEEE William E. Newell Power Electronics Award 2014, and the Villum Kann Rasmussen Research Award 2014. He was an Editor-in-Chief of the IEEE Transactions on Power Electronics from 2006 to 2012. He has been Distinguished Lecturer for the IEEE Power Electronics Society from 2005 to 2007 and for the IEEE Industry Applications Society from 2010 to 2011.

**Poh Chiang Loh** (S'01–M'04–SM'12) received the B.Eng. (Hons.) and M.Eng. degrees from the National University of Singapore, Singapore, in 1998 and 2000, respectively, and the Ph.D. from Monash University, Melbourne, Australia, in 2002, all in electrical engineering.

Since 2013, he has been with Aalborg University, Aalborg, Denmark.

Peng Wang (M'00) received the B.Sc. degree from Xian Jiaotong University, Xian, China, in 1978, the M. Sc. degree from the Taiyuan University of Technology, Taiyuan, China, in 1987, and the M. Sc. and Ph.D. degrees from the University of Saskatchewan, Saskatoon, SK, Canada, in 1995 and 1998, respectively.

He is currently an Associate Professor at Nanyang Technological University, Singapore.

Chi Jin received the B.Sc. degree in electrical engineering from Wuhan University, Wuhan, China, in 2007, and the M.Sc. degree from Nanyang Technological University, Singapore, in 2009, where he is currently working toward the Ph.D. degree in the School of Electrical and Electronic Engineering.

In 2011, he was a Visiting Scholar with the Institute of Energy Technology, Aalborg University, Aalborg East, Denmark, where he worked on the control strategies of hybrid ac/dc/storage microgrid system. Since 2013, he has also been a Research As-

sociate with the Energy Research Institute, Nanyang Technological University, Singapore.