# A Design of Boost Converter With Time-Domain MPPT and Digital Self-Tracking ZCD for Thermoelectric Energy Harvesting Applications

Jong Wan Jo<sup>®</sup>, *Graduate Student Member, IEEE*, Dae-Han Yu<sup>®</sup>, *Student Member, IEEE*, YoungGun Pu<sup>®</sup>, *Member, IEEE*, Yeon Jae Jung<sup>®</sup>, Seokkee Kim<sup>®</sup>, Joon-Mo Yoo<sup>®</sup>, *Student Member, IEEE*, Keum Cheol Hwang<sup>®</sup>, *Senior Member, IEEE*, Youngoo Yang<sup>®</sup>, *Senior Member, IEEE*, and Kang-Yoon Lee<sup>®</sup>, *Senior Member, IEEE*

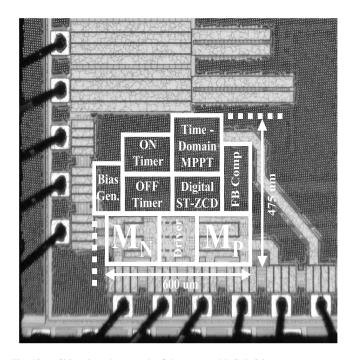

Abstract—This article presents a dc–dc boost converter for energy harvesting. The time-domain maximum power point tracking (MPPT) technique implements to maximize the source's energy harvesting performance with no additional switch and time slot. Furthermore, it is implementing digital self-tracking zero current detectors for high efficiency. This dc–dc boost converter fabricates with a 180-nm CMOS process. The input voltage of the boost converter ranges from 0.2 to 0.7 V and generates an output voltage of 1.2 V. The total area of this converter with the MPPT operation is 600  $\mu$ m  $\times$  475  $\mu$ m. The measured power conversion efficiency of this dc–dc boost converter is 85.5%.

*Index Terms*—DC–DC boost converter, digital self-tracking zero current detector (ST-ZCD), energy harvesting, time-domain maximum power point tracking (MPPT).

#### I. INTRODUCTION

THESE days, energy harvesting from ultralow power sources is more important because wearable electronics or wireless sensors are more popular. Especially the wireless

Jong Wan Jo, YoungGun Pu, Yeon Jae Jung, Seokkee Kim, and Kang-Yoon Lee are with the College of Information and Communication Engineering, Sungkyunkwan University, Suwon 16419, South Korea (e-mail: jw1114@skku.edu; hara1015@skku.edu; yj.jung@skku.edu; seokkeekim@skku.edu; klee@skku.edu).

Dae-Han Yu is with the LSI, Samsung Electronics, Suwon 16677, South Korea (e-mail: mysky467@g.skku.edu).

Joon-Mo Yoo is with the Department of Electrical and Computer Engineering, College of Information and Communication Engineering, Sungkyunkwan University, Suwon 16419, South Korea (e-mail: fiance2@g.skku.edu).

Keum Cheol Hwang and Youngoo Yang are with the School of Electronic and Electrical Engineering, Sungkyunkwan University, Suwon 16419, South Korea (e-mail: khwang@skku.edu; yang09@skku.edu).

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TPEL.2023.3303466.

Digital Object Identifier 10.1109/TPEL.2023.3303466

sensor is essential for the Internet of Things (IoT) and drawing more attention [1], [2]. The energy sources used in these systems are meager, so maximizing energy harvesting is essential.

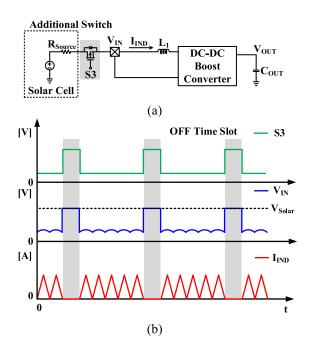

The maximum power point tracking (MPPT) operation is essential to maximum the energy harvesting performance from a source. An energy harvesting boost converter extracts maximum power from energy sources, such as solar or thermoelectric generators (TEGs), according to MPPT operation. This article presents a method that requires a reference voltage among various methods for MPPT operation, and this reference voltage is made by using the open-circuit input voltage [3], [4], [5]. The open-circuit input voltage is the boost converter's input voltage when the current does not flow through the energy source. The reference voltage of MPPT is some ratio of open-circuit input voltage, such as half of input voltage. The reference voltage of MPPT is compared with the input voltage at every switch. The conventional boost converter sensed the open-circuit input voltage by setting up the additional OFF-timing slot [6], [7], [8], [9]. Fig. 1(b) shows the conventional MPPT operation timing diagram. An OFF-time slot is used periodically to sense the open-circuit input voltage of the boost converter. At the OFF time, the S3 switch is open, and the current is not flowing through  $R_{\text{TEG}}$ . Therefore, the pure open-circuit  $V_{\text{IN}}$  voltage without any resistive voltage drop can be sensed in this way. Conventional MPPT circuits of energy harvesting had added a series switch to the boost converter, as shown in Fig. 1(a). The series switch's resistance must be minimal to reduce the conduction loss of the boost converter. This means that the size of this additional switch should be considerable. Moreover, the time slot's period is from millisecond to the second scale. So, to generate this periodical OFF-time slot, an internal clock and additional frequency dividing circuit are needed regardless of the boost converter's control. These additional blocks occupy the area and increase the quiescent current of the dc-dc boost converter. So, if the MPPT concept is changed, the additional series switch will not be required to perform the MPPT operation. Furthermore, the oscillator and frequency dividing circuit can be removed. This article proposes the time-domain MPPT concept with no additional huge series switch and other circuitry related to the time slot.

This work is licensed under a Creative Commons Attribution 4.0 License. For more information, see https://creativecommons.org/licenses/by/4.0/

Manuscript received 21 February 2023; revised 14 May 2023 and 12 July 2023; accepted 6 August 2023. Date of publication 9 August 2023; date of current version 22 September 2023. This work was supported in part by the Korea Institute for Advancement of Technology grant funded by the Korea Government (MOTIE) (P0012451, The Competency Development Program for Industry Specialist) and in part by the Institute of Information & Communications Technology Planning & Evaluation grant funded by the Korea Government (MSIT) (2020-0.00261, Development of low power/low delay/self-power suppliable RF simultaneous information and power transfer system and stretchable electronic epineurium for wireless nerve bypass implementation). Recommended for publication by Associate Editor M. Vitelli. (*Corresponding author: Kang-Yoon Lee.*)

Fig. 1. (a) Structure of conventional MPPT. (b) Operation of conventional MPPT.

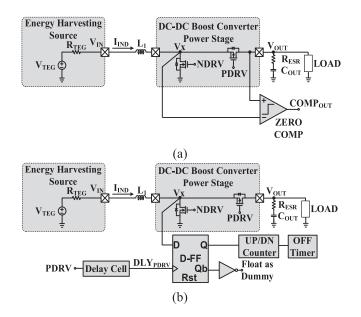

Fig. 2. (a) Conventional ZCD concept using comparator. (b) Conventional ZCD concept using D-flip flop.

To enhance the efficiency of the boost converter in energy harvesting applications, the accurate and low-power operation of the zero current detectors (ZCDs) is required for blocking reverse current from  $V_{OUT}$  to  $V_X$ . The conventional ZCD compares the  $V_X$  node voltage with the  $V_{OUT}$  voltage level [10], [11], [12], [13] when the inductor current flows through the PMOS switch, as shown in Fig. 2(a). This concept is very intuitive, but it is easy to be affected by the characteristics of the comparator. Furthermore, since the resistance of the PMOS pass transistor is minimal, the difference voltage between  $V_X$  node and  $V_{OUT}$ node is incomparably small when the current flowing through

Fig. 3. (a) Abnormal operation of the conventional ZCD using D-flip flop. (b) Normal operation of the proposed ZCD.

the PMOS switch is almost zero. Therefore, this concept is easily affected by the comparator's offset voltage or delay time. The comparator for detecting zero current will be designed in large size to minimize the comparator's offset. Also, to reduce the comparator's delay time, this comparator will consume a large amount of current, which may reduce the efficiency of the dc–dc boost converter, especially all light load conditions. Second, how to track the fall time of the  $V_X$  node is also used in [14], [15], [16], [17], and [18] to find the zero current point, as shown in Fig. 2(b).

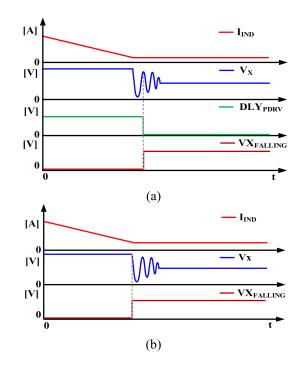

Compared to the previous one, the advantage of this concept is that comparator is not used for detecting the zero current of the inductor. Therefore, the ZCD design is simple and not affected by the comparator property. Nevertheless, the ringing of VX node voltage can cause the abnormal operation of zero current detecting. During the PMOS switch-OFF time, the inductor current flow path abruptly blocks the energy stored in the inductor, and parasitic capacitance can create a resonance phenomenon. For this reason, the  $V_{\rm X}$  voltage ringing is generated inherently. DLY<sub>PRDV</sub> is the delay time of the PDRV signal driving signal of the PMOS switch.  $VX_{FALLING}$  is  $V_X$  node voltages at free-wheeling operation boost converter.  $DLY_{PRDV}$ and VX<sub>FALLING</sub> can cause the abnormal operation of ZCDs, as shown in Fig. 3(a). In this case, the falling of the V<sub>X</sub> node is not sensed, and ZCD could not function normally. The proposed boost converter is not affected by the comparator's properties and is robust for ringing of  $V_{\rm X}$  node voltage.

The rest of this article is organized as follows. Section II presents the architecture of the proposed energy harvesting boost converter. The overall structure of this boost converter is shown in this section. After that, the details of the building blocks are presented in Section III. The circuit and operation of each block

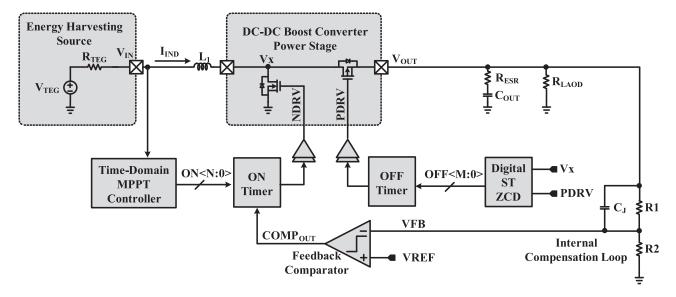

Fig. 4. Top diagram of the proposed boost converter for energy harvesting system.

Fig. 5. Operation of the proposed boost converter.

will be illustrated in this section. In Section IV, the experimental results are discussed. Finally, Section V concludes this article.

### II. ARCHITECTURE OF THE PROPOSED BOOST CONVERTER

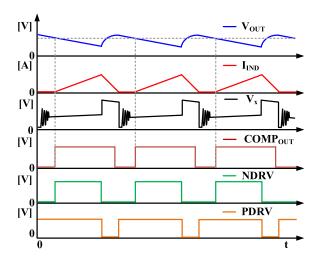

Fig. 4 shows the structure of the proposed boost converter. This boost converter consists of an ON timer, OFF timer, feedback comparator, the time-domain MPPT block, and the digital self-tracking ZCD (ST-ZCD). Fig. 5 shows the operation of the proposed dc–dc boost converter. The feedback comparator sets the switching timing. The feedback comparator compares the feedback voltage (VFB) divided by resistors with the reference voltage (VREF). The ON time duration of this converter is generated by ON timer. The ON time control by MPPT operation. The time-domain MPPT block selects the switching frequency for maximum efficiency. The digital ST-ZCD block decides the OFF time of this boost converter. The digital ST-ZCD block monitors the  $V_X$  node voltage and generates the OFF time control code OFF[M:0]. By controlling capacitor value in OFF timer, the

Fig. 6. (a) Model of TEG. (b) Relationship between input voltage and input voltage.

OFF time control and the zero current level of the inductor current are tracked. The OFF time control code is input to the OFF timer, and the OFF time pulse is generated proportional to OFF[M:0].

### **III. BUILDING BLOCKS**

#### A. Time-Domain MPPT

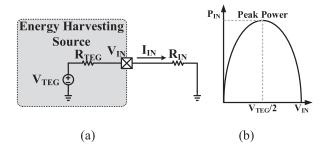

Fig. 6(a) shows a modeled TEG with a voltage source ( $V_{\text{TEG}}$ ) and internal resistance ( $R_{\text{TEG}}$ ) [19], [20], [21].

When the boost converter is connected to the TEG,  $R_{IN}$  means the input impedance of the dc–dc boost converter. In this model, the input current of the boost converter is calculated by

$$I_{\rm IN} = \frac{V_{\rm TEG} - V_{\rm IN}}{R_{\rm TEG}}.$$

(1)

So, the input power of boost converter is shown as follows:

$$P_{\rm IN} = V_{\rm IN} \times I_{\rm IN} = V_{\rm IN} \times \frac{V_{\rm TEG} - V_{\rm IN}}{R_{\rm TEG}}.$$

(2)

To find the maximum power point of TEG, the derivative equation of (2) is equal to 0, as shown in Fig. 6(b)

$$\frac{\partial P_{\rm IN}}{\partial V_{\rm IN}} = \frac{V_{\rm TEG}}{R_{\rm TEG}} - \frac{2V_{\rm IN}}{R_{\rm TEG}} = 0 \tag{3}$$

Fig. 7. (a) Structure of the proposed open-circuit VIN sensing. (b) Operation of the proposed open-circuit VIN sensing.

$$V_{\rm IN} = \frac{V_{\rm TEG}}{2}.$$

(4)

As (4) indicates, the input voltage should be half of the voltage of the open-circuit voltage to maximize the power of energy harvesting [22]. In order to meet this condition, the input voltage is compared with  $V_{\rm TEG}/2$  voltage, and adjusts the boost converter's time to control the boost converter's input voltage. To compare the input voltage, the open-circuit voltage needs the sense to generate the half of this voltage. In the proposed time-domain MPPT algorithm, by increasing the ON time control bit, the boost converter regulates half of the  $V_{\rm IN}$  for maximum efficiency.

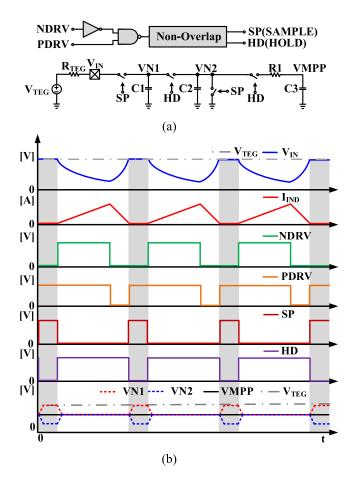

Fig. 7(a) and (b) show the proposed open-circuit  $V_{\rm IN}$  voltage sensing structure and operation, respectively. The additional large series switch and OFF-time control are unnecessary. The boost converter operates in discontinuous current mode (DCM), and dead time between switching generates inherently. Furthermore, this dead time using for open-circuit input voltage sensing instead of an additional OFF-time slot. Because the input current does not flow from the energy source at this time, the voltage of the input source can make sense without a resistive voltage drop. This means that the artificial OFF-time slot does not need it because of using the boost converter's normal operation. Therefore, the oscillator and frequency dividing circuit are also

Fig. 8. (a) Structure of the proposed time-domain MPPT. (b) Operation of the proposed time-domain MPPT.

not needed. Furthermore, the other large switch series connects to the boost converter, and the internal clock frequency does not even use.

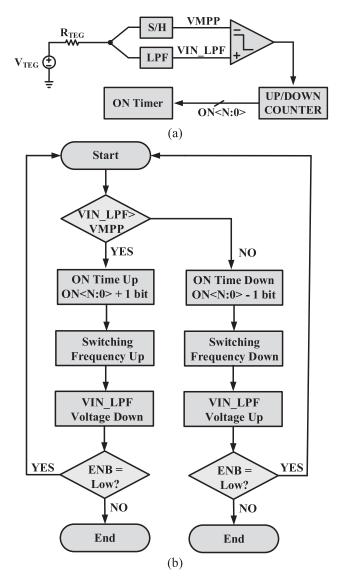

The reference voltage (VMPP) of the time-domain MPPT function is generated by the sampling and holding circuit. The input voltage is sampled at the dead time between switching. The sample (SP) and hold (HD) signals can generate using NDRV and PDRV power switch drive signals. At the dead time, the input voltage of the boost converter is sampled and stored in the sampling capacitor (C1). In the hold status, the sample voltage divides by x0.5 or x0.8 of the input voltage compares with the low-pass filtered input voltage (VIN\_LPF), and the ON time is determined by the compared result, as shown in Fig. 8(a).

The VMPP voltage is compared with the VIN\_LPF voltage, which determines whether to increase or decrease the ON time, as shown in Fig. 8(b). If the VIN\_LPF voltage is larger than

Fig. 9. Proposed ZCD concept.

the reference voltage of the MPPT (VMPP), the timing of the boost converter should increase. Then, the VIN\_LPF voltage is lowered. In contrast, if VIN\_LPF is lower than the VMPP voltage, the timing of the boost converter should be reduced, and the VIN\_LPF voltage will increase. By adjusting the time of the boost converter, the VIN\_LPF voltage tracks the VMPP voltage, and the MPPT operation performs automatically.

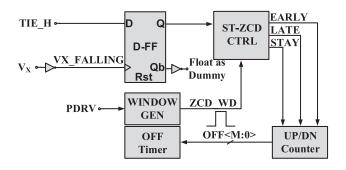

#### B. Digital ST-ZCD

In the case of conventional ZCD design, comparator is used to compare  $V_{\rm X}$  and  $V_{\rm OUT}$ , conventional ZCD design is depended on the comparator's offset and delay performance. The proposed digital ST-ZCD can detect zero current with low power consumption without depending on comparator performance, because of digital self-track  $V_{\rm X}$  node, as shown in Fig. 9. First, the  $V_{\rm X}$  node voltage's falling timing is monitored and detected using a D-flip flop. Because the comparator does not operate monitoring of VX node voltage, the performance of ZCD is not affected by the comparator's properties, such as offset and delay. The difference between the proposed concept and the work in [12], [13], [14], [15], and [16] is that the  $V_X$  node voltage's falling timing is detected by the D-flip flop's clock, which reacts to the edge of the signal. This concept's advantage is that the V<sub>X</sub> node ringing caused by PMOS/NMOS power switch-OFF does not affect the ZCD operation, as shown in Fig. 3(b). The D-flip flop outputs the VX\_FALLING signal once a switching, regardless of the  $V_{\rm X}$  node's ringing. Because the ringing cannot affect the output of the D-flip flop, it is robust compared to the previous concept.

The VX\_FALLING signal generated by the D-flip flop is compared with target  $V_X$  node falling time. The target time of the  $V_X$  node is the time at which the value of the inductor current is zero. Digital ST-ZCD CTRL controls UP/DN Counter using output of the WINDOW GEN for obtaining the target time. To prevent the OFF<M:0> code cycle in a steady state, the VX\_FALLING signal time is compared with the target timing window (ZCD\_WD), as shown in Fig. 10. After comparing the timing of VX\_FALLING with ZCD\_WD, the ST-ZCD CTRL determines whether the PMOS is required. The power switches OFF earlier or later than the target time. To start with, if the PMOS power switch OFF time is earlier than the target time, the OFF time of the boost converter should be greater than that shown in Fig. 10(b). In contrast, if the PMOS power is switched OFF

Fig. 10. Timing diagram of digital ST-ZCD at (a) STAY status, (b) EARLY status, and (c) LATE status.

longer than the target time, the OFF time of the boost converter should be shorter, as shown in Fig. 10(c). If the rising edge of the VX\_FALLING signal's is within the ZCD\_WD signal, the OFF<M: 0> code is neither increment nor decremented. Therefore, by deciding whether the PMOS power switches OFF earlier or later, the OFF time of the boost converter can be controlled to meet zero inductor current.

Fig. 11. (a) Structure of ON timer. (b) Operation of ON timer.

The UP/DN counter generates the OFF-time control code OFF[M:0] by adding or subtracting one code from the earlier code. The adding or subtracting of OFF<M:0> decides the PMOS power switch's OFF timing. By adding one code to the OFF[M:0] stored in advance, the OFF time of the boost converter is longer. In contrast, subtracting the OFF[M:0] code reduces the OFF time of the boost converter.

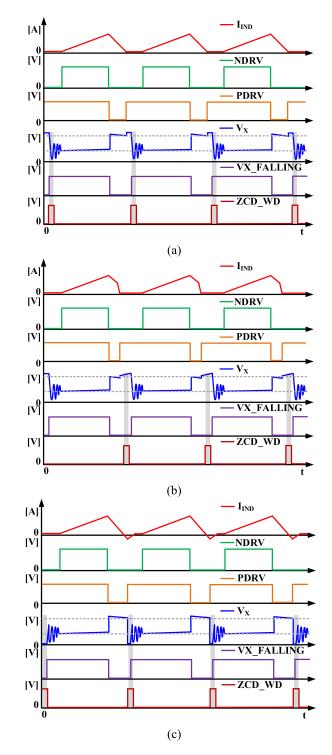

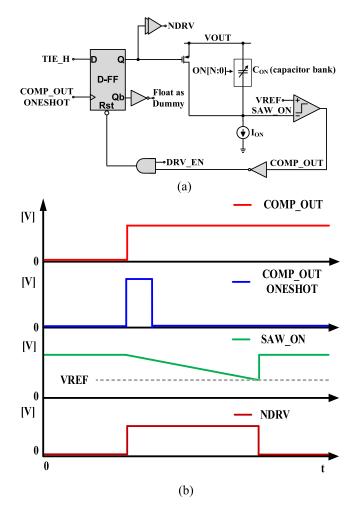

# C. ON/OFF Timer

The time-domain MPPT and digital ST-ZCD control blocks generate the ON/OFF time control code. Each code is input to ON/OFF timer blocks for control capacitor bank. Fig. 11(a) shows the proposed ON timer structure. The control code of ON time and real ON time of the boost converter is proportional. The ON time starts when the COMP\_OUT triggers from low to high.  $C_{\text{ON}}$  discharge constant bias current  $I_{\text{ON}}$  and the SAW\_ON node voltage is decreased with a constant slope decided by  $C_{\text{ON}}$ and  $I_{\text{ON}}$  as shown Fig. 11(b). The ON[N:0] code is decided in advance by the MPPT operation. When the SAW\_ON node voltage is lower than the VREF voltage, the comparator in the ON timer is triggered, and the D-flip flop resets. The boost converter decides when to terminate the NDRV pulse and reset the D-flip flop.

Fig. 12. (a) Structure of OFF timer. (b) Operation of OFF timer.

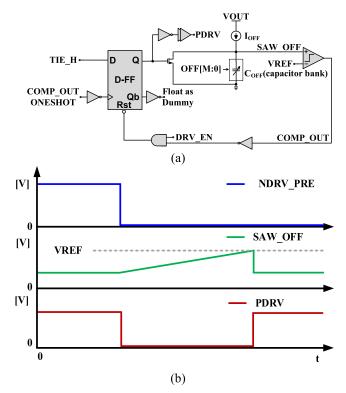

Similar to the ON timer, the OFF time determines the charging of the capacitor  $C_{\text{OFF}}$  with a constant bias current  $I_{\text{OFF}}$  as shown Fig. 12(a). When the NMOS power switch is OFF, the PMOS power switch is ON, and if the VREF voltage is lower than the SAW\_OFF node voltage, the D-flip flop is reset, and the PMOS power switch is OFF as shown Fig. 12(b).

#### **IV. EXPERIMENTAL RESULTS**

Fig. 13 shows the chip microphotograph. This chip fabricates with a 180-nm CMOS process, and the die area of the energy harvesting boost converter is  $600 \ \mu m \times 475 \ \mu m$ .

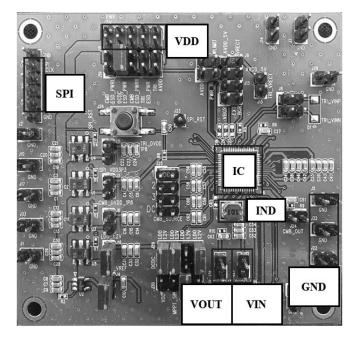

Fig. 14 shows the chip measurement board of the proposed dc–dc boost converter. This board comprises IC, an external inductor, and several ports for chip testing. There is a VDD and GND port for chip operation and  $V_{\rm IN}$  and  $V_{\rm OUT}$  pins of the dc–dc boost converter. To control the boost converter, the SPI control ports are used too.

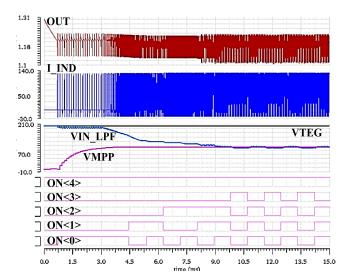

Fig. 15 shows the simulation results of the time-domain MPPT operation. The reference voltage of MPPT (VMPP) is generated using dead times between switching. The low-pass filtered  $V_{IN}$  voltage (VIN\_LPF) is compared with the VMPP voltage, and the ON time of the boost converter is adjusted by controlling the ON<4:0> code.

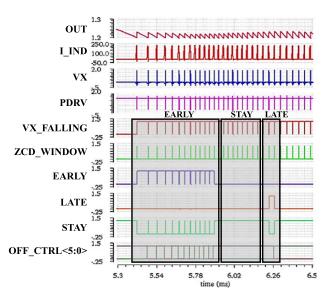

Fig. 16 shows the simulation waveform of the digital ST-ZCD operation. According to the timing of VX\_FALLING, the EARLY, LATE, or STAY signals are generated and the OFF time of the boost converter is controlled by adding or subtracting the OFF<5:0 code.

Fig. 13. Chip microphotograph of the proposed DC-DC boost converter.

Fig. 14. Measurement board of the DC-DC boost converter.

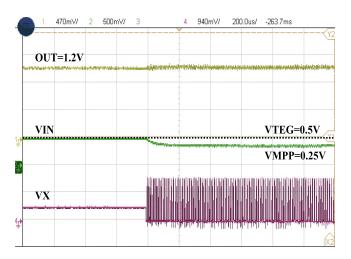

Fig. 17 shows the measured waveform of the energy harvesting boost converter. When the boost converter is operating, the input voltage of boost converter is controlled to MPPT target voltage (VMPP), such as the waveform of the time-domain MPPT operation simulation result. By observing the  $V_{\rm IN}$  voltage regulation, the VMPP voltage also can be found out indirectly. The ON time of boost converter is also controlled to meet the MPPT target voltage. Finally, the operation of generating the MPPT reference voltage and controlling the ON time code, the  $V_{\rm IN}$  voltage of boost converter is regulated to the MPPT target voltage and the maximum power tracking is functioned.

Fig. 15. Time-domain MPPT simulation results of the boost converter.

Fig. 16. Digital ST-ZCD simulation results of the boost converter.

Fig. 17. Measured waveform of the time-domain MPPT operation.

| Reference              |                 | [9]                                    | [10]                                   | [15]                            | [18]                                            | [23]                            | [24]                                   | This Works                                          |

|------------------------|-----------------|----------------------------------------|----------------------------------------|---------------------------------|-------------------------------------------------|---------------------------------|----------------------------------------|-----------------------------------------------------|

| Process                | nm              | 130                                    | 350                                    | 65                              | 180                                             | 180                             | 180                                    | 180                                                 |

| Application            | -               | Thermoelectric<br>Energy<br>Harvesting | Thermoelectric<br>Energy<br>Harvesting | Thermal<br>Energy<br>Harvesting | Autonomous<br>Body-Heat<br>Energy<br>Harvesting | Thermal<br>Energy<br>Harvesting | Thermoelectric<br>Energy<br>Harvesting | Thermoelectric<br>generator<br>Energy<br>Harvesting |

| MPPT                   | -               | YES                                    | YES                                    | NO                              | YES                                             | NO                              | YES                                    | YES                                                 |

| Input Voltage<br>Range | mV              | 80-300                                 | 70-600                                 | 50-200                          | 15-200                                          | 60-460                          | 25-300                                 | 200-700                                             |

| Output Voltage         | V               | 0.3                                    | 3-5.8                                  | 1.2                             | 1.2                                             | 1-1.8                           | 25-300                                 | 1.2                                                 |

| Load Current           | mA              | 0.1                                    | 1                                      | -                               | -                                               | 0-1.3                           | 0.225                                  | 0.1-1                                               |

| Input Inductor         | $\mu H$         | 22                                     | 22                                     | 27                              | 100                                             | 22                              | 82<br>(transformer)                    | 100                                                 |

| Output Capacitor       | $\mu$ F         | 4.7                                    | 10                                     | 1                               | 1                                               | 0.05                            | -                                      | 1                                                   |

| Peak Efficiency        | %               | 72.1                                   | 72.2                                   | 73                              | 82                                              | 78.55                           | 84                                     | 85.5                                                |

| Die Area               | mm <sup>2</sup> | 1.16                                   | 1.90                                   | 0.99                            | 1.02                                            | 0.5292                          | 1.6                                    | 0.29                                                |

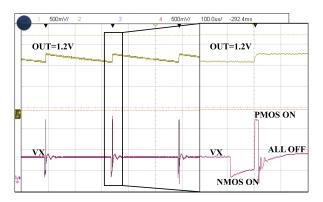

Fig. 18. Measured waveform of the digital ST-ZCD operation.

Fig. 19. Measured efficiency of the proposed energy harvesting boost converter.

Fig. 18 shows the measured digital ST-ZCD waveform. After the PMOS is switched-OFF, no diode conduction loss detects in this waveform. By measuring the waveform of  $V_X$  node voltage, the steady-state condition is in STAY operation, and the ST-ZCD function is also operating.

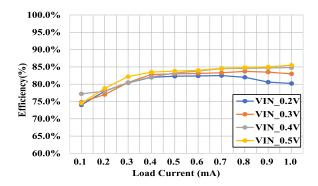

Fig. 19 shows the measured efficiency of the proposed boost converter. Efficiency is measured when the proposed boost converter output voltage regulated 1.2 V. The peak efficiency is 85.5% at input voltage 0.5 V and the load current upper 1 mA.

Table I shows the performance comparison of the proposed energy harvesting boost converter with prior works of the lowvoltage boost converter. This chip is fabricated with a 0.18- $\mu$ m process. The proposed energy harvesting boost converter has

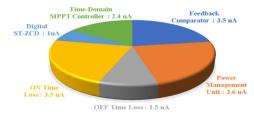

Fig. 20. Measured quiescent current of the proposed energy harvesting boost converter at 0.1-mA load condition.

inductor size as 100  $\mu$ H to minimize the conduction loss that can occur in metal routing and PCB parasitic, inductor size of 100  $\mu$ H improves conduction loss on minimizing the inductor current slope. The proposed energy harvesting boost converter output capacitor is selected as  $1-\mu F$  capacitor to drive an IoT device has operating current that 1  $\mu$ A in several milliseconds. The proposed energy harvesting boost converter has wide input voltage and high efficiency by using time-domain MPPT and digital ST-ZCD. The proposed energy harvesting boost converter is an output voltage of 1.2 V and a current load range from 0.1 to 1 mA while supporting a wide input range from 0.2 to 0.7 V. This work has 0.29-mm<sup>2</sup> small die area using the proposed digital ST-ZCD that removes input PMOS switch. Furthermore, using the concept of the time-domain MPPT, the peak efficiency of the proposed energy harvesting boost converter is 85.5%. When using the proposed energy harvesting boost converter, an efficiency improvement of 1.5% to 13.4% is achieved when using the proposed concept compared to prior work. The power loss distributions consist of fixed internal power consumption in the internal block, inductor  $R_{on}$  loss, power transistor conduction loss, and power transistor switching loss. Fixed power consumption is consisting of internal operating block, total quiescent current is 15.5  $\mu$ A at 0.1-mA load condition, as shown Fig. 20. The power loss of almost 10% is estimated from the inductor  $R_{\rm on}$  and power transistor conduction loss and switching loss.

## V. CONCLUSION

This article proposed a boost converter with the digital ST-ZCD for TEG energy harvesting applications. The proposed

method implements the time-domain MPPT concept using the dead time between switching in DCM mode, so additional series switching is unnecessary. This concept also does not require the additional time slot for MPPT generating slot used in open-circuit input voltage sensing. Because the input current does not flow from the energy source at this MPPT generating time using boost converter dead time. In this article, the digital ST-ZCD is proposed to operate with high efficiency. In this concept, the operation of the digital ST-ZCD is not affected by comparator performance and operated low power consumption due to not using a comparator. Also, by using the D-flip flop's clock, the detection of the  $V_{\rm X}$  node falling edge is robust for the ringing of  $V_{\rm X}$  node voltage. This chip fabricates with a 180-nm CMOS process. The area of the die is 600  $\mu$ m  $\times$  475  $\mu$ m. The measured peak efficiency of the energy harvesting boost converter is 85.5%.

#### REFERENCES

- [1] Z. Shang, Y. Zhao, W. Gou, L. Geng, and Y. Lian, "83.9% efficiency 100-mV self-startup boost converter for thermoelectric energy harvester in IoT applications," *IEEE Trans. Circuits Syst. II: Express Briefs*, vol. 67, no. 9, pp. 1654–1658, Sep. 2020, doi: 10.1109/TCSII.2020.2999331.

- [2] S. Zeadally, F. Shaikh, A. Talpur, and Q. Sheng, "Design architectures for energy harvesting in the Internet of Things," *Renewable Sustain. Energy Rev.*, vol. 128, 2020, Art. no. 109901, doi: 10.1016/j.rser.2020.109901.

- [3] L. Costanzo, A. L. Schiavo, M. Vitelli, and L. Zuo, "Optimization of AC–DC converters for regenerative train suspensions," *IEEE Trans. Ind. Appl.*, vol. 58, no. 2, pp. 2389–2399, Mar./Apr. 2022, doi: 10.1109/TIA.2021.3136145.

- [4] L. Costanzo, T. Lin, W. Lin, A. L. Schiavo, M. Vitelli, and L. Zuo, "Power electronic interface with an adaptive MPPT technique for train suspension energy harvesters," *IEEE Trans. Ind. Electron.*, vol. 68, no. 9, pp. 8219–8230, Sep. 2021, doi: 10.1109/TIE.2020.3009584.

- [5] K.-H. Chen, "Energy-harvesting systems," in Proc. Power Manage. Techn. Integr. Circuit Des., 2016, pp. 483–526, doi: 10.1002/ 9781118896846.ch8.

- [6] P. Zhang and L. Liu, "A photovoltaic and thermal energy combining harvesting interface circuit with MPPT and single inductor," in *Proc. IEEE 15th Int. Conf. Solid-State Integr. Circuit Technol.*, 2020, pp. 1–3, doi: 10.1109/ICSICT49897.2020.9278256.

- [7] K. Suzuki and M. Deng, "Operator-based MPPT control system for thermoelectric generation by measuring the open-circuit voltage," in *Proc. Int. Conf. Adv. Mechatronic Syst.*, 2016, pp. 236–241, doi: 10.1109/ICAMechS.2016.7813453.

- [8] T. Oh, O. Hassan, S. Shamsir, and S. K. Islam, "DC-DC boost converter design with maximum power point tracker (MPPT) used in RF- energy harvester," in *Proc. IEEE Int. Symp. Med. Meas. Appl.*, 2019, pp. 1–5, doi: 10.1109/MeMeA.2019.8802206.

- [9] S.-H. Wu, X. Liu, Q. Wan, Q. Kuai, Y.-K. Teh, and P. K. T. Mok, "A 0.3-V ultralow-supply-voltage boost converter for thermoelectric energy harvesting with time-domain-based MPPT," *IEEE Solid-State Circuits Lett.*, vol. 4, pp. 100–103, Apr. 2021, doi: 10.1109/LSSC.2021.3076923.

- [10] J. Kim and C. Kim, "A DC–DC boost converter with variation-tolerant MPPT technique and efficient ZCS circuit for thermoelectric energy harvesting applications," *IEEE Trans. Power Electron.*, vol. 28, no. 8, pp. 3827–3833, Aug. 2013, doi: 10.1109/TPEL.2012.2231098.

- [11] H. Chen, H. Huang, S. Jheng, H. Huang, and Y. Huang, "High-efficiency PFM boost converter with an accurate zero current detector," *IEEE Trans. Circuits Syst. II: Express Briefs*, vol. 65, no. 11, pp. 1644–1648, Nov. 2018, doi: 10.1109/TCSII.2017.2754514.

- [12] P. Chen, C. Wu, and K. Lin, "A 50 nW-to-10 mW output power tri-mode digital buck converter with self-tracking zero current detection for photovoltaic energy harvesting," *IEEE J. Solid-State Circuits*, vol. 51, no. 2, pp. 523–532, Feb. 2016, doi: 10.1109/JSSC.2015.2506685.

- [13] X. He, P. Huang, Z. Wu, Y. Yan, J. Yang, and Y. Zheng, "Synchronous coarse-fine comparators based zero-current detector for DC-DC converter operating in switching frequency beyond 10 MHz," in *Proc. Int. Conf. Electron Devices Solid-State Circuits*, 2017, pp. 1–2, doi: 10.1109/EDSSC.2017.8126530.

- [14] S.-Y. Kim et al., "Design of a high efficiency DC–DC buck converter with two-step digital PWM and low power self-tracking zero current detector for IoT applications," *IEEE Trans. Power Electron.*, vol. 33, no. 2, pp. 1428–1439, Feb. 2018, doi: 10.1109/TPEL.2017.2688387.

- [15] P.-S. Weng, H.-Y. Tang, P.-C. Ku, and L.-H. Lu, "50 mV-input batteryless boost converter for thermal energy harvesting," *IEEE J. Solid-State Circuits*, vol. 48, no. 4, pp. 1031–1041, Apr. 2013, doi: 10.1109/ JSSC.2013.2237998.

- [16] M. Alhawari, B. Mohammad, H. Saleh, and M. Ismail, "An all-digital, CMOS zero current switching circuit for thermal energy harvesting," in *Proc. Eur. Conf. Circuit Theory Des.*, 2015, pp. 1–4, doi: 10.1109/EC-CTD.2015.7300094.

- [17] S.-H. Park, K.-T. Kim, and K.-Y. Lee, "Buck DC-DC converter with PFM/PWM dual mode self-tracking zero current detector," in *Proc. Int.* SoC Des. Conf., 2017, pp. 186–187, doi: 10.1109/ISOCC.2017.8368902.

- [18] S. Bose, T. Anand, and M. L. Johnston, "A 3.5-mV input singleinductor self-starting boost converter with loss-aware MPPT for efficient autonomous body-heat energy harvesting," *IEEE J. Solid-State Circuits*, vol. 56, no. 6, pp. 1837–1848, Jun. 2021, doi: 10.1109/JSSC. 2020.3042962.

- [19] W. Xie, G. Huang, X. Zhang, and F. Deng, "A maximum power point tracking controller for thermoelectric generators," in *Proc. 36th Chin. Control Conf.*, 2017, pp. 9079–9084, doi: 10.23919/ChiCC.2017.8028802.

- [20] Y.-H. Liu, Y.-H. Chiu, J.-W. Huang, and S.-C. Wang, "A novel maximum power point tracker for thermoelectric generation system," *Renewable Energy*, vol. 97, pp. 306–318, 2016, doi: 10.1016/j.renene.2016.05.001.

- [21] Y. K. Ramadass and A. P. Chandrakasan, "A battery-less thermoelectric energy harvesting interface circuit with 35 mV startup voltage," *IEEE J. Solid-State Circuits*, vol. 46, no. 1, pp. 333–341, Jan. 2011, doi: 10.1109/JSSC.2010.2074090.

- [22] A. Paraskevas and E. Koutroulis, "A simple maximum power point tracker for thermoelectric generators," *Energy Convers. Manage.*, vol. 108, pp. 355–365, 2016, doi: 10.1016/j.enconman.2015.11.027.

- [23] J. Jhang, H.-H. Wu, T. Hsu, and C.-L. Wei, "Design of a boost DC–DC converter with 82-mV startup voltage and fully built-in startup circuits for harvesting thermoelectric energy," *IEEE Solid-State Circuits Lett.*, vol. 3, pp. 54–57, Mar. 2020.

- [24] P. Cao, Y. Qian, P. Xue, D. Lu, J. He, and Z. Hong, "A bipolar-input thermoelectric energy-harvesting interface with boost/flyback hybrid converter and on-chip cold starter," *IEEE J. Solid-State Circuits*, vol. 54, no. 12, pp. 3362–3374, Dec. 2019.

Jong Wan Jo (Graduate Student Member, IEEE) received the B.S. degree in electronic engineering from the Department of Electronic Engineering, Cheongju University, Cheongju, South Korea, in 2018, and the M.S. degree in electrical engineering in 2020 from the Department of Electrical and Computer Engineering, Sungkyunkwan University, Suwon, South Korea, where he is currently working toward the Ph.D. degree in electrical engineering with the School of Information and Communication Engineering.

His research interests include wireless power transfer systems, power management IC, and phase-locked loop.

**Dae-Han Yu** (Student Member, IEEE) received the B.S. degree in electronic engineering in 2014 from the Department of Semiconductor System Engineering, Sungkyunkwan University, Suwon, South Korea, where he is currently working toward the M.S. degree in electrical engineering with the School of Information and Communication Engineering.

His research interests include power management in I.C especially in dc–dc converter and LDO.

**YoungGun Pu** (Member, IEEE) received the B.S. degree in electronic engineering, the M.S. degree in electrical engineering, and the Ph.D. degree in electronic engineering from the Department of Electronic Engineering, Konkuk University, Seoul, South Korea, in 2006, 2008, and 2012, respectively.

From 2012 to 2013, he was a Senior Engineer with Modem RF Lab, DMC R&D Center, Samsung Electronics, South Korea. From 2013 to 2019, he was a Senior Engineer with WDT/Hivics, South Korea. He is currently a Research Professor with Sungkyunkwan

University, Suwon, South Korea. His research interests include high-speed interface, CMOS fully integrated frequency synthesizers, oscillators, and RF transceivers.

**Yeon Jae Jung** received the B.S. degree in electronic engineering, the M.S. degree in electrical engineering, and the Ph.D. degree in electronic engineering from the School of Electrical Engineering, Seoul National University, Seoul, South Korea, in 1997, 1999, and 2003, respectively.

From 2003 to 2014, he was with GCT Semiconductor, Inc., San Jose, CA, USA, where he was involved in the design of CMOS RF transceiver ICs for W-CDMA, WLAN, WIMAX, CDMA, GPS, and LTE. From 2014 to 2020, he was with Celfras Semicon-

ductor, Inc., where he worked on BLE v4.2 ultralow power RF transceiver IC and power ICs for wireless power receiver, battery charger, and dc–dc converter. He is currently a VP with SKAiChips and a university–industry collaboration Professor also with Sungkyunkwan University, Suwon, South Korea. His research interests include the design of power-integrated circuits and CMOS RF transceiver.

Seokkee Kim received the B.S. degree in electronic engineering, the M.S. degree in electrical engineering, and the Ph.D. degree in electronic engineering from Seoul National University, Seoul, South Korea, in 1997, 1999, and 2006, respectively.

From 2001 to 2016, he was with GCT Semiconductor, Inc., San Jose, CA, USA. From 2016 to 2021, he was with Celfras Semiconductor, Inc., Seoul, South Korea. In 2021, he joined SKAIChips Company, Suwon, South Korea, as a Chief Design Officer. He is currently a university–industry collaboration Pro-

fessor with Sungkyunkwan University, Suwon, South Korea. His research interests include analog backend design and mass-production management, power management integrated circuits implementation, and CMOS RF transceiver and SOC-integrated implementation.

**Joon-Mo Yoo** (Student Member, IEEE) received the B.S. degree in electronic engineering from the Department of Electronic Engineering, Ajou University, Gyeonggi-do, South Korea, in 2002, and the M.S. degree in electrical engineering from the School of Electrical Engineering, Seoul National University, Seoul, South Korea, in 2004.

From 2004 to 2014, he was a Principal Engineer and an R&D Manager with GCT Semiconductor, Inc., San Jose, CA, USA and GCT Research, Inc., Seoul, Korea, where he developed PHS, CDMA, WCDMA,

LTE RF multimode multiband transceivers. From 2014 to 2016, he was a Chip Development Director with MELFAS, Seongnam, South Korea, where he was leading the capacitive touch-screen controller IC development. From 2016 to 2021, he was a Senior Director with Celfras Semiconductor, Jiangxi, China, where he was leading various power of wireless-charging solutions. He is currently with SKAIChips as an R&D Executive with Sungkyunkwan University, Suwon, South Korea. His research interests include digital circuit design, CMOS RF transceiver. and wireless charging solutions.

Keum Cheol Hwang (Senior Member, IEEE) received the B.S. degree in electronics engineering from Pusan National University, Busan, South Korea, in 2001, and the M.S. and Ph.D. degrees in electrical and electronic engineering from the Korea Advanced Institute of Science and Technology, Daejeon, South Korea, in 2003 and 2006, respectively.

From 2006 to 2008, he was a Senior Research Engineer with Samsung Thales, Yongin, South Korea, where he was involved with the development of various antennas, including multiband fractal anten-

nas for communication systems and Cassegrain reflector antenna and slotted waveguide arrays for tracking radars. From 2008 to 2014, he was an Associate Professor with the Division of Electronics and Electrical Engineering, Dongguk University, Seoul, South Korea. In 2015, he joined the Department of Electronic and Electrical Engineering, Sungkyunkwan University, Suwon, South Korea, where he is currently an Associate Professor. His research interests include advanced electromagnetic scattering and radiation theory and applications, design of multiband/broadband antennas and radar antennas, and optimization algorithms for electromagnetic applications.

Dr. Hwang is a Life Member of KIEES and a member of the Institute of Electronics, Information and Communication Engineers.

Youngoo Yang (Senior Member, IEEE) was born in Hamyang, South Korea, in 1969. He received the Ph.D. degree in electrical and electronic engineering from the Pohang University of Science and Technology, Pohang, South, Korea, in 2002.

From 2002 to 2005, he was with Skyworks Solutions, Inc., Newbury Park, CA, USA, where he designed power amplifiers for various cellular handsets. Since March 2005, he has been with the School of Information and Communication Engineering, Sungkyunkwan University, Suwon, South Korea,

where he is currently an Associate Professor. His research interests include power amplifier design, RF transmitters, RFIC design, integrated circuit design for RFID/USN systems, and modeling of high power amplifiers or devices.

Kang-Yoon Lee (Senior Member, IEEE) received the B.S. degree in electronic engineering, the M.S. degree in electrical engineering, and the Ph.D. degree in electronic engineering from the School of Electrical Engineering, Seoul National University, Seoul, South Korea, in 1996, 1998, and 2003, respectively. From 2003 to 2005, he was with GCT Semiconduc-

From 2003 to 2000, he was with GC1 Semiconductor, Inc., San Jose, CA, USA, where he was a Manager of the Analog Division and worked on the design of CMOS frequency synthesizer for CDMA/PCS/PDC and single-chip CMOS RF chip sets for W-CDMA,

WLAN, and PHS. From 2005 to 2011, he was with the Department of Electronics Engineering, Konkuk University, Seoul, South Korea, as an Associate Professor. Since 2012, he has been with the College of Information and Communication Engineering, Sungkyunkwan University, Suwon, South Korea, where he is currently a Professor. His research interests include implementation of power-integrated circuits, CMOS RF transceiver, analog-integrated circuits, and analog/digital mixed-mode VLSI system design.