# Loss Characterization and Modeling of Class II Multilayer Ceramic Capacitors: A Synergistic Material-Microstructure-Device Approach

Yunlei Jiang , Student Member, IEEE, Borong Hu, Member, IEEE, Yanfeng Shen, Member, IEEE, Xufu Ren, Student Member, IEEE, Steve Sandler, Member, IEEE, Stephan Hofmann, and Teng Long, Member, IEEE

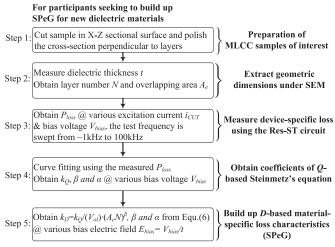

Abstract—This article motivates the loss characterization and modeling of Class II multilayer ceramic capacitors (MLCCs), which have been widely utilized owing to high energy density, in high-frequency resonant converters. In a resonant tank, MLCCs experience complex electrical operating conditions (e.g., largesignal, high-frequency, dc bias), but the incurred power loss has not been clearly characterized and modeled. This article first proposes a novel resonant-Sawyer-Tower circuit, which can experimentally extracts the loss of an MLCC in real operation in a resonant tank. A general loss modeling approach named Steinmetz's pre-electrified graph (SPeG) is then proposed to correlate capacitor's loss to the peak value of excitation, frequency, and dc bias voltage. The SpeG model provides the material-specific volume loss density of common class II dielectric materials and can be easily extrapolated to evaluate the loss of the MLCCs with different rated voltage and capacitance but employing the same dielectric material. To generalize the material-specific SPeG model to device-level application, this article also proposes an easy-to-follow tool, dielectric thickness observer (DTO), to estimate the internal microstructural geometry

Manuscript received 8 December 2022; revised 27 March 2023; accepted 16 May 2023. Date of publication 15 June 2023; date of current version 22 September 2023. This work was supported in part by the U.K. Engineering and Physical Sciences Research Council (EPSRC) under Grant EP/T02030X/1, in part by the Jardine Foundation, and in part by the Cambridge Trust. Recommended for publication by Associate Editor M. Vitelli. (*Corresponding authors: Teng Long; Borong Hu.*)

Yunlei Jiang was with the Electrical Engineering Division, Department of Engineering, University of Cambridge, CB3 0FA Cambridge, U.K. He is now with the Space Exploration Technologies Corporation, Hawthorne, CA 90230 USA (e-mail: yunlei.jiang@spacex.com).

Borong Hu, Xufu Ren, Stephan Hofmann, and Teng Long are with the Electrical Engineering Division, Department of Engineering, University of Cambridge, CB3 0FA Cambridge, U.K. (e-mail: bh529@cam.ac.uk; xr222@cam.ac.uk; sh315@cam.ac.uk; tl322@cam.ac.uk).

Yanfeng Shen is with the Danfoss Silicon Power R&D Munich, 85737 Ismaning, Germany (e-mail: ys523@cantab.ac.uk).

Steve Sandler is with Picotest, Phoenix, AZ 85085 USA (e-mail: steve@picotest.com).

To validate the effectiveness of the proposed dielectric thickness observer (DTO), this research includes a supplementary document encompassing cross-sectional scanning electron microscope (SEM) images of 9 X5R MLCC samples, along with the MATLAB script of the DTO. The provided MATLAB script empowers readers to estimate the dielectric thickness of an MLCC sample based on its *C-V* curve, showcasing remarkable concurrence with the dielectric thickness measured from the SEM images. The comparisons are presented in Table IV, V, VI, and VII, affirming the reliability and accuracy of the DTO in predicting the dielectric thickness of MLCC samples.

This article has supplementary material provided by the authors and color versions of one or more figures available at https://doi.org/10.1109/TPEL.2023.3286818.

Digital Object Identifier 10.1109/TPEL.2023.3286818

by tracking the C-V characteristic provided in product datasheet. The synergy of the proposed characterization circuit, SPeG loss model, and DTO establishes a toolkit that enables the estimation of MLCC losses in a manner similar to that of a ferromagnetic inductor/transformer core. This article is accompanied by microscope images of the investigated MLCC samples and MATLAB scripts of the proposed DTO.

*Index Terms*—Ceramic capacitor, class II, ferroelectric material, high frequency, loss modeling, resonant converter, Steinmetz's equation (SE).

### I. INTRODUCTION

APACITORS play a crucial role as key components in power electronics converters, encompassing applications, such as dc-link, filters, and resonant tanks, covering a wide frequency range from tens of Hz to mega-Hz [1]. The multilayer ceramic capacitors (MLCCs) have a compact format of alternatively sintering hundreds of thin layers (a few micrometers each) of metal electrode and ceramic dielectric. As one of the most popular high energy density capacitors, they are particularly favored in volume-sensitive designs. In comparison to class I counterparts, Class II MLCCs using BaTiO<sub>3</sub>-based ferroelectric dielectric material with a dielectric constant of 1000–10 000 have attracted more interest in applications where high power density is pursued.

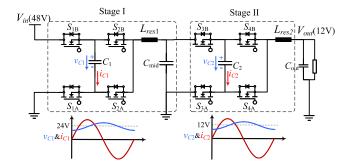

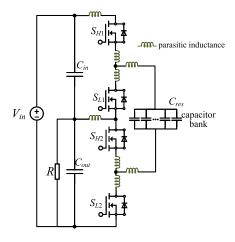

Class II MLCCs find extensive use in applications, such as filter capacitors in ac-tied systems, where they are subjected to high-amplitude excitation at relatively low frequencies [2], as well as energy transfer elements in resonant switched-capacitor converters (RSCs) [3]. For high-compact RSC applications, which are the primary focus of this work, Class II MLCC can serve as the primary energy transfer device over inductors in a series resonant tank operating at frequencies exceeding 100 kHz [3], [4], [5], as increasing the capacitance can eliminate physical inductors, resulting in a "magnetic-free" design [5] [6]. In a typical cascaded RSC, cf., Fig. 1, for instance, two high-capacitance capacitor banks, i.e.,  $C_1$  and  $C_2$ , undergo highfrequency and large-signal excitations superimposing 24 and 12 V dc bias voltage, respectively. However, the large signal equivalent series resistance (ESR) and power loss of Class II MLCCs under high-frequency and large-amplitude excitations have unfortunately not been adequately investigated.

Fig. 1. Representative application where class II capacitors are used for both resonant and input/output capacitors and are therefore exposed to large-signal, high-frequency excitation superimposed on a bias electric field: 48–12 V cascaded RSC.

Under large-signal excitations, due to the ferroelectric hysteresis of BaTiO<sub>3</sub>-based dielectric materials, Class II MLCCs yield significantly different loss characteristics or ESR compared to the values specified in datasheets, which are extracted from small-signal tests and referenced for low power applications [7]. A universal large-signal loss model of Class II MLCCs is always desired, but an accurate one is difficult to obtain, because of their low dissipation factor and nonlinear electrical hysteresis behavior, under the excitations of large amplitudes and wide-range frequencies.

Although the physics underlying the loss mechanism of Class II MLCCs is not yet fully understood, the nonlinear electrical hysteresis has been identified as the primary source of loss and the underlying cause of the discrepancy between small and largesignal losses [7], [8]. Based on the observation of large-signal charge versus voltage (Q-V) curves, such hysteresis loss has been fitted by Steinmetz's equation (SE):  $P = k_Q f^{\alpha} Q_{pk}^{\beta}$ , which relates the peak value of charge  $Q_{pk}$ , frequency f and loss P, first giving a quantitative estimation of MLCC's power loss [2], [7]. However, due to the limited frequency covered by conventional testing methods and the lack of interest in high frequency, the frequency dependence of MLCC loss has not been disclosed, resulting in the speculation that frequency exponent  $\alpha$  can be approximated to 1 and Q-V loop area is frequency-independent. In addition, the loss of Class II MLCCs was suspected to be sensitive to dc bias voltage in [9] and [10]. Such sensitivity is dependent on the manufacturers and product series but has not been fully quantified and modeled, due to the absence of an effective experimental characterization methodology. Therefore, in order to unveil the actual loss mechanism and develop a reliable analytical model for Class II MLCC, comprehensive investigations on a wide range of MLCCs involving large-signal measurement, dc voltage bias, and detailed knowledge of the internal microstructure of the MLCCs need to be accordingly conducted. This study intends to synergize characterization approaches using small and large-signal electrical measurements and material-level microscopy investigation for an accurate loss model of Class II MLCCs in RSC-oriented applications. The frequency range of interest spans from several hundred hertz to a hundred kilohertz, encompassing the simultaneous presence of dc voltage bias. The characterization and modeling process pay much attention to elucidating the power loss behavior at the

material level. The contributions of the work can be summarized as follows

- An experimental loss characterization method for ML-CCs under the coexistence of large-signal, wide-range frequency excitations and dc bias is developed based on a novel resonant-Sawyer-Tower (Res-ST) circuit. This method is also applicable to other capacitors under test (CUTs), which are sensitive to the level of excitation, such as antiferroelectric CeraLink capacitors.

- 2) The ferroelectric hysteresis behavior of four dielectric materials has been quantitatively identified with the help of a scanning electron microscope (SEM). The SEM is employed to examine the internal microstructure of commercial Class II MLCCs to obtain the equivalent plate capacitor model. The microscopic information isolates the influence from MLCCs' nickel electrodes and insulation packaging and enables a material-specific description of loss characteristics.

- 3) The proposed Steinmetz pre-electrified graph (SPeG) enables material-specific loss characterization and models the loss characteristics of dielectric materials. What sets SPeG apart is its ability to incorporate the influence of both dc bias and frequency into the loss modeling, making it the first of its kind to do so.

- 4) Applying the proposed SPeG on other MLCCs requires the internal microstructural geometry information to be known. A dielectric thickness observer (DTO) is therefore proposed, which can estimate the geometry information of an MLCC from its electrical characteristics. This method extends the applicability of the material-specific loss model (SPeG) to all the MLCC devices employing the same dielectric material, which provides users with an easy-to-follow power loss estimation route of Class II MLCC.

The rest of this article is organized as follows. Section II provides an overview of the state-of-the-art loss characterization methods for Class II MLCCs and outlines the motivation behind this work. Section III details the proposed characterization methodology based on the Res-ST circuit and presents large-signal experimental results from samples with different dielectric materials, e.g., X5R, X7R, and X7T. Section IV investigates the loss characterization at a material level, and proposes a method to estimate the geometry of MLCCs based on small-signal measurements, thereby linking material-specific information to device-specific information. Validations of the loss model on a broad range of MLCCs and a 400-W 2:1 RSC converter are presented in Section V. Finally, Section VI concludes this article.

### II. REVIEW OF CHARACTERIZATION AND MODELING OF CLASS II MLCCs

### A. Excitation Circuits for MLCC Characterization

In previously reported experimental characterizations, difficulties have been identified in terms of circuit designs, excitation sources, power loss separation [11], and operating temperature decoupling. Four typical characterization rigs in the literature

A.Power Meter B.PA Resonant Circuit Type Measurement [11] [12] mete V<sub>CUT</sub> CUT Structure Issues Limited accuracy Indirect loss extraction C.Current-source Measurement D.ST Circuit [2] Type Structure Limited test capability Non-sinusoidal excitation, for high-frequency/ Issues no Q-V curve capacitance CUTs

following the call for large-signal characterization of Class II MLCCs are summarized in Table I. Using an ac power supply and a transformer as the excitation source, as shown in Type A, is mostly applicable to low excitation frequency measurement [11]. Type B employs a radio-frequency power amplifier (PA) as the high-frequency excitation source [12], while a resonant circuit is constructed to reduce the current requirement from the PA. However, the use of the calorimetry approach for power loss extraction cannot decouple the temperature dependence of ferroelectric dielectric material. In Type C, a current-source excitation circuit consisting of a high-inductance  $L_{\text{bridge}}$  can excite the CUT with a sawtooth waveform [9], but harmonic components are naturally contained in the excitation. In addition, using a power meter to measure the power loss across the CUT in Type A [11] may compromise accuracy due to low sensitivity. All of these mentioned approaches prove to fit designated applications, where only qualitative characterization is of interest, the test frequency is low, the temperature dependence is negligible, and the exact Q-V curve is not a must.

Among these four approaches, the Sawyer-Tower (ST) circuit has been proven successful to extract the Q-V curve in Type D. This method allows for direct electric charge measurement through the reference capacitor  $(C_{REF})$  by series connecting  $C_{\rm REF}$  and CUT, thereby avoiding error-prone current measurements [13]. However, high-power PA can struggle to excite high-capacitance samples at high frequency considering the limitation in PA's current capability. For instance, driving a 10  $\mu$ F CUT at 100 kHz with 10 V peak–peak excitation requires a peak excitation current as high as 31 A, which by far exceeds the capability of most commercially available PAs. Meanwhile, the reference capacitor  $C_{REF}$  is recommended to have a much higher capacitance than that of  $C_{\mathrm{DUT}}$  in order for  $C_{\mathrm{DUT}}$  to share more voltage in the series-connected  $C_{REF}/C_{DUT}$  voltage divider [2], [14]. This, however, requires a significant number of reference capacitors when high-capacitance CUTs are of interest.

Fig. 2. Cross-section of a typical SMD MLCC overlapping structure: the dielectric material is the main body inside which a large number of overlapped electrode plates are terminated at the two ends of the body for external connections

To characterize MLCCs with a wide range of capacitances, it is necessary to develop a more flexible excitation solution that can supply high-power excitations in sinusoidal forms over a wide range of operating frequencies [15]. Furthermore, it is preferable to electrically extract the power losses of MLCCs from the charge-voltage hysteresis loop (Q-V loop), which also indicates the capacitance variation under different excitations. In this work, a Res-ST circuit is proposed accordingly to address these aforementioned challenges, as will be stated in Section III.

### B. Loss Modeling of Class II MLCCs

The hysteresis behavior of MLCC's charge against voltage (Q-V curve), which shares many similarities with the B-H hysteresis curve of magnetic materials, has been identified as the main source of power loss. Based on this ground, the correlation between peak value of charge  $(Q_{\rm pk})$  and loss  $(P_{\rm loss})$  is then noticed and fitted by SE to represent the loss of an MLCC under specific charge  $Q_{\rm pk}$  and operation frequency f in [2] as

$$P_{\text{loss}} = k_Q \cdot f^{\alpha} \cdot Q_{\text{pk}}^{\beta}. \tag{1}$$

This modeling approach has proven to be accurate by fitting different sets of loss parameters  $(\alpha,\,\beta,\,{\rm and}\,\,k_Q)$  for each MLCC, accommodating their unique loss characteristics. This feature, however, limits the generalization of this charge-based loss model due to the large number of commercially available MLCCs, even from the same manufacturers.

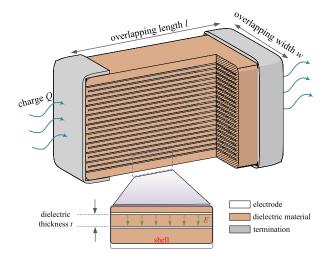

In [8], a new Steinmetz model has been proposed to address this limitation by predicting MLCC loss using a material-specific modeling approach. Fundamentally, this approach makes an assumption that the rated voltage ( $V_{\rm rated}$ ) of the MLCC is limited by the breakdown voltage of dielectric material. Therefore, the dielectric thickness t between the positive and negative electrode, as depicted in Fig. 2 where MLCC's overlapping structure is demonstrated, in any layers of a specific type of MLCC, e.g., X5R, X7R, X7T, et al., is expected to be proportional to its rated voltage ( $V_{\rm rated}$ ) specified by the

Fig. 3. Correlation between dielectric thickness (t) and rated voltages of four types of MLCCs: high voltage (rated from 100 to 630 V) MLCCs using X7R and X7T dielectric materials [see Fig. 3(a) and (b)] and low voltage (rated from 16 to 50V) MLCCs using X5R and X7R dielectric materials [see Fig. 3(c) and (d)]. The dielectric thickness is measured using SEM.

manufacturer. This assumption then enables the scaling of the measured loss from one benchmark to its peers using the same dielectric material, largely alleviating testing efforts.

This model's prediction error is under 20% when evaluating high-voltage MLCCs [8]. However, it may lose accuracy in lower voltage ranges, after surveying on 31 samples from both high-voltage and low-voltage categories. In Fig. 3, the correlation between dielectric thickness and rated voltage of four types of MLCCs are plotted by inspecting the microstructure of MLCC samples with the aid of SEM, which are detailed in Section V.

As shown in Fig. 3(a) and (b), the linear scaling claim between the dielectric thickness t and  $V_{\rm rated}$  is correct for high-voltage X7T(100-630 V) and X7R(100-630 V) MLCCs. However, such linear correlation no longer holds in Fig. 3(c) and (d) when investigating the low-voltage families (16-50 V). As can be seen, the relation between t and  $V_{\text{rated}}$  becomes irregular for low-voltage samples. Notably, the dielectric thickness of a 16 V MLCC (C2012X5R1C225K125) is higher than that of a 50 V sample (C2012X5R1H475K125) using the same dielectric material. Such outliers were previously mentioned in [16] and can be attributed to the emphasis on mechanical stiffness over energy density in low-voltage MLCCs, considering the mechanical fragility of the class II dielectric material [16], [17]. To counteract the capacitance reduction when a bias voltage is applied is another reasonable motivation to retain a dedicated thickness of the dielectric.

Meanwhile, the dependence of Steinmetz's parameters on do voltage bias deserves much attention, as Class II MLCCs are widely used in high-voltage-bias applications, such as dc-link capacitors and resonant capacitors illustrated in Fig. 1. However, there are no definitive conclusions on this topic yet. According to the experimental results of a limited number of MLCC samples, the dependence of power loss on dc bias has been ignored [2]. Opposite results have also been observed that, at a certain current level, power loss increases remarkably when a high bias voltage is applied [9]. This phenomenon, however, remains unexplained by the bias-independent ferroelectric hysteresis loss model, necessitating more accurate characterization methods and modeling tool to facilitate the loss prediction in resonant converters where the MLCCs are highly polarized.

#### C. Summary

As aforementioned, the existing characterization circuits and modeling approaches for Class II MLCCs have significant limits, preventing them from accurately capturing the actual loss profile of MLCCs, in particular, under high-frequency excitation and dc-biased applications. Furthermore, the lack of material-specific information hinders the development of a generalized loss model analogous to that of magnetic material, i.e., loss per unit volume can be derived directly from material loss parameters and applied excitations [18].

### III. EXPERIMENTAL SETUP AND LARGE-SIGNAL LOSS CHARACTERIZATION

### A. Proposed Res-ST Circuit for Large-Signal Characterization

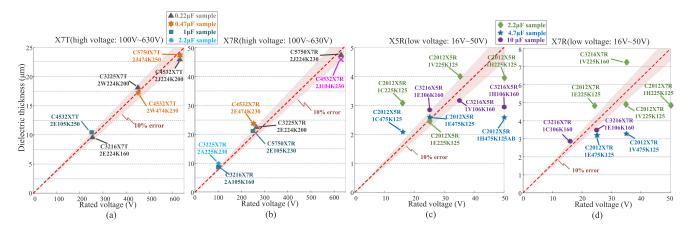

To overcome the summarized issues, this article presents a novel Res-ST circuit tailored to apply desired excitations on CUTs, representing realistic operating conditions in typical high-frequency resonant converters. As illustrated in Fig. 4(a) and (b), the test setup is developed from a 1:1 resonant switched-capacitor circuit, in which the resonant tank is reconstructed and a dc bias voltage is introduced. The upper (red) and lower (blue) switches are driven ON/OFF with complementary PWM signals. In the resonant tank, the cascaded combination of the CUT and the reference capacitor  $C_{\rm REF}$  is connected in series with the resonant inductor  $L_{\rm RES}$  to form a resonant ST circuit, which operates at a resonant frequency  $f_{\rm res}$  given by

$$f_{\rm res} = 1 / 2\pi \sqrt{L_{\rm res} \frac{C_{\rm REF} \cdot C_{\rm CUT}}{C_{\rm REF} + C_{\rm CUT}}}.$$

(2)

The testing frequency can be adjusted flexibly from hundreds of Hz to several hundred kHz by varying the value of  $L_{\rm RES}$ . The proposed Res-ST circuit behaves as a current source due to the charge balance in the periodic steady state of a switched-capacitor circuit [19]. Hence, the excitation current is bound by the load current  $i_o = V_o/R$  as  $i_{\rm RMS} = (\pi \cdot i_o)/\sqrt{2}$  at the resonant frequency, resulting in an extensive range of excitation amplitude. This feature makes it particularly suitable for the characterization of high-capacitance

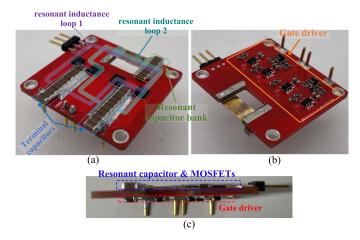

Fig. 4. Schematic of the Res-ST circuit and test setup. (a) Customized Res-ST circuit to adjust the excitation level applied on the CUT and its corresponding schematic composed of two half bridges, load and a resonant tank. (b)  $C_{\rm DUT}$ , along with the entire resonant tank, is immersed in silicon oil tank which emulates different operating temperatures. The voltage across  $C_{\rm CUT}$  and  $C_{\rm REF}$  are both measured by Kelvin sensing. (c) Experimental circuit board with integrated deskew circuit are used to calibrate voltage probes.

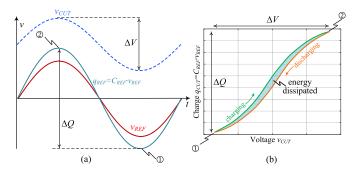

Fig. 5. Q-V loop obtained by the Res-ST circuit. (a) Obtained voltage waveforms across  $C_{\rm CUT}$  and  $C_{\rm REF}$  during one fundamental cycle. (b) Illustration of the nonlinear charge(Q)-voltage(V) curve by plotting  $v_{\rm CUT}$  against  $v_{\rm REF}$ , both obtained from (a). Circled numbers (1) and 2) denote different points of time in the measurement.

capacitors at high frequency. Moreover, dc bias voltages  $V_{\rm bias}$  can be applied to the CUT from an external power supply.

In contrast to the V-I method which is used as a common procedure for B-H loop characterization [20], this method represents essentially a V-V measurement since the charge on the CUT is reflected from the voltage across  $C_{\mathrm{REF}}$ , as shown in Fig. 5. This setup eliminates the need for current measurements which are prone to errors compared to voltage measurements, through extracting the charge of the CUT from the voltage across  $C_{\rm REF}$ . In the circuit, a bank of ten class I MLCCs (CGA8R2C0G1H224J320KA) with a capacitance of 220 nF and a low dissipation factor (smaller than  $2 \times 10^{-4}$ ) is employed as  $C_{REF}$  due to their linear relationship between voltage (v) and charge (Q). A 1 M $\Omega$  resistor is parallelled with the reference capacitor bank to tune the ratio of dc equivalent parallel resistance [2], ensuring a larger portion of the dc bias voltage would be allocated to the CUT. The voltages  $v_{\text{CREF}}$  and  $v_{\text{CUT}}$  across  $C_{\text{REF}}$  and CUT are measured individually by two differential

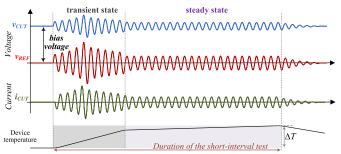

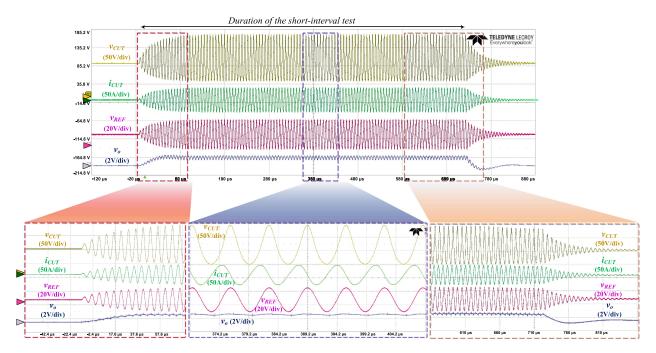

Theoretical and experimental waveforms of the Res-ST measurement circuit are given in Fig. 6 and Fig. 7, respectively, demonstrating good agreement. In Fig. 7, the part number of the CUT is C5750X7R2E105K230, of which the capacitance is 1  $\mu$ F. In experimental results, it can be seen that the CUT is biased by a 90 V dc voltage and the peak value of the excitation

Fig. 6. Illustration of theoretical current and voltage waveforms in a short interval in which the temperature rise of the CUT is subdued.

current reaches 35 A, corresponding to a peak excitation voltage of 73 V. The resonant frequency at this operation point is 156 kHz. Meanwhile, the output voltage remains at a relatively low value (<2 V), which introduces low common-mode voltage as the grounding points of voltage probes are floating. The Q-V curve of the CUT is obtained by plotting  $v_{\rm CUT}$  against  $q_{\rm CUT}=v_{\rm CREF}\cdot C_{\rm REF}$ , as shown in Fig. 5(a), and the enclosed area of the Q-V loop [cf., Fig. 5(b)] represents the power loss energy that the class II capacitor dissipates during one fundamental cycle.

### B. Temperature Control Via Short-Interval Test

Maintaining a constant ambient and capacitor temperature during measurement is essential, considering that  $BaTiO_3$  ferroelectric material is highly temperature sensitive [2]. As illustrated in Fig. 4(b), in order to maintain the ambient temperature around the capacitor at 25 °C, the entire resonant tank is placed in a temperature-controlled oil tank, immersed with Kryo 51 silicon oil, which has a high specific heat capacity of 1.63 kJ/(kg  $\cdot$  K). In this manner, the ambient temperature of the CUT is considered invariable during the measurement.

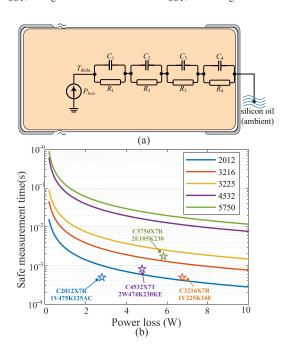

The self-heating of the CUT is avoided by implementing a short-interval measurement lasting for a few fundamental cycles at the resonant frequency, as shown in Figs 6 and 7. A tradeoff is made here, considering that a longer measurement time is beneficial in improving the signal-to-noise ratio of the measurement. The 4th-order Foster thermal network, shown in Fig. 8(a), of MLCCs with various packages, i.e., SMD 2012, 3216, 3225,

Fig. 7. Example excitation waveforms generated by the proposed Res-ST circuit in a short interval test. Key waveforms include the current waveform of the CUT:  $i_{\text{CUT}}$ , voltage waveform of the CUT:  $v_{\text{CUT}}$ , and voltage waveform of the  $C_{\text{REF}}$ :  $v_{\text{CREF}}$ . The part number of the CUT is C5750X7R2E105K230.

Fig. 8. (a) Thermal network of the MLCC, where the parameters of the structure-function [21] are extracted by FE analysis. (b) SMA for different MLCC packages of interest to determine the duration of the short-interval test.

5750, 2220, are first extracted from COMSOL finite-element (FE) simulation, to predict the transient temperature response at specific power losses. Then a safe measurement area (SMA) is defined as the boundary within which the short-interval duration should be strictly restricted under certain loss conditions. Thereby, the temperature rise would not jeopardize the accuracy of the measurement. The SMA curves, depicted in Fig. 8(b), represent the maximum allowed measurement duration with a

0.5 °C temperature rise restriction, corresponding to a 0.29% change in power loss [2]. In the FE simulation, the MLCC body is considered as a homogeneous block of the dielectric material. The heat capacity and thermal conductivity of BaTiO<sub>3</sub> are set to 434 J/(kg· K) and 2.61 W/(m· K), respectively. This setting represents a conservative estimation as the MLCC body contains a substantial amount of mass from the electrode plates made of nickel alloy, which has a much higher thermal conductivity [97.5 W/(m· K)].

### IV. LARGE SIGNAL LOSS CHARACTERIZATION OVER WIDE FREQUENCY RANGE AND DC BIAS VOLTAGE

The abovepresented Res-ST test rig and procedure enable the large-signal loss measurement of Class II MLCC samples with flexible excitation. The measurements are performed by recording the voltages across the CUT and the  $C_{\rm REF}$ , which are then mapped to the voltage (V) and charge (Q) of the CUT, respectively. In this section, the power losses of four CUTs with four different dielectric materials and rated voltages are first characterized under large-amplitude excitations and a wide range of frequencies. Then, the results from the loss measurement are used to extract the SE coefficient via curve fitting and to observe the influence of frequency and dc-bias voltage on loss behavior.

### A. Large-Signal Loss Characteristics Under Varying Frequency and DC-Bias Voltage

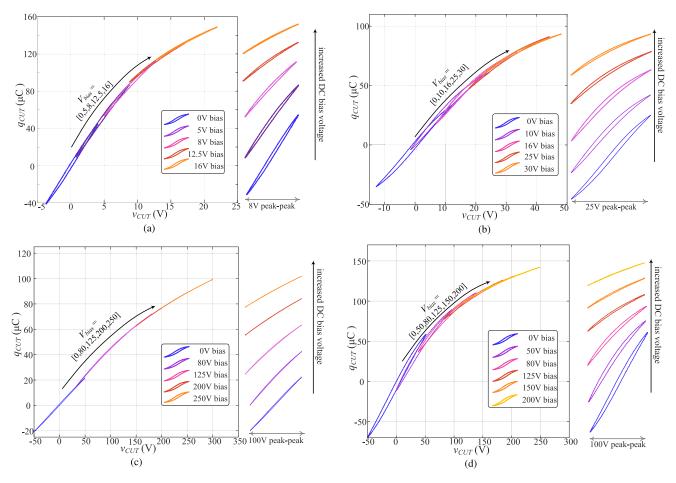

A series of hysteresis Q-V loops of four CUTs employing four dielectric materials marked as X5R-LV, X7R-LV, X7T-HV, and X7R-HV, respectively, are obtained by changing the positive dc biases supplied to the Res-ST circuit, as shown in Fig. 9. In this figure, subloops in the same plot are extracted from

Fig. 9. Measured hysteresis loops with constant voltage peak value and increasing bias voltage. *Q-V* loops of: (a) low-voltage X5R sample (C3216X5R1E106K160) under an increasing bias voltage (0, 5, 8, 12.5, and 16 V); (b) low-voltage X7R sample (C3216X7R1V225K160AE) under an increasing bias voltage (0, 10, 16, 25, and 30 V); (c) high-voltage X7T sample (C4532X7T2W474K230KE) under an increasing bias voltage (0, 50, 80, 125, 150, and 200 V); (d) high-voltage X7R sample (C5750X7R2E105K230KE) under an increasing bias voltage (0, 50, 80, 125, 150, and 200 V).

tests with fixed peak-peak voltage on CUT and similar test frequencies (74.43-83.20 kHz for X5R-LV; 95.21-116.6 kHz for X7R-LV; 43.86–62.6 kHz for X7T-HV; 120.4–183.5 kHz for X7R-HV), but different bias voltages. Thus, a combination of subloops provides a holistic hysteresis Q-V loop for each CUT. It is evident that these four samples exhibit various Q-V loop patterns, resulting in differences in large-signal loss characteristics, and the saturation of Q/V with increased dc-bias voltage leads to a decreasing capacitance. Therefore, it becomes possible to measure the MLCC loss behavior under varying dc voltage biases, excitation amplitudes, and frequencies. The large-signal losses of CUTs under each operating condition are calculated using the enclosed Q-V areas per cycle and indicated as dots, as illustrated in Fig. 10. The losses of the MLCCs under the maximum and minimum frequency are fitted by the SE function and colored in blue and red, respectively, to demonstrate the trend of power loss behavior over frequency variation.

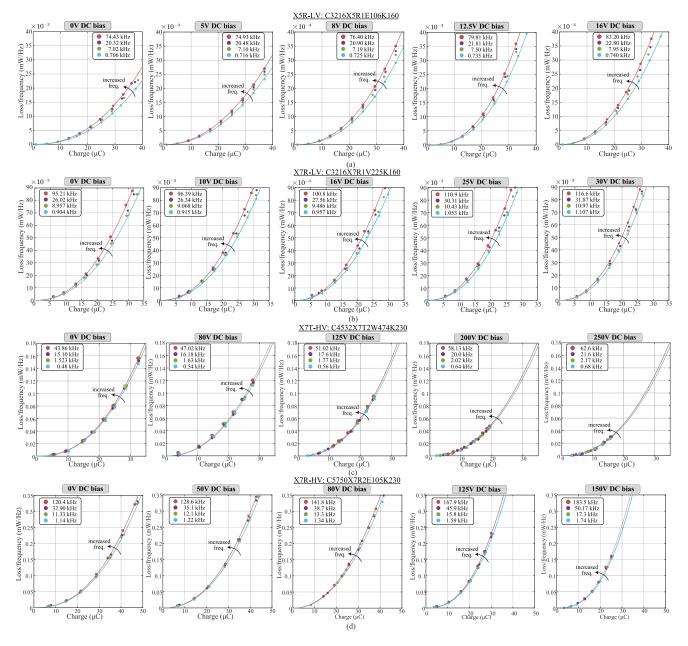

In Fig. 10, loss power/frequency, which physically represents the energy enclosed in an individual Q-V loop, of the four samples over a wide range of frequencies is plotted against charge Q, and it can be seen that different types of dielectric materials exhibit distinct dependence on frequency and bias

voltage. Specifically, the loss trend lines of the low-voltage X5R, X7R, and high-voltage X7R move upward with increased dc-bias voltage, indicating a strong positive loss sensitivity to dcbias voltage. Meanwhile, a positive correlation with frequency can be seen as well but the degree of dependency varies. The X7T-HV material, however, stands out as a special case as its dependencies on both dc-bias voltage and frequency variation are weak. At the same excitation level, i.e.,  $Q_{pk}$ , the loss changes by less than 5% when the dc-bias voltage spans from 0 to 250 V. This observation confirms the coexistence of both bias-sensitive and bias-insensitive dielectric material used in Class II MLCC. It also implies that the divergence between [2] and [9] regarding the dc-bias voltage dependence could be caused by the fact that dielectric materials with different recipes have been used but all are classified as class II by manufacturers. It should be noted that the plotted loss were measured at a certain ambient temperature (25 °C). In addition, a significant decrease in loss at higher operating temperatures, in alignment with the findings in [2], was also observed.

It is also desired to analytically describe the losses considering the impact of the dc-bias voltage. However, SE is only able to characterize hysteresis loops against different excitation

Fig. 10. Measured power loss/frequency (P/f), which physically represents energy enclosed per Q-V loop, against measured charge  $Q_{\rm pk}$  of four CUTs. (a) C3216X5R1E106K160 using LV X5R dielectric. (b) C3216X7R1V225K160AE using LV X7R dielectric. (c) C4532X7T2W474K230KE using HV X7R material. (d) C5750X7R2E105K230KE using HV X7R material. In the test, both the frequency and the applied charge  $Q_{\rm pk}$  were varied and different loss dependencies on frequency and DC-bias-voltage can be observed on these four types of dielectric materials.

amplitude. Therefore, based on the conventional SE, this article proposes an improved method where an SE coefficient graph is built up to include the dependency of Steinmetz's parameters on the bias voltage. The concept is analogous to the Steinmetz premagnetization graph introduced in [22], which is widely used for evaluating the core loss of an inductor/transformer under dc bias.

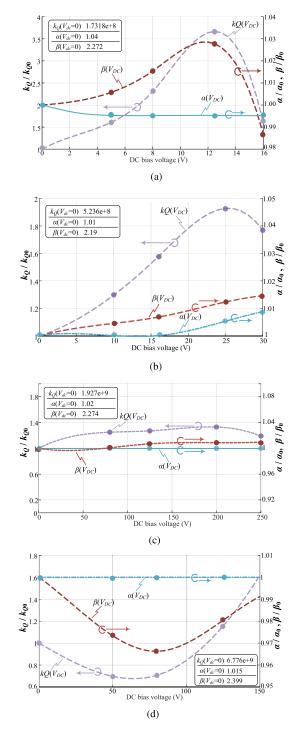

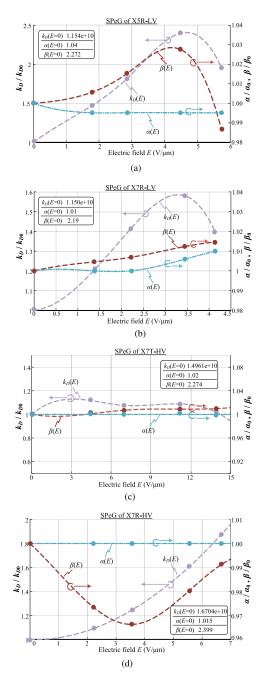

In the proposed graph,  $\alpha(V_{\rm dc})$ ,  $\beta(V_{\rm dc})$ , and  $k_Q(V_{\rm dc})$  in the SE are considered as functions of dc bias voltage  $V_{\rm dc}$ .  $\alpha_0$ ,  $\beta_0$ , and  $k_{Q0}$  are the SE coefficients to be experimentally extracted at zero bias voltage and used as reference values for normalizing  $\alpha(V_{\rm dc})$ ,  $\beta(V_{\rm dc})$ , and  $k_Q(V_{\rm dc})$ . The bias voltage is spanned from 0 to more than 60% of the rated voltage to be as inclusive as possible.

The SE coefficient graphs of four CUTs under different dc bias voltages are shown in Fig. 11. It is observed that the loss dependence on dc bias voltage varies among different dielectric materials. The frequency coefficient  $\alpha$  in the SE is not obviously influenced by  $V_{\rm dc}$ , valid on all four dielectric materials. The SE coefficients  $\beta$  and  $k_Q$  for X5R-LV, X7R-LV, and X7R-HV exhibit high sensitivity to the dc voltage, whereas X7T-HV material shows great independence from the dc bias voltage applied. The loss characteristic of the X7T-HV material changes only less than 5%, when the dc bias voltage is increased from 0 to 250 V. The corresponding coefficients in SE, i.e.,  $k_Q$  and  $\beta$ , have insignificant changes as a consequence. It should be noted that, for all CUTs, even minor changes in  $\beta(V_{\rm dc})$  can have a considerable influence on loss estimation.

Fig. 11. Changes of the coefficients in SE according to varying dc bias voltage. (a) C3216X5R1E106K160: X5R-LV. (b) C3216X7R1V225K160: X7R-LV. (c) C4532X7T2W474K230: X7T-HV. (d) C5750X7R2E105K230: X7R-HV.

To visually demonstrate the effect of dc bias voltage on various dielectric materials, Fig. 12 interprets high-frequency measurement results from Fig. 10, where power loss/frequency (P/f) is plotted against charge (Q), in terms of ESR values at various current and dc bias voltages. It is important to note that the variation in measurement frequency at different dc bias voltages shown in Fig. 10 has been normalized by the frequency coefficient  $\alpha$ . It is evident from the figure that the ESR of all four MLCC samples gradually increases with higher load

Fig. 12. ESR characteristics of four Class II MLCC samples at high frequency across various DC bias voltages: (a) C3216X5R1E106K160(@74.4 kHz), (b) C3216X7R1V225K160(@95.2 kHz), (c) C4532X7T2W474K230KE (@43.8 kHz), and (d) C5750X7R2E105K230(@120 kHz).

currents. Furthermore, an increase in dc bias voltage results in a higher ESR at the same current level for X5R-LV, X7R-LV, and X7R-HV dielectric materials. However, X7T-HV is unaffected by variations in the applied bias voltage, as its ESR remains stable. In addition, the figure displays the small-signal ESRs provided in the datasheet for each subplot. It can be observed that the discrepancy between the large-signal and small-signal ESR values is minimal at low currents, but increases significantly at higher load conditions.

### B. From Device-Specific to Material-Specific Loss

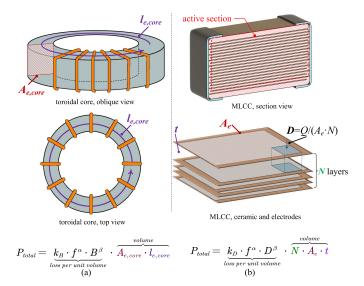

The measurement results presented previously primarily focus on device-specific parameters using the Q-V loop. Its generalization to other commercial devices, even having the same dielectric material, is limited. Nevertheless, it is worth noting that the loss mechanisms for magnetic core and MLCC dielectrics share similarities, as they both originate from the hysteresis loop, whether magnetically or electrically. Consequently, the loss modeling of MLCC can be expanded from the device level to a more fundamental material level by drawing insights from previous research conducted on magnetic components.

In the loss estimation of a magnetic component using homogeneous material, a B(flux-density)-based Steinmetz's loss equation is preferred by engineers, and material-specific loss information (loss per unit volume/weight) is usually provided for this equation by manufacturers. By incorporating knowledge of the device's geometric dimensions, the losses of the magnetic component of interest under specific excitation can be directly estimated. As depicted in Fig. 13(a), such a manner is conveniently achieved on a toroidal core power inductor as

Fig. 13. Analogy between the loss estimation of a typical toroidal core inductor and an MLCC, where (a) B-based and (b) D-based loss estimation methods are used, respectively.

both the path length  $(l_{e,core})$  and cross-section area  $(A_{e,core})$  are easy to access. As a result, with the available material-specific loss information, loss estimations can be made for all devices utilizing the same material.

With an attempt to apply this principle on an MLCC with a multilayered structure, an analogy is given in Fig. 13 to illustrate both commonalities and differences. Similar to the B-based SE, the loss of an equivalent capacitor can be alternatively represented in the form of a D-(displacement field)-based SE [8]

$$P = \rho \cdot V_{ol} = k_D \cdot f^{\alpha} \cdot D_{pk}^{\beta} \cdot V_{ol}$$

(3)

where,  $\rho$  is the loss density,  $V_{ol}$  denotes the volume of the device, and  $D=Q/(N\cdot A_e)$  represents the electric displacement field. Therefore, this D-based SE is a dielectric material-specific model and has the potential to be generalized to evaluate all devices using the same dielectric material. To achieve complete generalization, accounting for the complex MLCC structure, three parameters are necessary: layer number (N) and overlapping area  $(A_e)$  of each layer to derive the D, and in addition dielectric thickness (t) for calculating the volume. These three parameters are correlated by:  $C_{\rm rated} = \varepsilon_0 \frac{A_e \cdot N}{t}$  where  $C_{\rm rated}$  is the nominal capacitance and  $\varepsilon_0$  is the dielectric constant.

As  $C_{\rm rated}$  is readily accessible from the datasheet and  $\varepsilon_0$  is a device-invariant material property, knowing the value of t allows us to determine  $A_e \cdot N$ . Consequently, the three geometric parameters  $(N, A_e, \text{ and } t)$  can be gradually decoupled. The exact value of t, however, now stands out as the only unknown quantity, which is unfortunately rarely published by manufacturers. Using the rated voltage to speculate t is not physically supported by the survey in Fig. 3, particularly for low-voltage families. Meanwhile, although it is possible to conduct cross-section analysis on specific samples, repeating this equipment-intensive process for every single device is rather unrealistic given the vast number of MLCCs available on the market. Therefore, it is imperative to employ an efficient yet simple analysis to extract internal

Fig. 14. Process for establishing the loss characteristic of new ferroelectric dielectric material.

geometry information, i.e., N, t, and  $A_e$ . These parameters will facilitate the normalization of Q-based SE coefficients to their D-based counterparts, effectively extending the device-specific loss model to a material-specific format.

To demonstrate how the material-specific loss information will be built in the following section, a flow chart outlining the entire process of describing the loss characteristics of dielectric material is given in Fig. 14.

### V. DTO BRIDGING SMALL-SIGNAL AND LARGE-SIGNAL MEASUREMENT

Accordingly, this article presents a method to disclose dielectric thickness (t) by using SEM, and such destructive analysis is only required to be conducted once on one of the devices using the same dielectric material. Then, an easy-to-follow tool, DTO, is also introduced in this section to allow users to speculate t effectively without the need for further microstructural observation.

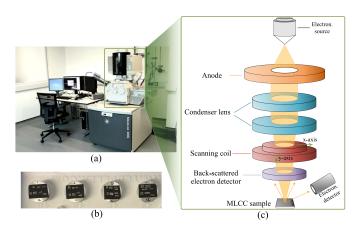

### A. Working Principle of SEM and Preparation of Samples

The SEM is a type of electron microscope, which generates images by scanning the surface with a focused beam of accelerated electrons. The emitted electrons interact with atoms in the sample, and those back-scattered electrons are collected to produce images. Compared to an optical microscope, the SEM is featured by high resolution, greater depth of field and the ability to different materials with similar optic characteristics, such as ceramics used for shell and dielectric in an MLCC. These features make SEM ideal for characterizing both magnetic [23] and dielectric components with delicate and complex structures.

The working mechanism of SEM requires careful sample preparation before scanning. MLCCs are manufactured by the co-firing of ceramic and nickel layers. While the nickel electrodes have high conductivity, that of the dielectric material is usually poor. The no-conductive dielectric material collects charge when scanned by the electron beams, and this phenomenon, also known as charge accumulation, causes scanning faults and image artifacts. To prevent charge accumulation, the

Fig. 15. (a) Magellan 400 SEM used to image the microstructure of MLCC samples. (b) Prepared MLCC samples which are mounted on a grounded aluminum holder. (c) Simplified schematic diagram of SEM.

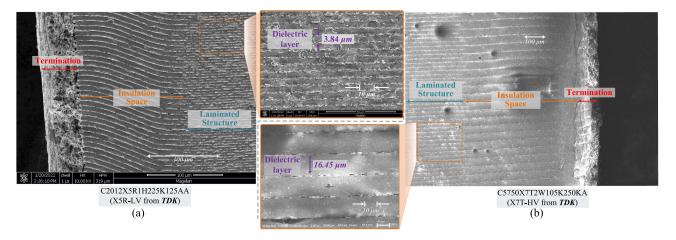

prepared MLCC samples should be mounted on electrically grounded metal plates through a thin layer of carbon adhesive tapes, as illustrated in Fig. 15(b). The MLCC samples are cut in the X-Z sectional surface to access t,N, and overlapping length. In Fig. 16, SEM images on both high-voltage and low-voltage samples are given. As can be seen, proper preparation ensures high image resolution, and geometric information of the samples is easily accessible. Additional SEM images of CUTs are provided in the supplemental document.

### B. Proposed DTO Bridging Small-Signal and Large-Signal Measurements

The dielectric thickness t of an MLCC is essential in making use of the material-specific loss information to estimate the loss of a certain device. The SEM is advantageous in capturing MLCC's geometrical parameters with ultrahigh accuracy. However, its limited availability hinder the popularization of such a loss model. In order to address this issue, we propose a new method, DTO, to estimate the dielectric thickness of MLCCs using their small-signal C-V characteristic, which is usually accessible from the product datasheet.

Due to its inherent nonlinear nature [24], the ferroelectric material's dielectric constant  $\varepsilon$  is highly sensitive to the dc electric field E applied. Notably, a strong negative correlation can be seen in BaTiO<sub>3</sub>-based dielectric material, and such dependence has been referred to as a  $\varepsilon$ -E dependence. This standalone material property is independent of the MLCC package [25], e.g., layer number N and active area  $A_e$  of each layer. Meanwhile, the electric filed E will be determined by both internal dielectric thickness t and applied dc-bias voltage externally. When the dielectric material is packaged into a MLCC, the  $\varepsilon$ -E dependence is manifested in the form of capacitance-dc-bias-voltage (C-V) dependence, which is readily available from the dc bias characteristic in the manufacturer's datasheet.

The  $\varepsilon$ -E and C-V characteristics are correlated by:  $C=\varepsilon\cdot\frac{A_\varepsilon N}{t}$  and  $V=E\cdot t$ , respectively. Therefore, if the  $\varepsilon$ -E dependence of a certain dielectric material, e.g., X5R, X7R, or X7T, is known, it can serve as a reference to speculate the dielectric thickness of counterparts using the same material

without conducting destructive cross-section analysis, given that the C-V characteristics have been known.

Fig. 17 illustrates the flowchart of the proposed DTO. Initially, the C-V characteristic of the CUT is acquired either from the datasheet or through small-signal measurements using a vector network analyzer (VNA). Subsequently, the  $C(V_{dc})$ - $V_{dc}$  curve is normalized to the  $C(V_{\rm dc})/C_0$ - $V_{\rm dc}$  characteristic of the CUT by substituting  $C(V_{dc})$  with  $C(V_{dc})/C_0$ , which ranges from 0 to 1. Here,  $C_0$  represents the capacitance of the CUT at zero bias voltage and  $C(V_{dc})/C_0$  denotes the normalized effective capacitance at bias voltage  $V_{dc}$ . Since capacitance C is given by  $\varepsilon \cdot \frac{A_e N}{t}$ , the normalization process cancels out the influence of  $A_e$ , N, and t as they are independent of E field applied, thus retaining the effect of relative permittivity  $\varepsilon$  only. In the next step, an initial value of the estimated dielectric thickness t is used to convert the bias voltage  $V_{\rm dc}$  into the corresponding bias electric field  $E_{dc}$  via  $E_{dc} = V_{dc}/\hat{t}$ . Subsequently, the  $C(V_{dc})/C_0 - V$ characteristic is transformed into  $C(\widehat{E}_{dc})/C_0 - \widehat{E}_{dc}$ , and then into  $\varepsilon(E_{

m dc})/\varepsilon_0 - \widehat{E_{

m dc}}$  characteristic, representing the normalized effective dielectric constant under various electric fileds. Importantly, since the capacitance  $C(V_{dc})$  has been normalized to  $C(E_{\rm dc})/C_0$ , the  $\varepsilon/\varepsilon_0$  can be directly obtained in this step as it holds the same value as  $C/C_0$ , under the same electric field.

With a proper estimation of dielectric thickness  $\widehat{t}$ , the estimated  $\widehat{\varepsilon(E_{dc})}/\varepsilon_0$ - $\widehat{E_{dc}}$  characteristic should exhibit the same shape as the true one of the dielectric material, and the relative distance between the estimated  $\varepsilon/\varepsilon_0$ - $\widehat{E}$  curve and the preknown true one, which is package independent, is expected to be zero. Therefore, an error function is defined to describe the distance between these two curves

error =

$$\sum_{k=1}^{N_{C-V}} \left[ f_{\varepsilon,E} \left( \widehat{E_k} \right) - \frac{\varepsilon_k}{\varepsilon_0} \right]^2$$

(4)

where,  $f_{\varepsilon,E}$  is a preknown analytical function describing the  $\varepsilon/\varepsilon_0$ -E dependence of the material,  $\widehat{E}_k$  and  $\frac{\varepsilon_k}{\varepsilon_0}$  is a pair of estimated electric field strength and normalized effective permittivity at this certain electric field strength, both obtained from the previous step, and  $N_{C-V}$  is the number of data points in the C-V curve provided in the datasheet. The estimation error is then fed to an optimizer and converges to the  $\widehat{t}$  with the least error after iterations.

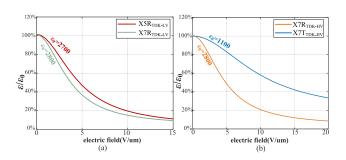

In order to implement the proposed DTO, the  $\varepsilon\text{-}E$  characteristic of multiple dielectric materials from TDK has been extracted and presented in Fig. 18. These  $\varepsilon\text{-}E$  characteristics are captured by normalizing a cluster of C-V coordinates from datasheet, after knowing all the necessary geometrical information of the internal structure, i.e., t, N, and  $A_{\varepsilon}$ . To analytically describe the dependence of  $\varepsilon$  on electric field strength E, a modified Johnson's formula, which is first unveiled in [26], is used to achieve such a purpose

$$\varepsilon(E) = \varepsilon_0 \left( \varepsilon_{00} + \frac{1}{\gamma + \delta E^2} \right) \tag{5}$$

where,  $\varepsilon_{00}$ ,  $\gamma$ , and  $\delta$  are characteristic constants of each material.  $\varepsilon_0$  is the dielectric constant at zero bias electric field strength. All the parameters in Johnson's formula of the four dielectric materials investigated have been listed in Table II.

Fig. 16. Cross-sectional SEM images of two typical MLCC samples. (a) Low-voltage X5R sample (C2012X5R1H225K125AA). (b) High-voltage X7T sample (C5750X7T2W105K250KA) from TDK.

Fig. 17. Working flow of the proposed DTO: C-V characteristic is fed as input to the DTO and estimated dielectric thickness is yielded as the output.

Fig. 18. Comparison of the  $\varepsilon$ -E characteristics of four types of dielectric materials from TDK. (a) LV X5R and LV X7R used in low-voltage MLCCs. (b) HV X7R and HV X7T used in high-voltage MLCCs.

TABLE II

PARAMETERS OF DIELECTRIC MATERIALS INVESTIGATED FITTED BY

JOHNSON'S FORMULA [26]

| parameters<br>Material | γ     | δ                      | $\varepsilon_{00}$ | $\varepsilon_0$ |

|------------------------|-------|------------------------|--------------------|-----------------|

| X5R-LV                 | 1.015 | $5.019 \times 10^{-2}$ | 0.0303             | 2700            |

| X7R-LV                 | 1.029 | $7.439 \times 10^{-2}$ | 0.0417             | 2800            |

| X7T-HV                 | 1.209 | $1.243 \times 10^{-2}$ | 0.1726             | 1100            |

| X7R-HV                 | 1.032 | $4.920 \times 10^{-2}$ | 0.0618             | 2800            |

Fig. 19. Small-signal capacitance measurement with the presence of DC bias voltage using one-port  $(S_{11})$  measurement. Short, load, and open calibration objects are needed to ensure accuracy.

The DTO relies on small-signal C-V characteristics of the MLCC as input data. These characteristics can be obtained either from the manufacturer's datasheet or by performing a one-port  $(S_{11})$  measurement, as illustrated in Fig. 19. The datasheet provides a set of discrete [C,V] coordinates describing the voltage-dependence of the sample. However, if the density of coordinates is limited or the information is not provided at all, a VNA and a DC bias injector (e.g., Picotest-J2130 A) can be used to perform a one-port S-parameter  $(S_{11})$  measurement with a bias voltage. The calibration and measurement procedures for the  $S_{11}$  measurement are detailed in [27] and [28]. The performance of the DTO fed by [C,V] coordinates obtained from a VNA is evaluated in the supplementary material of this work, and

the comparison between DTOs using VNA and datasheet [C,V] information is presented in Table IV, demonstrating similar results and good estimation accuracy. It should be emphasized that the  $S_{11}$  measurement is based on the output voltage ratio of Port 1 to the voltage input of Port 1. Therefore, the injected dc bias should not alter the essence of a one-port measurement.

### C. Performance of the Proposed DTO

To be more generic, capacitors were selected to encompass a vast range of package sizes, rated dc voltage, and capacitance. 31 samples from four types of dielectric materials were used as test datasets in this article. The cross section of these samples was firstly imaged under SEM to extract their t. Then, their C-V curves were fed to the proposed DTO to generate their corresponding  $\hat{t}$ . A comparison between the estimated  $\hat{t}$  and the measured t is given in Appendix Table IV, V, VI, and VII. According to the comparison, the DTO is able to achieve a high estimation accuracy with mean errors of 2.1%, 1.975%, 2.65%, and 3.31% for X5R-LV, X7R-LV, X7R-HV, and X7T-HV materials, respectively. The MATLAB scripts of the DTO have been included as part of the supplemental material for the manuscript.

### D. SpeG Describing Material-Specific Loss Information

Knowing both the device-specific loss and corresponding geometric information unblocks normalizing the loss information at material level, i.e., the power loss per volume of a certain ferroelectric material under arbitrary excitation. The conversion from device-specific SE coefficients to material-specific ones has been given in [2] and the process is simplified here as

$$P = \overbrace{k_Q \cdot f^{\alpha} \cdot Q_{\text{pk}}^{\beta}}^{\text{loss per device}} = \underbrace{k_D \cdot f^{\alpha} \cdot D_{\text{pk}}^{\beta}}_{\text{loss per volume}} \cdot \underbrace{V_{ol}}_{\text{volume}}$$

$$\xrightarrow{Q = A_e \cdot N \cdot D} k_D = \frac{k_Q}{V_{ol}} \left(\frac{Q_{\text{pk}}}{D_{\text{pk}}}\right)^{\beta} = \frac{k_Q}{V_{ol}} (A_e \cdot N)^{\beta} \quad (6)$$

where,  $k_Q$  and  $k_D$  are the first coefficients in the device-specific and material-specific SEs, respectively. Note that the coefficients  $\alpha$  and  $\beta$  remain the same in both device- and material-specific SEs. Subsequently, the distributions of device-specific coefficients in the SE equation given in Fig. 11 have been converted to their material-specific counterparts, as shown in Fig. 20. Since the dielectric thickness has been known, Fig. 20 is able to reflect the variation of SE coefficients at different electric (E) fields, and this method is therefore referred as SPeG.

The SpeG quantifies the frequency and electric (*E*) field dependence of a specific material used for MLCC. Whenever the geometrical information of a certain MLCC is known, either from a destructive cross-section analysis or a nondestructive DTO, the SpeG enables the generation of power loss information for the MLCC device.

### VI. DEVICE-LEVEL VALIDATION AND LOSS ESTIMATION FOR A TYPICAL RESONANT CONVERTER

In this section, the proposed loss model is validated at both the device and converter levels. The device-level validation

Fig. 20. SPeGs, which describe the effect of DC electric field bias on dielectric loss behavior, of four different materials: (a) X5R-LV, (b) X7R-LV, (c) X7T-HV, and (d) X7R-HV, all from TDK.

examines the accuracy of the proposed SPeG when used in conjunction with the DTO, whereas the converter-level validation predicts the power loss of MLCCs in a practical resonant converter.

### A. Device-Level Validation

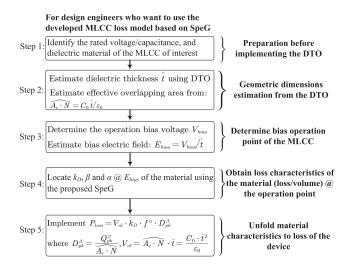

To summarize the loss estimation process using the proposed model, Fig. 21 provides an easy-to-follow guideline for users interested in directly implementing the proposed SPeG and DTO described in this article. Following this flow chart, one is expected to identify the dielectric material used in the device of interest and then extract its geometric information using

Fig. 21. Process for design engineers to calculate the MLCC loss by using material-specific parameters (SPeG).

the proposed DTO. The corresponding material-specific loss characteristics depicted in SpeG, combined with the geometric information, will finally provide the loss per unit volume and then the loss of the entire MLCC.

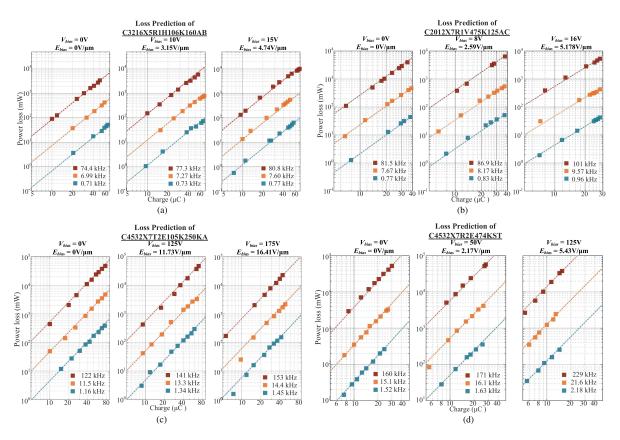

For the device-level validation, one device from each material category (X5R-LV, X7R-LV, X7T-HV, and X7R-HV) was selected. For fair validation, these validation samples were deliberately selected to be of both different packages and capacitances from those used to develop the SPeGs. Their dielectric thickness t was firstly obtained from the DTO. Then, the SPeG was used to unfold the material-specific loss information, following the flow given in Fig. 21. The obtained material-specific SE coefficients from SPeG then enable the loss estimation at various operation frequencies and dc bias voltages.

We take C3216X5R1H106K160AB, whose loss prediction results will be given in Fig. 22(a), as an example to provide a step-by-step process of loss prediction.

Step1. Preparation: The first step involves identifying the dielectric material and rated capacitance of the sample. In this case, the material is X5R-LV. The  $\varepsilon$ -E and loss characteristics of the material can be found in Fig. 18 and Fig. 20(a), respectively. The rated capacitance is 10  $\mu$ F for C3216X5R1H106K160AB.

Step2. Geometric dimension estimation: Next, the dielectric thickness t and total overlapping area  $A_e \cdot N$  of C3216X5R1H106K160AB are estimated using the proposed DTO, as detailed in Fig. 17, along with the accompanying MATLAB script in the supplemental material. The estimated dielectric thickness  $\hat{t}$  and overlapping area  $\widehat{A_e \cdot N}$  of the sample are 3.16  $\mu$ m and  $1.3 \times 10^{-3}$ mm<sup>2</sup>, respectively, as given in Table IV.

Step3. Determine operation point: The SPeG requires knowledge of the bias electric field. Thus, the corresponding bias electric field  $E_{\rm bias}$  is deduced from  $E_{\rm bias} = V_{\rm bias}/\hat{t}$ , where  $\hat{t}$  has been estimated as 3.16  $\mu$ m. In Fig. 22(a), the loss behavior under three bias voltages (0, 10, and 15 V) is investigated, and the corresponding  $E_{\rm bias}$  values are 0, 3.15, and 4.74 V/ $\mu$ m, respectively.

TABLE III

SPECIFICATION AND MAIN COMPONENT LIST OF THE PROTOTYPE

| Component                                          | Manufacturer, part number      | Parameters                 |

|----------------------------------------------------|--------------------------------|----------------------------|

| 40 V mosfet                                        | Infineon,<br>IQE013N04LM6ATMA1 | 40 V, 1.35 mΩ              |

| $C_{\rm in}$ and $C_{\rm out}$ terminal capacitors | TDK, C3216X5R1V106K160         | 50 V, $10 \mu F \times 14$ |

| C <sub>res</sub> resonant capacitors               | TDK, C3216X5R1V106K160         | 50 V, $10 \mu F \times 7$  |

| Switching frequency                                | N/A                            | 220 kHz                    |

| Resonant inductor                                  | parasitic inductance, air core | 21 nH                      |

| Gate driver                                        | Infineon 1EDN7550U             | SOT23-6                    |

Step4. Locate Steinmetz's coefficients in SPeG: Once the operation point, i.e.,  $E_{\text{bias}}$ , of the sample is known, the Steinmetz's coefficients, which represent the material-specific loss information and are functions of  $E_{\text{bias}}$ , can be located in the graphs illustrated in Fig. 20(a).

Step 5. Generate device's loss: Finally, substituting the Steinmetz's coefficients (i.e.,  $\alpha$ ,  $\beta$ , and  $k_D$ ) of the X5R-LV material, provided in Step 4, and the geometric dimensions extracted in Step 2 into (6) yields the loss of C3216X5R1H106K160AB under various bias voltages and excitation levels.

The same Res-ST circuit was employed to measure the losses of the validation samples. A comparison between the estimated and measured losses was conducted both w/ and w/o dc bias voltage. In Fig. 22, the measured losses are scattered against the peak value of the charge, and the calculated power losses are plotted as a cluster of dotted lines. As can be seen, the estimated losses match with the measured losses with high accuracy across various excitations and dc bias voltages, with only a few exceptions at low excitation levels, which can be attributed to measurement error.

Unlike the estimation of core losses, which is largely affected by the size and geometry of the core due to uneven magnetic flux distribution, that of a Class II MLCC shows low sensitivity to the device package. This feature can be attributed to the fact that it is easier to ensure an even distribution of D-field in an MLCC than B-field in a magnetic core, as long as dielectric thickness t remains uniform within one device and is significantly smaller than the electrode dimensions at the transverse plane, which is always the case for MLCCs.

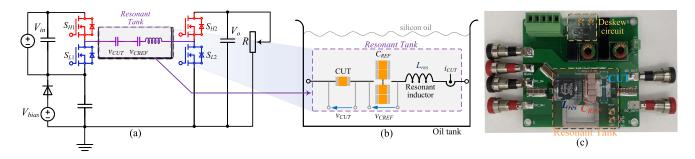

#### B. Example of Loss Estimation for RSC Converters

A 2:1 RSC was built to apply the proposed loss model for Class II MLCCs on a real converter, and the specifications and main components of the prototype are given in Table III. The prototype, of which the equivalent circuit is given in Fig. 23, utilizes the parasitic inductance of the PCB as the resonant inductor in the resonant tank, and serves as the basic building block within a larger architecture, e.g., the first/second stage in a cascaded 48 V-24 V-12 V structure or the fundamental units in an N:1 converter, and is therefore selected due to its representativeness. Operation principles of an RSC has been extensively described in pieces of literature [29], [30]. The accuracy of the loss model can be examined by comparing the calculated and measured power losses.

Fig. 22. Logarithmic representation of measured power loss against peak–peak charge  $Q_{\rm pk}$  with an increased DC bias voltage of four MLCC samples using different dielectric materials: (a) C3216X5R1H106K160AB, (b) C2012X7R1V475K125AC, (c) C4532X7T2E105K250KA, and (d) C4532X7R2E474KST. Squares represent the measurement results and dotted lines denote the calculated power losses using the material-specific SE coefficients obtained from the SPeGs given in Fig. 20.

Fig. 23. Equivalent circuit of the "magnetic-free" 2:1 resonant switch-capacitor converter.

As the resonant tank is in series with two MOSFETs at any moment, it is more intuitive to calculate the power loss using ESR instead of a *Q*-based loss model, with a conversion derived in [31]. Therefore, the charge-based loss model is converted to an ESR with the following derivation in the first step:

$$P_{\rm loss} = k_Q \cdot f^{\alpha} \cdot Q_{\rm pk}^{\beta} = k_Q \cdot f^{\alpha} \cdot \left(\frac{\sqrt{2}i_{\rm rms}}{2\pi f}\right)^{\beta}$$

Fig. 24. Hardware prototype of the "magnetic-free" 2:1 switched resonant-capacitor converter. Annotated photograph of: (a) the top layer where the parasitic inductance loops are denoted; (b) the bottom layer of the printed circuit board, and (c) the sectional view of the prototype.

$$= k_Q \cdot f^{\alpha - \beta} \cdot \left(\frac{1}{\sqrt{2}\pi}\right)^{\beta} \cdot (i_{\text{rms}})^{\beta}$$

$$\Longrightarrow R_{\text{ESR}} = P_{\text{loss}} / (i_{\text{rms}})^2 = \frac{k_Q}{\left(\sqrt{2}\pi\right)^{\beta}} \cdot f^{\alpha - \beta} \cdot (i_{\text{rms}})^{\beta - 2} . \tag{7}$$

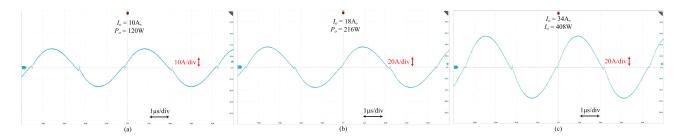

Fig. 25. Current waveforms through the resonant tank at various load conditions. (a)  $I_o = 10$  A. (b)  $I_o = 18$  A. (c)  $I_o = 34$  A.

Fig. 26. (a) Comparison between measured and estimated efficiency curves. (b) Loss breakdown of the prototype at four different load conditions.

According to the expression of  $R_{\rm ESR}$ , the ESR of the MLCC is a function of current  $i_{\rm rms}$ , and it is expected to see an increased ESR with higher current, as  $\beta$  is always slightly higher than 2.

The RSC experiences four types of power losses, namely semiconductor loss (which includes gate charge loss), inductor loss, stray loss (mainly composed of PCB trace loss), and capacitor loss. In this particular RSC prototype, the resonant frequency has been meticulously adjusted to ensure zero current switching (ZCS) throughout the entire load range, as illustrated in Fig. 25. This means that the estimation of semiconductor switching loss can be reduced to calculating the junction capacitance ( $C_{\rm oss}$ )-related loss and gate driver loss. To avoid inaccurate loss estimation of discrete inductors with ferrite cores, parasitic inductances from device packages and PCB traces are

utilized as the resonant inductor. This ensures that the only component exhibiting hysteresis behavior in the resonant tank is the MLCCs. The resonant tank has been designed with balanced loop inductance, as evidenced by the two highlighted loops in Fig. 24(a), and the actual operating current waveforms presented in Fig. 25. Consequently, the inductor loss and PCB ohmic trace loss are merged. The PCB trace resistance was determined through Ansys Q3D at the switching frequency.

Note that the terminal (input/output) capacitance of the prototype is only twice the resonant capacitance, which seemingly violates the practice that terminal capacitance should be considerably higher in an RSC converter. As a result, both  $C_{\rm in}$  and  $C_{\rm out}$  are involved in the resonant behavior [32], and their impact should be included by calculating their losses separately. Considering all these measures, the total power loss of the converter is expressed as

$$\begin{split} P_{\text{tot.}} &= 2 \cdot i_{\text{rms}}^2 \cdot R_{ds,\text{on}} + R_{\text{PCB}} \cdot i_{\text{rms}}^2 + 4Q_{\text{oss}} V_o f_{\text{sw}} \\ &+ \frac{R_{\text{ESR}}(\frac{i_{\text{rms}}}{N_{\text{res}}})}{N_{\text{res}}} \cdot i_{\text{rms}}^2 + \frac{R_{\text{ESR}}(\frac{i_{\text{rms}}}{N_{\text{term.}}})}{N_{\text{terms}}} \cdot i_{\text{rms}}^2 \end{split} \tag{8}$$

where,  $R_{ds, \rm on}$  is the on-state channel resistance of the MOSFET used,  $R_{\rm PCB}$  is the PCB trace resistance, and  $f_{\rm sw}$  is the switching frequency.  $Q_{\rm oss}$  represents the energy-equivalent junction charge of the MOSFET.  $N_{\rm res}$  and  $N_{\rm term.}$  are the number of paralleled capacitors in resonant tank and terminals, respectively. The RMS current flowing through the resonant tank is bound by

$$i_{\rm rms} = \frac{\pi}{2\sqrt{2}} \cdot I_0. \tag{9}$$

In the experiment, the converter was immersed in a silicon oil tank with a circulating pump to stabilize the ambient temperature of the CUTs. The load current was then swept from 2 to 36 A, and the readings from a Yokogawa WT5000 power analyzer were used to plot the efficiency curve.

It should be noted that all SE coefficients used in equations (7) and (8) are dependent on the bias voltage, as demonstrated in Fig. 20. The C3216X5R1V106K160 MLCC was used in the RSC converter, and its dielectric thickness *t* has been extracted by the DTO and is listed in Table IV. Feeding (7), where the ESR of C3216X5R1V106K160 is depicted, to (8) will generate the total loss of the RSC converter at various load conditions. Fig. 26 then plots the efficiency curves and illustrates a satisfying consistency between the calculated and measured efficiencies. This consistency demonstrates the accuracy and effectiveness of

the proposed loss model in real converter applications. However, relying on the ESR from the datasheet can lead to a significant underestimation of Class II MLCC power loss.

Furthermore, Fig. 26 also provides a breakdown of the converter loss at four different load conditions. As shown, the contribution from MLCC loss is negligible at light load but increases to 21% of the total loss at maximum power, which is a substantial amount of loss compared to MOSFET's ohmic loss. In summary, the proposed loss model has been validated at both the device and converter levels. Device-level validation confirmed that the model accurately estimates the losses of ML-CCs with different materials, packages, capacitances, and bias voltages. Converter-level validation demonstrated the accuracy of the model in predicting the power losses of ML-CCs in a resonant converter. These results validate the effectiveness of the proposed model, and provide a reliable tool for engineers to optimize power converter design by predicting the losses of MLCCs.

### VII. CONCLUSION

This article presents a novel methodology for characterizing and modeling the loss behavior of Class II MLCCs, specifically focusing on the influence of high frequencies (>100 kHz) and dc bias voltage. The proposed methodology aims to offer a simple yet accurate toolkit for loss estimation in Class II MLCCs. It consists of several key components: A Res-ST testing circuit that functions as the excitation and characterization circuit, a microscope investigation that builds up material-specific loss information, an SPeG derived from the analogy between magnetic and dielectric material material to generalize the material-level information to devices, and a DTO that estimates the internal microstructural geometry with minimal destructive analysis, thus extending the SPeG to all devices utilizing the same material.

The primary contribution of this work is an accurate reveal of the influence of various intertwined factors, such as frequency, excitation level, and dc bias, on the loss behavior of ferroelectric dielectric materials. In addition, our experimental results uncover the coexistence of both bias-sensitive, where loss increases with higher bias voltage, and bias-insensitive class II dielectric materials. This finding resolves the conflicts present in previous literature [2], [9].

The accuracy of the proposed loss model has been validated on devices using various materials, and an illustrative example has been provided to demonstrate the implementation of the loss model on an actual resonant converter. It is anticipated that these developed loss characterization and modeling techniques will facilitate the estimation of losses in Class II MLCCs, making it as straightforward as estimating losses in common magnetic devices.

#### **APPENDIX**

Understanding and mitigating measurement error is a crucial step to ensure the accuracy and validity of the loss characterization circuit. This appendix describes the procedures for deskewing and calibrating the proposed Res-ST circuit. In addition, it

Fig. 27. Schematic of calibration circuit for the proposed Res-ST circuit.

presents the estimation performance of the proposed DTO on different types of dielectric materials.

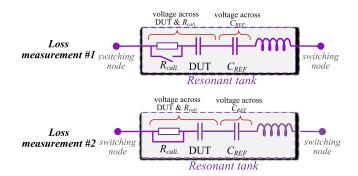

### A. Calibration of the Proposed Res-ST Circuit

To calibrate the accuracy of the test setup, we developed an electrical calibration method called differential power calibration. In this method, a shunt resistor ( $R_{\rm cali.}$ ) is placed in close proximity to the CUT, and two identical measurements are conducted sequentially, as shown in Fig. 27, with the only difference being the inclusion of the shunt resistor. By subtracting the loss obtained in measurement #2 from that obtained in measurement #1, and converting the differential power back to the ESR, the resulting ESR should match the nominal resistance of  $R_{\rm cali.}$ . The difference between ESR calculated using the differential power and the nominal resistance of  $R_{\rm cali.}$  serves as an index of the accuracy of the measurement setup.

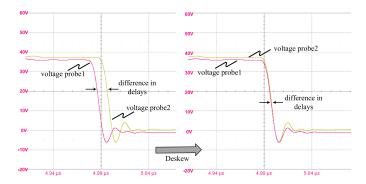

### B. Deskew of Differential Probes

- 1) Deskew via high steepness voltage edge: The Res-ST circuit's current-source driving capability comes with a floating test ground, which may introduce measurement inaccuracies. To address this, multiple measures have been implemented. As seen in Fig. 4(c), the measurement board is integrated with a half-bridge with a low loop inductance design, resulting in a high dv/dt voltage edge. Prior to the test, two differential probes with the same model (HVD3106A) are both connected across the switching node and the ground of the half-bridge to calibrate and compensate for the delay time in the oscilloscope. The adjustment process for the delay time of two probes, which aims to ensure proper alignment, has been depicted in Fig. 28.

- 2) Suppression of common-mode (CM) noise: The Res-ST is a measurement circuit that utilizes differential voltage probes in a floating-ground configuration. In this context, it is important to consider the effects of the alternating CM voltage that may impact the accuracy of the measurements. Among the various components of the CM voltage seen from the differential probe, the fast slew rate (dv/dt) of voltage at the switching node is of particular concern due to the high frequency components contained in the switching voltage transient. This can be problematic since it falls within the low common-mode rejection ratio range of the

Fig. 28. Waveforms of the voltage probes before deskew (left) and after deskew (right).

probe. However, in the test circuit, the output voltage  $(V_o)$ , which determines the amplitude of the dv/dt transients, is set to a low value (<2 V in all measurements in this work) due to the current-source nature of the driving circuit. In addition, since both half-bridges operate in ZCS, the dv/dt from the switching edge is considerably low (<0.4 V/ns). These measures help mitigate potential high-frequency CM noise from the source.

Fig. 7 shows the experimental waveforms, which demonstrate that the output voltage consistently maintains a low value ( $<\!2\,\mathrm{V}$ ) throughout the measurement process, ensuring that the amplitude of the high-frequency CM voltage is low. For benchmarking purposes, a pair of optically isolated probes with high CM noise immunity, IsoVu: TIVH08 from Tektronix, were used, and no differences were observed in the power loss results. However, as one of the motivations of this work is to develop a cost-effective test solution, the conventional HVD3106 A differential probes were used for the rest of the test.

## C. Estimation Accuracy of the Proposed DTO on Four Types of Dielectric Materials

TABLE IV ESTIMATION ACCURACY OF THE DTO ON X5R-LV SAMPLES

| Part number       | t under<br>SEM(μm) | $\hat{t}$ under DTO(VNA) | error | t under DTO(DS) | error |

|-------------------|--------------------|--------------------------|-------|-----------------|-------|

|                   |                    | (µm)                     |       | (µm)            |       |

| C2012X5R1C225K125 | 2.51               | 2.44                     | -2.8% | 2.53            | +0.9% |

| C2012X5R1E225K125 | 2.5                | 2.46                     | -1.6% | 2.55            | +1.9% |

| C2012X5R1V225K125 | 4.0                | 4.06                     | +1.6% | 3.84            | -4.1% |

| C2012X5R1H225K125 | 3.94               | 4.07                     | +3.2% | 4.22            | +7.1% |

| C2012X5R1C475K125 | 2.08               | 2.15                     | +3.4% | 2.27            | +9.1% |

| C2012X5R1E475K125 | 2.58               | 2.59                     | +0.3% | 2.82            | +8.8% |

| C2012X5R1H475K125 | 2.59               | 2.58                     | -0.1% | 2.79            | +7.7% |

| C3216X5R1E106K160 | 2.85               | 2.79                     | -2.1% | 3.05            | +7.0% |

| C3216X5R1V106K160 | 3.17               | 3.16                     | -0.3% | 3.22            | +1.6% |

| C3216X5R1H106K160 | 2.95               | 3.16                     | +7.1% | 3.25            | +10%  |

#### ACKNOWLEDGMENT

The authors would like to thank Dr. David Menzi from ETH Zurich for his valuable suggestions on the calibration of the measurement circuit and loss modeling under dc bias.

To validate the effectiveness of the proposed dielectric thickness observer (DTO), this research includes a supplementary

TABLE V ESTIMATION ACCURACY OF THE DTO ON X7R-LV SAMPLES

| Part number       | $t$ under SEM $(\mu \mathrm{m})$ | $\widehat{t}$ from DTO ( $\mu$ m) | error |

|-------------------|----------------------------------|-----------------------------------|-------|

| C2012X7R1E475K125 | 3.18                             | 3.10                              | -2.5% |

| C2012X7R1V475K125 | 3.29                             | 3.09                              | -5.8% |

| C3216X7R1V475K160 | 4.58                             | 4.75                              | +3.6% |

| C3216X7R1V225K160 | 7.25                             | 7.35                              | +1.4% |

| C3216X7R1E106K160 | 3.47                             | 3.35                              | -3.7% |

| C3216X7R1C106K160 | 2.85                             | 2.80                              | -1.8% |

| C2012X7R1E225K125 | 4.88                             | 4.88                              | +0.0% |

| C2012X7R1H225K125 | 4.88                             | 4.86                              | -0.4% |

| C2012X5R1V225K125 | 4.88                             | 4.87                              | -0.2% |

TABLE VI ESTIMATION ACCURACY OF THE DTO ON X7T-HV SAMPLES

| Part number       | $t$ under SEM $(\mu \mathrm{m})$ | $\widehat{t}$ from DTO $(\mu \text{m})$ | error |

|-------------------|----------------------------------|-----------------------------------------|-------|

| C3216X7T2E224K160 | 10.37                            | 10.00                                   | -3.5% |

| C4532X7T2E105K250 | 10.37                            | 10.66                                   | +2.8% |

| C4532X7T2W474K230 | 17.69                            | 17.28                                   | -2.3% |

| C4532X7T2J224K200 | 22.86                            | 22.88                                   | +0.1% |

| C5750X7T2J474K250 | 22.60                            | 23.37                                   | +3.4% |

| C5750X7T2W105K250 | 16.45                            | 15.37                                   | -6.5% |

TABLE VII

ESTIMATION ACCURACY OF THE DTO ON X7R-HV SAMPLES

| Part number       | t under SEM (μm) | $\widehat{t}$ from DTO | error |

|-------------------|------------------|------------------------|-------|

|                   | 9 /              | (µm)                   |       |

| C5750X7R2J224L230 | 48.0             | 49.4                   | +2.9% |

| C4532X7R2K104L230 | 48.0             | 46.83                  | -2.4% |

| C4532X7R2E474K230 | 23.0             | 22.27                  | -3.1% |

| C3225X7R2E224K200 | 23.0             | 21.93                  | -4.6% |

| C5750X7R2E105K230 | 22.2             | 21.5                   | -3.2% |

| C3216X7R2A105K160 | 8.9              | 8.58                   | -3.6% |

| C3225X7R2A225K230 | 8.88             | 9.18                   | +3.4% |

document encompassing cross-sectional scanning electron microscope (SEM) images of 9 X5R MLCC samples, along with the MATLAB script of the DTO. The provided MATLAB script empowers readers to estimate the dielectric thickness of an MLCC sample based on its C-V curve, showcasing remarkable concurrence with the dielectric thickness measured from the SEM images. The comparisons are presented in Table IV, V, VI, and VII, affirming the reliability and accuracy of the DTO in predicting the dielectric thickness of MLCC samples.

#### REFERENCES

- [1] D. Cittanti et al., "Analysis and design of a high power density full-ceramic 900 V DC-link capacitor for a 550 kVA electric vehicle drive inverter," in Proc. Int. Power Electron. Conf., 2022, pp. 1144–1151.

- [2] D. Menzi, D. Bortis, G. Zulauf, M. Heller, and J. W. Kolar, "Novel iGSE-C loss modeling of X7R ceramic capacitors," *IEEE Trans. Power Electron.*, vol. 35, no. 12, pp. 13367–13383, Dec. 2020.

- [3] M. Wei, Y. Li, Z. Ni, C. Liu, and D. Cao, "Zero voltage switching switchedtank modular converter for data center application," in *Proc. IEEE 7th* Workshop Wide Bandgap Power Devices Appl., 2019, pp. 245–250.