Received 10 November 2022, accepted 29 November 2022, date of publication 9 December 2022, date of current version 20 December 2022.

Digital Object Identifier 10.1109/ACCESS.2022.3228165

## RESEARCH ARTICLE

# Investigation of Junctionless Fin-FET Characterization in Deep Cryogenic Temperature: DC and RF analysis

#### DARIUSH MADADI

Electrical Engineering Department, University of Semnan, Semnan 989195574051, Iran e-mail: Madadi@semnan.ac.ir

**ABSTRACT** This work presents the SOI Junctionless Fin-FET characterization in Deep Cryogenic behavior (DC-JLFET). Results show that the JLT device is well-suited for various operations, such as computation, sensing, and communication in the quantum field. The cryogenic transfer characteristics, including bias, and interface trap density, are analyzed over a broad temperature range (300 Kelvin down to 4.2 Kelvin). Cryogenic DC and RF analyses were done on the conventional double-gate JL-FET structure, operating at 300 K and below 4.2 K for different geometries. The suggested study illustrates that cryogenic status in the new technology CMOS can be correctly anticipated by calibrating data using an experimental device.

**INDEX TERMS** Fin-FET, cryogenic, junctionless, quantum computing.

#### I. INTRODUCTION

The scaling down of the channel lengths in standard metaloxide-semiconductor (MOS) Field-Effect transistors (FET) poses several critical challenges, such as reducing SCEs, increasing on-current, and lower power consumption must be addressed [1], [2], [3]. SOI transistors have been broadly used as a good alternative for further downscaling for the low-power FET operations asked by ITRS. SOI wafers have low variability, improved electrostatic control, and lesser short-channel effects (SCEs) [4], [5], [6], [7], [8], [9]. Also, SOI's lower parasitic capacitances and resistances provide good RF and analog Figures of Merits (FoMs). The junctionless FETs (JLFETs) have been suggested as a further effort to solve the SCEs and stringent requirements of an ultra-steep doping characteristic at the metallurgical interfaces as well as complicated heat budgets in standard transistors [10], [11], [12], [13], [14], [15], [16], [17], [18]. The other way to reduce the SCEs is by using the multiple-gate transistors in the scaled MOSFETs [19], [20], [21]. To improve electrostatic integrity, three modes are combined in this work: SOI, multiple gate FET, and junctionless technology. In silicon structures, creating CMOS-compatible qubits [22], [23] helped us focus on low temperatures of CMOS semiconductor technology for computer operations. MOS transistor structures have been studied at extremely low temperatures since the 1970s to be used in applications and systems, including limitednoise, space devices, energy conversion devices, and so on [24], [25]. Although, despite the various advantages of high-efficiency and low-power information technology [26], cryogenic cooling did not remain in use for computer technology, reversing the pattern established by the ETA-10 liquid-nitrogen-cooled quantum computer [27]. Quantum computers get the theoretical potential, supported by experimental data, to operate in an enormous problem situation and thus can solve several more computer processing issues that traditional computers cannot. Quantum bit (Qubit) manipulation and readout are vital for achieving quantum computers. Another strategy would be to use low-temperature electronics, which perform at/or close to the temperatures at which qubits exist [28], [29], [30], [31], [32], [33], [34]. Aside from quantum computing, the original function for low-temperature devices is dispersed and huge. In the specific situation of Quantum Computers, FinFETs, as the most common logic circuit structure, are the first of many contemporary devices to be investigated for quantum control circuits.

The associate editor coordinating the review of this manuscript and approving it for publication was Wei Huang<sup>(D)</sup>.

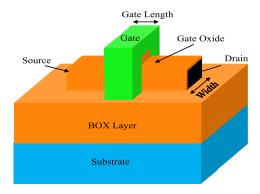

FIGURE 1. A 3-D view of the proposed DC-JLFET.

In this work, we demonstrate that the electrical specifications of junctionless FETs are highly affected by the physical properties of the structures. As a result, the main goal of this study focuses on the effect of temperature decrement on the working of JLFETs down to 4 K in the DC and RF characteristics. The I/V curve, transconductance ( $G_m$ ), subthreshold slope (SS), radio frequency (RF), and interface traps have all been investigated. Also, the influence of different geometries (W/L) on the device characteristics has been analyzed. The goal for comparing 40 and 28 nodes is to investigate the channel length effect on the device features.

#### **II. DEVICE CHARACTERISTICS**

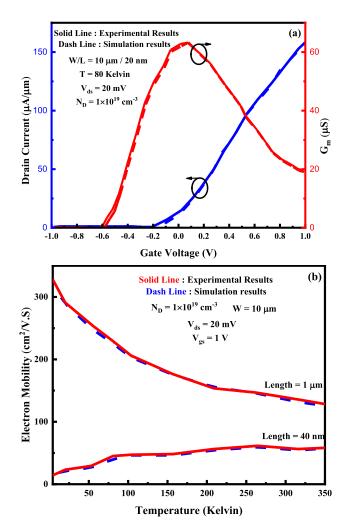

A 3-D schematic of the DC-JLFET is depicted in Fig. 1. First, we have calibrated the simulation data for validation by regenerating the experimental data of a junctionless FET [35], which is demonstrated in Fig. 2. This work is based on an N-type JLFETT structure on <100> orientation SOI wafers with a 100 nm thick buried oxide layer (BOX) and an active silicon layer with 5 nm thickness. Uniformly doping of active regions of the device is considered at one × 10<sup>19</sup> cm<sup>-3</sup>. The gate comprises a 5.0 eV work function with an oxide thickness of 1 nm. The gate mask length ranged from 28 nm to 40 nm, and the gate mask width ranged from 1  $\mu$ m to 2  $\mu$ m. Surface roughness, coulomb, and phonon scattering have been considered to investigate the impact of scattering effect on mobility.

#### **III. RESULTS AND DISCUSSIONS**

#### A. IMPACT OF CRYOGENIC TEMPERATURE ON THE DC CHARACTERISTICS

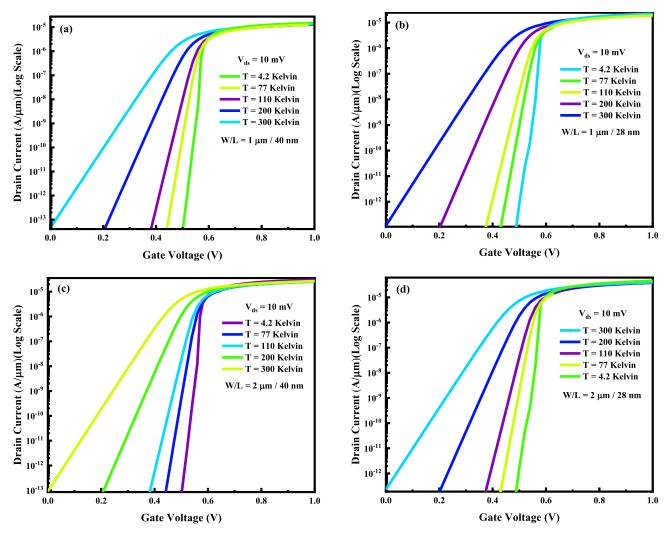

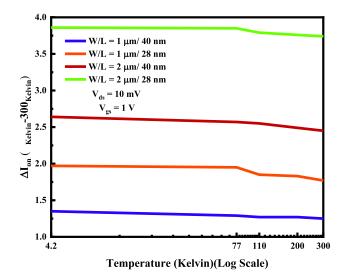

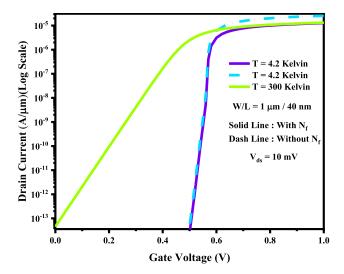

This paper investigates the cryogenic temperature effects on the RF and DC modes and also analyzes these effects on the subthreshold slope, threshold voltage, and transconductance. Transfer characteristics of the JLFET structure for short channel sizes (L = 28 nm and L = 40 nm) have been analyzed at various temperatures in the wide range from 4.2–300 Kelvin, as shown in Fig. 3. The widely known point of crossing, which is known as the zero-temperature coefficient (ZTC) [17], [36], [37], has not to rely on the temperature owing to the heat recompense impacts of carrier mobility and threshold

**FIGURE 2.** Calibration of (a) transfer characteristic and (b) electron mobility of the JLTFET with experimental results [35] for validation of the simulation data.

voltage ( $V_{th}$ ) [35]. The ZTC phenomenon is defined by the fact that for large gate sizes,  $V_{th}$  and electron mobility have both been enhanced at lower temperatures [35], whereas those differed in reduction of temperature for short gate length and increment of mobility is not high.

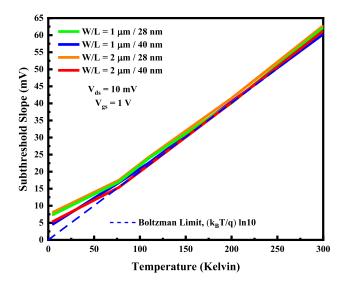

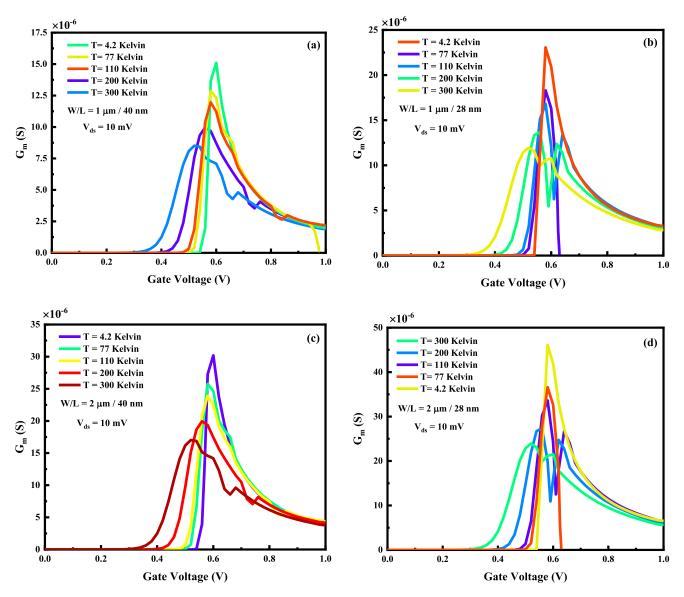

The subthreshold slope SS, described as  $\eta kT/q$  (ln10) (mV/dec), decreases the thermal voltage at 77 and 4.2 Kelvin for all structures. As demonstrated in Fig. 4, the SS reduces to 4.5 mV/dec in 4.2 K for L = 40 nm; however, this reduction is smaller than the predicted amount, which is 0.8 mV/dec at extremely low temperatures; this is due to insufficient dopant ionization. Also, the SS is 4.8 mV/dec when the gate size is L = 28 nm.

The  $I_{on}$  increases slightly at 4.2 Kelvin for the small-length structures but rises for the extensive-length designs, as shown in Fig. 5. It could be defined by the expression of the electron current [30]:

$$J_n = q\mu_n \left( nE + \frac{n\nabla kT}{q} \right) \tag{1}$$

FIGURE 3. Transfer characteristic curve (a) W/L=1  $\mu$ m/ L=40 nm (b) W/L=1  $\mu$ m/ L=28 nm (c) W/L=2  $\mu$ m/ L=40 nm (d) W/L=2  $\mu$ m/ L=28 nm of the JLFET at V<sub>ds</sub> = 10 mV with different temperatures.

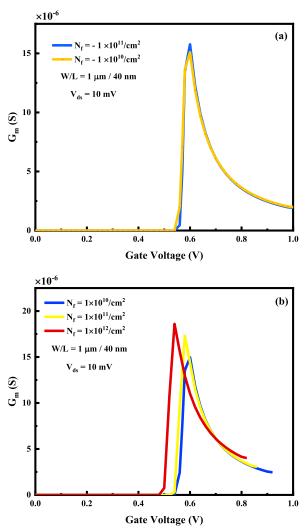

The current density is proportional to the temperatures at low drain voltages, and field-assisted ionization is poor, but at high drain voltages, the current density rises with lowering the temperature due to carrier mobility, and field-assisted ionization is significant in this channel size. The G<sub>m</sub> improves at 4.2 Kelvin ( $\sim \times 2$ , W/L = 2  $\mu$ m/ 28 nm), as illustrated in Fig. 6.

For JLFET structures, the  $G_m$  curve was plotted in Fig. 6, with different W/L geometries at  $V_{ds} = 10$  mV, while the  $G_m$  show high degradation in large  $V_{gs} < V_{fb}$  in regards to increasing the series resistance  $R_{Se}$ . The oscillations observed in  $G_m$  curves credit this impact to the quantum transport in such Structures [38]. When the  $V_{gs}$  of an n-type transistor is raised, electrons may fill the possible sub-band step by step, causing the current to behave step-like. In particular, at extremely small  $V_{ds}$ , the quantization of energy states in the conduction band is seen [39] because the total energy at larger voltages is substantially more than the band gap among two quantized energy states.

In a short channel DGJLFET, the  $V_{th}$  can be described as [15] (2), as shown at the bottom of the next page, where;

$$\beta = \frac{-1 + e^{-\frac{L_{gate}}{\lambda}}}{2 \sinh(\frac{L_{gate}}{\lambda})}$$

$$\delta = \frac{V_{ds} - \omega\left(-1 + e^{-\frac{L_{gate}}{\lambda}}\right)}{2 \sinh(\frac{L_{gate}}{\lambda})}$$

$$\gamma = \frac{1 - e^{\frac{L_{gate}}{\lambda}}}{2 \sinh(\frac{L_{gate}}{\lambda})}$$

$$\theta = \frac{-V_{ds} + \omega\left(-1 + e^{\frac{L_{gate}}{\lambda}}\right)}{2 \sinh(\frac{L_{gate}}{\lambda})}$$

$$\lambda = \sqrt{\frac{t_{si}(4\varepsilon_{si} + C_{ox}t_{si})}{8C_{ox}}}$$

FIGURE 4. Variation of SS versus different temperatures and W/L geometries.

**FIGURE 5.** Impact of the temperature on the I<sub>on</sub> of JLFET versus different temperatures.

$$\omega = V_{fb} - \frac{qN_D t_{si}}{2C_{ox}} - \frac{qN_D t_{si}^2}{8\varepsilon_{si}}$$

(3)

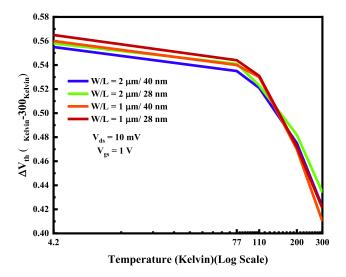

where the  $\lambda$  is the natural length and V<sub>fb</sub> is the flat band voltage. We must note that the  $\beta$  and  $\gamma$  are zero in long channel lengths. Eq. (3) shows that the only temperaturedependent parameter is the V<sub>fb</sub>. Besides, the V<sub>th</sub> shifts to higher gate voltages at 4.2 Kelvin versus 300 Kelvin because of incomplete ionization. Indeed, larger drain voltages are necessary to absorb enough electrons to the top to form the inversion area. The V<sub>th</sub> variation with different temperatures is shown in Fig. 7 with various W/L geometries. It is worth noting that the maximum V<sub>th</sub>change has been illustrated in W/L = 1  $\mu$ m / 28 nm ( $\Delta$ V<sub>th</sub> = 0.15 V).

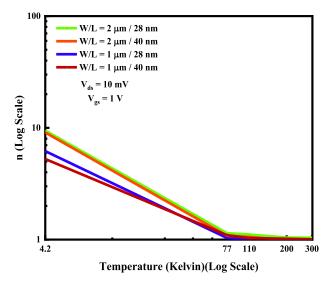

Fig. 8 shows that until reaching 77 Kelvin, the  $\eta$  remains close to the value at 300 Kelvin. From 77 Kelvin down to 4.2 Kelvin, the slope factor increases sharply.

### B. INFLUENCE OF INTERFACE CHARGE DENSITY ON THE JLFET I-V CURVE IN THE DEEP CRYOGENIC TEMPERATURE

The charge density for every unit area measured in interface states  $Q_f$  is [40]:

$$Q_f = \int_{E_i}^{+\infty} N_f(E) f(E) dE$$

(4)

In this equation,  $N_f$  denotes the overall distribution of interface traps across the energy. In cryogenic conditions, the concentration of dangling bonds at the junction does not increase considerably. The clear temperature-dependent rise of the rate of  $N_f$  value (for example, in charge-pump calculations [40]) is because, at very low temperatures, the Fermi level covers a large section of the energy bandgap. This logarithmic rise in trap intensity at the band edge was also required to account for the bend of the I-V curve and the SS degradation caused by conduction-band or valence-band tails [41]. Depending on the type (acceptor/donor) and the placement of the Fermi level in the bandgap, Interface density Nf can be either charged or uncharged. Their charge contribution varies with the surface potential,  $\psi_s$ . Fig. 9 depicts the transfer characteristics of JLFET in the deep cryogenic temperature and RT with and without interface charge density.

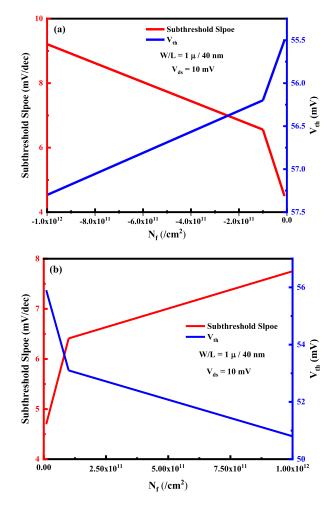

The interface traps play an essential role in determining the V<sub>th</sub>, the  $\mu_{ch}$ , and the G<sub>m</sub> of FETs, and their effect is especially evident in the SS of the transfer characteristics. Fig. 10 demonstrates the influence of the various  $N_f$  on the SS & V<sub>th</sub> in the deep cryogenic temperature.

Fig. 11 shows the JLFET  $G_m$  curve in deep cryogenic temperatures with various  $N_f$ . To analyze the effect of the  $N_f$  on the SS can be expressed [7]:

$$SS = \frac{kT}{q} ln(10) \left[ 1 + \frac{C_f}{C_{ox}} + n \right]$$

(5)

where  $C_f = qN_f$  is the capacitances of the  $N_f$  at the gate oxide,  $C_{ox}$  is the gate oxide capacitance,  $C_{Si}$  is the active regions capacitance, and  $N_f$  represents the interface trap density at the gate oxide. The n is the body factor, defined by  $n = (C_{ox}+C_f+C_{Si})/C_{ox}$  for an SOI structure. The impacts of traps related to the BOX layer have been neglected.

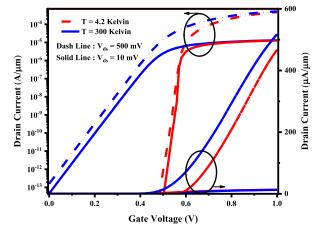

Fig. 12 illustrates the influence of  $V_{ds}$  on the I-V curve of JLFET in the deep cryogenic temperature. As demonstrated in Fig. 12, at higher drain voltages, current density rises

$$V_{\rm th} = \frac{2(\delta\gamma + \beta\theta) + \omega + \sqrt{((2(\delta\gamma + \beta\theta) + \omega)^2 - (1 - 4\beta\gamma)(\omega^2 - 4\delta\theta))}}{(1 - 4\beta\gamma)}$$

(2)

FIGURE 6. Characteristic of the G<sub>m</sub> curve (a) W/L=1  $\mu$ m/ L=40 nm (b) W/L=1  $\mu$ m/ L=28 nm (c) W/L=2  $\mu$ m/ L=40 nm (d) W/L=2  $\mu$ m/ L=28 nm of the JLFET at V<sub>ds</sub> = 10 mV with different temperatures.

with reducing the temperature through mobility, and fieldassisted ionization is critical in the channel. We understand that  $N_f$  increases with lowering the temperature, achieving  $10^{13}$  cm<sup>-2</sup> at deep cryogenic temperatures.

#### C. RF ANALYSIS

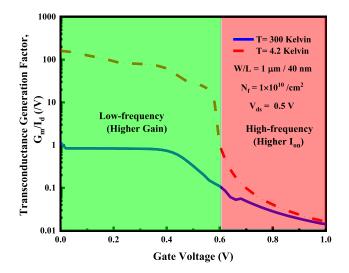

Fig. 13 shows the impact of the Transconductance Generation Factor (TGF) versus  $V_{gs}$  in various cryogenic temperatures. TGF has been described as  $G_m$ /drain-current relation and represents the power losses of the structure in digital operations. The higher TGF leads to smaller power losses.

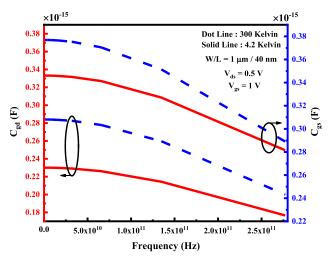

Plotting TGF, which gives a detailed perspective of the analyzed device, from low-frequency (depletion/partial depletion) application where high gain is obtained to highfrequency (flat band/accumulation) application where higher sis solution that enables for a first world admiration of the device under research for analog analysis. In the green regime (depletion/partial depletion), TGF is inversely proportional to the SS. On the purple side (flat band/accumulation), It would be proportionally to  $\mu_n.C_{ox}/n$  (where  $\mu_n$  is electron mobility,  $C_{ox}$  is gate oxide capacitance, and n is body factor). On the other hand, A device's analog/RF efficiency is mainly restricted by intrinsic terminal capacitances. The effect of temperature on parasitic capacitances versus  $V_{gs}$  can be seen in Fig. 14.

drive current is needed, seems to be a constructive analy-

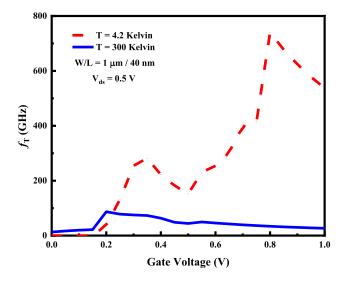

The transit frequency  $(f_T)$  of FETs is achieved as follows() [42]:

$$f_T = \frac{G_m}{2\pi \left(c_{gs} + c_{gd}\right)} \tag{6}$$

FIGURE 7. Variation of  $\mathrm{V}_{\mathrm{th}}$  versus different temperatures and W/L geometries.

FIGURE 8. Impact of the temperature on the  $\eta$  of JLFET.

and is calculated from the current gain (H<sub>21</sub>) and shown in Fig. 15 as one of the main RF FoMs. Due to the lower parasitic capacitances and higher  $G_m$ , the  $f_T$  improves, and the maximum  $f_T$  is achieved, about 563 GHz. Because of the lower variation of capacitances in cryogenic temperatures, the transit frequency  $f_T$  follows the increment in the  $G_m$ , as demonstrated in Fig. 7. This rise may be offset by decreased power usage, which is also advantageous for thermal losses from the management system to the quantum bits. This increment becomes particularly significant in shorter channel lengths.

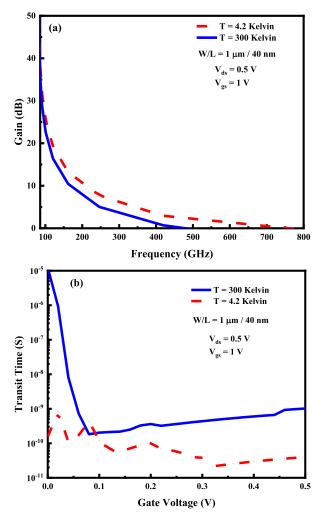

We analyzed the influence of the various temperatures on the unilateral-power-gain (UPG),  $(f_{max})$  is the frequency where UPG becomes unity, or zero dB, and the transit time  $(\tau)$  of JLFET. These ratios have been achieved from the

FIGURE 9. Effect of  $N_f$  on the on-current ( $I_{on}$ ).

FIGURE 10. Impact of the various  $N_{\rm f}$  on the SS &  $V_{\rm th}$  in the 4.2 Kelvin temperature (a) Negative (b) Positive.

equations [43], [44]:

$$f_{max} = \frac{f_T}{2} \sqrt{\frac{R_{ds}}{R_g}} \tag{7}$$

FIGURE 11. Impact of the various interface charge density on the  $G_m$  curve at the 4.2 Kelvin temperature (a) Negative (b) Positive.

FIGURE 12. Impact of  $V_{\mbox{ds}}$  on the JLFET I-V curve in the various temperatures.

$$\tau = \frac{1}{2\pi fT} \tag{8}$$

$$UPG = \left(\frac{f_{max}}{f}\right)^2 \tag{9}$$

FIGURE 13. Impacts of TGF on the various temperatures.

FIGURE 14. Impact of various temperatures on parasitic capacitance.

FIGURE 15. Impact of various temperatures on the f<sub>T</sub>.

The obtained results above equations are illustrated in Fig. 16. The gate resistance  $(R_g)$  decreases because of the reduced

FIGURE 16. Influence of several temperatures on the (a) UPG and (b) transit time.

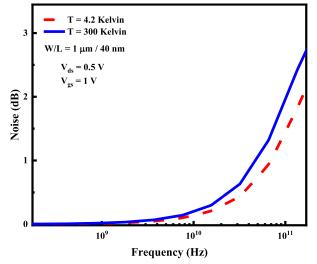

FIGURE 17. Impact of various temperatures on the noise.

resistivity of gate metal contact at the cryogenic temperature, and due to the higher  $f_T$  at 4.2 Kelvin,  $f_{max}$  increases. It can be inferred that the 4.2 Kelvin temperature leads to better

performance and reduces transit time. Improvement in  $G_m$  and  $f_T$  enables a reduction in transit time. Charge carriers have a very low transit time in the ON-condition.

The NF of FETs can be obtained as follows:

$$NF = 1 + 5\pi f C_{g_s} \sqrt{\frac{R_S + R_G}{G_m}} \tag{10}$$

Fig. 17 shows the impact of various temperatures on the Noise Figure (NF). By reducing parasitic capacitance and due to higher  $G_m$ , the value of NF reduces at lower temperatures.

#### **IV. CONCLUSION**

The effect of cryogenic temperature on an (L = 28 nm and L = 40 nm) Junctionless SOI Fin-FET innovation for quantum information management systems is presented in this paper. Starting with a deep study of the physical structures at extremely low temperatures, actually promoting changes in the essential analog design specifications are achieved, even though increment in the slope factor at very low temperatures decreases the predicted current savings; however, this increase is not significant. The suggested study illustrates that cryogenic status in the new technology CMOS may be correctly anticipated by calibrating data using an experimental device. This is an attractive idea for future small cryogenic models for silicon-based quantum information structures.

#### REFERENCES

- S. Veeraraghavan and J. G. Fossum, "Short-channel effects in SOI MOSFETs," *IEEE Trans. Electron Devices*, vol. 36, no. 3, pp. 522–528, Mar. 1989, doi: 10.1109/16.19963.

- [2] M. J. Kumar and G. V. Reddy, "Evidence for suppressed shortchannel effects in deep submicron dual-material gate (DMG) partially depleted SOI MOSFETs—A two-dimensional analytical approach," *Microelectron. Eng.*, vol. 75, no. 4, pp. 367–374, Nov. 2004, doi: 10.1016/j.mee.2004.07.058.

- [3] D. Madadi and A. A. Orouji, "Investigation of short channel effects in SOI MOSFET with 20 nm channel length by a β-Ga<sub>2</sub>O<sub>3</sub> layer," *ECS J. Solid State Sci. Technol.*, vol. 9, no. 4, Apr. 2020, Art. no. 045002, doi: 10.1149/2162-8777/ab878b.

- [4] Y.-K. Lin, P. Kushwaha, H. Agarwal, H.-L. Chang, J. P. Duarte, A. B. Sachid, S. Khandelwal, S. Salahuddin, and C. Hu, "Modeling of back-gate effects on gate-induced drain leakage and gate currents in UTB SOI MOSFETs," *IEEE Trans. Electron Devices*, vol. 64, no. 10, pp. 3986–3990, Oct. 2017.

- [5] H. Bohuslavskyi, A. G. M. Jansen, S. Barraud, V. Barral, M. Casse, L. Le Guevel, X. Jehl, L. Hutin, B. Bertrand, G. Billiot, G. Pillonnet, F. Arnaud, P. Galy, S. De Franceschi, M. Vinet, and M. Sanquer, "Cryogenic subthreshold swing saturation in FD-SOI MOSFETs described with band broadening," *IEEE Electron Device Lett.*, vol. 40, no. 5, pp. 784–787, May 2019, doi: 10.1109/LED.2019.2903111.

- [6] D. Flandre, J. P. Colinge, J. Chen, D. D. Ceuster, J. P. Eggermont, L. Ferreira, B. Gentinne, P. G. A. Jespers, A. Viviani, R. Gillon, J. P. Raskin, A. Vander Vorst, D. Vanhoenacker-Janvier, and F. Silveira, "Fully-depleted SOI CMOS technology for low-voltage low-power mixed digital/analog/microwave circuits," *Anal. Integr. Circuits Signal Process.*, vol. 21, no. 3, pp. 213–228, 1999, doi: 10.1023/A:1008321919587.

- [7] J. P. Colinge, D. Flandre, and F. Van de Wiele, "Subthreshold slope of long-channel, accumulation-mode *p*-channel SOI MOSFETs," *Solid. State. Electron.*, vol. 37, no. 2, pp. 289–294, Feb. 1994, doi: 10.1016/0038-1101(94)90080-9.

- [8] J.-P. Colinge, "Multiple-gate SOI MOSFETs," Solid-State Electron., vol. 48, no. 6, pp. 897–905, Jun. 2004, doi: 10.1016/j.sse.2003.12.020.

- [9] D. Madadi and A. A. Orouji, "Scattering mechanisms in β-Ga<sub>2</sub>O<sub>3</sub> junctionless SOI MOSFET: Investigation of electron mobility and short channel effects," *Mater. Today Commun.*, vol. 26, Mar. 2021, Art. no. 102044, doi: 10.1016/j.mtcomm.2021.102044.

- [10] F. Jazaeri, L. Barbut, and J.-M. Sallese, "Modeling and design space of junctionless symmetric DG MOSFETs with long channel," *IEEE Trans. Electron Devices*, vol. 60, no. 7, pp. 2120–2127, Jul. 2013, doi: 10.1109/TED.2013.2261073.

- [11] F. Jazaeri and J.-M. Sallese, Modeling Nanowire and Double-Gate Junctionless Field-Effect Transistors. Cambridge, U.K.: Cambridge Univ. Press, 2018, doi: 10.1017/9781316676899.

- [12] S. Sahay and M. J. Kumar, "Diameter dependence of leakage current in nanowire junctionless field effect transistors," *IEEE Trans. Electron Devices*, vol. 64, no. 3, pp. 1330–1335, Mar. 2017, doi: 10.1109/TED.2016.2645640.

- [13] D. Madadi and A. A. Orouji, "β-Ga<sub>2</sub>O<sub>3</sub> double gate junctionless FET with an efficient volume depletion region," *Phys. Lett. A*, vol. 412, Oct. 2021, Art. no. 127575, doi: 10.1016/j.physleta.2021.127575.

- [14] S. Barraud, M. Berthome, R. Coquand, M. Cassé, T. Ernst, M.-P. Samson, P. Perreau, K. K. Bourdelle, O. Faynot, and T. Poiroux, "Scaling of trigate junctionless nanowire MOSFET with gate length down to 13 nm," *IEEE Electron Device Lett.*, vol. 33, no. 9, pp. 1225–1227, Sep. 2012, doi: 10.1109/LED.2012.2203091.

- [15] S. Sahay and M. J. Kumar, "Modeling junctionless field-effect transistors," in *Junctionless Field-Effect Transistors*. Hoboken, NJ, USA: Wiley, 2019, pp. 327–384, doi: 10.1002/9781119523543.ch8.

- [16] J.-P. Colinge, C.-W. Lee, I. Ferain, N. D. Akhavan, R. Yan, P. Razavi, R. Yu, A. N. Nazarov, and R. T. Doria, "Reduced electric field in junctionless transistors," *Appl. Phys. Lett.*, vol. 96, no. 7, Feb. 2010, Art. no. 073510, doi: 10.1063/1.3299014.

- [17] D. Madadi, " $\beta$ -Ga<sub>2</sub>O<sub>3</sub> junctionless FET with an  $\Omega$  shape 4H-SiC region in accumulation mode," *Silicon*, vol. 14, no. 13, pp. 7595–7602, Nov. 2021, doi: 10.1007/s12633-021-01510-9.

- [18] M. Bolokian, A. A. Orouji, A. Abbasi, and D. Madadi, "Realization of double-gate junctionless field effect transistor depletion region for 6 nm regime with an efficient layer," *Phys. Status Solidi*, *A*, vol. 219, no. 21, Nov. 2022, Art. no. 2200214, doi: 10.1002/pssa.202200214.

- [19] J.-M. Sallese, N. Chevillon, C. Lallement, B. Iñiguez, and F. Prégaldiny, "Charge-based modeling of junctionless double-gate field-effect transistors," *IEEE Trans. Electron Devices*, vol. 58, no. 8, pp. 2628–2637, Aug. 2011, doi: 10.1109/TED.2011.2156413.

- [20] P. Razavi, G. Fagas, I. Ferain, N. D. Akhavan, R. Yu, and J. P. Colinge, "Performance investigation of short-channel junctionless multigate transistors," in *Proc. Ulis Ultimate Integr. Silicon*, Mar. 2011, pp. 1–3, doi: 10.1109/ULIS.2011.5758005.

- [21] A. Motamedi, A. A. Orouji, and D. Madadi, "Physical analysis of β-Ga<sub>2</sub>O<sub>3</sub> gate-all-around nanowire junctionless transistors: Short-channel effects and temperature dependence," *J. Comput. Electron.*, vol. 21, no. 1, pp. 197–205, Feb. 2022, doi: 10.1007/s10825-021-01837-x.

- [22] J. M. Elzerman, R. Hanson, L. H. W. van Beveren, B. Witkamp, L. M. K. Vandersypen, and L. P. Kouwenhoven, "Single-shot read-out of an individual electron spin in a quantum dot," *Nature*, vol. 430, no. 6998, pp. 431–435, 2004, doi: 10.1038/nature02693.

- [23] J. J. Pla, K. Y. Tan, J. P. Dehollain, W. H. Lim, J. J. L. Morton, D. N. Jamieson, A. S. Dzurak, and A. Morello, "A single-atom electron spin qubit in silicon," *Nature*, vol. 489, no. 7417, pp. 541–545, Sep. 2012, doi: 10.1038/nature11449.

- [24] C. Claeys and E. Simoen, "The perspectives of silicon-on-insulator technologies for cryogenic applications," *J. Electrochem. Soc.*, vol. 141, no. 9, pp. 2522–2532, Sep. 1994, doi: 10.1149/1.2055155.

- [25] T. Elewa, "Performance and physical mechanisms in SIMOX MOS transistors operated at very low temperature," *IEEE Trans. Electron Devices*, vol. 37, no. 4, pp. 1007–1019, Apr. 1990, doi: 10.1109/16.52436.

- [26] M. J. Deen, "Cryogenic operation of CMOS-based microsystems and computers," *Microprocessors Microsyst.*, vol. 13, no. 4, pp. 245–253, May 1989, doi: 10.1016/0141-9331(89)90062-8.

- [27] D. M. Carlson, D. C. Sullivan, R. E. Bach, and D. R. Resnick, "The ETA 10 liquid-nitrogen-cooled supercomputer system," *IEEE Trans. Electron Devices*, vol. 36, no. 8, pp. 1404–1413, Aug. 1989, doi: 10.1109/ 16.30952.

- [28] A. Beckers, F. Jazaeri, and C. Enz, "Cryogenic MOSFET threshold voltage model," in *Proc. 49th Eur. Solid-State Device Res. Conf. (ESSDERC)*, Sep. 2019, pp. 94–97, doi: 10.1109/ESSDERC.2019. 8901806.

- [29] A. Beckers, F. Jazaeri, H. Bohuslavskyi, L. Hutin, S. De Franceschi, and C. Enz, "Characterization and modeling of 28-nm FDSOI CMOS technology down to cryogenic temperatures," *Solid-State Electron.*, vol. 159, pp. 106–115, Sep. 2019, doi: 10.1016/j.sse.2019.03.033.

- [30] A. Beckers, F. Jazaeri, A. Ruffino, C. Bruschini, A. Baschirotto, and C. Enz, "Cryogenic characterization of 28 nm bulk CMOS technology for quantum computing," in *Proc. 47th Eur. Solid-State Device Res. Conf. (ESSDERC)*, Sep. 2017, pp. 62–65, doi: 10.1109/ESS-DERC.2017.8066592.

- [31] B. K. Esfeh, N. Planes, M. Haond, J.-P. Raskin, D. Flandre, and V. Kilchytska, "28 nm FDSOI analog and RF figures of merit at N<sub>2</sub> cryogenic temperatures," *Solid-State Electron.*, vol. 159, pp. 77–82, Sep. 2019, doi: 10.1016/j.sse.2019.03.039.

- [32] S. O'uchi, K. Endo, M. Maezawa, T. Nakagawa, H. Ota, Y. X. Liu, T. Matsukawa, Y. Ishikawa, J. Tsukada, H. Yamauchi, W. Mizubayashi, S. Migita, Y. Morita, T. Sekigawa, H. Koike, K. Sakamoto, and M. Masahara, "Cryogenic operation of double-gate FinFET and demonstration of analog circuit at 4.2 K," in *Proc. IEEE Int. SOI Conf. (SOI)*, Oct. 2012, pp. 6–7, doi: 10.1109/SOI.2012.6404376.

- [33] G. Zhou, F. A. Mamun, J. Yang-Scharlotta, D. Vasileska, and I. S. Esqueda, "Cryogenic characterization and analysis of nanoscale SOI FETs using a virtual source model," *IEEE Trans. Electron Devices*, vol. 69, no. 3, pp. 1306–1312, Mar. 2022, doi: 10.1109/TED.2022.3142650.

- [34] R. M. Incandela, L. Song, H. Homulle, E. Charbon, A. Vladimirescu, and F. Sebastiano, "Characterization and compact modeling of nanometer CMOS transistors at deep-cryogenic temperatures," *IEEE J. Electron Devices Soc.*, vol. 6, pp. 996–1006, 2018, doi: 10.1109/JEDS.2018.2821763.

- [35] D.-Y. Jeon, S. J. Park, M. Mouis, S. Barraud, G.-T. Kim, and G. Ghibaudo, "Low-temperature electrical characterization of junctionless transistors," *Solid-State Electron.*, vol. 80, pp. 135–141, Feb. 2013, doi: 10.1016/j.sse.2012.10.018.

- [36] M. de Souza, M. A. Pavanello, R. D. Trevisoli, R. T. Doria, and J. Colinge, "Cryogenic operation of junctionless nanowire transistors," *IEEE Electron Device Lett.*, vol. 32, no. 10, pp. 1322–1324, Oct. 2011, doi: 10.1109/LED.2011.2161748.

- [37] D. Y. Jeon, S. J. Park, M. Mouis, S. Barraud, G. T. Kim, and G. Ghibaudo, "Low-temperature operation of junctionless nanowire transistors: Less surface roughness scattering effects and dominant scattering mechanisms," *Appl. Phys. Lett.*, vol. 105, no. 26, pp. 1–6, 2014, doi: 10.1063/1.4905366.

- [38] X. Li, W. Han, L. Ma, H. Wang, Y. Zhang, and F. Yang, "Lowtemperature quantum transport characteristics in single n-channel junctionless nanowire transistors," *IEEE Electron Device Lett.*, vol. 34, no. 5, pp. 581–583, May 2013, doi: 10.1109/LED.2013.2250898.

- [39] J.-P. Colinge, A. J. Quinn, L. Floyd, G. Redmond, J. C. Alderman, W. Xiong, and C. R. Cleavelin, "Low-temperature electron mobility in trigate SOI MOSFETs," *IEEE Electron Device Lett.*, vol. 27, no. 2, pp. 120–122, Feb. 2006, doi: 10.1109/LED.2005.862691.

- [40] A. Beckers, F. Jazaeri, A. Grill, S. Narasimhamoorthy, B. Parvais, and C. Enz, "Physical model of low-temperature to cryogenic threshold voltage in MOSFETs," *IEEE J. Electron Devices Soc.*, vol. 8, pp. 780–788, 2020, doi: 10.1109/JEDS.2020.2989629.

- [41] A. Beckers, F. Jazaeri, and C. Enz, "Inflection phenomenon in cryogenic MOSFET behavior," *IEEE Trans. Electron Devices*, vol. 67, no. 3, pp. 1357–1360, Mar. 2020, doi: 10.1109/TED.2020.2965475.

- [42] D. Madadi and A. A. Orouji, "New high-voltage and high-speed β-Ga<sub>2</sub>O<sub>3</sub> MESFET with amended electric field distribution by an insulator layer," *Eur. Phys. J. Plus*, vol. 135, no. 7, p. 578, Jul. 2020, doi: 10.1140/epjp/s13360-020-00523-4.

- [43] D. Madadi and A. A. Orouji, "A β-Ga<sub>2</sub>O<sub>3</sub> MESFET to amend the carrier distribution by using a tunnel diode," *IEEE Trans. Device Mater. Rel.*, vol. 21, no. 1, pp. 26–32, Mar. 2021, doi: 10.1109/TDMR.2020.3046530.

- [44] I. C. Cherik, S. Mohammadi, and A. A. Orouji, "Switching performance enhancement in nanotube double-gate tunneling field-effect transistor with germanium source regions," *IEEE Trans. Electron Devices*, vol. 69, no. 1, pp. 364–369, Jan. 2022, doi: 10.1109/TED.2021.3124984.

**DARIUSH MADADI** received the M.Sc. degree in nanoelectronics engineering from Semnan University, Semnan, Iran, in 2020. His research interests include simulation of nanoscale transistors, MOSFETs, TFETs, and solar-cell devices.

...