Received April 6, 2022, accepted April 6, 2022, date of current version April 19, 2022. Digital Object Identifier 10.1109/ACCESS.2022.3165957

## COMMENTS AND CORRECTIONS Corrections to "Design and Implementation of Seventeen Level Inverter With Reduced Components"

C. DHANAMJAYULU<sup>(1)</sup><sup>1,2</sup>, (Senior Member, IEEE), DEVALRAJU PRASAD<sup>(1)</sup><sup>1</sup>, (Graduate Student Member, IEEE), SANJEEVIKUMAR PADMANABAN<sup>(1)</sup><sup>2</sup>, (Senior Member, IEEE), PANDAV KIRAN MAROTI<sup>(1)</sup><sup>2</sup>, (Senior Member, IEEE), JENS BO HOLM-NIELSEN<sup>(1)</sup><sup>2</sup>, (Senior Member, IEEE), AND FREDE BLAABJERG<sup>(1)</sup><sup>3</sup>, (Fellow, IEEE)

<sup>1</sup>School of Electrical Engineering, Vellore Institute of Technology (VIT) University, Vellore 632014, India

<sup>2</sup>Center for Bioenergy and Green Engineering, Department of Energy Technology, Aalborg University, 6700 Esbjerg, Denmark

<sup>3</sup>Center of Reliable Power Electronics (CORPE), Department of Energy Technology, Aalborg University, 9220 Aalborg, Denmark

Corresponding authors: C. Dhanamjayulu (dhanamjayulu.c@vit.ac.in) and Sanjeevikumar Padmanaban (san@et.aau.dk)

This work was supported by the Danida Mobility Grant, responsible for the Ministry of Foreign Affairs of Denmark (MFA), Act 7 on Denmark's International Development Cooperation, under Project 19-MG06AAU.

In the above article [1], reference [2] was missing.

The third sentence in Section II should read: "The THD of the structure in [2] with multicarrier modulation technique can be reduced by incorporating a novel staircase modulation technique. Also, the bidirectional switch  $S_a$  is designed with only two diodes which reduces the overall components count of the system. Despite the proposed topology being developed for high power ratings, the TSV, losses, and THD are reduced which increases the overall efficiency of the system."

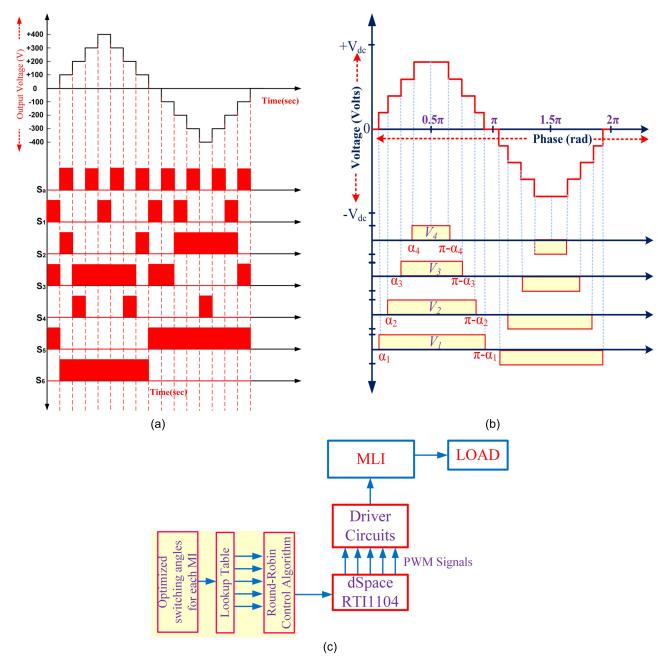

The last sentence in Section II-A, and *Mode 0* should read: "The expected nine level output voltage waveform is represented in FIGURE 3(a). The staircase modulation technique is represented in FIGURE 3(b). The control architecture of the proposed topology is shown in FIGURE 3(c)."

40214

## REFERENCES

- [1] C. Dhanamjayulu, D. Prasad, S. Padmanaban, P. K. Maroti, J. B. Holm-Nielsen, and F. Blaabjerg, "Design and implementation of seventeen level inverter with reduced components," *IEEE Access*, vol. 9, pp. 16746–16760, 2021.

- [2] S. P. Gautam, L. Kumar, and S. Gupta, "Hybrid topology of symmetrical multilevel inverter using less number of devices," *IET Power Electron.*, vol. 8, no. 11, pp. 2125–2135, Nov. 2015.

...

FIGURE 3. (a) Expected 9 level waveform of the proposed topology. (b) Staircase modulation. (c) Control block diagram.