Received December 1, 2021, accepted January 27, 2022, date of publication January 31, 2022, date of current version February 8, 2022.

Digital Object Identifier 10.1109/ACCESS.2022.3147879

# A Methodology to Derive a Symbolic Transfer Function for Multistage Amplifiers

HAMED AMINZADEH<sup>®</sup>1, (Member, IEEE), ALFIO DARIO GRASSO<sup>®</sup>2, (Senior Member, IEEE), AND GAETANO PALUMBO<sup>®</sup>2, (Fellow, IEEE)

<sup>1</sup>Department of Electrical Engineering, Payame Noor University (PNU), Tehran 19395-4697, Iran

Corresponding author: Alfio Dario Grasso (agrasso@dieei.unict.it)

**ABSTRACT** In this paper, a simple while effective methodology to calculate the symbolic transfer function of a multistage amplifier with frequency compensation is proposed. Three general amplifier models are introduced and analyzed, which represent basic topologies found in the literature. For these amplifier models, the symbolic transfer function is derived and specific strategies for the zero and non-dominant pole expressions are presented. The methodology is suited for hand calculations and yields accurate results while offering more intuition into the operation of the widely adopted frequency compensation solutions discussed in the literature. The effectiveness of the proposed approach is validated through various typical cases of study.

**INDEX TERMS** Amplifier, compensation capacitance, frequency compensation, Miller compensation, multistage amplifiers, pole/zero analysis, transfer function.

# I. INTRODUCTION

A preliminary and fundamental task to the design of a multistage amplifier is the derivation of its symbolic transfer function. Indeed, knowledge of the voltage transfer function is required to gain more insight into the operation of a multistage amplifier and to set and design the amplifier compensation network, which is a fundamental design step where interactions between the power consumption, noise, area, bandwidth, and stability are involved. Moreover, starting from a generalized symbolic transfer function expression, a designer can readily study and compare the several design features of an amplifier compensated with different frequency compensation solutions.

Since the early years of MOS analog integrated circuits, the compensation of two or more stage amplifiers was a key research area [1]–[28]. In this field several novel solutions were continuously proposed, especially for three- and four-stage amplifiers, and, despite several decades have been devoted to this subject, even in the last ten years the interest on this topic appears active [29]–[40]. Indeed, due to the continuous degradation of transistors' intrinsic gain and the low supply voltage of modern scaled technologies, more gain

The associate editor coordinating the review of this manuscript and approving it for publication was Teerachot Siriburanon.

stages are required [35] and in any case the development of novel compensation networks remains an important research area in advanced CMOS technologies.

Despite from one side several multistage amplifier compensation networks were proposed and analyzed [1]–[40], and, hence, we know their voltage transfer functions which are typically reported in the original or successive papers, the continuous research on this domain maintains unchanged the need to evaluate the voltage transfer function especially in a novel more complex topology that could be adopted. Hence, methodologies to calculate the symbolic voltage transfer function simply and efficiently are still important.

Traditionally, the calculation of a symbolic transfer function is a very lengthy and complex task if only Kirchhoff laws at nodes and meshes are used. To help the designer, computer-aided design (CAD) tools are developed to carry out the small-signal analysis such that the transfer function can be extracted in factorized or non-factorized form [41]–[48]. Simplifying circuit-level methods are used for pole/zero extraction, some of which are relied on dividing the frequency spectrum into small pieces [43], approximation of the time constants [44], developing new circuit micromodel [49], [50], or analysis of signal flow-graph [41]. Despite these approaches could be ideally suited also for pencil and paper evaluation, the final expressions are,

<sup>&</sup>lt;sup>2</sup>Dipartimento di Ingegneria Elettrica Elettronica e Informatica (DIEEI), University of Catania, 95125 Catania, Italy

however, complicated and cannot be analyzed simply, thus these strategies are more suited for CAD tools rather than for hand calculations.

Among the several papers and books where compensation techniques for multistage amplifiers are treated and their voltage transfer function is calculated, some circuit-level techniques suitable for a pencil and paper approach can be found in the literature [51]–[54]. For instance, one may calculate the location of the poles of a three-stage nested Miller compensated (NMC) amplifier by assuming that the second compensation capacitor is short-circuited, and the inner gain stage is in unity-feedback configuration [51]. Alternatively, the compensation network of an amplifier may be analyzed directly based on the concepts of control-centric Local Feedback Loop (LFL) [52], [32] or equivalent output impedance of the compensation loop [55], [56]. Similar methodologies facilitate the designer's ability to calculate the transfer function given that the type of the amplifier was specified a priori. A control-centric design-oriented analysis methodology based on a simplified feedback theory is presented in [54], helping to quickly evaluate the pole frequencies. Nevertheless, no clear symbolic expression can be extracted in general form, hindering a general understanding of the contributing and the limiting factors of the amplifier's performance.

In this paper, we develop a simple methodology that allows to efficiently calculate the symbolic transfer function of a multistage amplifier with its specific compensation networks. The methodology is suited to be also applied with pencil and paper and gives very accurate results. In particular, three general amplifier models are introduced and analyzed, which represent basic topologies found in the literature. For these amplifier models, the symbolic transfer function is derived and specific strategies for the zero and non-dominant pole expressions are presented. Thus, the final symbolic transfer function can be written in the required standard form.

The application and accuracy of the approach are reported for a set of six amplifiers, which includes classical and advanced topologies that can be considered as typical cases of study, even if the approach was positively used and tested for other several topologies. In particular, the amplifiers considered to validate the methodology are:

- a two-stage Miller compensation with nulling resistor (MCNR) [1];

- a three-stage with NMC [5], [6];

- a three-stage with reversed Nested-Miller compensation (RNMC) [6];

- a three-stage with the nested Miller compensation and a current buffer in the external loop, named active-feedback frequency compensation (AFFC) [16];

- a three-stage with single Miller compensation named impedance adapting compensation named (IAC) [29];

- a three-stage with single Miller compensation and current buffer, named cross feedforward cascode compensation (CFCC) [31].

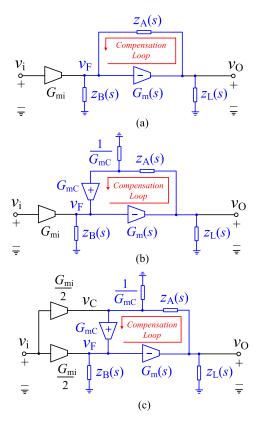

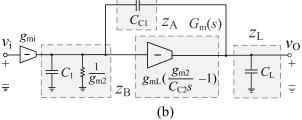

FIGURE 1. The general amplifier models proposed in this section; (a) type I; (b) type II; (c) type III (combined).

Moreover, the results show that the entire procedure can be summarized to find the variables used in a symbolic transfer function expression.

The manuscript is organized as follows. In Section II, after some preliminary considerations, the methodology is presented and developed, showing the evaluation of zero and poles and of the whole transfer function, as well as approximated calculation of the dominant pole. Section III reports the application, in order of complexity, on the six amplifier topologies selected as typical cases. Design considerations and remarks arising from the proposed methodology are included in Section IV. Finally, the conclusions are given in Section V.

### II. THE PROPOSED METHODOLOGY

# A. ABBREVIATIONS AND ACRONYMS

After inspecting the circuit topology of a huge number of multistage amplifiers presented in the literature, which includes both the conventional and the novel solutions, it was found that a generic topology can be modeled by using, in a recursive way if needed, the generalized three circuit configurations shown in Fig. 1 and named type I, type II, and type III.

In particular, as it will be better detailed and explained in the next Section, considering the well-known topology reported in references, the type I model can be used for the amplifier that adopts the Miller compensation [1], NMC [5],

RNMC [6], single Miller compensation (SMC) [22], together with the IAC single Miller topology [29], (i.e., compensation topologies without current or buffer or amplifier in the external loop). The type II model can be considered for two-stage amplifiers with Miller compensation and current buffer [8], [53], [66] and AFFC amplifier [16], while single miller topologies with a current buffer, like CFCC [31] and the cascode Miller-compensation with local impedance attenuation (CLIA) [34] (not included in this manuscript for space reason) can be reported and analyzed with the type III model.

It is worth noting that the main difference between the models in Fig. 1 is the way the input is connected to the feedback pathway of the frequency compensation network. In any case, the input transconductance,  $G_{mi}$ , converts the input voltage into an equivalent ac current, and the current is applied to the compensation loop. The transconductance  $G_{mi}$  is considered unchanged at the frequencies of interest and can be positive or negative depending on circuit implementation. The compensation loop is comprised of the frequency-dependent transconductance  $G_m(s)$ , in negative feedback configuration, and supplies the load impedance  $z_L(s)$ .

Considering the feedback network of the three model types, for the type I model the feedback elements in Fig. 1(a) connect the output of  $G_m(s)$  to its input directly, whereas for type II in Fig. 1(b) the one-way current buffer with constant  $G_{mC}$  (and an input impedance of  $1/G_{mC}$ ) buffers the feedback current, and prevents the feedforward current flowing to the output through  $z_A(s)$ . Finally, the type III model in Fig. 1(c), where the input transconductance is broken into identical  $G_{mi}/2$  stages, can be seen as a combination of the two other models in Fig. 1(a) and (b).

Note that also a type IV model could be considered, which uses a voltage buffer inside the feedback loop instead of the current buffer [7], [64], but presently, especially for the low voltage power supply of the typical application, it is not a practical solution. Moreover, by inspection of Fig. 1, it is apparent that type III model can be seen as a more general topology of type II model and hence could be, in principle, merged. However, since the zeros of the type II model, unlike to type III model, may depend on  $G_m(s)$  (as it will be shown in the next sub-section), we decided to maintain two different models which appear to be more effective from a practical point of view.

In all the cases considered, the symbolic voltage-gain transfer function from  $v_i$  to  $v_o$  can be generally expressed as

$$A_V(s) = \frac{v_o}{v_i} = \frac{A_0}{1 + \frac{s}{|p - 3dB|}} \cdot \frac{N_Z(s)}{D_{NP}(s)}$$

(1)

where  $A_0$  and  $p_{-3dB}$   $p_{-3dB}$  denote the DC voltage gain and the dominant pole, respectively, and  $N_Z(s)$  and  $D_{NP}(s)$  are the zeros and nondominant poles polynomials, respectively, being

$$\lim_{s \to 0} N_Z(s) = \lim_{s \to 0} D_{NP}(s) = 1 \tag{2}$$

The polynomial  $D_{NP}(s)$  contains the most important bandwidth- and stability-limiting pole frequencies, whereas  $N_Z(s)$  contains the zero frequencies which generally may also affect the overall stability, depending of course on their frequency.

A symbolic transfer function in the form of relationship (1) is very helpful for writing all the design expressions in symbolic form. For instance, a symbolic phase margin (PM) expression can then be expressed as

$$PM \approx 90^{\circ} + \tan^{-1} \left( \text{Im} \left[ N \left( jGBW \right) \right] / \text{Re} \left[ N \left( jGBW \right) \right] \right)$$

$$-\tan^{-1} \left( \text{Im} \left[ D_{NP} \left( jGBW \right) \right] / \text{Re} \left[ D_{NP} \left( jGBW \right) \right] \right) \tag{3}$$

where GBW is the gain-bandwidth product and is given by  $A_0 \cdot p_{-3dB}$ .

Moreover, to take advantage of the model treated, it is conventionally assumed that the amplifier contains linear elements only. Hence, the transfer function would be fractional, and contains unchanged coefficients for N(s) and  $D_{NP}(s)$  expressions:

$$z_A(s) = \frac{nz_A(s)}{dz_A(s)} \tag{4}$$

$$z_B(s) = \frac{nz_B(s)}{dz_B(s)}$$

(5)

$$z_L(s) = \frac{nz_L(s)}{dz_L(s)} \tag{6}$$

$$z_{A}(s) = \frac{nz_{A}(s)}{dz_{A}(s)}$$

$$z_{B}(s) = \frac{nz_{B}(s)}{dz_{B}(s)}$$

$$z_{L}(s) = \frac{nz_{L}(s)}{dz_{L}(s)}$$

$$G_{m}(s) = \frac{nG_{m}(s)}{dG_{m}(s)}$$

$$(4)$$

$$(5)$$

$$(6)$$

Analysis of the transfer function provides insightful knowledge on the behavior of the frequency compensation applied. To this end, N(s) and  $D_{NP}(s)$  in their most general form must be evaluated. Thus, instead of using a direct transfer function evaluation, or the adoption or other approaches such as Rosenstark method [57] or Signal Flow Analysis [58], the analysis in the rest of this section is devoted to directly derive N(s) and  $D_{NP}(s)$  through a depth circuit observation and practical considerations. In particular, it will be shown that the zeros originate from the feedforward pathways and the shunt elements within the input-output pathway, whereas the location of nondominant poles is mainly governed by the compensation loop.

#### **B.** ANALYSIS OF ZEROS

It is possible to formulate the transfer function zero expressions by revisiting the conditions leading to a 'zero'. A zero is a complex frequency,  $s_{zi}$ , where  $v_o$  evaluated at its value is equal to zero (i.e.,  $v_o(s_{zi}) = 0$ ), and it can be regarded as the input frequency  $s_{zi}$  that yields a virtual grounded output. Different scenarios end up with such result for the models under consideration. In particular, considering the type I model in Fig. 1(a), we found the zeros under the following conditions:

a) an input frequency that generates a load impedance equal to zero (i.e.,  $z_L(s) = 0$ ), which in turn means

$$nz_L(s) = 0 (8)$$

b) the input of the  $G_m(s)$  stage,  $v_F$ , equal to zero, (i.e.,  $z_B(s) = 0$ ), or in other terms

$$nz_{R}(s) = 0 (9)$$

c) a current through the load impedance equal to zero; this case corresponds to a complex frequency where the current supplied by the  $G_m(s)$  becomes equal to the current of the feedback element  $z_A(s)$  (i.e.,  $G_m(s)$ ).  $v_F$  equal to  $v_F/z_A(s)$ ), which means

$$\frac{dz_A\left(s\right)}{nz_A\left(s\right)} - \frac{nG_m\left(s\right)}{dG_m\left(s\right)} = 0\tag{10}$$

yielding

$$\frac{dz_A\left(s\right) \cdot dG_m\left(s\right) - nz_A\left(s\right) \cdot nG_m\left(s\right)}{nz_A\left(s\right) \cdot dG_m\left(s\right)} = 0 \tag{11}$$

Thus, any zero of the type I model transfer function is obtained from one of the three above cases and combining them in a general and compact form we get

$$N_{1}(s) = nz_{L}(s) \cdot nz_{B}(s)$$

$$\cdot [dz_{A}(s) \cdot dG_{m}(s) - nz_{A}(s) \cdot nG_{m}(s)] \quad (12)$$

The two zero expressions in (8) and (9) are valid for the amplifier model type II illustrated in Fig. 1(b). The one-way current buffer,  $G_{mC}$ , however, prevents  $z_A(s)$  draining any current from the input of  $G_m(s)$  Hence, since  $G_m(s)$ .  $v_F = 0$ , instead of Eq. (10) we have

$$nG_m(s) = 0 (13)$$

The series combination of  $z_A(s)$  and  $1/G_{mC}$  is connected to the output and generates additional zeros. The output will be grounded when the series impedance of the two elements becomes zero (i.e.,  $z_A(s) + 1/G_{mC} = 0$ ) and we can write

$$G_{mC}nz_A(s) + dz_A(s) = 0 (14)$$

Thus, the generalized zero expression of model type II is given by

$$N_2(s) = nz_L(s) \cdot nz_B(s) \cdot nG_m(s) \cdot [G_{mC}nz_A(s) + dz_A(s)]$$

$$\tag{15}$$

Equation (8) still holds for the model type III illustrated in Fig. 1(c). Other zero expressions can be, however, found by setting the output voltage to zero. In particular, if  $v_o = 0$ , the voltage  $v_C$  can be expressed in terms of the input voltage,  $v_i$ , as

$$v_C = \frac{G_{mi}}{2} \left[ \frac{z_A(s)}{1 + G_{mC} \cdot z_A(s)} \right] v_i \tag{16}$$

Hence, taking into account the above relation, the feedback voltage,  $v_F$ , is related to  $v_i$  by

$$v_F = \left(G_{mC} \cdot v_C + \frac{G_{mi}}{2} \cdot v_i\right) \cdot z_B(s)$$

$$= \frac{G_{mi}}{2} \cdot \frac{1 + 2G_{mC} \cdot z_A(s)}{1 + G_{mC} \cdot z_A(s)} \cdot z_B(s) \cdot v_i \qquad (17)$$

Thus, applying the current law to the output node yields

$$\frac{v_C}{z_A(s)} - G_m(s) \cdot v_F = 0 \tag{18}$$

and

$$1 - G_m(s) \cdot [1 + 2G_{mC}z_A(s)] \cdot z_B(s) = 0$$

(19)

and the zero equation is expressed by

$$2G_{mC} \cdot nG_{m}(s) \cdot nz_{A}(s) \cdot nz_{B}(s) + nG_{m}(s) \cdot dz_{A}(s) \cdot nz_{B}(s)$$

$$-dG_{m}(s) \cdot dz_{A}(s) \cdot dz_{B}(s) \approx 2G_{mC} \cdot nz_{A}(s) + dz_{A}(s) = 0$$

(20)

where the approximation holds since the first 1 in relationship (19) can be safely neglected with respect to the other terms which are normally much higher (remember that  $G_m(s)$ .  $z_A(s)$  and  $G_{mC}(s)$ .  $z_B(s)$  represent two gains). The symbolic zero expression of the model type III can be written as

$$N_3(s) = nz_L(s) \cdot [2G_{mC} \cdot nz_A(s) + dz_A(s)]$$

(21)

By inspection of the  $N_i(s)$  expressions derived above for different amplifier models, it is worth noting that the feedforward pathways and the shunt elements are responsible for generating a zero.

# C. ANALYSIS OF POLES

Remembering that in a network the natural frequencies, i.e. the poles, only depend on the network topology and component values, but not on the input [59], to evaluate the poles of the transfer function we can calculate the input or the output impedance and take their poles.

Consider the model type I illustrated in Fig. 1(a). The output impedance is that of a typical simple feedback circuit and, consequently, it can be simply evaluated by applying any usual method for impedance evaluation in feedback amplifiers, such as Blackman [60] or modified Rosenstark [57], or even directly. In particular, we get

$$z_{eq}(s) = \frac{z_A(s) + z_B(s)}{1 + G_m(s) \cdot z_B(s)} / / z_L(s)$$

$$= \frac{[z_A(s) + z_B(s)] \cdot z_L(s)}{z_A(s) + z_B(s) + z_L(s) + G_m(s) \cdot z_B(s) \cdot z_L(s)}$$

(22)

Thus, by using (4)-(7), after routine manipulations, the final  $z_{eq}(s)$  can be expressed by

$$z_{eq}(s) = \frac{dG_m(nz_Adz_B + dz_Anz_B)nz_L}{dG_mdz_Adz_Bnz_L + nG_mdz_Anz_Bnz_L + dG_mnz_Adz_Bdz_L}$$

(23)

and hence the pole expression of the transfer function, being the same of the relationship (23), is given by

$$D_{P1}(s) = dG_m dz_A dz_B nz_L + nG_m dz_A nz_B nz_L + dG_m nz_A dz_B dz_L + dG_m dz_A nz_B dz_L$$

(24)

Concerning the type II and type III models, their output impedance is equal<sup>1</sup> and by inspection of Fig. 1(b) or 1(c), observing that to evaluate the output impedance type II and type III models are equivalent to type I if

$$G'_{m}(s) = G_{mC} \cdot z_{B}(s) \cdot G_{m}(s)$$

(25)

$$z_B'(s) = \frac{1}{G_{mC}} \tag{26}$$

are used in the compensation loop instead of  $G_m$  and  $z_B$ , respectively. Thus, from (22) we get<sup>2</sup>

$$z_{eq}(s) = \frac{z_A(s) + z'_B(s)}{1 + G'_m(s) \cdot z'_B(s)} / / z_L(s)$$

$$= \frac{\left[ z_A(s) + z'_B(s) \right] \cdot z_L(s)}{z_A(s) + z'_B(s) + z_L(s) + G'_m(s) \cdot z'_B(s) \cdot z_L(s)}$$

(27)

Therefore, from (24) the denominator of type II and type III models is given by

$$D_{P2}(s)$$

$$= D_{P3}(s) = dG'_m dz_A dz'_B nz_L$$

$$+ nG'_m dz_A nz'_B nz_L + dG'_m nz_A dz'_B dz_L + dG'_m dz_A nz'_B nz_L$$

(28)

Moreover, being

$$nz_B'(s) = 1 (29)$$

$$dz_B'(s) = G_{mC} (30)$$

and

$$nG'_{m}(s) = G_{mC} \cdot nz_{B}(s) \cdot nG_{m}(s)$$

(31)

$$dG'_{m}(s) = dz_{B}(s) \cdot dG_{m}(s) \tag{32}$$

equation (28) becomes

$D_{P2}(s)$   $= D_{P3}(s) = G_{mC}(dG_m dz_A dz_B nz_L + nG_m dz_A nz_B nz_L + dG_m nz_A dz_B dz_L) + dG_m dz_A dz_B dz_L$ (33)

# D. GENERAL TRANSFER FUNCTION

Noticing that the feedback element  $z_A(s)$ , contains generally a series compensation capacitor, which means

$$\lim_{s \to 0} z_A(s) = \infty \tag{34}$$

for any of the proposed models, the symbolic DC gain formula can thus be expressed by

$$A_0 = G_{mi} \cdot G_m(0) \cdot z_B(0) \cdot z_L(0) \tag{35}$$

$^{1}$ We are implicitly assuming for type III model, as it happens for real cases, that the output impedance of the upper  $G_{mi}/2$  transcoductance can be neglected (i.e., much higher than  $1/G_{mC}$ ).

<sup>2</sup>Using (25) and (26), eq. (27) reduces to  $\frac{z_A(s)+z_B'(s)}{1+G_m(s)\cdot z_B(s)}//z_L(s)$  but this form is less practical at this moment.

To ensure that condition (2) is met for the type of the transfer function in (1), the standard  $N_Z(s)$  should be implied in the form of  $(1 + \alpha s + \beta s^2 + \ldots)$ , while inspecting the N(s) expressions derived in subsection II.B we find a constant term. Hence, we can write that

$$N_{Zi}(s) = \frac{N_i(s)}{N_i(0)}$$

(36)

where i is equal to 1, 2 or 3.

Concerning eqs. (24) and (33), to represent the transfer function as in (1), despite  $D_{Pi}(s)$ , with i from 1 to 3, contains all the amplifier poles, we have to identify the dominant pole and factorize it. At this purpose we can consider that the dominant pole,  $p_{-3\text{dB}}$ , can be evaluated by applying the open-circuit time constant method [62] and, since it is typically imposed by exploiting the Miller effect on the  $C_C$ , of  $z_A(s)$  [49], we can write (37), as shown at the bottom of the next page, where  $C_B$  and  $C_L$  are the capacitive contribute of  $z_B(s)$  and  $z_L(s)$ .

The function  $D_{Pi}(s)$  in a general form can be written as

$$D_{Pi}(s) = a_0 + a_1 s + a_2 s^2 + \ldots + a_n s^n$$

(38)

where, of course,

$$a_0 = D_{Pi}(0)$$

(39)

Thus, remembering that a compensated amplifier has a dominant pole approximated by

$$p_{-3dB} = \frac{D_{Pi}(0)}{a_1} \tag{40}$$

the transfer function related to the non-dominant poles only with the unitary constant term can be expressed by

$$D_{NPi}(s) \approx \frac{D_{Pi}(s)}{D_{Pi}(0)\left(1 + \frac{s}{p - 3dB}\right)}$$

$$= 1 + \frac{a_2}{a_1}s + \frac{a_3}{a_1}s^2 + \dots + \frac{a_n}{a_1}s^{n-1}$$

(41)

In conclusion, expression (42) summarizes the analysis of this section, providing a symbolic voltage-gain transfer function expression for most multistage amplifiers used in the literature

$$A_{V}(s) = A_{0} \frac{N_{i}(s)}{N_{i}(0)} \frac{D_{Pi}(0)}{D_{Pi}(s)} = \frac{A_{0}}{1 + \frac{s}{|p-3dB|}} \cdot \frac{N_{Zi}(s)}{D_{NPi}(s)}$$

$$\approx \frac{GBW}{s} \cdot \frac{N_{Zi}(s)}{D_{NPi}(s)}$$

(42)

where i is from 1 to 3 and  $N_i(s)$  and  $D_{Pi}(s)$  are summarized in Table 1.

# E. APPROXIMATED POLE EXPRESSIONS

A useful approximation can be obtained by noting that in a compensated amplifier the non-dominant poles are at frequencies higher than the transition frequency. They are, consequently, much higher than the dominant pole that is usually entirely set by the Miller compensation capacitor. Then, at the frequency of the non-dominant poles we can assume the compensation capacitor is short-circuited.

**TABLE 1.** Approximated expressions.

| i | $N_i(s)$                                                                                                                 |

|---|--------------------------------------------------------------------------------------------------------------------------|

| 1 | $nz_L(s) \cdot nz_B(s) \cdot \left[ dz_A(s) dG_m(s) - nz_A(s) nG_m(s) \right]$                                           |

| 2 | $nz_L(s) \cdot nz_B(s) \cdot nG_m(s) \cdot \left[G_{mC}nz_A(s) + dz_A(s)\right]$                                         |

| 3 | $nz_L(s) \cdot \left[ 2G_{mC}nz_A(s) + dz_A(s) \right]$                                                                  |

| i | $D_{Pi}(s)$                                                                                                              |

| 1 | $G_m dz_A dz_B nz_L + nG_m dz_A nz_B nz_L + dG_m nz_A dz_B dz_L + dG_m dz_A nz_B dz_L$                                   |

| 3 | $G_{mC}\left(dG_{m}dz_{A}dz_{B}nz_{L}+nG_{m}dz_{A}nz_{B}nz_{L}+dG_{m}nz_{A}dz_{B}dz_{L}\right)+dG_{m}dz_{A}dz_{B}dz_{L}$ |

| i | Approximated $D_{NGNP}(s)$                                                                                               |

| 1 | $dG_m dz_B nz_L + nG_m nz_B nz_L + dG_m z_{A \text{lim}} dz_B dz_L + dG_m nz_B dz_L$                                     |

| 3 | $G_{mC}\left(dG_{m}dz_{B}nz_{L}+nG_{m}nz_{B}nz_{L}+dG_{m}z_{A\mathrm{lim}}dz_{B}dz_{L}\right)+dG_{m}dz_{B}dz_{L}$        |

\*the dependence on s is not explicated for length reasons

The compensation capacitor is inside  $z_A(s)$ , thus the assumption of short-circuited compensation capacitor means to evaluate

$$z_{A \lim} = \lim_{s \to \infty} z_A(s) \tag{43}$$

and substitute it to  $z_A(s)$  in (24) and (32) to achieve the equation for the non-dominant poles. In particular, rewriting (24) and (33) by introducing  $z_{Alim}$  we respectively get

$D_{P \lim_{s \to \infty} 1}(s)$

$$= dz_A D_{NGPN1}(s) = dz_A (dG_m dz_B nz_L + nG_m nz_B nz_L + dG_m z_A \lim_{L} dz_B dz_L + dG_m nz_B dz_L)$$

$$(44)$$

$$D_{P \lim 2}(s)$$

$$= D_{P \lim 3}(s) = dz_A D_{NGPN3}(s)$$

$$= dz_A [G_{mC}(dG_m dz_B nz_L + nG_m nz_B nz_L + dG_m z_A \lim_{L} dz_B dz_L) + dG_m nz_B dz_L]$$

$$(45)$$

where  $D_{NGNPi}(s)$  are equations with only the non-dominant poles, but not in the required form. Indeed, note that the dominant pole of the transfer function can be approximated by

$$1 + \frac{s}{|p - y_{dR}|} \approx \frac{s}{|p - y_{dR}|} \approx dz_A D_{NGNPi}(0)$$

(46)

Then, the expression for the non-dominant poles with one as constant term is given by

$$D_{NPi}(s) = \frac{D_{NGNPi}(s)}{D_{NGNPi}(0)}$$

(47)

Despite being useful, especially when a Miller capacitance or a nulling resistance in the compensation path is adopted (i.e., for amplifiers that are represented with type I model), this approximation may lead to errors when current buffers are introduced in the compensation path. As such, the small input resistance of the current buffer in series makes quite important the size of the Miller capacitance and its ac current on the location of non-dominant poles. Approximated  $D_{NGNPi}(s)$  are summarized in Table 1.

# **III. APPLICATIONS OF THE PROPOSED METHODOLOGY**

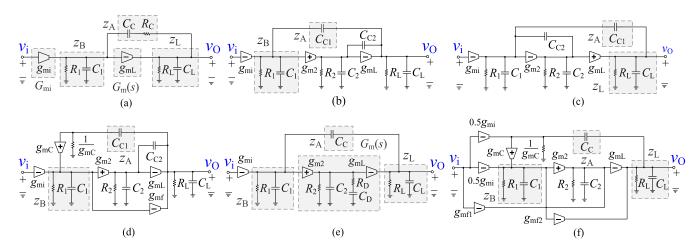

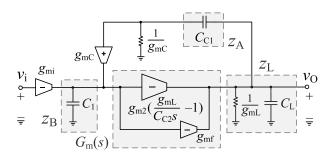

The achieved symbolic transfer function expression can significantly reduce the calculations of OTA transfer function. Fig. 2 presents several well-known circuit diagrams used to realize two-stage and three-stage amplifiers, where resistors, capacitors, and transconductors of different blocks are explicitly represented using conventional notations. In this section, we shall analyze these amplifiers as a typical case of study by using the methodology developed in the previous section based on the models introduced in Fig. 1 and summarized by equation (42) and Table 1.

# A. MILLER COMPENSATION WITH NULLING RESISTOR

As the classical method to stabilize a two-stage amplifier [51], Miller compensation places a compensation capacitor among the input and output of the second stage to dominate the pole of the first stage output. The original Miller compensation is mostly avoided since it suffers from stability problems due to a right-half plane (RHP) zero and improvements that avoid the RHP are usually adopted [51], [63].

The most known and used solution that allows to avoid the RHP is based on a nulling resistor  $(R_C)$  which is therefore

$$p_{-3dB} = \frac{-1}{z_B(0) C_B + z_L(0) C_L + [z_B(0) + z_L(0) + z_B(0) G_m(0) z_L(0)] C_C}$$

(37)

FIGURE 2. Block diagrams of multistage amplifiers; (a) Miller compensation with nulling resistor; (b) NMC; (c) RNMC; (d) AFFC; (e) IAC; (f) CFCC.

placed in series with the compensation capacitor  $(C_C)$  to create a negative zero according to the circuit diagram shown in Fig. 2(a). In addition to the input  $g_{mi}$  stage with the output capacitor  $(C_1)$  and resistor  $(R_1)$ , the block diagram of Fig. 2(a) is composed of an inverting  $g_{mL}$  stage with the feedback  $R_C$  and  $C_C$ , driving  $C_L$  and  $R_L$  of the amplifier. This structure is analogous to the model type I discussed in Section 2, when taking into consideration  $G_{mi} = g_{mi}$ , and the following relations for remaining components:

$$z_A(s) = \frac{nz_A}{dz_A} = \frac{1 + R_C C_C s}{C_C s}$$

(48)

$$z_B(s) = \frac{nz_B}{dz_B} = \frac{R_1}{1 + R_1 C_1 s}$$

(49)

$$G_m(s) = \frac{nG_m}{dG_m} = \frac{g_{mL}}{1} \tag{50}$$

$$z_L(s) = \frac{nz_L}{dz_L} = \frac{R_L}{1 + R_L C_L s}$$

(51)

The DC gain and dominant pole are obtained from (35) and (37), respectively. Moreover, usually (37) can be simplified into

$$p_{-3dB} \approx \frac{-1}{z_B(0) G_m(0) z_L(0) C_C + z_L(0) C_L}$$

$$= \frac{-1}{g_{mL} R_1 R_L C_C + R_L C_L}$$

(52)

The zeros expressions are easily derived as

$$N_{z1}(s) = \frac{N_1(s)}{N_1(0)} = \left[1 + C_C\left(R_C - \frac{1}{g_{mL}}\right)s\right]$$

(53)

Concerning the non-dominant poles, we can use the approximated expression (44). Thus, approximating the first term of  $D_{P1}(s)$  as

$$dG_m dz_B nz_L = R_L + R_1 g_{mL} R_L + R_C + R_1 \approx R_1 g_{mL} R_L$$

$$(54)$$

and being

$$z_{A \lim} = \lim_{s \to \infty} z_A(s) = R_C \tag{55}$$

we get

$$D_{NGPN1}(s)$$

$$= (dG_m dz_B nz_L + nG_m nz_B nz_L + dG_m z_A \lim_{l \to \infty} dz_B dz_L + dG_m nz_B dz_L)$$

$$= R_1 g_{mL} R_L + (R_1 C_1 R_L + R_1 C_1 R_C + R_L C_L R_1 + R_L C_L R_C) s$$

$$+ R_1 C_1 R_L C_L R_C s^2$$

(56)

which from (47) gives the non-dominant pole function in the required form

$$D_{NP1}(s) = 1 + \left[ \frac{C_1}{g_{mL}} \left( 1 + \frac{R_C}{R_L} \right) + \frac{C_L}{g_{mL}} \left( 1 + \frac{R_C}{R_1} \right) \right] s + C_1 C_L \frac{R_C}{g_{mL}} s^2$$

(57)

It is worth noting that application of the accurate relationship (41) only adds the negligible term,  $C_LC_1/C_Cg_{mL}$ , thus yielding the same result.

# **B. NESTED MILLER COMPENSATION**

Nested Miller compensation is an advanced variant of the Miller compensation presented formerly for three-stage amplifiers [3], [5], [6]. Fig. 2(b) illustrates the circuit schematic of a three-stage NMC amplifier, comprising from an inverting first stage, a non-inverting second stage, and an inverting third stage modeled by their equivalent transconductor ( $g_{mi}$ ,  $g_{m2}$  and  $g_{mL}$ ), output stage resistor ( $R_1$ ,  $R_2$  and  $R_L$ ) and output stage capacitor ( $C_1$ ,  $C_2$  and  $C_L$ ).

The two compensation capacitors of NMC, i.e.  $C_{C1}$  and  $C_{C2}$ , connect the third stage output to the first and the second stage outputs, respectively. The capacitor  $C_{C1}$  creates the main pole of the amplifier, while  $C_{C2}$  controls the quality factor of the non-dominant poles. This structure is analogous to the model type I in Fig. 1(a), when considering

$$z_A(s) = \frac{1}{C_{C1}s} \tag{58}$$

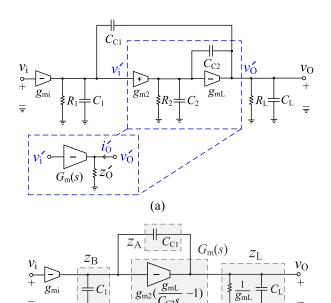

FIGURE 3. Structure of NMC three-stage amplifier as model type I; (b) equivalent high-frequency model.

(b)

$$z_B(s) = R_1 / \frac{1}{C_1 s} \approx \frac{1}{C_1 s}$$

(59)

where the rightmost approximation in (59) holds if  $R_1C_1s >> 1$ .

The DC gain and the dominant pole can be evaluated from (35) and (37) noting that  $z_B(0) = R_1$ ,  $G_m(0) = g_{m2}g_{mL}R_2$  and  $z_L(0) = R_L$ . Nonetheless, it is essential to evaluate the  $G_m(s)$  and  $z_L(s)$  expressions before the proposed method can be applied to evaluate  $N_{zi}(s)$  and  $D_{NPi}(s)$ . To this end, the elements inside the rectangular dash line in Fig. 3(a) can be represented by an equivalent transconductor  $G_m(s)$ , with input voltage  $v_i$ , output voltage  $v_o$ , and an output impedance of  $z_o$ .

By applying the current law at the output of the second stage, the output current,  $i'_o$  is related to  $v'_i$  and  $v'_o$  by

$$i'_{0} = G_{m}(s) v'_{i} + \frac{v'_{o}}{z'_{o}}$$

$$= g_{m2} \left[ \frac{g_{mL}R_{2} - R_{2}C_{2}s}{1 + R_{2}(C_{C2} + C_{2})s} \right] v'_{i}$$

$$+ C_{C2}s \left[ \frac{1 + g_{mL}R_{2} + R_{2}C_{2}s}{1 + R_{2}(C_{C2} + C_{2})s} \right] v'_{o}$$

(60)

Thus, since typically  $C_{C2} >> C_2$ ,  $R_2C_{C2}s >> 1$  and  $g_{mL} >> C_{C2}s$  we get

$$G_{m}(s) = g_{m2} \frac{g_{mL} - C_{C2}s}{C_{C2}s}$$

$$z_{L}(s) = z'_{o} / /R_{L} / /\frac{1}{C_{L}s} \approx \frac{1}{g_{mL}} / /R_{L} / /\frac{1}{C_{L}s}$$

$$\approx \frac{1}{g_{mL} + C_{L}s}$$

(62)

Due to the impedance  $z_0$  at the output of  $G_m(s)$  the load impedance is modified according to the equivalent high-frequency model of NMC amplifier shown in Fig. 3(b).

By using (58) to (62), being  $N_1(0) = -g_{m2}g_{mL}$ , relationship  $N_{z1}(s)$  is expressed by

$$N_{z1}(s) = \frac{N_1(s)}{N_1(0)} = 1 - \frac{C_{C2}}{g_{mL}}s - \frac{C_{C1}C_{C2}}{g_{m2}g_{mL}}s^2$$

(63)

which is exactly the expression that is found in papers [12]–[14] and textbooks [49], and applying the approximated pole expression, being  $z_{Alim} = 0$  and  $D_{NGNP1}(0) = g_{m2}g_{mL}$ , we get  $D_{NP1}(s)$  as

$$D_{NP1}(s) = \frac{D_{NGNP1}(s)}{D_{NGNP1}(0)}$$

$$= 1 + C_{C2} \frac{g_{mL} - g_{m2}}{g_{m2}g_{mL}} s + C_{C2} \frac{C_L + C_1}{g_{m2}g_{mL}} s^2$$

(64)

In this case application of the accurate relationship (41) only adds the terms  $(C_{C2}C_1/g_{m2}C_{C1})s$  and  $(C_{C2}C_1/g_{m2}g_{mL})$   $(C_{C2}/C_{C1})s^2$  which are negligible. Moreover, neglecting  $C_1$  in the  $s^2$  term, which is typically much lower than  $C_L$ , (64) gives exactly the approximated denominator reported in papers [12]–[14] and textbooks [51].

#### C. REVERSE NESTED MILLER COMPENSATION

When a three-stage amplifier is realized with an inverting first and second stage and a non-inverting last stage, the NMC cannot be applied and the RNMC is adopted (Fig. 2(c)), formerly presented in [6] and analyzed with details in [15]. As compared to NMC, RNMC also shows inherent benefits in terms of speed performance as demonstrated in [64].

An RNMC amplifier diagram is fitted to the generalized model type I, where

$$z_A(s) = \frac{1}{C_{C1}s} \tag{65}$$

$$z_L(s) = R_L / \frac{1}{C_L s} \approx \frac{1}{C_L s}$$

(66)

and considering the generalized  $G_m(s)$  and  $z_B(s)$  found according to Fig. 4. In particular, the elements inside the rectangular dashed box of Fig. 4(a) can be integrated to an equivalent transconductor with input voltage  $v_i$ , output voltage  $v_o$ , and an input impedance  $z_o$ . The voltage  $v_x$  of the second stage output is related to  $v_i$  by

$$v_x' = \left[1 - \frac{1 + g_{m2}R_2 + R_2C_2s}{1 + R_2\left(C_{C2} + C_2\right)s}\right]v_i' \tag{67}$$

The output current  $iv_o$ , can be expressed in terms of  $vv_x$  and  $vv_y$  as

$$i_0' = -g_{mL}v_x' = g_{mL} \left[ \frac{1 + g_{m2}R_2 + R_2C_2s}{1 + R_2(C_{C2} + C_2)s} - 1 \right] v_i'$$

(68)

FIGURE 4. Structure of RNMC three-stage amplifier as model type I; (b) equivalent high-frequency model.

Thus, by using the usual approximations  $(g_{mL}R_1, g_{mL}R_2 >> 1, C_{C2} >> C_2, g_{m2} >> C_2s, R_2C_{C2}s >> 1)$  we get

$$G_{m}(s) = g_{mL} \left[ \frac{1 + g_{m2}R_{2} + R_{2}C_{2}s}{1 + R_{2}(C_{C2} + C_{2})s} - 1 \right]$$

$$\approx g_{mL} \left( \frac{g_{m2}}{C_{C2}s} - 1 \right)$$

(69)

The ratio between  $v_i$  and  $i_i$  should be measured to additionally evaluate  $z_i$  of the new transconductor. Applying the current law at the second stage output,  $z_i$  is calculated as

$$z_{i}' = \frac{v_{i}'}{i_{i}'} = \frac{1}{C_{C2}s} \left[ \frac{1 + R_{2} (C_{C2} + C_{2}) s}{1 + g_{m2}R_{2} + R_{2}C_{2}s} \right]$$

(70)

Fig. 4(b) illustrates the equivalent high-frequency circuit schematic of the RNMC amplifier. The equivalent  $zt_i$  modifies  $zt_i$  of the first stage to

$$z_{B}(s) = \frac{1}{C_{C2}s} \left[ \frac{1 + R_{2} (C_{C2} + C_{2}) s}{1 + g_{m2}R_{2} + R_{2}C_{2}s} \right] / R_{1} / \frac{1}{C_{1}s}$$

$$\approx \frac{1}{g_{m2} + C_{1}s}$$

(71)

From (65), (66), (69) and (71),  $N_{z1}(s)$  is again given by (63), while application of relationship (41) and (24) yields

$$D_{NP1}(s) = 1 + \left(\frac{C_{C2}C_L}{g_{mL}C_{C2}} + \frac{C_{C2}}{g_{mL}} - \frac{C_{C2}}{g_{m2}}\right)s + \frac{C_{C2}(C_L + C_1) + C_LC_1\frac{C_{C2}}{C_{C1}}}{g_{m2}g_{mL}}s^2$$

(72)

Note that in this case  $a_0 = 0$  in (41), but this happens for the approximation adopted in (65), (66), (69) and (71). Neglecting the second-order addends in the  $s^2$  term of (72), as suggested in [15], we find exactly the transfer function reported in [15]. It is worth noting that if we apply the approximated pole expression, where  $z_{Alim} = 0$ , we lack the two terms  $(C_{C2}C_1/g_{m2}C_{C1})s$  and  $(C_1C_{C2}/g_{m2}g_{mL}C_{C1})s^2$ , where the former of the two cannot be considered negligible as compared to the others in (72).

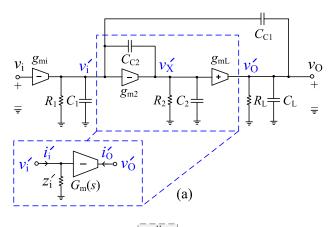

# D. ACTIVE-FEEDBACK FREQUENCY COMPENSATION

Fig. 2(d) illustrates the architecture of the named three-stage AFFC amplifier [16]. It implements an active feedback network from the third stage output through the transconductor  $g_{mC}$ , and the capacitor  $C_{C1}$  to the second stage input (i.e., a NMC with a current buffer in the external loop). Again capacitor  $C_{C2}$  adjusts the quality of the complex poles similar to NMC and RNMC amplifiers. Moreover, it also includes an additional feedforward  $g_{mf}$  stage, which shunts to the main signal pathway comprised from  $g_{m2}$  and  $g_{mL}$ , extending the bandwidth for  $g_{mf} >> g_{m2}$  [39].

The AFFC block diagram is similar to that of model type II for  $G_{mC} = g_{mC}$  and  $G_{mi} = g_{mi}$ , and the combination of the second and the third stages can be analyzed similarly to the approach used for the NMC amplifier in sub section 3.2. The result is, hence, an equivalent  $G_m(s)$  between the first and third stage outputs reported in (61), but including  $g_{mf}$ :

$$G_m(s) \approx \frac{g_{m2}g_{mL} - g_{m2}C_{C2}s}{C_{C2}s} + g_{mf}$$

(73)

and the load impedance given by (62).

Fig. 5 reports the block scheme of the high-frequency AFFC amplifier as a model type II. In addition to  $G_m(s)$  and  $z_L(s)$ , it includes the  $z_A(s)$  and  $z_B(s)$  given by (58) and (59), respectively. Of course, the DC gain and dominant pole are evaluated from (35) and (37), and again the dominant pole can be simplified with (52).

Beginning from (15), and since  $N_2(0) = g_{m2}g_{mL}g_{mC}$ , the zero expressions  $N_{z2}(s)$  is given by

$$N_{z2}(s) = \frac{N_2(s)}{N_2(0)} = \left[1 - \frac{(g_{m2} - g_{mf})C_{C2}}{g_{m2}g_{mL}}s\right] \left(1 + \frac{C_{C1}}{g_{mC}}s\right)$$

(74)

From (41) and (33) (noting that in (41)  $a_0 = 0$ ) we get

$$D_{NP2}(s) = \frac{D_{NGNP2}(s)}{D_{NGNP2}(0)} = 1 + \left[ \frac{1}{g_{mL}} \left( \frac{g_{mf}}{g_{m2}} - 1 \right) + \frac{1}{g_{m2}} \frac{C_1}{C_{C1}} \right] C_{C2}s + \left[ \frac{1}{g_{mL}} \left( 1 + \frac{C_L}{C_{C1}} \right) + \frac{1}{g_{mC}} \right] \frac{C_1 C_{C2}}{g_{m2}} s^2 + \frac{C_1 C_{C2} C_L}{g_{m2} g_{mL} g_{mC}} s^3$$

$$(75)$$

If the approximated expression (44) is used, where  $z_{Alim} = 0$  and  $D_{NGNP1}(0) = g_{m2}g_{mL}g_{mC}$ , we lose in the s term the negligible addend with  $C_1/C_{C2}$ , but also the term with the

FIGURE 5. Block scheme of the three-stage AFFC amplifier as model type II.

ratio  $C_L/C_{C1}$  in the  $s^2$  term. It is worth noting that neglecting in the s term of the denominator the contribute with  $C_1/C_{C2}$  we find that the first non-dominant pole is almost perfectly cancelled by the first zero in (74). Thus (74) and (75) reduce to the relationship reported in the original paper [16].

#### E. SINGLE MILLER CAPACITOR COMPENSATION

A more recent compensation techniques with respect to NMC and RNMC is based on the use of only a single Miller capacitor [26], [27], [29]–[32], [34]–[36], [39]. Since the first paper dates back twenty years ago [11] and another one five years later [22], investigation and application of this kind of strategy is increasing, especially for multistage amplifiers having high capacitive loads, such as [32], [34]–[36] and [39].

Among the various single Miller topologies with only passive components on the compensation loop, one of the most popular topologies named Impedance Adapting Compensation (IAC) [29] is considered in the following. The topology reported in Fig. 2(e) adopts a series R-C network ( $R_D$  and  $C_D$ ) added to the second stage output, to further split the non-dominant real poles.

In order to evaluate the voltage-gain transfer function, the following model parameters have to be used

$$z_A(s) = \frac{1}{C_{C1}s} \tag{76}$$

$$z_B(s) = R_1 / \frac{1}{C_1 s} \approx \frac{1}{C_1 s}$$

(77)

$$z_L(s) = R_L / / \frac{1}{C_L s} \approx \frac{1}{C_L s}$$

(78)

For  $C_D >> C_2$ ,  $R_2 >> R_D$ , and  $R_2C_Ds >> 1$ , the equivalent  $G_m(s)$  is expressed as

$$G_{m}(s) = g_{m2}g_{mL} \left[ R_{2} / / \frac{1}{C_{2}s} / / \left( R_{D} + \frac{1}{C_{D}s} \right) \right]$$

$$\approx g_{m2}g_{mL} \left( \frac{1 + R_{D}C_{D}s}{C_{D}s} \right)$$

(79)

The expressions  $z_B(0) = R_1$  and  $z_L(0) = R_L$  should be used when evaluating the dominant pole and the DC gain from (35) and (37). The zeros are given by the polynomial

$$N_{z1}(s) = \frac{N_1(s)}{N_1(0)} \approx 1 + R_D C_D s - \frac{C_D C_C}{g_{m2} g_{mL}} s^2$$

(80)

and from the approximated pole expression, being  $z_{Alim} = 0$  and  $D_{NGNP1}(0) = g_{m2}g_{mL}$ , we get

$$D_{NP1}(s) \approx 1 + R_D C_D s + \frac{C_D (C_L + C_1)}{g_{m2} g_{mL}} s^2$$

(81)

Note that the precise relationship (41) has one more negligible term  $(C_DC_LC_1/g_{m2}g_{mL}C_C)s^2$ . The resulting transfer function is the same of that reported in [29], even if the order of the numerator and denominator is reduced due to the approximation adopted on  $G_m(s)$  according to (79).

# F. CROSS FEEDFORWARD CASCODE COMPENSATION

Among the amplifier with single Miller compensation the first specifically devoted to high capacitive load was the topology named cross feedforward cascode compensation (CFCC) [31]. A single compensation capacitor with a current buffer realizes an active feedback network to enable driving the ultra-large load capacitors, according to the CFCC diagram in Fig. 2(f). The amplifier also contains two feedforward stages  $g_{mf\,1}$  and  $g_{mf\,2}$ , which improve the large-and small-signal operation [36].

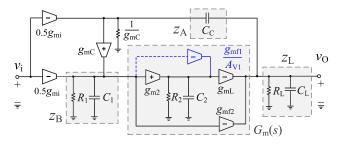

As shown in Fig. 6, we simplify the analysis by transferring the input of  $g_{mf 1}$  from the first stage to the second stage input. Thus, the equivalent transconductor, denoting  $A_{v1}(s) = g_{mi}(R_1/(1/C_1s))$  as the gain of the first stage, is  $g_{mf 1}/A_{v1}$ .

The CFCC architecture matches with the type III model  $(G_{mC} = g_{mC} \text{ and } G_{mi} = g_{mi})$ , with the corresponding  $z_A(s)$ ,  $z_B(s)$  and  $z_L(s)$  are again given by (76), (77) and (78), respectively.

The new transconductor  $g_{mf1}/A_{v1}$ , is now shunted to  $g_{m2}$  resulting to an effective transconductance of  $g_{m2} + g_{mf1}/A_{v1}$ . Hence,  $G_m(s)$  is

$$G_{m}(s) = \left(g_{m2} + \frac{g_{mf1}}{A_{\nu 1}}\right) g_{mL} \left(R_{2} / / \frac{1}{C_{2}s}\right) + g_{mf2}$$

$$\approx g_{m2} g_{mL} \frac{R_{2}}{1 + R_{2}C_{2}s}$$

(82)

Being  $N_3(0) = 2g_{mC}$ ,  $N_{73}(s)$  yields

$$N_{z3}(s) = \frac{N_3(s)}{N_3(0)} = 1 + \frac{C_C}{2g_{mC}}s$$

(83)

and from (41) with (33) we get

$$D_{NP3}(s) = 1 + \frac{C_1 \left(1 + \frac{C_L}{C_C}\right)}{g_{m2}g_{mL}R_2}s + \left[\frac{C_1C_2 \left(1 + \frac{C_L}{C_C}\right)}{g_{m2}g_{mL}} + \frac{C_1C_L}{g_{m2}g_{mL}g_{mC}R_2}\right]s^2 + \frac{C_1C_2C_L}{g_{m2}g_{mL}g_{mC}}s^3$$

(84)

Relationship (83) and (84) gives zeros and non-dominant poles also reported in [31], even if the results are more accurate since in the original manuscript additional approximations are done from the assumption that  $C_L$  is much higher than  $C_C$ . It is worth noting that, in this case in

| Метнор     | MODEL<br>TYPE | $G_{mC}$ | $z_A(s) = \frac{nz_A}{dz_A}$ | $z_{B}(s) = \frac{nz_{B}}{dz_{B}}$   | $G_{m}(s) = \frac{nG_{m}}{dG_{m}}$                                  | $z_L(s) = \frac{nz_L}{dz_L}$       |

|------------|---------------|----------|------------------------------|--------------------------------------|---------------------------------------------------------------------|------------------------------------|

| MCNR       | I             | _        | $R_C + \frac{1}{C_C s}$      | $\approx R_1  /  /  \frac{1}{C_1 s}$ | $g_{mC}$                                                            | $\approx R_L / / \frac{1}{C_L s}$  |

| NMC        | I             | _        | $\frac{1}{C_{C1}s}$          | $\approx \frac{1}{C_1 s}$            | $\approx g_{m2} \left( \frac{g_{mL}}{C_{C2}s} - 1 \right)$          | $\approx \frac{1}{g_{mL} + C_L s}$ |

| RNMC       | I             | _        | $\frac{1}{C_{C1}s}$          | $\approx \frac{1}{g_{m2} + C_1 s}$   | $\approx g_{m2} \left( \frac{g_{mL}}{C_{C2}s} - 1 \right)$          | $\approx \frac{1}{g_{mL} + C_L s}$ |

| AFFC       | II            | $g_{mC}$ | $\frac{1}{C_C s}$            | $\approx \frac{1}{C_1 s}$            | $\approx g_{m2} \left( \frac{g_{mL}}{C_{C2}s} - 1 \right) + g_{mf}$ | $\approx \frac{1}{g_{mL} + C_L s}$ |

| IAC (SMC)  | I             | _        | $\frac{1}{C_C s}$            | $\approx \frac{1}{C_1 s}$            | $\approx g_{m2}g_{mL}\left(R_D + \frac{1}{C_D s}\right)$            | $\approx \frac{1}{C_L s}$          |

| CFCC (SMC) | III           | $g_{mC}$ | $\frac{1}{C_C s}$            | $\approx \frac{1}{C_1 s}$            | $\approx \frac{g_{m2}g_{mL}R_2}{1 + R_2C_2s} + g_{mf2}$             | $pprox rac{1}{C_L s}$             |

TABLE 2. Summary of the model type and model parameters of the amplifiers considered in Section III.

FIGURE 6. Equivalent block diagram of CFCC amplifier as model type III.

which the compensation loop has an active component, the approximated pole expression may be not sufficiently accurate since it lacks the two terms  $(C_L C_1/g_{m2}g_{mL}R_2C_C)s$  and  $(C_L C_1/g_{m2}g_{mL}C_C)s^2$ .

# IV. COMPARISON AND REMARK ON THE ANALYZED MODELS

Table 2 summarizes the model parameters of the compensation schemes analyzed in Section III. By inspection of Table 2, it is apparent that, regardless of the amplifier model, the main difference between different schemes is from the perspective of  $G_m(s)$ . It affects the entire features of the amplifier with frequency compensation and results in many advantages and disadvantages in terms of power and area. Of course, the type of the model is another factor that impacts considerably the operation of an amplifier.

Moreover, from Table 2, it is evident that NMC and AFFC, and IAC and CFCC have similar model parameters. The differences of the amplifier models, however, enhance the operation of the AFFC and CFCC topologies over their counterparts. Indeed, for identical model parameters, both models type II and III employ a series  $G_{mC}$  with  $z_A(s)$ , a property that leads to superior operation as compared to model type I, for identical parameters. This can be demonstrated by investigating the pole expressions of the three models.

In particular, looking into (24), among the four terms appearing in  $D_{P1}(s)$  the factor  $nG_m dz_A nz_B nz_L$  is typically the term with the lowest order, as it contains three nominators that are mostly constant (see Table 2). And considering this condition, we can factorize the terms in (24) that can be rearranged as

$$D_{P1}(s) = nG_m dz_A nz_B nz_L \left[ 1 + \frac{1}{G_m(s) z_B(s)} \left( 1 + \frac{z_A(s) + z_B(s)}{z_L(s)} \right) \right]$$

(85)

For the same reason, the order of  $G_{mC}nG_{m}dz_{A}nz_{B}nz_{L}$  term is mostly the lowest in the  $D_{P2,3}(s)$  of models type II and III. Thus, factorizing this term in (33), yields

$$D_{P2,3}(s) = G_{mC} n G_m dz_A n z_B n z_L \left[ 1 + \frac{1}{G_m(s) z_B(s)} \left( 1 + \frac{z_A(s) + 1/G_{mC}}{z_L(s)} \right) \right]$$

(86)

Since typically  $z_B(s) >> 1/G_{mC}$ , the models type II and III generate larger nondominant poles for identical  $C_L$  (i.e.,  $z_L(s)$ ) and  $C_C$  (i.e.,  $z_A(s)$ ),  $z_B(s)$  and  $G_m(s)$  of the model type I.

The pole expressions in (85) and (86) also suggest the following design rules for improving the performance when the load and compensation capacitors are known a priori (unchanged  $z_L(s)$  and  $z_A(s)$ , respectively):

- 1. The impedance  $z_B(s)$ , of the first stage should be increased to reduce the second term of the standard pole expressions, thereby pushing the nondominant poles to higher frequencies (this can be accomplished by trying to further reduce the parasitic output capacitor  $C_1$  of the first stage).

- 2. The second term inside the brackets in (83) and (84) can be suppressed by further enlarging  $G_m(s)$ . This can be made possible by increasing  $G_m(0)$ , and by pushing further the nondominant poles of  $G_m(s)$  to higher frequencies.

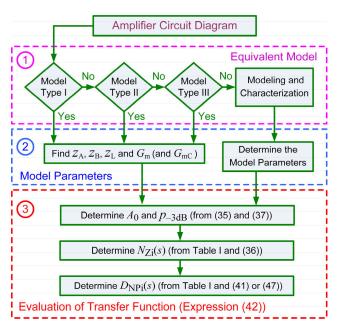

FIGURE 7. Flowchart to apply the proposed methodology.

For all the models proposed in Fig. 1, the zeros of  $z_L(s)$  will be also the same zeros of the transfer function. Such zeros are, indeed, very common in low-dropout regulators (LDOs) [64]–[66]. The zeros of the models type I and II may depend on  $G_m(s)$ , contrary to model type III which does not contain a zero related to  $G_m(s)$ . An advantage of model type II is its potential to generate a LHP zero at frequencies lower than that of model type III, which can be concluded by comparing the zero expressions appeared for these models in (15) and (21). More LHP zeros might be generated by model type II via  $G_m(s)$  and  $z_B(s)$ .

# V. CONCLUSION

A simple methodology to quickly carry out a closed-form expression for the symbolic transfer function of multistage amplifiers with frequency compensation is proposed.

The method can be applied to any amplifier that can be modelled through the general models reported in Fig.1, which, to the best of the authors' knowledge, unless for the old and not used case where a voltage buffer is used [7], allows to represent all the different solution reported in the literature so far. Anyway, it can also be simply extended to other novel and original topologies that cannot be represented by the model in Fig. 1, by simply following the procedure described in Section II for the three type models.

While simplifying the fundamental task of symbolic analysis of an amplifier, the methodology gives an insightful view into the operation of the applied frequency compensation network, offering design rules for improving the performance when the load and compensation capacitors are known a priori. The proposed method is validated through the analysis of a number of the widely adopted amplifiers found in the

literature and it is shown that, in all cases, the same transfer function reported in the original paper is obtained.

To sum up, the main advantages of the proposed methodology are as follows:

1. It happens frequently that, after writing several pages of the small-signal equations for a multistage amplifier, the designer gets confused by the theoretical complications and is forced to get back and check the results again. The same problem led to different forms of transfer functions with inaccurate results in the literature, some of which happen to be even incorrect. With the proposed systematic solution, the designer will not deal with the lengthy and complex small-signal equations of the amplifier. They should only specify the amplifier's model and find the elements before using the proposed symbolic transfer function. This is equivalent to breaking a difficult problem into several simple and easy steps.

With the aim of providing the reader with a guideline to apply the proposed methodology, Fig. 7 show a flowchart that summarizes the steps to follow in order to carry out the transfer function.

Modeling the transfer function of several amplifiers in the form of a single symbolic equation paves the way to compare their properties easily. Some results can be found in Section IV where the terms inside the symbolic transfer functions are compared.

# **REFERENCES**

- D. Senderowicz, D. A. Hodges, and P. R. Gray, "High-performance NMOS operational amplifier," *IEEE J. Solid-State Circuits*, vol. SSC-13, no. 6, pp. 760–766, Dec. 1978.

- [2] W. C. Black, D. J. Allstot, and R. A. Reed, "A high performance low power CMOS channel filter," *IEEE J. Solid-State Circuits*, vol. SSC-15, no. 6, pp. 929–938, Dec. 1980.

- [3] E. M. Cherry, "Nested differentiating feedback loops in simple audio amplifiers," J. Audio Eng. Soc., vol. 30, pp. 295–305, May 1982.

- [4] B. K. Ahuja, "An improved frequency compensation technique for CMOS operational amplifiers," *IEEE J. Solid-State Circuits*, vol. SSC-18, no. 6, pp. 629–633, Dec. 1983.

- [5] M. Fonderie and J. Huijsing, Design of Low-Voltage Bipolar Operational Amplifiers. New York, NY, USA: Academic, 1993.

- [6] R. G. H. Eschauzier and J. H. Huijsing, Frequency Compensation Techniques for Low-Power Operational Amplifiers. New York, NY, USA: Academic, 1995.

- [7] G. Palmisano and G. Palumbo, "An optimized compensation strategy for two-stage CMOS op amps," *IEEE Trans. Circuits Syst. I, Fundam. Theory Appl.*, vol. 42, no. 3, pp. 178–182, Mar. 1995.

- [8] G. Palmisano and G. Palumbo, "A compensation strategy for two-stage CMOS opamps based on current buffer," *IEEE Trans. Circuits Syst. I, Fundam. Theory Appl.*, vol. 44, no. 3, pp. 257–262, Mar. 1997.

- [9] F. You, S. H. K. Embabi, and E. Sanchez-Sinencio, "Multistage amplifier topologies with nested G<sub>m</sub>-C compensation," *IEEE J. Solid-State Circuits*, vol. 32, no. 12, pp. 2000–2011, Dec. 1997.

- [10] H.-T. Ng, R. M. Ziazadeh, and D. J. Allstot, "A multistage amplifier technique with embedded frequency compensation," *IEEE J. Solid-State Circuits*, vol. 34, no. 3, pp. 339–347, Mar. 1999.

- [11] K. N. Leung, P. K. T. Mok, W.-H. Ki, and J. K. O. Sin, "Three-stage large capacitive load amplifier with damping-factor-control frequency compensation," *IEEE J. Solid-State Circuits*, vol. 35, no. 2, pp. 221–230, Feb. 2000.

- [12] K. N. Leung and P. K. T. Mok, "Nested Miller compensation in low-power CMOS design," *IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process.*, vol. 48, no. 4, pp. 388–394, Apr. 2001.

- [13] K. N. Leung and P. K. T. Mok, "Analysis of multistage amplifier-frequency compensation," *IEEE Trans. Circuits Syst. I, Fundam. Theory Appl.*, vol. 48, no. 9, pp. 1041–1056, Sep. 2001.

- [14] G. Palumbo and S. Pennisi, "Design methodology and advances in nested-Miller compensation," *IEEE Trans. Circuits Syst. I, Fundam. Theory Appl.*, vol. 49, no. 7, pp. 893–903, Jul. 2002.

- [15] R. Mita, G. Palumbo, and S. Pennisi, "Design guidelines for reversed nested Miller compensation in three-stage amplifiers," *IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process.*, vol. 50, no. 5, pp. 227–233, May 2003.

- [16] H. Lee and P. K. T. Mok, "Active-feedback frequency-compensation technique for low-power multistage amplifiers," *IEEE J. Solid-State Circuits*, vol. 38, no. 3, pp. 511–520, Mar. 2003.

- [17] K.-P. Ho, C.-F. Chan, C.-S. Choy, and K.-P. Pun, "Reversed nested Miller compensation with voltage buffer and nulling resistor," *IEEE J. Solid-State Circuits*, vol. 38, no. 10, pp. 1735–1738, Oct. 2003.

- [18] H. Lee and P. K. T. Mok, "Advances in active-feedback frequency compensation with power optimization and transient improvement," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 51, no. 9, pp. 1690–1696, Sep. 2004.

- [19] P. J. Hurst, S. H. Lewis, J. P. Keane, F. Aram, and K. C. Dyer, "Miller compensation using current buffers in fully differential CMOS two-stage operational amplifiers," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 51, no. 2, pp. 275–285, Feb. 2004.

- [20] X. Peng and W. Sansen, "AC boosting compensation scheme for low-power multistage amplifiers," *IEEE J. Solid-State Circuits*, vol. 39, no. 11, pp. 2074–2079, Nov. 2004.

- [21] X. Peng and W. Sansen, "Transconductance with capacitances feedback compensation for multistage amplifiers," *IEEE J. Solid-State Circuits*, vol. 40, no. 7, pp. 1514–1520, Jul. 2005.

- [22] X. Fan, C. Mishra, and E. Sánchez-Sinencio, "Single Miller capacitor frequency compensation technique for low-power multistage amplifiers," *IEEE J. Solid-State Circuits*, vol. 40, no. 3, pp. 584–592, Mar. 2005.

- [23] A. D. Grasso, G. Palumbo, and S. Pennisi, "Three-stage CMOS OTA for large capacitive loads with efficient frequency compensation scheme," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 53, no. 10, pp. 1044–1048, Oct. 2006.

- [24] A. D. Grasso, G. Palumbo, and S. Pennisi, "Advances in reversed nested Miller compensation," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 54, no. 7, pp. 1459–1470, Jul. 2007.

- [25] A. D. Grasso, G. Palumbo, and S. Pennisi, "Analytical comparison of frequency compensation techniques in three-stage amplifiers," *Int. J. Circuit Theory Appl.*, vol. 36, no. 1, pp. 53–80, Jan. 2008.

- [26] S. O. Cannizzaro, A. D. Grasso, G. Palumbo, and S. Pennisi, "Single Miller capacitor frequency compensation with nulling resistor for threestage amplifiers," *Int. J. Circuit Theory Appl.*, vol. 36, no. 7, pp. 825–837, Oct. 2008.

- [27] S. Guo and H. Lee, "Single-capacitor active-feedback compensation for small-capacitive-load three-stage amplifiers," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 56, no. 10, pp. 758–762, Oct. 2009.

- [28] H. Aminzadeh, "Three-stage nested-Miller-compensated operational amplifiers: Analysis, design, and optimization based on settling time," Int. J. Circuit Theory Appl., vol. 39, no. 6, pp. 573–587, Jun. 2011.

- [29] X. Peng, W. Sansen, L. Hou, J. Wang, and W. Wu, "Impedance adapting compensation for low-power multistage amplifiers," *IEEE J. Solid-State Circuits*, vol. 46, no. 2, pp. 445–451, Feb. 2011.

- [30] S. Guo and H. Lee, "Dual active-capacitive-feedback compensation for low-power large-capacitive-load three-stage amplifiers," *IEEE J. Solid-State Circuits*, vol. 46, no. 2, pp. 452–464, Feb. 2011.

- [31] S. S. Chong and P. K. Chan, "Cross feedforward cascode compensation for low-power three-stage amplifier with large capacitive load," *IEEE J. Solid-State Circuits*, vol. 47, no. 9, pp. 2227–2234, Sep. 2012.

- [32] Z. Yan, P.-I. Mak, M.-K. Lau, and R. P. Martins, "A 0.016-mm<sup>2</sup> 144-μ W three-stage amplifier capable of driving 1-to-15 nF capacitive load with >0.95-MHz GBW," *IEEE J. Solid-State Circuits*, vol. 48, no. 2, pp. 527–540, Feb. 2013.

- [33] H. Aminzadeh, M. Danaie, and W. A. Serdijn, "Hybrid cascode feedforward compensation for nano-scale low-power ultra-area-efficient three-stage amplifiers," *Microelectron. J.*, vol. 44, no. 12, pp. 1201–1207, Dec. 2013.

- [34] M. Tan and W.-H. Ki, "A cascode Miller-compensated three-stage amplifier with local impedance attenuation for optimized complex-pole control," *IEEE J. Solid-State Circuits*, vol. 50, no. 2, pp. 440–449, Feb. 2015.

- [35] A. D. Grasso, G. Palumbo, and S. Pennisi, "High-performance four-stage CMOS OTA suitable for large capacitive loads," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 62, no. 10, pp. 2476–2487, Oct. 2015.

- [36] D. Marano, A. D. Grasso, G. Palumbo, and S. Pennisi, "Optimized active single-Miller capacitor compensation with inner half-feedforward stage for very high-load three-stage OTAs," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 63, no. 9, pp. 1349–1359, Sep. 2016.

- [37] C. Qin, L. Zhang, C. Zhou, L. Zhang, Y. Wang, and Z. Yu, "Dual AC boosting compensation scheme for multistage amplifiers," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 64, no. 8, pp. 882–886, Aug. 2017.

- [38] M. W. Lau, K. H. Mak, K. N. Leung, J. Guo, and W. L. Goh, "Enhanced active-feedback frequency compensation with on-chip-capacitor reduction feature for amplifiers with large capacitive load," *Int. J. Circuit Theory Appl.*, vol. 45, no. 12, pp. 2119–2133, Dec. 2017.

- [39] A. D. Grasso, D. Marano, G. Palumbo, and S. Pennisi, "High-performance three-stage single-Miller CMOS OTA with no upper limit of C<sub>L</sub>," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 65, no. 11, pp. 1529–1533, Nov. 2018.

- [40] H. Aminzadeh, M. M. Valinezhad, and A. D. Grasso, "Global impedance attenuation network for multistage OTAs driving a broad range of load capacitor," *Int. J. Circuit Theory Appl.*, vol. 48, no. 2, pp. 181–197, Feb. 2020.

- [41] G. Nebel, U. Kleine, and H.-J. Pfleiderer, "Symbolic pole/zero calculation using SANTAFE," *IEEE J. Solid-State Circuits*, vol. 30, no. 7, pp. 752–761, Jul. 1995.

- [42] A. Luchetta, S. Manetti, and A. Reatti, "SAPWIN—A symbolic simulator as a support in electrical engineering education," *IEEE Trans. Educ.*, vol. 44, no. 2, p. 9, May 2001.

- [43] W. Daems, G. Gielen, and W. Sansen, "Circuit simplification for the symbolic analysis of analog integrated circuits," *IEEE Trans. Comput.-Aided Design Integr. Circuits Syst.*, vol. 21, no. 4, pp. 395–407, Apr. 2002.

- [44] O. Guerra, J. D. Rodriguez-Garcia, F. V. Fernandez, and A. Rodriguez-Vazquez, "A symbolic pole/zero extraction methodology based on analysis of circuit time-constants," *Analog Integr. Circuits Signal Process.*, vol. 31, pp. 101–118, May 2002.

- [45] G. G. E. Gielen, H. C. C. Walscharts, and W. M. C. Sansen, "ISAAC: A symbolic simulator for analog integrated circuits," *IEEE J. Solid-State Circuits*, vol. 24, no. 6, pp. 1587–1597, Dec. 1989.

- [46] A. D. Grasso, D. Marano, S. Pennisi, and G. Vazzana, "Symbolic factorization methodology for multistage amplifier transfer functions," *Int. J. Circuit Theory Appl.*, vol. 44, no. 1, pp. 38–59, Jan. 2016.

- [47] G. A. Vazzana, A. D. Grasso, and S. Pennisi, "A toolbox for the symbolic analysis and simulation of linear analog circuits," in *Proc. 14th Int. Conf. Synth., Modeling, Anal. Simulation Methods Appl. Circuit Design* (SMACD), Jun. 2017, pp. 1–4.

- [48] M. Shokouhifar and A. Jalali, "Simplified symbolic transfer function factorization using combined artificial bee colony and simulated annealing," Appl. Soft Comput., vol. 55, pp. 436–451, Jun. 2017.

- [49] G. Shi, "Automatic stage-form circuit reduction for multistage opamp design equation generation," ACM Trans. Design Autom. Electron. Syst., vol. 25, no. 1, pp. 1–26, Jan. 2020.

- [50] H. Aminzadeh, "Systematic circuit design and analysis using generalised g<sub>m</sub>/I<sub>D</sub> functions of MOS devices," *IET Circuits, Devices Syst.*, vol. 14, no. 4, pp. 432–443, Jul. 2020.

- [51] G. Palumbo and S. Pennisi, Feedback Amplifiers: Theory and Design. Boston, MA, USA: Springer, 2002.

- [52] K. H. Lundberg, "Internal and external op-amp compensation: A control-centric tutorial," in *Proc. Amer. Control Conf.*, Jun./Jul. 2004, pp. 5197–5211.

- [53] W. Aloisi, G. Palumbo, and S. Pennisi, "Design methodology of Miller frequency compensation with current buffer/amplifier," *IET Circuits*, *Devices Syst.*, vol. 2, no. 2, p. 227, 2008.

- [54] W. Qu, S. Singh, Y. Lee, Y. S. Son, and G. H. Cho, "Design-oriented analysis for Miller compensation and its application to multistage amplifier design," *IEEE J. Solid-State Circuits*, vol. 52, no. 2, pp. 517–527, Feb. 2017.

- [55] H. Aminzadeh, "Analysis of multistage amplifiers with hybrid cascode feedforward compensation using a modified model for load impedance," *Analog Integr. Circuits Signal Process.*, vol. 95, no. 2, pp. 271–282, May 2018.

- [56] H. Aminzadeh, "Evaluation of the pole expressions of nano-scale multistage amplifiers based on equivalent output impedance," AEU Int. J. Electron. Commun., vol. 72, pp. 243–251, Feb. 2017.

- [57] S. Rosenstark, "A simplified method of feedback amplifier analysis," IEEE Trans. Educ., vol. E-17, no. 4, pp. 192–198, Nov. 1974.

- [58] J. Choma, Jr., "Signal flow analysis of feedback networks," *IEEE Trans. Circuits Syst.*, vol. 37, no. 4, pp. 455–463, Apr. 1990.

- [59] C. A. Desoer and E. S. Kuh, *Basic Circuit Theory*. New York, NY, USA: McGraw-Hill, 1969.

- [60] R. B. Blackman, "Effect of feedback on impedance," Bell Syst. Tech. J., vol. 22, no. 3, pp. 269–277, Oct. 1943.

- [61] A. D'amico, C. Falconi, G. Giustolisi, and G. Palumbo, "Resistance of feedback amplifiers: A novel representation," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 54, no. 4, pp. 298–302, Apr. 2007.

- [62] B. Cochrun and A. Grabel, "A method for the determination of the transfer function of electronic circuits," *IEEE Trans. Circuit Theory*, vol. CT-20, no. 1, pp. 16–20, Jan. 1973.

- [63] A. D. Grasso, G. Palumbo, and S. Pennisi, "Comparison of the frequency compensation techniques for CMOS two-stage Miller OTAs," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 55, no. 11, pp. 1099–1103, Nov. 2008.

- [64] A. D. Grasso, D. Marano, G. Palumbo, and S. Pennisi, "Analytical comparison of reversed nested Miller frequency compensation techniques," *Int. J. Circuit Theory Appl.*, vol. 38, no. 7, pp. 709–737, Sep. 2010.

- [65] H. Aminzadeh and W. Serdijn, "Low-dropout regulators: Hybrid-cascode compensation to improve stability in nano-scale CMOS technologies," in Proc. IEEE Int. Symp. Circuits Syst. (ISCAS), May 2011, pp. 2293–2296.

- [66] G. Giustolisi, G. Palumbo, and E. Spitale, "Robust Miller compensation with current amplifiers applied to LDO voltage regulators," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 59, no. 9, pp. 1880–1893, Sep. 2012.

- [67] H. Aminzadeh, M. R. Nabavi, and W. A. Serdijn, "Low-dropout voltage source: An alternative approach for low-dropout voltage regulators," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 61, no. 6, pp. 413–417, Jun. 2014.

the M.S. and Ph.D. degrees in electronics engineering, in 2008 and 2010, respectively. From 2010 to 2014, he was with the Delft University of Technology, The Netherlands, where he worked on low-voltage power regulation techniques for biomedical implanted devices. Since 2012, he has been with Payame Noor University, Tehran, Iran, where he is currently an Associate Professor. He has coauthored more than

50 articles on international journals and conference proceedings. His current research interests include modeling and optimization of analog circuits for low-voltage IoT and biomedical devices and low-power digital-to-analog and analog-to-digital converters design for telecommunication applications.

**ALFIO DARIO GRASSO** (Senior Member, IEEE) was born in Catania, Italy, in 1978. He received the Laurea (*summa cum laude*) and Ph.D. degrees in electronic engineering from the University of Catania, Italy, in 2003 and 2006, respectively.

From 2006 to 2011, he worked as a Freelance Engineer in the field of electronic systems. From 2009 to 2010, he was an Adjunct Professor of electronics at the University Kore of Enna, Italy. In 2011, he became a Researcher (an Assistant

Professor) and in 2015, he was appointed as an Associate Professor at the University of Catania. He teaches graduate courses on advanced VLSI digital design, microelectronics, and basic electronics. He has coauthored more than 90 articles on refereed international journals and conference proceedings. His current research interests include low-voltage low-power analog circuit design and analog and mixed signal processing for energy harvesting applications.

Prof. Grasso has received the Italian National Scientific Qualification for the position of a Full Professor, in 2017. He is an Associate Editor of the *Electronics Letters* (IET), the *International Journal of Circuit Theory and Applications* (Wiley), and the *Journal of Circuits, Systems and Computers*. He is a member of the Editorial Board of *Sensors* (MDPI).

**GAETANO PALUMBO** (Fellow, IEEE) was born in Catania, Italy, in 1964. He received the Laurea degree in electrical engineering and the Ph.D. degree from the University of Catania, in 1988 and 1993, respectively.

In 1994, he joined the University of Catania, where he has been a Full Professor, since 2000. He was the coauthor of four books by Kluwer Academic Publishers and Springer, in 1999, 2001, 2005, and 2014, respectively, and a textbook on

electronic devices, in 2005. He is the author of more than 450 scientific papers on referred international journals (more than 200) and conferences. Moreover, he has coauthored several patents. His primary research interests include analog and digital circuits.

Dr. Palumbo has served as a member of the Board of Governors for the IEEE CAS Society for the period 2011–2013. In 2005, he was one of the 12 panelists in the scientific-disciplinary area 09—industrial and information engineering of the Committee for Italian Research Assessment (CIVR). In 2003, he received the Darlington Award. He has served as an Associated Editor for the IEEE Transactions on Circuits and Systems—I: Regular Papers, in 1999–2001, 2004–2005, and 2008–2011, and the IEEE Transactions on Circuits and Systems—II: Express Briefs, in 2006–2007.

. . .