Received October 14, 2021, accepted November 5, 2021, date of publication December 10, 2021, date of current version December 29, 2021.

Digital Object Identifier 10.1109/ACCESS.2021.3134930

# **ConvFusion: A Model for Layer Fusion in Convolutional Neural Networks**

LUC WAEIJEN<sup>®</sup> 1,2, SAVVAS SIOUTAS<sup>1</sup>, MAURICE PEEMEN<sup>3</sup>, MENNO LINDWER<sup>1</sup>, AND HENK CORPORAAL<sup>®</sup> 2

<sup>1</sup>GrAI Matter Labs, 5656 AG Eindhoven, The Netherlands

<sup>2</sup>Electronic Systems Research Group, Department of Electrical Engineering, Eindhoven University of Technology, 5612 AP Eindhoven, The Netherlands

Corresponding author: Luc Waeijen (lwaeijen@tue.nl)

**ABSTRACT** The superior accuracy and appealing universality of convolutional neural networks (CNNs) as a generic algorithm for many classification tasks have made the design of energy efficient CNN accelerators an important topic in both academia and industry. Of particular interest in the design and use of CNN accelerators is the scheduling of the computational workload, which can have a major impact on the quality of the final design. The many inherently independent operations in CNNs result in a vast scheduling space however, rendering the selection of the optimal schedule(s) non-trivial. To aid in this complex task, this work introduces a generic mathematical cost model of the external memory accesses, internal memory footprint, and compute load for CNN execution schedules. The model enables fast exploration of the scheduling space, including loop tiling, loop reordering, explicit data transfer scheduling, recomputation, and, crucially, layer fusion, which recently has attracted interest as a method to reduce external memory accesses. An accompanying open source tool is released to perform schedule space exploration for CNNs using the introduced cost model. Leveraging the code generation capabilities of this tool the proposed model is validated on six real world networks, demonstrating that layer fusion can reduce the external memory accesses by more than two orders of magnitude compared to the best non-fused schedules. Confusing at first glance however, a high-level energy analysis shows that the practical benefits of layer fusion may be overestimated if other parts of the system are not tuned accordingly.

**INDEX TERMS** Energy efficiency, modeling, neural networks, scheduling.

#### I. INTRODUCTION

There is no longer any debate regarding the advantages of the class of convolutional neural network (CNN) algorithms. Many important problems, previously deemed difficult if not impossible to compute, are now being solved by CNNs. The plethora of application domains includes: control systems, pattern recognition, power systems, robotics, forecasting, manufacturing, art, and medical diagnosis [1].

Despite their successful application to many computational problems over the last decade, CNNs also have several major drawbacks. In particular, they are both compute and memory intensive algorithms. In the early years this kept the execution of CNNs confined to data centres, as evaluation on available general purpose, embedded processors required too much energy to be practical in mobile, energy constrained devices.

The associate editor coordinating the review of this manuscript and approving it for publication was Felix Albu

To overcome this, many dedicated CNN accelerators have been proposed since to bring CNNs to the edge, and in general reduce CNN energy consumption [2]. In modern technology nodes the main challenge in achieving a high energy efficiency for such accelerators is not so much the compute complexity, but rather the required memory accesses. Compared to an ALU operation, accessing an SRAM requires about  $5\times$  the energy, and going to external DRAM about  $200\times[3]$ . This phenomenon, commonly referred to as the memory wall [4], will only aggravate with further technology scaling. To attain high energy efficiency it is therefore imperative that compute devices use their memory systems optimally.

Apart from techniques at the algorithmic level to reduce the total required memory accesses, minimizing the energy spent on the memory system constitutes of maximizing data reuse captured in small local memories. In essence this reduces the problem to finding a beneficial execution schedule for a given CNN. Due to the massive amount of independent operations

<sup>&</sup>lt;sup>3</sup>Thermo Fisher Scientific, 5651 GG Eindhoven, The Netherlands

in CNNs many valid schedules exist however, and finding the optimal schedule(s) for a given network and compute platform is exceedingly complex. In particular, the combination and parametrisation of scheduling techniques such as loop tiling [5], loop reordering [6], and more recently loop/layer fusion [7]–[10], results in a vast scheduling space. To deal with this vast space existing research typically restricts itself to a subset of the complete space. This leads to the selection of potentially suboptimal schedules, and prohibits the generic application of the obtained results across different compute platforms.

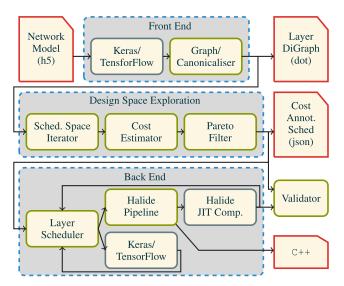

This work introduces a generic cost model which can efficiently compute the cost of a CNN schedule in terms of external memory accesses, required internal buffer space, and total multiply accumulates. The model is platform agnostic, and capable of handling CNN schedules that can be created using loop tiling, loop reordering, explicit scheduling of memory transfers, and layer fusion. This enables a fast search through possible schedules for CNNs without the need to perform profiling runs to obtain the cost of a particular schedule. The model is generic, and as such can be integrated in auto-schedulers for various accelerators and architectures by adequately bounding the schedule space based on specific architectural properties. A proof of concept, open source tool is developed building upon Keras/TensorFlow [11] as a frontend, and Halide [3] as a back-end. This tool is capable of performing exhaustive design space exploration for selected CNNs using the proposed model. Furthermore the Halide back-end generates code for each schedule, and instruments that code such that the modelled costs can be verified.

Various related works have demonstrated the potential of schedules that employ layer fusion to reduce external memory accesses [7]–[10]. However, the effect of these reductions on the net energy efficiency is typically overlooked. This work includes a high-level energy analysis based on the introduced schedule cost model, which results in some potentially surprising conclusions regarding the benefits of layer fusion.

The main contributions of this work are:

- Introduction of a platform agnostic, mathematical model

of the cost of a CNN schedule in terms of memory

accesses, memory footprint, and compute load, considering the vast scheduling space defined by loop interchange, loop tiling, loop fusion, recomputation, and

explicit data transfer scheduling (Sections III & IV).

- An open source tool that implements the introduced model, enabling exhaustive design space exploration for CNNs [12] (Section V).

- Validation of the proposed models accompanied with detailed analysis of the effects of various scheduling techniques on six real-world networks (Section VI).

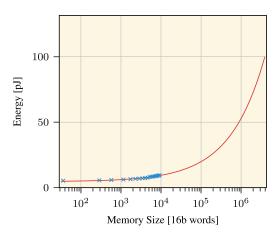

- Generic energy evaluation using the modelled schedule costs, which shows that the reduction in external memory accesses achieved by layer fusion does not automatically translate to significant net energy reduction (Section VII).

The remainder of this paper is organised as follows. First, the related work on CNN scheduling is discussed in Section II. Next, the scheduling space is formally defined in Section III. The cost model defined on this space is introduced in Section IV. Section V details the open source tool and experimental setup. Results on model validation and design space exploration are provided and analysed in Section VI. Section VII contains an energy evaluation of the discovered schedules for a platform with a multi-level memory hierarchy. Finally, Section VIII discusses current limitations and future work, and Section IX concludes this work.

#### **II. RELATED WORK**

Deep neural networks are both compute and memory intensive algorithms, and only have become viable methods by the merit of increased compute capacity about a decade ago. The recent renewed interest in deep neural networks was initiated by the successes in image classification of general purpose computing on graphical processing unit (GP-GPU) based implementations of CNNs [13], [14] circa 2011-2012. Since then tremendous effort has been made to enable the efficient execution of deep neural networks on energy-constrained (embedded) devices. Because the basic algorithm does not change much over different applications, CNNs in essence provide a universal solution to many compute tasks. This makes them a highly eligible target for dedicated hardware solutions, and as such has inspired the design of many CNN hardware accelerators [2].

Because CNNs have a large memory footprint, these accelerators typically require a form of external memory to store the network parameters and intermediate results. One of the first published accelerator designs to recognize the importance of minimizing accesses to this external memory was the Eyeriss by Chen *et al.* [5]. Based on manual analysis an execution schedule of CNNs is proposed for Eyeriss, which exploits spatial features of the architecture, and leverages strip-mining (a subset of tiling) to handle networks that do not match naturally with the dimensioning of the compute elements inside the accelerator. The iteration order over the CNN operations is fixed however, and tailored towards the architecture.

Rather than fixing the iteration order, SmartShuttle [6] takes more of the scheduling space into account by defining three iteration strategies, each targeting capturing reuse of different data. In particular, there are schedules that primarily optimise capturing parameter/weight reuse, input feature map data reuse, or output feature map reuse. Selecting between these schedules depends on the dimensions of the network layers. This choice already starts to outline the trilemma of selecting of which data elements to capture the reuse in local buffers, and the difficulty of finding the schedule that minimises the overall external memory accesses, as optimising for one subset of the data typically hurts the captured reuse of other parts.

To address the selection of a schedule based on tiling Peemen *et al.* [15] introduce generic formulas to enable fast

schedule space exploration. The proposed formulas require manual tuning for different loop orders however, which is addressed by the model proposed by Waeijen *et al.* [16]. This model can generically compute the cost of schedules that include loop reordering, loop tiling, and explicit scheduling of data transfers. A very extensive framework that combines the same scheduling techniques with multi-level memory mapping is ZigZig [17]. Missing in these models and framework, however, is the capability to handle loop fusion, or layer fusion as first introduced by Alwani *et al.* [7].

Alwani et al. [7] introduce the concept of fusing the computation of two consecutive layers in order to avoid the transfer of intermediate results to external memory. In essence this is an on-demand computation of the intermediate results, which are immediately consumed by the next layer. Because of overlap in tiles, as the authors note, there is the option to recompute intermediate results of which not all uses fall within a single tile, or to store this subset of intermediate results. Eventually only schedules without recompute are considered however. The layer fusion proposed by Alwani et al. [7] suffers from another shortcoming, aptly dubbed the computation pyramid by the authors. This term refers to the phenomenon that when more layers are fused, the number of points a tile in the output layer depends on expands rapidly, creating a pyramid of dependencies towards the input of the network. The AivoTTA accelerator [18] exhibits this very same imperfection.

This particular issue is addressed by Li et al. [8] by modifying the CNN algorithm and removing several dependencies between layers, while maintaining acceptable accuracy. An arguably preferable solution which does not require changes to the CNN algorithm is proposed by Goetschalckx and Verhelst [10], who employ line buffers to fuse layers, or execute depth-first in their terminology. This solution is more attractive as the functionality of the network remains unchanged, while large gains can be achieved in particular for networks with large layer dimensions. However, the proposed approach prohibits tiling in the channel dimension, and requires to always store the entire weight set on-chip, which may be highly suboptimal for networks with relatively small layer dimensions, i.e., layers of which the memory footprint is not dominated by data, but by weights. Despite these shortcomings, the depth-first methodology of Goetschalckx and Verhelst [10] sets the standard for schedules with layer fusion, and will be used as an important benchmark throughout this work.

Finally, several recent works have included layer fusion in GPU code generation [19], [20]. These works clearly show the potential gains of layer fusion, although both rely on heuristics to find good schedules, and require profiling runs on the target hardware. The models proposed in this work can be adapted towards SIMD and GPU execution as is further discussed in Section VIII, and can give insight into the performance of a schedule without execution on a target machine. Consequently they may be used to speed-up and

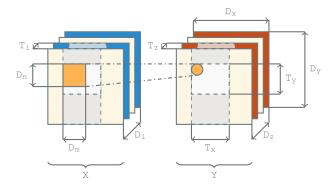

FIGURE 1. Single convolutional layer with input array x of and output array x. Dimensional notation shown here is used throughout this work, where  $D_x$  and  $D_x$  denote the kernel height and width,  $D_x$  and  $D_z$  the number of feature maps in the input and output array, and finally  $D_x$  and  $D_y$  the width and height of the output array, respectively. Furthermore,  $T_x$ ,  $T_y$  and  $T_x$  denote a tile size in the input feature maps, output feature maps, and output array height and width, respectively.

TABLE 1. Set of structural parameters of a convolution layer.

| Parameter        | Description                       |

|------------------|-----------------------------------|

| $D_{\mathbf{x}}$ | Width of output (Y) feature maps  |

| $D_V$            | Height of output (Y) feature maps |

| Dz               | Number of output (Y) feature maps |

| Di               | Number of input (X) feature maps  |

| $D_{m}$          | Convolutional kernel width        |

| Dn               | Convolutional kernel height       |

expand the design space searches of such heuristic (GPU) auto-schedulers.

## III. SCHEDULING SPACE

To facilitate the definition of the cost models later in Section IV, first the covered scheduling space is formally defined in this section. This definition starts with a high-level description of CNNs, followed by detailed descriptions of the considered scheduling techniques.

In a nutshell, a convolutional neural network functionally consists of a series of parallel, convolutional filters, or layers, connected by non-linear activation functions. The weights of these filters are determined during a learning phase in such a way that the network can perform its intended classification task. Once a suitable set of weights has been established, it remains static throughout the classification, or inference, phase, which is the focus of this work. Readers left desiring a more detailed description can find an excellent in-depth introduction to convolutional neural networks in the 'Deep Learning' book by Goodfellow *et al.* [21].

A single convolution layer consists of a set of convolution filters which are to be applied to a set of input surfaces to produce a set of output surfaces. These surfaces are referred to as feature maps. In the general case, a filter is applied for each pair of input and output feature maps, which is also the type of convolutional layer considered in the remainder of this work. More advanced layer types, such as depthwise convolution, are not directly considered, although possible model extensions are discussed in Section VIII-C.

Structurally a standard convolution layer is completely defined by the set of parameters listed in Table 1. Figure 1 is a visual representation of such a layer, and its various dimensions. Convolutions are applied to the source feature maps on the left (X), and their results, after application of a non-linear transformation, are aggregated in the feature maps on the right (Y). From an implementation viewpoint, a convolutional layer is a deep loop nest. The pseudocode of a single layer is shown in Code 1. Here variables Sx and Sy represent the stride of the filter on the input, which typically is one. A complete neural network consists of several of these layers connected through their feature maps. As such, a neural network can represented as a directional graph G(V, E) with the network layers V as nodes, and directional edges E to indicate their producer — consumer relationships.

```

for (int z=0; z<Dz; z++)</pre>

2

for (int y=0; y<Dy; y++)</pre>

3

for (int x=0; x<Dx; x++) {</pre>

4

Y[z][y][x]=bias[z];

5

for (int i=0; i<Di; i++)</pre>

6

for (int n=0; n<Dn; n++)</pre>

7

for (int m=0; m<Dm; m++)</pre>

8

Y[z][y][x] +=

9

X[i][y*Sy+n][x*Sx+m]

10

* W[z][i][n][m];

11

Y[z][y][x] = act(Y[z][y][x]);

12

```

Code 1. Loopnest for a single convolution layer.

From Code 1 it can be seen that the multiply-accumulate operations (lines 8-10) within a layer are completely independent. As such they may be executed in any order, yielding  $(D_z \times D_i \times D_v \times D_x \times D_m \times D_n)!$  scheduling options, ignoring the bias initialisation and the application of the activation function which even further increase the scheduling space. Reordering these operations will result in different reuse-distance distributions for the input data elements X, output data elements Y, and weights W. A smart reordering will capture more data-reuse in an internal buffer of given size, and as such minimize the accesses to an external memory. However, many of these schedules are highly irregular, and impossible to capture within reasonable code size. Therefore, this work only considers those schedules that can be generated using loop reordering and loop tiling at the layer level, as will be further discussed in Sections III-A, and III-B respectively.

Apart from scheduling the compute operations, the data transfers between memory levels can also be explicitly scheduled. For accelerators that typically use scratchpad memory such scheduling is imperative, but machines using caches can also benefit from grouping data transfers. Explicitly scheduling these transfers consists of specifying what data will be stored and reused, and when this data is loaded from the external memory. To specify this, the store level and compute level concepts of the Halide language [3] are used, and made part of the considered scheduling space as described in Section III-C.

Apart from scheduling the data transfers these concepts also allow for a precise expression of recomputation of intermediate results; a scheduling technique which provides a trade-off between (external) memory accesses and compute workload, as described in Section III-E.

Finally the scheduling space is expanded beyond scheduling individual layers by allowing layer fusion. Assume two convolutional layers A and B, which are connected in a network in such a way that B consumes the output of A. Following the dependencies, it is clear that some operations in B can already be executed, even if not all operations that belong to A are completed. Therefore it is possible to move (part of) the production of layer A into the loop nest of layer B using loop fusion. In this manner the results of layer A can potentially be consumed and discarded by B shortly after their production, effectively reducing their lifetime. Compared to an approach without layer fusion this has the potential to significantly reduce the accesses to a large external memory. The technique can furthermore be applied recursively, allowing any number of consecutive convolutional layers to be fused. Details on how this affects the overall scheduling space are provided in Section III-D.

## A. LOOP REORDERING

To formally define the loop order of a schedule, let L denote the set of all loop variables in a convolutional layer. In accordance to Code 1,  $L = \{z, y, x, i, m, n\}$ . The loop order  $O \subseteq L \times L$  defines a set of binary relations over L, where, with  $1, 1' \in L$ , 1 < 1' yields true iff 1 is inner to 1' in the loop nest, resulting in a total ordering of L. In Code 1, the following expression holds: m < n < i < x < y < z.

With this definition of loop order in place, consider the reuse distance of data elements in the X and Y arrays. Note that the accesses to array Y are independent of loop variable i (Line 8 in Code 1), while those to array X (Line 9 in Code 1) are dependant on i. Henceforth, because  $i \prec z$  in Code 1, the accumulations to a single z-coordinate in the Y array on line 8 are relatively close in time. However, for each of these accumulations an element from a unique i index has to be loaded from the X array on line 9. Therefore the reuse distances on array X are relatively long, while those on array Y are relatively short. Yet, when loops i and z are interchanged, i.e., z < i, the reverse holds. Which of these orders is favourable depends, amongst other factors, on the particular dimensioning of the layer. To complicate matters further, the other loops can also be reordered, and the data reuse of array W is also significant, rendering a complex tradeoff. Nonetheless, it can be stated that moving kernel loops m and n will likely not be beneficial, as typically  $D_m$  and  $D_n$  are very small (common values encountered in practice include one, three, and five). As such, loop reordering in this work is restricted to the remaining loop levels.

# B. LOOP TILING

Tiling is a classic scheduling technique to alter the execution order of operations. As discussed in the previous

section, a particular loop order may decrease the reuse on one data array, but increase it in another one. A different loop order may achieve the reverse. Loop tiling enables a hybrid approach, allowing a balanced average reuse distance for all data accesses. By splitting a loop  $1 \in L$  that iterates over a complete dimensions into an inner part 1i, and outer part 1i, it is possible to only compute part of a dimension inner to the iteration over another dimension.

For CNN layers in particular, each loop in Code 1 can be split. Again, because the kernel dimension  $D_m$  and  $D_n$  are typically very small, tiling loops m and n are not considered. However, the remaining loops, i.e.,  $\{i, x, y, z\}$ , can all be tiled into parts of size  $T_1$ , where  $1 \in \{i, x, y, z\}$ . Since  $T_1$  can be set to one, it is possible to rewrite Code 1 into Code 2 without loss of generality.

```

//outer tile loops

1

2

for (int zo=0; zo<Dz; zo+=Tz)</pre>

3

for (int yo=0; yo<Dy; yo+=Ty)</pre>

4

for (int xo=0; xo<Dx; xo+=Tx)</pre>

5

for(int io=0; io<Di; io+=Ti)</pre>

6

//inner tile loops

7

for(int zi=zo; zi<zo+Tz; zi++)</pre>

8

for (int yi=yo; yi<yo+Ty; yi++)</pre>

9

for(int xi=xo; xi<xo+Tx; xi++) {</pre>

10

if(io==0)

11

Y[zi][yi][xi]=bias[zi];

12

for(int ii=io; ii<io+Ti; ii++)</pre>

13

for (int n=0; 1<Dn; n++)</pre>

14

for(int m=0; m<Dm; m++)</pre>

15

Y[zi][yi][xi]+= \

16

X[ii][yi*Sy+n][xi*Sx+m] \setminus

17

* W[ii][zi][m][n];

18

if(io+Ti>=Di)

19

Y[zi][yi][xi]= \

20

act(Y[zi][yi][xi]);

21

```

Code 2. Tiled loopnest for a single convolution layer.

For the remainder of this work, Code 2 will be used to define schedules of a single layer. As such, a tiled schedule formally consists of an ordering O on the set of tiled loop levels  $TL = \{z \circ, y \circ, x \circ, i \circ, z i, y i, x i, i i, n, m\}$ , and a set of tile sizes  $T = \{T_z, T_y, T_x, T_i\}$ .

## C. STORE & COMPUTE LEVELS

Besides the computations, transfers between external memory and local buffers can be scheduled explicitly as well. To capture these memory operations the store and compute level concepts from the Halide language [3] are employed. These levels are defined for each array X, Y, and W, and dictate respectively what data volume is transferred when.

Let  $ARR = \{X, Y, W\}$  denote the set of all data arrays in a layer. The store level is then defined as follows:

The store level  $SL_{arr} \in TL$  for array  $arr \in ARR$  determines that at all data accesses to elements in

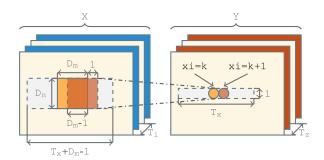

FIGURE 2. Overlap of  $(\mathtt{T_i} \times \mathtt{D_n} \times (\mathtt{D_m}-1))$  elements in the input data x between iterations 'n' and 'n+1' of loop  $\mathtt{xi}$  in Code 2 N. B. The volume required for  $SL_X = \mathtt{yi}$  is  $(\mathtt{T_i} \times \mathtt{D_n} \times (\mathtt{T_x} + \mathtt{D_m} - 1))$ , yet a rotating buffer of size  $(\mathtt{T_i} \times \mathtt{D_n} \times \mathtt{D_m})$  is sufficient.

X inside a single iteration of loop  $SL_{arr}$  have to be served from local memory after an initial load.

In Code 2, for example, if  $SL_X$  is set to loop level xi on line 9, the data required for the  $(T_i \times D_n \times D_m)$  operations inside one iteration of xi need to be served from local memory. Note that there is also data reuse of elements in X between two iterations of loop xi, as illustrated in Figure 2. In particular, there is an overlap of ( $T_i \times D_n \times (D_m - 1)$ ) elements between two consecutive iterations. The store level does not specify to capture this reuse in a local memory. To capture this reuse, the store level has to be moved one loop level up, to yi. Since one iteration of loop yi encapsulates  $T_x$  iterations of loop xi, the reuse between these iterations must now be captured by the internal buffer as well. As a consequence the volume of data that needs to be captured increases from  $(T_i \times D_m \times D_n)$  to  $(T_1 \times D_n \times (T_x + D_m - 1))$ , as visualised in Figure 2. Note that  $T_x$  is defined on the output layer, and because of the kernel size  $D_m$  a tile of size  $(T_x + D_m - 1)$  is thus required of the input layer. This demonstrates the trade-off between required on-chip buffer size and number of external memory accesses that can be explored using the store level.

Apart from the store level  $SL_{\tt arr} \in {\tt TL}$ , also a compute level is defined.

The **compute level**  $CL_{arr} \in TL$  determines at what loop iteration new data is produced/loaded for each array  $arr \in ARR$ .

This additional directive enables an optimization known as buffer folding. For  $SL_X = yi$  the data volume that has to be delivered by on-chip memory is equal to  $(T_i \times D_n \times (T_x + D_m - 1))$  elements<sup>1</sup>, but that does not require that this data is all live at the same time. In fact, as the  $(T_i \times D_m \times D_n)$  kernel moves from left to right as the xi loop proceeds, old data to the left will no longer be reused within the current iteration of loop yi. By selecting xi as the compute level of array X, i.e.,  $CL_X = xi$ , new data is only produced, i.e., fetched from external memory, at each iteration of xi. Since there are  $(T_i \times D_n \times (D_m - 1))$  elements overlap between each iteration, as discussed before, for each iteration only  $T_i \times D_n$  new elements are required.

<sup>&</sup>lt;sup>1</sup>Assuming stride Sx = 1 for simplicity.

These can be kept in a rotating buffer of only  $(T_i \times D_m \times D_n)$  elements. Note that the reuse captured by the internal buffer is unchanged, and dictated only by the store level. The addition of the compute level enables folding of buffers, such that the same reuse can be captured with less buffer space. Combined, the store and compute levels respectively dictate what data is transferred when.

Unlike loop ordering and tiling, the store and compute levels can not be chosen freely. In particular, data dependencies dictate that the production of the weights and input must be scheduled before, or in parallel with, the production of the feature maps, i.e.,  $SL_Y \leq SL_W$  and  $SL_Y \leq SL_X$ . Furthermore, the store level is always to be selected from one of the inner loops, or one level higher, i.e., any loop in Code 2 between lines 5–12. Setting the store level any higher would encompass at least one outer and inner loop of the same dimension, cancelling the effect of tiling. The same can be achieved by equating the tile size to the dimension, and as such these schedules are covered without the need to consider the remaining outer loop levels.

Finally the compute level of a data array should always be equal to, or lower than the store level of that array, i.e.,  $CL_{\mathtt{arr}} \leq SL_{\mathtt{arr}}$ . This requirement originates from the trivial dependency between the production of an element and the allocation of its storage. If no storage is allocated, the element can not be produced.

# D. LAYER FUSION

Apart from reordering computations within a layer, as performed by loop reordering and tiling, there is also the possibility to reorder operations between layers. In particular, if one layer is computed partially, some of the computations of the succeeding layer may already have all their input operands ready, enabling their execution. This concept is best described in terms of producers and consumers, where a first layer produces data which is consumed by a second layer. Rather than computing the producer completely before starting the computation of the consumer, the computation of the producer can be inlined to the computation of the consumer. Again, these transformations alter reuse distances and lifetimes of the various data arrays. Critically, the results from the producer can be consumed much earlier. Unless there is already sufficient on-chip memory to buffer an entire layer, loop fusion can be used to consume the results of intermediate layers, rather then sending them out to external memory only to be retrieved again later.

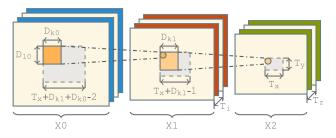

The data dependencies between two convolutional layers are illustrated in Figure 3. Note that for a layer v fused into a layer u, the output array Y of layer v is the same as the input array X of u. Generically,  $Y_k = X_{k+1}$  Therefore, in Figure 3, the Y arrays have been named by their X array equivalent. In this figure a tile of size  $T_z \times T_x \times T_y$  is to be produced in array X2. Assume X1 is not yet computed. When the production of  $T_z \times T_x \times T_y$  is about to start, first a tile in X1 of size  $T_i \times (T_x + D_{m1} - 1) \times (T_y + D_{n1} - 1)$  is produced.

```

//outer tile loops of X1->X2

for (int zo=0; zo<Dz; zo+=Tz)</pre>

3

for (int yo=0; yo<Dy; yo+=Ty)</pre>

4

for (int xo=0; xo<Dx; xo+=Tx)</pre>

5

for (int io=0; io<Di; io+=Ti) {</pre>

6

7

//Inline production of X0->X1

8

for (int z=0; z<Ti; z++)</pre>

9

for (int y=0; y<Ty+Dn1-1; y++)</pre>

10

for (int x=0; x<Tx+Dm1-1; x++) {</pre>

11

X1[z][y][x]=bias[z];

for (int i=0; i<Di0; i++)</pre>

12

13

for (int n=0; n<Dn0; n++)</pre>

14

for (int m=0; k<Dm0; m++)</pre>

15

X1[z][y][x] +=

16

X0[i][y*Sy0+n][x*Sx0+m]

17

* W01[z][i][n][m];

18

X1[z][y][x]=act(X1[z][y][x]);

19

20

21

//inner tile loops of X1->X2

22

for (int zi=zo; zi<zo+Tz; zi++)</pre>

23

for (int yi=yo; yi<yo+Ty; yi++)</pre>

24

for(int xi=xo; xi<xo+Tx; xi++) {</pre>

25

if(io==0)

26

X2[zi][yi][xi]=bias[zi];

27

for (int ii=io; ii<io+Ti; ii++)</pre>

28

for (int n=0; n<Dn1; n++)</pre>

29

for (int m=0; k<Dm1; m++)</pre>

30

X2[zi][yi][xi]+= \

31

X1[ii][yi*Sy1+n][xi*Sx1+m]

32

* W12[ii][zi][m][n];

33

if (io+Ti>=Di)

34

X2[zi][yi][xi]= \

35

act(X2[zi][yi][xi]);

36

37

```

Code 3. Code for 2 fused layers as illustrated in Figure 3.

Once this tile is ready, the computation of  $T_z\times T_x\times T_y$  in X1 commences.

The basic code of two fused layers is given in Code 3. As can be seen, the production of a  $T_i \times (T_x + D_{m1} - 1) \times (T_y + D_{n1} - 1)$  sized tile X1 is inlined in the loop nest of X2. This technique is generically known as loop fusion. Since in this particular context it is applied to loop nests of CNN layers the term layer fusion is used.

Although not shown for simplicity in Code 3, it is entirely possible to also tile and reorder the production of the inlined producer. From this perspective, tiling and reordering are orthogonal concepts to layer fusion. Furthermore, layer fusion can be applied recursively, fusing an unlimited number of consecutive layers. This increases the scheduling space tremendously, complicating the task of finding an optimal schedule for a given network.

**FIGURE 3.** Three state arrays x of two consecutive convolutional layers. To produce tile  $\mathtt{T}_z \times \mathtt{T}_x \times \mathtt{T}_y$  on x2, a tile of  $\mathtt{T}_{\underline{1}} \times (\mathtt{T}_x + \mathtt{D}_m - 1) \times (\mathtt{T}_y + \mathtt{D}_n - 1)$  is required from array x1. In a fused schedule, this tile of x1 is produced in-line to the production of the tile in x2, rather than first computing x1 completely.

The connections between layers in a neural network can generically be captured in a directed graph G(V, E) where V represents the set of individual layers and their associated structural parameters as listed in table 1, and E is a set of tuples (src, dst) with  $src, dst \in V$  that define a directional relation from src to dst. The production of a layer may be fused into one of its direct successors in this network graph G or it may not be fused at all. To denote this, each layer  $v \in V$  is assigned a fuse target  $Fuse(v) \in successors(v) \cup \{v\}$ , where  $successors(v) = \{v' \mid (v, v') \in E\}$  is the set of all direct successors of layer v in G(V, E). The production of layer v is then scheduled inline into the production of Fuse(v). When the fuse target is set to layer v itself, the layer is consequently not fused.

# E. RECOMPUTATION

Apart from shortened data lifetimes, layer fusion also introduces another interesting trade-off. As discussed, depending on tiling and store levels not all data reuse may be captured from a local buffer. The same naturally holds for the data of an intermediate, fused layer. In Figure 3 the data of X1 has multiple uses in the production of X2. If not all uses of an element are captured, there is the option to store the intermediate value of X1 in external memory and reload it for future uses. Alternatively it can be discarded, and recomputed from X0 when it is needed again. In this way a trade-off can be made between compute load and external memory traffic. This is particularly interesting for modern and future technology nodes, where (re)compute typically can be orders of magnitude cheaper in both time and energy than re-accessing external memory [3].

## F. FORMAL SCHEDULE

As stated, a convolutional layer is structurally defined by the set of parameters listed in table 1. For each layer  $v \in V$ , where V represents the complete set of layers that make up a particular CNN, a layer schedule s can be defined according to the various scheduling options discussed in this section. Such a scheduled layer s consists of the parameters listed in Table 2. A network schedule  $S = \{(v, s) \mid v \in V\}$  is consequently defined as the set of tuples of layers and accompanying layer schedules for each layer in the network.

**TABLE 2.** Layer schedule s of a convolution layer  $v \in V$ .

| Parameter                                                       | Description    |  |  |

|-----------------------------------------------------------------|----------------|--|--|

| $O \subseteq \mathtt{TL} \times \mathtt{TL}^*$                  | Loop ordering  |  |  |

| $T_z, T_v, T_x, T_i \leq D_z, D_v, D_x, D_i$                    | Tile sizing    |  |  |

| $SL_{	exttt{X}}, SL_{	exttt{Y}}, SL_{	exttt{W}} \in 	exttt{TL}$ | Store levels   |  |  |

| $CL_{	exttt{X}}, CL_{	exttt{Y}}, CL_{	exttt{W}} \in 	exttt{TL}$ | Compute levels |  |  |

| $Fuse \in successors(v) \cup \{v\}^{**}$                        | Fuse target    |  |  |

<sup>\*</sup> Recall, TL = {zo, zi, yo, yi, xo, xi, io, ii} denotes the set of all tiled loop levels in a convolution layer.

**TABLE 3.** Model summary.

| Function                                                                        | Description                                                               |

|---------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| $\operatorname{Buf}_{W},\operatorname{Buf}_{X},\operatorname{Buf}_{Y}$          | Buffer sizes of the weight, input, and output arrays respectively.        |

| $\mathrm{Acc}_{\mathbb{W}},\mathrm{Acc}_{\mathbb{X}},\mathrm{Acc}_{\mathbb{Y}}$ | Number of weight, input and out-<br>put elements respectively transferred |

| MACS                                                                            | from/to external memory.  Total number of multiply-accumulate operations. |

#### **IV. COST MODELS**

For real-world neural networks, merely iterating through the entire scheduling space as described in Section III already presents a significant task. Benchmarking each of these schedules on a target machine to find the best match is simply intractable. This section describes a set of mathematical expressions which, given a network schedule, accurately model the required number of external memory accesses, the required internal buffer space, and the number of computations measured in multiply-accumulates, as summarized in Table 3. These expressions only require a handful of computations compared to benchmarking a network schedule on a target machine, and as such enable fast design space exploration. The remainder of this section defines these expressions precisely. Readers primarily interested in applying these models may skip ahead to Section V which introduces the open source implementation of these equations in the form of the ConvFuser tool [12]. Also the final results in Section VI can be interpreted without in-depth understanding of the detailed model presented in this section.

#### A. PREREQUISITES

To aid the formulation of these models, a number of notational shorthands and auxiliary functions are defined first. In general, the multiplication of each element in an arbitrary set S will be abbreviated to  $\prod S$ , i.e.,

$$\prod S = \prod_{s \in S} s.$$

Note that in accordance with the common definition of the product operator, the product of the empty set  $\emptyset$  is defined as one.

Given a layer and an associated schedule  $(v, s) \in S$ , the (sub)set of structural dimensions of layer  $v \in V$  as defined in table 1, and the (sub)set of tile sizes in schedule s as

<sup>\*\*</sup> Note, when Fuse = v the layer is not fused.

defined in table 2, that belong to a given (sub)set of loop levels  $L' \subseteq L$ , is defined by the following two auxiliary functions respectively:

$$D(v, L') = \{D_1 \mid 1 \in L' \land D_1 \in v\},$$

$$T(s, L') = \{T_1 \mid 1 \in L' \land T_1 \in s\}.$$

Furthermore a translation function  $\kappa$  ( $\nu$ , 1) is defined, with layer  $\nu \in V$  and loop level  $1 \in \{x, y\}$ . This function converts loop levels x and y to their spatially related kernel dimensions  $D_m$  and  $D_n$  respectively:

$$\kappa (v, 1) = \begin{cases} D_m \in v, & 1 = x \\ D_n \in v, & 1 = y. \end{cases}$$

The corresponding set operator K, which translates all loop levels in a set  $L' \subseteq L$ , is defined as:

$$K(v, L') = \{ \kappa(v, 1) \mid 1 \in L' \}.$$

Another helper function translates a loop level  $1 \in L$  into the corresponding inner tiled loop level  $1i \in TL$ :

$$inner(1) = 1i.$$

Since for many models it matters whether or not the inner loop of a particular loop level  $1 \in L$  is preceded by the store level in a given layer schedule s, the set of all loop levels in set  $L' \subseteq L$  which are preceded by the store level  $SL_{arr}$  of array  $arr \in ARR$ , i.e., the collection of loop levels below/inner to the store level for array arr, is defined as:

$$LT_{arr}(s, L') = \{1 \mid 1 \in L' \land inner(1) \prec SL_{arr}\},\$$

where  $SL_{arr} \in TL \in s$ ,  $\prec \in O$ , and  $O \in s$ .

The complement of this set, i.e., the set of loop levels which are equal to or above/outer to the store level, is defined as:

$$GE_{arr}(s, L') = L' - LT_{arr}(s, L')$$

.

Furthermore the set of folded loop levels F, i.e., the levels between the store and compute level is defined as:

$$F_{arr}(s, L') = \{1 \mid 1 \in L' \land CL_{arr} \prec inner(1) \prec SL_{arr}\},\$$

where  $SL_{arr}$ ,  $CL_{arr} \in TL \in s$ ,  $\prec \in O$ ,  $O \in s$ , and the operator  $(1 \leq 1') = (1 \prec 1' \lor 1 = 1')$ . Finally a set selection function is defined, which selects set A if the layer is fused, or set B otherwise.

$$FuseSel(v, s, A, B) = \begin{cases} A, & fuse \neq v \\ B, & \text{o.w.,} \end{cases}$$

with fuse target  $fuse \in s$ .

For all these helper functions, when it is clear only a single layer v or schedule s is described, the v and s arguments are omitted for further brevity. An overview of these helper functions is provided in Table 4.

**TABLE 4.** Helper functions summary.

| Function                          | Description                                                                                                                                                                                                      |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D(v, L')                          | Set of loop dimensions $D_1$ belonging to loop levels $1\in L'\subseteq L$                                                                                                                                       |

| $T\left(s,\mathbf{L'}\right)$     | Set of tile dimensions ${\bf T}_1$ belonging to loop levels $1\in {\bf L'}\subseteq {\bf L}$ in schedule $s$                                                                                                     |

| $\kappa\left(v,1 ight)$           | Translation of loop level $1 \in \{\texttt{x}, \texttt{y}\}$ to loop dimension of corresponding kernel in layer $v$                                                                                              |

| K(v, L')                          | Application of $\kappa(v,1)$ to complete set of loop levels $1\in \mathbf{L'}\subseteq \mathbf{L}$                                                                                                               |

| $inner(1) = 1i$ $LT_{arr}(s, L')$ | Translates a non-tiled loop level $1 \in L$ into the corresponding inner tiled loop level $1i \in TL$<br>Set of loop levels in $L' \subseteq L$ that are below or equal to the store level in layer schedule $s$ |

| $GE_{ m arr}\left(s,{f L'} ight)$ | Set of loop levels in $\mathbf{L'}\subseteq \mathbf{L}$ that are above the store level in layer schedule $s$                                                                                                     |

| $F_{ m arr}\left(s,{f L'} ight)$  | Set of loop levels in $L'\subseteq L$ that are in between the compute and store level in layer schedule $s$                                                                                                      |

| $FuseSel(\\v,s,A,B)$              | If layer $v$ is fused in layer schedule $s$ return set $A$ , else return set $B$ .                                                                                                                               |

## **B. INTERNAL MEMORY FOOTPRINT**

With this notation in place, the required internal buffer size of a single scheduled layer  $(v, s) \in S$  can be concisely and accurately modelled. This buffer size is comprised of three parts, the sum of the memory footprints of the X, Y, and W arrays respectively. All these footprints can be obtained by computing the volume of data below the respective store level  $SL_{\tt arr}$ , since this is the volume that will be loaded by the scheduled external memory access.

In general, for each loop level  $1 \in \{x, y, z, i, m, n\}$  a selection has to be made between two options for each data array  $arr \in \{X, Y, W\}$ , one contribution to the data volume if said dimension is below  $SL_{arr}$ , and one when it is equal or above. The product of these contributions yields the complete data volume.

## 1) WEIGHT ARRAY

For weight array W these options for the dimensions are explicitly listed in Table 5. Since the accesses to W are independent of loop levels x and y, as can be seen in line 10 of Code 1, these loop levels do not contribute to the memory footprint of W (set to 1 for unit operation in the final product). For loop levels m and n the full dimension  $D_m$  and  $D_n$  has to be counted respectively, since these loops are excluded from tiling in the defined schedule space, and they are also always below the store level. More interesting are loop levels z and i, which require a full tile  $T_z$  or  $T_i$  to be counted when they are below the store level, or only a single slice if they are not. The product of all correct contributions in Table 5 yields the initial memory footprint of the W array. However, care has to be taken when the compute level  $CL_{\mathbb{W}}$  is below the store level, and buffer folding is applied. In the case that z and/or i are folded (below the store level, but above or equal to the compute level), they only contribute as if they were above the store level.

**TABLE 5.** Memory footprint contributions of W for all loop levels.

| Loop Lvl (1) | $SL_{\rm W} \prec 1$ | $SL_{\mathtt{W}}\succeq \mathtt{1}$ |

|--------------|----------------------|-------------------------------------|

| x            | 1                    | 1                                   |

| У            | 1                    | 1                                   |

| m            | $D_{m}$              | _                                   |

| n            | $D_n$                | =                                   |

| Z            | $T_z$                | 1                                   |

| i            | Ti                   | 1                                   |

Using the introduced notation, the memory footprint of the weight array W of a single convolution layer can be expressed as follows:

$$\operatorname{Buf}_{\mathbb{W}} = \prod T(LT_{\mathbb{W}}(\Lambda) - F_{\mathbb{W}}(\Lambda)) \times \prod D(\{m, n\}) \times \operatorname{FuseSel}(\mathbb{D}_{1}, 1),$$

where  $\Lambda = FuseSel(\{z\}, \{z, i\})$ . I.e., for the kernel loops m and n the full dimensions  $D_m$  and  $D_n$  are counted. For the non-fused case as described in Table 5, the tile sizes of loop dimensions z and i are taken into account, provided they are below the store level and not folded. When the layer is fused into a successor however, the computation changes slightly because dimension i can no longer be tiled. Considering the nonlinear activation function on line 11 of Code 1, all contributions in the i dimension have to be reduced before this activation can be applied, and the next layer can start its dependent computations. This can be more clearly seen in Code 3, where, due to the activation function on line 18, the complete (untiled) i loop on line 12 has to be computed before the next layer can start production on line 22. Thus, i can not be tiled and instead the full D<sub>i</sub> dimension is required, as is covered by the FuseSel selection function.

# 2) INPUT ARRAY

For input array X a similar equation can be derived. The notable differences are that X is independent of loop level z, and that at loop levels x and y at least  $D_m$  and  $D_n$  input elements are required. When a tile is required in these dimensions, i.e.  $x \prec SL_X$  or  $y \prec SL_X$ , the kernel size also comes into play and, as illustrated in Figure 2, a contribution of  $T_x + D_m - 1$  or  $T_y + D_n - 1$  is required respectively. Another complicating factor is formed by the strides in the x and y dimensions, which change these terms to  $(T_x - 1) \times S_x + D_m$  and  $(T_y - 1) \times S_y + D_n$  respectively. The resulting memory footprint of a single layer is captured by the following expression:

$$\begin{aligned} \operatorname{Buf}_{\mathsf{X}} &= \operatorname{\it FuseSel}\left(\operatorname{D}_{\dot{\mathtt{l}}}, \prod T\left(\operatorname{\it LT}_{\mathsf{X}}\left(\{\dot{\mathtt{l}}\}\right) - \operatorname{\it F}_{\mathsf{X}}\left(\{\dot{\mathtt{l}}\}\right)\right)\right) \\ &\times \prod K\left(\operatorname{\it GE}_{\mathsf{X}}\left(\{\mathsf{x},\,\mathsf{y}\}\right) \cup \operatorname{\it F}_{\mathsf{X}}\left(\{\mathsf{x},\,\mathsf{y}\}\right)\right) \\ &\times \prod \{\left(\operatorname{T}_{\mathsf{d}}-1\right) \times \operatorname{S}_{\mathsf{d}} + \kappa(\mathsf{d}) \mid \\ &\quad \mathsf{d} \in \operatorname{\it LT}_{\mathsf{X}}\left(\{\mathsf{x},\,\mathsf{y}\}\right) - \operatorname{\it F}_{\mathsf{X}}\left(\{\mathsf{x},\,\mathsf{y}\}\right)\right\}. \end{aligned}$$

Again, *FuseSel* is used to account for the full dimension in i when the layer is fused, for the same reason as in Buf<sub>W</sub>, i.e., due to the nonlinear activation function on line 11 in Code 1.

## 3) OUTPUT ARRAY

Finally, the memory footprint of the output array Y is relatively straightforward, and depends on x, y, and z. For each of these dimensions the contribution is equal to the tile size, unless the dimension is above the store level or folded. That is, unless the current layer will be fused into the next layer, in which case the output array Y is effectively replaced by data array X of the next layer, yielding no memory contribution for Y. Furthermore it is important to note that once an output is complete, i.e., all  $D_{\dot{1}}$  contributions of the preceding layer have been processed and the activation function is applied, there is no need to keep the completed output on-chip. From a memory viewpoint this resembles buffer folding, which is also how this optimization is taken into account in the final equation. The footprint contributions of those loop levels in  $\{x, y, z\}$  which are above  $\dot{1}$  fold to one, resulting in:

$$Buf_{Y} = FuseSel(0, \prod T(LT_{Y}(\{x, y, z\}) - F_{Y}(\{x, y, z\}))).$$

#### C. EXTERNAL MEMORY ACCESSES

The number of required external memory accesses can be derived in a similar manner as the internal memory footprint. The crucial difference is to not only account for the data volume transferred, but also how many times such a transfer takes place. These two terms can be considered separately, such that for data array  $\mathtt{arr} \in \mathsf{ARR}$ , the external memory accesses  $\mathsf{Acc}_{\mathtt{arr}}$  are expressed as the volume of a data transfer  $\mathsf{Vol}_{\mathtt{arr}}$ , multiplied by the number of those transfers  $\mathsf{Trans}_{\mathtt{arr}}$ :

$$Acc_{arr} = Vol_{arr} \times Trans_{arr}$$

.

# 1) WEIGHT ARRAY

For weight array  $\mathbb{W}$ , the volume of a transfer  $Vol_{\mathbb{W}}$  is nearly identical to its internal memory footprint  $Buf_{\mathbb{W}}$ , with the notable exception that for the transfer volume buffer folding has no effect. The fact that the buffer is smaller due to liveness of the variables does not invalidate the requirement to transfer the complete volume eventually. The transfer volume of array  $\mathbb{W}$  can therefore be expressed as:

$$Vol_{\mathbb{W}} = \prod T(LT_{\mathbb{W}}(\Lambda)) \times \prod D(\{m, n\}) \times FuseSel(D_{1}, 1),$$

where  $\Lambda = FuseSel(\{z\}, \{z, i\})$ . Note that when the current layer is fused into the next, all inputs  $D_i$  need to be handled before the results can be passed to the next layer. Again, the nonlinear activation function on line 11 of Code 1 prevents partial updates of only  $T_i$  inputs to be consumed.

Next the number of transfers is to be determined. In general, if a loop level 1 is above or equal to the store level, the associated volume needs to be transferred for every  $D_1$  iterations. When 1 is beneath the store level however, that volume will have to be transferred only  $\left\lceil \frac{D_1}{T_1} \right\rceil$  times. The ceiling operator is used here to arrive at a conservative bound, which accounts for a full tile transfer in case tile size  $T_1$  is not an exact multiple of  $D_1$ . For weight array W the number

of transfers is given by:

$$\operatorname{Trans}_{\mathbb{W}} = \prod D\left(GE_{\mathbb{W}}\left(\Lambda\right)\right) \times \prod \left\{ \left\lceil \frac{\mathbf{D}_{\mathsf{d}}}{\mathbf{T}_{\mathsf{d}}} \right\rceil \ \middle| \ \mathsf{d} \in LT_{\mathbb{W}}\left(\Lambda\right) \right\},$$

where  $\Lambda = FuseSel(\{x, y, z\}, \{x, y, z, i\})$  is used to compensate when due to fusion the entire volume is transferred.

## 2) INPUT ARRAY

For data array X the transfer volume resembles the internal buffer size of array X, Buf<sub>X</sub>, again ignoring any buffer folding:

$$\begin{aligned} \operatorname{Vol}_{X} &= \operatorname{\it FuseSel}\left(\operatorname{D}_{\mathtt{i}}, \prod T\left(LT_{\mathtt{X}}\left(\{\mathtt{i}\}\right)\right)\right) \\ &\times \prod K\left(\operatorname{\it GE}_{\mathtt{X}}\left(\{\mathtt{x},\mathtt{y}\}\right)\right) \\ &\times \prod \left\{\left(\operatorname{T}_{\mathtt{d}}-1\right)\times\operatorname{S}_{\mathtt{d}}+\kappa(\mathtt{d})\mid \mathtt{d}\in \operatorname{\it LT}_{\mathtt{X}}\left(\{\mathtt{x},\mathtt{y}\}\right)\right\}. \end{aligned}$$

The number of transfers for X is in fact equal to those of W (TransW), apart from checking against the store level of X instead of W, i.e.,

$$\operatorname{Trans}_{\mathsf{X}} = \prod D(G\mathsf{T}_{\mathsf{X}}(\Lambda)) \times \prod \left\{ \left\lceil \frac{\mathsf{D}_{\mathsf{d}}}{\mathsf{T}_{\mathsf{d}}} \right\rceil \;\middle|\; \mathsf{d} \in \mathit{LT}_{\mathsf{X}}(\Lambda) \right\},$$

where  $\Lambda = FuseSel(\{x, y, z\}, \{x, y, z, i\}).$

# 3) OUTPUT ARRAY

Finally, for the number of external memory accesses for array Y, it is easier to deviate from the volume/transfer approach used above. When a layer is fused, the output simply does not contribute to the external transfers, as the outputs are stored directly in the X array of the layer that is being fused into. When a layer is not fused, eventually the complete output, i.e.  $D_x D_y D_z$  elements, have to be transferred at least once to the external memory. More than one transfer per output element may be required if partial results are stored in (and later loaded from) external memory. Here, a partial result is a partial sum in array Y which is not yet ready to be passed to the nonlinear activation function. For internal buffer space it could be interesting to evict some of these partial results from the local buffer, and load them back later. This happens only if tiling is applied to the i loop. In that particular case the partial output elements have to be transferred twice for each tile in i, once for storing the partial results externally, and once for loading them back (excluding the first update of Y). Combined this yields the following expression for the number of elements transferred for output array Y:

$$Acc_{\text{Y}} = \text{D}_{\text{x}} \text{D}_{\text{y}} \text{D}_{\text{z}} \times \left( \left\lceil \frac{\text{D}_{\text{i}}}{\text{T}_{\text{i}}} \right\rceil \times 2 - 1 \right).$$

## D. COMPUTE

The final part of the model represents the number of multiply-accumulate operations (MACs) required to complete a schedule. Without recompute, this number is trivial to obtain by multiplying all dimensions of a layer  $D_x \times D_y \times D_z \times D_c \times D_n \times D_m$ . However, to account for recompute due to overlap of input tiles detailed later in Section IV-E, this formula is split into three terms: the number of MACs to produce a single

output pixel PMACs, the volume of a produced output tile OVol, and the number of such output volumes in a layer.

The number of MACS for a single output pixel is fairly straightforward, and is determined by the number of input feature maps multiplied by the kernel size:

PMACs =

$$\prod K(\{x, y\}) \times D_i$$

.

The produced volume in number of features for every transfer is also straightforward, and amounts to those tiles which are below the store level of array X:

$$OVol = \prod T(GE_X(\{x, y, z\})).$$

Note that the store level of array X is used, since the input volume determines the produced output volume. Consequently, the number of such volumes is simply equal to the number of transfers of array X, Trans $_X$ .

The total number of MACS is thus given by:

$$MACS = PMACS \times OVol \times Trans_v$$

.

## E. LAYER FUSION

Now that models have been established for the memory footprint, external memory accesses, and number of multiply-accumulate operations per layer for each of the W, X, and Y arrays in the preceding sections, these models can be combined to provide the same properties for complete sets of fused layers. This is achieved by 'chaining' the provided layer models in a recursive fashion. This is best understood by observing the consumption of X0 in Figure 3 used to produce X1. Instead of producing complete array X1, i.e.,  $D_{x1} \times D_{y1} \times D_{i1}$  as the output size of X0, in a fused schedule only a single tile  $(T_x + D_{k1} - 1) \times (T_y + D_{11} - 1) \times D_{i1}$  needs to be produced at a time. Substituting  $D_x$ ,  $D_y$ ,  $D_z$  with  $(T_x + D_{k1} - 1) \times (T_y + D_{11} - 1) \times D_{i1}$  respectively in the models provides the costs of this intermediate tile:

- Multiply accumulates: The number of multiply accumulates required to produce the tile from x0 to X1 are simply given by PMACs(L01), where L01 represents the layer that consumes X0 and produces X1.

- Memory footprint: The local memory footprint of the tile in X0 is given by Buf<sub>X</sub>(L01), the required footprint of the tile in X1 is given by Buf<sub>X</sub>(L12). The footprints of the weights can used without any substitution.

- Accesses: The intermediate tile in X0 of course does not require any external data accesses, as it is produced and consumed in a fused fashion. However, the number of transfers Trans<sub>X</sub>(L12) specify how many times the tile needs to be produced in the case of recomputation, and tile overlap in general. For the overall cost of the fused set of layers, the multiply accumulates for the tile are to be multiplied with the number of productions. Same holds for the loads of the weights required to produce the tile, unless they are completely stored in the local buffer. Also, this number of required productions moves further up the set of fused layers, as consequently any producers of this tile may in turn need to be produced

multiple times if they are not stored for the complete lifetime of the network depending on their store level and tile sizes. Only the first layer of a set of fused layers, has external memory accesses. If this first layer needs multiple transfers of its own, i.e., not all uses of the data elements are captured on first load, the number of additional accesses can grow quite quickly due to the recomputation effect. The more profitable schedules therefore typically ensure the input is loaded only once, such that the cost of recomputation indeed only affects the compute cost, and does not increase the number of external accesses.

Hence, using substitution of tile dimensions for the output dimensions, and propagation of the number of productions required for each tile, the total cost of a fused segment can be derived from the individual cost models presented in the previous sections.

#### F. COMPLETE NETWORK MODEL

The total costs of a complete network are now trivial. The network schedule effectively partitions the layers into groups of fused layers. These groups contain one or multiple layers, for which the costs can be derived using the fusion approach described in the previous section. The total number of multiple accumulates required by a network schedule is simply obtained by adding the multiply accumulates of all groups. Same holds for the number of external accesses, the sum of the accesses of each group forms the cost for the entire network. The memory however only requires the maximum buffer size over all groups, since only a single group is active at any given time during network evaluation assuming no pipelining of the execution. Using these simple rules, the costs of an entire network can be computed.

# V. AUTOMATED DESIGN SPACE EXPLORATION

The formal model introduced in Section IV enable automated exploration of the vast scheduling space described in Section III. To achieve complete automation Section V-A describes a strategy to efficiently traverse the entire scheduling space. Section V-B introduces ConvFuser [12], an open source tool which implements the presented traversal strategy and cost models, enabling automated design space exploration and verification of any neural network described in the popular Keras framework [11].

## A. SPACE TRAVERSAL

To effectively explore the scheduling space as described in Section IV four steps are required:

# 1) IDENTIFICATION OF SEQUENCES

Since the proposed models do not include provisioning to handle residual/skip connections, only consecutive layers without forks or joins are considered for fusion. The first step of a design space exploration (DSE) is therefore to select sets of layers that may be fused. Such a set of eligible layers is

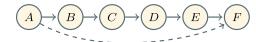

FIGURE 4. Example layer graph with sequence [B, C, D, E], and a residual connection between A and F.

referred to as a sequence, an example of which is shown in Figure 4.

#### 2) SEGMENTATION

Within each sequence it needs to be decided which layers to fuse (if any) to obtain the Pareto optimal schedules of the network. A set of fused layers within a sequence is referred to as a segment. The sequence [B, C, D, E] of Figure 4 contains the following valid segments: B, C, D, E, BC, CD, DE, BCD, CDE, BCDE. Each of these segments is evaluated individually, yielding a vector of schedules  $\vec{S}$  per segment.

# 3) PARTITIONING

Once all possible segments have been identified and their costs have been evaluated, those segments that cover the entire sequence need to be combined. For example segments BC and DE cover sequence [B, C, D, E], but also segments B, C, and DE, as well as many more. Combining the schedule vectors  $\vec{S}$  of each segment into an overall schedule vector  $\vec{SS}$  for the sequence is done by taking their product, and using the rules outlined in Section IV-F. Note that this procedure can be significantly accelerated by first Pareto-filtering the segment schedule vectors  $\vec{S}$ . It can be trivially proven that considering only the Pareto points of each segment is sufficient to yield all the Pareto points of the entire partition, since the combining (reduction) functions of Section IV-F, i.e., summation and maximum selection, are monotonically increasing.

## 4) NETWORK SCHEDULE COST COMPUTATION

Finally the costs of all valid partitions are combined using the same rules of Section IV-F to obtain the cost of the entire network. Similarly to the partition cost computation, segment schedule vectors  $\overrightarrow{SS}$  can be Pareto-filtered before combination with other partitions to yield a Pareto optimal scheduling of the entire network.

## B. CONVFUSER

An embodiment of the automated design space exploration described in this work is provided in the form of an open source tool: ConvFuser [12]. Apart from automated DSE, ConvFuser also features code generation for any selected schedule, enabling reliable validation of the models.

ConvFuser builds upon the popular Keras/TensorFlow framework [11] to read standard HDF5 graph models (See Figure 5). After loading a network using Keras/TensorFlow, a graph is constructed from the network layers, and a custom canonicalisation pass is employed to normalize the network

FIGURE 5. Schematic overview of the ConvFuser tool. Green boxes are developed for this work.

description. An important part of this canonicalisation is performing trivial layer merges, including but not limited to:

- merging of batch normalization layers into convolutional layers, which can be achieved by modification of the weights of the target convolutional layer.

- merging of activation layers into convolutional layers.

Note that some literature refers to these trivial layer merges as layer fusion. This term is apt in the case of merging activation layers, which also involves loop fusion, but it should not be confused with the much more complicated fusing of consecutive convolutional layers as described in this work.

After canonicalisation, design space exploration can be performed. Many smart search strategies could be employed here, but by virtue of the mathematical models and their fast evaluation, straightforward exhaustive search is feasible for smaller networks. Additionally the tool provides several options to restrict the design space, such as limiting the number of layers considered for fusion, selection of tile sizes such as only exact multiples of their respective dimension, or only powers of two, and whether to consider recomputation.

Finally, to enable validation of the found schedules, a hybrid back end based on the Halide language [3] and Keras/TensorFlow [11] is provided. Any non-convolutional layers are evaluated directly by Keras/TensorFlow. The scheduled convolutional layers however are implemented using a modified version of Halide. In particular this modification consists of additional python bindings to be able to insert instrumentation code. This code utilizes Halide's internal tracing mechanism to keep track of accesses to buffers, and sizes of allocated buffers. To emulate an external memory and internal buffers, a construct similar to Halide's recently added in operator is used. This construct adds an extra layer of buffering, where one large buffer essentially mimics external memory, and working data is loaded into a smaller, internal buffer. By keeping track of the accesses to these two levels of buffering, the required external accesses can be exactly monitored. An optional validation step can be used to check the external accesses, internal buffer size, and multiply-accumulates measured from Halide execution with the values predicted by the models.

## **VI. MODEL VALIDATION & EVALUATION**

The validity of the models introduced in Section IV is confirmed experimentally using the ConvFuser tool introduced in Section V. The experiments consist of a design space exploration for several synthetic and real-world networks, followed by code generation for each of the Pareto optimal schedules. This code is automatically instrumented by the ConvFuser tool to measure the number of multiply accumulates, internal memory size, and external accesses, which are then compared against the modelled values.

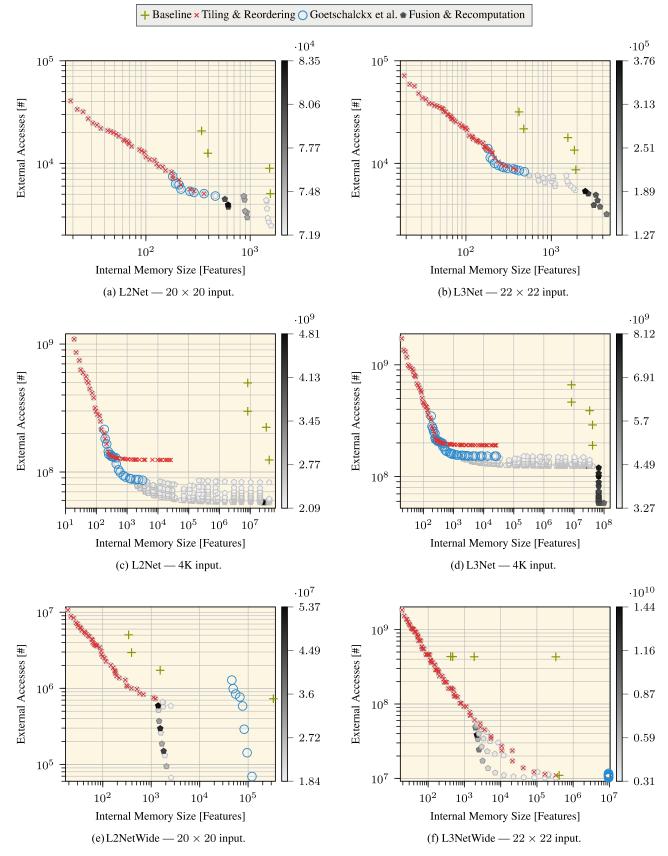

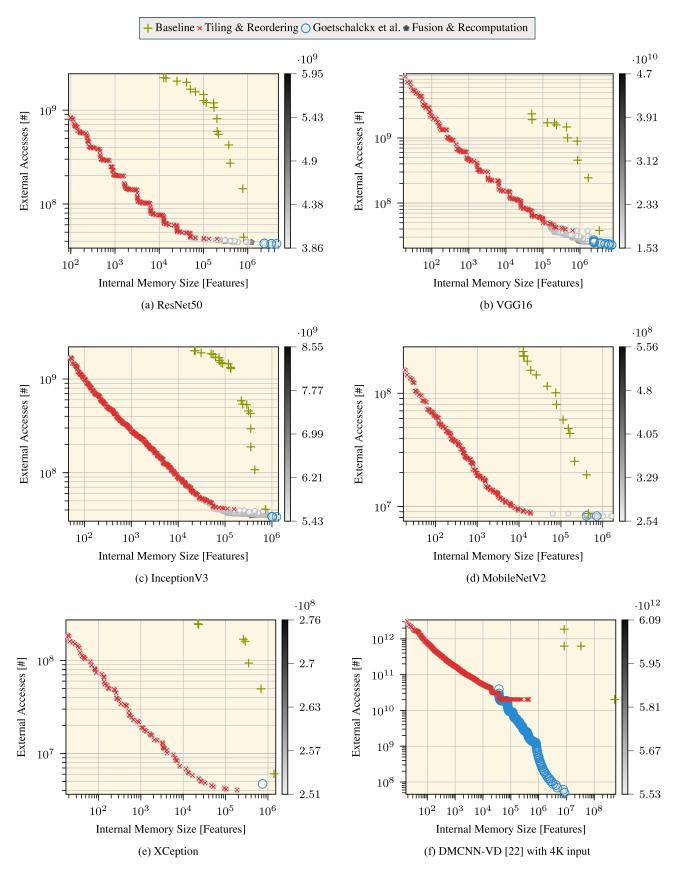

Besides this model validation, the tool also enables the evaluation of the impact of various scheduling techniques. In essence, the scheduling space described in Section III can be restricted to subsets by disallowing or limiting certain scheduling techniques. For this evaluation four progressively inclusive scheduling spaces are defined:

- 1) Baseline: The baseline scheduling space follows the straightforward implementation in Code 1 for each layer. It thus excludes loop reordering, tiling, and fusion, but does allowing different store and compute levels.

- 2) Tiling & Reorder: This space adds both loop tiling and reordering to the allowed options to the baseline space. Tiling is restricted to sizes that are integer factors of the dimensions to keep the space to a size that can be completely traversed in reasonable time. Other tiling options are built into ConvFuser, but are not further evaluated in this section.

- 3) Goetschalckx *et al.*: This space extends the tiling and reorder options with layer fusion. The allowed fusion however does not recompute any elements. Furthermore weights are not tiled, and are always stored on-chip for a fused section. This space matches the work of Goetschalckx *et al.* [10], enabling direct comparison. One notable exception for this space is that the tiling factor is not limited as is the case in the work of Goetschalckx *et al.*, since for this particular design space it is possible to use a fast branch and bound algorithm on the tiling factor while still guaranteeing an optimal result.

- 4) Fusion & Recomputation: This extends the *Goetschalckx et al.* space with tiling of weights and recomputation. The addition of tiling the weight accesses however disallows the previously mentioned branch and bound technique on the tiling factor without losing optimality. Therefore this space again is constrained to the same tiling limitations as the Tiling & Reorder space, i.e., integer factors of the dimensions.

This partitioning of the scheduling space enables the investigation of the impact of tiling, loop reordering, fusion, and

**TABLE 6.** Layer dimensions of L2Net and L3Net for  $20 \times 20$  and 4K inputs.

| Net       | $\mathtt{D}_{\mathtt{x}}$ | $\mathtt{D}_{\mathtt{y}}$ | $D_{\text{i}}$ | $D_{Z}$ | $D_n$ | $D_{m}$ |

|-----------|---------------------------|---------------------------|----------------|---------|-------|---------|

| L2Net     | 18                        | 18                        | 3              | 4       | 3     | 3       |

|           | 16                        | 16                        | 4              | 4       | 3     | 3       |

| L3Net     | 20                        | 20                        | 3              | 4       | 3     | 3       |

|           | 18                        | 18                        | 4              | 4       | 3     | 3       |

|           | 16                        | 16                        | 4              | 4       | 3     | 3       |

| L2Net 4K  | 3838                      | 2158                      | 3              | 4       | 3     | 3       |

|           | 3836                      | 2156                      | 4              | 4       | 3     | 3       |

| L3Net 4K  | 3838                      | 2158                      | 3              | 4       | 3     | 3       |

|           | 3836                      | 2156                      | 4              | 4       | 3     | 3       |

|           | 3834                      | 2154                      | 4              | 4       | 3     | 3       |

| L2NetWide | 18                        | 18                        | 3              | 1024    | 3     | 3       |

|           | 16                        | 16                        | 1024           | 4       | 3     | 3       |

| L3NetWide | 20                        | 20                        | 3              | 1024    | 3     | 3       |

|           | 18                        | 18                        | 1024           | 1024    | 3     | 3       |

|           | 16                        | 16                        | 1024           | 4       | 3     | 3       |

recomputation on MAC count, required on-chip memory, and external accesses.

#### A. MICRO BENCHMARKS

In order to validate the models introduced in Section IV, and obtain insight into the effect of different scheduling techniques, first a number of micro benchmarks is performed. To this end two synthetic networks, L2Net and L3Net, are defined. These networks consists of respectively two or three convolutional layers with a  $3 \times 3$  kernel. This enables a study into the effects on the resulting scheduling space when deepening networks. The dimensions of these layers are shown in Table 6 for both a  $20 \times 20$  input and a 4K input, used to see the effects of network input size on the resulting schedules. Finally the number of feature maps of these two nets is increased, yielding L2NetWide and L3NetWide in Table 6, to examine the effect of this parameter on the effect of the modelled scheduling techniques.

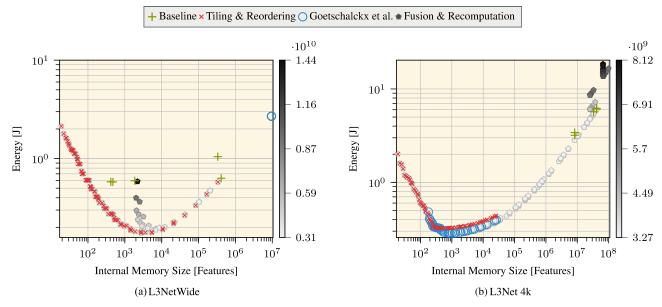

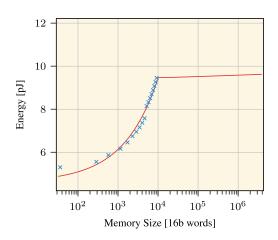

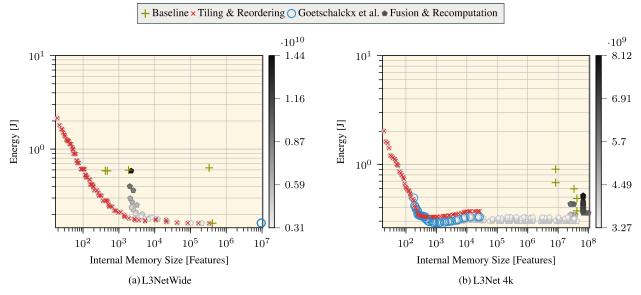

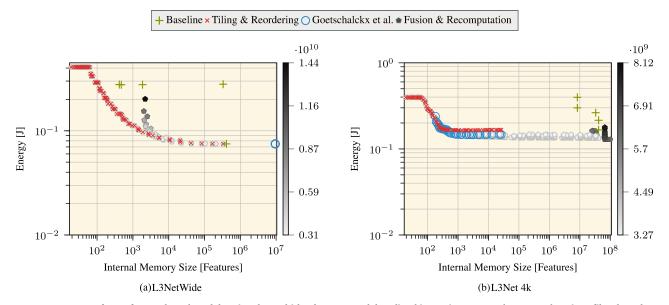

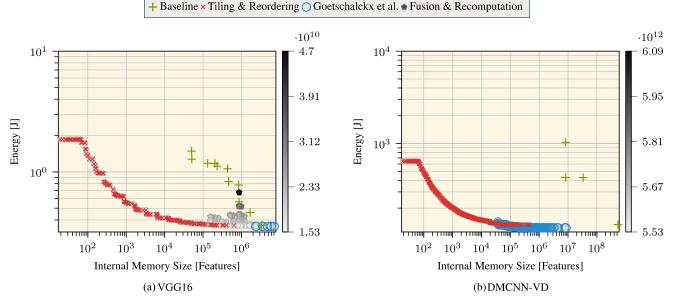

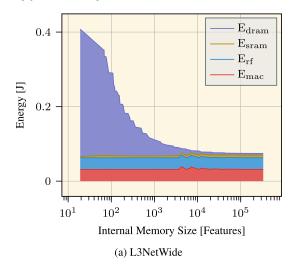

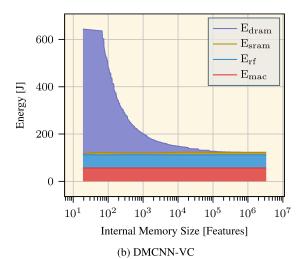

The results of the schedule space exploration for L2Net and L3Net with  $20 \times 20$  and  $22 \times 22$  inputs respectively are shown in Figures 6b and 6c. For all schedules of a network the number of multiply-accumulates is constant, with the exception of those schedules that include recomputation. To indicate the number of required multiply-accumulates, a colour coding is added for the Fusion & Recomputation schedules. The Pareto schedules for L2Net and L3Net with 4k inputs are shown in Figures 6d and 6e respectively. Finally the Pareto fronts for L2NetWide and L3NetWide are given in Figures 6f and 6g. Note that the verification with instrumented halide for the selected points in Figure 6 showed a one to one match between the models and the measurements, apart from some corner cases where Halide failed to apply complete buffer folding. These results confirm the accuracy of the models presented in section IV.

From these figures five key observations can be made:

1) The baseline schedules are consistently poor over all networks, although they always include a point that minimizes the external accesses when fusion and

- recomputation are not considered. This naturally happens for the store-level that cover all data uses, but due to the lack of tiling and smart loop reordering these points typically require a huge amount of memory.

- 2) Adding tiling and loop reordering on top of the baseline schedule results exclusively in schedules that require less internal memory, and thus completely Pareto dominate the baseline points.

- 3) Fusion without recomputation and weight tiling, i.e., the space defined by Goetschalckx and Verhelst [10] does not add many interesting points for the small input versions of L2Net and L3Net. The accesses saved by omitting transfers on the small intermediate layers does not add much for these small networks where the number of weights are relatively significant. When applied to the 4k input networks however, some gains can be observed as the weight transfers become insignificant compared to the data transfers. However, the gains are still rather modest since the remaining transfers on the input layer have also scaled with the input resolution. More interesting are the points for L2NetWide, where fusion does yield larger gains as the number of feature maps increases, and the intermediate transfers start to dominate the remaining input transfers. However, as the weights are again important in these networks, the ideal combination for the Goetschalckx scheduling space, i.e., large inputs and wide intermediate layers, is not achieved in these synthetic benchmarks.

- 4) Enabling weight tiling and recomputation however does yield some interesting points. In particular for the wide networks with small input, i.e., those networks where weights are significant, some schedules with even modest recomputation are found to outperform the Goetschalckx schedules by an order of magnitude in required memory size, demonstrating the added value of the more generic models presented in this work.

- 5) As the input size and number of layers increases, recomputation becomes more and more relevant, but only for very large memory sizes. Apart from these extreme cases, the memory saved by heavy recomputation is rather marginal compared to neighbouring schedules with minimal to no recomputation.

# B. REAL-WORLD NETWORKS

Although above synthetic micro benchmarks provide insight into general trends, it is important to also evaluate the scheduling techniques in the context of real world networks. To this end six widely used networks are selected for experimentation: ResNet50, VGG16, InceptionV3, MobileNetv2, and XCeption as implemented in the Keras framework [11], and DMCNN-VD, the demosaicing as described by Syu *et al.* [22] and also evaluated by Goetschalkx *et al.* allowing for direct comparison. The scheduling Pareto fronts of these networks are given in Figures 7b, 7c, 7d, 7e, and 7g respectively. Because the complete design spaces of these networks are exceptionally large,

FIGURE 6. Pareto schedules of the synthetic networks for the four defined scheduling spaces. The colour maps only apply to fusion & recomputation, and represents the number of multiply-accumulate operations.

FIGURE 7. Pareto schedules of six Real-World networks for the four defined scheduling spaces. The colour maps only apply to fusion & recomputation, and represents the number of multiply-accumulate operations.