Received November 3, 2021, accepted November 23, 2021, date of publication November 25, 2021, date of current version December 8, 2021.

Digital Object Identifier 10.1109/ACCESS.2021.3131094

# **Design and Analysis of InP/InAs/AlGaAs Based Cylindrical Surrounding Double-Gate (CSDG)** MOSFETs With La<sub>2</sub>O<sub>3</sub> for 5-nm Technology

PATTUNNARAJAM PARAMASIVAM<sup>1</sup>, NAVEENBALAJI GOWTHAMAN<sup>©</sup><sup>2</sup>, (Senior Member, IEEE), AND VIRANJAY M. SRIVASTAVA (Senior Member, IEEE)

1 Department of Electronics and Communication Engineering, Prince Shri Venkateshwara Padmavathy Engineering College, Chennai 600127, India

Corresponding author: Naveenbalaji Gowthaman (dr.gnb@ieee.org)

**ABSTRACT** The structural improvement and rapid production of InP, InAs (III-V, binary), and AlGaAs (III-V, ternary) compound semiconductor materials have invariably enabled its utilization in typical highspeed device applications. Using the electronic simulator tool, the ON- and OFF-state drain current (I<sub>ON</sub>/I<sub>OFF</sub>) performance of InP/InAs/AlGaAs High Electron Mobility Transistors (HEMTs) with Lanthanum Oxide (La<sub>2</sub>O<sub>3</sub>) as a dielectric material has been analyzed. Thereafter, a design of cylindrical surrounding gate MOSFET has been planned with this novel heterostructures. The InAs spacer (primary) layer is placed as per requirement below the source and drains the terminal to improve mobility. A heavily doped AlGaAs channel layer is employed beneath the primary layer, followed by the required layers. The given device gate length of  $L_G = 5 \text{ nm}$ , source-drain device length  $L_{SD} = 0.15 \mu m$  and  $V_{GS} = V_{DS} = 1 \text{ V}$  of InP/InAs/Al<sub>0.53</sub>Ga<sub>0.47</sub>As HEMT having Equivalent Oxide Thickness (EOT) of La<sub>2</sub>O<sub>3</sub> as 2 nm (gate dielectric oxide), the measured values of maximum drain current  $(I_{D,max})$ , transconductance  $(G_m)$ , Charge carrier density  $(\rho)$ , and leakage current ( $I_{leak}$ ) are 10 mA/ $\mu$ m, 12 mS/ $\mu$ m, 1.5 C/cm<sup>3</sup>, and 0.03  $\mu$ A/ $\mu$ m, respectively. The electrostatic potential  $(\varphi)$  and electric field (E) are 2.58 V and -47.12 V/ $\mu m$  are obtained when  $V_{DS} = 1$  V. This proposed design enhances the heterostructures immune to all the Short Channel Effects (SCEs) in the RF range that can be used in low power circuits design. Furthermore, the rotational cylindrical structure paves the way for a lesser board area to be occupied to reduce heat generation.

INDEX TERMS Charge carrier density, composite channel, CSDG MOSFET, electrostatic potential, high-k dielectric, nanotechnology, VLSI.

### I. INTRODUCTION

Over the last few decades, the InP and AlGaAs semiconductor materials have excellent electron transport characteristics, making them promising options for future nanoscale CMOS. Indium Phosphide (InP) is a direct band-gap III-V compound semiconductor material with a short carrier time. It is primarily employed for lasers, sensitive photo-detectors, and modulators at 1550 nm wavelength, which is widely used in media communications. Due to its operation with GHz frequency range and excellent intrinsic properties, InP-based transistors are widely used in high-speed applications [1], [2]. Their applications include aerospace industries, high-speed fiber optics, and microwave communications [2]–[4]. Recent

The associate editor coordinating the review of this manuscript and approving it for publication was Rahul A. Trivedi.

High Electron Mobility Transistors (HEMTs) are made with compound semiconductor (AlInN/AlGaN/GaN) materials that are extensively utilized for high-speed applications operating in the Ka-band between 26.5 GHz - 40 GHz and in high power applications at the X-band frequencies between the 8 GHz to 12 GHz. The GaN is a semiconductor material with a wide band-gap (3.6 eV) similar to SiC and diamond, whose band-gap energy is 3.3 eV and 5.5 eV, respectively. These materials exhibit low intrinsic carrier concentrations at high temperatures of above 500°. The sheet charge density, high carrier density, and mobility were considered for high power operations of AlInN/GaN Heterostructure FETs [3].

Feng et. al. [4] and Wong et. al. [5] have proposed two different structures for GaN HEMTs and named them Vertical Polarity Inversion Heterostructures (VPIH) and

<sup>&</sup>lt;sup>2</sup>Department of Electronic Engineering, Howard College, University of KwaZulu-Natal, Durban 4041, South Africa

Ga polar Metal Insulator Semiconductor (MIS) HEMT, respectively. The VPIH structure predominantly utilizes an insulator interlayer to reduce gate interference. In E-mode devices, the N-polar GaN, with a reverse polarization field, is beneficial compared to Ga-polar GaN devices, which are at a disadvantage due to their low access resistance. The AlGaAs grown on the InP layer-base have aided in creating heterostructures and have been extensively researched and widely considered to be the best in matching the semiconductor's lattice constants. The original mobility enhancement methods and heterostructures were not remarkable at ambient temperature, but these structures exhibited promising results at a minimal temperature [6], [7]. To achieve ultra-high frequency applications, Kim et. al. [8] have focused on device structures and scaling methods. To enhance high-frequency operations, reduction in the gate length (Lg < 50 nm), improvement in the transportation of charge carriers either by applied electric field or concentration gradient, upgradation of Electrostatic Integrity Factor (EIF), reduction in the resistance and parasitic capacitance must be taken into consideration.

Fiegna et. al. [9] have analyzed that the SCEs can be controlled by considering various factors like device geometry, increased channel doping, fabricating a device with gate length ( $L_G$ ) < 100 nm, and a thin channel to hold constricted coupling of gate potential with the channel potential. This makes it essential to analyze the effects of Single-Gate (SG) HEMT along with L<sub>G</sub> parameter, the source to drain device length (L<sub>SD</sub>), the material of the channel layer, the oxide layer, and its altered thickness. For the last few decades, amphoteric doping has been prominent in most III-V compound semiconductors. At temperatures between 700 °C - 900 °C, the Silicon atoms act as the acceptors and donors after combining GaAs semiconductors with Arsenic and Gallium layers. Hence, the concentration of Silicon is an essential aspect of amphoteric doping. The surface driving force is powerful at critical doping concentration, such that the dopants drift to the surface faster than the rate of development and are not extended into the semiconductor. Hence, the high impurity concentrations are not permitted to reach an epitaxial growth limit. The n-type and p-type dopants of GaAs, InP semiconductors are Se, Sn, Ge, C, and Zn, respectively [8], [9].

Garcia *et. al.* [10] have analyzed the inertia, memory effects, and diffusion by doping Tellurium (Te) in the GaInP semiconductor. All these parameters depend upon doping profile and the surface growth of Te in the semiconductor. The doping profile matches  $\delta$ -doping Dirac's delta functions when doped with III–V semiconductors. The  $\delta$ -doping technique has several advantages such as the increase in the carrier concentration, vicinity between the channel and the gate conductor, a large gate Breakdown Voltage (BV), reduction of effects due to short channel, and increase in transconductance (G<sub>m</sub>). The investigation of the doping profile with a thickness of few angstroms and a limited temperature below 550 °C had been carried out in previous years [11]–[14]. As a result of

heavy doping, the narrow band-gap occurs in bipolar devices. Thus, the additional amount of doping strongly changes the Fermi level crossing bands at the forward bias junction of the Heterojunction Bipolar Transistor (HBT). This, in turn, changes the accumulation of charges in the devices and varies the thermionic and tunneling currents [15], [16]. The direct tunneling current depends upon the physical thickness and barrier height (h). Hence, the tunneling current is expressed as:

$$I\alpha V. \exp\left[-\frac{4\pi d\sqrt{2m.\phi_b}}{h}\right] \tag{1}$$

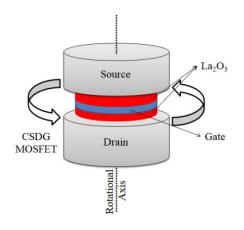

Since 2011, authors have designed Cylindrical Surrounding Double-Gate (CSDG) MOSFET [17], [18] and realized its various parametric analysis. An extension of these, the author's recent research [19] utilizes the La<sub>2</sub>O<sub>3</sub>, which is mainly suitable for high-frequency applications. The capacitance effect in 2D structures was estimated. The gate insulator of the high-k dielectric material (La<sub>2</sub>O<sub>3</sub>) layer plays a vital role. This distinctive material offers greater control over the applied gate voltage. The La<sub>2</sub>O<sub>3</sub> layer oxide in the CSDG MOSFET improves the transistor sub-threshold controllability, and the simulation results clearly illustrate the parametric evaluation, the quantity of energy stored in the cylindrical MOSFET, and the associated electrical field in it.

To extend the author's recent research work of [19], this present research work has been enabled for HEMT design in low power applications. The stacking of several layers of nearby band-gap can enable the resultant heterostructures immune to SCEs and benefit with low power consumption with high-speed switching. This research work has been organized as follows: Section II discusses the basics of MOSFET based on high-\(\epsilon\) dielectric material between the gate and the channel. Section III elaborates the compound semiconductor materials used in the design of HEMTs and heterostructures. Section IV proposes the novel CSDG MOSFET using HEMT technology based on the high-\(\epsilon\) dielectric oxide. Section V has the qualitative analysis followed by the discussions. Finally, Section VI concludes the work and recommends the future aspect.

## II. BASICS OF MOSFETS AND ITS DEVELOPMENTS BASED ON Inp SEMICONDUCTORS

Several researchers proposed Al<sub>2</sub>O<sub>3</sub> as the gate dielectric preferably in InGaAs III–V group semiconductor MOSFETs. Kim *et. al.* [20] illustrated that the channel in the InP quantum-well MOSFET is purely intrinsic and acts as a barrier between the channel and the dielectric gate layer. There are two types of InP-based MOSFETs, surface channel and buried channel MOSFETs. In these two devices, the movement of charge carriers is faster in buried channel MOSFETs than surface channel MOSFETs. This buried channel type MOSFET is considered as one of the notable MOSFET in next-generation CMOS technologies. The prevalence of high mobility in the buried channel MOSFETs is due to its thick InAs layer. Whereas the surface channel MOSFETs,

whose surface layer is rough due to the dielectric oxide layer, developed between the boundaries of the channel. The major drawback in the buried channel MOSFET is that the thickness of the InAs layer reduces the surface scattering and improves channel mobility. Therefore, the buried channel MOSFET shows superior transfer characteristics, resulting in better performance [21]–[23]. The charge density ' $\rho$ ' and state performance are superior in InGaAs MOSFETs than GaAs MOSFETs. There may be production losses when the gate dielectric interface is of poor quality and has high access resistance at the source and drain connections. Thus, the production can be improved by utilizing a lowimpact self-aligned approach by introducing high-quality Aluminum Gallium Arsenide (AlGaAs) channels in InGaAs (MOSFETs). This approach has been used as a shadow mask on top of the T-gate for source and drain deposition. Excellent results are attained when considering the head size of the gate and the separation of 300 nm between source and drain in 0.05- $\mu m$  technology. The fringing capacitance formed by the T-overlap gates with the source/drain areas acts as a drawback, and hence, this solution is not suitable for Very/Ultra Large Scale Integration (VLSI/ULSI) [24]–[27].

## III. COMPOUND SEMICONDUCTOR WITH HIGH-& DIELECTRIC OXIDE MATERIALS

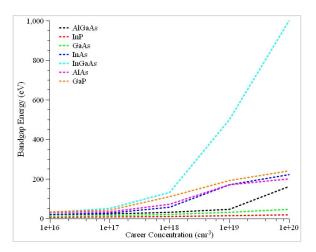

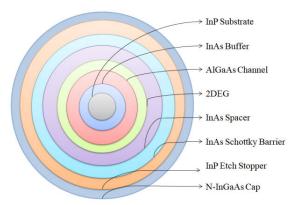

Aluminium Gallium Arsenide (also known as Gallium Aluminum Arsenide) (Al<sub>x</sub>Ga<sub>1-x</sub>As) is a semiconductor material with a higher band-gap than GaAs and a nearly identical one lattice constant. The energy band-gap depends upon the value of aluminum content 'x'. The band-gap energy of  $E_g = 2$  eV and a gap wavelength of  $\lambda_g = 620$  nm is obtained by adding 53 % aluminum content and 47 % Ga content into the AlGaAs semiconductor. The material properties of AlGaAs compared to the attributes of InP are tabulated in Table 1 (appendix). In the manufacturing of InP HEMTs, Si deactivation plays an important role. It primarily deactivates Si impurities in InAs layers. The complete system output degrades when carrier concentration reduces [28], [29]. AlGaAs is a wide band-gap semiconductor material that outperforms other compound materials in the HEMT design. Unfortunately, the materials with a higher band-gap than the AlGaAs exhibit unstable properties in the HEMT construction, as shown in Fig. 1. Thus, AlGaAs act as an appropriate material for design purposes.

Zhao *et al.* [30] and Kim *et al.* [31] have analyzed the inversion-mode surface channel III–V MOSFETs through several dielectric oxides like  $Al_2O_3$  and  $HfO_2$ , HfAlO and  $ZrO_2$  or  $La_2O_3$  dielectrics.  $Ga_2O_3$  dielectrics from Molecular Beam Epitaxy (MBE), Interfacial Passivation Layer (IPL) using Si, Ge,  $Si_xN_y$ ,  $Ge_xN_y$ , or  $Al_xN_y$  and high- $\hat{k}$  gate stack and HfLaO are chosen to exhibit properties with high dielectric constant ( $\epsilon$ ), low OFF current ( $I_{OFF}$ ) good thermal strength, insignificant dispersion, high breakdown voltage, and good consistency. The comparison among each oxide led to achieving the desired results [32]–[35]. The Hafnium-Lanthanum gate insulator has amorphous

FIGURE 1. Band-gap in III-V semiconductors.

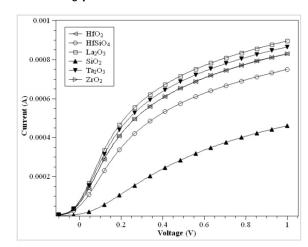

FIGURE 2. Drain characteristics of E- mode AlGaAs MOSFETs with various oxide concentrations.

properties processed with thin-film oxide for high stable performances while operating at low voltage. The mixture of Hf and La exhibits excellent dielectric properties and high crystallization temperature (up to  $900\,^{\circ}C$ ), reduces the leakage current, and improves the high dielectric constant, which is more suitable for future device technologies.

A novel gate stack for III-V QW-MOSFETs was created using a bilayer dielectric consisting of Beryllium Oxide (BeO) and hafnium dioxide (HfO<sub>2</sub>). The BeO exhibits a significant energy band gap (10.6 eV), a wide conduction band offset (E<sub>c</sub>), and a trapping interface layer when compared to Al<sub>2</sub>O<sub>3</sub>. This layer improves the retention properties of MOSFET output by reducing leakage trapped charges [12], [36]. Largely, the drain current is proportional to the thickness of the oxide  $(t_{ox})$  layer. To attain the desired output, Lanthanide Oxide is chosen for its characteristic features. In the Lanthanum Oxide layer, the drain current increases with reduced thickness and its resistive property. Thus, the drain current (I<sub>D</sub>) variations concerning changes in drain-source voltage (V<sub>DS</sub>) with various oxide concentrations are depicted in Fig. 2. The dielectric constant  $\varepsilon$  and leakage currents I<sub>LEAK</sub> usually have a trade-off relationship in a

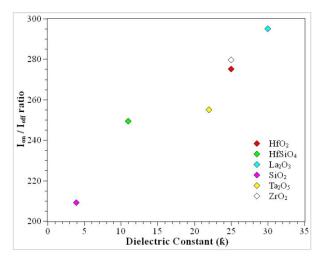

FIGURE 3.  $I_{ON}/I_{OFF}$  ratio in SG MOSFET.

high-k dielectric system. To overcome this severe tradeoff, an appropriate amount of impurities added into HfO<sub>2</sub> using the Atomic Layer Decomposition (ALD) technique is a promising solution. However,  $\varepsilon$  values of most dielectric materials and the gate leakage current of SG-MOSFET are shown in Table 2 (appendix). It has been observed from Table 3 (appendix) the dielectric constant  $\varepsilon$  is inversely proportional to the band-gap. The leakage current proportionality depends upon dielectric constant  $\varepsilon$  of dielectric oxide, the thickness of the oxide layer or gate thickness  $(t_{ox})$ , gate length  $(L_G)$ , and the cross-sectional area (A) of the SG MOSFET. The discussions and comparison of the properties of HfO2 with basic MOSFET by doping with different elements such as N, Si, Al, Ti, and Ta have been carried out [17], [23], [30]. The leakage current densities of both n-MOSFET and p-MOSFET were measured as 9.8  $\times$  $10^{-13}$  and  $9.2 \times 10^{-12}$   $nA/\mu m^2$  under an electric field of +0.75 and -0.75 mV/cm, respectively. The change in ON-current (I<sub>ON</sub>) and OFF-current (I<sub>OFF</sub>) current ratio of E-mode Al<sub>0.53</sub>Ga<sub>0.47</sub>As surface channel SG MOSFET varies differently as compared to the dielectric oxide materials, as shown in Fig. 3. In the associated results of I<sub>ON</sub>/I<sub>OFF</sub> with high-k dielectric constant illustrates, the lanthanum oxide provides OFF-current of  $2.41 \times 10^{-4} A/\mu m$ .

The I<sub>ON</sub>/I<sub>OFF</sub> ratio is expected to be increased by introducing several EOTs as in conventional MOSFETs. The ON-current is the current that passes through the device, while OFF-current is the current that passes through the insulator or high-k dielectric material. The oxide capacitance (C<sub>ox</sub>) between the gate metal and the semiconductor determines the ON-current I<sub>ON</sub>. In contrast, sub-threshold leakage, Gate-Induced Drain Leakage (GIDL), and gate leakage determine the off current I<sub>OFF</sub> in any compound semiconductor MOSFET [37]–[39]. In contrast to gate leakage, sub-threshold leakage makes it impossible to reduce off-state current. The reduction can be possible only when high threshold voltage V<sub>TH</sub> transistors are employed. A Sandwich Tunnel Barrier kind of FET (STBFET) with a

2 *nm* tunneling distance into it had been effective with the conventional design of MOSFETs. The non-local band investigates the device specifications for tunneling, mainly determined by the band-edge profile located around the tunneled cross-sectional area [40], [41].

Accordingly, the electric field at each tunneled location changes dynamically. The result of STBFETs using advanced method standardization with Monte Carlo implantation determines the increase in ON-current ( $I_{ON} > 1 \text{ mA/m}$ ) and OFF-current (I<sub>OFF</sub> at 0.1 mA/m) with a sub-threshold fluctuate less than 40 mV/dec. The high I<sub>ON</sub> current is accomplished by tunneling in the gate region rather than the gate width specified; however, the value of I<sub>OFF</sub> is low, and it mainly depends on spacer thickness. The investigations that the spacer length thickness in any compound semiconductor technology must be within the optimal limit were performed [42]–[45]. Exceeding the limit leads to an increase in source and drain resistances and causes an overall degradation by a decrease in on-state current ION. Compared to SiN and SiO<sub>2</sub>, Lanthanum oxide La<sub>2</sub>O<sub>3</sub> is used as a passivation layer due to its resistivity, lowest lattice energy among the rare earth oxides, and dielectric constant property  $(\varepsilon = 27)$  is 4 - 6 times greater than that of SiO<sub>2</sub>.

The relationship between on-resistance R<sub>ON</sub> and the gate length L<sub>g</sub> is proportional to each other. Thus, R<sub>ON</sub> decreases as gate length (L<sub>G</sub>) decreases. By observing the result, choosing an L<sub>G</sub> < 50 nm to achieve high current I<sub>ON</sub> and maximum transconductance (G<sub>m</sub>) can be inferred. With decreasing L<sub>G</sub>, the device sub-threshold voltage and drain to source voltage (VDS) also increase. It is also evident that the high subthreshold swing and reduced gate length are the major reasons for severe short-channel effects. The InGaAs/InAs/InGaAs composite channel MOSFETs using 1 nm Al<sub>2</sub>O<sub>3</sub>/ZrO<sub>2</sub> as a dielectric with dielectric constant  $\varepsilon = 25$  is suitable for high-frequency applications. When compared ZrO<sub>2</sub> with Al<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub>, the drain current obtained using ZrO<sub>2</sub> as a dielectric is greater as  $520 \,\mu A/\mu m$ than Al<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub>, whose value is 290  $\mu A/\mu m$  and  $400 \ \mu A/\mu m$  for the same EOT = 1.2 nm [46]–[50]. The  $I_{ON}/I_{OFF}$  ratio and  $I_{ON}$  current for  $L_g = 200 \ nm$  are  $220 \times 10^2$  and  $220 \times 10^2 \mu A/\mu m$ . Hence, it is concluded that an increase in drain current of 700  $\mu A/\mu m$  is achieved with an increase in gate length L<sub>g</sub> of 100 nm. With the effect of an increase in gate length L<sub>g</sub>, the I<sub>ON</sub>/I<sub>OFF</sub> ratio also

The mobility of the charge carriers increases concerning the gate voltage. The carrier mobility increases when the channel charge density is less than  $2.6 \times 10^{12}~cm^{-2}$ . Thus, mobility drops when carrier density is increased further. The increase in gate length of 100~nm leads to the rise in drain current of  $700~\mu A/\mu m$ . The  $I_{ON}/I_{OFF}$  ratio increases because of an increase in  $L_G$ . Also, the mobility of the charge carriers increases concerning gate voltage. Under investigation, the carrier mobility increases when the channel charge density is less than  $2.6 \times 10^{12}~cm^{-2}$ . Thus, mobility drops when there is a further increase in carrier density [51]–[53].

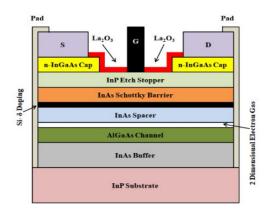

FIGURE 4. Structure of InAs/AlGaAs/InAs HEMT.

## IV. PROPOSED InP/InAs/AlGaAs HEMTS IN CSDG REGIME

Several researchers proposed HEMTs with various compound materials like InP & AlGaN/GaN to improve high frequency, breakdown voltage, transconductance, and noise characteristics. The gate structure has been fabricated to adjust gate recess length ( $L_{gr}$ ) and gate length ( $L_{G}$ ). The condition to improve transconductance ( $G_{m}$ ), drain current ( $I_{D}$ ), and Breakdown Voltage (BV) can be achieved by adjusting with  $L_{gr}$  and  $L_{G}$ . The drain current in HEMT can be controlled by setting up the  $L_{gr}$  with constant  $V_{DS}$  and varying the etch time. Persistent etch time may alter surface hardness and roughness, resulting in decreasing drain current. The frequency response of the HEMT can be increased by reducing the  $L_{G} < 50 \, nm$  [19], [29]. Poor channel modulation and low breakdown voltage exist due to reduced gate length.

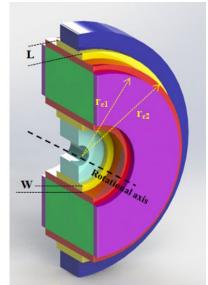

Scaling L<sub>G</sub> and distance from the gate to the channel L<sub>GS</sub> must be examined to achieve excellent performance. Recommended improved results can be achieved by keeping the value of gate-source length concerning drain  $L_{GS}/d$  as maximum. In general, the band-gap energy of InP HEMTs with AlGaAs channel layers (Aluminium content can be up to 30 % depending on the application) increases. The electronic device simulator has been used to create a 5 nm gate-length Al<sub>0.53</sub>Ga<sub>0.47</sub>As/InP based HEMT to demonstrate the features of HEMTs. Fig. 4 shows the cross-sectional structure of the InAs/AlGaAs/InAs HEMT. The arrangement includes a 15 nm InP substrate layer, a 5 nm InAs buffer layer, a 10 nm Al<sub>0.53</sub>Ga<sub>0.47</sub>As channel layer, and a thin layer of undoped InAs is utilized as a spacer layer. To reduce columbic scattering, the undoped InAs have been proposed in this work. The InAs Schottky barrier layer and an InP etching layer are consecutively placed above the channel with a separation of 3 nm thickness.

Hence, adding up indium content in the substrate has been limited to reducing the gate leakage current in the MOSFET regime. The impact ionization in the high indium content material may lead to more gate leakage current. To address these issues, a dielectric layer of La<sub>2</sub>O<sub>3</sub> is sandwiched between the metal gate and the InAs Schottky barrier layer

to provide a high-energy barrier layer. The proposed HEMT has been revolved around the axis outside the substrate to form a cylindrical structure suitable for the design of CSDG MOSFETs with HEMTs.

The addition of aluminum content in the Schottky layer is practiced to avoid leakage current issues, reducing breakdown voltage. The capacitance can be given as:

$$C = \frac{Q}{V} \tag{2}$$

where Q and V are charge and voltage, respectively. It has been substituted with the author's previous work [18, 19]. The voltage is the potential difference between the layers of the cylindrical capacitor between  $r_{c1}$  and  $r_{c2}$  is given as:

$$V = -\int_{r_{c1}}^{r_{c1}} \frac{Q}{2\pi \varepsilon_0 r l} \tag{3}$$

$$V = \frac{Q}{2\pi \varepsilon_0 h} \int_{r_{c1}}^{r_{c2}} \frac{dr}{r}$$

(4)

$$V = \frac{Q}{2\pi\varepsilon_0 h} \ln\left(r \left| \frac{r_{c2}}{r_{c1}} \right| \right) \tag{5a}$$

$$V = \frac{Q}{2\pi\varepsilon_0 h} \ln \frac{r_{c2}}{r_{c1}} \tag{5b}$$

The  $r_{c1}$  and  $r_{c2}$  are shown in Fig. 5(a). The final equation of the voltage across the imaginary capacitance has been given in (5(b)). The flux density along the capacitor has been given as:

$$\phi = \frac{Q_{cap}}{\varepsilon_0} \tag{6}$$

where  $Q_{cap}$  can be substituted with the (7) in (6) to get (9).

$$Q_{cap} = \frac{Q_h}{I} \tag{7}$$

In (6) with the electrical field along with the small distance *ds* changes to:

$$\phi = \int \overrightarrow{E} \cdot \overrightarrow{ds} = E.A = E.2\pi \, rh \tag{8}$$

The voltage differences in the cylindrical structure can be given as the potential difference between the  $r_{c1}$  and  $r_{c2}$ :

$$V_{c1} - V_{c2} = -\int_{r_{c2}}^{r_{c1}} \overrightarrow{E} . \overrightarrow{dr}$$

(9)

The flux has been substituted with the general expressions for the  $Q_{cap}$  and can be rewritten as (10) for the insight of the CSDG regime.

$$\phi = \frac{Q_{cap}}{\varepsilon_0} = \frac{k\varepsilon_0 \frac{A}{d}}{\varepsilon_0} = k\frac{A}{d}$$

(10)

On further reduction, it becomes:

$$\phi = \frac{k\varepsilon_0 \frac{2\pi \left[ (r_{c1}^2 - r_{c2}^2) + h(r_{c1} - r_{c2}) \right]}{d}}{\varepsilon_0}$$

$$\phi = \frac{2\pi k}{d} \left[ \left( r_{c1}^2 - r_{c2}^2 \right) + h(r_{c1} - r_{c2}) \right]$$

(11)

(a) Basic CSDG MOSFET [19]

(b) Proposed CSDG after rotating the HEMT as in Fig. 4

(c) Isometric view of InP/InAs/AlGaAs based CSDG MOSFET

FIGURE 5. Improvement in the basic CSDG MOSFET using InP/InAs/AlGaAs.

It can be used for analysis in the CSDG MOSFET design.

$$\frac{Q_h}{L} = k\varepsilon_0 \frac{2\pi \left[ \left( r_{c1}^2 - r_{c2}^2 \right) + h \left( r_{c1} - r_{c2} \right) \right]}{d}$$

(12a)

$$Q_{h} = \frac{2\pi k \varepsilon_{0} L}{d} \left[ \left( r_{c1}^{2} - r_{c2}^{2} \right) + h \left( r_{c1} - r_{c2} \right) \right]$$

(12b)

$$E_{ox} = \frac{1}{2r} \mu_{0} \mu_{n} k \varepsilon_{0} \cdot \left\{ \left[ \ln \left( \frac{a}{b} \right) \right] - a \right\}$$

$$\cdot \frac{W}{L} \left[ 2 \left( V_{GS} - V_{T} \right) V_{DS} - V_{DS}^{2} \right]$$

(13)

The charge along the height of the capacitor has been derived in (12) and has been used to determine the electrical field of the oxide as in (13). The proposed design can be used to create an extensive structure that abides the cylindrical structural characteristics of the HEMTs.

### **V. RESULTS AND DISCUSSIONS**

To stream charge carriers towards source/drain contact regions and reduce resistance at source and drain-Si- $\delta$  doping concentration ( $20 \times 10^{11}~cm^{-2}$ ) of 2 nm thickness is sandwiched between the InAs Schottky Barrier (SB) and a spacer layer. Introducing a thick InAs SB layer with a thickness of 3 nm reduces gate leakage, eliminates surface scattering, and aids in confining and improving electron mobility in the channel. The difference between EOT and physical thickness is expressed as:

$$C_{ox} = C_{La_2O_3} = \frac{\varepsilon_0.k_{La_2O_3}.L.W}{t_{La_2O_3}} = \frac{\varepsilon_{La_2O_3}.A}{t_{La_2O_3}}$$

$$EOT = t_{La_2O_3} \left(\frac{k_{SiO_2}}{k_{La_2O_3}}\right)$$

(14)

where L and W are the length and width of the channel; A is the area of the channel; k of La<sub>2</sub>O<sub>3</sub> is 2I; k high  $\gg 12$  - 25. In the proposed research work, the direct high-k /Si-sub contact becomes a significant concern when the EOT of the high-k dielectric decreases.

strongly doped n-In<sub>0.7</sub>Ga<sub>0.3</sub>As/In<sub>0.53</sub>Ga<sub>0.47</sub>As MOSFET with the multi-level arrangement in the source and drain terminal significantly reduces its terminal resistances R<sub>S</sub> and R<sub>D</sub>. In addition, the In<sub>0.53</sub>Ga<sub>0.47</sub>As multi-cap layer minimizes the potential barrier in the source/drain access region via the InAs spacer layer, and thus, the channel carrier concentration increases. The higher permittivity of high-k Lanthanum oxide material improvises the accessibility of nanoscale CMOS MOSFETs and also regulates the charge carrier current based on oxide capacitance and gate leakage. The channel behavior of E-mode Ga-polar GaN Metal Insulator Semiconductor (MIS) HEMT has been demonstrated. With a gate length  $L_G = 0.62 \ \mu m$  and a threshold voltage  $V_{TH} = 1 V$ , a high ON-state current I<sub>ON</sub> of 0.74 A/mm is obtained. Due to shorter gate length, the reduction in threshold-voltage roll-off caused DIBL. Feng et al. [28] have proposed GaN-based MIS-HEMT devices composed of nitride stacks with varying polarities that may provide numerous channels via flexible gate(s) control. Thus, a high ON-state current ION of 4 A/mm is achieved by fixing the same  $L_G = 0.62 \ \mu m$  and  $V_{TH} < 2 \ V$ .

Table 4 (appendix) shows the effect of gate length  $L_g=5\,\text{nm}$  on maximum drain current ( $I_{D,max}$ ) and maximum transconductance ( $G_m$ ) of E-mode  $Al_{0.57}Ga_{0.43}As$  channel

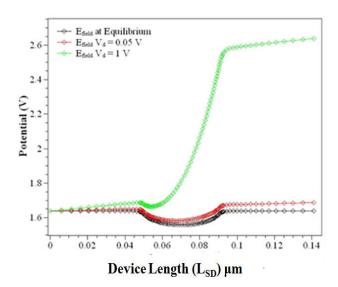

FIGURE 6. Device length Vs. Electro static potential.

MOSFETs with varying drain-source voltages. When  $V_{DS}$  and  $V_{GD}$  are held at 0.78 V and 0.16 V, respectively, the maximum transconductance of 11.4 mS/ $\mu$ m is attained. Table 5 (appendix) compares the proposed InP/InAs/AlGaAs HEMT with standard HEMT. According to the results, the maximum drain current ( $I_{D,max}$ ) of 5.4 mA/ $\mu$ m is reached when  $V_{DS}=0.5~V$  and  $V_{GS}=1~V$ . The leakage current  $I_{leak}$  is given by considering two cases:

Case 1: Drain: ON; Gate: OFF condition (I<sub>G</sub>, OFF) Case 2: Gate: ON; Drain: OFF condition (I<sub>D</sub>, OFF)

$$I_{leak} = [(I_G, OFF) + (I_D, OFF)] \tag{15}$$

where (I<sub>G</sub>, OFF) as when the drain is ON and (I<sub>D</sub>, OFF) as when the gate is ON. Hence, the considered OFF-current depends on V<sub>GS</sub>, V<sub>TH</sub>, and supply voltages (V<sub>DD</sub>) of 0.5 V and 0.05 V, respectively. The I<sub>ON</sub>/I<sub>leak</sub> ratio obtained for the 5 nm enhancement device is of value  $1.8 \times 10^3$ . Thus, it is observed and concluded that the I<sub>ON</sub>/I<sub>leak</sub> ratio decreases when a thin insulator is used in enhancement-mode devices. The E-mode nFETs of L<sub>G</sub> = 30 nm and SiO<sub>2</sub> of 0.1 nm thickness whose I<sub>D</sub> current is measured to be 1.4 mA/ $\mu$ m and transconductance of 2.3 mS/ $\mu$ m when (V<sub>GS</sub>-V<sub>TH</sub>) is positive and is equal to the value of 0.83 V.

Fig. 6 shows the plot of electrostatic potential varied with device length measured between 50 nm - 100 nm. In the absence of drain voltage or equilibrium, the potential variation along the channel has been examined. A potential emerges at the edges (source/drain) in the absence of drain-to-source voltage (V<sub>DS</sub>). The lower potential of 1.5 V occurs close to the middle of the device length, where the channel is placed when drain voltage V<sub>DS</sub> = 0 V and 0.5 V is applied. Between the device lengths of 0.05  $\mu$ m and 0.09  $\mu$ m, an exponential increase in the potential from 1.682 V to 2.639 V arises when V<sub>DS</sub> = 1 V. Besides, the potential remains constant when L<sub>SD</sub>  $\geq$  0.1  $\mu$ m.

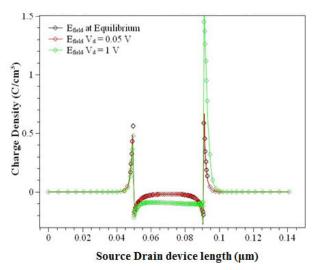

**FIGURE 7.** Source drain Length (L<sub>SD</sub>) Vs. Charge density ( $\rho$ ).

Fig. 7 illustrates the charge carrier density with variations in the structural device length. Here the charge carriers and their mobility in the channel are determined by  $V_{GS}$  and  $V_{DS}$ . However, when  $V_{GS} > V_{TH}$  and  $V_{DS}$  is in equilibrium state at a voltage of 0.05~V, the more accumulation of charge carriers is expected in the device length  $L_{SD}$  of 90~nm from source and drain per unit area defined as charge density ' $\rho$ ', which is equal to  $0.5830~C/cm^3$  and  $0.5905~C/cm^3$ . Further, increase in drain voltage of  $V_{DS} = 1~V$ , the charge carrier density ' $\rho$ ' increases at the peak of  $1.4493~C/cm^3$  whose value is 75 % increase when compared with variation in the drain voltage of 0~V and 0.5~V. Thus, carrier transport efficiency improves in the constant electric field along the channel. This, in turn, provides advantages to measure low-frequency noise measurements on the drain current source.

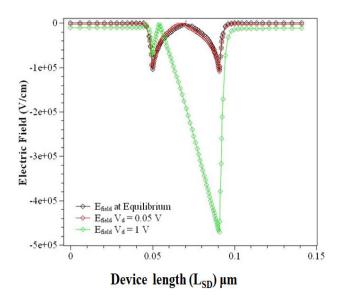

The graph of Fig. 8 between device length vs. electric field along X-and Y-axis, respectively, depict the rapid variations in channel lengths between 50 nm and 100 nm for electric field values at equilibrium, 0.05 V and 1.00 V. At equilibrium V<sub>DS</sub>, the electric field increases to a peak value of -  $50 \text{ mV/}\mu\text{m}$ . As indicated above, the proposed field value increases to a peak value of - 93 mV/ $\mu$ m for V<sub>DS</sub> = 0.05 V. The rise of the vertical electric field 'E' and the shortening of channel length cause carrier dispersion at the surface. As a result, there is less mobility near the surface. Similarly, at  $L_{SD}$  of 90 nm, when  $V_{DS} = 1 V$ , the electric field rapidly reduces to - 47.1259 V/m. When  $V_{DS} = 1 V$ , the lateral electric field in short channel MOSFETs is very high, causing electron injection (hot carrier injection) into the oxide layer and an increase in V<sub>TH</sub>, as seen in Fig. 8. The lateral electric field diminishes over the length of the channel as the V<sub>DS</sub> increases. When the V<sub>DS</sub> is low and the V<sub>GS</sub> is high, the channel potential decays linearly, resulting in a constant electric field. When the drain and gate-source biases are substantial, the electric field created in the channel is strong and fluctuates non-linearly with the position. The electric field is low at the source (at the top of the barrier), but it rises near the drain, reducing the hot carrier effect. In the

FIGURE 8. Device length vs electric field.

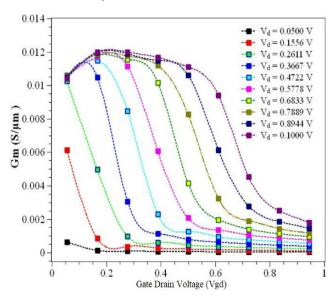

FIGURE 9. The transconductance of E-mode Al 0.53Ga 0.47As surface channel.

saturation region, the increase in  $V_{DS}$  would cause a large potential drop in the channel. Thus, the top of the barrier remains unchanged when DIBL is small.

Asymmetric  $In_{0.53}Ga_{0.47}As/InP$  MOSFETs through different sources and drain have been analyzed.  $In_{0.53}Ga_{0.47}As$  compound semiconductor is currently grown at the source and drain, whereas InP is grown distinctly at the drain. The  $G_m$  and  $I_D$  are proportional to  $L_G$  when monitored (Fig. 9). From the result, it can be inferred that when InGaAs is used as the drain, an increase in drain current and transconductance occurs when the gate length is lowered to  $L_G = 50 \ nm$  rather than  $L_G = 100 \ nm$ . The comparison between InGaAs and InP concludes that InGaAs have superior growth on drain than InP. The properties of lower doping and a wide band-gap of  $1.34 \ eV$  in InP MOSFET achieve reduced Band-To-Band

TABLE 1. Parameters used for capacitance modeling.

| Symbol          | Description of the parameters used                             |

|-----------------|----------------------------------------------------------------|

| a               | The inner radius of the cylindrical capacitor                  |

| b               | The outer radius of the cylindrical capacitor                  |

| $C_{ox}$        | The specific capacitance of the gate oxide                     |

| $C_{ox\_cyl}$   | The cylindrical capacitance (CSDG)                             |

| $E_{cap}$       | Energy stored in the capacitor                                 |

| $E_{cap\_cyl}$  | Energy stored in the cylindrical capacitor (CSDG)              |

| $E_{inner}$     | Energy stored in the inner cylinder                            |

| $E_{outer}$     | Energy stored in the outer cylinder                            |

| h               | Height of the cylindrical capacitor (CSDG)                     |

| L               | The gate length of the transistor                              |

| $L_{c}$         | Unit length of the capacitor                                   |

| r               | The radius of the cylindrical capacitor (General)              |

| $r_{c1}$        | The inner radius of the cylindrical capacitor (CSDG)           |

| $r_{c2}$        | The outer radius of the cylindrical capacitor (CSDG)           |

| $ m V_{GS}$     | Gate to Source voltage                                         |

| $ m V_{DS}$     | Drain to Source voltage                                        |

| $V_T$           | Threshold voltage                                              |

| W               | The width of the transistor                                    |

| $\epsilon_0$    | The permittivity of free space                                 |

| $\epsilon_{ox}$ | The relative permittivity of the gate oxide                    |

| ƙ               | High Dielectric constant (kappa)                               |

| π               | Pi ( $\approx 3.1416$ ), constant                              |

| $\mu_n$         | The electron mobility of the transistor substrate (n-type)     |

| $\mu_0$         | The electron mobility of the transistor substrate (free space) |

**TABLE 2.** Properties of III-V binary and ternary compound semiconductors [19].

| S.No | Properties                                               | InP   | AlGaAs   |

|------|----------------------------------------------------------|-------|----------|

| 1    | Lattice constant(A°)                                     | 5.869 | 5.6351   |

| 2    | Electron Effective Mass                                  | 0.077 | 0.067    |

| 3    | Electron Mobility $\mu_n$ (cm <sup>2</sup> /Vs)          | 4600  | $10^{7}$ |

| 4    | Hole mobility $\mu_p(\text{cm}^2/\text{Vs})$             | 150   | 400      |

| 5    | Velocity Saturation at low field (×10 <sup>7</sup> cm/S) | 2.5   | 2.3      |

| 6    | Band-gap (eV)                                            | 1.35  | 1.93     |

| 7    | $N_C(\times 10^{17} \text{cm}^{-3})$                     | 5.7   | 4.82     |

| 8    | $N_V(\times 10^{18} \text{cm}^{-3})$                     | 9.0   | 4.82     |

TABLE 3. Dielectric oxides vs leakage current for SG-MOSFET.

| Dielectric                     | Dielectric               | Band-gap | Leakage Current               |  |  |

|--------------------------------|--------------------------|----------|-------------------------------|--|--|

| Oxide                          | constant $(\varepsilon)$ | (eV)     | $(I_{OFF})$ ( $\mu A/\mu m$ ) |  |  |

| La <sub>2</sub> O <sub>3</sub> | 27                       | 6        | 2.91                          |  |  |

| $HfO_2$                        | 22-25                    | 5.5-6    | 2.85                          |  |  |

| $ZrO_2$                        | 25                       | 5.8      | 2.90                          |  |  |

| HfSiO <sub>4</sub>             | 11                       | 6.7 -7.3 | 2.8                           |  |  |

| $SiO_2$                        | 4                        | 9        | 1.9                           |  |  |

| $Ta_2O_3$                      | 22                       | 4.4      | 3.23                          |  |  |

**TABLE 4.** Parametric measurement with variation in V<sub>DS</sub>.

| Parameter                           | $V_{DS} = 0.05 \text{ V}$ | $V_{DS} = 0.5 \text{ V}$ | $V_{DS} = 1 \text{ V}$ |

|-------------------------------------|---------------------------|--------------------------|------------------------|

| I <sub>D,max</sub> (mA/μm)          | 0.64                      | 5.4                      | 10                     |

| $G_{\rm m}  ({\rm mS/\mu m})$       | 0.644                     | 11.4                     | 12                     |

| Electrostatic Potential (V)         | 1.6361                    | 1.6739                   | 2.58                   |

| Charge Density (C/cm <sup>3</sup> ) | 0.5830                    | 0.5905                   | 1.5                    |

| Electric Field (V/μm)               | $-5.07 \times 10^{2}$     | $-9.29 \times 10^{2}$    | -47.12                 |

Tunneling (BTBT) effect at drain substrate junction, immune to higher impact ionization at the drain. The same BTBT becomes inconvenient when the thickness of the oxide tox and electric field 'E' increases. The reduction of space length from 8 nm to 3 nm with the supply voltage of  $V_{DS} = 0.5 \text{ V}$  and  $V_{GS} = 0.3 \text{ V}$  decreases the leakage current  $I_{leak}$  in the ratio of 5:I. The spacer length reduces at low drain voltage, thereby causing more degradation in the analog performance.

| MOSFETs   | Dielectric oxide                                  | T <sub>ox</sub> ( nm) | L <sub>g</sub> (nm) | ID <sub>max</sub> (mA/μm) | $G_{m}$ (mS/ $\mu$ m) | $I_{\rm ON}/I_{\rm OFF}$ | I <sub>OFF</sub> (μA/μm) |

|-----------|---------------------------------------------------|-----------------------|---------------------|---------------------------|-----------------------|--------------------------|--------------------------|

| [4]       | GaN                                               | 5                     | 22                  | 0.950                     | 0.45                  | 100                      | 7.4                      |

| [13]      | Al <sub>2</sub> O <sub>3</sub> /InAlAs gate stack | 5                     | 90                  | 0.001                     | 1.32                  | $1.8 \times 10^{3}$      | 5.5×10 <sup>-4</sup>     |

| [15]      | Al <sub>2</sub> O3, HfO <sub>2</sub> and HfAlO    | 8                     | 60                  | 1.8                       | 2.4                   | 1000                     | 1.8                      |

| [19]      | HfSiON                                            | 2.3                   | 15                  | 2.57                      | 0.60                  | $7.73 \times 10^{7}$     | 0.01                     |

| [21]      | $Al_2O_3/ZrO_2$                                   | 1                     | 30                  | 1                         | 2                     | $7 \times 10^{4}$        | 0.01                     |

| [30]      | $Al_2O_3$                                         | 5                     | 500                 | 0.813                     | 0.25                  | $8.13 \times 10^{8}$     | 10×10 <sup>-8</sup>      |

| [37]      | Al <sub>2</sub> O <sub>3</sub> /InAlAs gate stack | 4.6                   | 50                  | 1.327                     | 1.7                   | $1.7 \times 10^{4}$      | 0.07                     |

| [41]      | $\mathrm{SiO}_2$                                  | 1                     | 30                  | 0.514                     | 1.2                   | 5140                     | 0.1                      |

| [50]      | $\mathrm{SiO}_2$                                  | 2                     | 10                  | 1.4                       | 2.3                   | 600                      | 1                        |

| This work | $La_2O_2$                                         | 2                     | 5                   | 5.4                       | 8.4                   | 290                      | 0.03                     |

TABLE 5. Comparison of various HEMTs with conventional HEMTs.

The deterioration occurs when spacer length increases with a less maximum operating voltage than a high driving voltage.

The mechanism of gate leakage in Al<sub>2</sub>O<sub>3</sub>/Al<sub>0.55</sub>Ga<sub>0.45</sub> N/GaN HEMTs  $L_g = 500 \text{ nm}$  and  $Al_2O_3$  of 5 nm thickness whose  $I_D$  current, leakage currents, and  $G_m$  have been measured to be  $8.13 \, mA/\mu m$ ,  $10 \times 10^{-8} \, \mu A/\mu m$ , and  $2.57 \, mS/\mu m$ , respectively at  $V_{DS} = 1 V$  and 0.05 V. The findings suggest that structural improvement is required to increase the FinFET's driving current and prevent degradation of analog performance. The on/off ratio of  $7.73 \times 10^7$  is achieved when the spacer length increases to 80 nm. The OFF- and ON-current decreases from  $10^{-8}$  to  $10^{-13}$  A and  $10^{-4}$  to  $10^{-5}A$ , when spacer length varies from 30 nm to 110 nm. Heterostructures often vary the characteristics based on the calculated gate voltage at the gate to drain terminals. The V<sub>GD</sub> has been analyzed over G<sub>m</sub> values with an L<sub>G</sub> of 5 nm for fixed V<sub>DS</sub>. As an alternative for the gate to source connection, mutual conductance occurs between the gate to drain terminals. It has been observed that the Gm value remains peak in the linear region and exponentially decreases at high V<sub>GD</sub>.

#### VI. CONCLUSION AND FUTURE RECOMMENDATIONS

In this research work, the analog parameters required to build the structure of novel InP/InAs/AlGaAs HEMT with a gate length of  $L_{\rm g}=5~nm$  were investigated. The quantum wave MOSFETs with high- $\hat{k}$  gate dielectrics promise to enhance Moore's law by scaling gate length to 5~nm is considered. Thus, a strong electric field is induced in the channel and fluctuates non-linearly with position when the drain and gate-source biases are kept large. A 10~nm E-mode Al $_{0.53}$ Ga $_{0.47}$ As MOSFET on InP substrates featuring La $_{2}$ O $_{3}$ / InGaAs gate stack obtain a high-level transconductance of  $11.4~mS/\mu m$  and a drain current (ID) of  $5.4~mA/\mu m$ .

The InP technology is favored over other technologies due to its characteristics such as strong intrinsic transconductance, maximum extrinsic transconductance, high drain current, practical breakdown voltage, a high-\hat{k} dielectric layer, low leakage current, and high I<sub>ON</sub>/I<sub>OFF</sub> current. These characteristics play a vital role in millimeter-wave LNA applications and high-speed applications in the THz frequency range.

To achieve high-speed applications in future microelectronics technology, high-k metal oxide film ZrO<sub>2</sub> is to be chosen as the best oxide layer due to its properties,

such as high dielectric constant and low leakage current density. The fabrication involves challenges constrained to the cylindrical environment, but it has potential advantages. The HEMT, after making into the cylindrical surrounding structure, consumes lesser area onboard, making way for other components to be placed.

#### **APPENDIX**

See Tables 1-5.

#### **REFERENCES**

- (2020). International Roadmap for Devices and Systems?. [Online]. Available: https://irds.ieee.org/

- [2] B. Duan, S. Xue, X. Huang, and Y. Yang, "Novel Si/SiC heterojunction lateral double-diffused metal oxide semiconductor with SIPOS field plate by simulation study," *IEEE J. Electron Devices Soc.*, vol. 9, pp. 114–120, 2021.

- [3] P. Ghosh, S. Haldar, R. S. Gupta, and M. Gupta, "An analytical drain current model for dual material engineered cylindrical/surrounded gate MOSFET," *Microelectron. J.*, vol. 43, no. 1, pp. 17–24, Jan. 2012.

- [4] P. Feng, K. H. Teo, T. Oishi, K. Yamanaka, and R. Ma, "Design of enhancement mode single-gate and double-gate multi-channel GaN HEMT with vertical polarity inversion heterostructure," in *Proc. 25th Int. Symp. Power Devices IC's (ISPSD)*, May 2013, pp. 203–206, doi: 10.1109/ISPSD.2013.6694481.

- [5] M. H. Wong, F. Wu, J. S. Speck, and U. K. Mishra, "Polarity inversion of N-face GaN using an aluminum oxide interlayer," *J. Appl. Phys.*, vol. 108, no. 12, Dec. 2010, Art. no. 123710, doi: 10.1063/1.3524473.

- [6] I. Daumiller, C. Kirchner, M. Kamp, K. J. Ebeling, and E. Kohn, "Evaluation of the temperature stability of AlGaN/GaN heterostructure FETs," *IEEE Electron Device Lett.*, vol. 20, no. 9, pp. 448–450, Sep. 1999, doi: 10.1109/55.784448.

- [7] E. Y. Chang, "Realization of GaN-based technology for high power and high frequency applications," in *Proc. IEEE Int. Conf. Semiconductor Electron. (ICSE)*, Kuala Lumpur, Malaysia, Aug. 2014, pp. 27–29.

- [8] T. Kim, D. Kim, and J. A. del Alamo, "60 nm self-aligned-gate InGaAs HEMTs with record high-frequency characteristics," in *IEDM Tech. Dig.*, San Francisco, CA, USA, Dec. 2010, pp. 30.7.1–30.7.4, doi: 10.1109/IEDM.2010.5703454.

- [9] Fiegna, Iwai, Wada, Saito, Sangiorgi, and Ricco, "A new scaling methodology for the 0.1–0.025 μm MOSFET," in *Proc. Symp. VLSI Technol.*, Kyoto, Japan, 1993, pp. 33–34, doi: 10.1109/VLSIT.1993.760231.

- [10] I. García, I. R. Stolle, B. Galiana, and C. Algora, "Analysis of tellurium as the n-type dopant in GaInP: Doping, diffusion, memory effect, and surfactant properties," *J. Crystal Growth*, vol. 298, pp. 794–799, Jan. 2006, doi: 10.1016/j.jcrysgro.2006.10.099.

- [11] R. Chau, S. Datta, M. Doczy, B. Doyle, B. Jin, J. Kavalieros, A. Majumdar, M. Metz, and M. Radosavljevic, "Benchmarking nanotechnology for high-performance and low-power logic transistor applications," *IEEE Trans. Nanotechnol.*, vol. 4, no. 2, pp. 153–158, Mar. 2005, doi: 10.1109/TNANO.2004.842073.

- [12] P. Nagaiah, V. Tokranov, M. Yakimov, S. Koveshnikov, S. Oktyabrsky, D. Veksler, W. Tsai, and G. Bersuker, "Mobility and remote scattering in buried InGaAs quantum well channels with high-k gate oxide," J. Vac. Sci. Technol. B, Nanotechnol. Microelectron., Mater., Process., Meas., Phenomena, vol. 28, no. 3, p. C3H5, May 2010, doi: 10.1116/1.3360903.

- [13] N. Hayafuji, Y. Yamamoto, N. Yoshida, T. Sonoda, S. Takamiya, and S. Mitsui, "Thermal stability of AlInAs/GaInAs/InP heterostructures," *Appl. Phys. Lett.*, vol. 66, no. 7, pp. 863–865, Feb. 1995, doi: 10.1063/1.113412.

- [14] M. Tanabe, N. Kashiwagi, T. Matsuno, and A. Tamura, "The impact of using AlGaAs as a carrier supplying layer in an InAlAs/InGaAs high electron mobility transistor structure on thermal stability," *Appl. Phys. Lett.*, vol. 70, no. 25, pp. 3386–3388, Jun. 1997, doi: 10.1063/1.119179.

- [15] U. K. Mishra, P. Parikh, and Y.-F. Wu, "AlGaN/GaN HEMTs-an overview of device operation and applications," *Proc. IEEE*, vol. 90, no. 6, pp. 1022–1031, Jun. 2002, doi: 10.1109/JPROC.2002.1021567.

- [16] P. Roblin and H. Rohdin, High-Speed Heterostructure Devices: From Device Concepts to Circuit Modeling, 1st, ed. Cambridge, U.K.: Cambridge Univ. Press, 2002.

- [17] V. M. Srivastava, K. S. Yadav, and G. Singh, "Design and performance analysis of cylindrical surrounding double-gate MOSFET for RF switch," *Microelectron. J.*, vol. 42, no. 10, pp. 1124–1135, Oct. 2011, doi: 10.1016/j.mejo.2011.07.003.

- [18] M. A. Uchechukwu and V. M. Srivastava, "Channel length scaling pattern for cylindrical surrounding double-gate (CSDG) MOSFET," *IEEE Access*, vol. 8, pp. 121204–121210, 2020, doi: 10.1109/ACCESS.2020. 3006705.

- [19] N. Gowthaman and V. M. Srivastava, "Capacitive modeling of cylindrical surrounding double-gate MOSFETs for hybrid RF applications," *IEEE Access*, vol. 9, pp. 89234–89242, 2021.

- [20] T. Kim, D.-H. Koh, C.-S. Shin, W.-K. Park, T. Orzali, C. Hobbs, W. P. Maszara, and D.-H. Kim, " $L_g = 80$  nm tri-gate quantum-well  $In_{0.53}Ga_{0.47}As$  metal-oxide-semiconductor field-effect transistors with  $Al_2O_3/HfO_2$  gate-stack," *IEEE Electron Device Lett.*, vol. 36, no. 3, pp. 223–225, Mar. 2015, doi: 10.1109/LED.2015.2393554.

- [21] D. Nirmal, P. Vijayakumar, D. M. Thomas, B. K. Jebalin, and N. Mohankumar, "Subthreshold performance of gate engineered Fin-FET devices and circuit with high-k dielectrics," *Microelectron. Rel.*, vol. 53, no. 3, pp. 499–504, Mar. 2013, doi: 10.1016/j.microrel.2012. 09.008.

- [22] T. Mimura and M. Fukuta, "Status of the GaAs metal—Oxide—Semiconductor technology," *IEEE Trans. Electron Devices*, vol. ED-27, no. 6, pp. 1147–1155, Jun. 1980, doi: 10.1109/T-ED.1980.19998.

- [23] D. A. J. Moran, R. J. W. Hill, X. Li, H. Zhou, D. McIntyre, S. Thoms, R. Droopad, P. Zurcher, K. Rajagopalan, J. Abrokwah, M. Passlack, and I. G. Thayne, "Sub-micron, metal gate, high-k dielectric, implantfree, enhancement-mode III-V MOSFETs," in *Proc. 37th Eur. Solid-State Device Res. Conf.*, Munich, Germany, Sep. 2007, pp. 466–469, doi: 10.1109/ESSDERC.2007.4430979.

- [24] M. Passlack, "Development methodology for high-k gate dielectrics on III–V semiconductors: Gd<sub>X</sub>Ga<sub>0,4-X</sub>O<sub>0,6</sub>/Ga<sub>2</sub>O<sub>3</sub> dielectric stacks on GaAs," J. Vac. Sci. Technol. B Microelectron. Nanom. Struct., vol. 23, no. 4, 2005, doi: 10.1116/1.1943448.

- [25] S. Koveshnikov, W. Tsai, I. Ok, J. C. Lee, V. Torkanov, M. Yakimov, and S. Oktyabrsky, "Metal-oxide-semiconductor capacitors on GaAs with high-k gate oxide and amorphous silicon interface passivation layer," *Appl. Phys. Lett.*, vol. 88, no. 2, Jan. 2006, Art. no. 022106, doi: 10.1063/1.2164327.

- [26] H. Zhao, H.-S. Kim, F. Zhu, M. Zhang, I. Ok, S. I. Park, J. H. Yum, and J. C. Lee, "Metal-oxide-semiconductor capacitors on GaAs with germanium nitride passivation layer," *Appl. Phys. Lett.*, vol. 91, no. 17, Oct. 2007, Art. no. 172101, doi: 10.1063/1.2795802.

- [27] F. Schwierz and J. J. Liou, "Semiconductor devices for RF applications: Evolution and current status," *Microelectron. Reliab.*, vol. 41, no. 2, pp. 145–168, Feb. 2001, doi: 10.1016/S0026-2714(00)00076-7.

- [28] P. Feng, K. H. Teo, T. Oishi, M. Nakayama, C. Duan, and J. Zhang, "Design and simulation of enhancement-mode N-polar GaN singlechannel and dual-channel MIS-HEMTs," in *Proc. Int. Semiconductor Device Res. Symp. (ISDRS)*, College Park, MD, USA, Dec. 2011, pp. 1–2, doi: 10.1109/ISDRS.2011.6135163.

- [29] N. Gowthaman and M. V. Srivastava, "Analysis of InN/La<sub>2</sub>O<sub>3</sub> twosome for double-gate MOSFETs for radio frequency applications," in *Proc. 3rd Int. Conf. Mater. Sci. Manuf. Technol.*, Coimbatore, India, Apr. 2021, pp. 1–10.

- [30] H. Zhao, J. H. Yum, Y. T. Chen, and J. C. Lee, "In<sub>0.53</sub>Ga<sub>0.47</sub>As n-metal-oxide-semiconductor field-effect transistors with atomic layer deposited Al<sub>2</sub>O<sub>3</sub>, HfO<sub>2</sub>, and LaAlO<sub>3</sub> gate dielectrics," *J. Vac. Sci. Technol. B Microelectron. Nanom. Struct.*, vol. 27, no. 4, pp. 2024–2027, 2009, doi: 10.1116/1.3125284.

- [31] K. H. Kim, R. G. Gordon, A. Ritenour, and D. A. Antoniadis, "Atomic layer deposition of insulating nitride interfacial layers for germanium metal oxide semiconductor field effect transistors with high-k oxide/tungsten nitride gate stacks," *Appl. Phys. Lett.*, vol. 90, no. 21, May 2007, Art. no. 212104, doi: 10.1063/1.2741609.

- [32] N. Gowthaman and M. V. Srivastava, "Design of hafnium oxide (HfO<sub>2</sub>) sidewall in InGaAs/InP for high-speed electronic devices," in *Proc. Int. Conf. Mater. Sci. Nanomater.*, London, U.K., Jul. 2021, pp. 1–6.

- [33] M. A. Khan, A. Bhattarai, J. N. Kuznia, and D. T. Olson, "High electron mobility transistor based on a GaN-Al<sub>X</sub>Ga<sub>1-X</sub>N heterojunction," *Appl. Phys. Lett.*, vol. 63, no. 9, pp. 1214–1215, Aug. 1993, doi: 10.1063/1.109775.

- [34] C. Y. Chen, A. Y. Cho, K. Y. Cheng, T. P. Pearsall, P. O'Connor, and P. A. Garbinski, "Depletion mode modulation doped Al<sub>0.48</sub>In<sub>0.52</sub>As-Ga<sub>0.47</sub>In<sub>0.53</sub>As heterojunction field effect transistors," *IEEE Electron Device Lett.*, vol. ED-3, no. 6, pp. 152–155, Jun. 1982, doi: 10.1109/EDL.1982.25519.

- [35] T.-W. Kim, D.-H. Kim, and J. A. del Alamo, "Logic characteristics of 40 nm thin-channel InAs HEMTs," in *Proc. 22nd Int. Conf. Indium Phosph. Rel. Mater. (IPRM)*, Takamatsu, Japan, May 2010, pp. 1–4, doi: 10.1109/ICIPRM.2010.5516257.

- [36] D. Koh, J. H. Yum, T. Akyol, D. A. Ferrer, M. Lei, T. W. Hudnall, M. C. Downer, C. W. Bielawski, R. Hill, G. Bersuker, and S. K. Banerjee, "Novel atomic layer deposited thin film beryllium oxide for InGaAs MOS devices," in *Proc. Int. Conf. Indium Phosph. Rel. Mater.*, Santa Barbara, CA, USA, Aug. 2012, pp. 163–166, doi: 10.1109/ICIPRM.2012.6403347.

- [37] T. Takahashi, K. Makiyama, N. Hara, M. Sato, and T. Hirose, "Improvement in high frequency and noise characteristics of InP-based HEMTs by reducing parasitic capacitance," in *Proc. 20th Int. Conf. Indium Phosph. Rel. Mater.*, Versailes, France, May 2008, pp. 1–4, doi: 10.1109/ICIPRM.2008.4702964.

- [38] J. Ajayan and D. Nirmal, "A review of InP/InAlAs/InGaAs based transistors for high frequency applications," *Superlattices Microstruct.*, vol. 86, pp. 1–19, Oct. 2015, doi: 10.1016/j.spmi.2015.06.048.

- [39] Y. Mishima, T. Kanazawa, H. Kinoshita, E. Uehara, and Y. Miyamoto, "InGaAs tri-gate MOSFETs with MOVPE regrown source/drain," in *Proc.* 72nd Device Res. Conf., Santa Barbara, CA, USA, Jun. 2014, pp. 121–122, doi: 10.1109/DRC.2014.6872327.

- [40] A. Rajoriya, M. Shrivastava, H. Gossner, T. Schulz, and V. R. Rao, "Sub 0.5 V operation of performance driven mobile systems based on area scaled tunnel FET devices," *IEEE Trans. Electron Devices*, vol. 60, no. 8, pp. 2626–2633, Aug. 2013, doi: 10.1109/TED.2013.2270566.

- [41] R. Asra, M. Shrivastava, V. R. M. K. Murali, K. R. Pandey, H. Gossner, and V. R. Rao, "A tunnel FET for VDD scaling below 0.6 V with a CMOS-comparable performance," *IEEE Trans. Electron Devices*, vol. 58, no. 7, pp. 1855–1863, Jul. 2011, doi: 10.1109/TED.2011.2140322.

- [42] J. Park, J. Kim, S. Showdhury, C. Shin, H. Rhee, M. S. Yeo, E.-C. Cho, and J. Yi, "Electrical characteristics of bulk FinFET according to spacer length," *Electronics*, vol. 9, no. 8, p. 1283, Aug. 2020, doi: 10.3390/electronics9081283.

- [43] J. W. Liu, M. Y. Liao, M. Imura, H. Oosato, E. Watanabe, and Y. Koide, "Electrical characteristics of hydrogen-terminated diamond metal-oxide-semiconductor with atomic layer deposited HfO2 as gate dielectric," *Appl. Phys. Lett.*, vol. 102, no. 11, Mar. 2013, Art. no. 112910, doi: 10.1063/1.4798289.

- [44] J. Mo, E. Lind, and L.-E. Wernersson, "Asymmetric InGaAs/InP MOSFETs with source/drain engineering," *IEEE Electron Device Lett.*, vol. 35, pp. 5, pp. 515–517, May 2014, doi: 10.1109/LED.2014.2308925.

- vol. 35, no. 5, pp. 515–517, May 2014, doi: 10.1109/LED.2014.2308925.

[45] A. Kuliev, V. Kumar, R. Schwindt, D. Selvanathan, A. M. Dabiran, P. Chow, and I. Adesida, "0.15 μm gate-length AlGaN/GaN HEMTs with varying gate recess length," *Solid. State. Electron.*, vol. 47, no. 1, pp. 117–122, Jan. 2003, doi: 10.1016/S0038-1101(02)00258-7.

- [46] Ñ. Gowthaman and V. M. Srivastava, "Dual gate material (Au and Pt) based double-gate MOSFET for high-speed devices," *Revista Tecnología Marcha*, vol. 34, no. 6, pp. 10–16, Nov. 2021, doi: 10.18845/tm.v34i6.5966.

- [47] M. Micovic, N. X. Nguyen, P. Janke, W.-S. Wong, P. Hashimoto, L.-M. McCray, and C. Nguyen, "GaN/AlGaN high electron mobility transistors with f of 110 GHz," *Electron. Lett.*, vol. 36, no. 4, p. 358, 2000, doi: 10.1049/el:20000296.

- [48] S. Lee, C.-Y. Huang, D. Cohen-Elias, J. J. M. Law, V. Chobpattanna, S. Krämer, B. J. Thibeault, W. Mitchell, S. Stemmer, A. C. Gossard, and M. J. W. Rodwell, "High performance raised source/drain InAs/In<sub>0.53</sub>Ga<sub>0.47</sub>As channel metal-oxide-semiconductor field-effect-transistors with reduced leakage using a vertical spacer," *Appl. Phys. Lett.*, vol. 103, no. 23, Dec. 2013, Art. no. 233503, doi: 10.1063/1.4838660.

- [49] N. Gowthaman and V. M. Srivastava, "Analysis of nanometer-scale n-type double-gate (DG) MOSFETs using high-k dielectrics for high-speed applications," in *Proc. 44th Int. Spring Seminar Electron. Technol. (ISSE)*, Bautzen, Germany, May 2021, pp. 1–5, doi: 10.1109/ISSE51996.2021.9467619.

- [50] S. P. Kumar, R. Chaujar, M. Gupta, R. S. Gupta, and A. Agrawal, "Analytical modeling and simulation of potential and electric field distribution in dual material gate HEMT for suppressed short channel effects," in *Proc. Asia–Pacific Microw. Conf.*, Bangkok, Thailand, Dec. 2007, pp. 1–4, doi: 10.1109/APMC.2007.4554703.

- [51] A. K. Singh, S. Gurunarayanan, V. Ramachandran, and M. Umashankar, "Edge potential effect on the operation of short-channel devices," *Microelectron. Int.*, vol. 20, no. 3, pp. 23–28, Dec. 2003, doi: 10.1108/13565360310487918.

- [52] S. Koveshnikov, N. Goel, P. Majhi, H. Wen, M. B. Santos, S. Oktyabrsky, V. Tokranov, R. Kambhampati, R. Moore, F. Zhu, J. Lee, and W. Tsai, "In<sub>0.53</sub>Ga<sub>0.47</sub>As based metal oxide semiconductor capacitors with atomic layer deposition ZrO<sub>2</sub> gate oxide demonstrating low gate leakage current and equivalent oxide thickness less than 1 nm," *Appl. Phys. Lett.*, vol. 92, no. 22, Jun. 2008, Art. no. 222904, doi: 10.1063/1.2931031.

- [53] V. M. Srivastava, "Scaling effect on parameters of HfO<sub>2</sub> based CSDG MOSFET," Int. J. Eng. Technol., vol. 9, no. 2, pp. 420–426, Apr. 2017.

**PATTUNNARAJAM PARAMASIVAM** received the B.E. degree in electronics and communication engineering from Madras University, Chennai, Tamil Nadu, India, in 1997, the M.Tech. degree in VLSI design from Bharath University, Chennai, in 2006, and the Ph.D. degree in VLSI design from Anna University, Chennai, in 2020.

She has more than 24 years of teaching and research experience in VLSI design. She has supervised various bachelor's and master's

projects. She has authored and coauthored many technical offerings, including articles in international refereed journals and international/national conferences. Her research interests include low power VLSI circuits, testing of VLSI circuits, and digital electronics.

Dr. Pattunnarajam has become an Active Member of ISTE, India (LM'13), IETE, India (LM'13), IAENG (M'21), and SDIWC (M'19). She is a reviewer in reputed peer-review journals, include Interscience and Springer (JAIHSC).

**NAVEENBALAJI GOWTHAMAN** (Senior Member, IEEE) received the bachelor's degree in electronics and communication engineering, in 2011, the master's degree in VLSI design, in 2013, and the Ph.D. degree in low power VLSI circuits, in 2019.

He is currently a Postdoctoral Research Scholar with the Department of Electronic Engineering, Howard College, University of KwaZulu-Natal, Durban, South Africa. His research interests

include cylindrical surrounding double-gate MOSFETs, low power VLSI circuits, testing of VLSI circuits, and digital electronics. He has more than eight years of teaching and research experience in VLSI design, microprocessors, and microcontrollers. He has supervised various bachelor's and master's projects. He has authored and coauthored more than 120 technical contributions, including articles in international refereed journals, book chapters, and international/national conferences. He has coedited a book entitled *Advanced Controllers for Smart Cities—An Industry 4.0 Perspective* (Springer Nature Switzerland AG), which presents applications of advanced microcontrollers that can control large systems and devices.

Dr. Gowthaman has become an Active Member of IEEE Smart Grid and Smart City Community, India Chapter. He is also a member of ISTE, India (LM'17), IETE, India (LM'17), and IAENG (M'15). He was a recipient of the Best Teaching Faculty, in 2017, the Innovative Research and Dedicated Teaching Professional Award, in 2018, the Young Scientist, in 2018, the Outstanding Researcher Award, in 2018, and the Bright Engineer Award, in 2019. He is an Associate Editor and a Reviewer in many reputed peerreview journals, including *IET C&DT* and *P&UC* (Springer).

**VIRANJAY M. SRIVASTAVA** (Senior Member, IEEE) received the bachelor's degree in electronics and instrumentation engineering, in 2002, the master's degree in VLSI design, in 2008, and the Ph.D. degree in the field of RF microelectronics and VLSI design, in 2012.

He has worked on the fabrication of devices and the development of circuit design. He is currently working with the Department of Electronic Engineering, Howard College, University of KwaZulu-

Natal, Durban, South Africa. He is the author/coauthor of more than 290 scientific contributions, including articles in international refereed journals and conferences, and also the author of various books. He has more than 19 years of teaching and research experience in the area of VLSI design, RFIC design, and analog IC design. He has supervised various bachelor's, master's, and doctorate theses.

Prof. Srivastava is a Professional Engineer of ECSA, South Africa, a Life Member of IEEE-HKN, a Senior Member of SAIEE, a member of IET, and a member of IITPSA. He has worked as a reviewer for several journals and conferences, both national and international.