Received September 15, 2021, accepted October 16, 2021, date of publication October 26, 2021, date of current version November 19, 2021.

Digital Object Identifier 10.1109/ACCESS.2021.3123167

# An Ultra-Low-Power 2.4 GHz All-Digital Phase-Locked Loop With Injection-Locked Frequency Multiplier and Continuous Frequency Tracking

MUHAMMAD RIAZ UR REHMAN<sup>®1</sup>, ARASH HEJAZI<sup>®1</sup>, (Student Member, IEEE), IMRAN ALI<sup>®1</sup>, MUHAMMAD ASIF<sup>®1</sup>, (Member, IEEE), SEONGJIN OH<sup>®1</sup>, (Student Member, IEEE), PERVESH KUMAR<sup>®1</sup>, (Student Member, IEEE), YOUNGGUN PU<sup>®1,2</sup>, SANG-SUN YOO<sup>®3</sup>, (Member, IEEE), KEUM CHEOL HWANG<sup>®1</sup>, (Senior Member, IEEE), YOUNGOO YANG<sup>®1</sup>, (Senior Member, IEEE), YEONJAE JUNG<sup>1,2</sup>, HYUNGKI HUH<sup>1,2</sup>, SEOKKEE KIM<sup>1,2</sup>, JOON-MO YOO<sup>1,2</sup>, AND KANG-YOON LEE<sup>®1,2</sup>, (Senior Member, IEEE) <sup>1</sup>College of Information and Communication Engineering, Sungkyunkwan University, Suvon 16419, South Korea <sup>2</sup>SKAIChips, Sungkyunkwan University, Suvon 16419, South Korea

Corresponding author: Kang-Yoon Lee (klee@skku.edu)

This work was supported by the Technology Innovation Program (or Industrial Strategic Technology Development Program-Development of Integrated Chip for Transceiver and Power Management for Ultrasonic Imaging Scanner) (20011971, Development of Integrated Chip for Transceiver and Power Management for Ultrasonic Imaging Scanner) funded By the Ministry of Trade, Industry & Energy (MOTIE, Korea) and National Research Foundation of Korea (NRF) grant funded by the Korea government (MSIT) (No. 2021R1A4A1033424). This work was also supported by Institute of Information & communications Technology Planning & Evaluation (IITP) grant funded by the

Korea government (MSIT) (No.2019-0-00421, Artificial Intelligence Graduate School Program (Sungkyunkwan University)).

**ABSTRACT** This paper presents a 0.46 mW and 2.4 GHz; All-Digital Phase-Locked Loop (ADPLL) through an Injection-Locked Frequency Multiplier (ILFM) and Continuous Frequency Tracking Loop (CFTL) circuitry for low power Internet-of-Thing (IoT) applications. In the proposed ADPLL architecture to save power, the need for Time-to-Digital Converter (TDC) is eliminated through providing the CFTL circuitry. This feature makes the design compact, low power, and suitable for IoT applications. The proposed design is based on a synthesizable pulse injection and frequency-locked loop along with an ultra-low-power LC Digitally-Controlled Oscillator (LC-DCO). The presented CFTL circuit adjusts the frequency of the DCO continuously and prevents the frequency drift after the reference injection. Inside the designed LC-DCO core, the power consumption is minimized by optimizing the  $g_m$  /I<sub>D</sub> and adjusting the power supply to 0.5 V. The proposed ILFM based ADPLL is fabricated in 55 nm CMOS technology and covers the operational frequency range of 2.402 GHz to 2.480 GHz with a reference frequency of 32 MHz. The measured phase noise performance of the ADPLL is -111.15 dBc/Hz at 1 MHz offset frequency from the carrier frequency of 2.4 GHz. It consumes only 0.46 mW power with an active area of 0.129 mm<sup>2</sup>.

**INDEX TERMS** ADPLL, injection locked frequency multiplier, low power, small area, Internet of Things, digitally-controlled oscillator.

## I. INTRODUCTION

Nowadays, a frequency synthesizer is a key building block of a Radio Frequency (RF) transceiver, which provides the Local Oscillator (LO) signal to convert up or down the signal to the desired frequency band. With the advancement in

The associate editor coordinating the review of this manuscript and approving it for publication was Moussa Ayyash<sup>(D)</sup>.

Complementary-Metal-Oxide-Semiconductor (CMOS) technology, the design of a frequency multiplier based PLL is shifting from analog to digital, for low power and low area target applications [1]. The digital design provides significant advantages in terms of low power and low area [2], [3]. Due to the benefits of the All-Digital Phase-Locked Loop (ADPLL), it becomes an attractive candidate for low power Internet-of-Things (IoT) applications. Traditional ADPLL design utilizes

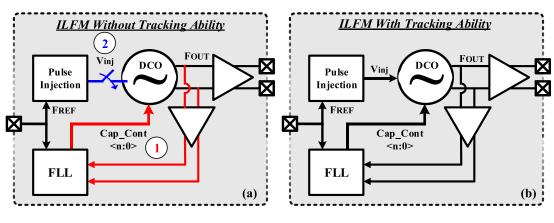

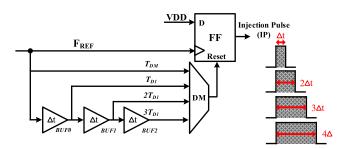

FIGURE 1. Conventional ILFM (a) Injection only (b) injection with frequency tracking.

the Time-to-Digital Converter (TDC) for the phase offset detection [4]–[6]. But due to the high power consumption and complexity of the TDC, it is not suitable for low power design. Recently the Injection-Locked Frequency Multipliers (ILFM) become attractive options for the design of digital PLLs for a low phase noise performance with low power consumption [7]–[9]. As compared to analog sampling PLL, injection locked ADPLL offers less complexity, low cost and less area utilization. Through this technique, a very low jitter integer-N sclock multiplier can be implemented by using a ring oscillator (RO) or an LC Digitally Controlled Oscillator (DCO). The RO offers a wider tuning range with a small area but exhibits poor jitter performance [10]. On the other hand, the LC-oscillator based ILFM offers better phase noise performance and outstanding power efficiency [11]. In [17], [18] an injection locked rotary traveling- wave oscillator (IL-RTWO) is presented which offers low skew clock generation. We can get multiple phases and its provides similar phase noise performance as LC-VCO.

By taking the benefit of the LC-DCO, a low phase noise and power LC-DCO based ILFM is proposed in this paper. It offers low power consumption and better jitter and phase noise performance as compared to the RO based ADPLL or ILFM design.

The error between the oscillator target frequency and the free-running frequency degrades the performance of the ILFM. On the other hand, the work proposed in [12] does only foreground frequency adjustment. After the injection by the reference clock, the frequency of the oscillator drifts due to PVT variations. This frequency drift would not be detected by the frequency-locked loop, and the structure can suffer from large reference spurs. Besides, without continuous frequency tracking ability the ILFM does not offer excellent jitter performance. To keep the oscillator at the target frequency, a frequency tracking loop is required. To overcome this problem the works [4]–[16] propose different techniques to keep the frequency error as low as possible. Although it gives better jitter performance but at the cost of high power consumption and design complexity. Figure 1 demonstrates the two approaches, with and without frequency tracking in the implementation of the ILFM. In Fig. 1(a), a frequency lock loop (FLL) is used to bring the oscillator frequency near to the target frequency. After that, the FLL is disabled and reference frequency ( $F_{REF}$ ) is injected directly to the oscillator. In Fig. 1 (b), an FLL is running continuously in the background to keep the DCO at the target frequency against PVT variations.

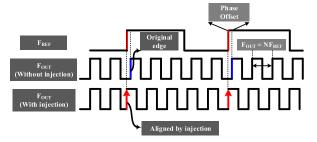

When the frequency tuning of the DCO through the FLL finished, the pulse injection circuit aligns the output phase of the DCO with  $F_{REF}$  and resets the phase error between two clocks. The effect of the reference frequency injection on the DCO output  $F_{OUT}$  is shown in Fig. 2. The relationship of injection pulse width and phase noise performance is analyzed in [14]. Higher harmonic power at frequency 2N.  $f_{REF}$  results in improved phase noise performance of injection-locked oscillator. Asume injection pulse has width D and amplitude  $V_0$  then the Fourier series of 2Nth harmonic power at frequency of 2N.  $f_{REF}$  is given as

$$p(t) = a_0 V_0 + \sum_{n=1}^{\infty} a_n V_0 . cos(2\pi . f_{REF} . n.t)$$

(1)

where  $a_0 = f_{REF}.D$  and  $a_n = \frac{2}{n\pi}.sin(2\pi).f_{REF}.n.\frac{D}{2}$ .

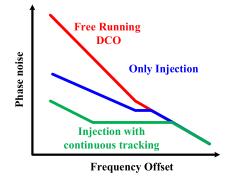

Fig. 3 compares the phase noise performance for free running DCO, ILFM with the only injection, and ILFM with injection and frequency tracking ability. In this paper, an ILFM based ADPLL design is proposed, that offers low complexity and low power consumption. The reference injection controller and FLL controller are designed using HDL, which is fully synthesizable. The major contributions of this paper are as follows:

- Design of low power ILFM based ADPLL, which makes it suitable for low power and low-cost IoT applications.

- Design of FLL and injection controller are fully synthesizable which offers low area and design portability.

- Design of low phase noise and low power LC-DCO that makes the whole design low power and suitable for the required specifications.

The rest of the paper is structured as follows: In section 2, the proposed architecture of the ILFM based ADPLL is

FIGURE 2. Phase adjustment after injection of the reference frequency.

FIGURE 3. Phase noise trend for RI-based ADPLL when Injection without CFTL and injection with CFTL.

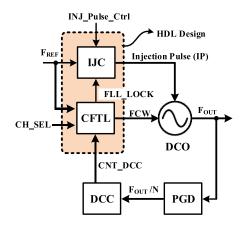

FIGURE 4. Block diagram of the ILFM based ADPLL.

discussed. Experimental results are discussed in section 3. Lastly, the paper is concluded in section 4.

### **II. PROPOSED ILFM BASED ADPLL ARCHITECTURE**

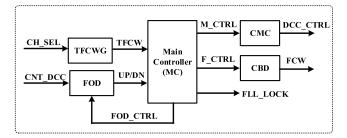

The block diagram of the proposed architecture of the ILFM based ADPLL is shown in Fig. 4. It consists of Injection Controller (IJC), Continuous Frequency Tracking Loop (CFTL), DCO, Programmable Divider (PGD), and DCO Clock Counter (DCC). The task of the CFTL is to bring the DCO output frequency  $F_{OUT}$  to the target center frequency which can be selected by the CH\_SEL. The CFTL is operating at the reference frequency of  $F_{REF}$ . The Frequency Control Word (FCW) is provided to the DCO output ( $F_{OUT}$ ).

FIGURE 5. Block diagram of the injection controller.

FIGURE 6. Block diagram of CFTL.

The F<sub>OUT</sub> is divided by the PGD and the output of the PGD is fed to the DCC. The output of the DCC is used by the CFTL and it is compared with the target value depending on the channel frequency. The CFTL increase or decrease the output frequency of DCO by adjusting the FCW. Once the CFTL brings the DCO frequency to the target frequency, it sets the FLL\_LOCK signal to high and enables the IJC. The IJC adjusts the phase of the DCO by periodically injecting the reference frequency pulse to the DCO. The pulse width of the injection pulse is controlled by the INJ\_Pulse\_Ctrl, and different injection pulse widths would be made through this block. Narrow pulse width for the injection process is essential for reduction in distortion caused by pulse injection. However lock failure can occur due to excessively narrow pulse width or strong distortion can occur due to wide pulse width. Fig. 5 shows the block diagram of the IJC. It mainly consists of the Flip-Flop (FF), Delay Multiplexer (DM), and buffer delay line. It is designed through HDL to make it fully synthesizable. The data input of the FF is set to high, and it is clocked by FREF. The FREF propagates through the delay line.

The output of each delay cell is connected to the DM input. By controlling the INJ\_Pulse\_Ctrl, we can get the delayed version of  $F_{REF}$  at the output of the DM. The output of DM is used to reset the FF to control the injection pulse width. The timing diagram of the operation of the IJC is shown in Fig. 5. The purpose of the CFTL is to bring the free-running DCO output frequency to the target channel frequency. It uses a binary searching algorithm to bring the DCO frequency to the target frequency. Let's suppose we have 40 channels which can be specified through k where k = 0, 1, 2...39. To select a channel among 40 channels, the FLL generates the frequency

FIGURE 7. Flow diagram of CFTL.

control word (FCW) for the DCO by the following equation.

$$N_{FCW}(k) = k + N_{CH0}(\frac{M}{D} \times 10^{-6})$$

(2)

where the  $N_{FCW}(k)$  is the required FCW as a function of k,  $N_{CH0}$  is the base frequency of the channel 0, M is the frequency multiplier for the DCO and DCO frequency division factor is given by D.

The block diagram of the CFTL is shown in the Fig. 6. The main blocks of the CFTL consist of the Main Controller (MC), Counter Mask Control (CMC), Target Frequency Control Word Generator (TFCWG), Frequency Offset Detector (FOD), and Capacitor Bank Decoder (CBD). The CFTL is fully synthesizable and designed by HDL coding. The MC is controlling the overall operation of the CFTL.

The DCC will count the DCO clock cycles within the counter mask duration generated by CMC. The TFCWG generates the target frequency control word (TFCW) which is provided to the MC. The FOD compares the current DCO frequency with the target DCO frequency. It generates the control signals for the MC to increase or decrease the DCO frequency. To achieve the target frequency, the CBD controls the capacitor banks in the DCO and increases or decreases the DCO frequency. The CBD generates a corresponding thermometer code to control the capacitor's bank in the DCO.

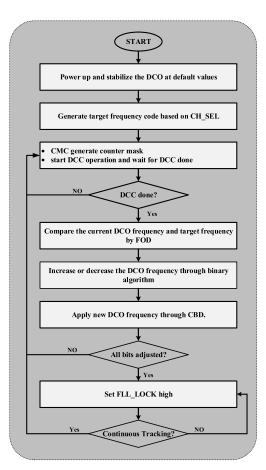

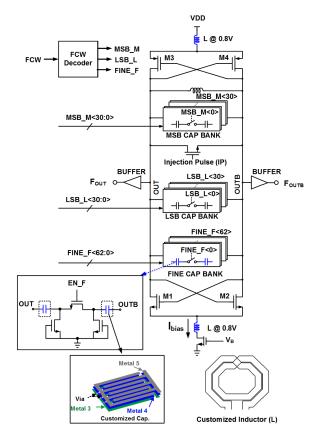

FIGURE 8. Simplified architecture of DCO.

The flow diagram indicating the operation of the CFTL is shown in Fig. 7. When the CFTL is powered up, then it is initialized with the default setting of the DCO and waits till DCO output frequency is stable. Then the TFCW generates the Target\_F code based on the CH\_SEL. The MC provides mask control (M\_CTRL) signal to the CMC to generate the counter mask. The DCC starts counting the number of cycles based on the counter mask provided by DCC\_CTRL. The MC waits till DCC complete its operation. After the completion, the MC activates the FOD to compare the DCO current frequency (CNT\_DCC) and the target frequency.

The FOD generates the UP/DN control signals accordingly to increase or decrease the  $F_{OUT}$ . The MN adjust the DCO frequency through a binary algorithm. The binary algorithm adjusts bits of the capacitor banks from MSB to LSB to achieve target DCO frequency. After adjusting all control bits of DCO, the MN generates the FLL LOCK signal and the DCO output frequency is set at the target frequency. In the case of continuous tracking, the CFTL again calculates the DCO current frequency and compensates any PVT variations. Reference frequency is used as 32 MHz with 50% duty cycle. Duty cycle of reference frequency significantly affects the operation of the ADPLL. It can result in incorrect calculation of output frequency of ADPLL and cause strong distortion at the output of ADPLL.

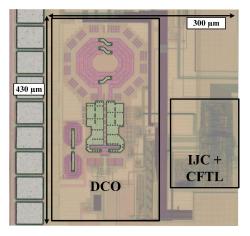

FIGURE 9. Chip photograph of the proposed ILFM based ADPLL.

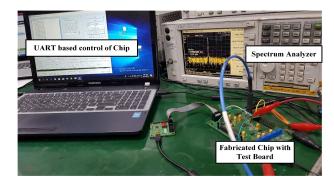

FIGURE 10. Chip measurement setup.

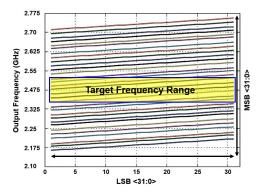

FIGURE 11. Tuning curve of DCO versus tuning codes to cap banks MSB and LSB.

The DCO is designed by focusing on the ultra-low power consumption for IoT applications. The target frequency range of the DCO is from 2.402 GHz to 2.480 GHz. The DCO is designed by MOSFET switches and their sizes are adjusted to provide almost ideal characteristics. During the design, considering the Process, Voltage, and Temperature (PVT) variations, the frequency range of the DCO is optimized to use the maximum inductance value for the resonance. Besides, it offers high swing characteristics and omits the need for increasing current to achieve sufficient swing.

152988

The proposed DCO operates in the sub-threshold region and satisfies the oscillation condition of equation (3) as represented in [13].

$$g_m \ge 1/R_p \tag{3}$$

where gm and Rp are the transconductance of the crosscoupled pair and equivalent parallel resistance of the tank, respectively. The high-frequency resolution is achieved through the fine-tuning bank. The small capacitance is achieved through customized lateral MOM capacitors. This provides low capacitance values of 16.22 aF. An ultra-wide Aluminum (Al) metal layer is used as a superconductor to eliminate routing metal parasitic inductance. The simplified DCO schematic is shown in Fig. 8. Three capacitor banks configurations (MSB CAP BANK, LSB CAP BANK, and FINE CAP BANK) are shown which are controlled by the decoding FCW. A low supply voltage (VDD) of 0.5 V is used for the DCO, which reduces the total power consumption of the DCO circuit efficiently. Each MSB CAP Bank and LSB CAP bank consists of 32 capacitors units. While the FINE CAP bank consists of 64 unit capacitors. The 1-bit resolution of the MSB CAP BANK, LSB CAP BANK, and FINE CAP BANK is 18.7 MHz, 72 kHz, and 4.8 kHz, respectively

# **III. EXPERIMENTAL RESULTS**

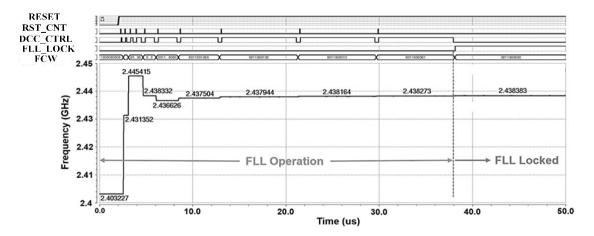

The chip is fabricated using 55 nm CMOS technology. Fig. 9 shows the microphotograph of the proposed chip. The active area of the proposed ILFM is 0.129 mm<sup>2</sup>. The active size of DCO is  $0.1175 \text{ mm}^2$  which mainly because of the inductor. The area of IJC and CFTL is significantly smaller than the DCO. The measurement environment of the proposed ILFM is shown in Fig. 10. It consists of a fabricated chip with the test board, spectrum analyzer, power supply, and UART based control of chip The tuning curves for the DCO versus tuning codes to capacitor banks MSB and LSB are shown in Fig. 11. As we increase the tuning codes for the MSB capacitor bank, the output frequency of DCO is changing with a large frequency offset which is around 18 MHz. Due to PVT variation, the step size for the output frequency of DCO is not equal to the lower tuning range but in target frequency range the output frequency of DCO shows linear step size. The change in LSB tuning codes for the DCO shows almost linear behaviors and it has fewer effects of PVT variation at the DCO output frequency. Phase noise is measured by using divider output which divides the DCO output frequency by a factor of 4. The phase noise performance of the ILFM based ADPLL is about -111.15 dBc/Hz at 1 MHz offset from the carrier frequency of 2.4 GHz. The operation of the FLL is shown in Fig. 12. The DCC generates a counter mask for counting the number of cycles of DCO output. At the start, the difference in the target frequency and DCO output frequency is large so a small counter mask is generated. When the output frequency of DCO is getting closer to the target frequency, CMC adaptively increases the duration of mask for the better accuracy of the target frequency. When the target frequency is achieved at the DCO output, the FLL\_LOCK signal is set high. When the

FIGURE 12. The frequency-locked loop operation.

#### TABLE 1. Performance comparison.

|                                 | [14]    | [15]  | [16]      | [10]     | [7]      | This work   |

|---------------------------------|---------|-------|-----------|----------|----------|-------------|

| Technology (nm)                 | 40      | 55    | 65        | 65       | 65       | 55          |

| Architecture                    | PLL     | PLL   | PLL       | PLL      | PLL      | PLL         |

| Output Frequency<br>Range (GHz) | 0.4-1.6 | 0.216 | 0.52-1.15 | 2.5-5.75 | 2.5-5.63 | 2.402-2.480 |

| Reference<br>Frequency (MHz)    | 50      | 27    | 150       | 125      | 156.25   | 32          |

| Integrated RMS<br>jitter (ps)   | 2.29    | 2.4   | 0.42      | 0.34     | 0.168    | 1.652       |

| Phase noise dBc<br>@1MHz        | -106    | -122  | -119      | -115     | -105     | -110.78     |

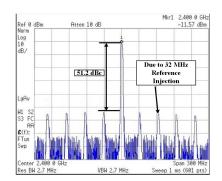

| Spur Level dBc                  | -44     | -70   | NA        | -45      | -42      | -51.2       |

| Power (mW)                      | 1.49    | 6.9   | 3.8       | 5.3      | 15.4     | 0.46        |

| Area (mm <sup>2</sup> )         | 0.14    | 0.03  | 0.028     | 0.09     | 0.06     | 0.129       |

| FOM                             | -231.1  | -224  | -241.3    | -242.1   | -243.6   | -245.3      |

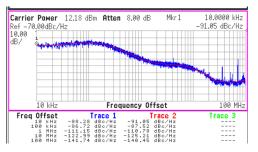

FIGURE 13. Phase noise plot of ILFM based ADPLL at 2.4 GHz.

FIGURE 14. The Spectrum of the output of ILFM based ADPLL after injection of 32 MHz reference.

counter mask is generated through DCC\_CTRL, the counter is reset through the RST\_CNT signal. The phase noise of ILFM based ADPLL is shown in Fig. 13. The output frequency is 2.4 GHz for the measurement of DCO phase noise. The phase noise at offset of 10 kHz, 100 kHz, 1 MHz,

10 MHz and 100 MHz are -88.28 dBc/Hz, -86.72 dBc/Hz, -111.15 dBc/Hz, -122.99 dBc/Hz, and -141.74 dBc/Hz respectively. The Spectrum of the output of ILFM based

ADPLL after injection of 32 MHz reference are shown in Fig. 14. Table 1 shows the comparison of the proposed design with the previous architectures. The integrated rms jitter of proposed design is 1.652ps. Other works such as [16], [10] and [7] shows better integrated rms jitter performance but at the cost of additional hardware which results in design complexity and higher power consumption.

The figure of merit (FoM) to evaluate the performance of the design based on the measured integrated jitter and the power consumption is given by equation (4).

$$FOM = 10\log_{10}\left[\left(\frac{\sigma_t}{1s}\right)\left(\frac{P_{DC}}{1mW}\right)\right] \tag{4}$$

where  $\sigma t$  is integrated jitter, P<sub>DC</sub> is the power consumption of the design, and 1s indicates the one second time reference. Table 1 indicates that FOM of proposed design shows better performance than previous works. It is mainly due to less power consumption as compared to previous designs.

# **IV. CONCLUSION**

An ILFM based ADPLL was proposed for low power IoT sensor applications. The ILFM based ADPLL eliminates the requirement of TDC which makes the design simple and reduces the power consumption. The operating frequency range of the ILFM based ADPLL is from 2.402 to 2.480 GHz. The power consumption of the whole architecture is minimized using all-digital implementation and design of an ultra low power LC-DCO. It consumes only 0.46 mW with an area of 0.129 mm<sup>2</sup>. The phase noise is -111.15 dBc/Hz at 1 MHz offset from the carrier frequency of 2.4 GHz.

#### REFERENCES

- [1] R. B. Staszewski, J. L. Wallberg, S. Rezeq, C.-M. Hung, O. E. Eliezer, S. K. Vemulapalli, C. Fernando, K. Maggio, R. Staszewski, N. Barton, and M. C. Lee, "All-digital PLL and transmitter for mobile phones," *IEEE J. Solid-State Circuits*, vol. 40, no. 12, pp. 2469–2482, Dec. 2005, doi: 10.1109/JSSC.2005.857417.

- [2] I. Ali, H. Abbasizadeh, M. R. U. Rehman, M. Asif, S. J. Oh, Y. G. Pu, M. Lee, K. C. Hwang, Y. Yang, and K.-Y. Lee, "An ultra-low power, adaptive all-digital frequency-locked loop with gain estimation and constant current DCO," *IEEE Access*, vol. 8, pp. 97215–97230, 2020, doi: 10.1109/ACCESS.2020.2995853.

- [3] I. Ali, B. Rikhan, D.-G. Kim, D.-S. Lee, M. Rehman, H. Abbasizadeh, M. Asif, M. Lee, K. Hwang, Y. Yang, and K.-Y. Lee, "Design of a lowpower, small-area AEC-Q100-compliant SENT transmitter in signal conditioning IC for automotive pressure and temperature complex sensors in 180 nm CMOS technology," *Sensors*, vol. 18, no. 5, p. 1555, May 2018.

- [4] A. Hejazi, S. Oh, M. R. U. Rehman, R. E. Rad, S. Kim, J. Lee, Y. Pu, K. C. Hwang, Y. Yang, and K.-Y. Lee, "A low-power multichannel time-to-digital converter using all-digital nested delay-locked loops with 50-ps resolution and high throughput for LiDAR sensors," *IEEE Trans. Instrum. Meas.*, vol. 69, no. 11, pp. 9262–9271, Nov. 2020, doi: 10.1109/TIM.2020.2995249.

- [5] J. Borremans, K. Vengattaramane, V. Giannini, B. Debaillie, W. Van Thillo, and J. Craninckx, "A 86 MHz–12 GHz digital-intensive PLL for softwaredefined radios, using a 6 fJ/Step TDC in 40 nm digital CMOS," *IEEE J. Solid-State Circuits*, vol. 45, no. 10, pp. 2116–2129, Oct. 2010, doi: 10.1109/JSSC.2010.2063630.

- [6] D. Liao, H. Wang, F. F. Dai, Y. Xu, R. Berenguer, and S. M. Hermoso, "An 802.11a/b/g/n digital fractional-N PLL with automatic TDC linearity calibration for spur cancellation," *IEEE J. Solid-State Circuits*, vol. 52, no. 5, pp. 1210–1220, May 2017, doi: 10.1109/JSSC.2016.2638882.

- [7] S.-Y. Cho, S. Kim, M.-S. Choo, H.-G. Ko, J. Lee, W. Bae, and D.-K. Jeong, "A 2.5–5.6 GHz subharmonically injection-locked all-digital PLL with dual-edge complementary switched injection," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 65, no. 9, pp. 2691–2702, Sep. 2018, doi: 10.1109/TCSI.2018.2799195.

- [8] M.-S. Choo, H.-G. Ko, S.-Y. Cho, K. Lee, and D.-K. Jeong, "An optimum injection-timing tracking loop for 5-GHz, 1.13-mW/GHz RO-based injection-locked PLL with 152-fs integrated jitter," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 65, no. 12, pp. 1819–1823, Dec. 2018, doi: 10.1109/TCSII.2018.2878565.

- [9] Z. Zhang, J. Yang, L. Liu, N. Qi, P. Feng, J. Liu, and N. Wu, "An 18–23 GHz 57.4-fs RMS jitter –253.5-dB FoM sub-harmonically injection-locked all-digital PLL with single-ended injection technique and ILFD aided adaptive injection timing alignment technique," *IEEE Trans. Circuits Syst. 1, Reg. Papers*, vol. 66, no. 10, pp. 3733–3746, Oct. 2019, doi: 10.1109/TCS1.2019.2911531.

- [10] D. Coombs, A. Elkholy, R. K. Nandwana, A. Elmallah, and P. K. Hanumolu, "A 2.5-to-5.75 GHz 5 mW 0.3 psrms-jitter cascaded ringbased digital injection-locked clock multiplier in 65 nm CMOS," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, San Francisco, CA, USA, Feb. 2017, pp. 152–153, doi: 10.1109/ISSCC.2017.7870306.

- [11] A. Elkholy, M. Talegaonkar, T. Anand, and P. K. Hanumolu, "Design and analysis of low-power high-frequency robust sub-harmonic injectionlocked clock multipliers," *IEEE J. Solid-State Circuits*, vol. 50, no. 12, pp. 3160–3174, Dec. 2015, doi: 10.1109/JSSC.2015.2478449.

- [12] S. Kim, D.-G. Kim, C. Kim, D. Lee, B. Samadpoor Rikan, Y. Pu, S.-S. Yoo, M. Lee, K. Hwang, Y. Yang, and K.-Y. Lee, "A design of small area, 0.95 mW, 612–1152 MHz open loop injection-locked frequency multiplier for IoT sensor applications," *Sensors*, vol. 18, no. 6, p. 1777, Jun. 2018.

- [13] A. Hejazi, Y. Pu, and K.-Y. Lee, "A design of wide-range and low phase noise linear transconductance VCO with 193.76 dBc/Hz FoMT for mmwave 5G transceivers," *Electronics*, vol. 9, no. 6, p. 935, Jun. 2020.

- [14] C. L. Wei, T. K. Kuan, and S. I. Liu, "A subharmonically injectionlocked PLL with calibrated injection pulsewidth," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 62, no. 6, pp. 548–552, Jun. 2015, doi: 10.1109/TCSII.2015.2407753.

- [15] C.-F. Liang and K.-J. Hsiao, "An injection-locked ring PLL with selfaligned injection window," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, San Francisco, CA, USA, Feb. 2011, pp. 90–92, doi: 10.1109/ISSCC.2011.5746232.

- [16] H. C. Ngo, K. Nakata, T. Yoshioka, Y. Terashima, K. Okada, and A. Matsuzawa, "A 0.42 ps-jitter –241.7 dB-FOM synthesizable injectionlocked PLL with noise-isolation LDO," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, San Francisco, CA, USA, Feb. 2017, pp. 150–151, doi: 10.1109/ISSCC.2017.7870305.

- [17] Z. Bai, X. Zhou, R. D. Mason, and G. Allan, "Low-phase noise clock distribution network using rotary traveling-wave oscillators and built-in self-test phase tuning technique," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 62, no. 1, pp. 41–45, Jan. 2015.

- [18] K. Takinami, R. Strandberg, P. C. P. Liang, G. L. G. de Mercey, T. Wong, and M. Hassibi, "A distributed oscillator based all-digital PLL with a 32-phase embedded phase-to-digital converter," *IEEE J. Solid-State Circuits*, vol. 46, no. 11, pp. 2650–2660, Nov. 2011.

- [19] Z. Yang, Y. Chen, S. Yang, P.-I. Mak, and R. P. Martins, "A 25.4-to-29.5 GHz 10.2 mW isolated sub-sampling PLL achieving -252.9 dB jitter-power FoM and -63 dBc reference spur," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, San Francisco, CA, USA, Feb. 2019, pp. 270–272, doi: 10.1109/ISSCC.2019.8662364.

- [20] Z. Yang, Y. Chen, P.-I. Mak, and R. P. Martins, "A 0.003-mm<sup>2</sup> 440 fsRMS-jitter and -64 dBc-reference-spur ring-VCO-based type-I PLL using a current-reuse sampling phase detector in 28-nm CMOS," in *Proc. IEEE Asian Solid-State Circuits Conf. (A-SSCC)*, Macau, Macao, Nov. 2019, pp. 283–284, doi: 10.1109/A-SSCC47793.2019. 9056944.

- [21] A. Hejazi, B. Jang, R. E. Rad, J. W. Jo, B. S. Rikan, Y. Pu, S.-S. Yoo, K. C. Hwang, Y. Yang, and K.-Y. Lee, "A 2.4 GHz power receiver embedded with a low-power transmitter and PCE of 53.8%, for wireless charging of IoT/wearable devices," *IEEE Trans. Microw. Theory Techn.*, vol. 69, no. 9, pp. 4315–4325, Sep. 2021, doi: 10.1109/TMTT.2021. 3088503.

- [22] Z. Bai, X. Zhou, R. D. Mason, and G. Allan, "A 2-GHz pulse injectionlocked rotary traveling-wave oscillator," *IEEE Trans. Microw. Theory Techn.*, vol. 64, no. 6, pp. 1854–1866, Jun. 2016.

# **IEEE**Access

MUHAMMAD RIAZ UR REHMAN received the B.S. degree in computer engineering and the M.S. degree in electrical engineering from the University of Engineering and Technology, Taxila, Pakistan, in 2007 and 2011, respectively. He is currently pursuing the Ph.D. degree with the School of Information and Communication Engineering, Sungkyunkwan University, Suwon, South Korea. From 2007 to 2016, he was with Horizon Tech Services, Islamabad, Pakistan, where he was a

Senior Engineer of the Product Development Division. His research interests include time to digital conversion systems, and embedded and digital systems design.

ARASH HEJAZI (Student Member, IEEE) was born in Iran, in 1989. He received the Ph.D. degree in electrical and electronics engineering from Sungkyunkwan University (SKKU), South Korea, in 2021. Since 2020, he has been a Senior RFIC Engineer at SKAIChips Company Ltd. His research interests include CMOS RF transceivers blocks (PLLs and frequency synthesizers), RF front-end products for mobile communication systems (RF antenna switches and low-noise amplifiers), and time-to-digital converters for time-of-flight

applications.

IMRAN ALI received the B.S. and M.S. degrees in electrical engineering from the University of Engineering and Technology (UET), Taxila, Pakistan, in 2008 and 2014, respectively, and the Ph.D. degree in electronic and electrical engineering from Sungkyunkwan University, South Korea, in 2020. From 2008 to 2015, he was with Horizon Tech. Services, Islamabad, Pakistan, where he was a Senior Engineer with the Product Development Division and worked on the design and

development of hardware-based crypto/non-crypto systems. He is currently a Postdoctoral Research Associate with the College of Information and Communication Engineering, Sungkyunkwan University. His research interests include digital system design, digital controllers, digital calibration algorithms, artificial intelligence, and analog/digital mixed-signal integrated circuits.

MUHAMMAD ASIF (Member, IEEE) received the B.S. degree in electrical and electronic engineering from the National University of Modern Languages and Science, Islamabad, Pakistan, in 2013, and the M.S. degree in electrical and computer engineering from Sungkyunkwan University, Suwon, South Korea, in 2020. He is currently working as a Researcher with the Integrated Circuits (IC) Laboratory, Sungkyunkwan University. His research interests include the

implementation of power integrated circuits, analog/digital mixed circuits, and CMOS digital controller.

SEONGJIN OH (Student Member, IEEE) received the B.S. degree from the Department of Electronic Engineering, Sungkyunkwan University, Suwon, South Korea, in 2014. He is currently pursuing the combined M.S. and Ph.D. degrees with the School of Information and Communication Engineering, Sungkyunkwan University. His research interests include CMOS RF transceiver, all digital phase-locked loop, wireless power transfer receiver, and rectifier.

PERVESH KUMAR (Student Member, IEEE) received the B.S. degree in electrical (computer) engineering from the COMSATS Institute of Information Technology, Lahore, Pakistan, in 2013, and the M.Sc. degree in computer science from South Asian University, New Delhi, India, in 2015. He is currently pursuing the Ph.D. degree in electrical and computer engineering with the School of Information and Communication Engineering, Sungkyunkwan University, Suwon, South Korea.

His research interests include VLSI systems, digital system design, artificial intelligence, and deep learning.

YOUNGGUN PU received the B.S., M.S., and Ph.D. degrees from the Department of Electronic Engineering, Konkuk University, Seoul, South Korea, in 2006, 2008, and 2012, respectively.

From 2012 to 2013, he worked as a Senior Engineer with the Modem RF Laboratory, DMC Research and Development Center, Samsung Electronics, South Korea. From 2013 to 2019, he worked as a Senior Engineer at WDT/Hivics, South Korea. He is currently a Research Profes-

sor at Sungkyunkwan University. His research interests include high-speed interface, CMOS fully integrated frequency synthesizers, oscillators, and RF transceivers.

SANG-SUN YOO (Member, IEEE) received the B.S. degree from Dongguk University, Seoul, South Korea, in 2004, and the M.S./Ph.D. degree from the Korea Advanced Institute of Science and Technology (KAIST), Daejeon, in 2012. From 2012 to 2015, he worked with the System LSI Division, Samsung Electronics, where he focused on ADPLL for 3/4G mobile applications as a Senior Design Engineer. From 2015 to 2016, he was a Research Assistant Professor with KAIST

and Sungkyunkwan University. Since 2017, he has been with the Department of Smart Automobile, Pyeongtaek University, where he is currently an Assistant Professor. His research interests include RF systems for mobile communications, reconfigurable RFICs, automotive ICs, ADPLL, RFID, and sensor communications.

KEUM CHEOL HWANG (Senior Member, IEEE) received the B.S. degree in electronics engineering from Pusan National University, Busan, South Korea, in 2001, and the M.S. and Ph.D. degrees in electrical and electronic engineering from the Korea Advanced Institute of Science and Technology (KAIST), Daejeon, South Korea, in 2003 and 2006, respectively. From 2006 to 2008, he was a Senior Research Engineer with Samsung Thales, Yongin, South Korea, where he was involved with

the development of various antennas including multiband fractal antennas for communication systems and Cass-grain reflector antenna and slotted waveguide arrays for tracking radars. From 2008 to 2014, he was an Associate Professor with the Division of Electronics and Electrical Engineering, Dongguk University, Seoul, South Korea. In 2015, he joined the Department of Electronic and Electrical Engineering, Sungkyunkwan University, Suwon, South Korea, where he is currently an Associate Professor. His research interests include advanced electromagnetic scattering and radiation theory and applications, design of multi-band/broadband antennas and radar antennas, and optimization algorithms for electro-magnetic applications. He is a Life Member of KIEES and a member of IEICE.

**YOUNGOO YANG** (Senior Member, IEEE) was born in Hamyang, South Korea, in 1969. He received the Ph.D. degree in electrical and electronic engineering from the Pohang University of Science and Technology (POSTECH), Pohang, South Korea, in 2002. From 2002 to 2005, he was with Skyworks Solutions Inc., Newbury Park, CA, USA, where he designed power amplifiers for various cellular handsets. Since March 2005, he has been with the School of Information and

Communication Engineering, Sungkyunkwan University, Suwon, South Korea, where he is currently an Associate Professor. His research interests include power amplifier design, RF transmitters, RFIC design, integrated circuit design for RFID/USN systems, and modeling of high-power amplifiers or devices.

**YEONJAE JUNG** received the B.S., M.S., and Ph.D. degrees from the School of Electrical Engineering, Seoul National University, Seoul, South Korea, in 1997, 1999, and 2003, respectively.

From 2003 to 2014, he was with GCT Semiconductor Inc., San Jose, CA, USA, where he was involved in the design of CMOS RF transceiver ICs for W-CDMA, WLAN, WIMAX, CDMA, GPS, and LTE. From 2014 to 2020, he was with Celfras Semiconductor Inc., where he worked on

BLE v4.2 ultra-low power RF transceiver IC and power ICs for wireless power receiver, battery charger, and dc–dc converter. He is currently a VP with SKAiChips and a University-Industry Collaboration Professor with Sungkyunkwan University. His research interests include the design of power integrated circuits and CMOS RF transceiver.

**HYUNGKI HUH** was born in Seoul, South Korea. He received the B.S., M.S., and Ph.D. degrees from the School of Electrical Engineering and Computer Science, Seoul National University, in 1998, 2001, and 2006, respectively.

From 2001 to 2014, he was with GCT Semiconductor Inc., San Jose, CA, USA, where he was involved in designing wireless transceivers. From 2017 to 2021, he was with Anapass Inc., Seoul, where he was involved in designing

high-speed serial links. In 2021, he joined SKAIChips Company., Suwon, as a Chief Design Officer. He is currently a University-Industry Collaboration Professor at Sungkyunkwan University. His research interests include frequency synthesizers, high-speed communication interfaces, and PMIC.

**SEOKKEE KIM** received the B.S., M.S., and Ph.D. degrees from Seoul National University, South Korea, in 1997, 1999, and 2006, respectively.

From 2001 to 2016, he was with GCT Semiconductor Inc. From 2016 to 2021, he was with Celfras Semiconductor Inc., Seoul, South Korea. In 2021, he joined SKAIChips Company., Suwon, as a Chief Design Officer. He is currently a University-Industry Collaboration Professor at

Sungkyunkwan University. His research interests include analog backend design and mass-production management, power management integrated circuits (PMICs) implementation, and CMOS RF transceiver and SOC integrated implementation.

**JOON-MO YOO** received the B.S. degree from the Department of Electronic Engineering, Ajou University, Gyeonggi-do, South Korea, in 2002, and the M.S. degree from the School of Electrical Engineering, Seoul National University, Seoul, South Korea, in 2004.

From 2004 to 2014, he worked as a Principal Engineer and a Research and Development Manager with GCT Semiconductor, Inc., San Jose, CA, USA, and GCT Research, In.c, South Korea,

where he's developing PHS, CDMA, WCDMA, and LTE RF multi-mode multi band transceivers. From 2014 to 2016, he worked as a Chip Development Director at MELFAS, South Korea, where he was leading the capacitive touch-screen controller IC development. He worked as the Sr. Director at Celfras Semiconductor, Jiangxi, China, from 2016 to 2021, where he leading for the various power of wireless-charging solutions. He is currently working as a Research and Development Executive with SKAIChips, Sungkyunkwan University. His research interests include digital circuit design and CMOS RF transceiver and wireless charging solutions.

**KANG-YOON LEE** (Senior Member, IEEE) received the B.S., M.S., and Ph.D. degrees from the School of Electrical Engineering, Seoul National University, Seoul, South Korea, in 1996, 1998, and 2003, respectively. From 2003 to 2005, he was with GCT Semiconductor Inc., San Jose, CA, USA, where he was a Manager of the Analog Division and worked on the design of CMOS frequency synthesizer for CDMA/PCS/PDC and single-chip CMOS RF chipsets for W-CDMA,

WLAN, and PHS. From 2005 to 2011, he was an Associate Professor with the Department of Electronics Engineering, Konkuk University. Since 2012, he has been with the College of Information and Communication Engineering, Sungkyunkwan University, where he is currently a Professor. His research interests include the implementation of power integrated circuits, CMOS RF transceiver, analog integrated circuits, and analog/digital mixed-mode VLSI system design.

. . .