Received August 16, 2021, accepted September 25, 2021, date of publication October 15, 2021, date of current version October 26, 2021.

Digital Object Identifier 10.1109/ACCESS.2021.3120704

# Frequency-Multiplexed Array Digitization for MIMO Receivers: 4-Antennas/ADC at 28 GHz on Xilinx ZCU-1285 RF SoC

NAJATH AKRAM<sup>®1</sup>, (Member, IEEE), ARJUNA MADANAYAKE<sup>®1</sup>, (Member, IEEE), SRAVAN PULIPATI<sup>®1</sup>, (Member, IEEE), VIDUNETH ARIYARATHNA<sup>2</sup>, (Member, IEEE), SATHEESH BOJJA VENKATAKRISHNAN<sup>®1</sup>, (Senior Member, IEEE), DIMITRA PSYCHOGIOU<sup>®3</sup>, (Senior Member, IEEE), JOHN VOLAKIS<sup>®1</sup>, (Life Fellow, IEEE), THEODORE S. RAPPAPORT<sup>®4</sup>, (Fellow, IEEE),

Corresponding author: Najath Akram (akram.m.n@ieee.org)

This work was supported in part by the U.S. National Science Foundation (NSF) under Grant 800010635.

**ABSTRACT** Communications at mm-wave frequencies and above rely heavily on beamforming antenna arrays. Typically, hundreds, if not thousands, of independent antenna channels are used to achieve high SNR for throughput and increased capacity. Using a dedicated ADC per antenna receiver is preferable but it's not practical for very large arrays due to unreasonable cost and complexity. Frequency division multiplexing (FDM) is a well-known technique for combining multiple signals into a single wideband channel. In a first of its kind measurements, this paper explores FDM for combining multiple antenna outputs at IF into a single wideband signal that can be sampled and digitized using a high-speed wideband ADC. The sampled signals are sub-band filtered and digitally down-converted to obtain individual antenna channels. A prototype receiver was realized with a uniform linear array consisting of 4 elements with 250 MHz bandwidth per channel at 28 GHz carrier frequency. Each of the receiver chains were frequency-multiplexed at an intermediate frequency of 1 GHz to avoid the requirement for multiple, precise local oscillators (LOs). Combined narrowband receiver outputs were sampled using a single ADC with digital front-end operating on a Xilinx ZCU-1285 RF SoC FPGA to synthesize 4 digital beams. The approach allows *M*-fold increase in spatial degrees of freedom per ADC, for temporal oversampling by a factor of *M*.

**INDEX TERMS** Analog-digital conversion, antenna arrays, MIMO systems, millimeter wave radio communication.

#### I. INTRODUCTION

Emerging mm-wave 5G/6G wireless communication systems will rely on multiple-input-multiple-output (MIMO) systems to achieve high capacity and high data-rates while overcoming high path loses and challenging channel conditions [1], [2]. Emerging systems, such as holographic massive MIMO systems used in mmWave, will consist of hundreds if not thousands of antenna elements at the access point [3]–[6]. Maximum ratio combining with interference nulling is neces-

The associate editor coordinating the review of this manuscript and approving it for publication was Walid Al-Hussaibi.

sary and can be achieved using multi-beam digital beamforming at the access point [7]. Fully digital techniques provide the highest flexibility and allows the maximum degrees of freedom as required for maximum capacity. Digital beamforming in antenna arrays has the best flexibility and system capacity when compared to analog and analog-digital hybrid alternatives [4], [8]–[13]. However, digital beamforming also leads to the highest digital and microwave hardware complexity because of the need for dedicated transceivers per spatial channel (antenna) and the exclusive use of digital signal processing (DSP) for all aspects of multi-beam beamforming across all of the antennas [14]–[21]. For example,

AND THOMAS L. MARZETTA <sup>104</sup>, (Life Fellow, IEEE)

Department of ECE, Florida International University, Miami, FL 33174, USA

<sup>&</sup>lt;sup>2</sup>Department of ECE, Northeastern University, Boston, MA 02115, USA

<sup>&</sup>lt;sup>3</sup>School of Engineering, University College Cork, Cork 21, T12 K8AF Ireland

<sup>&</sup>lt;sup>4</sup>Department of EE, NYU Wireless, New York University, Brooklyn, NY 11220, USA

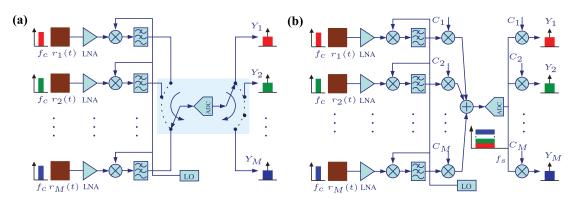

FIGURE 1. Implementation architectures for (a) TDM and (b) CDM-based hardware reduction schemes.

fully-digital multi-beam beamforming and spatial interference nulling at the access point receiver requires a dedicated wideband analog to digital converter (ADC) for every antenna element, leading to N ADCs for N elements in the array.

While emerging wireless concepts such as holographic massive-MIMO requires access to a very large number of ADCs, there has been promising growth in the integrated mixed-signal-RF field which has focused on combining multiple ADCs with programmable logic on the same chip [6], [22]-[28]. The best example is perhaps the advent of RF-enabled digital field programmable gate arrays (RF-FPGAs), such as the Xilinx RF system on chip (SoC) technology. RF SoCs support the combined realization of programmable digital fabrics with highspeed ADC/DAC on the same chip [29]-[31]. Interestingly, RF SoCs have up to16 ADCs/DACs at a bandwidth of more than 1 GHz per channel [32]. However, today's 5G system operating at 28 GHz aim at increasing capacity by increasing the number of spatial channels, with system bandwidths below 800 MHz [33]. A practical bandwidth requirement per channel for a massive-MIMO based systems may be in the sub-200 MHz range. Therefore, we exploit the relatively high bandwidth of available ADCs in order to increase the supported spatial channels (i.e., spatial degrees of freedom) where each channel has relatively low bandwidth requirements in comparison to ADC bandwidth.

Time division multiplexing (TDM), code-division multiplexing (CDM) [34]–[37] and frequency-division multiplexing (FDM) are the three main techniques for combining multiple analog streams into an over-sampled ADC with the objective of ADC reuse over multiple spatial channels. In this case, we are employing FDM and multiplexing of multiple receiver channels into a single wideband signal with subsequent digitization using a high-precision RF-ADC is a trade-off between number of ADCs M and signal bandwidth B [38]. If the sample rate is  $F_s$ , then it follows that multiplexing in the primary Nyquist zone is bounded by  $MB \leq F_s/2$ . The multiplexing of M antenna channels into a single ADC allows M—fold increase in the supported independent spatial channels on a single RF-SoC device.

This paper discusses the possibility of using FDM to multiplex *M* receiver antenna channels to a single ADC. The proposed architecture was experimentally verified for a 4-element uniform linear array (ULA) at 28 GHz [39].

# II. COMPARISON OF TIME-, CODE-, AND FREQUENCY-DIVISION SCHEMES

#### 1) TDM

In TDM, antenna elements are periodically switched to the same RF channel using a commutating analog switch as shown in Fig. 1 (a). The switching rate has to be greater than MB Hz, which in turn, leads to artifacts and non-linearities in the signal due to practical constraints with real-world RF switches. Since signal from each antenna is received for 1/M duration of time, for an M-element system, this approach exhibits a considerable amount of SNR degradation. To overcome this, FDM and CDM based approaches can be considered.

### 2) CDM

CDM solves the problem of switching artifacts and non-linearities by modulating each channel using an orthogonal code (shown in Fig. 1 (b), such as Walsh-Hadamard (WH) codes [40], before summation and digitization in a single ADC [34], [35]. The multiplexed channels are recovered using cross-correlation.

On-site coding receiver (OSCR) is a recently proposed approach [34]-[36] that facilitates the use of a single ADC instead of using dedicated ADC for each antenna element. This approach uses CDM concept to uniquely identify the signal received by the corresponding antenna element as shown in Fig. 1 (b). The receiver consists of a series of analog multipliers to code the output from each receiver by multiplying with a set of orthogonal, binary (typically WH) coded waveforms. Since these coding waveforms are orthogonal, coded outputs from multiple receivers can be summed up without having interference, such that the summed output can be sampled and quantized using a single ADC. Once digitized, the original channels can be recovered with minimal signal degradation using auto-correlation digitally. SNR does not degrade in this approach. Since every signal is coded with a unique code, this approach is resilient to interference and

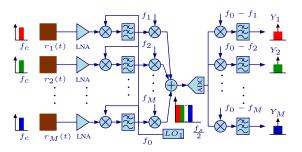

FIGURE 2. Architecture for an FDM-based hardware reduction scheme.

jamming. Combination of multiple channels (M) require M unique modulation waveforms for coded down-conversation and sampling. The bandwidth of these coded outputs extensively increases with the length of the code. Therefore, the ADCs are required to possess high sampling rates and support high bandwidths in order for CDM to be applicable in wideband applications.

#### 3) FDM

Signal received by each antenna is frequency multiplexed into bands with different center frequencies in this approach. FDM based approaches may use a single ADC to process each shared group of channels, but strict filtering is required to separate channels in the digital domain. We propose FDM in multi-antenna access points with fully-digital DSP beamforming. The proposed concept is verified using a 4-element prototype operating at 28 GHz using Xilinx RF SoC ZCU-1285 where a discrete Fourier transform (DFT) is applied spatially to achieve 4 orthogonal receive-mode RF beams at 28 GHz, thereby experimentally verifying M=4- fold increase in the number of supported spatial degrees of freedom per ADC channel.

#### III. DESIGN OF FDM ARRAY RECEIVER

#### A. MULTI-STAGE DOWN-CONVERSION

The proposed system shown in Fig. 2 will employ FDM for M antenna signals into an intermediate frequency (IF) channel where each receiver is frequency translated to a known center frequency using a two-stage down-conversion. In stage - 1, a common local oscillator (LO) is employed to achieve bulk down-conversion to the microwave band  $f_0$ . Subsequently in stage - 2, an M-array of different LOs provide frequency-division multiplexed IF signals that are combined in the analog/microwave domain after suitable passive filtering to obtain the FDM signal that is sampled by a single ADC. After sampling, the IF signal is processed using DSP where FDM multiplexed signals are split into their corresponding antenna channels in baseband using digital sub-band filtering. Sub-band filtering is realized in a real-time DSP filterbank, such as a polyphase finite impulse response (FIR) perfect-reconstruction filterbank [41]. Sub-banded channels are finally down-converted to baseband using a digital downconverter (DDC) per channel. Towards this goal, a variety of DSP filter topologies can be utilized for baseband signal recovery. The recovered signals correspond to the *M* individual antenna channels and are available for subsequent multi-beam DSP beamforming, spatial interference nulling, computation of channel state information (CSI) or any other MIMO signal processing operation.

Major challenges involved with FDM realization include,

- 1) phase synchronization,

- 2) computation of phase offset term corresponding to the element index,

- 3) calibration of analog/digital stage 2 LO, and

- 4) increased digital hardware complexity.

Section III-B presents an extensive analysis on the impact of the first three challenges and proposes an approach to overcome them. Digital hardware complexity reduction is achieved by designing optimized the poly-phase FIR filter structures, which is discussed in section III-C.

# B. PHASE SYNCHRONIZATION AND FREQUENCY LOCKING

FDM across multiple antenna channels require synchronization between the stage-2 analog down-conversion and the digital down-conversion to retrieve phase information from the M channels. Here, we will discuss the mathematical reasoning behind this requirement.

Consider a planar wave impinging on a M-element ULA with an inter-element spacing of  $\Delta x$  at a DOA of  $\psi$ . The signal received by the  $k^{th}$  antenna element  $r_k(t)$  is given by Eq. (1), where x(t) is the information bearing signal.

$$r_k(t) = x(t - \tau_k)\cos(\omega_c t - \theta_k) \tag{1}$$

Here,  $\omega_c = 2\pi f_c$  where  $f_c$  is the carrier frequency,  $\theta_k = \omega_c \tau_k$  and  $\tau_k = \frac{\Delta x \sin \psi}{c} (k-1)$ , c is the speed of light. Since  $x(t-\tau_k) \approx x(t)$  for a narrowband signal, the signal  $p_k(t)$ ,  $k \in [1,2,\ldots,M]$  at each of the  $k^{th}$  receiver after the first down conversion can be expressed as,

$$p_k(t) = LPF \{r_k(t)\cos(\omega_0 t + \phi_0)\}\$$

=  $K_1 x(t)\cos[(\omega_c - \omega_0)t - \phi_0 - \theta_k],$  (2)

where  $K_1$  is a constant dependent on the gain of the LPF response and  $K_1 = 1/2$  for a unit gain filter. Here,  $\omega_0 = 2\pi f_0$  and the angle  $\phi_0$  is the phase of the stage-1 down-converter LO at the initial time of consideration (i.e., t=0). For  $(\omega_c - \omega_0) = \omega'$ , Eq. (2) is simplified as,

$$p_k(t) = K_1 x(t) \cos(\omega' t - \theta_k - \phi_0). \tag{3}$$

Assume there exists a temporal offset of  $t'_k$  between the stage-2 downconverter and the digital downconversion stage. This  $t'_k$  is caused by propagation delays and synchronization issues between two systems. If the  $k^{th}$  frequency division multiplexed output is  $q_k(t)$  at the second stage of downconversion, it is given by

$$q_k(t) = LPF \left\{ p_k(t) \cos(\omega_k(t - t'_k)) \right\}$$

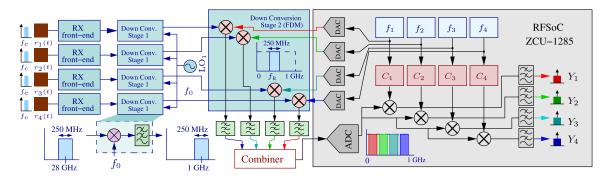

FIGURE 3. System overview of the prototype 28 GHz 4-element FDM array receiver with 240 MHz bandwidth per channel.

$$= LPF \left\{ p_k(t) \cos(\omega_k t - \underbrace{2\pi (ku + v)t'_k)}_{k\alpha + \beta + \phi_k}) \right\}. \quad (4)$$

Since each of the  $k^{th}$  frequency band in the FDM output has a unique center frequency, the discrete frequency variable  $\omega_k$  can be expressed as,  $\omega_k = 2\pi(ku + v)$  where  $(u, v) \in \mathbb{R}$ . Since  $t_k'$  is a constant for a channel, we can find three angles  $\alpha, \beta, \phi_k$ , such that,  $2\pi(ku + v) = k\alpha + \beta + \phi_k$ , where  $0 \le (\alpha, \beta, \phi_k) \le \pi$ . The angle  $\phi_k$  is caused by the mismatch of propagation delays and  $\phi_k = 0$ ;  $k = [1, 2, \ldots, M]$  for equal length paths of propagation. The term  $k\alpha + \beta$  is caused by out of synchronization of analog FDM LOs and corresponding digital downconverter LOs. Therefore,

$$q_{k}(t) = LPF \left\{ K_{1}x(t)\cos(\omega't - \theta_{k} - \phi_{0}) \cos(\omega_{k}t - k\alpha - \beta - \phi_{k}) \right\}$$

(5)

$$= K_{2}x(t)\cos\left((\omega' - \omega_{k})t - \theta_{k} + \phi_{k} + k\alpha + \beta - \phi_{0}\right)$$

(6)

Equation (6) shows that the phase shift has a linear dependency on the array index k, in addition to the phase shift caused by the inter-element propagation delay  $\theta_k$ , for equal length (i.e.,  $\phi_k = 0$ ) propagation. The digital beamforming core takes  $\theta_k$  into account, and the  $\phi$  parameter could be eliminated by calibration. Yet, the  $k\alpha$  term still remains and causes an additional, progressive phase offset between each of the downconverted channels. Frequency mismatches and additional phase offsets have considerable effects in beamforming applications. consequently, use of frequency locked oscillators allow the digital downconverter to bring FDM channels down to the same frequency as required by the digital beamformer. In order for the proposed approach to be used in beamforming, it is required to eliminate the  $k\alpha$  term from the equation.

This can be achieved by the use of the same LO samples in the digital downconverter to generate the stage-2 LO signal to ensure synchronization. This requires the operation of both ADC and the DAC using the same clock. A calibration stage is required between the DAC oscillator and the digital

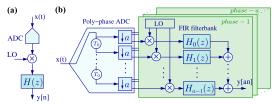

**FIGURE 4.** Architectures of the (a) digital down-conversion and (b) poly-phase filterbank.

downconverter to compensate for the phase offset term corresponding to the element index (i.e., $(k\alpha + \phi_1 + \phi_2)$  term).

The complex calibration coefficient  $C_k = A_k e^{-j[\phi + k\alpha]}$  is determined by a test downconversion measurement at the broadside, and this value can be used to compensate for the issues caused by different cable lengths and RF components as shown in Fig. 3. Finding the  $C_k$  values using an oscilloscope before sampling is challenging, since all the M inputs are combined at the ADC input. Therefore,  $C_k$  needs to be set to (1+0j) for all k in the initial design and corresponding phase and magnitude offsets of the digitally downconverted (DDC) signals are measured at the broadside. To compensate for these magnitude mismatches and the phase offsets, calibration coefficients are updated and the digital design is regenerated.

# C. DDC AND FIR FILTERING

High sampling rates of ADCs (GSamples/s) can provide billions data samples per second. However, the operation frequency of digital hardware is limited due to certain timing restrictions as dictated by the critical path delay (CPD) in the design. Complex designs introduce larger CPDs to the system, which leads to a reduction of the operable clock frequency and these designs often run at few hundreds of MHz rates. Therefore, it is required to have a parallel processing system to process multiple samples at each digital hardware clock cycle. In practice, high speed ADCs in an RF chain (shown in Fig. 4(a)) provide a polyphase data stream as shown in Fig. 4(b). A *a*—phase system, the ADC provides *a* samples at each digital hardware clock cycle as illustrated. Therefore, it is required to follow a polyphase architecture in implementing desired filter structures.

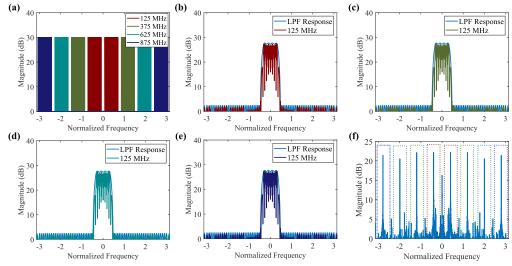

FIGURE 5. Simulations of a) combined output from the second stage downconversion. Digital downconversion and filtering for narrowband signals centered at (b) 125 MHz, (c) 375 MHz, (d) 625 MHz, and (e) 875 MHz. (f) Measured combined signal sampled by Xilinx ZCU-1285 RF SoC.

FIGURE 6. Experimental setup used for Digital FDM multi-beam measurements. (a) 28 GHz 4—element receiver array supported by FDM down-conversion stage, (b) 28 GHz horn antenna transmitter with an 28 GHz up-converter module from Analog Devices (c) Xilinx RF SoC ZCU1285 digital hardware platform.

Use of polyphase ADCs and implementation of the FIR filterbank in polyphase results in lower clock rate requirement for sampling and signal processing. Derivation of polyphase filter function follows an approach similar to radix factorizing in discrete Fourier transform implementations. Assuming an ADC of a channels with an  $f_s/2$  sampling clock is used and the  $K^{th}$ -order FIR filter with a Z domain transfer function H(z) is given by coefficients b:

$$y[n] = \sum_{k=0}^{K} b[k]x[n-k].$$

(7)

By factorizing Eq. (7), polyphase filter functions for a phases can be derived as;

$$y[n] = \sum_{k=0}^{K/a} b[ak]x[a(n-k)]$$

$$+\sum_{k=0}^{K/a} b[ak+1]x[a(n-k)+1] + \dots + \sum_{k=0}^{K/a} b[ak+a-1]x[a(n-k)+a-1].$$

$$+ \dots + \underbrace{\sum_{k=0}^{K/a} b[ak+a-1]x[a(n-k)+a-1]}_{H_{a-1}}.$$

(8)

The filterbank can be implemented in polyphase as shown in Fig. 4(b). It should be noted that, the output data stream from each of phase is undersampled by a factor of a and, the set of a phases reconstruct the total response together by providing a sets of outputs at every digital clock period. However, as the same filter is repeated a times, the hardware complexity for polyphase structures increases by a factor of a. Designing FIR filters in the digital domain and determining

**FIGURE 7.** (a) Dimensions of the designed patch antenna sub-array; (b) CST-simulated vs. measured return loss (|S<sub>11</sub>|).

FIGURE 8. Comparison of measured and CST-simulated polar pattern of the sub-array at 28 GHz. Note that the polar pattern is along the axis of the array i.e., in the elevation plane.

the guard band  $(B_g)$  carry a tradeoff between the system bandwidth and hardware complexity. We aim to pack as many frequency bands in the spectrum with the smallest possible guard band. FIR filter implementations to filter closely packed frequency bands require high order "brick-wall filter" like structures. Poly-phase implementations of FIR filters require extensive hardware resources. We employed the Xilinx SSR blockset for Xilinx RF-SoCs. For synchronization, both the DAC and the ADC use a common clock signal.

## D. TEST-BED VALIDATION OF FDM-DIGITIZATION

A bank of M phase- and frequency-locked oscillators are used to frequency translate inputs at known frequency offsets. The proposed FDM architecture is shown in Fig. 3. Here stage-2 oscillators are required to be synchronized using a stable low-jitter reference clock via a bank of integer-N frequency synthesizers with each other as well as with the digital down-conversion clock. To achieve precise synchronized samples, we use an RF-SoC DAC to generate  $LO_2$  while using the same sampling clock for both the ADC and the DAC. A double-sided signal bandwidth of B=240 MHz per receiver, each

FIGURE 9. Down conversion *stage* – 2 setup for 4 element, 28 GHz antenna array.

designed for 28 GHz operation, have been assumed. The double-sided bandwidth of 4 frequency multiplexed channels with a 10 MHz guard band ( $B_g$ ) per channel is 1 GHz.

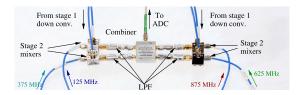

In the next stage (stage - 2), the IF signals are down-converted to the required IF for sampling, centered at  $LO_{2,k} = 250k - 125$  MHz, where k = 1, 2...M. LO frequencies of 125, 375, 625, and 875 MHz are then applied to each of the antennas to translate the received signals to 875, 625, 375, and 125 MHz center frequencies, respectively. These IF components are fed into a combiner to create the FDM signal. Note that the FDM "baseband" can be sampled using a single ADC and the subsequent digital signal can be filtered, down-converted, and subjected to a Hilbert transform to obtain the quadrature component. The inter-band frequency guard bands  $B_g$  are needed for accommodating finite order FIR filtering in the digital domain. The output from this second stage analog down-conversion is fed to the ADC and sampled at  $F_s = 2$  GHz sampling rate.

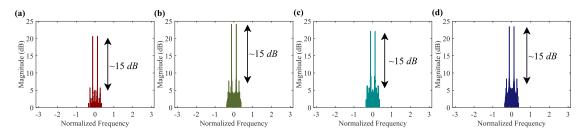

Figure 5 a) shows the sampled spectrum for M=4 FDM channels each having a 250 MHz bandwidth (i.e., including  $B_g$ ). Simulations have used a combination of 32 tones with 240/32=7.5 MHz space to generate the wideband signal, such that  $\sum_{n=1}^{16}\cos(2\pi(f_k\pm7.5~n)t)$  for k=1,2,3,4. DDC leads the aliased image components to fall back into the same Nyquist zone. Highly-selective FIR low-pass digital filters of order 70 were applied to filter out the image components from each of the antenna spectra. The simulation of DDC shows the filtered spectrum in Figs. 5 (b-e).

#### E. DIGITAL FDM MULTI-BEAM MEASUREMENTS

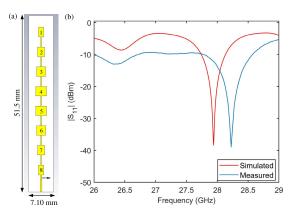

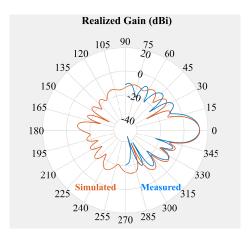

The proposed digital FDM concept is verified through measurements by using a prototype experimental setup shown in Fig. 6. A four-element patch antenna array operating in the frequency range of 27.5-28.35 GHz designed in [42] is employed for this work. Each patch antenna is an 8-element series fed patch sub-array. Series-feeding structure provides additional gain in the elevation plane and also by tapering the patch widths, we can significantly reduce the side-lobe levels. Following the analysis described in [43] and wavelengthapart series-fed analysis in [44], design dimensions for each patch were calculated for the board specifications shown in Table 1. The sub-array is designed in CST antenna simulation software. The dimensions for each patch are shown in Table 2, and its geometry is shown in Fig. 7 (a). Matching to the 50  $\Omega$  feed is based on a quarter-wave transformer. Completed details about the design can be found in one of our

FIGURE 10. Retrieved carrier signals digitally down-converted to baseband having SINR  $\approx$  15 dB.

TABLE 1. Specifications for the patch antenna design.

| Frequency $(f_0)$                  | 28 GHz   |

|------------------------------------|----------|

| Substrate                          | RO4350B  |

| Dielectric constant $(\epsilon_r)$ | 3.66     |

| Dielectric height (h)              | 0.254 mm |

**TABLE 2.** Dimensions for the patch antenna design.

| Patches | 1st, 8th | 2nd, 7th | 3rd, 6th | 4th, 5th |

|---------|----------|----------|----------|----------|

| Width   | 1.55     | 2.06     | 2.59     | 3.12     |

| Length  | 2.81     | 2.77     | 2.74     | 2.72     |

recent works [42]. Simulated and measured results for  $|S_{11}|$  are shown in Fig. 7(b), whereas far-field patterns (vertical plane) are shown in Fig. 8. The proposed antenna resonates at 28.25 GHz with a return loss of 27.41 dB. Measured realized gain pattern of the sub-array coincides with the simulation at 28 GHz. Notably, the antenna was measured in an anechoic chamber and the pattern in Fig. 8. The tapered array results in a SLL less than -18 dB, compared to -13 dB for uniform excitation. The 4-element ULA is built using four sub arrays with a separation of 0.75 wavelengths (8.0 mm at 28 GHz) which is employed for this measurement.

Following this, the down conversion stage-1 for each of the 28 GHz receiver antennas are using Analog Devices EVAL01-HMC1065LP4E [45] module containing the HMC1065 chips. The experimental validation requires an initial measurement to calibrate the phases of each of the RF channels and synchronize  $f_k$  with DDC LO. Therefore, a pilot tone is transmitted at 28 GHz and the antenna array is used to receive the signal at a DOA of  $0^o$  measured from the broadside.

Each EVAL01-HMC1065LP4E RF receiver contains an internal frequency doubling circuit in the LO path of the first down-conversion stage. National instruments RF signal generator was used to generate the first LO signal of 13.5 GHz, yielding an LO of 27 GHz. The 1 GHz centered IF signals resulted from mix-down operation are low pass filtered for image-rejection and noise suppression, and passed to the second down-conversion stage as shown in Fig. 9.

RF-SoC DACs were used to generate the four phase and frequency synchronized LO frequencies that are needed for the stage-2 down-conversion. Frequency translation at the second stage, down-converts antenna outputs to differ-

ent center frequencies such that, corresponding narrowband signals of 4 antennas are visible at 125 MHz, 375 MHz, 625 MHz, and 875 MHz. Four MiniCircuits commercial-off-the-shelf (COTS) RF mixer ZX05-12MH-S+ was used in *stage* – 2 followed by VLF-180, VLF-400+, VLF-630+, and VLF-800 LPFs respectively. These LPFs were chosen to have sufficient attenuation to suppress the effect of second order harmonic of the corresponding FDM channel. COTS combiner ZFRSC-4-842-S+ was used to combine four FDMed RF channels together.

After the stage-2 downconversion, outputs are combined and sampled at 2 GS/s to obtain the spectrum shown in Fig. 5 (f). Xilinx ZCU-1285 shown in Fig 6 (c) is used to sample the input, DDC and FIR filtering. Since the digital hardware is designed to run using a 250 MHz clock, samples at 2 GS/s are processed using a 8-phase multi-rate DSP implementation (i.e., a=8). Samples arriving from the ADC are then digitally down-converted to a lower IF (10 MHz in this case) and then lowpass filtered to retrieve the spectra.

Downconversion plots shown in Fig. 10 carry information on the frequency and the magnitude. Measurements show an SINR of approximately 15 dB, which is an artifact of the measurement setup and LPF gains.

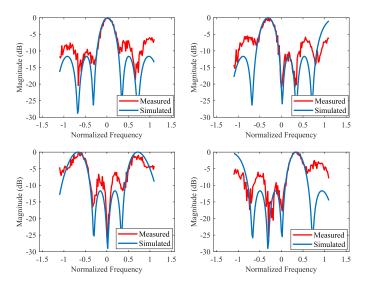

A digital spatial FFT was used to generate multiple beams. The RF source DOA was swept from  $-\pi/3 \le \psi \le \pi/3$ (measured from the broadside) to obtain spatial beam patterns. MATLAB was used to generate the simulated beam pattern for a 4-element antenna array with  $\Delta x = 0.75\lambda$  spacing between antenna elements, and measured RF received beams are plotted with their corresponding simulated beams in Fig. 11. An ideal digital beamformer is expected to have the beam pattern shown (black), whereas the measured beam pattern (red) is observed to show the desired array factor with some deviations in the sidelobes. The 4-beam beamformer is operating as expected but there is deviation in the sidelobes, most likely due to reflections in the measurement area (we were unable to access a sufficiently large anechoic chamber due to pandemic restrictions within the last six months and therefore the measurements were conducted in an indoor open space that may suffer from unexpected reflections).

The same mixer is used in all 4 RF channels in the stage-2 downconversion and LPFs were chosen carefully to reduce the effect of second and third order harmonics, which is the primary determinant of the SINR in this system. Second order harmonic for 125 MHz and 250 MHz channels lie closer to

FIGURE 11. Simulated and measured beams at 28 GHz using digital real-time beamforming using a single ADC to sample 4 independent channels with each channel shown in each plot above. Simulated beams are generated from Matlab fixed point simulations.

the passband and the filter roll-offs of chosen COTS are not sufficient to completely block the prominence of intermods and harmonics. In addition, implementation of two cascaded downconversion stages may combine the noise figures of active and passive elements, in both stages leading to a lower SINR. Effects of such non-idealities can be reduced by choosing steeper LPFs at a tradeoff with the cost. Extension of the implemented system to larger values of M, say M=16, could achieve greater savings from a cost standpoint for implementing massive-MIMO at scale for large arrays.

## **IV. CONCLUSION**

The requirement for large numbers of independent ADC channels is a bottleneck for the implementation of mm-wave massive-MIMO. RF-SoCs are FPGA devices with inbuilt ADCs and DACs for reconfigurable MIMO applications. M-number of antenna signals were multiplexed in the frequency domain and sampled using a single ADC to increase the number of antennas per RF SoC by a factor of M. The largest available RF for-SoC device from Xilinx at the time of submission facilitates 16 ADCs per chip. Frequency division multiplexing was proposed to reduce ADC counts in the receivers in order to facilitate large massive-MIMO arrays receiver. The M-fold FDM allows 16M independent receive streams using a single RF-SoC and without compromising spatial degrees of freedom. The proposed architecture was verified using only a single ADC (of the 16 total available) for an example array containing 4-elements operating at center frequency of 28 GHz. A single-ADC was demonstrated to furnish 4 independent FFT-beams using Xilinx ZCU-1285 RF-SoC platform. Measurements of the receive far-field DFT-beam patterns verified 240 MHz of bandwidth per channel at an SINR of 15 dB. By extension, had all 16 ADC channels in the RF-SoC platform were to be used, the proposed method is seen to furnish 64 independent antenna/receivers and their corresponding 64 independent spatial channels compared to the traditional 16 channels thereby providing an enabling technology for future massive MIMO receivers.

#### **REFERENCES**

- T. S. Rappaport, Y. Xing, O. Kanhere, S. Ju, A. Madanayake, S. Mandal, A. Alkhateeb, and G. C. Trichopoulos, "Wireless communications and applications above 100 GHz: Opportunities and challenges for 6G and beyond," *IEEE Access*, vol. 7, pp. 78729–78757, 2019.

- [2] K. Zheng, A. Dhananjay, M. Mezzavilla, A. Madanayake, S. Bharadwaj, V. Ariyarathna, A. Gosain, T. Melodia, F. Restuccia, J. Jornet, M. Polese, M. Zorzi, J. Buckwalter, M. Rodwell, S. Mandal, X. Wang, J. Haarla, and V. Semkin, "Software-defined radios to accelerate mmWave wireless innovation," in *Proc. IEEE Int. Symp. Dyn. Spectr. Access Netw. (DySPAN)*, Nov. 2019, pp. 1–4.

- [3] E. J. Black, "Holographic beam forming and MIMO," Pivotal Commware, Kirkland, WA, USA, Tech. Rep., 2017. [Online]. Available: https://pivotalcommware.com/wp-content/uploads/2017/11/Holographic-Beamforming-and-MIMO-1.pdf

- [4] E. Björnson, L. Sanguinetti, H. Wymeersch, J. Hoydis, and T. L. Marzetta, "Massive MIMO is a reality—What is next?: Five promising research directions for antenna arrays," *Digital Signal Processing*, vol. 94, pp. 3–20, Nov. 2019.

- [5] T. Ayhan, W. Dehaene, and M. Verhelst, "A 128: 2048/1536 point FFT hardware implementation with output pruning," in *Proc. 22nd Eur. Signal Process. Conf. (EUSIPCO)*, Sep. 2014, pp. 266–270.

- [6] L. Iotti, G. LaCaille, and A. M. Niknejad, "A 12 mW 70-to-100 GHz mixer-first receiver front-end for mm-wave massive-MIMO arrays in 28 nm CMOS," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2018, pp. 414–416.

- [7] A. Puglielli, A. Townley, G. LaCaille, V. Milovanović, P. Lu, K. Trotskovsky, A. Whitcombe, N. Narevsky, G. Wright, T. Courtade, E. Alon, B. Nikolić, and A. M. Niknejad, "Design of energy- and cost-efficient massive MIMO arrays," *Proc. IEEE*, vol. 104, no. 3, pp. 586–606, Mar. 2016.

[8] T. L. Marzetta, *Fundamentals of Massive MIMO*. Cambridge, U.K.:

- [8] T. L. Marzetta, Fundamentals of Massive MIMO. Cambridge, U.K.: Cambridge Univ. Press, 2016.

- [9] A. Morsali, S. Norouzi, and B. Champagne, "Single RF chain hybrid analog/digital beamforming for mmWave massive-MIMO," in *Proc.* IEEE Global Conf. Signal Inf. Process. (GlobalSIP), Nov. 2019, pp. 1–5.

- [10] S. Pulipati, V. Ariyarathna, A. L. Jayaweera, C. U. S. Edussooriya, C. Wijenayake, L. Belostotski, and A. Madanayake, "FPGA-based 2-D FIR frost beamformers with digital mutual coupling compensation," in *IEEE MTT-S Int. Microw. Symp. Dig.*, Aug. 2020, pp. 1077–1080.

- [11] V. Ariyarathna, D. F. G. Coelho, S. Pulipati, R. J. Cintra, F. M. Bayer, V. S. Dimitrov, and A. Madanayake, "Multibeam digital array receiver using a 16-point multiplierless DFT approximation," *IEEE Trans. Anten*nas Propag., vol. 67, no. 2, pp. 925–933, Feb. 2019.

- [12] S. Li, Z. N. Chen, T. Li, F. H. Lin, and X. Yin, "Characterization of metasurface lens antenna for Sub-6 GHz dual-polarization full-dimension massive MIMO and multibeam systems," *IEEE Trans. Antennas Propag.*, vol. 68, no. 3, pp. 1366–1377, Mar. 2020.

- [13] Y. Hu, W. Hong, C. Yu, Y. Yu, H. Zhang, Z. Yu, and N. Zhang, "A digital multibeam array with wide scanning angle and enhanced beam gain for millimeter-wave massive MIMO applications," *IEEE Trans. Antennas Propag.*, vol. 66, no. 11, pp. 5827–5837, Nov. 2018.

- [14] R. W. Heath, Jr., N. González-Prelcic, S. Rangan, W. Roh, and A. M. Sayeed, "An overview of signal processing techniques for millimeter wave MIMO systems," *IEEE J. Sel. Topics Signal Process.*, vol. 10, no. 3, pp. 436–453, Apr. 2016.

- [15] W. Zhang, X. Xia, Y. Fu, and X. Bao, "Hybrid and full-digital beamforming in mmWave massive MIMO systems: A comparison considering low-resolution ADCs," *China Commun.*, vol. 16, no. 6, pp. 91–102, Jun. 2019.

- [16] V. A. Coutinho, V. Ariyarathna, D. F. G. Coelho, R. J. Cintral, and A. Madanayake, "An 8-beam 2.4 GHz digital array receiver based on a fast multiplierless spatial DFT approximation," in *IEEE MTT-S Int. Microw.* Symp. Dig., Jun. 2018, pp. 1538–1541.

- [17] S. Pulipati, V. Ariyarathna, and A. Madanayake, "A 16-element 2.4-GHz digital array receiver using 2-D IIR spatially-bandpass plane-wave filter," in *IEEE MTT-S Int. Microw. Symp. Dig.*, Jun. 2018, pp. 667–670.

- [18] A. Madanayake, S. Mandal, T. S. Rappaport, V. Ariyarathna, S. Madishetty, S. Pulipati, R. J. Cintra, D. Coelho, R. Oliviera, F. M. Bayer, and L. Belostotski, "Towards a low-SWaP 1024-beam digital array: A 32-beam subsystem at 5.8 GHz," *IEEE Trans. Antennas Propag.*, vol. 68, no. 2, pp. 900–912, Feb. 2020.

- [19] S. K. Pulipati, V. Ariyarathna, A. Madanayake, R. T. Wijesekara, C. U. S. Edussooriya, and L. T. Bruton, "A 16-element 2.4-GHz multibeam array receiver using 2-D spatially bandpass digital filters," *IEEE Trans. Aerosp. Electron. Syst.*, vol. 55, no. 6, pp. 3029–3038, Dec. 2019.

- [20] A. Madanayake, R. J. Cintra, N. Akram, V. Ariyarathna, S. Mandal, V. A. Coutinho, F. M. Bayer, D. Coelho, and T. S. Rappaport, "Fast radix-32 approximate DFTs for 1024-beam digital RF beamforming," *IEEE Access*, vol. 8, pp. 96613–96627, 2020.

- [21] V. A. Coutinho, V. Ariyarathna, D. F. G. Coelho, S. K. Pulipati, R. J. Cintra, A. Madanayake, F. M. Bayer, and V. S. Dimitrov, "A low-SWaP 16-beam 2.4 GHz digital phased array receiver using DFT approximation," *IEEE Trans. Aerosp. Electron. Syst.*, vol. 56, no. 5, pp. 3645–3654, Oct. 2020.

- [22] B. S. Ramesh Harjani, Cognitive Radio Receiver Front-Ends. New York, NY, USA: Springer, 2013.

- [23] M. Huang, T. Chi, S. Li, T. Huang, and H. Wang, "A 24.5–43.5 GHz ultracompact CMOS receiver front end with calibration-free instantaneous fullband image rejection for multiband 5G massive MIMO," *IEEE J. Solid-State Circuits*, vol. 55, no. 5, pp. 1177–1186, Jan. 2020.

- [24] M. Tabesh, J. Chen, C. Marcu, L. Kong, S. Kang, E. Alon, and A. Niknejad, "A 65 nm CMOS 4-element sub-34 mW/element 60 GHz phased-array transceiver," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2011, pp. 166–168.

- [25] Y. S. Yeh and B. A. Floyd, "Multibeam phased-arrays using dual-vector distributed beamforming: Architecture overview and 28 GHz transceiver prototypes," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 67, no. 12, pp. 1–14, Oct. 2020.

- [26] O. Zetterstrom, C. I. Kolitsidas, B. L. G. Jonsson, and A. A. Glazunov, "A 28-port MIMO cube for micro base station applications," *IEEE Trans. Antennas Propag.*, vol. 68, no. 5, pp. 3443–3452, May 2020.

- [27] A. O. Martínez, J. Ø. Nielsen, E. De Carvalho, and P. Popovski, "An experimental study of massive MIMO properties in 5G scenarios," *IEEE Trans. Antennas Propag.*, vol. 66, no. 12, pp. 7206–7215, Dec. 2018.

- [28] R. Zhao, T. Woodford, T. Wei, K. Qian, and X. Zhang, "M-cube: A millimeter-wave massive MIMO software radio," in *Proc. 26th Annu. Int. Conf. Mobile Comput. Netw.*, Apr. 2020, pp. 1–14.

- [29] B. Farley, J. McGrath, and C. Erdmann, "An all-programmable 16-nm RFSoC for digital-RF communications," *IEEE Micro*, vol. 38, no. 2, pp. 61–71, Mar. 2018.

- [30] B. Farley, C. Erdmann, B. Vaz, J. McGrath, E. Cullen, B. Verbruggen, R. Pelliconi, D. Breathnach, P. Lim, A. Boumaalif, P. Lynch, C. Mesadri, D. Melinn, K. P. Yap, and L. Madden, "A programmable RFSoC in 16 nm FinFET technology for wideband communications," in *Proc. IEEE Asian Solid-State Circuits Conf. (A-SSCC)*, Nov. 2017, pp. 1–4.

- [31] S. Pulipati, V. Ariyarathna, A. Dhananjay, M. E. Eltayeb, M. Mezzavilla, J. M. Jornet, S. Mandal, S. Bhardwaj, and A. Madanayake, "Xilinx RF-SoC-based digital multi-beam array processors for 28/60 GHz wireless testbeds," in *Proc. Moratuwa Eng. Res. Conf. (MERCon)*, Jul. 2020, pp. 254–259.

- [32] (2020). Zynq UltraScale+ RFSoC: Direct-RF Signal Chain Features. Accessed: Oct. 25, 2020. [Online]. Available: https://www.xilinx.com/products/silicon-devices/soc/rfsoc.html

- [33] Release Description; Release 15, document TS 21.915, 3rd Generation Partnership Project (3GPP), Technical Specification, Mar. 2018. [Online]. Available: https://portal.3gpp.org/desktopmodules/Specifications/SpecificationDetails.aspx?specificationId=3389

- [34] E. A. Alwan, A. Akhiyat, M. LaRue, W. Khalil, and J. L. Volakis, "Low cost, power efficient, on-site coding receiver (OSCR) for ultra-wideband digital beamforming," in *Proc. IEEE Int. Symp. Phased Array Syst. Technol.*, Oct. 2013, pp. 202–206.

- [35] S. B. Venkatakrishnan, D. K. Papantonis, A. A. Akhiyat, E. A. Alwan, and J. L. Volakis, "Experimental validation of on-site coding digital beamformer with ultra-wideband antenna arrays," *IEEE Trans. Microw. Theory Techn.*, vol. 65, no. 11, pp. 4408–4417, Nov. 2017.

- [36] S. B. Venkatakrishnan, A. Akhiyat, E. A. Alwan, W. Khalil, and J. L. Volakis, "Realization of a novel on-site coding digital beamformer using FPGAs," in *Proc. USNC-URSI Radio Sci. Meeting Joint AP-S Symp.*, Jul. 2014, p. 196.

- [37] Y. C. Eldar, Sampling Theory. Cambridge, U.K.: Cambridge Univ. Press, 2017

- [38] K. Greene, V. Chauhan, and B. Floyd, "Code-modulated embedded test for phased arrays," in *Proc. IEEE 34th VLSI Test Symp. (VTS)*, Apr. 2016, pp. 1–4.

- [39] N. Akram, "Digital and mixed domain hardware reduction algorithms and implementations for massive MIMO," Ph.D. dissertation, Dept. Elect. Comput. Eng., Florida Int. Univ., Miami, FL, USA, 2020. [Online]. Available: https://digitalcommons.fiu.edu/etd/4548/

- [40] Walsh-Hadamard Code. Accessed: Oct. 14, 2020. [Online]. Available: https://wiki.cse.buffalo.edu/cse545/content/walsh-hadamard-code

- [41] P. P. Vaidyanathan, Multirate Systems and Filter Banks. London, U.K.: Pearson. 2006.

- [42] S. Pulipati, V. Ariyarathna, U. D. Silva, N. Akram, E. Alwan, A. Madanayake, S. Mandal, and T. S. Rappaport, "A direct-conversion digital beamforming array receiver with 800 MHz channel bandwidth at 28 GHz using Xilinx RF SoC," in *Proc. IEEE Int. Conf. Microw.*, Antennas, Commun. Electron. Syst. (COMCAS), Nov. 2019, pp. 1–5.

- [43] C. A. Balanis, Antenna Theory: Analysis and Design. Hoboken, NJ, USA: Wiley, 2016.

- [44] R. A. Sainati, CAD of Microstrip Antennas for Wireless Applications. Norwood, MA, USA: Artech House, 1996.

- [45] Analog Devices. GaAs MMIC I/Q Downconverter HMC1065LP4E. Accessed: Oct. 6, 2020. [Online]. Available: https://www.analog.com/media/en/technical-documentation/data-sheets/hmc1065.pdf

NAJATH AKRAM (Member, IEEE) received the B.Sc. degree in electrical and information engineering from the University of Ruhuna, Sri Lanka, in 2016, and the Ph.D. degree in electrical and computer engineering from Florida International University, in 2020, with a focus on digital and mixed domain hardware complexity reduction algorithms and implementations for massive MIMO. His research interests include multi-dimensional signal processing, RF systems

design, and antenna array processing. He has been a Tau Beta Pi Member, since 2019.

**ARJUNA MADANAYAKE** (Member, IEEE) received the B.Sc. degree (Hons.) in electronic and telecommunication engineering from the University of Moratuwa, Sri Lanka, and the M.Sc. and Ph.D. degrees in electrical engineering from the University of Calgary, Canada. He is a Tenured Associate Professor of electrical and computer engineering (ECE) with Florida International University (FIU), Miami, USA. Before joining FIU, he was a Tenured Associate Professor with the

Department of ECE, The University of Akron, OH, USA. His research has been sponsored by the National Science Foundation (NSF), the National Institute of Health (NIH), Office of Naval Research (ONR), and Defense Advanced Research Projects Agency (DARPA) through multiple awards in the recent past.

**SRAVAN PULIPATI** (Member, IEEE) received the B.Sc. degree in electronics and communication engineering from Kakatiya University, India, in 2014, and the M.Sc. degree in electronics and computer engineering from The University of Akron, USA. He is currently pursuing the Ph.D. degree, and working as a Research Scholar, with Florida International University (FIU). Since 2015, he has been an active Research Member of the Advanced Signal Processing Circuits Labora-

tory under the supervision of Dr. Arjuna Madanayake. His research interests include mixed-signal processing, digital communications, RF transceivers, EM modeling/circuit simulation, digital logic design, and VLSI. He has abundant expertise in developing wireless RF testbeds used for validating novel algorithms implemented on an FPGA (Virtex-6, Virtex Ultrascale, and Ultrascale+ RF SoC).

VIDUNETH ARIYARATHNA (Member, IEEE) received the B.Sc. degree in electronic and telecommunication engineering from the University of Moratuwa, Sri Lanka, in 2013, the M.Sc. degree in electrical engineering from The University of Akron, OH, USA, in 2016, and the Ph.D. degree in electrical engineering from Florida International University, FL, USA, in 2019, with a focus on low complexity multibeam beamforming circuits for millimeter-wave communication sys-

tems. He is currently an Associate Research Scientist with the Institute for the Wireless Internet of Things, Northeastern University. His main research interests include software-defined radios, one- and multi-dimensional signal processing, ultra-broadband wireless systems, and high-speed modem design.

**SATHEESH BOJJA VENKATAKRISHNAN** (Senior Member, IEEE) was born in Tiruchirappalli, India, in 1987. He received the bachelor's degree in electronics and communication engineering from the National Institute of Technology Tiruchirappalli, in 2009, and the M.S. and Ph.D. degrees in electrical engineering from The Ohio State University (OSU), Columbus, OH, USA, in 2017.

He was a Scientist at DRDO, India, from 2009 to 2013, working on the development and implemen-

tation of active electronic steerable antennas. He is currently a Research Assistant Professor of electrical and computer engineering at Florida International University. His current research interests include receiver design for communication circuits, RF systems, and digital signal processing using FPGAs. He is also working on simultaneous transmit and receive systems (STAR), to improve the spectral efficiency. He has been a Phi Kappa Phi Member, since 2015, and is also an Associate Member of USNC-URSI. He was a recipient of the IEEE Electromagnetic Theory Symposium (EMTS-2019) Young Scientist Award. He won the 2nd prize in International Union of Radio Science General Assembly and Scientific Symposium (URSI-GASS) Student Paper Competition held at Montreal, Canada, in August 2017. He also received the Honorable Mention in the Student Paper Competition at the IEEE Antenna and Propagation Symposium (AP-S/URSI), in 2015 and 2016, and the Student Fellowship Travel Grant Award at the U.S. National Committee for the International Union of Radio Science (USNC-URSI), in 2016 and 2017.

**DIMITRA PSYCHOGIOU** (Senior Member, IEEE) received the Dipl.-Eng. degree in electrical and computer engineering from the University of Patras, Patras, Greece, in 2008, and the Ph.D. degree in electrical engineering from the Swiss Federal Institute of Technology (ETH) Zürich, Switzerland, in 2013. She is currently a Professor of electrical and electronic engineering with University College Cork (UCC) and the Tyndall National Institute, Cork, Ireland. Prior to joining

UCC, she was a Sr. Research Scientist at Purdue University, West Lafayette, IN, USA, and an Assistant Professor with the University of Colorado Boulder, Boulder, CO, USA. Her current research interests include RF design and characterization of reconfigurable microwave and millimeter-wave passive components, RF-MEMS, acoustic wave resonator-based filters, tunable filter synthesis, and frequency-agile antennas. Her research has been presented in more than 160 IEEE publications and has received the 2020 CAREER award from the National Science Foundation (NSF), the 2020 URSI Young Scientist Award, and the Junior Faculty Outstanding Research Award from UC Boulder. She is a Senior Member of URSI and a member of the IEEE MTT-S Filters and Passive Components (MTT-5) and Microwave Control Materials and Devices (MTT-13) committees. Furthermore, she serves on the Technical Review Board of various IEEE and EuMA conferences and journals and is the Chair of MMT-13 and the Secretary of the USNC-URSI Commission. She is an Associate Editor of the IEEE MICROWAVE AND Wireless Components Letters and the International Journal of Microwave and Wireless Technologies. Previously, she was an Associate Editor of the IET Microwaves, Antennas & Propagation journal.

JOHN VOLAKIS (Life Fellow, IEEE) was born in Chios, Greece, in May 1956, and immigrated to the USA, in 1973. He received the B.E. degree (*summa cum laude*) from Youngstown State University, Youngstown, OH, USA, in 1978, and the M.Sc. and Ph.D. degrees from The Ohio State University, Columbus, OH, in 1979 and 1982, respectively.

He started his career at Rockwell International, from 1982 to 1984, and is currently with Boeing. In 1984, he was appointed an Assistant Professor

at the University of Michigan, Ann Arbor, MI, USA, and became a Full Professor, in 1994. He also served as the Director of the Radiation Laboratory, from 1998 to 2000. From January 2003 to August 2017, he was the Roy and Lois Chope Chair Professor of engineering with The Ohio State University and served as the Director of the ElectroScience Laboratory, from 2003 to 2016. Since August 2017, he has been the Dean of the College of Engineering and Computing and a Professor with the Electrical and Computer Engineering Department, Florida International University (FIU). His publications include eight books, nearly 440 journal papers and 900 conference papers, 29 book chapters, and 29 patents/disclosures. He coauthored books which include: Approximate Boundary Conditions in Electromagnetics (1995), The Finite Element Method in Electromagnetics (1998), Antenna Engineering Handbook (Fourth Edition, 2007), Small Antennas (2010), and Integral Equation Methods for Electromagnetics (2011). He has graduated/mentored over 95 doctoral students/postdoctoral researchers with 43 of them receiving best paper awards at conferences. Over the years, he carried out research in antennas, wireless communications and propagation, computational methods, electromagnetic compatibility and interference, design optimization, RF materials, multi-physics engineering, millimeter waves, terahertz, and medical sensing.

Prof. Volakis was listed by ISI among the top 250 most referenced authors, in 2004, and is a fellow of AAAS, ACES, URSI, and NAI. His awards include: the University of Michigan College of Engineering Research Excellence Award, in 1993, the Scott Award from The Ohio State University College of Engineering for Outstanding Academic Achievement, in 2011, the IEEE AP Society C-T. Tai Teaching Excellence Award, in 2011, the IEEE Henning Mentoring Award, in 2013, the IEEE Antennas & Propagation Distinguished Achievement Award, in 2014, The Ohio State University Distinguished Scholar Award, in 2016, The Ohio State University ElectroScience Laboratory George Sinclair Award, in 2017, the URSI Booker Gold Medal, in 2020, and the National Academy of Inventors Fellow Award, in 2021. His service to professional societies include: the President of the IEEE Antennas and Propagation Society, in 2004, the Chair of USNC/URSI Commission B, from 2015 to 2017, twice the General Chair of the IEEE Antennas and Propagation Symposium, IEEE APS Distinguished Lecturer, the IEEE APS Fellows Committee Chair, the IEEE-Wide Fellows Committee Member, and an associate editor of several journals.

**THEODORE S. RAPPAPORT** (Fellow, IEEE) received the Ph.D. degree from Purdue University, in 1987. He is currently the David Lee/Ernst Weber Professor with New York University (NYU) and holds faculty appointments with the Electrical and Computer Engineering Department, NYU Tandon School of Engineering, the Courant's Computer Science Department, and the NYU Langone Health, NYU Grossman School of Medicine. He is also the Founder and the Director of NYU Wire-

less, a multidisciplinary research center focused on the future of wireless communications and applications. His research has led the way for modern wireless communication systems. His Ph.D. degree at Purdue University provided fundamental knowledge of indoor wireless channels used to create the first Wi-Fi standard (IEEE 802.11), and he conducted fundamental work that led to the first U.S. Digital cellphone standards, TDMA IS-54/IS-136,

and CDMA IS-95. He and his students engineered the world's first public Wi-Fi hotspots, and more recently, his work proved the viability of millimeter waves for mobile communications, and the global wireless industry adopted his vision for 5th generation (5G) cellphone networks. He founded three academic wireless research centers at Virginia Tech, The University of Texas at Austin, and NYU that have produced thousands of engineers and educators, since 1990, and has coauthored over 300 papers and 20 books, including the most cited books on wireless communications, adaptive antennas, wireless simulation, and millimeter-wave communications. He co-founded two wireless companies, TSR Technologies and Wireless Valley Communication, which were sold to publicly traded companies, and he has advised many others. He co-founded the Virginia Tech Symposium on Wireless Communications, in 1991, the Texas Wireless Summit, in 2003, and the Brooklyn 5G Summit (B5GS), in 2014. He has more than 100 patents. He serves on the Technological Advisory Council of the Federal Communications Commission (FCC). He is a fellow of the Radio Club of America and the National Academy of Inventors, a Life Member of the American Radio Relay League, a licensed Professional Engineer in Texas City and Virginia City, and an Amateur Radio Operator (N9NB). He has received the ASEE's Terman Award, the Sir Monty Finniston Medal from the Institution of Engineering and Technology (IET), the IEEE Vehicular Technology Society's James R. Evans Avant Garde and Stu Meyer awards, the IEEE Education Society William E. Sayle Award for achievement in education, the IEEE Communications Society Armstrong Award, and the Armstrong Medal from the Radio Club of America.

THOMAS L. MARZETTA (Life Fellow, IEEE) was born in Washington, DC, USA. He received the bachelor's (S.B.) and Ph.D. degrees in electrical engineering from the Massachusetts Institute of Technology, in 1972 and 1978, respectively, the M.S. degree in systems engineering from the University of Pennsylvania, in 1973, and the Honorary Doctorate degree from Linköping University, in 2015. He is a Distinguished Industry Professor with the ECE Department, NYU Tandon

School of Engineering, and the Director of the NYU Wireless. Prior to joining NYU, in 2017, he had three industrial research careers: Schlumberger-Doll Research (petroleum exploration), from 1978 to 1987; Nichols Research Corporation (defense), from 1987 to 1995; and Bell Labs (telecommunications), from 1995 to 2017. At Bell Labs, he directed the Communications and Statistical Sciences Department within the former Mathematical Sciences Research Center, and was elected as a Bell Labs Fellow. He originated massive MIMO, one of the cornerstones of fifth generation wireless technology. He is a lead-author of the book *Fundamentals of Massive MIMO*. He was elected as a member of the National Academy of Engineering, in 2020. Additional recognition for his contributions to massive MIMO include the 2019 Radio Club of America Armstrong Medal, the 2017 IEEE Communications Society Industrial Innovation Award, the 2015 IEEE Stephen O. Rice Prize, and the 2015 IEEE W. R. G. Baker Award.

• • •