Received August 5, 2021, accepted August 21, 2021, date of publication August 24, 2021, date of current version September 1, 2021. *Digital Object Identifier* 10.1109/ACCESS.2021.3107620

# **Extraction of Nitride Trap Profile in 3-D NAND Flash Memory Using Intercell Program Pattern**

JOUNGHUN PARK<sup>®1</sup>, (Student Member, IEEE), GILSANG YOON<sup>®1</sup>, (Graduate Student Member, IEEE), DONGHYUN GO<sup>®1</sup>, (Graduate Student Member, IEEE), JUNGSIK KIM<sup>®2</sup>, (Member, IEEE), AND JEONG-SOO LEE<sup>®1</sup>, (Senior Member, IEEE)

<sup>1</sup>Department of Electrical Engineering, Pohang University of Science and Technology, Pohang 37673, South Korea

<sup>2</sup>Division of Electrical Engineering, Gyeongsang National University, Jinju 52828, South Korea

Corresponding authors: Jungsik Kim (jungsik@gnu.ac.kr) and Jeong-Soo Lee (ljs6951@postech.ac.kr)

This work was supported in part by Samsung-POSTECH Research Center (SPRC) through Samsung Electronics under Grant IO201211-08125-01, in part by the Korea Institute of Planning and Evaluation for Technology in Food, Agriculture, Forestry, and Fisheries (IPET) through the Animal Disease Management Technology Development Program, which is funded by the Ministry of Agriculture, Food, and Rural Affairs (MAFRA) under Grant 120091-02-1-CG000, and in part by the Future Semiconductor Device Technology Development Program under Grant 10067739 funded by Ministry of Trade, Industry & Energy (MOTIE) and Korea Semiconductor Research Consortium (KSRC).

**ABSTRACT** The extraction of nitride trap density  $(N_t)$  filled with electrons emitted by thermal emission (TE) in the charge-trapping layer of 3-D NAND flash memory is demonstrated. The intercell program (IP) pattern was adopted to intentionally inject electrons into the intercell region to minimize the influence of lateral migration (LM) on the trap profiles. This was confirmed by the retention characteristics observed at 120 °C, where the charge loss is mainly caused by the TE of the trapped electrons in the nitride layer. The extracted peak value of  $N_t$  at  $E_C$ - $E_T$  value of 1.20 eV using the IP pattern was as low as  $1.01 \times 10^{19}$  cm<sup>-3</sup> eV<sup>-1</sup>, in the scan range of 0.96 eV to 1.27 eV. This value was 17% lower than that from the conventional adjacent cell program (P-P-P) pattern. Therefore, the IP pattern can be used in extracting trap profiles in the SiN layer in scaled 3-D NAND memories.

**INDEX TERMS** 3D NAND flash memory, data retention, lateral migration, trap profiling.

#### I. INTRODUCTION

The three-dimensional (3-D) charge-trap (CT) NAND flash memory has been dominated in non-volatile memory (NVM) applications due to its higher bit density and lower bit cost [1]–[3]. The large cell size and gate-all-around (GAA) channel structure of 3-D NAND have improved its reliability when compared with the conventional planar NAND. These properties have led to the successful introduction of 3- and 4-bits/cell (quadruple-level cell, QLC) in the industry [4], [5]. Also, 5- (penta-level-cell, PLC) and 6-bits/cell (hexa-level-cell, HLC) have been newly demonstrated [6], [7]. Data retention is one of the key challenges in realizing those future memory devices [8]–[10].

In a CT based 3-D NAND, the continuous silicon nitride (SiN) layer along the pillar causes a lateral migration (LM) of trapped charges due to the Poole–Frenkel (PF) conduction [11]–[15]. LM depends strongly on the neighboring  $V_T$

The associate editor coordinating the review of this manuscript and approving it for publication was Jiajie Fan<sup>(1)</sup>.

patterns and becomes more severe with the scaling of 3-D NAND [16]–[20]. Also, the energy and location of traps in the nitride layer affect the overall memory parameters such as the program/erase (P/E) speed, retention, and bit error rate. Trap centers in SiN layer could mainly originate from H incorporated defects, mostly likely H atom incorporated N vacancy and Si substitute N defects [21], [22].

An adjacent cell program (P-P-P) pattern which is naturally appeared during the storage process, was adopted to extract nitride trap density ( $N_t$ ) in CT layer [23]. It can reduce LM and separate the thermal emission (TE) component from the total charge loss. Compared to the adjacent cell erase (E-P-E) pattern, the extracted  $N_t$  profile from the P-P-P pattern showed a lower trap density. However, the P-P-P pattern is still insufficient to precisely determine the  $N_t$  profile because of the movement of trapped charges into the space region, resulting in an overestimation of trap distributions.

Recently, the space region surrounded by word-line (WL) metals has received attention because the narrow space region is affected by the fringing electric field from the adjacent

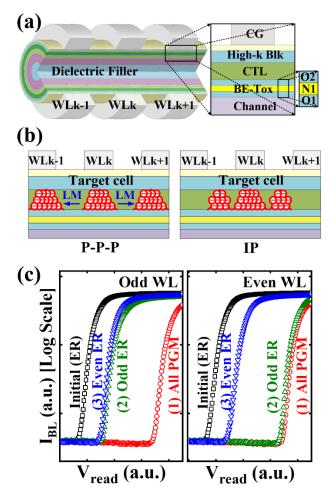

**FIGURE 1.** (a) Schematics of 3-D NAND flash memory. (b) Comparison of the electron distribution between P-P-P pattern and IP pattern with a programmed target cell. (c) The measured  $I_{BL} - V_{read}$  curves of odd-WL (left) and even-WL (right) with IP pattern which is performed as follows; (1) all program (PGM) – (2) odd erase (ER) – (3) even ER.

WLs [24]. The intercell program (IP) or space program was adopted to achieve a reliable triple-level cell (TLC) operation and to analyze the impact of P/E cycling on the retention mechanism [25]–[27]. As 3-D NAND continues to scale, the influence of charges in intercell regions on the memory performance becomes significant.

Here, the trap profiles of the SiN layer and the related charge loss characteristics are presented using the IP pattern. Firstly, the quantitative influence of IP on LM is evaluated based on the retention characteristics with various IP charges. The comparison of  $V_T$  variation between IP and P-P-P at different temperatures confirms the validity of the IP pattern, which mitigates the charge loss along the channel direction. Finally, the trap density using the IP pattern based on a novel cylindrical retention model is extracted and compared with the P-P-P pattern.

## **II. RESULTS AND DISCUSSION**

**Fig. 1(a)** shows a schematic diagram of 3-D NAND flash memory consisting of a dielectric filler, poly-Si channel, band engineering (BE)-tunneling oxide (O1/N1/O2), charge trap

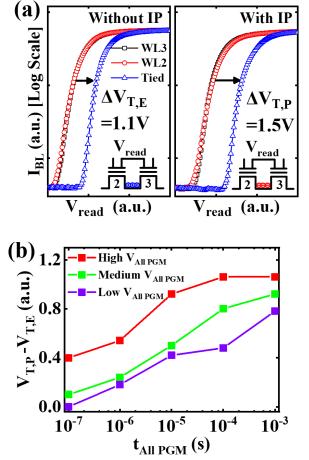

**FIGURE 2.** (a) Representative  $I_{BL} - V_{read}$  curves of WL2, WL3 and tied two WLs with and without IP pattern. (b)  $V_{T,P} - V_{T,E}$  versus all WLs program time ( $t_{All PGM}$ ) at different WLs program voltage ( $V_{All PGM}$ ).

layer (CTL), blocking oxide with a high- $\kappa$  layer. Fig. 1(b) shows the trapped electron distribution in a continuous SiN layer after applying IP and P-P-P patterns. The experimental procedures for comparing the retention efficiency of target programmed cells by each pattern are as follows: After setting an initial erase state of a string to remove the remaining electrons, (1) for the P-P-P pattern, firstly the adjacent WLs are programmed and then the target cell is programmed until  $V_T$  of the PV7 is reached. (2) For the IP pattern, firstly all gates are programmed and then odd-WLs are erased. Next even-WLs are erased. Finally, the target cell is programmed by applying the same PV7 condition. (3) For the E-P-E pattern, only the target cell is programmed. Fig. 1(c) shows the measured BL current  $(I_{BL})$ -read voltage  $(V_{read})$  curves for odd and even WLs. All WLs were simultaneously programmed with high program voltages ( $V_{All PGM}$ ) at a fixed program time  $(t_{All PGM})$ , and the fringing electric field caused electrons to accumulate in the intercell region. The variation in the threshold voltage  $(V_T)$  is clearly observed due to the trapped charges in the intercell region. Then during the erase operation, the protect bias  $(V_{protect})$  is sequentially applied to odd WLs and even WLs to prevent the intercell electrons from being de-trapped through a tunneling layer.

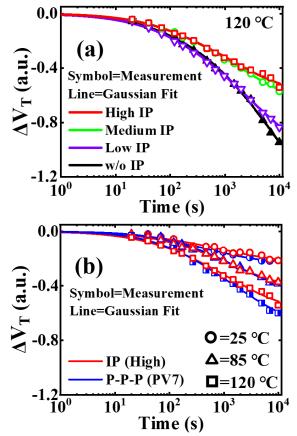

**FIGURE 3.** Retention characteristics of a programmed target cell with (a) different IP conditions ( $t_{AII} PGM = 10^{-4}$  s) at 120 °C. (b) Comparison of IP and P-P-P patterns at 25 °C (circle), 85 °C (triangle) and 120 °C (square).

Fig. 2(a) shows a comparison of the  $V_T$  shift with IP and without IP pattern using the measured  $I_{BL}$ - $V_{read}$  curves. WL2 and WL3 are electrically tied to evaluate the effect of trapped electrons on the  $I_{BL}$ - $V_{read}$  characteristics in the intercell region. When all WLs and intercell areas of CTL were erased (without IP), the  $\Delta V_{T,E}$  increases compared to individual WL because of the intercell region. The larger  $\Delta V_{T,P}$  than  $\Delta V_{T,E}$  suggests that the electrons are filled in the intercell region caused by the fringing field during the IP pattern. Fig. 2(b) shows  $\Delta V_T$  (=  $V_{T,P} - V_{T,E}$ ) shifts with varying  $V_{All PGM}$  and  $t_{All PGM}$  values. At medium and low  $V_{All,PGM}$  values,  $\Delta V_T$  increases monotonously. A high  $V_{All,PGM}$  values,  $\Delta V_T$  saturates after a  $t_{All,PGM}$  value of  $10^{-4}$ s. Such a  $\Delta V_T$  saturation indicates that the concentration of trapped electrons is close to its maximum value in the intercell region.

**Fig. 3(a)** shows the retention characteristics of the target programmed cell in different IP conditions with a fixed  $t_{All PGM}$  of  $10^{-4}$ s at 120 °C. The retention characteristics largely improve for high and medium  $V_{All.PGM}$  values. This confirms the validity of the IP pattern that the trapped electrons in the intercell region can effectively suppress the LM. **Fig. 3(b)** shows the retention characteristics of the IP and P-P-P patterns at different temperatures. At 120 °C, IP with a high  $V_{All.PGM}$  shows less  $\Delta V_T$  variation than that of the P-P-P

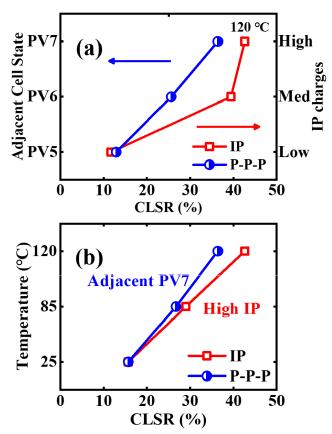

**FIGURE 4.** (a) Comparison of charge loss suppression ratio (CLSR) extracted from the retention characteristics at 10<sup>4</sup> s with IP and P-P-P patterns. (b) CLSR vs. temperature of IP and P-P-P patterns.

pattern, indicating that IP can more effectively suppress LM via PF mechanism at high retention temperatures in the range of 1 s to  $10^4$  s. A charge loss suppression ratio (CLSR) is introduced as the value of  $V_T$  loss is normalized by  $\Delta V_T$  of E-P-E at  $10^4$  s:

$$CLSR(\%) = \frac{|\Delta V_T(pattern) - \Delta V_T(E - P - E)|}{|\Delta V_T(E - P - E)|} \times 100$$

(1)

**Fig. 4(a)** shows a comparison of the CLSR under various IP conditions and P-P-P patterns at 120 °C. CLSR is calculated to be as high as 43% and 39% for high and medium IP conditions, respectively. The CLSR of P-P-P pattern at PV7 level is calculated to be 36%, which is even lower than that for the medium IP. **Fig. 4(b)** shows a comparison of the CLSR between high IP and P-P-P at different temperatures. Adjacent cells are programmed at PV7 level. This clearly shows that the IP pattern is more effective in suppressing the LM at elevated temperatures.

To further understand the effect of IP patterns on the LM, the energy band diagram in the CT layer is analyzed using a technology-computer aided design (TCAD) simulation. Hurkx Band-to-band tunneling model for GIDL erase at SSL and GSL junction, Shockley-read-hall (SRH) recombination model was adopted. Acceptor-like trap with the density of  $4.0 \times 10^{19}$  cm<sup>-3</sup> was used in the entire SiN layer [12]. Transient simulation with non-local tunneling model was

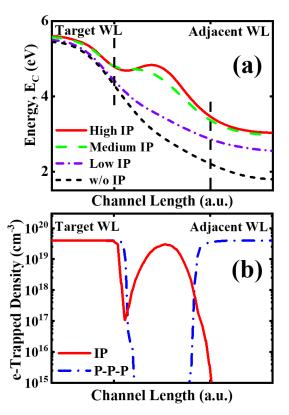

**FIGURE 5.** (a) A schematic conduction energy band diagram ( $E_C$ ) of nitride layer along the channel direction under different IP charges. (b) Concentrations of trapped electron along the channel direction using TCAD simulation.

used to obtain the distribution of trapped electrons in the CTL layer.

Fig. 5(a) shows the conduction energy band ( $E_C$ ) along the channel direction under different IP conditions. For high and medium IP conditions, the peak of the potential barrier is observed closer to the target WL in the intercell region. Fig. 5(b) shows the concentration of trapped electrons along the channel direction in the middle of the CT layer using TCAD simulation. The concentration of trapped electrons of IP pattern is as high as  $3 \times 10^{19}$  cm<sup>-3</sup> in the middle and  $4 \times 10^{15}$  cm<sup>-3</sup> in the gate edge, respectively. The  $V_T$ of each cell for the IP and P-P-P patterns and tied  $\Delta V_T$ (=  $V_{T,P} - V_{T,E}$ ) shifts for IP pattern are confirmed to be the same both in the simulation and the measurement.

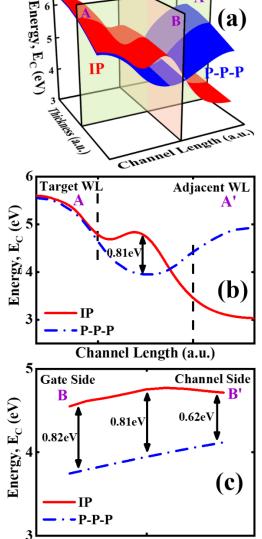

**Fig. 6(a)** shows the variation in 3-D  $E_C$  with IP and P-P-P patterns. **Fig. 6(b)** shows the  $E_C$  variation along the channel direction (A-A'). The potential barrier is minimum in the middle of the intercell region and increases towards adjacent cells for the P-P-P pattern. **Fig. 6(c)** shows a comparison of the  $E_C$  difference between the P-P-P and IP along the vertical direction (B-B'). While the  $E_C$  of the P-P-P pattern decreases monotonously towards the gate side, the maximum  $E_C$  value of the IP pattern is located near the center of the CT layer. An energy difference of 0.82 eV at the blocking oxide-CT layer interface is obtained. The higher  $E_C$  difference suggests an exponential increase of trapped

Thickness (a.u.)

**FIGURE 6.** (a) 3-D  $E_C$  profile in CT layer with P-P-P and IP patterns. Comparison of  $E_C$  of nitride layer with P-P-P and IP patterns (b) along the channel direction (A-A') and (c) the vertical direction (B-B').

electrons in the intercell region, resulting in a significant LM reduction.

The  $V_T$ -loss at high temperature can be mainly caused by the trap-assisted tunneling (TAT) and thermal emission (TE) process, which can be expressed by using the following expressions:

$$\frac{\partial \Delta V_T(t)}{\partial log(t)} = \frac{\partial \Delta V_{T,TAT}(t)}{\partial log(t)} + \frac{\partial \Delta V_{T,TE}(t)}{\partial log(t)}$$

(2)

Firstly, the TAT from CTL to the channel consists of two components; tunneling from CTL through O2 to N1 and tunneling from N1 through O1 to the channel. These tunneling processes can be characterized by a time constant  $\tau_{TB}$  [28]. If the tunneling probability from N1 to the channel is 1, then  $\tau_{TB}$  from CTL to the channel can be

**FIGURE 7.** The extracted  $N_t$  vs.  $E_C - E_T$  at 120 °C (a) using IP pattern with different IP values and (b) comparison with P-P-P and E-P-E patterns.

expressed as [29],

$$\tau_{TB}^{-1} = \tau_{TB0}^{-1} \cdot exp \left(-\alpha_{ox} \left(R_{O2} - R_{N1}\right)\right) \\ \cdot \frac{1}{R_{CTL} - R_{O2}} \int_{0}^{R_{CTL} - R_{O2}} exp(-\alpha_{n}x) \, dx \quad (3)$$

where  $R_{N1}$ ,  $R_{O2}$ ,  $R_{CTL}$ ,  $\tau_{TB}$ ,  $\tau_{TB0}$ ,  $\alpha_n$ ,  $\alpha_{ox}$ , x are the radii of BE-tunneling oxide (N1, O2) and CTL, the time constant of tunneling, the intrinsic time constant  $(1.0 \times 10^{-13} \text{ s})$  of tunneling, the attenuation coefficient of nitride  $(7.2 \times 10^7 \text{ cm}^{-1})$ , and the attenuation coefficient of oxide  $(1.0 \times 10^8 \text{ cm}^{-1})$ , the distance from the O2-CTL interface into CTL, respectively. The  $V_T$ -loss by TAT mechanism can be modified as [30]:

$$\Delta V_{T,TAT}(t) \propto -C_{cyl}^{-1} \cdot \left(exp\left(-\frac{t}{TB}\right) - 1\right)$$

(4)

where the parameter  $C_{cyl}$  is given by

$$C_{cyl}^{-1} = \frac{1}{2\varepsilon_{nit}} \cdot \left[ -R_{O2}^2 ln \frac{R_{CTL}}{R_{O2}} + \frac{1}{2} \left( R_{CTL}^2 - R_{O2}^2 \right) \left( 1 + \frac{2\varepsilon_{nit}}{\varepsilon_{ox}} ln \frac{R_{box}}{R_{CTL}} + \frac{2\varepsilon_{nit}}{\varepsilon_{high-\kappa}} ln \frac{R_{high-\kappa}}{R_{box}} \right) \right]$$

(5)

where  $R_{box}$ ,  $R_{high-\kappa}$ ,  $\varepsilon_{nit}$ ,  $\varepsilon_{ox}$ , and  $\varepsilon_{high-\kappa}$  are the radii of the blocking oxide and high- $\kappa$  layer, the permittivity of nitride,

oxide, and high- $\kappa$  layer, respectively. Differentiating Eq. (4) with respect to log(t), the  $V_T$ -loss rate can be expressed as:

$$\frac{\partial \Delta V_{T,TAT}(t)}{\partial log(t)} \propto \frac{t}{TB} exp\left(-\frac{t}{TB}\right)$$

(6)

The calculated  $\partial \Delta V_{T,TAT}(t)/\partial log(t)$  at t > 1 s is insignificant because the characteristic time constant  $\tau_{TB}$  from Eq. (3) is as low as  $8.3 \times 10^{-3}$  s. Thus the TAT component causing  $V_T$ -loss is negligible and the remaining TE component can be the main mechanism in the charge loss at high temperature. The TE process in  $V_T$ -loss is the emission of trapped electrons to the  $E_C$  of CTL. Based on the equations describing the TE in cylindrical coordinate at high temperature [31], the  $V_T$ -loss equation versus log-scale time is modified as:

$$\frac{\partial \Delta V_{T,TE}(t)}{\partial log(t)} = -2.3qk_BT \cdot C_{cyl}^{-1} \cdot N_{t,E_C-E_T}$$

(7)

Trap energy level  $(E_T)$  from  $E_C$  in CTL is calculated using the following equation.

$$E_C - E_T = k_B T ln \left( 2\sigma_n \sqrt{\frac{3k_B}{m_n^*}} \left[ \frac{2\pi m_n^* k_B}{h^2} \right]^{\frac{3}{2}} T^2 t \right)$$

(8)

where the effective mass  $(m_n^*)$  and the capture-cross section of electron in the SiN layer  $(\sigma_n)$  are  $0.42m_0$  and  $1 \times 10^{-14}$  cm<sup>2</sup>, respectively [11], [32].

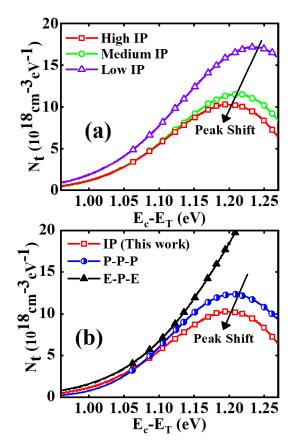

The trap density in SiN layer is successfully extracted using Eq. (7) and Eq. (8). Fig. 7(a) shows the extracted  $N_t$  profile filled with electrons emitted by TE under different IP conditions in the scan range of 0.96 eV to 1.27 eV, applying Gaussian fitting curves of retention characteristics to the modified  $V_T$ -loss equation at 120 °C. The peak and amplitude of the  $N_t$  profile clearly decrease as IP level increases, suggesting that the suppression of LM largely affects the  $N_t$  profiles. Fig. 7(b) shows the extracted  $N_t$  profiles using IP, P-P-P, and E-P-E patterns. The E-P-E pattern seems to be improper in  $N_t$ extraction due to a severe LM effect [23]. The calculated peak  $N_t$  is as low as  $1.01 \times 10^{19}$  and  $1.21 \times 10^{19}$  cm<sup>-3</sup>eV<sup>-1</sup> for IP and P-P-P patterns, respectively. The peak  $N_t$  extracted by the P-P-P pattern concurs recently reported results [23], and the newly extracted  $N_t$  peak by the IP pattern reduces by 17%. Compared with P-P-P pattern, the  $N_t$  profile with a shallower  $E_C$ - $E_T$  value and a smaller amplitude using IP pattern, indicating that LM is more suppressed in IP pattern than P-P-P pattern. Even though this work is done by measuring TEG of 3-D NAND flash memory, the result for LM suppression of IP pattern can be solutions to reduce the system operations of 3-D NAND chip at high temperature [8], [10].

While the increase of vertical stacks for further 3-D NAND flash technology, the difference of aspect ratio becomes a major issue in etching the channel hole [33]. Thus the gate length and intercell length should be shrink, which affects trapped charge distribution. The changes of gate length or intercell length can affect the total amount of intercell trapped charges associated with LM suppression [20]. Therefore, further study is needed on future technology nodes or device scaling for IP pattern and related  $N_t$  profiling.

## **III. CONCLUSION**

The extraction of nitride trap profiles in 3-D NAND flash memories using intercell program patterns is successfully demonstrated. Compared to the P-P-P pattern, the IP pattern is more effective in mitigating the LM at elevated temperatures, as confirmed by the retention characteristics and CLSR values at 120 °C. The high IP condition shows a higher CLSR value than that of P-P-P under PV7 conditions. Using modified TE equations, trap profiles are extracted from retention characteristics. The extracted  $N_t$  peak value using the IP pattern is 17 % lower than that of the P-P-P pattern. Therefore, the intercell program pattern is very useful in determining trap profiles in the SiN layer in scaled 3-D NAND memories.

#### ACKNOWLEDGMENT

The EDA Tool was supported by the IC Design Education Center.

### REFERENCES

- J. Jang *et al.*, "Vertical cell array using TCAT(terabit cell array transistor) technology for ultra high density NAND flash memory," in *VLSI Symp. Tech. Dig.*, Jun. 2009, pp. 192–193.

- [2] H. Tanaka, M. Kido, K. Yahashi, M. Oomura, R. Katsumata, M. Kito, Y. Fukuzumi, M. Sato, Y. Nagata, Y. Matsuoka, Y. Iwata, H. Aochi, and A. Nitayama, "Bit cost scalable technology with punch and plug process for ultra high density flash memory," in *Proc. IEEE Symp. VLSI Technol.*, Jun. 2007, pp. 14–15, doi: 10.1109/VLSIT.2007.4339708.

- [3] E.-S. Choi and S.-K. Park, "Device considerations for high density and highly reliable 3D NAND flash cell in near future," in *IEDM Tech. Dig.*, Dec. 2012, pp. 9.4.1–9.4.4, doi: 10.1109/IEDM.2012.6479011.

- [4] A. Goda, "3-D NAND technology achievements and future scaling perspectives," *IEEE Trans. Electron Devices*, vol. 67, no. 4, pp. 1373–1381, Apr. 2020, doi: 10.1109/TED.2020.2968079.

- [5] N. Shibata, K. Kanda, T. Shimizu, J. Nakai, O. Nagao, N. Kobayashi, M. Miakashi, Y. Nagadomi, T. Nakano, T. Kawabe, and T. Shibuya, "A 1.33Tb 4-bit/cell 3D-flash memory on a 96-word-line-layer technology," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2019, pp. 210–212, doi: 10.1109/ISSCC.2019.8662443.

- [6] K. Ishimaru, "Future of non-volatile memory -From storage to Computing-," in *IEDM Tech. Dig.*, Dec. 2019, pp. 1.3.1–1.3.6, doi: 10.1109/IEDM19573.2019.8993609.

- [7] Y. Aiba, H. Tanaka, T. Maeda, K. Sawa, F. Kikushima, M. Miura, T. Fujisawa, M. Matsuo, and T. Sanuki, "Cryogenic operation of 3D flash memory for new applications and bit cost scaling with 6-bit per cell (HLC) and beyond," in *Proc. 5th IEEE Electron Devices Technol. Manuf. Conf.* (*EDTM*), Apr. 2021, pp. 1–3, doi: 10.1109/EDTM50988.2021.9421051.

- [8] Y. Wang, J. Tan, R. Mao, and T. Li, "Temperature-aware persistent data management for LSM-tree on 3-D NAND flash memory," *IEEE Trans. Comput.-Aided Design Integr. Circuits Syst.*, vol. 39, no. 12, pp. 4611–4622, Dec. 2020, doi: 10.1109/TCAD.2020.2982623.

- [9] Y. Luo, S. Ghose, Y. Cai, E. F. Haratsch, and O. Mutlu, "HeatWatch: Improving 3D NAND flash memory device reliability by exploiting self-recovery and temperature awareness," in *Proc. IEEE Int. Symp. High Perform. Comput. Archit. (HPCA)*, Feb. 2018, pp. 504–517, doi: 10.1109/HPCA.2018.00050.

- [10] Y. Wang, J. Huang, J. Yang, and T. Li, "A temperature-aware reliability enhancement strategy for 3-D charge-trap flash memory," *IEEE Trans. Comput.-Aided Design Integr. Circuits Syst.*, vol. 38, no. 2, pp. 234–244, Feb. 2019, doi: 10.1109/TCAD.2018.2808227.

- [11] A. Arreghini, N. Akil, F. Driussi, D. Esseni, L. Selmi, and M. J. van Duuren, "Long term charge retention dynamics of SONOS cells," *Solid-State Electron.*, vol. 52, no. 9, pp. 1460–1466, Sep. 2008, doi: 10.1016/j.sse.2008.04.016.

- [12] A. Maconi, A. Arreghini, C. M. Compagnoni, G. Van den bosch, A. S. Spinelli, J. Van Houdt, and A. L. Lacaita, "Comprehensive investigation of the impact of lateral charge migration on retention performance of planar and 3D SONOS devices," *Solid-State Electron.*, vol. 74, pp. 64–70, Aug. 2012, doi: 10.1016/j.sse.2012.04.013.

- [13] D. Oh, B. Lee, E. Kwon, S. Kim, G. Cho, S. Park, S. Lee, and S. Hong, "TCAD simulation of data retention characteristics of charge trap device for 3-D NAND flash memory," in *Proc. IEEE Int. Memory Workshop* (*IMW*), May 2015, pp. 1–4, doi: 10.1109/IMW.2015.7150306.

- [14] C. Woo, S. Kim, J. Park, D. Lee, M. Kang, J. Jeon, and H. Shin, "Modeling of lateral migration mechanism during the retention operation in 3D NAND flash memories," in *Proc. Electron Devices Technol. Manuf. Conf.* (*EDTM*), Mar. 2019, pp. 261–263, doi: 10.1109/EDTM.2019.8731083.

- [15] Y. Kong, M. Zhang, X. Zhan, R. Cao, and J. Chen, "Retention correlated read disturb errors in 3-D charge trap NAND flash memory: Observations, analysis, and solutions," *IEEE Trans. Comput.-Aided Design Integr. Circuits Syst.*, vol. 39, no. 11, pp. 4042–4051, Nov. 2020, doi: 10.1109/TCAD.2020.3025514.

- [16] B. Choi, S. H. Jang, J. Yoon, J. Lee, M. Jeon, Y. Lee, J. Han, J. Lee, D. M. Kim, D. H. Kim, and C. Lim, "Comprehensive evaluation of early retention (fast charge loss within a few seconds) characteristics in tube-type 3-D NAND flash memory," in *Proc. IEEE Symp. VLSI Technol.*, Jun. 2016, pp. 1–2, doi: 10.1109/VLSIT.2016.7573385.

- [17] K. Mizoguchi, S. Kotaki, Y. Deguchi, and K. Takeuchi, "Lateral charge migration suppression of 3D-NAND flash by Vth nearing for near data computing," in *IEDM Tech. Dig.*, Dec. 2017, pp. 465–468, doi: 10.1109/IEDM.2017.8268420.

- [18] C. Woo, S. Kim, and H. Shin, "Cell pattern dependency of charge failure mechanisms during short-term retention in 3-D NAND flash memories," *IEEE Electron Device Lett.*, vol. 41, no. 11, pp. 1645–1648, Nov. 2020, doi: 10.1109/LED.2020.3023188.

- [19] C. Woo, M. Lee, S. Kim, J. Park, G.-B. Choi, M.-S. Seo, K. H. Noh, M. Kang, and H. Shin, "Modeling of charge loss mechanisms during the short term retention operation in 3-D NAND flash memories," in *Proc. Symp. VLSI Technol.*, Jun. 2019, pp. T214–T215, doi: 10.23919/VLSIT.2019.8776579.

- [20] C. Woo, S. Kim, J. Park, and H. Shin, "Effect of device scaling on lateral migration mechanism of electrons in V-NAND," in *Proc. Silicon Nanoelectron. Workshop (SNW)*, Jun. 2019, pp. 1–2, doi: 10.23919/SNW.2019.8782947.

- [21] J. Wu, D. Han, W. Yang, S. Chen, X. Jiang, and J. Chen, "Comprehensive investigation on charge diffusion physics in SiN-based 3D NAND flash memory through systematical Ab-initio calculations," in *IEDM Tech. Dig.*, Dec. 2017, pp. 4.5.1–4.5.4, doi: 10.1109/IEDM.2017.8268327.

- [22] J. Wu, J. Chen, and X. Jiang, "Multiscale simulation of lateral charge loss in Si<sub>3</sub>N<sub>4</sub> 3D NAND flash based on density functional theory," *J. Phys. D, Appl. Phys.*, vol. 52, no. 39, Jul. 2019, Art. no. 395103, doi: 10.1088/1361-6463/ab2eaa.

- [23] H.-J. Kang, N. Choi, S.-M. Joe, J.-H. Seo, E. Choi, S.-K. Park, B.-G. Park, and J.-H. Lee, "Comprehensive analysis of retention characteristics in 3-D NAND flash memory cells with tube-type poly Si channel structure," in *VLSI Symp. Tech. Dig.*, Jun. 2015, pp. T182–T183, doi: 10.1109/VLSIT.2015.7223670.

- [24] M. Kim and H. Shin, "Investigation and SPICE compact model of spacer region for static characteristics of 3-D NAND flash memories," *IEEE Trans. Electron Devices*, vol. 67, no. 10, pp. 4158–4165, Oct. 2020, doi: 10.1109/TED.2020.3014066.

- [25] H.-J. Kang, N. Choi, D. Lee, T. Lee, S. Chung, J.-H. Bae, B.-G. Park, and J.-H. Lee, "Space program scheme for 3-D NAND flash memory specialized for the TLC design," in *Proc. IEEE Symp. VLSI Technol.*, Jun. 2018, pp. 201–202, doi: 10.1109/VLSIT.2018.8510660.

- [26] R. Cao, J. Wu, W. Yang, J. Chen, and X. Jiang, "Program/erase cycling enhanced lateral charge diffusion in triple-level cell charge-trapping 3D NAND flash memory," in *Proc. IEEE Int. Rel. Phys. Symp.*, Apr. 2019, pp. 978–981, doi: 10.1109/IRPS.2019.8720412.

- [27] X. Jia, L. Jin, W. Hou, Z. Wang, S. Jiang, K. Li, D. Huang, H. Liu, W. Wei, J. Lu, A. Zhang, and Z. Huo, "Impact of cycling induced intercell trapped charge on retention charge loss in 3-D NAND flash memory," *IEEE J. Electron Devices Soc.*, vol. 8, pp. 62–66, Jan. 2020, doi: 10.1109/JEDS.2019.2963473.

- [28] I. Lundström and C. Svensson, "Tunneling to traps in insulators," J. Appl. Phys., vol. 43, no. 12, pp. 5045–5047, Dec. 1972, doi: 10.1063/1.1661067.

- [29] S.-H. Gu, C.-W. Hsu, T. Wang, W.-P. Lu, Y.-H.-J. Ku, and C.-Y. Lu, "Numerical simulation of bottom oxide thickness effect on charge retention in SONOS flash memory cells," *IEEE Trans. Electron Devices*, vol. 54, no. 1, pp. 90–97, Jan. 2007, doi: 10.1109/TED.2006.887219.

- [30] Y. Yang and M. H. White, "Charge retention of scaled SONOS nonvolatile memory devices at elevated temperatures," *Solid-State Electron.*, vol. 44, no. 6, pp. 949–958, Jun. 2000, doi: 10.1016/S0038-1101(00)00012-5.

- [31] M.-K. Jeong, H.-J. Kang, S.-M. Joe, S.-K. Park, B.-G. Park, and J.-H. Lee, "Trap profiling in nitride storage layer in 3-D NAND flash memory using retention characteristics and AC-g<sub>m</sub> method," *IEEE Electron Device Lett.*, vol. 36, no. 6, pp. 561–563, Jun. 2015, doi: 10.1109/LED.2015.2419277.

- [32] G.-H. Lee, H.-J. Yang, S.-W. Jung, E.-S. Choi, S.-K. Park, and Y.-H. Song, "Physical modeling of program and erase speeds of metal-oxide-nitrideoxide-silicon cells with three-dimensional gate-all-around architecture," *Jpn. J. Appl. Phys.*, vol. 53, no. 1, Dec. 2013, Art. no. 014201, doi: 10.7567/JJAP.53.014201.

- [33] C.-W. Yoon, H.-G. Kim, S.-K. Lee, J. Lee, and J. H. Song, "Issues and key technologies for next generation 3D NAND," in *Proc. Int. Conf. Electron., Inf., Commun. (ICEIC)*, Feb. 2021, pp. 1–4, doi: 10.1109/ICEIC51217.2021.9369795.

**DONGHYUN GO** (Graduate Student Member, IEEE) received the M.S. degree in electrical engineering (EE) from Pohang University of Science and Technology (POSTECH), where he is currently pursuing the Ph.D. degree in electrical engineering. His research interests include characterization and reliability of 3-D vertical NAND flash memory.

**JUNGSIK KIM** (Member, IEEE) received the Ph.D. degree in IT convergence engineering from Pohang University of Science and Technology, Pohang, South Korea, in 2016.

From February 2016 to March 2018, he worked at SK-Hynix for modeling of 96-stacks VNAND. From April 2019 to February 2020, he worked at Samsung Electronics for compact modeling of 1a-node DRAM. From April 2018 to March 2019, he was a Visiting Scholar with the

NASA Ames Research Center for reliability due to radiation effect in silicon devices. He is currently an Assistant Professor with the Department of Electrical Engineering, Gyeongsang National University, Jinju, South Korea. His research interests include the modeling and reliability of nano-scale devices based on technical computer-aided simulation and measurement, respectively.

**JOUNGHUN PARK** (Student Member, IEEE) received the B.S. degree in electrical engineering (EE) from Pohang University of Science and Technology (POSTECH), where he is currently pursuing the Ph.D. degree in electrical engineering. His research interests include characterization and reliability of 3-D vertical NAND flash memory.

JEONG-SOO LEE (Senior Member, IEEE) received the B.S., M.S., and Ph.D. degrees in electrical engineering from POSTECH, South Korea, in 1991, 1993, and 1996, respectively. In 1996, he joined Samsung Electronics and worked as a Senior Engineer on the development of logic devices and nonvolatile memory devices. He was a Visiting Scholar at UC Berkeley, in 2001, where he developed Fin-FETs and ultra-thin-body (UTB) FETs. In 2005, he was a Founding Member of the

National Center of Nanomaterials Technology (NCNT) established by the Ministry of Knowledge Economy, South Korea. Since 2008, he has been a Full Professor with the Department of Electrical Engineering, POSTECH, and also served as the Vice-Director of NCNT. His research interests include Si-based nonplanar transistors, nanoscale devices, bottom-up nanowire transistors, and their biosensor applications.

**GILSANG YOON** (Graduate Student Member, IEEE) received the M.S. degree in electrical engineering (EE) from Pohang University of Science and Technology (POSTECH), where he is currently pursuing the Ph.D. degree in electrical engineering. His research interests include characterization and reliability of 3-D vertical NAND flash memory.