Received July 26, 2021, accepted August 15, 2021, date of publication August 18, 2021, date of current version August 24, 2021.

Digital Object Identifier 10.1109/ACCESS.2021.3105690

# Modified Nearest Level Modulation for Full-Bridge Based HVDC MMC in Real-Time Hardware-in-Loop Setup

JAHANGEER BADAR SOOMRO<sup>®1</sup>, F. AKHTER<sup>®1</sup>, (Member, IEEE), SADDAQAT ALI<sup>®1</sup>, SYED SABIR HUSSAIN BUKHARI<sup>®1,2</sup>, (Member, IEEE), IRFAN SAMI<sup>®2</sup>, (Graduate Student Member, IEEE), AND JONGSUK RO<sup>®2,3</sup>

Corresponding author: Jongsuk Ro (jongsukro@gmail.com)

This work was supported in part by the Human Resources Development of the Korea Institute of Energy Technology Evaluation and Planning (KETEP) Grant through the Korean Government Ministry of Trade, Industry and Energy under Grant 20204030200090, in part by the Basic Science Research Program through the National Research Foundation of Korea by the Ministry of Education under Grant 2016R1D1A1B01008058, and in part by the Brain Pool (BP) Program through the National Research Foundation of Korea (NRF) by the Ministry of Science and ICT under Grant 2019H1D3A1A01102988.

**ABSTRACT** Modular Multilevel Converter (MMC) is an emerging converter topology for medium and high voltage applications. Nearest level Modulation (NLM) is the conventional control topology used to control the MMC that produces the N+1 AC output waveform. In previous research work, the Modified NLM has been already proposed, producing a 2N+1 and 4N+1 output waveform while utilizing a half-bridge (HB) submodule (SM) topology. However, half-bridge-based MMC has a similar behavior as two-level Voltage Source Converter (VSC) and cannot block DC fault current in case of DC-side short circuit fault. So, in recent years, full-bridge-based MMC topology is preferably used by manufacturers as it has DC fault blocking capabilities. This paper presents the Modified NLM for Full bridge (FB) SM topology to take the critical benefits of FB SM topology and improve power quality. The proposed method is simpler to implement and produces a 4N+1 AC output waveform. The THD of the output voltage and current reduces to half compared to the conventional NLM method. The proposed method is verified using LabVIEW Multisim co-simulation and as well as real-time simulation.

INDEX TERMS Modified NLC, full bridge, HVDC MMC, hardware-in-loop simulation.

## I. INTRODUCTION

Modular Multilevel Converter (MMC) is a promising converter topology used nowadays, especially in the applications of High Voltage Direct Current (HVDC) Transmission systems and in multi-terminal DC (MTDC) grids due to its various advantages over conventional converters [1]. Series connected identical submodules (SMs) make its design simpler, modular, easily scalable in voltage and current, and provides redundancy [2], [3].

Generally, fundamental switching frequency methods such as space vector modulation, selective harmonic

The associate editor coordinating the review of this manuscript and approving it for publication was Chandan Kumar.

elimination (SHE), and nearest level modulation (NLM) are preferred in MMC to limit the switching losses [4]–[9]. For MMC with a high number of SMs, the NLM modulation method is given preference due to its attractive features such as simple implementation, not involving complex mathematics as in the SHE modulation method, and natural capacitor voltage balancing [10], [11]. In NLM, the three-phase grid voltages are taken as a reference, fed back to a modulator. These voltages are converted to the staircase waveform using a round function. The switching pulses for all SMs present in the upper and lower arm of the MMC are generated. Finally, the SMs are inserted and bypassed using a conventional sorting algorithm depending upon arm current polarity, SM voltage, and voltage required at the output [12], [13].

<sup>&</sup>lt;sup>1</sup>Center for Research in Energy and Smart Grids, Department of Electrical Engineering, Sukkur IBA University, Sukkur, Sindh 65200, Pakistan

<sup>&</sup>lt;sup>2</sup>School of Electrical and Electronics Engineering, Chung-Ang University, Seoul 06910, South Korea

<sup>&</sup>lt;sup>3</sup>Department of Intelligent Energy and Industry, Chung-Ang University, Seoul 06910, South Korea

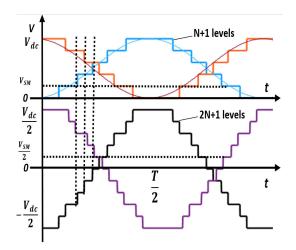

The conventional NLM method generates N+1 AC output levels (N is the number of SMs in the upper/lower arm) [14]. More SMs are employed to raise the number of levels in the output, which increases the number of switches, capacitors, and gate driver circuitry and, therefore, the system's complexity [15], [16]. To increase the number of levels, the power quality of the output voltage and current Modified NLM methods are presented in various research articles. For instance, the authors in [15] proposed modified NLM for Half Bridge (HB) MMC to produce 4N+1 level output AC waveform. However, HB MMC cannot block dc fault currents in case of dc short circuit fault. The authors in [17] proposed the binary, trinary, and modified MMC-based topology to improve power quality and reduce circuit complexity. The proposed method involves complex calculations and gives higher THD. The reference [18] presented a modified NLM to improve the power quality, but this study lacks experimental verification. The research reported in [19] provided an improved NLM with fewer SMs, although their technique had a larger THD and no experimental validation. The authors in [20] also presented an increased NLM method with fewer SMs and less THD. In various other articles [21]–[25], the authors presented the Modified NLM method to improve the power quality and reduce the circuit complexity.

Nevertheless, the studies presented were only limited to the half-bridge topology of MMC. Full bridge SM topology has many advantages such as inherent DC fault blocking capability, increased AC output voltage, and twice the number of output voltage levels [26], [27]. Thus, there is a tire need to develop a Modified NLC method for full-bridge SM topology to get the above-discussed features of full-bridge topology. In this paper, a modified NLC approach to operate full-bridge SM-based MMC HVDC is presented. The proposed modified NLC produces a 4N+1 AC output waveform which improves the power quality of the voltage and currents.

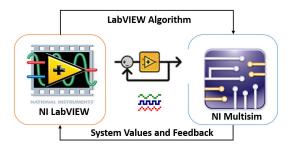

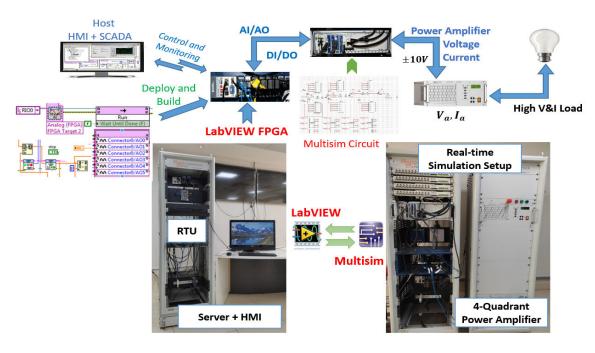

Offline simulation is done using LabVIEW Multisim Co-simulation to evaluate the efficacy of the proposed technique, in which the control algorithm is created in LabVIEW and the circuit is implemented in Multisim. The results are obtained for conventional and modified NLC control with various levels, and comparisons are drawn between both techniques. The Modified NLC is then implemented in FPGA-based controller Compact Reconfigurable input/output (CRIO), and the circuit is implemented in NI PXI for real-time results verification.

### **II. WORKING PRINCIPLE OF MMC**

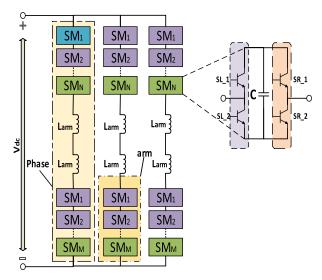

The topology of FB-based HVDC MMC is shown in Fig. 1. It consists of three phases, with each phase includes the upper and lower arm connected in series through an inductor. The arms are formed using FB SMs. Each SM contains four switches and a capacitor connected across them. To derive output voltage and current equations, use Kirchhoff's voltage law (KVL) and current law (KCL) in the upper and lower

FIGURE 1. Three-phase MMC HVDC with FB SM topology.

arms of any phase. The equations can be written as

$$V_{x\_upper} = -\sum_{1}^{N} V_{SM\_N} + \frac{1}{2} V_{dc} - L_{arm} \frac{di_{upper}}{dt}, \quad (1)$$

$$V_{x\_lower} = \sum_{1}^{M} V_{SM\_M} - \frac{1}{2} V_{dc} + L_{arm} \frac{di_{lower}}{dt}, \qquad (2)$$

where,  $V_{x\_upper}$  and  $V_{x\_lower}$  are the output voltage of the upper arm and lower arm,  $V_{dc}$  is the total DC link voltage,  $L_{arm}$  is the inductance of inductor connected to the arm,  $i_{upper}$  and  $i_{lower}$  are the upper and lower arm currents and  $V_{SM_N}$  and  $V_{SM_M}$  are the SM voltages of the upper and lower arm, respectively. Depending upon the switches, the voltages of SMs i.e.,  $V_{SM_N}$  and  $V_{SM_M}$  can be positive, negative, and zero. Thus, the output current can be found by equation (3).

$$i_x = i_{upper} - i_{lower} \tag{3}$$

From equation (1) and (2), the output voltage can be written as

$$V_{x} = \frac{1}{2} \left( \sum_{1}^{M} V_{SM_{M}} - \sum_{1}^{N} V_{SM_{N}} \right) + \frac{1}{2} L_{arm} \frac{di_{x}}{dt}. \tag{4}$$

The ac equivalent voltage can be calculated by

$$V_{ac} = \frac{1}{2} \left( \sum_{1}^{M} V_{SM_M} - \sum_{1}^{N} V_{SM_N} \right). \tag{5}$$

In general, ac equivalent voltage is found as

$$V_{ac}^{ref} = \frac{mV_{dc}}{2}\cos(\omega t). \tag{6}$$

The reference voltages for upper and lower arm operation are written as

$$V_{upper}^{ref} = \frac{V_{dc}}{2} [1 - m\cos(\omega t)], \tag{7}$$

$$V_{lower}^{ref} = \frac{V_{dc}}{2} [1 + m\cos(\omega t)], \tag{8}$$

where m is the modulation index in the range 0 < m < 1 and  $\omega$  is the angular frequency.

#### III. NLM METHOD

The following formulae can calculate the number of SMs inserted in the upper and lower arm

$$N_{upper} = (\frac{V_{dc}}{2V_{SM}} [1 - m\cos(\omega t)])_{round(0.5)}.$$

(9)

$$N_{lower} = (\frac{V_{dc}}{2V_{SM}} [1 + m\cos(\omega t)])_{round(0.5)}.$$

(10)

$$N_{lower} = (\frac{V_{dc}}{2V_{SM}} [1 + m\cos(\omega t)])_{round(0.5)}.$$

(10)

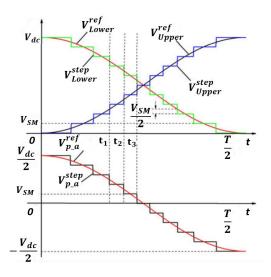

In both the equations,  $V_{SM}$  is the SM capacitor voltage. The round function rounds the real number to the closest available integer as per its decimal fraction. The conventional NLM method produces N+1 AC output waveform as shown in the Fig. 2. Where N is the number of SMs in either arm.

FIGURE 2. Conventional NLM method.

## IV. PROPOSED MODIFIED NLC

The proposed Modified NLC method for FB SM-based MMC is derived by adding a small phase shift in reference waveforms for the left and right arms of the FB SM. As shown in Fig. 1, the switches in the FB SMs are named S<sub>L1</sub> and S<sub>L2</sub> for the left arm and S<sub>R1</sub> and S<sub>R2</sub> for the right arm, respectively. The initial phase shift is introduced in the reference waveforms for all the FB SMs, as shown in Fig. 3. This phase shift produces 2N+1 AC output levels in voltage and current waveform.

$$V_{right}^{ref} = \frac{V_{dc}}{2} [1 - m\cos(\omega t + \alpha)]$$

(11)

$$V_{right}^{ref} = \frac{V_{dc}}{2} [1 - m\cos(\omega t + \infty)]$$

$$N_{right} = (\frac{V_{dc}}{2V_{SM}} [1 - m\cos(\omega t + \infty)])_{round(0.5)}$$

(11)

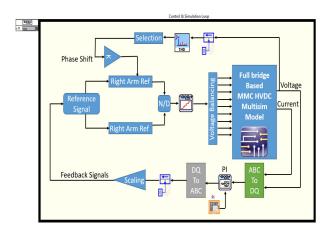

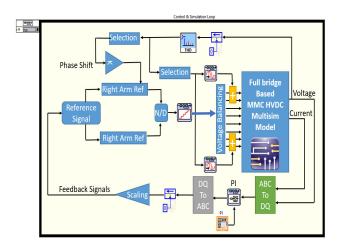

The above equations (11) and (12) are used for the right upper and lower arm, and equations (7) and (8) are used for the left upper and lower arm of the FB MMC. The complete schematic layout of the Modified NLC for full-bridge is implemented in LabVIEW is shown in Fig. 4.

As shown in the above closed-loop LabVIEW program, three-phase voltage and current are measured and feedback

FIGURE 3. Modified NLC in FB SM for 2N+1 levels.

FIGURE 4. Modified NLC in LabVIEW for FB SM for 2N+1 levels.

to generate the reference signal for Modified NLC. The reference signal for right and left arm are then generated, and a phase shift is added in either of the respective arm (right arm in our case). The control signals are then generated and sent to the voltage balancing algorithm to select respective FB SMs. To extract the required phase shift i.e. value of the angle  $\propto$ , the THD of the voltage is measured and dispatched to the selection block containing previous and current value of THD. If the previous THD is less than the current value, the phase shift is retained to its previous value, otherwise the phase shift is increased by some value. To ensure the minimum THD, the phase shift is not kept constant but it is varied between 9.5 to 11 degrees, where optimum value of angle  $\propto$  lies.

Moreover, to produce 4N+1 AC output levels, more phase shift is introduced in half of the SMs of the upper arm and half of the SMs in the lower arm of FB based HVDC MMC. The complete process is further illustrated in Fig. 5. When the controller achieves a stable value of the angle alpha, the levels are raised from 2N+1 to 4N+1 by inserting a small phase shift for half of the SMs in the upper and half of the SMs in the lower arm.

115000 **VOLUME 9. 2021**

FIGURE 5. Modified NLC in LabVIEW for FB SM for 4N+1 levels.

FIGURE 6. LabVIEW multisim co-simulation method.

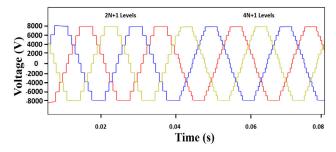

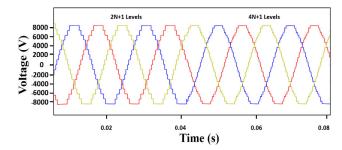

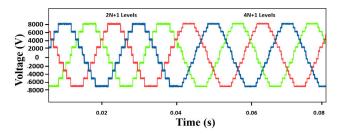

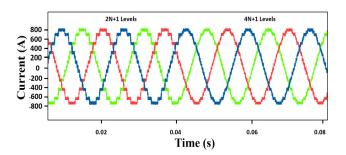

FIGURE 7. Three-phase output voltage with 9 levels and 17 levels.

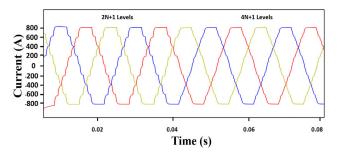

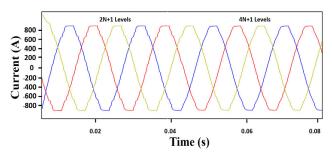

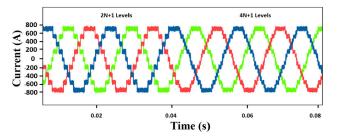

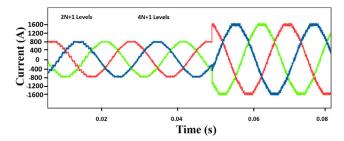

FIGURE 8. Three-phase output current with 9 and 17 levels.

## **V. Labview Multisim Co-Simulation Results**

To validate the simulation results, LabVIEW Multisim Co-simulation is carried out, as shown in Fig. 6.

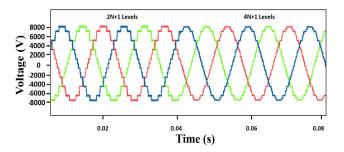

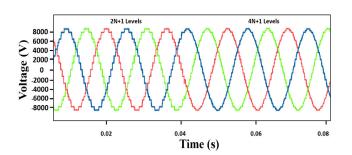

FIGURE 9. Three-phase output voltage with 17 and 33 levels.

FIGURE 10. Three-phase output current with 17 levels and 33 levels.

FIGURE 11. Three-phase output voltage with 23 and 49 levels.

FIGURE 12. Three-phase output current with 23 and 49 levels.

Modified NLC is designed in LabVIEW, and MMC circuit is designed in Multisim. Both modified and conventional NLM method is designed in LabVIEW and activated to verify the proposed algorithm. Different AC output levels have been simulated to observe the behaviour and effectiveness of the Modified NLC.

The system parameters are shown in table 1, and simulation results are compiled using different FB SMs in the arm, such

FIGURE 13. Real-time simulation Setup for result verification.

TABLE 1. Conventional and modified NLM in terms of THD.

| Item No | Parameter        | Value            |

|---------|------------------|------------------|

| 1       | Nominal Power    | 15 MVA           |

| 2       | Grid Voltage     | 4.2 kV           |

| 3       | DC Link Voltage  | $10~\mathrm{kV}$ |

| 4       | System Frequency | 50 Hz            |

| 5       | SM Voltage       | 2 kV             |

| 6       | SM capacitance   | 5000uF           |

| 7       | Arm Inductance   | 5mH              |

**TABLE 2.** Conventional and modified NLM in terms of THD for offline simulation.

| SMs | Conventional NLM<br>% THD |         | Modified NLM<br>% THD |         |

|-----|---------------------------|---------|-----------------------|---------|

|     | Current                   | Voltage | Current               | Voltage |

| 4   | 6.36                      | 9.50    | 3.14                  | 4.71    |

| 8   | 3.17                      | 4.60    | 1.57                  | 2.21    |

| 12  | 1.52                      | 2.19    | 0.80                  | 1.09    |

as 4, 8, and 12, to obtain different AC output levels. It should be noted that prior to 0.04 seconds, conventional NLM is activated. It generates 2N+1 level AC output waveform, having 9.5% voltage THD and 6.36% current THD as shown in Fig. 7 and Fig. 8. Modified NLM is activated after 0.04 seconds. Modified NLM produces 4N+1 level and generates high-quality AC waveforms closed to the reference sinusoidal waveform. Therefore, Modified NLM has improved power quality and reduced harmonic content as compared to conventional NLM. THD of the voltage and current reduces to 4.71%

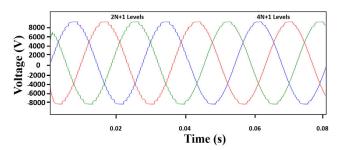

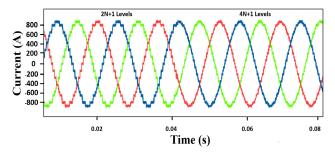

FIGURE 14. Three-phase output voltage with 9 and 17 levels.

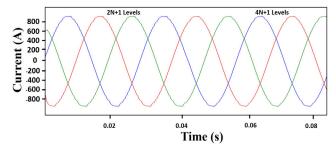

FIGURE 15. Three-phase output current with 9 and 17 levels.

and 3.14%, respectively in modified NLM. The results are further shown from figure 9 to 12 and compared in Table. 2 for the different number of levels.

#### **VI. REAL-TIME SIMULATION RESULTS**

The setup for real-time simulation is shown in Fig. 13. The three-phase MMC circuit designed in Multisim is loaded in NI PXI, an FPGA-based floating-point solver that creates a bit file of the circuit and runs it at nanoseconds on FPGA.

115002 VOLUME 9, 2021

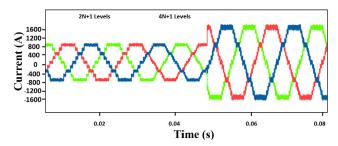

FIGURE 16. Three-phase output voltage with 17 and 33 levels.

FIGURE 17. Three-phase output current with 17 and 33 levels.

FIGURE 18. Three-phase output voltage with 23 levels and 49 levels.

FIGURE 19. Three-phase output current with 23 levels and 49 levels.

The early designed Modified NLC is then loaded on an FPGA-based Compact RIO controller to control the circuit running in PXI. The real-time simulation results are obtained from Figures 14 to 18. Conventional NLM is activated initially, and then the modified NLM is turn on at 0.04 seconds to achieve 4N+1 levels. The results are obtained and summarized in Table 3 for different number of AC output levels to

FIGURE 20. Current waveform showing load variation with 9 and 17 output levels.

FIGURE 21. Current waveform showing load variation with 17 and 33 output levels.

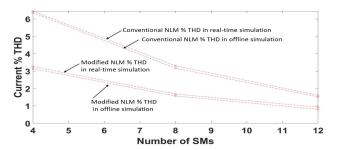

FIGURE 22. Current THD in offline and real-time simulation for modified and convention NLM.

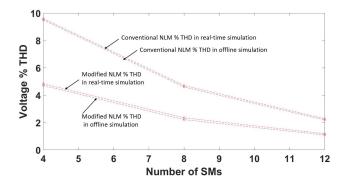

FIGURE 23. Voltage THD in offline and real-time simulation for Modified and convention NLM.

show the effectiveness of the modified control. It should be noted that THD is reduced and the power quality is improved by increasing AC output levels as shown in Table 3. It can be seen from figure 14 to 19 that due to the step size of nanoseconds, ripples appeared in voltage and current. Therefore slight

TABLE 3. Conventional and modified NLM in terms of THD for real-time simulation.

| SMs | Conventional NLM<br>% THD |         | Modified NLM<br>% THD |         |

|-----|---------------------------|---------|-----------------------|---------|

|     | Current                   | Voltage | Current               | Voltage |

| 4   | 6.45                      | 9.59    | 3.26                  | 4.83    |

| 8   | 3.31                      | 4.71    | 1.68                  | 2.35    |

| 12  | 1.61                      | 2.28    | 0.93                  | 1.18    |

difference in THD for offline and real-time simulation can be observed. This slight difference is clearly shown graphically for current and voltage THD, considering offline and real-time simulation in Fig. 22 and 23 respectively. The load is also varied to validate the performance of proposed method. The results are shown in Fig. 20 and 21 for different number of AC output levels.

#### VII. CONCLUSION

Compared to previously presented Modified NLM, which was only confined to HB SMs in HVDC MMC, the Modified NLM method is developed and applied for Full Bridge MMC configuration in this paper. The Modified NLM is simple to implement and produces 4N+1 AC output levels. The method is initially verified with offline simulation using LabVIEW Multisim co-simulation and later executed in NI PXIe for real-time simulation and verification of results. Finally, the results are compared for both offline and real-time simulation in terms of THD.

#### **ACKNOWLEDGMENT**

(Jahangeer Badar Soomro, F. Akhter, Saddaqat Ali, Syed Sabir Hussain Bukhari, and Irfan Sami contributed equally to this work.)

## **REFERENCES**

- B. Qin, W. Liu, R. Zhang, T. Ding, and J. Liu, "Small-signal stability analysis and optimal control parameters design of MMC-based MTDC transmission systems," *IET Gener., Transmiss. Distrib.*, vol. 14, no. 21, pp. 4675–4683, Nov. 2020.

- [2] J. Freytes, S. Akkari, P. Rault, M. M. Belhaouane, F. Gruson, F. Colas, and X. Guillaud, "Dynamic analysis of MMC-based MTDC grids: Use of MMC energy to improve voltage behavior," *IEEE Trans. Power Del.*, vol. 34, no. 1, pp. 137–148, Feb. 2019.

- [3] S. Wenig, M. Goertz, C. Hirsching, M. Suriyah, and T. Leibfried, "On full-bridge bipolar MMC-HVDC control and protection for transient fault and interaction studies," *IEEE Trans. Power Del.*, vol. 33, no. 6, pp. 2864–2873, Dec. 2018.

- [4] M. A. Perez, S. Bernet, J. Rodriguez, S. Kouro, and R. Lizana, "Circuit topologies, modeling, control schemes, and applications of modular multilevel converters," *IEEE Trans. Power Electron.*, vol. 30, no. 1, pp. 4–17, Jan. 2015.

- [5] J. Li, G. Konstantinou, H. R. Wickramasinghe, and J. Pou, "Operation and control methods of modular multilevel converters in unbalanced AC grids: A review," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 7, no. 2, pp. 1258–1271, Jun. 2019.

- [6] L. Zhang, Y. Zou, J. Yu, J. Qin, V. Vijay, G. G. Karady, D. Shi, and Z. Wang, "Modeling, control, and protection of modular multilevel converter-based multi-terminal HVDC systems: A review," CSEE J. Power Energy Syst., vol. 3, no. 4, pp. 340–352, Dec. 2017.

- [7] G. S. Konstantinou, M. Ciobotaru, and V. G. Agelidis, "Analysis of multicarrier PWM methods for back-to-back HVDC systems based on modular multilevel converters," in *Proc. 37th Annu. Conf. IEEE Ind. Electron. Soc.* (IECON), Nov. 2011, pp. 4391–4396.

- [8] G. Konstantinou, M. Ciobotaru, and V. Agelidis, "Selective harmonic elimination pulse-width modulation of modular multilevel converters," *IET Power Electron.*, vol. 6, no. 1, pp. 96–107, Jan. 2013.

- [9] A. Dekka, B. Wu, N. R. Zargari, and R. L. Fuentes, "A space-vector PWM-based voltage-balancing approach with reduced current sensors for modular multilevel converter," *IEEE Trans. Ind. Electron.*, vol. 63, no. 5, pp. 2734–2745, May 2016.

- [10] M. Guan, Z. Xu, Q. Tu, and W. Pan, "Nearest level modulation for modular multilevel converters in HVDC transmission," *Automat. Electr. Power Syst.* vol. 2, p. 12, Jan. 2010.

- [11] P. M. Meshram and V. B. Borghate, "A simplified nearest level control (NLC) voltage balancing method for modular multilevel converter (MMC)," *IEEE Trans. Power Electron.*, vol. 30, no. 1, pp. 450–462, Jan. 2015.

- [12] S. Ali, J. Badar, F. Akhter, S. S. H. Bukhari, and J. Ro, "Real-time controller design test bench for high-voltage direct current modular multilevel converters," *Appl. Sci.*, vol. 10, no. 17, p. 6004, Aug. 2020.

- [13] F. Martinez-Rodrigo, D. Ramirez, A. B. Rey-Boue, S. de Pablo, and L. C. H.-D. Lucas, "Modular multilevel converters: Control and applications," *Energies*, vol. 10, no. 11, p. 1709, 2017.

- [14] S. Debnath, J. Qin, B. Bahrani, M. Saeedifard, and P. Barbosa, "Operation, control, and applications of the modular multilevel converter: A review," *IEEE Trans. Power Electron.*, vol. 30, no. 1, pp. 37–53, Jan. 2015.

- [15] S. Ali, J. B. Soomro, M. Mughal, F. A. Chachar, S. S. H. Bukhari, and J. Ro, "Power quality improvement in HVDC MMC with modified nearest level control in real-time HIL based setup," *IEEE Access*, vol. 8, pp. 221712–221719, 2020.

- [16] W. Zhou, Y. Dong, H. Yang, W. Li, X. He, J. Hu, and X. Yuan, "Common-mode voltage injection-based nearest level modulation with loss reduction for modular multilevel converters," *IET Renew. Power Gener.*, vol. 10, no. 6, pp. 798–806, 2016.

- [17] A. Alexander and M. Thathan, "Modelling and analysis of modular multilevel converter for solar photovoltaic applications to improve power quality," *IET Renew. Power Gener.*, vol. 9, no. 1, pp. 78–88, 2015.

- [18] Q. Liu, A. Chen, C. Du, and C. Zhang, "A modified nearest-level modulation method for modular multilevel converter with fewer submodules," in *Proc. Chin. Autom. Congr. (CAC)*, Oct. 2017, pp. 6551–6556.

- [19] W. Zhao, K. Yang, and G. Chen, "An improved nearest-level-modulation of modular multilevel converter—STATCOM," in *Proc. IEEE 11th Int. Conf. Power Electron. Drive Syst.*, Jun. 2015, pp. 219–223.

- [20] P. Hu and D. Jiang, "A level-increased nearest level modulation method for modular multilevel converters," *IEEE Trans. Power Electron.*, vol. 30, no. 4, pp. 1836–1842, Apr. 2015.

- [21] A. Shojaei and G. Joos, "An improved modulation scheme for harmonic distortion reduction in modular multilevel converter," in *Proc. IEEE Power Energy Soc. Gen. Meeting*, Jul. 2012, pp. 1–7.

- [22] Y. Deng, M. Saeedifard, and R. G. Harley, "An improved nearest-level modulation method for the modular multilevel converter," in *Proc. IEEE Appl. Power Electron. Conf. Expo. (APEC)*, Mar. 2015, pp. 1595–1600.

- [23] L. Lin, Y. Lin, Z. He, Y. Chen, J. Hu, and W. Li, "Improved nearest-level modulation for a modular multilevel converter with a lower submodule number," *IEEE Trans. Power Electron.*, vol. 31, no. 8, pp. 5369–5377, Aug. 2016.

- [24] P. Mishra and M. M. Bhesaniya, "Comparison of total harmonic distortion of modular multilevel converter and parallel hybrid modular multilevel converter," in *Proc. 2nd Int. Conf. Trends Electron. Informat. (ICOEI)*, May 2018, pp. 890–894.

- [25] A. R. Kumar, M. S. Bhaskar, U. Subramaniam, D. Almakhles, S. Padmanaban, and J. B.-H. Nielsen, "An improved harmonics mitigation scheme for a modular multilevel converter," *IEEE Access*, vol. 7, pp. 147244–147255, 2019.

- [26] W. Lin, D. Jovcic, S. Nguefeu, and H. Saad, "Full-bridge MMC converter optimal design to HVDC operational requirements," *IEEE Trans. Power Del.*, vol. 31, no. 3, pp. 1342–1350, Jun. 2016.

- [27] H. Xiao, K. Sun, J. Pan, and Y. Liu, "Operation and control of hybrid HVDC system with LCC and full-bridge MMC connected in parallel," *IET Gener., Transmiss. Distrib.*, vol. 14, no. 7, pp. 1344–1352, Apr. 2020.

115004 VOLUME 9, 2021

JAHANGEER BADAR SOOMRO received the B.E. degree in electronics engineering and the M.E. degree in electrical power systems from Mehran UET Sindh. He is currently pursuing the Ph.D. degree in electrical engineering with Sukkur IBA University, Pakistan. He is currently an Assistant Professor and the Principal Investigator of power hardware with the Loop Laboratory, Electrical Department, Sukkur IBA University. His research interests include power quality anal-

ysis of power converters, PWM techniques to control power converters, PWM inverters, and real-time simulation of power converters.

**F. AKHTER** (Member, IEEE) received the master's degree in electrical and electronics engineering with entrepreneurship from University of Nottingham, U.K., in 2011, and the Ph.D. degree in energy systems from The University of Edinburgh, U.K. He worked, as a Trainee Engineer at Universal Cables Industries Ltd. He then joined Sukkur IBA, in February 2010. He has published a paper in an international journal (Springer) and also presented papers in international conferences. He has also

been presenting and participated in international seminars. His major area of research was the integration of offshore wind farms to onshore AC grids through VSC-HVDC Technology.

**SADDAQAT ALI** received the B.E. degree in electrical engineering from Sukkur IBA University, in 2018, where he is currently pursuing the M.E. degree. From 2018 to 2019, he worked as a Research Assistant with the PHIL Laboratory, Sukkur IBA University. He is currently working as a Subject Specialist (electrical) with the IBA Community College. His research interests include HVDC converters, power quality, and DC microgrids.

**SYED SABIR HUSSAIN BUKHARI** (Member, IEEE) received the B.E. degree in electrical engineering from the Mehran University of Engineering and Technology Jamshoro, Pakistan, in 2009, and the Ph.D. degree from the Department of Electronic Systems Engineering, Hanyang University, South Korea, in 2017. He joined the Sukkur IBA University, as an Assistant Professor, in December 2016. He is currently working as a Research Professor with Chung-Ang University,

Seoul, South Korea, under Korean Research Fellowship (KRF) Program. His research interests include electric machine design, power quality, and drive controls.

**IRFAN SAMI** (Graduate Student Member, IEEE) received the B.Sc. degree in electrical engineering from the University of Engineering and Technology, Peshawar, Bannu Campus, Pakistan, in 2016, and the M.Sc. degree in electrical engineering from COMSATS University Islamabad, Abbottabad Campus, Pakistan, in 2019. He is currently pursuing the Ph.D. degree in electrical engineering with Chung-Ang University, Seoul, South Korea. His research interests include electric

drives, renewable energies, and electrical machine design.

JONGSUK RO received the B.S. degree in mechanical engineering from Hanyang University, Seoul, South Korea, in 2001, and the Ph.D. degree in electrical engineering from Seoul National University (SNU), Seoul, in 2008. He conducted research at the Research and Development Center of Samsung Electronics, as a Senior Engineer, from 2008 to 2012. From 2012 to 2013, he was with the Brain Korea 21 Information Technology, SNU, as a Postdoctoral Fellow. He conducted

research at the Electrical Energy Conversion System Research Division, Korea Electrical Engineering & Science Research Institute, as a Researcher, in 2013. From 2013 to 2016, he worked with the Brain Korea 21 Plus, SNU, as a BK Assistant Professor. In 2014, he was with the University of Bath, Bath, U.K. He is currently an Associate Professor with the School of Electrical and Electronics Engineering, Chung-Ang University, Seoul. His research interests include the analysis and optimal design of next-generation electrical machines using smart materials, such as electromagnet, piezoelectric, and magnetic shape memory alloys.