Received July 7, 2021, accepted July 18, 2021, date of publication July 26, 2021, date of current version August 6, 2021. Digital Object Identifier 10.1109/ACCESS.2021.3100540

# A Survey on the Security of Wired, Wireless, and 3D Network-on-Chips

AMIN SARIHI<sup>®1</sup>, (Graduate Student Member, IEEE), AHMAD PATOOGHY<sup>®2</sup>, AHMED KHALID<sup>®3</sup>, MAHDI HASANZADEH<sup>®4</sup>, MOSTAFA SAID<sup>®5</sup>, AND ABDEL-HAMEED A. BADAWY<sup>®1</sup>, (Senior Member, IEEE)

<sup>1</sup>Klipsch School of Electrical and Computer Engineering, New Mexico State University, Las Cruces, NM 88003, USA

<sup>2</sup>Department of Computer Science, University of Central Arkansas, Conway, AR 72035, USA

<sup>4</sup>Independent Researcher, Tehran 25529, Iran

<sup>5</sup>Department of Computer and Electrical Engineering and Computer Science, California State University, Bakersfield, CA 93311, USA

Corresponding author: Amin Sarihi (sarihi@nmsu.edu)

**ABSTRACT** Network-on-Chips (NoCs) have been widely used as a scalable communication solution in the design of multiprocessor system-on-chips (MPSoCs). NoCs enable communications between on-chip Intellectual Property (IP) cores and allow processing cores to achieve higher performance by outsourcing their communication tasks. NoC paradigm is based on the idea of resource sharing in which hardware resources, including buffers, communication links, routers, etc., are shared between all IPs of the MPSoC. In fact, the data being routed by each NoC router might not be related to the router's local core. Such a utilization-centric design approach can raise security issues in NoC-based designs, e.g., integrity and confidentiality of the data being routed in an NoC might be compromised by unauthorized accesses/modifications of intermediate routers. Many papers in the literature have discovered and addressed security holes of NoCs, aiming at improving the security vulnerabilities and countermeasures for NoCs. This paper will review security threats and countermeasures proposed so far for wired NoCs, wireless NoCs, and 3D NoCs. The paper aims at giving the readers an insight into the attacks and weaknesses/strengths of countermeasures.

**INDEX TERMS** Network-on-chip, threat model, hardware security, hardware trojan, DoS attack.

### I. INTRODUCTION

Ever increasing VLSI technology shrinkage has enabled Multi-Processor System-on-Chips (MPSoCs) to accommodate tens of Intellectual Properties (IPs), e.g., processing cores, memory modules, and various I/O components. This technology shift urges the necessity for an efficient communication architecture to enable fast, yet energy-efficient data exchange across the chip. Network-on-Chips (NoCs) were first introduced in 2004 [1] as a scalable communication architecture and later widely used in the design and fabrication of many chips (e.g., Tilera TILE64 [2] and Kalaray's MPAA-256 [3]). As most of the modern MPSoCs use an on-chip network as their backbone communication architecture, the industry has already started offering NoC IPs (for instance, FlexNoC IP from Arteris company [4]) to facilitate the design process.

The associate editor coordinating the review of this manuscript and approving it for publication was Yanjiao Chen<sup>(D)</sup>.

The main idea of on-chip networks is to share resources to boost resource utilization, i.e., a number of on-chip components are interconnected via a shared network that is governed by a set of structural, routing, switching, and flow-control rules. While attaining a satisfactory bandwidth, the structured architecture of NoCs helps to avoid long communicating wires (also known as long interconnects) that are significant contributors to dynamic power consumption [5] as well as reliability issues [6]. NoCs offer high resource utilization, design modularity, and support for parallel communications with moderate performance/energy efficiency [7]. NoCs' moderate efficiency has its roots in i) having communications between far cores in which messages have to be forwarded over a long chain of adjacent routers, and ii) one-to-many message broadcast situations that have to be handled sequentially. To address these shortcomings, researchers have introduced the idea of adding wireless communications through wireless routers. In a WNoC (Wireless Network-on-Chip), far-distant messages and one-to-many

This work is licensed under a Creative Commons Attribution-NonCommercial-NoDerivatives 4.0 License. For more information, see https://creativecommons.org/licenses/by-nc-nd/4.0/

<sup>&</sup>lt;sup>3</sup>Department of Computer Engineering, Assiut University, Assiut 71515, Egypt

messages are broadcasted in a one-hop fashion through wireless links/transceivers, boosting the overall performance and energy efficiency [8].

While performance aspects of NoC have been addressed over the years in different proposals/papers, security, nevertheless, has remained a serious challenge for designers. The idea of an on-chip network that easily accesses/forwards messages of different IP cores chip-wide may complicate the security issues, i.e., the benefit gained by resource sharing in NoC fabrics might be counter-productive when data integrity and confidentiality are essential.

Utilization of 3rd-party IPs (3PIPs) to avoid the exorbitant cost and design time of MPSoCs is common among SoC designers [9]. The IPs could range from processing cores and DSP units [10] to even the NoC itself [4]. NoC IPs are widely used in different devices such as tablets, mobile phones, and autonomous vehicles as a part of the MPSoC. 80% of the top five Chinese fabless companies are using the 3rd-party Arteris FlexNoC interconnect [11]. In fact, MPSoC designers prefer to use the 3PIP (third-party IP) NoC due to the lower time-to-market and production cost. However, the utilization of 3PIPs products in the design of MPSoCs, may ultimately introduce new security vulnerabilities, e.g., security holes or threats. Some of the 3PIPs could be infected by some type of Hardware Trojan (HT) [11]. This includes IPs designed in-house using a trusted design team and trusted CAD tools such as Synopsys and Cadence. They might be infected by a foundry during the post-design stage [12]. HT-infected IPs use specific trigger conditions, making them substantially harder to detect [13], so they mostly bypass verification and manufacturing testing procedures. Upon activation, HTs could take a severe toll on the functionality of the chip. A successful attack could lead to irrecoverable economic and social losses that might not be easily compensated [14].

Generally, a malicious activity targets at least one of the major security requirements including *confidentiality*, *integrity*, and *availability* which are called the CIA triad [15] and are defined as follows:

- **Confidentiality**: sensitive information should be only available to authorized agents.

- **Integrity**: unauthorized agents are not allowed to modify the contents of a message.

- Availability: network resources remain available during its operation.

Attackers try to undermine these three security aspects, and SoC designers must obtain and keep the security goals to safeguard the system. While NoC security has been surveyed briefly in some previous works [16]–[19], to the best of our knowledge, there is no solid work that surveys the recent security solutions for various NoC technologies. This paper covers both the different attack models and the proposed countermeasures for wired, wireless, and 3D NoCs.

The rest of this paper is organized as follows. In section II, we explain the architecture of wired, wireless, and 3D NoC. In section III, the attacks and the related taxonomy in the literature are discussed. Proposed countermeasures in wired, wireless, and 3D NoC is discussed in details in sections IV, V, VI, respectively based on the threat model. Lastly, In section VII, a guideline for future research in NoC security is provided.

## **II. PRELIMINARIES**

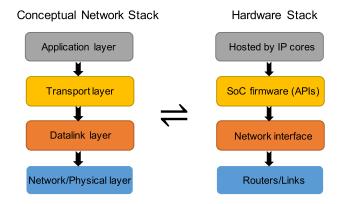

NoCs were introduced to implement the idea of separating communications and computations inside modern multi-core chips. Every communicating agent on the chip is equipped with the required tools to interact with the on-chip network. The network stack (shown in Figure 1) is widely used in the design of on-chip networks. According to this figure, layers of the network stack are accommodated using some layers in the hardware. The application layer provides communications between applications running on different processing/DSP cores and/or applications accessing memory/IO module. The application layer is, in fact, a communication layer between an application running on a processing/DSP core and another processing core or a memory/IO module. The transport layer is the SoC firmware that offers system-level services to send/receive messages between IPs/modules. The data link layer, which makes data chunks ready for transmission, is hosted on the hardware component known as the network interface (NI). The NI is the gateway that connects every local IP to the global (chip-wide) network. Finally, the network and physical layers of the stack are implemented as the on-chip routers and channels. Routers are responsible for storing, routing, and forwarding data units over the channels. They are interconnected using channels following a predefined topology structure such as 2D/3D mesh, butterfly, fat-tree. etc.

FIGURE 1. The network stack model.

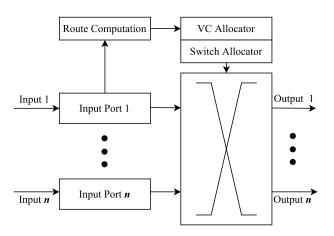

Figure 2 shows the architecture of a typical router used in NoCs, known as a virtual channel (VC) router. It consists of the following components:

- VC buffers: store ingress/egress data units (so-called flits) for each port.

- Ports or channels: pass data between adjacent routers.

- Routing computation unit: computes the appropriate outgoing port for packets based on the routing policy used and the network congestion situation.

FIGURE 2. Architecture of a typical VC-enabled router for NoCs.

- VC allocator: finds an available VC buffer for the outgoing packets.

- Switch allocator: responsible for the arbitration of the input/output ports of the crossbar switch.

Routers/channels of on-chip networks are treated as shared resources to achieve better utilization, i.e., every router is responsible for storing, routing, and even forwarding packets that might not be issued by the router's local core. In fact, several on-chip routers may contribute to forwarding a packet that might not be directly related to them. The benefit gained by resource sharing in NoCs may be counter-productive when data integrity and confidentiality are considered. This raises the chances for malicious routers to access, sniff or modify packets of data. This is especially true if the NoC is integrated as a 3PIP in a bigger design [11]. While cores and NIs deal with local data only, routers and channels are in charge of forwarding local and global data.

Looking at the components of an NoC-based MPSoC, vulnerability points of such chips can be listed as follows:

- Processing cores/IPs are bought from various IP providers and can contain HTs injected by the designer/manufacturer to either implement or facilitate malicious activities. They can also be infected by software malware [20], [21].

- One or more of the working NIs in the network might be infected by an HT to interrupt expected services of a clean NI.

- One or more routers or links of the network might be infected by HTs to conduct malicious activities.

In Section III of the paper, we discuss how each of the infections mentioned above may result in a security threat. There might be additional components in the NI or the router logic if the NoC is a more advanced one, e.g., wireless NoC, 3D NoC, or a custom NoC architecture. Considering two major classes of advanced NoCs, we describe other components that can be found in wireless NoCs and 3D NoCs and their corresponding security threats in the next subsections.

## A. 3D NETWORK-ON-CHIPS (3D NoCs)

The implementation of NoCs in 3D stacked ICs creates what is called 3D NoCs. This newborn communication architecture allows for significant performance, area, and power improvements over traditional 2D NoCs [22]. One major architectural difference observed in 3D NoCs is the use of vertical channels to realize inter-layer communications. Vertical channels add two more ports to the router and crossbar switch to communicate with upper and lower layers. Due to the different fabrication processes of vertical connections, mainly based on Through Silicon Vias (TSVs), the following changes compared to 2D NoCs are worth mentioning. 1) TSV channels introduce several advantages, including lower signal delay, smaller chip form factor, and higher integration density. 2) TSVs help 3D NoCs mitigate inter-layer traffic load and use fewer signal drivers and repeaters [23]. 3) Due to their high fabrication costs, TSV channels are implemented only in a handful of routers in some designs. This makes TSV channels security/reliability hot-spots in the 3D NoCs [24].

## B. WIRELESS NETWORK-ON-CHIPS (WiNoCs)

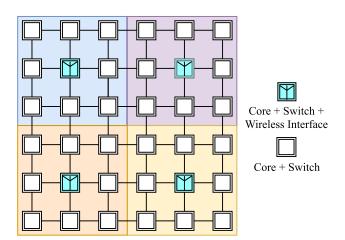

Packets in wireless NoCs (WiNoCs) can pass through two paths: one is the conventional wired NIs, routers, and channels; the other is the shared wireless medium by using wireless interfaces and wireless signal transceivers of the NI. The wireless hub is basically a conventional NoC router with an extra port connected to the wireless interface. Depending on the application needs, some researchers assume all routers are connected to wireless interfaces [8] and many others assume that the network is divided into clusters where each cluster is connected to a single wireless hub to minimize the design cost [25], [26], Figure 3 shows an example of such a clustered network. The most significant advantage of WiNoCs lies in its low delay in broadcast and multicast transmissions. Thanks to the millimeter-wave omnidirectional antennas that are usually adopted in WiNoCs [27], applications such as cache coherency protocols are performed tremendously fast

FIGURE 3. A simple example of a WiNoC with four clusters.

using WiNoCs. For instance, WiNoCs are able to transfer a 64B cache line anywhere within 5–15 cycles [28].

## **III. TAXONOMY AND ATTACKS**

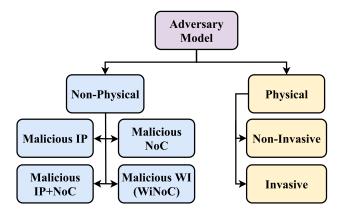

Figure 4 represents a high-level taxonomy of the attacks on MPSoCs. The so-called *physical attacks* require physical access to the chip to conduct the intended malicious activity, i.e., read some internal/external signals of the chip, access NoC channels, or monitor the chip's power profile. Physical attacks can either be: 1) invasive, in which the packaging of the victim chip is dissected by the attacker for more detailed analysis, e.g., probing attacks; however, the chip must remain functional after decapsulation, or 2) non-invasive, which do not impose physical modifications to the chip. Non-invasive physical attacks are relatively cheaper and easier to implement, e.g., power side-channel attacks.

FIGURE 4. High-level taxonomy of the attacks on MPSoCs.

The need for physical access limits the applicability of physical attacks. In contrast, non-physical attacks do not rely on having physical access to the chip that eases their application in MPSoCs. In the rest of this section, we assess and classify non-physical security attacks. In Section III-A, attacks that are common for traditional 2D NoCs, 3D NoCs, and WiNoCs are discussed. In sections III-B and III-C, attacks that are specifically applicable on WiNoCs, and 3D NoCs are discussed, respectively.

In MPSoCs, *Malware Injections* and *Hardware Trojans* are the two major sources of non-physical attacks by introducing malicious IP, malicious NoC, or a combination of both. IPs infected by malware contribute to 80% of the total attacks on embedded systems [29]. Malware infections mostly happen at the device firmware/software update/patching process [30] where the software accesses bare-metal hardware.

HTs are tiny circuits that start their malicious activity after being triggered. The triggering part of HTs seeks for very rare conditions (mostly a set of signals acquiring their rare values). Subsequently, most traditional logic testing methods mostly fail in detecting HTs [31]. As HTs show negligible power and area footprints, side-channel analysis methods would also exhibit deficiencies in detecting them. Many researchers have addressed HT-induced malfunctions in NoC-based MPSoCs. HTs can be inserted by different agents at various stages of the design manufacturing process. Some insertion scenarios are as follows:

- HTs can be inserted through gate-level manipulation of the NoC netlist by an adversary designer [32], [33].

- EDA tools can also target companies' products to insert HTs for defamation purposes.

- Designs layout might be modified at the fabrication stage [34].

- 3PIPs used to expedite MPSoC design might be pre-infected by HTs [33].

Researchers have proposed various HT circuits for processing/NoC IPs. HTs proposed for processing IPs are beyond the scope of this paper, we only review NoC HTs in the rest of this section.

A malicious NoC comprises situations of having at least a malicious Network Interface (NI) or a malicious router in the NoC fabric. Either the NoC vendor or the fabrication factory can insert HT circuitry into the clean NoC design to infect the NoC. HT insertions target i) the network interface to alter packetizing/de-packetizing or flow control of data, or ii) the router logic to negatively impact route computation which leads to packet misroute/loss/duplication, or to inject low-priority packets to discover the timing information of high-priority packets [35].

Ancajas et al. [11] have explored the consequences of inserting an HT in a cloud MPSoC system. The proposed HT initiates a duplication attack once inserted in the router. The area and power overheads of the proposed HT are 4.62% and 0.28%, respectively. The HT proposed in [14] targets allocator modules of NoC routers by de-prioritizing arbiters. It prolongs the crossbar traversal delay by denying fair crossbar allocation to the packets destined to or originated from a victim node. The HT's overhead is nearly 4% compared to the baseline router. Another study by Daoud and Rafla [36] has proposed an HT to be inserted within the NoC routers. This HT is capable of misrouting packets and eventually causing DoS while having less than 1% area overhead compared to the baseline router. Daoud and Rafla [37] have introduced a DoS attack using a black hole router that drops packets passing through it with less than 2% power and area overhead. Raparti and Pasricha [38] have implemented an HT in the NI that facilitates information stealing. The HT works by manipulating the FIFO header pointer in the NI FIFO queue that eventually leads to duplication attacks. The HT yields a 1.3% overhead compared to the baseline NI. Table 1 summarizes the HTs area and power costs in the previous work.

Malicious IP+NoC is, of course, a more serious threat as it is capable of carrying out a wider spectrum of threats; however, it is harder to achieve by adversaries. As the SoC designers order IPs from different IP providers, the activation chances of malicious NoC and IPs at the same time to conduct a collaborative attack are slim.

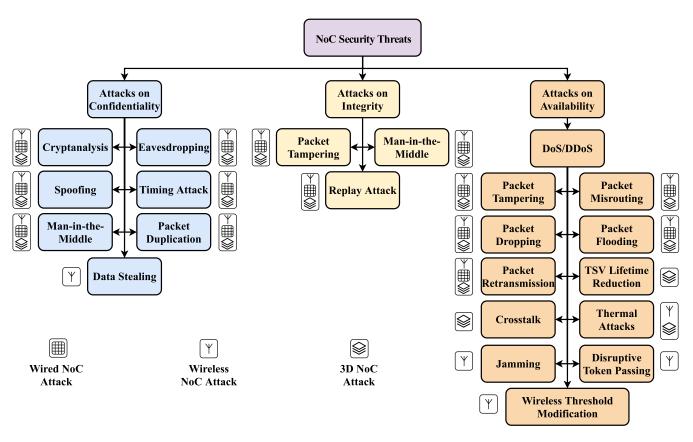

FIGURE 5. Classification of the addressed attacks based on the attacker's target security goal.

| Reference                          | Area  | Power  | WRT*   |

|------------------------------------|-------|--------|--------|

| Ancajas et al. [11]                | 4.62% | 0.28%  | Router |

| Rajesh et al. [14]                 | 4.32% | 0.014% | Router |

| Daoud and Rafla [36]               | 0.2%  | -      | Router |

| Daoud and Rafla [37]               | 1.98% | 0.74%  | Router |

| Raparti and Pasricha [38]          | 1.3%  | -      | NI     |

| *WRT $\triangleq$ With Respect To. |       |        |        |

#### TABLE 1. HT implementations costs.

#### A. COMMON ATTACKS ON 2D, 3D, AND WIRELESS NoCs

Figure 5 shows our proposed attack classification based on the attacker's target security goal. In this figure, it is considered that an attacker aims to undermine at least one of the three security bases, i.e., *confidentiality*, *integrity* and *availability*. Following is an explanation of the bases and the attacks proposed for each one in the context of NoC-enabled MPSoCs.

*Confidentiality*, as one of the major factors of security, denotes to protect assets of a system from any unauthorized access. In the NoC context, this is equivalent to guaranteeing that the messages/packets traversing the network are kept private between the sender and receiver nodes. For this aim, packet encryption is considered as one of the solutions to ensure data confidentiality in NoCs. Based on assessments we have done in our studies, attacks that alter data confidentiality In the NoC context can be summarized as follows:

- **Eavesdropping:** data communication between a source and a destination node is being sniffed by an unauthorized adversary, e.g., a malicious router, or a router along with an IP. The data may contain sensitive information such as passwords or encryption keys [32].

- **Differential Cryptanalysis:** analogous to differential power analysis attacks, the attacker tries to infer secret information by analyzing the transmitted data over a channel and guessing the encryption key [11]. In most cases, the attack needs collaboration between a malicious router and a malicious IP.

- **Timing Attack:** intentional collisions between the attacker's data and others' sensitive data on a specific path are made to release valuable information regarding the timing and the volume of the sensitive information to the attacker [39]. The key idea is that the attacker measures the timing delay of their own data that is proportional to the existence or non-existence of the sensitive information on the same path.

- **Spoofing:** gaining unauthorized access to data by using a counterfeit identity [39]. The accessed data could be a portion of the shared memory that is, by default, not accessible [40].

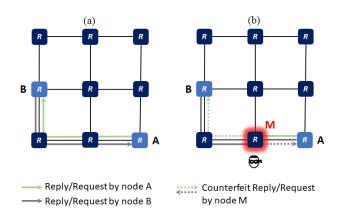

- Man-in-the-middle (MITM): an unapproved node meddles in the communication between a pair of source and destination nodes to monitor the passed data.

Figure 6 shows the threat model used in the MITM attacks. Node A will send a communication request to Node B and node B replies. The malicious node M intercepts the connection between A and B through impersonating as the other party to A and B, respectively. It serves both nodes by fraudulently tampering with the connection between them to infer secret information. The MITM node has to keep the connection flowing between A and B and for the continuity of the attack. MITM attack can alter confidentiality and/or integrity of NoCs.

#### FIGURE 6. The threat model used in MITM attacks.

• **Duplication:** A malicious router duplicates incoming packets and forwards them to a new destination for further processing, e.g., cryptanalysis or timing analysis. Due to the fact that the router still forwards the packets to the intended destinations, detecting this activity as a part of a multi-agent attack might not be easy.

*Integrity*, as another major security factor, is also subject to various attacks by adversaries. In the security context, integrity refers to preventing any unauthorized agent from modifying security assets. In the NoC context, this translates to preventing unauthorized changes in any field of packets, including data or control fields. We review attacks on integrity in the following:

- **Tampering:** the content of a packet can be modified by a malicious node on different levels such as source corruption, payload corruption, and tag corruption [21]. This can lead to various network-level problems, including packet misrouting [41], packet dropping, and packet retransmission.

- **Replay Attack:** an intercepted packet is replayed by an adversary to the same destination to ask for unauthorized resources. As the original and replayed packets are the same, the receiver treats them as two valid packets [42].

The last type of attacks in our classification targets the *Availability* of an NoC fabric. Traditionally, availability is defined as having assets accessible to legitimate agents at any time. Assets may include routers, buffers, channels, and other resources in the network. The goal of such attacks is to ultimately stop the chip from working by rendering some

of its resources unavailable. The attacks classified in this category are as follows:

- Denial of Service (DoS): an adversary disrupts the system's functionality by malicious activities such as flooding the network with junk packets or misrouting packets to artificially-made congested paths [39]. As the latency degradation (network-level impacts of the attack) translates to application performance degradation, DoS attacks can alter the functionality of real-time MPSoCs without even completely stopping them [14].

- **Distributed Denial of Service (DDoS):** if a DoS attack is collaboratively carried out by multiple adversaries on a common victim [43], it is referred to as a distributed DoS attack.

- **Retransmission Attack:** when a tampered packet fails the error checking mechanism (done either hop-by-hop or only at the destination node), a retransmission request is sent to the source node. Repeating this process over and over will eventually lead to denial of service [44].

- **Packet Dropping:** when some packets of the network are discarded. This can be done on either random packets or packets carrying certain information in the header or body [45].

- **Packet Misrouting:** attackers misroute packets of the network with the aim of creating livelocks or deadlocks that may halt the operation of the whole chip [36].

- **Packet Flooding:** attackers flood the system with arbitrary data to delay or drop the legitimate flow of data [46].

## **B. ATTACKS ON WIRELESS NoCs**

The following attacks exploit features/specifications of wireless connectivity to launch attacks on wireless NoCs.

- Jamming-based DoS: transmitting junk packets on the same frequency band that legitimate wireless routers use, causes collisions and prevents the legitimate packets from being received properly. If the junk packets are sent using higher transmission power than the legitimate ones, even more distortion will happen.

- **Eavesdropping:** taking advantage of the broadcasting nature of the wireless medium, a malicious eavesdropper can passively listen to all packets being transmitted over the wireless medium. In some cases, an external attacker (a device located outside the chip packaging) with an antenna tuned to the working frequency of the chip can listen to the chip's communications without any of the internal nodes ever knowing.

- **Packet Tampering:** If a malicious wireless interface (WI) is malicious, it can tamper with the content of the messages sent through it. This may cause the entire chip to malfunction or experience degraded performance.

- **Broadcast Data Stealing:** a smart packet tampering attack launched by converting unicast packets (destined to a specific receiver) to broadcast ones. When broadcast

packets are sent over the wireless medium, this allows external eavesdroppers to steal the packets.

- Threshold Modification Attack: the adversary tampers with the message-size threshold in the router to have fewer/more messages sent wirelessly. If the adversary sets the threshold to zero, all messages will be directed to the wireless interfaces leading to QoS and over-utilization issues. In contrast, setting the threshold to a high value leads to under-utilization of the wireless interfaces.

- Token Tampering: attackers tamper with the communication time limit (known as token) in contention-free wireless NoCs. By setting the token time to i) zero: no node will ever transmit over the wireless channel, or ii) maximum: all nodes start transmitting at the same time without any actual receivers or vice versa. Such over-utilization of the wireless hubs leads to a massive power drain.

- Thermal Attack: as a side effect of over-utilization of resources, attackers can overheat the chip that eventually leads to performance degradation and/or data loss. To tackle the heat issues, the operating system may apply thermal throttling by reducing the operating frequency, thus degrading the performance.

## C. ATTACKS ON 3D NoCs

Adversaries can attack 3D NoCs in some unique ways targeting the stacked architecture of the chips. We review these attacks next.

- TSV Crosstalk Attack: crosstalk happens due to electrical coupling between wires of a TSV, and can be used to invalidate packets while passing through the TSVs. The attacker will inject some bait packets to pre-charge the TSV wires in a way that maximizes the tampered bits in the packet. Tampering happens by delaying or accelerating signal transitions on the victim wires of the TSV. It has been shown in [47] that this type of tampering may have a wide range of consequences, including packet misrouting that can lead to a global deadlock over the network.

- **TSV Lifetime Degradation:** TSVs degrade over time depending on the intensity of the workload passing through them. An attacker can shorten the lifespan of the chip by over-utilizing a specific TSV. For this attack, extra packets are being intentionally forwarded toward a specific vertical link. This attack can have drastic impacts on the chip's lifetime [48].

- **Thermal Attack:** having multiple dies stacked vertically results in trapping heat between them due to the relatively long distance to the heat sink. This creates opportunities to leverage heat to either stealthily trigger an HT or generate excess heat. Excess heat can degrade the performance due to thermal throttling or even shorten the lifespan of the chip.

## **IV. WIRED NoCs COUNTERMEASURES**

A key factor of an NoC-security countermeasure is the unit in which the countermeasure is implemented. If the NIs are assumed trusted (in-house design), the countermeasure(s) can be integrated within the NI units. Many researchers have integrated their security solutions in the NI units, e.g., bulky modules for symmetric and asymmetric cryptography [40], [49], [50]. Also, most countermeasures that guarantee secure memory access are implemented in NIs. These countermeasures can profoundly enhance data confidentiality, while they might not be able to address DoS attacks such as packet misrouting, packet dropping, and packet tampering.

Routers are literally the first line of defense, so researchers have also used routers to integrate their security solutions [32], [35], [36], [51], [52]. Suppose a packet injected by a malicious task is heading towards a secured zone of the network to carry out an attack, e.g., timing attack, spoofing attack, etc. Security-enhanced routers can easily prevent such attacks. However, built-in countermeasures (mostly DoS protection countermeasures) of 3PIP routers are susceptible to reverse-engineering, so the functionality and security services of these routers might not be highly reliable. NoC designers must consider these trade-offs in the design stage to make optimal decisions based on the characteristics of the target applications of the MPSoC.

## A. DATA CONFIDENTIALITY COUNTERMEASURES

Figure 7 depicts a situation where a malicious router makes copies of sensitive packets with high-security requirements and redirects them to an unauthorized IP to infer secret information. The details of this attack are explained in section III-A. Data encryption and data scrambling methods can significantly prevent these threats, and they are widely used to achieve confidentiality in NoC-enabled MPSoCs. By obfuscating ciphertext relation with plaintext and key (also known as confusion and diffusion), adversaries cannot extract secret information from the ciphertext.

FIGURE 7. The threat model used in packet duplication attacks.

Researchers have used various types of encryption methods to address security threats covered in section III-A. In the rest of this subsection, we first briefly review various types of encryption methods as a preliminary and then review the literature.

Symmetric-key encryption algorithms use the same cryptographic keys for both encryption and decryption processes [53], [54]. Consequently, they would need to agree on keys ahead of time, i.e., a process known as key exchange. The key is exchanged either by sending unencrypted data over a secure channel or through key exchange mechanisms, such as Diffie-Hellman, in an insecure environment. In addition to the key exchange, symmetric-key encryption method can either work on i) data blocks obtained by dividing the plaintext into fixed-size blocks and encrypting each block of data (so-called Block ciphers), or ii) data streams obtained by dividing the plaintext into single bits, and each bit is encrypted individually (known as stream ciphers). The asymmetric-key (public-key) encryption algorithms, on the other hand, use different keys for encryption and decryption processes. The encryption key (public key) is visible to everyone; however, each user's decryption key (private key) is kept private [55], [56]. In general, the symmetric-key encryption methods (and in particular block ciphers) have been used more frequently in the NoC security context. This is due to the lower hardware requirements of these methods (less memory, less logic, etc) as well as being more predictable in terms of establishing a secure connection.

Assuming malicious NoC+IP model, Sepúlveda *et al.* [21] proposed security countermeasures integrated into the NI. Authors argue that the NI is built in-house and, therefore, can be trusted. The so-called tunnel-based NI encrypts all portions of the packet except the destination address. The encryption used is straightforward, i.e., XOR of the packet payload with a random key (AES in counter mode). A hash function is also applied to the packet for authentication and tamper detection. However, the AES encryption leads to a relatively large area overhead when compared to the baseline MPSoC.

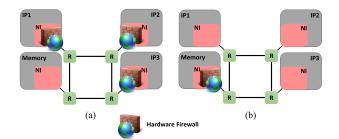

Oliveira *et al.* [49] aimed at measuring the latency overhead of AES encryption when used between the NI and the router. The proposed architecture consists of a manager element that generates unique random keys for each communication session. A firewall is placed between the IP and NI to monitor and manage the IP's incoming/outgoing traffic. Encryption keys are sent through the firewall that decides whether the data must be encrypted or decrypted. The ASIC implementation shows a 193.7% increase in area, while hardware simulation shows a 395.92% surge in worst-case latency, making this architecture an unrealistic solution. The paper has failed to provide a key exchange algorithm that remains one of the most critical problems in the security of today's MPSoCs.

Charles *et al.* [57] proposed a key exchange mechanism along with an anonymous routing approach that hides the source/destination of a packet while traversing the network. The anonymous routing has two phases: route discovery and data transfer. In the route discovery phase, a packet is broadcasted from the source node that contains three security fields: i) the source's one-time public key in plaintext, ii) the encrypted version of the source's one-time public key, and a random number using the destination's public key, iii) the temporary public key of the sender node. Every node that receives this packet tries to decrypt the encrypted portion of the message and compare it with the first part; if it succeeds, it is the intended receiver; otherwise, the node only forwards that packet. Once the packet gets to the intended destination, the first and second fields will match, and the packet will not be forwarded anymore. At this point, the receiver generates a symmetric key (using a random number embedded in the encrypted part of the packet) and returns an encrypted packet that contains a nonce for establishing an anonymous path and a key for symmetric-key encryption. In this method, each node only knows its previous and next neighbor and is unaware of the final source and destination. Although the method is claimed to be highly secure, an attacker can break the route discovery phase by tampering with the route-confirmation packets. Also, the method imposes significant area and power overheads as it requires hop by hop decryption during the key exchange phase. Finally, this method needs to have keys pre-loaded in the routers.

Sant'Ana *et al.* [58] have noted the shortcomings of secure zones, encryption, and firewalls. They argue that these remedies limit MPSoC utilization and incur a substantial hardware cost. They have proposed two encryption schemes (AES and SIMON [59]) to be embedded into the network with stark area overhead differences. The high-security achievement by AES comes with significant power and area overhead. Simon, on the other hand, offers security on constrained devices. Its area is almost one-fifth of AES's area, and its power overhead is 25 times less; however, it is nearly seven times slower than AES. There is no information provided regarding what percentage of the packets were encrypted.

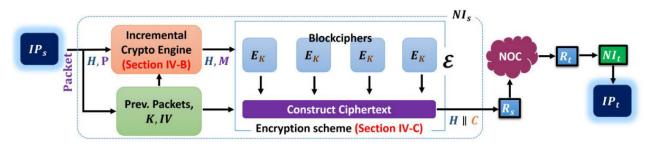

To reduce the cost of AES and still add high level of security, the authors of [50] adopted the Hummingbird-2 [60] block cipher scheme. Hummingbird-2 is a lightweight encryption which is mostly implemented in RFID tags. The authors assumed malicious NoC+IP adversary model, where sniffed packets could be sent to a malicious IP for further analysis. They used incremental cryptography, which outperforms other encryption algorithms, to guarantee secure communications between IPs. As depicted in Figure 8, the encryption module is placed in the NI. The proposed incremental encryption is claimed to be suitable for specific data types such as images where chunks of data are fetched from consecutive memory locations. In this method, packets take advantage of the previous encrypted memory requests and the corresponding decrypted memory responses to partially reduce the required encryption/decryption computations. Indeed, new packets are encrypted with fewer computations since the whole encryption process is no longer needed. Although the authors have claimed 80% similarity in packets

FIGURE 8. The incremental encryption module is placed within the NI [50]. The proposed architecture can encrypt four blocks of data simultaneously.

of specific applications such as image-processing, they did not address the actual chance of similar data block positions as well as the same cryptographic nonces (per requirements of the proposed incremental encryption). Moreover, packet headers should be kept as plaintext to enable routing, which may result in data-stealing attacks. The key exchange scheme between two IPs is not addressed in the paper, too.

Unlike the former mentioned works in this section, [11] has not addressed confidentiality with standard encryption methods. Instead, the authors have developed/used their own lightweight data scrambling methods. The authors have proposed a security mechanism to attain data confidentiality and thwart packet duplication. Data is scrambled by the SoC firmware at the first layer using XOR cipher encryption (one-time pad) to lower the chance of HT activation. While effective in stopping functional HTs, the security depends on the key distribution and generation mechanisms that were not explained. To cope with other types of HTs like always-on and internally triggered HTs, authors also used encryption in other layers to guarantee NoC confidentiality. However, the authors have not studied the impacts of the used encryption methods on the activity of the SoC signals. As the encryption keys should be generated randomly, the XOR operation used in the encryption algorithm can increase the signal activity<sup>1</sup> when the ciphertext is being routed over the network. This acts against the paper's goal of not triggering possible HTs of the chip.

In [38] Raparti and Pasricha have addressed snooping attacks (duplication) in their work where a malicious IP and an HT in the NI can cooperate to steal information. The paper aims at detecting HTs during runtime and pinpointing the software task that initiates the snooping attack. The authors implemented their own version of an HT in the NI's FIFO queue. A lightweight HT mitigation mechanism is also implemented in the NI to ensure that the flits are not reproduced with different destination IDs. Also, an analog-based HT detection mechanism is utilized. It is based on the observation that the ratio of incoming/outgoing messages in a trusted node is less than 1. The detection mechanism is not fast-acting and may need up to two days to alert the system about the attack.

Moreover, the proposed countermeasure is unable to detect HTs that copy data in the router instead of the NI.

Table 2 summarizes confidentiality countermeasures and compares them in terms of the encryption method, area/power overheads, and performance impact.

#### **B. TIMING-ATTACK COUNTERMEASURES**

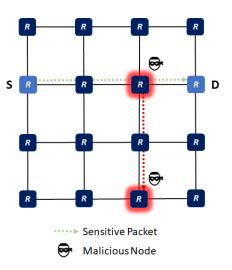

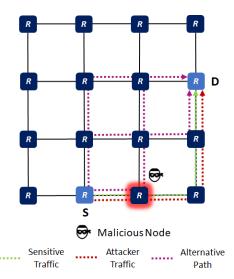

Figure 9 illustrates an example of the timing attack scenario. Node S sends a sensitive packet to node D. The attacker node injects its packets with the same destination to monitor the sensitive packets from S to D. Consequently, both packet types follow the same route. Since both the attacker's data and sensitive data request the same output ports in the routing path, arbiters decide which dataflow to grant first. Degradation of the attacker's throughput stems from the injection of the sensitive traffic, thereby leaking information about the attacker's sensitive traffic.

FIGURE 9. The threat model used in timing attacks.

The implementation of timing attacks requires ample information about NoC topology, sensitive and non-sensitive information/tasks mapping, and the used routing algorithm. The impact of timing attacks can be significant, e.g., in [64], a malicious task observes AES encryption sensitive traffic and recovers 12 out of 16 bytes of the 128-bit key. This makes

<sup>&</sup>lt;sup>1</sup>Signal activity denotes the rate of having signal transitions (0  $\Leftrightarrow$  1) on a net of a digital circuit.

| Reference                 | Adversary   | <b>Encryption Method</b>                                  | Area / Power<br>Overhead | WRT                    | Performance Impact                              |

|---------------------------|-------------|-----------------------------------------------------------|--------------------------|------------------------|-------------------------------------------------|

| Sepúlveda et al. [21]     | IP+NoC      | AES                                                       | 3.4% / 2.6%              | MPSoC                  | 2.1% gain                                       |

| Oliveira et al. [49]      | IP+NoC      | AES                                                       | 193.7% / N/A             | Router                 | 395.9% loss                                     |

| Charles et al. [57]       | IP+NoC      | Authenticated Encryption [61]<br>(AES + Galois hash [62]) | N/A                      | N/A                    | 4% loss                                         |

| Sant'Ana et al. [58]      | IP+NoC      | AES                                                       | 177.7% / N/A             | Router                 | 2.5% loss *                                     |

| Sant Ana et al. [56]      | IF+NOC      | SIMON                                                     | 37.7% / N/A              | Router                 | 46.5% loss **                                   |

| Charles and Mishra [50]   | IP+NoC      | Hummingbird-2                                             | 2% / N/A                 | NoC                    | 30% gain <i>W.R.T</i><br>traditional encryption |

| Ancajas et al. [11]       | IP+NoC      | One-time pad                                              | 9.5%, / 5.1%             | SoC OCP Interface [63] | 3.8% loss                                       |

| Raparti and Pasricha [38] | IP+NoC (NI) | N/A                                                       | 5.5% / 2.1%              | NI                     | 48.4% gain <i>W.R.T</i><br>HT-infected NI       |

#### TABLE 2. Summary of countermeasures addressing confidentiality of NoCs.

\*For real traffic

\*\*For synthetic traffic

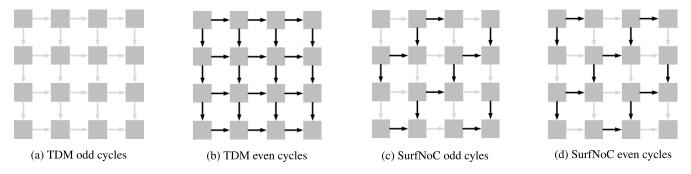

FIGURE 10. Time-division multiplexing scheduling for 16 nodes in a 2D mesh vs. the proposed SurfNoC architecture [65].

cryptanalysis attacks easier by hugely reducing the keyspace. To address timing attacks, a variety of approaches such as static (e.g. allocating links in time using time-division multiplexing and dynamic (e.g. task migration) resource allocation have been proposed. These works are reviewed in the rest of this subsection.

The idea of resource allocation to counter timing attacks started in [51] by Wang and Suh as a static scheme. The authors employ temporal network partitioning to thwart timing attacks. In this paper, a set of applications with a specific security requirement are called a domain, e.g., high-security and low-security domains. The goal of the countermeasure is to decouple the high-security domain from the low-security domain. This goal can be achieved by prioritizing low-security domains over high-security domains. The twofold countermeasure consists of a static allocation of input VCs to each domain, and a priority-based arbitration for router resources, e.g, the router crossbar. To prevent DoS attacks caused by the low-priority domain's traffic, the network enforces a static bandwidth limit on the low-security traffic. While the proposed security countermeasure offers negligible performance impact under a specific traffic pattern, imposing a static threshold will contribute to performance degradation on highly-sensitive domain traffic.

Wassel *et al.* [65] borrowed the static domain concept from the previous study in [51]. The authors have explored two approaches to achieve domain non-interference as depicted in Figure 10. Time-division multiplexing (TDM) is illustrated in Figures 10.a and 10.b where packets in each black and grey domains must wait for their turn to advance in the network. The whole network is divided into time slices that are dedicated to each application domain. In contrast, Figures 10.c and 10.d depict a scenario where domains are washed over the network as waves. In any given cycle, packets of both domains are being served in the network. Thus, the packets do not have to wait an extra cycle to move throughout the network. The so-called SurfNoC architecture notably enhances performance over TDM; however, it needs more buffering space and bigger switch allocators.

Although static allocation provides implementation simplicity, its static behavior can be guessed/outperformed by the attacker. Hence the achieved security is fragile. That motivation leads to dynamic schemes in [11], [66], [67], where they yield higher security as compared to the static-based architectures.

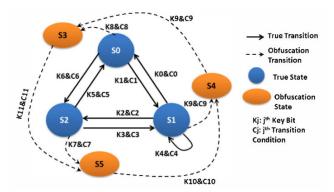

The authors in [11] used node obfuscation to tackle timing attack. Applications are migrated (task migration) to other nodes to provide more path diversity. It is worth mentioning that the new nodes should be compatible with the mapped application. The migrations are managed by the SoC firmware, where it keeps a list of PEs that match. Nevertheless, node obfuscation poses a substantial performance overhead and is subject to resource limitations on the chip. Sepúlveda *et al.* [66] applied dynamic resource allocation but in a different way. The authors proposed a router architecture to address timing attacks by dynamically allocating several virtual channels to each input stream according to the communication and security requirements. The authors used this to keep the attacker's traffic independent of the sensitive traffic. A pool of virtual channels is available in the router, along with a pseudo-random number generator that randomly allocates a virtual channel to each input. While the approach produces promising results in terms of decoupling the sensitive and malicious traffic, it shows a relatively large area overhead compared to previous works [51]. Additionally, the authors have ignored the presence of HTs in the NoC.

Sepúlveda *et al.* [67] appended their work in [66] by proposing another dynamic allocation scheme. They proposed random arbitration and adaptive routing to address timing attacks. Generally, arbitration schemes are mostly deterministic, e.g., round-robin arbitration. In this study, the random arbiter uses pseudo-random number generators and physically unclonable functions (PUF) to achieve arbitration randomness. Moreover, the West-First routing algorithm provides route randomization to tackle both the security and performance problems.

To avoid the performance penalty of resource allocation, researchers in [52], [68] [35] opted for another approach. They diversify the routes from source to destination in various ways to avoid bottlenecks that are susceptible to DoS attackers. Indrusiak et al. [52] have factored in hard real-time performance constraints in addition to security. Authors have used a combination of source and distributed routing techniques to randomize the sensitive path. In source routing, the path selection is made within the local IP or the NI, in which packet latency and performance constraints are considered. In distributed routing, the path is randomly chosen according to the relative position of the packet and a set of rules derived by the turn-model. Also, to balance the security-performance trade-off, an evolutionary algorithm for task mapping has been used with the following inputs: NoC parameters, the security level, and the routing randomization approach. In this study, random route selection leads to higher packet latency.

Boraten and Kodi [68] have suggested routing traffic through under-utilized routers for security and performance gains. The proposed approach addresses both DoS and timing attacks. Applications are assigned with a security domain before data transmission. When there is a conflict between the high-security and low-security data domains, precedence is given to the low-security domain. If backpressure in the high-security domain is detected, the domain can request a routing change. A set of four routing algorithms with different levels of routing flexibility are used. Extra virtual channels are used to allow packets to switch their routing without having a deadlock. The proposed approach obtains a good security-performance trade-off; however, utilizing extra VCs and different routing mechanisms lead to a notable area overhead.

Reinbrecht et al. [35] introduced distributed timing attack involving at least two malicious routers/IPs. The two types of infected nodes are Injectors and Observers. In this scenario, a sensitive path carrying packets sent by the main memory is monitored by the Observers. The goal is to congest the sensitive path by Injectors and observe the throughput of the Observer node and detect sensitive packets. The nodes are constantly monitoring link bandwidth, and if the bandwidth threshold is exceeded, the routers send an alert to the neighboring routers. Upon detecting an attack, the routing algorithm switches from XY to YX to avoid using the same path for sensitive information. It is worth mentioning that this routing randomization strategy will fail to provide security if the attacker knows about the alternative routing strategy. Based on the previous assumptions, it is highly possible. The same threat model and countermeasure are used in [64] to recover AES key bits.

Table 3 compares the previous work in this section based on route randomization, resource allocation, area/power overhead, and performance impact.

#### C. PRESERVING DATA INTEGRITY & AUTHENTICITY

Given that the NoC fabric can attain data integrity, a message recipient can verify whether the received message has been tampered with or not. As in many cases where data integrity can be achieved through sender authentication, researchers have jointly addressed the integrity and authenticity in some works. In general, there are three major approaches to guarantee data integrity and authenticity in NoC-based MPSoCs. i) The application of error detection/correction codes and/or unkeyed hash functions that only addresses data integrity. ii) Joint use of keyed hash functions and message authentication codes to address both data integrity and authenticity. iii) Incorporating physically unclonable functions for authentication-only purposes. In this section, we review papers addressing data integrity/authenticity after a quick review of the preliminaries of the mentioned approaches.

A cryptographic hash function is a one-way mathematical function that creates a fixed-length message digest regardless of the input message size. The output of the hash function is called a message digest. The one-way property guarantees that the input data cannot be extracted based on the message digest. When the hash of the input data is computed, it is then appended to the original message and sent to the receiver. The receiver evaluates data integrity by running the hash algorithm on the message's body and comparing the result with the received tag. Since the message space could be far greater than the hash digest space, used hash functions must be collision-resistant, meaning that no two similar messages can be found with the same hash digest.

Boraten and Kodi [69] have proposed a combination of algebraic manipulation detection (AMD) and cyclic redundancy check (CRC) codes to address the integrity of NoCs. The authors have assumed that the HTs are smart enough to tamper with a packet while keeping its CRC correct. To address this threat model, they use AMD codes for

| Reference                 | Adversary | Route Ran-<br>domization | Resource<br>Allocation | Area/Power Overhead                                             | WRT                 | Performance<br>Impact | WRT                |

|---------------------------|-----------|--------------------------|------------------------|-----------------------------------------------------------------|---------------------|-----------------------|--------------------|

| Wang and<br>Suh [51]      | IP        | No                       | Static                 | $\approx 0\%$                                                   | NoC                 | N/A                   | N/A                |

| Wassel et<br>al. [65]     | IP        | No                       | Static                 | 162% - 316% / 146% - 310%                                       | Buffer,<br>Crossbar | 75% gain              | TDMA               |

| Ancajas et<br>al. [11]    | IP+NoC    | No                       | Dynamic                | N/A                                                             | N/A                 | Software-level        | N/A                |

| Sepúlveda<br>et al. [66]  | IP        | No                       | Dynamic                | 9% / 8%                                                         | Router              | $\approx 25\%$ gain   | SurfNoC<br>[65]    |

| Sepúlveda<br>et al. [67]  | IP        | West-First               | Dynamic                | 11% / 5% for Random arbitration<br>9% / 8% for Adaptive routing | NoC                 | Up to 90% gain        | Unprotected<br>NoC |

| Indrusiak et<br>al. [52]  | IP        | XY/YX,<br>West-First     | N/A                    | N/A                                                             | N/A                 | N/A                   | N/A                |

| Boraten and<br>Kodi [68]  | IP        | XY, 01TURN<br>*, ROMM ** | N/A                    | N/A / 1.84%                                                     | NoC                 | 2 - 20% gain          | NoC                |

| Reinbrecht<br>et al. [35] | IP        | XY/YX                    | N/A                    | 21.1% / 16.2%                                                   | Router              | N/A                   | N/A                |

#### TABLE 3. Details of the previous works addressing timing attacks.

\*Orthogonal one turn routing

\*\*Randomized oblivious minimal multi-phase routing

sensitive packets and prioritize them against regular packets. The AMD code mechanism embeds the path information into the packet header. As a result, the packet integrity is preserved, and unauthorized duplicated packets can be detected/dropped at the destination router. As the sensitive packets (coded with AMD) are given a higher priority than normal packets (coded with CRC), the method is vulnerable to DoS attacks through the injection of junk sensitive traffic. The proposed approach is not immune to any HTs inserted in the NI as all mechanisms are being applied/checked at NoC routers. Overall, AMD yields significant area overhead compared to CRC. Also, the header flit is left unprotected, which could lead to the revelation of sensitive information according to [35].

Authors of [70] have tried to expand the idea of error detection/correction codes by utilizing a model checking method for NoC integrity. They have proposed a model checking approach to check computations of the router's pipeline stages. The checker's hardware is distributed over the router stages to perform model checking at the exact pipeline stage. The authors have claimed that the rules used in [71] are not enough to pinpoint HTs, so they have extended the ruleset. This model checker tries to detect more transient faults (through functional correctness checking) with the hope of activating/detecting probable HTs at the router. The proposed method assumes that HT characteristics are analogous to transient faults. HTs in this work are assumed to be capable of influencing resource allocations and corrupting data. Also, NoC buffers and status registers are protected from fault injection attacks. The hardware and the power overhead are 1.1% and 1.5%, respectively, compared to the baseline router. Since the behavior of HTs and transient faults is not the same in all cases, the proposed model checker fails in detecting some HTs, e.g., non-functional HTs trying to perform thermal attacks. Also, the model completely ignores any attacks that are not altering routers' functionality. This may include many confidentiality and integrity-related attacks.

certification to guarantee source integrity. Based on a lookup table located at the IP, a fixed tag generated by the SoC firmware is appended to the data. The data is then passed to the NoC and is routed to the destination. The SoC firmware checks this tag at the destination to ensure that a legitimate source IP issued the packet. As tags are updated only after the system boot-up, the system is not highly secure, i.e., it is susceptible to replay attacks and all analysis-based attacks. Moreover, it is not clear how the method should distribute the tags after every boot-up. The area, power, and performance overheads posed by packet certification are negligible.

Fort-NoCs [11] architecture proposes a hash-based packet

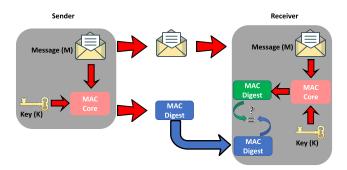

The message digest of unkeyed hash functions only depends on the input data, whereas keyed hash functions additionally utilize a secret key to generate the message digest. Keyed hash functions are mostly used where the authenticity and integrity of data are both considered, whereas unkeyed hash functions only guarantee integrity. Data authentication is a process in which the receiver ensures that the intended party sent the data. The message authentication codes (MACs) generate a digest by using a private key shared between the source and the destination. The message and the tag are sent to the receiver to verify the message's security properties. Authentication will not be compromised as long as the key is not revealed to a third party. Keyed hash function and block ciphers are used as the MAC backbone. HMAC, SipHash, and cipher blocks in CBC and GCM modes are examples of used techniques. Figure 11 illustrates the MAC process. Although, authentication is achieved even with sending plaintext messages, authenticated encryption (AE) and authenticated encryption with associated data (AEAD) have been proposed to avoid information leakage. In AE, the integrity and authenticity of the ciphertext are evaluated at the destination. On the other hand, AEAD adds the ability to check the integrity and authenticity of some associated data (AD) in the plaintext appended to the ciphertext.

**FIGURE 11.** Message authentication process in the source and destination nodes.

The associated data can be the header information which is kept in plaintext for proper routing mechanism.

An authenticated encryption approach is used in the study by Sajeesh and Kapoor [61]. IPs are dynamically divided into secure and non-secure. Non-secure IPs are prevented from communicating with secure ones. Subsequently, malicious code injection attacks such as buffer overflow are prevented. The Authenticated encryption module is implemented within the secure IPs to verify the packet's source/integrity. The authors have used Galois counter mode (GCM) with GHASH [62] for encrypted authentication. There is a nearly 20% increase in slice LUT utilization and less than 15% increase in slice register utilization in FPGA implementation. The most notable shortcoming is that the encryption key remains constant throughout the lifetime of NoC. Also, the header information is left in plaintext, which could lead to cryptanalysis attacks [72].

Sepúlveda *et al.* [21] have used SipHash, a keyed hash function for message authentication [73] to address both integrity and authentication in the network. SipHash iteratively performs a series of add, rotation, and XOR operations to achieve fast MAC computation for short messages. The proposed scheme incurs hardware overhead of as big as 2% when compared to the entire baseline MPSoC.

Moriam et al. [74] have proposed an approach to send a linear combination of data packets (also known as network coding) for forwarding data packets. The method helps to ensure integrity, boost availability, and enhance the efficiency and robustness of NoCs. Additionally, this method can address replay attacks. The assumed threat model of the paper consists of malicious routers capable of packet dropping and tampering. The paper assumes that other components of the MPSoC, including NIs and IPs, are secure since they were designed in-house. However, due to design parameters like time-to-market and cost, these components have, in fact, higher chances to be designed by 3rd parties. A block cipher called mCrypton in CBC mode has been used as a lightweight solution for authentication without addressing any key exchange mechanism. The MAC computation needs up to 39 cycles at the sender/receiver while providing more security aspects. The area overhead compared to the baseline MPSoC is 2.7%. Overall, the devised approach incurs significant performance overhead.

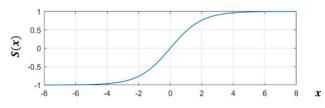

Charles and Mishra [72] devised a trust-aware routing mechanism to circumvent the malicious nodes. The assumed threat model consists of malicious IPs that can modify packets' content to fail the authentication process, which will increase network congestion. A trust value ranging from -1 (untrusted) to +1 (trusted) is defined in the paper to utilize secure paths. Each node observes the trust values of its 1-hop and 2-hop neighbors to choose a trusted path. Nodes continually update their trust values based on a sigmoid function (depicted in Figure 13) and their recent communications history. Trust values diminish either if a packet is lost or the sender does not receive the ACK packet. In contrast, successful secure communications that deliver ACK packets to the sender will help boost the trust values. The proposed approach demonstrates significant performance improvements with only 6% area overhead compared to the baseline router. It is noteworthy that this method requires an end-to-end flow control mechanism to let secure packets return their ACK packets to the senders, which incurs performance overhead.

The concept of Physically Unclonable Function (PUF) was coined by Pappu *et al.* [75]. PUFs are one-way lightweight hardware security primitive which produce a unique output called a *Response* for a given input called a *Challenge*. The unique response will act as the entity identifier and can be used for device authentication and key generation. Unlike the encryption algorithms that integrate confusion and diffusion as sources of entropy, PUFs leverage manufacturing process variation [76]. Despite all the advantages, PUFs should be utilized with care due to their reliability issues caused by temperature and voltage variations [77].

The study by [78] has embedded two delay-based PUFs, namely arbiter PUF (APUF) and ring-oscillator PUF (ROPUF), in NoC. Since the PUF structure is intertwined in the router's architecture, it is extremely difficult for an attacker to initiate PUF removal/replacement attacks. The proposed PUFs use the available pool of multiplexers of the router's crossbar switch in its architecture; however, their architecture is reorganized to a cascaded form. The router can either work in its normal mode or switch to PUF mode. Pass transistors have been used [79] to enable these features. To produce random challenges, the buffer occupancy of the input ports under the dynamic adaptive deterministic (DyAD) routing algorithm [80] is used as a source of randomness. The hardware evaluations show an 11% and 7% increase in the area overhead compared to the baseline router for the APUF and ROPUF, respectively. Moreover, the PUF impact on the router's critical path is negligible, and the performance overhead is less than 0.1%; however, no network-level simulation is provided. Despite the promising result and thorough security analysis of the design, the functionality of the design relies on an adaptive routing algorithm.

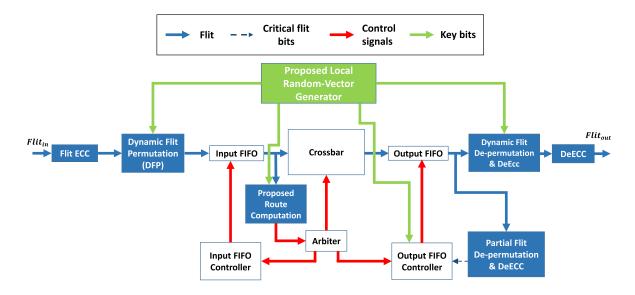

One form of packet tampering is malicious modifications of the header flit, e.g., changing the flit type. This may compromise the flit's data integrity and result in a misrouted packet, deadlock, livelock, or flit loss. Frey and Yu [33]

FIGURE 12. The proposed router architecture in [33] for HT mitigation and detection.

**FIGURE 13.**  $S(x + \delta)$  and  $S(x - \delta)$  are computed to update the trust values where S is the sigmoid function and  $\delta$  is a small positive number.

have targeted packet tampering prevention by conducting flit integrity check and permutation of flit contents inside the router. The paper's assumed threat model is malicious routers capable of modifying the flit type or changing the packet address to give access to unauthorized IPs (spoofing attack). To tackle the problem, the ingress packets' critical fields are first encoded before entering the input FIFO of a router using Error Control Code (ECC). Next, they are scrambled using dynamic flit permutation. The whole process is shown in Figure 12. A PUF structure is implemented within each router to ensure the randomness of the permutation function. Extra modules for flit de-permutation and ECC decoding must also be implemented in the router to allow flits to be forwarded to the next node. The area and power overheads are 39% and 13%, respectively, with respect to the baseline router.

Table 4 compares the previous work in this section in terms of the integrity scheme, area, power, and performance overheads.

#### D. PRESERVING AVAILABILITY

In this sub-section, we review the DoS attacks in NoC-enabled MPSoCs that can be conducted by either malicious IPs or malicious NoC. Malicious IPs mostly use packet flooding to introduce congested areas to violate the real-time constraints of the chip. Malicious NoCs, on the other hand, perform packet tampering to cause packet retransmission, packet dropping and/or packet misrouting. Most of the papers that explore DoS attacks have assumed that the 3PIP NoC is the main suspect. Both software-level and hardware-level solutions have been provided to mitigate DoS in MPSoCs; however, hardware-level approaches introduce lower performance impact.

An attack model that has been repeatedly addressed in the literature is packet misrouting carried out by HT-infected NoC routers. The following steps should be taken to tackle this attack model:

- The HT-infected NoC router must be pinpointed with a proper detection mechanism.

- The router should be isolated from the rest of the network.

- Proper routing algorithms should be utilized to bypass the isolated router.

The countermeasures are generally composed of two main stages: 1) HT or DoS detection and 2) isolating the adversary or avoiding it by routing the packets in alternative paths. The HT/DoS detection is done in a variety of ways, mostly using machine learning techniques. On the other hand, the routing part is usually done using partially dynamic routing, as will be seen in the following.

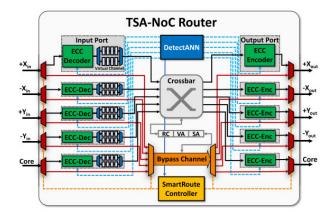

Addressing the adverse performance impact of HT isolation techniques in [65], [68] is the primary motivation of the study by Wang *et al.* [34]. The authors have proposed using an artificial neural network (ANN) for HT detection. The model is trained offline using feature sets consisting of link and buffer utilization of each input port, local operation temperature, and the last epoch's transient error rate. In the detection phase, the trained model will label the routers as

107638

| Reference               | Adversary | Integrity Scheme         | Area / Power Overhead                                 | WRT                       | Performance Impact                            |

|-------------------------|-----------|--------------------------|-------------------------------------------------------|---------------------------|-----------------------------------------------|

| Ancajas et al. [11]     | IP+NoC    | Packet Certification     | 0.3% / 0%                                             | SoC OCP<br>Interface [63] | 2% loss                                       |

| Sepúlveda et al. [21]   | IP+NoC    | SipHash                  | 1.1% / 1.2%                                           | MPSoC                     | 1.8%loss                                      |

| Frey and Yu [33]        | NoC       | Dynamic Flit Permutation | 39% / 17%                                             | NI                        | N/A                                           |

| Charles and Mishra [72] | NoC       | Trust-Aware Routing      | (6% / 28.3% Real Traffic<br>67.6% Synthetic Traffic)* | Router                    | 43.6% gain compared to<br>the HT-infected NoC |

| Sajeesh and Kapoor [61] | IP        | AES (GCM mode),<br>GHASH | 20%** / N/A                                           | NI                        | $\approx 0\%$                                 |

| Moriam et al. [74]      | NoC       | mCrypton (CBC Mode)      | 2.7% / N/A                                            | MPSoC                     | 26-39 cycles                                  |

| Boraten and Kodi [69]   | IP+NoC    | AMD, CRC                 | N/A                                                   | N/A                       | 1% loss                                       |

#### TABLE 4. Summary of the previous works addressing data integrity.

\*Energy improvement compared to the HT-infected SoC

\*FPGA resoruces

HT-infected or HT-free. This phase is followed by an HT mitigation stage in which the predicted labels are fed to a smart routing module to choose between one of the three available routing algorithms: O1TURN, West-First, and Negative-First. Packets are also labeled as high-security or low-security packets if any of the source or destination routers are HT-free and HT-infected, respectively. A bypass channel is integrated into each router to pass the high-security packets to avoid the HT-infected routers. The router's routing decisions are based on a deep reinforcement learning (DRL) controller that selects the routing algorithms with the highest expected long-term return in terms of network performance and energy efficiency. The results show higher HT detection accuracy and lower latency and energy consumption compared to the previous works with only 3% area overhead compared to the baseline router.

Madden et al. [32] proposed a remedy for DoS attacks using spiking neural networks (SNN). SNN is adopted because it is usually used in applications that require minor changes in the neurons' weights as a result of minor changes in the input training set, such as a moving object in a static environment in video applications. In fact, this is very similar to the anomaly in network traffic caused by HT to congest the network. The attack is carried out by flooding the network with unnecessary packets. The detection scheme tries to detect the anomalies in the NoC traffic patterns to pinpoint the attack. The spiking network identifies the temporal patterns within the data. It observes the total number of requestto-send signals in a certain time interval by a router to detect potential attacks. While achieving 86% HT detection accuracy in different attack scenarios, the area overhead was not reported; however, it seems to be significantly high. Moreover, this method does not support credit-based flow control NoCs, and the accuracy depends on the length of the attacks.

Another application of machine learning techniques is used to address misrouting as well. Firstly, a model has to be trained based on a dataset. Then the trained model is used to detect anomalies at runtime. The training phase of supervised learning algorithms requires significant time/energy, and due to the limited power budget and timing constraints in the NoC context, it is done offline. On the other hand, unsupervised learning algorithms do not require any training.

Authors of [81] have proposed supervised and unsupervised machine learning frameworks to detect real-time anomalies such as packet retransmission, packet misrouting, and tampering in NoC-based many-core architectures. The feature extraction is narrowed down to the packet source and destination addresses, transfer path, and transfer distance. To reduce the hardware complexity, the model is trained offline using a "Golden Dataset" (an HT-free network), and anomalies are injected randomly in the routers. Four supervised learning algorithms have been used: K-Nearest Neighbor (KNN), Support Vector Machine (SVM), Linear Regressor, and Decision Tree. Moreover, four unsupervised learning algorithms are used: Simple K-Means, Farthest First, Estimation Maximization, and Hierarchical Clustering. While being more costly, supervised learning techniques outperform unsupervised techniques in accuracy, which is above 90%. In a quad-core router, the area and the power overhead are 3% and 9%. The latency overhead of the proposed architecture is 18% of the total execution time. Also, the unsupervised learning techniques are not as effective as supervised algorithms against the detection of spoofing attacks.

To compensate for the fact that the model could lack training on unseen attacks during the initial training phase, the same authors devised an approach to update the trained model by utilizing a modified balanced window (MBW) online machine learning algorithm. In other words, it is a mistake-driven learning model for detecting unexpected attacks at runtime. The prediction model is updated if its prediction was wrong [82]. Overall, using MBW leads to a lower area overhead, lower detection latency, and higher detection accuracy.

Rather than costly ML models, Daoud and Rafla in [36] addressed the same threat model. The HT circuit is first inserted into the router's logic with less than 1% area overhead. The HT detection scheme is implemented within the router and locates the HT-infected router based on the packet input port and its destination. The malicious router's address will be propagated to the adjacent routers, and a routing algorithm borrowed from the fault-tolerant context is employed to detour the infected node with less than 1% area overhead. Since it is unknown that at what router's pipeline stage the packet was misrouted, the proposed countermeasure in [70]

can be utilized to pinpoint the HT's exact location. In the presence of more complex HTs, the detection messages from the HT-infected router to the neighboring node can also be dropped.

In [37], the same authors addressed the packet dropping attack caused by an HT-infected router in which a black-hole router drops any packet that passes through. Subsequently, the infected node will not forward the received packet and, therefore, will cause DoS. The HT model poses less than 2% power and area overhead compared to the baseline router. The number of black-hole routers and their spatial distribution over the network has a drastic impact on the attack's effective-ness. To remedy the problem, the same security-aware routing used in [36] was proposed.

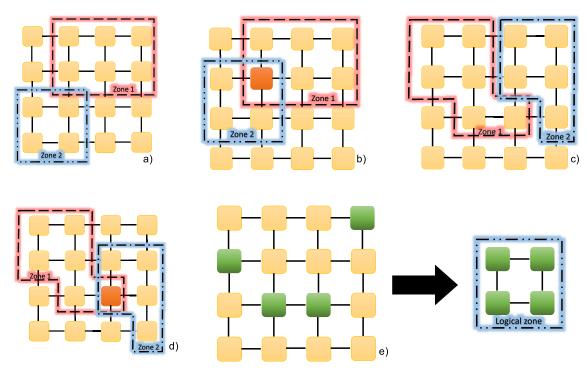

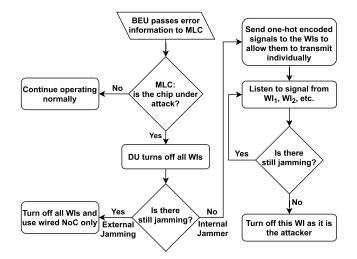

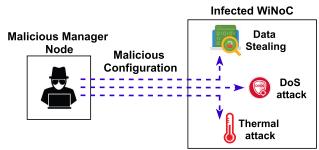

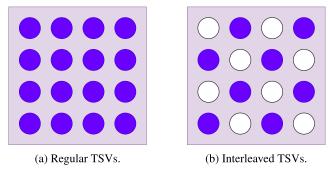

Trojan-aware routing was also adopted in [83] to address DoS attacks started by malicious routers. The assumed HT takes control of the router to misroute any packet heading to destinations located at the same column as the malicious router. The proposed routing consists of three stages: detection, shielding (isolation), and HT detouring. Each router uses a combination of the source ID, input port, and destination ID for each packet to check if the XY routing was violated. In case a router detects a routing violation, it alerts its neighbors to bypass the malicious router. The proposed method achieves acceptable latency and throughput results while having area and power overheads less than 3% compared to the baseline router. However, the application of the proposed method is limited only to the NoCs using XY routing algorithms.