Received May 28, 2021, accepted June 20, 2021, date of publication June 23, 2021, date of current version July 1, 2021.

Digital Object Identifier 10.1109/ACCESS.2021.3091777

# A Gain Levelling Technique for On-Chip Antennas Based on Split-Ring Resonators

CARMINE MUSTACCHIO<sup>®</sup>, (Member, IEEE), LUIGI BOCCIA<sup>®</sup>, (Senior Member, IEEE), EMILIO ARNIERI<sup>®</sup>, (Member, IEEE), AND GIANDOMENICO AMENDOLA<sup>®</sup>, (Senior Member, IEEE)

Dipartimento di Ingegneria, Informatica, Modellistica, Elettronica e Sistemistica, dell'Università della Calabria, 87036 Rende, Italy

Corresponding author: Emilio Arnieri (emilio.arnieri@unical.it)

This work was supported in part by the European Union Project TARANTO "TowARds Advanced bicmos NanoTechnology platforms for rf and thz applicatiOns."

**ABSTRACT** This paper introduces a gain enhancement technique for monolithically integrated antennas. Such devices can suffer from gain dips within their operating bandwidth due to standing waves arising in the die or caused by interactions with other on-chip components. In this work, it is shown how these effects can be significantly mitigated by parasitically coupling square Split Ring Resonators (SRR) to the fed antenna. The SRRs geometry and their coupling with the master antenna can be set in such a way that they create an additional resonance that cancels gain drops and improves impedance matching. The proposed configuration has been validated using a W-band monopole antenna in a standard 0.13  $\mu$ m SiGe BiCMOS process. Thanks to the proposed approach, it was possible to compensate a gain drop of about 7 dB at about 85 GHz. As a result, the experimental assessment showed a maximum measured antenna gain of 1.61 dB at 81.5 GHz and an operating bandwidth from 77 to 87 GHz.

**INDEX TERMS** Antenna on-chip (AoC), monopole antenna, SiGe BiCMOS, split ring resonator (SRR), MIM capacitors.

#### I. INTRODUCTION

In order to cope with emerging high-speed communication requirements, upcoming wireless networks are expanding to new portions of the electromagnetic spectrum. Back-hauling [1] links operating in the millimeter-wave frequencies are becoming an essential technology foundation to fulfill the multiple gigabits per second connectivity challenge posed by the 5G network infrastructures. Among the upcoming frequencies, growing attention is being received by E, W and D-bands, which provide a total of around 50 GHz of available spectrum. The reduced wavelength associated with these frequencies creates a new context of opportunities that finds fertile ground on emerging microelectronic technologies. From this perspective, it is particularly attractive the possibility to monolithically integrate a complete wireless sub-system, included the antenna, in a single chip [2]. Such an approach allows overall system miniaturization, and it permits avoiding interconnection losses, which can be very high in the millimeter-wave region.

The associate editor coordinating the review of this manuscript and approving it for publication was Davide Comite .

On the other hand, on-chip systems are unfavorable for antenna integration due to the inherent low gain. The low efficiency of monolithically integrated antennas (MIAs) is due to two main factors. First, the low resistivity of the semiconducting substrate, which for a standard CMOS process is equal to 10  $\Omega$ -cm, inherently causes losses that drastically limit the antenna gain. The second trigger of antenna gain reduction is due to the high dielectric permittivity (silicon relative permittivity constant is  $\varepsilon_r = 11.9$ ) of the silicon substrate, which enforces most of the field to be confined within the substrate and not radiated in free air. Furthermore, with a typical wafer thickness of 300  $\mu$ m not only the fundamental TM0 surface-wave mode will be excited but also the TM1 mode. The latter has a cut-off frequency of about 75 GHz. Surface waves launched into the silicon wafer strongly harm the MIA gain performance not only because of the consequent power leakage. They propagate within the substrate bouncing on the die boundary and forming standing waves which can, in turn, create distortions in the antenna pattern and gain response. These unwanted effects depend on the chip size and, as such, they can significantly affect the design of complex monolithically integrated systems. To the

authors' knowledge, most of the existing techniques rather than tackling the interactions between the MIA and the die size are focused on gain improvement. For example, off-chip focusing elements such as dielectric resonators [1] or lenses [2], [3] were proposed. However, this approach makes the

integration process more complicated, and it is usually not preferred. Other approaches exploit sophisticated technological features of advanced semiconductor processes such as the selective removal of the silicon substrate underneath the radiating element [4], [5]. Alternatively, different techniques have been proposed to overcome the MIA low-gain in conventional CMOS and BiCMOS processes and within the silicon chip back-end-of-line (BEOL) stack. For example, partially reflective surfaces [6] or artificial magnetic surfaces [7] can be realized in the BEOL inter-layers shielding the antenna from the silicon substrate and generating constructive reflections. As a result, MIA placed on such surfaces have improved gain, smoother radiation patterns while showing gain performance invariant with respect to variations of the die size [8]. The main disadvantage is that the techniques require the reflecting surface to extend over a large area which cannot be used to integrate other parts of the transceiver.

This work introduces a new solution to control MIAs' gain to compensate for deteriorations caused by the die size or by interactions with other components present on the same MMIC [10]. It will be demonstrated how parasitically coupled capacitively-loaded Split Ring Resonators (SRR) can be used to control the gain of a monolithically integrated monopole antenna. As shown, SRRs can be employed to constructively scatter the field of the monopole antenna and the surface waves to improve its radiation performance by canceling gain drops caused by die resonances or by other interactions taking place within the silicon chip.

## **II. REFERENCE MONOPOLE DESIGN**

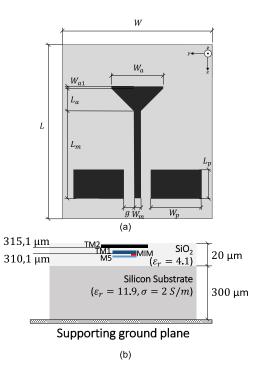

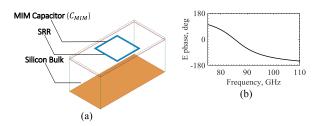

The proposed work was developed employing a standard 0.13 µm SiGe BiCMOS process, namely the SG13S technology provided by IHP Microelectronics which offers 5 thin and 2 thick metal layers referred to as TM1 (2  $\mu$ m) and TM2 (3  $\mu$ m) (FIGURE 1). To evaluate the effectiveness of the proposed approach, a conventional monopole antenna was first designed and taken as a reference. As it can be seen in FIGURE 1a, the reference antenna is implemented on TM2 and it has a length  $L_m$  and width  $W_m$ . Following the approach reported in [9], the monopole was loaded by a triangle,  $L_a$ , and its length was set to achieve a resonant frequency at around 92 GHz. The width of the triangle,  $W_a$ , was tuned to increase the bandwidth and to match the 50 ohm input impedance [11]. The antenna is designed to have ground reference whose width,  $W_p$ , and length,  $L_p$ , mainly control its gain and radiation pattern. The ground reference and the monopole itself forms a coplanar waveguide (CPW) feeding configuration, which will be connected to the 50 Ohm GSG probe pads employed during the experimental characterization. The dimensions of the different geometrical parameters of the antenna are summarized in Table 1. The actual

**FIGURE 1.** Geometry of the monolithically integrated monopole antenna (a) and simplified cross section of the IHP 0.13  $\mu$ m SiGe BiCMOS process (b).

**TABLE 1. Simulated geometrical parameters.**

| Symbol                                | Value<br>[μm] | Description                      |  |  |

|---------------------------------------|---------------|----------------------------------|--|--|

| $\overline{W_a}$                      | 450           | Loading triangle width           |  |  |

| $W_{a1}$                              | 19.95         |                                  |  |  |

| $L_a$                                 | 195           | Loading triangle length          |  |  |

| $W_{m}$                               | 60            | Monopole feeding line width      |  |  |

| L <sub>m</sub>                        | 750           | Monopole length                  |  |  |

| $L_{SRR}$                             | 250           | SRR length                       |  |  |

| c                                     | 12.85         | SRR width                        |  |  |

| g                                     | 85            | SRR distance from the antenna    |  |  |

| $\widetilde{\mathrm{W}}_{\mathrm{p}}$ | 440           | Monopole ground reference width  |  |  |

| $L_p$                                 | 250           | Monopole ground reference length |  |  |

| W                                     | 1296          | Seal ring width                  |  |  |

| L                                     | 1508          | Seal ring length                 |  |  |

| $C_{MIM}$                             | 250 fF        | MIM capacitor loading the SRRs   |  |  |

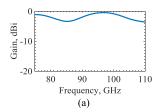

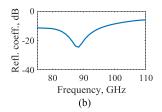

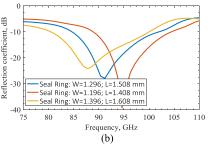

antenna geometry, as it appears in Fig. 1, was simulated in different configurations using Ansys HFSS [12], to perform full-wave simulations. The simulated reflection coefficient and gain of the isolated die are reported in FIGURE 2. For the case at hand, the antenna exhibits a minimum of the reflection coefficient at about 90 GHz, and it has wideband performance. The antenna has a maximum gain of -0.5 dBi at about 96 GHz and its -3dB bandwidth is comprised in the range between 87 and 109 GHz. Both gain and matching are deeply influenced by the dielectric size which is defined by the die seal ring, namely W and L. Standing waves within the high permittivity silicon substrate strongly affect both the reflection coefficients and the antenna gain response. As can

VOLUME 9, 2021 90751

FIGURE 2. Simulated gain (a) and reflection coefficient (b) vs. frequency of the reference monopole antenna without ground plane extension.

**FIGURE 3.** Simulated gain (a) and reflection coefficient (b) vs. frequency of the reference monopole antenna on an isolated die for different seal ring sizes.  $W_q$  is equal to 4 cm in all cases.

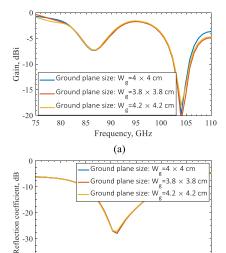

be seen in FIGURE 3, these effects are even more evident when the die is placed over a square ground plane having a size  $W_g$  equal to 4 cm. It is worth noticing that the sharp gain dips observed at 85 and 105 GHz are due to cavity modes similar to the ones arising in a rectangular dielectric resonator antenna (RDRA) having the same size of the silicon die and placed on a ground plane [13]. The spurious modes distort the monopole pattern causing gain drops of 7 or 20 dB. Moreover, the gain reduction occurs within the antenna's reflection coefficient bandwidth, thus strongly limiting its realized gain. A set of simulations was performed to evaluate how the die size and the supporting ground plane affect the behavior of the monopole antenna at hand. As it can be observed in FIGURE 3, variations of 100  $\mu$ m in the die size result in gain and reflection coefficient swings of about 3 GHz. On the other hand, lateral waves extending through the ground have a limited impact thus making its dimension not critical for the antenna performance, as shown in FIGURE 4.

## III. UNITS SPLIT RING RESONATORS (SRRs) LOADED MONOPOLE

MIA radiation pattern distortions due to die resonances harm the overall antenna performance, especially when the die size

FIGURE 4. Simulated gain (a) and reflection coefficient (b) vs. frequency of the reference monopole antenna on an extended ground plane of different sizes.

90

95

Frequency, GHz

(b)

105

110

100

cannot be modified *ad libitum* (i.e. freely). As a possible solution to avoid dips in the antenna response without changing the die size, a gain equalization methodology exploiting split-ring resonators (SRR) is proposed in this work. SRR can be parasitically coupled to the monopole antenna to generate a perturbation of the fields within the silicon. Their geometry can be controlled so that the scattered field can constructively add to the one radiated by the monopole.

The use of parasitically coupled radiators is widely exploited in conventional microstrip antennas and it has been applied to a variety of antenna geometries. For example, several studies can be found in the literature concerning microstrip technology [14]–[17]. In general, coupled radiating elements are used for gain improvement, to enlarge the operating band, or for reconfigurability purposes. Nevertheless, no examples are reported in the literature concerning monolithically integrated SRR.

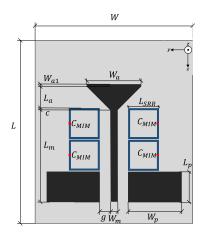

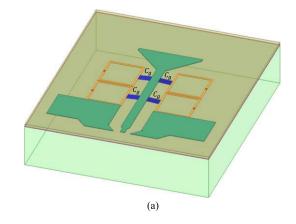

The geometry of the proposed configuration is shown in FIGURE 5. The monopole antenna is coupled to four square SRR elements placed in TM1. The resonant frequency of the SRRs depends on their size,  $L_{SRR}$ , and on the gap capacitance. To fine-tune the latter, a monolithically integrated Metal-Insulator-Metal (MIM) capacitor,  $C_{MIM}$ , was added between the SRR arms [18]. The SRRs affect the monopole performance in two ways. First, they act as a parasitic radiator, hence contributing to the overall antenna gain in relation to their resonance frequency. Second, their coupling to the monopole antenna, depending on the distance g, affects the monopole input impedance and reflection coefficient.

### A. DESIGN RATIONALE

The gain compensation design can be implemented as reported in the following.

90752 VOLUME 9, 2021

FIGURE 5. Geometry of the SRR-loaded monopole antenna.

**FIGURE 6.** Rectangular Split Ring Resonators (SRR) with capacitive load: a) simulation set-up; b) resonance frequency as seen from an incident wave.

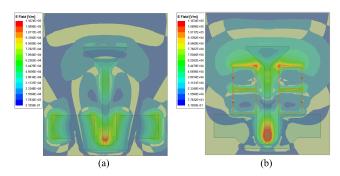

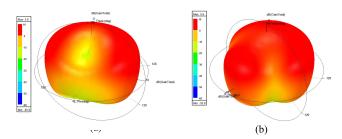

First, the SRR should be designed so that its resonance frequency is equal to one of the gain drop. For the case at hand, the SRR geometrical parameters, shown in Table 1, were set so as its resonant frequency and peak gain are both at 85 GHz. To identify the correct SRR geometry one could use different methods. In the proposed work, the characterization of the SRR was performed through full-wave simulations in Ansys HFSS [12] using an incident plane wave with Master and Slave as boundary condition, as illustrated in FIGURE 6. The null in the phase of the scattered field indicates an SRR resonance, as shown in FIGURE 6b. The SRR strongly couples with the surface waves in the die [18]. This interaction perturbs the surface wave fields within the die and it contributes to cancel the drop in the gain, which was present in the standalone monopole. As it can be observed in FIGURE 7, the electric field within the die identifies a cavity mode for the unloaded monopole. The resonant frequency of this mode is 85 GHz and it is compatible with the horizontal cavity resonance of the silicon bulk [19]. The SRRs shift the resonance frequency of this mode and generate a field that constructively adds to the one of the monopole. As a result, the dip is canceled and a small gain improvement is achieved. The gain drop compensation effect generated by the SRR loading is clearly visible in the 3D radiated field pattern shown in FIGURE 8 where it is clearly visible the cancellation of the dip in the radiation pattern when the monopole is loaded with the SRR.

FIGURE 7. Electric field amplitude distribution within the silicon die of the proposed monopole antenna without (a) and with (b) SRR loads. Results are plotted in correspondence to the gain drop, at 85 GHz.

FIGURE 8. Simulated 3D radiation patterns of the proposed monopole antenna at 85 GHz without (a) and with (b) SRR loads.

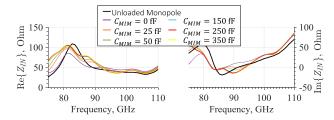

The MIM capacitance,  $C_{\text{MIM}}$ , can be used to control the SRR resonance frequency or, more effectively, as a further degree of freedom to fine tune the monopole behavior.

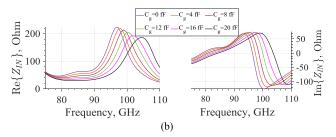

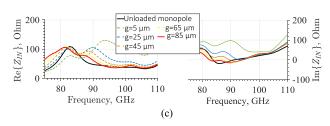

The second step in the gain levelling strategy is to exploit the capacitive coupling effect between the monopole and the SRR to control the matching bandwidth of the antenna. The loading effect of the SRR on the monopole input impedance can be controlled by varying the gap distance, g. Although the SRR coupling effect to the monopole is due to both capacitive and inductive effects, a rough estimation can be performed using only the predominant capacitive effect. The gap coupling effect can be estimated using simple analytical formulas. For instance, following the approach [19], a gap reference value of  $g = 85 \mu m$  corresponds to a coupling capacitance of approximately  $C_g = 9$  fF. A first estimation of the different gap distances can be obtained by adding a lumped model capacitor in the full-wave simulator as shown in FIGURE 7a. By performing a set of parametric analysis with different capacitance values it can be estimated the effect of changing the coupling distance, g.

An example is reported in FIGURE 7b where input impedances of the SRR-loaded and unloaded monopole are reported. The SRR-loaded simulations were performed by adding a lumped capacitance in the range from 0 to 20 fF between each SRR and the monopole. This lumped capacitance is connected in parallel to the coupling capacitance,  $C_g$ , and it emulates a variation of the gap distance, g. As it can be observed, the coupling distance has a relevant effect in determining the antenna resonances and it can be thus

VOLUME 9, 2021 90753

used as a degree of freedom to control the monopole input impedance. The four SRRs create two additional resonances, at about 85 and 103 GHz. These values depend on the SRR geometry, on the loading capacitance and on the coupling distance g. This behavior is fully confirmed by performing full-wave simulation of the entire SRR-loaded monopole antenna whose results are reported in FIGURE 7-c. As it can be observed, higher coupling upshifts the resonance frequency of the SRR as it is seen from the antenna input port. On the other hand, the influence of the MIM capacitor (reported in FIGURE 8) is less pronounced as it only contributes to fine-tuning the input impedance [18].

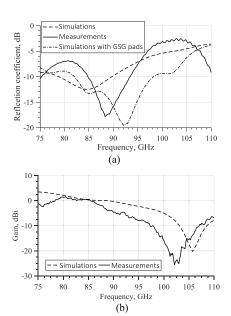

The SRR resonance and coupling can be thus employed to optimize the antenna matching and to cancel the dips due to die resonances. For the case at hand, the simulated reflection coefficient and gain are shown in FIGURE 11. As illustrated, the SRRs canceled the gain drop at 85 GHz by bringing its value from about -7 dBi (FIGURE 4) to approximately 0.6 dBi while a peak gain of 3.46 dBi is achieved at 75 GHz. Moreover, controlling the coupling between the SRRs and the monopole allows achieving a wide matching to 50 Ohm at 85 GHz.

#### **IV. RESULTS**

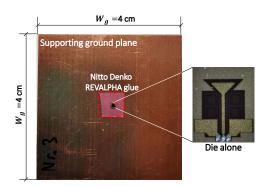

A prototype of the SRR loaded antenna was designed and fabricated. The antenna was fed using GSG pads with a pitch of  $100~\mu m$ . For this purpose, a transition from the monopole to the GSG pads was included in the layout. A microphoto of the prototype is reported in FIGURE 12. For measurement purposes, the die was bonded to the center of a  $4 \times 4$  cm ground layer using a  $150~\mu m$  thick Nitto Denko REVALPHA No. 3195V glue. The glue sheet, as well as the GSG pad, were included in a full-wave simulation to reflect the test environment more accurately.

The measured reflection coefficient and gain vs. frequency of the prototype are reported respectively in FIGURE 11a and FIGURE 11b, where they have been compared to the simulated ones in the presence of the GSG pads. The glue sheet and the GSG transition slightly upshift the antenna's operating frequency. This behavior is visible in both simulation and experimental data and it might be ascribed to the pad's capacitive loading. The measured -10 dB bandwidth of the reflection coefficient is comprised between 84.5 and 93.5 GHz. Although similar effects can also be observed in the gain response, the overall performance matches the simulated one well. In particular, the gain response is uniform within the antenna operating band, its 3-dB bandwidth is comprised between 77 GHz and 87 GHz. The gain response is uniform over the bandwidth while the peak gain is equal to 1.61 dBi at 81.5 GHz, near the resonance frequency of the SRR.

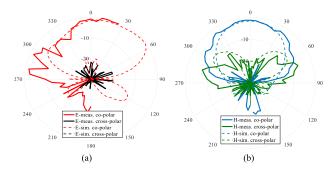

Measured and simulated radiation patterns are reported in FIGURE 13 at 81.5 GHz. E-plane pattern data could not be collected between 25 and 90 deg due to an inherent limitation of the on-wafer radiation pattern measuring system. As it can be noticed, in the H-plane there is an excellent agreement

**FIGURE 9.** Coupling effects between the SRR and the loaded monopole antenna: a) simulation set-up using a lumped coupling capacitor,  $C_g$ ; b) input impedance variations for different coupling capacitances,  $C_g$ ; c) variations of the gap distance, g, without any coupling capacitance.

FIGURE 10. Simulated SRR loaded monopole antenna input impedance variations of the MIM capacitor.

between simulated and measured results. In the E-plane the monopole tends to have a tilted pattern. This effect is visible both in the simulation and measurement. The measured data show a maximum gain in the E-plane of 2.06 dBi at around 25°. In FIGURE 13, the measured E-plane pattern shows a side lobe in the direction opposite to the GSG feeding probe. As documented in the literature [20], [21], this effect is due to the probe itself, which distorts the radiation pattern.

90754 VOLUME 9, 2021

FIGURE 11. Monopole on-chip loaded with SRRs including ground and the glue sheet effect: a) comparison between measured and simulated reflection coefficient (without de-embedding); b) comparison between measured and simulated gain in the broadside direction (i.e.  $\theta=0$  deg,  $\Phi=0$  deg) vs. frequency.

FIGURE 12. Photograph of the proposed on-chip monopole antenna attached to a 4  $\times$  4 cm ground plane.

FIGURE 13. Measured vs. simulated radiation patterns of the SRR-loaded monopole antenna: a) co-polar and cross-polar E-plane patterns at 81.5 GHz; b) co-polar and cross-polar H-plane patterns at 81.5 GHz.

A comparison table with other relevant monolithically integrated antennas is reported on TABLE 2. Although the SRR loading is conceived for gain levelling rather than for

**TABLE 2.** Comparison table.

| Ref          | Description                         | Freq<br>(GHz) | Gain<br>(dBi) | Area<br>(mm²) |

|--------------|-------------------------------------|---------------|---------------|---------------|

| [22]         | EBG Slot antenna                    | 84            | -0.58         | 1 x 1         |

| [7]          | PRS Monopole                        | 60            | 1.42          | 1.1 x 0.78    |

| [23]         | AMC Patch with 2 parasitic elements | 60            | 0.12          | 1.65 x 1.63   |

| [24]         | AMC Loop antenna                    | 60            | -4.4          | 1.8 x 1.8     |

| This<br>work | Parasitically coupled SRR Monopole  | 81.5          | 1.61          | 1.296 x 1.508 |

gain increase, the proposed antenna provides a higher gain with respect to both conventional monolithically integrated monopoles and to more complex architectures employing artificial magnetic conductors (AMC) or partial radiating surfaces (PRC). It is worth noticing that the only other on-chip antenna having a comparable gain [7], is measured on a ground plane having the same size of the one employed in the proposed work.

#### V. CONCLUSION

This work demonstrates how the gain of on-chip antennas can be controlled by using parasitically coupled SRR elements. Specifically, a monopole antenna operating in W-band was coupled to four capacitively-loaded SRRs. By tuning the resonance of the SRRs and their coupling with the fed radiator, one can increase the gain response's uniformity. Simulated and measured results have proved the effectiveness of the proposed technique, demonstrating how SRR can compensate for gain dips of about 5 dB while contributing to increasing the overall antenna gain. Similar effects can occur when the die is integrated into a more complex circuit or embedded within a larger MMIC.

#### **ACKNOWLEDGMENT**

The authors would like to thank the Karlsruhe Institute of Technology (KIT) for having provided the antenna measurements.

#### **REFERENCES**

- E. Arnieri, G. Amendola, and L. Boccia, "A cavity-backed shorted annular patch (SAP) array for mid-range V-band backhauling applications," *IEEE Access*, vol. 7, pp. 38179–38184, 2019, doi: 10.1109/ACCESS.2019.2905106.

- [2] H. M. Cheema and A. Shamim, "The last barrier: On-chip antennas," *IEEE Microw. Mag.*, vol. 14, no. 1, pp. 79–91, Jan. 2013, doi: 10.1109/MMM.2012.2226542.

- [3] A. Ali, J. Yun, H. J. Ng, D. Kissinger, F. Giannini, and E. P. Colantonio, "Sub-THz on-chip dielectric resonator antenna with wideband performance," in *Proc. 49th Eur. Microw. Conf. (EuMC)*, Oct. 2019, pp. 912–915, doi: 10.23919/EuMC.2019.8910822.

- [4] J. Grzyb, M. Andree, R. Jain, B. Heinemann, and U. R. Pfeiffer, "A lens-coupled on-chip antenna for dual-polarization SiGe HBT THz direct detector," *IEEE Antennas Wireless Propag. Lett.*, vol. 18, no. 11, pp. 2404–2408, Nov. 2019, doi: 10.1109/LAWP.2019.2927300.

- [5] M. Seyyed-Esfahlan, M. Kaynak, B. Gottel, and I. Tekin, "SiGe process integrated on-chip dipole antenna on finite-size ground plane," *IEEE Antennas Wireless Propag. Lett.*, vol. 12, pp. 1260–1263, 2013, doi: 10.1109/LAWP.2013.2282971.

VOLUME 9, 2021 90755

- [6] E. Jefors, H. Kratz, K. Grenier, R. Plana, and A. Rydberg, "Micromachined loop antennas on low resistivity silicon substrates," *IEEE Trans. Antennas Propag.*, vol. 54, no. 12, pp. 3593–3601, Dec. 2006, doi: 10.1109/TAP.2006.886532.

- [7] C. C. Liu and R. G. Rojas, "V-band integrated on-chip antenna implemented with a partially reflective surface in standard 0.13-μm BiC-MOS technology," *IEEE Trans. Antennas Propag.*, vol. 64, no. 12, pp. 5102–05109, Dec. 2016, doi: 10.1109/TAP.2016.2620606.

- [8] H.-C. Kuo, H.-L. Yue, Y.-W. Ou, C.-C. Lin, and H.-R. Chuang, "A 60-GHz CMOS sub-harmonic RF receiver with integrated onchip artificial-magnetic-conductor Yagi antenna and balun bandpass filter for very-short-range gigabit communications," *IEEE Trans. Microw. Theory Techn.*, vol. 61, no. 4, pp. 1681–1691, Apr. 2013, doi: 10.1109/TMTT.2013.2247622.

- [9] C. Mustacchio, L. Boccia, E. Arnieri, and E. G. Amendola, "Gain enhancement technique for on-chip monopole antenna," in *Proc.* 50th Eur. Microw. Conf. (EuMC), Jan. 2021, pp. 650–653, doi: 10.23919/EuMC48046.2021.9338160.

- [10] D. Sievenpiper, L. Zhang, R. F. J. Broas, N. G. Alexopolous, and E. Yablonovitch, "High-impedance electromagnetic surfaces with a forbidden frequency band," *IEEE Trans. Microw. Theory Techn.*, vol. 47, no. 11, pp. 2059–2074, Nov. 1999, doi: 10.1109/22.798001.

- [11] K.-L. Wong and Y.-F. Lin, "Stripline-fed printed triangular monopole," Electron. Lett., vol. 33, no. 17, p. 1428, 1997, doi: 10.1049/el:19970960.

- [12] HFSS: High Frequency Structure Simulator Based on the Finite Element Method, ANSYS, Canonsburg, PA, USA. [Online]. Available: http://www.ansys.com/products/electronics/ansyshfss

- [13] (Nov. 26, 2020). Dielectric Resonator Antenna Handbook—Artech Books. [Online]. Available: https://ieeexplore.ieee.org/abstract/ document/9101088

- [14] M. Barbuto, F. Bilotti, and A. Toscano, "Design of a multifunctional SRR-loaded printed monopole antenna," *Int. J. RF Microw. Comput.-Aided Eng.*, vol. 22, no. 4, pp. 552–557, Jul. 2012, doi: 10.1002/mmce.20645.

- [15] S. Dakhli, H. Rmili, J.-M. Floc'h, M. Sheikh, K. Mahdjoubi, F. Choubani, and R. W. Ziolkowski, "Capacitively loaded loop-based antennas with reconfigurable radiation patterns," *Int. J. Antennas Propag.*, vol. 2015, pp. 1–10, Jun. 2015.

- [16] M. Smari, S. Dakhli, and F. Choubani, "A frequency-reconfigurable printed antenna with switchable capacitively loaded loops," in *Proc.* 15th Int. Wireless Commun. Mobile Comput. Conf. (IWCMC), Jun. 2019, pp. 1422–1425, doi: 10.1109/IWCMC.2019.8766771.

- [17] D.-F. Guan, Y.-S. Zhang, Z.-P. Qian, Y. Li, W. Cao, and F. Yuan, "Compact microstrip patch array antenna with parasitically coupled feed," *IEEE Trans. Antennas Propag.*, vol. 64, no. 6, pp. 2531–2534, Jun. 2016, doi: 10.1109/TAP.2016.2547019.

- [18] E. Serrano, A. L. Borja, L. Boccia, J. Cascon, S. Ibrahim, D. Calzona, and G. Amendola, "SiGe BiCMOS balanced transmission line based on coplanar waveguide and split ring resonator," *Radio Sci.*, vol. 51, no. 6, pp. 868–875, Jun. 2016, doi: 10.1002/2016RS006033.

- [19] M. Kirschning, R. H. Jansen, and N. H. L. Koster, "Measurement and computer-aided modeling of microstrip discontinuities by an improved resonator method," in *IEEE MTT-S Int. Microw. Symp. Dig.*, May 1983, pp. 495–497, doi: 10.1109/MWSYM.1983.1130959.

- [20] Q. Liu, A. C. F. Reniers, U. Johannsen, M. C. van Beurden, and A. B. Smolders, "Improved probing reliability in antenna-on-chip measurements," *IEEE Antennas Wireless Propag. Lett.*, vol. 17, no. 9, pp. 1745–1749, Sep. 2018, doi: 10.1109/LAWP.2018.2865605.

- [21] M. R. Karim, X. Yang, and M. F. Shafique, "On chip antenna measure-ment: A survey of challenges and recent trends," *IEEE Access*, vol. 6, pp. 20320–20333, 2018, doi: 10.1109/ACCESS.2018.2821196.

- [22] M. S. Khan, F. A. Tahir, A. Meredov, A. Shamim, and H. M. Cheema, "A W-band EBG-backed double-rhomboid bowtie-slot on-chip antenna," *IEEE Antennas Wireless Propag. Lett.*, vol. 18, no. 5, pp. 1046–1050, May 2019, doi: 10.1109/LAWP.2019.2908891.

- [23] H. Chu, L. Qingyuan, and Y.-X. Guo, "60-GHz broadband CMOS on-chip antenna with an artificial magnetic conductor," in *IEEE MTT-S Int. Microw. Symp. Dig.*, Jul. 2016, pp. 1–2, doi: 10.1109/IMWS-AMP.2016.7588396.

- [24] X.-Y. Bao, Y.-X. Guo, and Y.-Z. Xiong, "60-GHz AMC-based circularly polarized on-chip antenna using standard 0.18-\(\mu\)m CMOS technology," *IEEE Trans. Antennas Propag.*, vol. 60, no. 5, pp. 2234–2241, May 2012, doi: 10.1109/TAP.2012.2189725.

**CARMINE MUSTACCHIO** (Member, IEEE) was born in Crotone, Italy, in 1993. He received the degree in telecommunications engineering from the University of Calabria, Rende, Italy, in 2017, where he is currently pursuing the Ph.D. degree in information and communication technologies with the Department of Informatics, Modeling, Electronic and System Engineering. His current research interests include high gain 5G backhauling antennas and gain enhancement techniques for

on-chip antennas. He is also a member of the Società Italiana di Elettromagnetismo (SIEm).

**LUIGI BOCCIA** (Senior Member, IEEE) was born in Lungro, Italy, in 1975. He received the degree in information technology engineering from the University of Calabria, Rende, Italy, in 2000, and the Ph.D. degree in electronics engineering from the University Mediterranea of Reggio Calabria, Reggio Calabria, Italy, in 2003. He has been an Assistant Professor of electromagnetics with the Faculty of Engineering, University of Calabria, since 2005. His current research interests include

low-multipath global navigation satellite system antennas, reflectarrays, beam scanning antennas, and micro and millimeter-wave IC design. He is also a member of the European Microwave Association and the Società Italiana di Elettromagnetismo. He serves as a technical reviewer for many international journals and conferences. He is currently the Co-Editor of the book entitled *Space Antenna Handbook* (Wiley, 2012).

**EMILIO ARNIERI** (Member, IEEE) was born in Cosenza, Italy, in 1977. He received the degree (Hons.) in information technology engineering from the University of Calabria, Rende, Italy, in 2003, and the Ph.D. degree in electronics engineering from the University Mediterranea of Reggio Calabria, Reggio Calabria, Italy, in 2007. He is currently an Assistant Professor with the Department of Informatics, Modeling, Electronics and System Engineering, University of Calabria,

where he has participated in several National, EU, and ESA projects. He is the Co-Founder of the academic Spin-off "Antecnica." He has coauthored more than 70 articles published in international journals and proceedings of international conferences. His current research interests include circular polarizers, the development of dual-band antennas and millimeter-wave components, synthetic aperture radar, and beam scanning antennas. He was selected as a Finalist for the Best Paper Award in Antenna Design at the 13th European Conference on Antennas and Propagation (EuCap 2019). He serves as an Associate Editor for the IEEE ANTENNAS AND WIRELESS PROPAGATION LETTERS as an Advisory Editor for the Engineering Reports (Wiley) and as a Guest Editor for Sensors (MDPI) and Electronics (MDPI).

GIANDOMENICO AMENDOLA (Senior Member, IEEE) received the degree in electrical engineering from the University of Calabria, Rende, Italy, in 1987. From 1988 to 1992, he was a Research Fellow with the Proton Synchrotron Division, European Center for Nuclear Research, Geneva, Switzerland. He is currently an Associate Professor with the Department of Informatics, Modeling, Electronics and System Engineering, University of Calabria. His current research inter-

ests include antennas, phased arrays, and microwave and millimeter-wave circuits. He is an Associate Editor of IEEE Transactions on Antennas and Propagation.

90756 VOLUME 9, 2021