Received January 11, 2021, accepted February 23, 2021, date of publication February 26, 2021, date of current version March 8, 2021. Digital Object Identifier 10.1109/ACCESS.2021.3062360

# Wideband Variable-Gain Amplifiers Based on a Pseudo-Current-Steering Gain-Tuning Technique

LINGSHAN KONG<sup>®1</sup>, YONG CHEN<sup>®2</sup>, (Senior Member, IEEE), HAOHONG YU<sup>1</sup>, CHIRN CHYE BOON<sup>®1</sup>, (Senior Member, IEEE), PUI-IN MAK<sup>®2</sup>, (Fellow, IEEE), AND RUI P. MARTINS<sup>®2,3</sup>, (Fellow, IEEE)

<sup>1</sup>Nanyang Technological University, Singapore 677669

<sup>2</sup>State-Key Laboratory of Analog and Mixed-Signal VLSI and IME/ECE-FST, University of Macau, Macau 999078, China <sup>3</sup>(On leave) the Instituto Superior Técnico, Universidade de Lisboa, 1049-001 Lisbon, Portugal

Corresponding author: Yong Chen (ychen@um.edu.mo)

This work was supported in part by the Macau Science and Technology Development Fund (FDCT)—SKL Fund under Grant SKL-AMSV(UM)-2020-2022, in part by the Guangzhou Science and Technology Innovation and Development of Special Funds (GSTIC) under Grant EF002/IME-CY/2019/GSTIC, and in part by the NRF/DELTA/NTU Research Fund under Grant DELTA-NTU CORP-SLE-RP3.

**ABSTRACT** This paper reports two variable-gain amplifiers (VGAs) featuring a new pseudo-currentsteering gain-tuning technique. In the first VGA (VGA-I), a single-voltage-controlled dual-branch current mirror is developed as a standalone gain control block. In the second VGA (VGA-II), two NMOS transistors, which are biased by a tunable voltage, are integrated into a conventional common-source amplifier to steer away from a part of the total current. Meanwhile, the theoretical analysis is developed to reveal the mechanism of different gain tuning. Fabricated in a 40-nm CMOS process, VGA-I (VGA-II) occupies a tiny area of 0.03 mm<sup>2</sup> (0.024 mm<sup>2</sup>) and consumes 22 mW (20 mW). Measured over a gain range of > 64 dB, the -3-dB bandwidth of VGA-I (VGA-II) is 9 GHz (6.6 GHz). For the time-domain tests, VGA-I (VGA-II) exhibits a jitter of 40 ps (30 ps), under a 2<sup>7</sup>-1 PRBS input at 12 Gb/s. Their power efficiencies (1.83 and 1.67 pJ/bit) compare favorably with state-of-the-art.

**INDEX TERMS** CMOS, high-speed transceiver, variable-gain amplifier (VGA), negative capacitance (NC), peak-to-peak jitter, data-dependent jitter (DDJ), pseudo-current steering, wide-tuning gain control, dual-branch current mirror, active inductor.

#### I. INTRODUCTION

Dynamic range is an important aspect of both wireless and wireline communication systems. It determines the capability of a transceiver to process and handle the signal, or the tolerance on the variation of input power. A wide dynamic range is always desirable since it makes the system insusceptible to interference and versatile for multi-standard applications [1], [2]. Therefore, great efforts have been made to maximize the dynamic range of a certain system. Although gain tuning technique has been implemented with various building blocks, such as low noise amplifier (LNA) [3], power amplifier (PA) [4], trans-impedance amplifier (TIA) [5], [6], etc., incorporating variable gain amplifier (VGA) is still the most efficient way to boost the dynamic range. Based on the control methods, two categories of VGAs are well

The associate editor coordinating the review of this manuscript and approving it for publication was Dušan Grujić<sup>10</sup>.

adopted in the communication systems, namely, digitallycontrolled VGA and analog-controlled VGA. The former usually employs an array of switchable resistors [7], [8]. Consequently, the gain changes in a discrete manner, leading to phase discontinuity which may cause problems in the system [9]–[11]. Meanwhile, if a large tuning range and fine gain steps are required, the large number of the control bits will exacerbate the complexity and power consumption of the circuit design. Therefore, continuously-tuned VGA controlled by the analog signal is more preferred.

Due to the rapid increase of data rate, wideband VGA is widely employed in both high-frequency and high-speed communications, such as in the baseband of 60-GHz wireless transceivers [12], and tens-of-Gb/s backplane receivers [13], [14]. To reach a bandwidth (BW) of several gigahertz, many efforts have been made during the last decade. Cherry-Hooper amplifier [15]–[17] is made use to extend the BW of VGA up to 2.2 GHz [18], while the

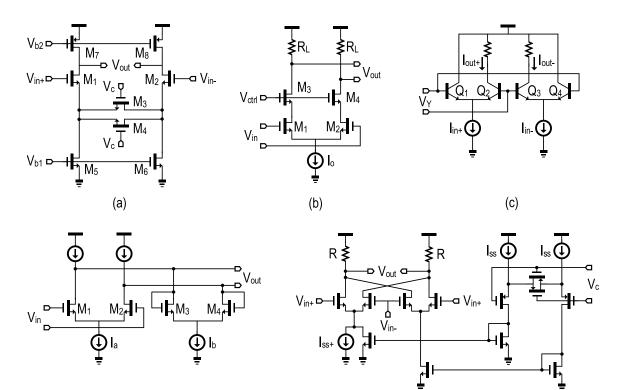

(d)

FIGURE 1. Overview of the state-of-the-art gain tuning methods.

grounded or floating active inductors [19]–[27] are used to further extend the BW to 4 GHz [19]. These prior works obtain a wide tuning range as well as low power consumption, but little design room is left for improvements on the BW. To alleviate the stringent requirement on both the gain range and BW, the overall architecture with a postamplifier (PA) following the variable gain stage is extensively used [28]–[30]. In such a way, the cascading stages can provide an adequate small-signal gain while maintaining broadband feature, whereas the preceding stage only needs to take care of the gain tuning.

This paper reports a pseudo-current-steering gain-tuning method. By incorporating it into two different VGA topologies, both achieve a wide tuning range with a single variable-gain stage [31]. Their BW can be extended beyond 7 GHz, thanks to adopting the PA-embedded scheme. Section II overviews the state-of-art gain tuning methods from two different perspectives. Next, Section III elaborates the proposed gain tuning method and implementations with two variable-gain stages. The complete structures of VGAs are sketched out in Section IV. The measurement results are summarized in Section V, followed by a brief summary in Section VI as the conclusion.

## II. REVIEW OF STATE-OF-THE-ART GAIN TUNING METHODS

Based on the control mechanism, the tuning methods can be categorized into voltage-mode and current-mode. The achievable gain tuning range depends strongly on the specific tuning methods and structure of the core amplifier. Next, we will review the state-of-the-art gain control methods and their implementation approaches.

(e)

To make use of single-ended voltage control, the signal can be applied to the source degenerative amplifier [32], [33] and cascode amplifier [34], so that their effective trans- conductance is adjustable, as shown in Fig. 1(a). By controlling the gate voltage of the source degenerative transistor, its resistance is increased with decreased biasing, and inversely for the overall gain. However, the transistor will not be turned on until the control voltage is above the sum of its threshold voltage and the drain-to-source voltage across the current tail transistor. Therefore, the useful gain control region, as well as gain variation range, are both limited. As for the cascode structure, as shown in Fig. 1(b), the source voltage of the cascode transistor follows its gate voltage, resulting in a change in the drain-to-source voltage of the input transistors. If the input transistor operates in the triode region, its transconductance varies. Therefore, the gate voltage of the cascode transistor must be high enough to keep the input transistor operating in the triode region. Such limitation prohibits this structure from low power applications. To attain a wide gain variation range with low supply voltage, the single-ended control voltage is applied to both of the feedback resistors and load resistors of the Cherry-Hooper amplifier in [15]–[18]. The two dominant factors of the voltage gain, namely transconductance and load resistance, tune the amplifier simultaneously. Meanwhile, the voltage-control signal can also be applied differentially, as shown in Fig. 1(c).

With the signal-summing VGA [35]–[38], the input signal is applied to the lower transistor pair while the upper-level transistors control the amount of current flowing to the output. Similar to the cascode structure, the range of control voltage also needs to be designed carefully, in order to guarantee a normal operation of the input transistors.

On the contrary, the current-control signal is usually applied differentially, such that the change in the current difference determines the gain of the amplifier. Although it is demonstrated in [39] that single-ended current-control is feasible for tuning the current tail of cascaded amplifiers, the common-mode voltage will be altered in such design, and to avoid problems caused by large variations, the tuning range must be restrained. To implement a differential current-control signal, one popular way is to use the architecture shown in Fig. 1(d), whose load and input transistor share a total current. This structure is efficient in a way that changes the gm and output resistance simultaneously, but the bandwidth keeps changing when the gain is tuned. Another popular choice is the Gilbert cell implementation [28]–[31]. As shown in Fig. 1(e), the lower transistor pair mirrors a differential current-control from the right-hand side circuit. With the input signal applied to the upper transistor pairs, the resultant output is the difference between the two branches of the amplifier.

The desirable feature of gain-tuning characteristics affects the evolution of the VGA's topologies. Generally, the stateof-the-art VGAs can be categorized into two groups: one of which requires a standalone gain-control block, either to convert the linear control voltage to an exponential output [28]–[30] or to enlarge the gain-control range [31], [40], while the other topology possesses the gain-control feature with the amplifier itself [41], [42]. The advantage of standalone topology is that the separate gain-control block is isolated from the signal path. Consequently, the performance of the amplifier, including frequency response, linearity, and power consumption, can be optimized independently. Furthermore, according to different requirements for each application, different exponential generators with desired accuracies and tuning ranges can be chosen, which provides the designers with another degree of freedom. The integrated VGAs, on the other hand, usually have a simpler structure, thereby reducing the size and complexity of the designs. Yet, the architecture is more confined with its corresponding gaintuning algorithms, exacerbating the trade-off between BW, linearity, and power consumption.

# **III. PROPOSED GAIN-TUNING METHOD**

#### A. CONCEPTUAL PRINCIPLE

Although the VGA designed in [22] has achieved extremely low complexity, it controls the gain of the amplifier in two steps. First, the negative exponential generator generates a differential control signal in the voltage domain. Then, a pseudo-folded Gilbert cell converts it into the current domain, controlling the two branches of the amplifier.

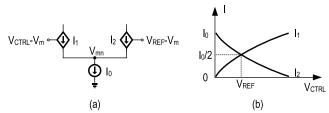

**FIGURE 2.** (a) Illustration of the proposed pseudo-current-steering gain-tuning technique. (b) Current flow versus gain-control signal (V<sub>CTRL</sub>) corresponding to (a) when  $\alpha_1 = \alpha_2$ .

To further simplify the structure, the two-step conversion can be saved if the gain-control signal can be converted to a differential output in the current domain directly. The illustration is shown in Fig. 2(a), in which two voltage-dependent current sources share a constant total current of I<sub>0</sub>, and the junction voltage (V<sub>m</sub>) is flexible. Assuming one of the current sources is related to a variable voltage, V<sub>CTRL</sub>, while the other is related to a fixed voltage, V<sub>REF</sub>, and both of them have a negative voltage-to-current relationship regarding V<sub>m</sub>. As a result,

$$I_1 = \alpha_1 \left( V_{CTRL} - V_m \right) \tag{1}$$

$$I_2 = \alpha_2 \left( V_{REF} - V_m \right) \tag{2}$$

where  $\alpha_1$  and  $\alpha_2$  are the voltage-to-current conversion coefficients of the two voltage-dependent current sources, respectively. Since the sum of I<sub>1</sub> and I<sub>2</sub> is immutable, V<sub>m</sub> must change accordingly such that,

$$\alpha_1 \left( V_{CTRL} - V_m \right) + \alpha_2 \left( V_{REF} - V_m \right) = I_0 \tag{3}$$

The above condition in (3) should always be satisfied, from which the mechanism of current flows in the two branches can be deduced as depicted in Fig. 2(b). As the gain-control voltage increases, I<sub>1</sub> increases from 0 to I<sub>0</sub>, while I<sub>2</sub> decreases to maintain a constant total current. If we set  $\alpha_1 = \alpha_2$ , each of the branch shares the same current, which equals to I<sub>0</sub>/2, when V<sub>CTRL</sub> is equal to V<sub>REF</sub>. As a result, two continuously varying currents can be obtained from one single-ended control voltage, which could be used to adjust the transconductance (g<sub>m</sub>) of the transistors and thus the gain of the amplifier. To implement this control method into VGA design, both standalone and integrated gain-control topologies are developed later.

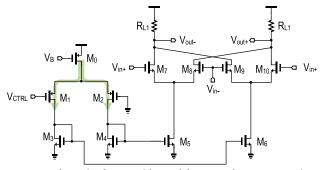

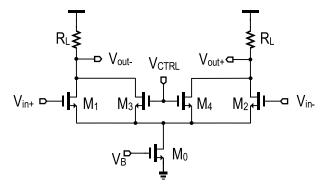

# B. IMPLEMENTATION WITH STANDALONE GAIN-TUNING TOPOLOGY

Fig. 3 shows a single stage of our proposed VGA with a standalone gain-control block. The single-ended gain control voltage,  $V_{CTRL}$ , is converted to a pseudo-differential current output, thereafter mirrored to the current tail of the gain amplifier on the right-hand side. To guarantee the amplifier's gain increases monotonically across the entire gain-control range, one of the PMOS transistors, M<sub>1</sub>, is connected to  $V_{CTRL}$ , while the other one, M<sub>2</sub>, is tight to the ground, such that the maximum current flowing through M<sub>1</sub> is half of the total current, which happens at  $V_{CTRL} = 0$ . Under this condition, the drain-to-source voltage of M<sub>1</sub> and M<sub>2</sub> are sustainably large, and the transistors work in the triode region, i.e. zone I

in Fig. 4. Since M<sub>3</sub> works in the saturation region, we have

$$I_{1} = I_{3} = K_{1} \left[ (V_{S} - V_{C} - V_{th1}) V_{SD} - \frac{1}{2} V_{SD}^{2} \right]$$

$$= \frac{1}{2} K_{3} (V_{G3} - V_{th3})^{2}$$

(4)

where  $V_S$  is the source voltage of  $M_1$  and  $V_{SD}$  is the sourceto-drain voltage of  $M_1$ . Then

$$V_{G3} = \sqrt{\frac{2K_1 \left[ (V_S - V_{CTRL} - V_{th1}) V_{SD} - \frac{1}{2} V_{SD}^2 \right]}{K_3}} + V_{th3}$$

(5)

When  $V_{CTRL}$  is increased, the overdrive voltage of  $M_1$  becomes smaller than that of  $M_2$ , resulting in a larger current flowing through  $M_2$  while less current through  $M_1$ . As the current through  $M_1$  and  $M_3$  are reduced, the node voltage at the drain of  $M_3$  is decreased, pushing  $M_1$  to operate in the subthreshold region. With  $M_3$  remained in the saturation region, the current-to-voltage relationship is written as

$$I_{1} = I_{3} = I_{D0} exp\left(\frac{V_{S} - V_{C} - V_{th1}}{nV_{T}}\right) \left(1 - exp\left(\frac{-V_{SD}}{V_{T}}\right)\right)$$

$$= \frac{1}{2}K_{3} \left(V_{G3} - V_{th3}\right)^{2}$$

(6)

where  $I_{D0}$  is the reverse saturation current and can be obtained from simulation; n is the subthreshold slope factor and can be expressed as  $n = 1 + \frac{C_d}{C_{ox}}$ , where  $C_{ox}$  is the gate oxide capacitance per unit area and  $C_d$  is barrier capacitance;  $V_T$ is the thermal voltage. Thus, it gives as

$$V_{G3} = \sqrt{\frac{2I_{D0}\frac{W}{L}}{K_3}} \exp\left(\frac{V_S - V_C - V_{th1}}{nV_T}\right) \left(1 - \exp\left(\frac{-V_{SD}}{V_T}\right)\right) + V_{th3}}$$

(7)

At the same time, the node voltage between  $M_2$  and  $M_4$  keeps increasing to provide a larger current, making the transistor  $M_2$  work in a deep triode region. Consistently in both zone I and II, we have

$$I_{4} = I_{2} = \frac{1}{2} K_{4} (V_{G4} - V_{th4})^{2}$$

=  $K_{2} \left[ (V_{S} - V_{th2}) V_{SD} - \frac{1}{2} V_{SD}^{2} \right]$  (8)

where  $V_S$  is the source voltage of  $M_2$  and  $V_{SD}$  is the sourceto-drain voltage of  $M_2$ . Therefore,

$$V_{G4} = \sqrt{\frac{2K_2 \left[ (V_S - V_{th2}) V_{SD} - \frac{1}{2} V_{SD}^2 \right]}{K_4}} + V_{th4} \qquad (9)$$

While  $V_{CTRL}$  keeps increasing,  $M_1$  enters into the subthreshold region with a much smaller  $I_1$  and  $M_2$  maintains in the triode region to flow through most of the current. The difference in current keeps increasing until  $M_1$  is fully turned off and the entire current goes through  $M_2$ , at which point the amplifier provides the maximum gain.

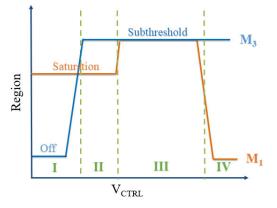

FIGURE 3. Schematic of VGA-I with standalone pseudo-current-steering gain control.

FIGURE 4. Analysis of the operation region of M<sub>1</sub> and M<sub>3</sub> in VGA-I.

Note that, when  $V_{CTRL} = 0$ , the amplifier's gain will be zero if the effects of the transistors' non-idealities are not considered. In a practical design, the layout routing from M<sub>4</sub> to M<sub>5</sub> is considerably shorter than the one from M<sub>3</sub> to M<sub>6</sub>, leading to a relatively larger voltage drop of the latter one and thus a minimum gain close but not equal to zero. Simulation result reveals that one such stage can provide a wide-tuning gain range from -40 to 2 dB, with a BW of 20 GHz.

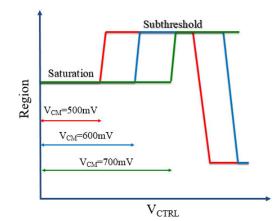

#### C. DESIGN WITH INTEGRATED GAIN-TUNING TOPOLOGY

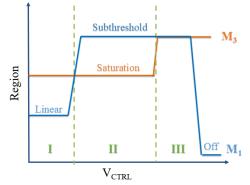

Interestingly, our proposed pseudo-current-steering gaincontrol method can be integrated with a conventional amplifier as well. As illustrated in Fig. 5, an auxiliary NMOS transistor pair, M<sub>3</sub> and M<sub>4</sub>, is placed parallel with the input differential pair, M<sub>1</sub> and M<sub>2</sub>, while its gate is connected to V<sub>CTRL</sub> instead of the input signal. Intuitively, the extra pair manipulates the effective gm by steering away a partial of the total current, thereby controlling the gain of amplifier. When the control voltage is much lower than the common-mode voltage, the control pair, M<sub>3</sub> and M<sub>4</sub>, are turned off and the gain of the amplifier is fixed at its maximum level. As V<sub>CTRL</sub> is gradually increased near to common-mode voltage, M3 and M<sub>4</sub> start to turn on and work in the subthreshold region. Since the input pair works in the saturation region, only a small amount of current is steered away by the control pair. While V<sub>CTRL</sub> is increased further beyond the common-mode voltage, the control pair steers away a considerable amount of current and still works in the subthreshold region due to its large transistor size. Meanwhile, the input transistor pair operate from the saturation region to the subthreshold region

FIGURE 5. Schematic of VGA-II with integrated pseudo-current steering gain control.

FIGURE 6. Analysis of operation region of M<sub>1</sub> and M<sub>3</sub> in VGA-II.

and even to the cut-off region. Thus, the transconductance of the input transistors shrinks continually, providing a lower and lower gain. The working region of the two pairs is shown in Fig. 6.

When both transistors are working in the subthreshold region, the current through the input and control transistor is given by

$$I_{1} = I_{D0} \frac{W}{L} exp\left(\frac{V_{G} - V_{S} - V_{th1}}{nV_{T}}\right)$$

$$\left(1 - \exp\left(\frac{-V_{DS}}{V_{T}}\right)\right)$$

(10)

and

$$I_{3} = I_{D0} \frac{W}{L} exp\left(\frac{V_{C} - V_{S} - V_{th3}}{nV_{T}}\right)$$

$$\left(1 - \exp\left(\frac{-V_{DS}}{V_{T}}\right)\right)$$

(11)

respectively. Since

$$\frac{I_0}{2} = I_1 + I_3 \tag{12}$$

we obtain

$$V_{S} = nV_{T} \left[ ln \left( e^{\frac{V_{G} - V_{th1}}{nV_{T}}} + \frac{(w/L)_{3}}{(w/L)_{1}} e^{\frac{V_{C} - V_{th3}}{nV_{T}}} \right) - ln \left( \frac{I_{0}}{2I_{D0}} \left( \frac{L}{W} \right)_{1} \right) \right]$$

(13)

FIGURE 7. The effect of common-mode voltages on the transition point of the operating regions.

Since the effective transconductance of the amplifier  $(G_m)$  depends only on the  $g_m$  of the input transistor pair, it can be derived as

$$G_m = \frac{I_{D0} \frac{W}{L} \exp\left(\frac{V_G - V_S - V_{th1}}{nV_T}\right)}{nV_T}$$

(14)

Additionally, as the operating region of the input differential pair is determined by the difference between the common-mode voltage and control voltage, one can expand or shrink the gain control range by adjusting the commonmode voltage. Fig. 7 illustrates this idea by comparing different common-mode voltages from 500 to 700 mV. The higher the common-mode voltage is set, the later the transition from saturation to subthreshold occurs. To obtain the maximum gain tuning range with a wide gain control range, the common-mode mode of 600 mV is chosen, so that the control transistor is turned off when the control voltage is increased near to the supply voltage, i.e. 800 mV in this design.

Different from the traditional current-steering VGAs, as shown in Fig. 1(c), our proposed design adjusts the transconductance of the input transistors directly, instead of manipulating with the cascode device. In such a way, the number of devices stacked in each branch is reduced, making it suitable for low power applications. Moreover, the current goes through the load resistor does not vary under the different gain setting. Therefore, the common-mode voltage of the output node is constant, and any stage following the VGA can be directly coupled.

Compared to the topology in Fig. 3, this integrated design employs fewer transistors, but the parasitic capacitance accumulated at the output node may bring concerns for high-speed applications. Consequently, a BW of 17 GHz is obtained along with a gain ranging from -30 to 4 dB.

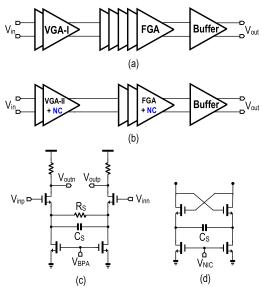

# **IV. COMPLETE ARCHITECTURE**

Plotted in Fig. 8(a) and (b), two completed architectures are implemented with the abovementioned VGA-I/-II, respectively. Both of them comprise two variable gain stages, multiple fixed stages, a DC offset cancellation (DCOC) network, and an output buffer for testing. The broadband technique of

# **IEEE**Access

FIGURE 8. (a) Complete design-I for VGA-I with standalone gain control. (b) Complete design-II for VGA-II with integrated gain control. Detailed schematic of (c) fixed gain amplifier and (d) negative capacitance (NC) circuit.

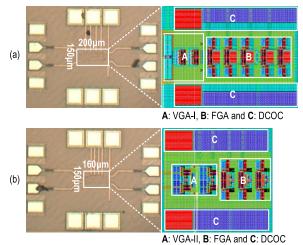

FIGURE 9. Chip photos and their detailed layouts of (a) design-I and (b) design-II.

resistive and capacitive degeneration is adopted in the fixed gain amplifier (FGA), to reduce the effect on bandwidth from cascading multiple stages.

To accommodate different features of the two variable gain stages introduced in the last section, care must be taken when incorporating them into the complete architectures (Fig. 3 and Fig. 5). In design-I, since the pseudo-Gilbert cell in Fig. 3 works in such a way that the gain provided by one input pair is minus from that of another, the resultant maximum gain is lower compared to the integrated design. Thus, five stages of the fixed gain amplifiers [Fig. 8(c)] are required to elevate its maximum gain up to 25 dB, each of which provides a gain of 4 dB with a power consumption of 3.5 mW. On the other hand, to improve the internal BW of design-II, the negative capacitance circuit [43]–[49] [Fig. 8(d)] is inserted between adjacent stages to partially cancel the larger node-to-ground capacitance. With a similar

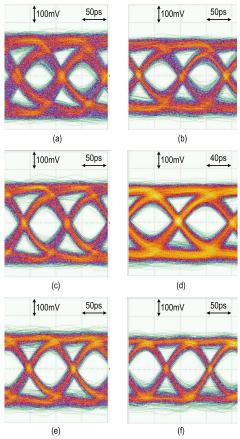

**FIGURE 10.** Measured eye diagrams at 12Gb/s with different input V<sub>in</sub>: (a) design-I, V<sub>in</sub> =75mV, (b) design-II, V<sub>in</sub> =75mV, (c) design-I, V<sub>in</sub> =250mV, (d) design-II, V<sub>in</sub> =250mV, (e) design-I, V<sub>in</sub> =1V, (f) design-II, V<sub>in</sub> =1V when the input pattern is 2<sup>7</sup>-1 PRBS.

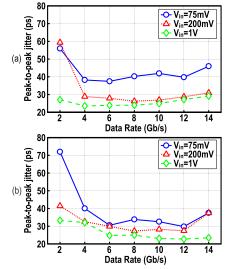

FIGURE 11. Measured peak-to-peak jitter versus data rate: (a) design-I and (b) design-II under different input swing (V<sub>in</sub>), when the input pattern is a 2<sup>7</sup>-1 PRBS.

power budget, three stages of the fixed gain amplifiers are cascaded, such that an overall gain of 23 dB is achieved. The DCOC employs a low pass filter followed by a transconductor cell, while the output buffer adopts the  $f_T$  doubler structure [30].

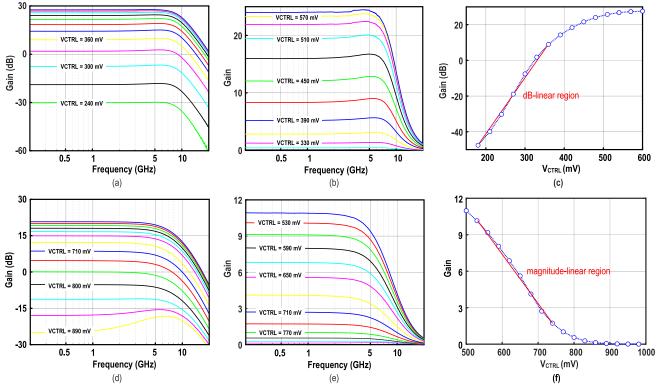

FIGURE 12. Mearsurement results: (a) frequency response of design-I in dB scale, (b) frequency response of design-I in linear scale, (c) gain characteristic of design-I in dB scale, (d) frequency response of design-II in dB sacle, (e) frequency response of design-II in linear scale, and (f) gain characteristic of design-II in linear scale.

| Parameters                     | JSSC'12 [28]       | JSSC'16 [29]       | TCAS-I'18 [30]    | TCAS-I'12 [18]    | MWCL'15 [39]          | ISSCC'04 [40]      | This work         |                   |

|--------------------------------|--------------------|--------------------|-------------------|-------------------|-----------------------|--------------------|-------------------|-------------------|

|                                |                    |                    |                   |                   |                       |                    | VGA-I             | VGA-II            |

| Technology                     | 130nm<br>BiCMOS    | 130nm<br>CMOS      | 65nm CMOS         | 90nm CMOS         | 65nm CMOS             | 180nm CMOS         | 40nm CMOS         |                   |

| Data rate (Gb/s)               | 5                  | 10                 | 10                | N/A               | N/A                   | 3.125              | 12                |                   |

| Jitter (ps)                    | < 40               | < 44               | < 36              | N/A               | N/A                   | < 95               | 40                | 30                |

| PRBS                           | 2 <sup>15</sup> -1 | 2 <sup>31</sup> -1 | 2 <sup>7</sup> -1 | N/A               | N/A                   | 2 <sup>31</sup> -1 | 2 <sup>7</sup> -1 |                   |

| BW (GHz)                       | 0.0002 to 7.5      | 0.0001 to 5.0      | 0.0001 to 7.0     | 0.0002 to 2.2     | 0.0002 to 4           | 0.0004 to 2        | 0.0001 to<br>9    | 0.0001 to<br>6.6  |

| dB-linear                      | Yes                | Yes                | Yes               | No                | No                    | No                 | No                |                   |

| Gain range (dB)                | 40<br>(-10 to 30)  | 40<br>(-15 to 25)  | 57<br>(-26 to 31) | 60<br>(-10 to 50) | 60<br>(-39.4 to 20.2) | 50<br>(-16 to 34)  | 74<br>(-47 to 27) | 64<br>(-44 to 20) |

| Power (mW)                     | 72                 | 50                 | 28                | 2.5               | 26                    | 40                 | 22                | 20                |

| Power eff. (pJ/bit)            | 14.4               | 5.0                | 2.8               | N/A               | N/A                   | 12.8               | 1.83              | 1.67              |

| Active area (mm <sup>2</sup> ) | 1                  | 0.4                | 0.045             | 0.01              | 0.06                  | 0.7                | 0.03              | 0.024             |

# **V. MEASUREMENT RESULTS**

Fig. 9 shows the chip photos of the proposed prototypes, both of which were fabricated in standard 40-nm CMOS technology, with an active area of 0.03 and 0.024 mm<sup>2</sup>, respectively. Their time-domain performance is verified by the pseudorandom binary sequence (PRBS) with a length of  $2^7$ -1, and

the eye diagram is captured by the real-time oscilloscope, as shown in Fig. 10. With different levels of input swing under the weak, moderate, and strong conditions, the measured peak-to-peak jitter is plotted in Fig. 11, covering a data rate from 2 to 14 Gb/s. Under the lower data rate of 2 Gb/s, the jitter is prominent due to the DC wander resulting from the

DCOC network. At the higher data rate beyond 12 Gb/s, high-frequency peaking and its corresponding phase distortion incur data-dependent jitter and inter-symbol interference (ISI), so the time-domain waveform is worsened. In both cases, it is observed that higher input levels can lead to a better jitter performance. Moreover, frequency responses are measured by the network analyzer and are plotted in Fig. 12, both in conventional dB scale and linear magnitude scale. Although incorporating the negative capacitive circuit, design-II rolls off earlier  $\sim$ 7 GHz, while design-I has a higher BW up to 9 GHz. This may owe to an insufficient compensation of negative capacitance or an underestimation of the parasitic capacitance from the simulation results. By plotting their gain characteristic over the gain-control voltage (V<sub>CTRL</sub>) in both dB and linear scales, it is interesting to observe that both designs preserve a linear-in-magnitude feature in the high-gain mode whereas a linear-in-dB feature in the lowgain mode.

Table 1 shows the performance summary and comparison with recent state-of-the-art VGAs targeting for similar applications. Both designs show a wider gain range, higher power efficiency as well as a smaller core area.

## **VI. CONCLUSION**

This paper presented a pseudo-current-steering gain-tuning method. Two design examples (Design-I and Design-II) were prototyped in a 40-nm CMOS. Measurement results show that this work obtains a wide gain range (>64 dB) and broad BW (> 6.6 GHz), while occupying a small active area (<0.024 mm<sup>2</sup>) and achieving a high power efficiency (<1.83 pJ/bit) up to 12 Gb/s.

#### REFERENCES

- [1] S. D'Amico, A. Baschirotto, M. De Matteis, N. Ghittori, A. Vigna, and P. Malcovati, "A CMOS 5 nV/√Hz 74-dB-gain-range 82-dB-DR multistandard baseband chain for Bluetooth, UMTS, and WLAN," *IEEE J. Solid-State Circuits*, vol. 43, no. 7, pp. 1534–1541, Jul. 2008.

- [2] J. C. Fan, C. L. Liu, and L. G. Kazovsky, "Dynamic-range requirements for microcellular personal-communication systems using analog fiber-optic links," *IEEE Trans. Microw. Theory Techn.*, vol. 45, no. 8, pp. 1320–1331, Aug. 1997.

- [3] R. Kulkarni, J. Kim, H.-J. Jeon, J. Xiao, and J. Silva-Martinez, "UHF receiver front-end: Implementation and analog baseband design considerations," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 20, no. 2, pp. 197–210, Feb. 2012.

- [4] H.-Y. Shih and C.-W. Wang, "A highly-integrated 3–8 GHz ultra-wideband RF transmitter with digital-assisted carrier leakage calibration and automatic transmit power control," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 20, no. 8, pp. 1357–1367, Aug. 2012.

- [5] W.-Z. Chen, Y.-L. Cheng, and D.-S. Lin, "A 1.8-V 10-Gb/s fully integrated CMOS optical receiver analog front-end," *IEEE J. Solid-State Circuits*, vol. 40, no. 6, pp. 1388–1396, Jun. 2005.

- [6] T. Halvorsrod, O. Birkenes, and C. Eichrodt, "A low-power method adding continuous variable gain to amplifiers," in *Proc. IEEE Int. Symp. Circuits Syst.*, May 2005, pp. 1593–1596.

- [7] M. A. I. Mostafa, S. H. K. Embabi, and M. Elmala, "A 60-dB 246-MHz CMOS variable gain amplifier for subsampling GSM receivers," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 11, no. 5, pp. 835–838, Oct. 2003.

- [8] P.-I. Mak, U. Seng-Pan, and R. P. Martins, "On the design of a programmable-gain amplifier with built-in compact DC-offset cancellers for very low-voltage WLAN systems," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 55, no. 2, pp. 496–509, Mar. 2008.

- [9] F. Carrara and G. Palmisano, "High-dynamic-range VGA with temperature compensation and linear-in-dB gain control," *IEEE J. Solid-State Circuits*, vol. 40, no. 10, pp. 2019–2024, Oct. 2005.

- [10] H. D. Lee, K. A. Lee, and S. Hong, "A wideband CMOS variable gain amplifier with an exponential gain control," *IEEE Trans. Microw. Theory Techn.*, vol. 55, no. 6, pp. 1363–1373, Jun. 2007.

- [11] Q.-H. Duong, Q. Le, C.-W. Kim, and S.-G. Lee, "A 95-dB linear low-power variable gain amplifier," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 53, no. 8, pp. 1648–1657, Aug. 2006.

- [12] S. D'Amico, A. Spagnolo, A. Donno, V. Chironi, P. Wambacq, and A. Baschirotto, "A low-power analog baseband section for 60-GHz receivers in 90-nm CMOS," *IEEE Trans. Microw. Theory Techn.*, vol. 62, no. 8, pp. 1724–1735, Aug. 2014.

- [13] K.-L. Fu and S.-I. Liu, "A 56 Gbps PAM-4 optical receiver front-end," in *Proc. IEEE Asian Solid-State Circuits Conf. (A-SSCC)*, Nov. 2017, pp. 77–80.

- [14] K.-L. Fu and S.-I. Liu, "A 64-Gb/s PAM-4 optical receiver with amplitude/phase correction and threshold voltage/data level calibration," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 28, no. 7, pp. 1726–1735, Jul. 2020, doi: 10.1109/TVLSI.2020.2991721.

- [15] A. Balachandran, Y. Chen, and C. C. Boon, "A 0.013-mm<sup>2</sup> 0.53-mW/Gb/s 32-Gb/s hybrid analog equalizer under 21-dB channel loss in 65-nm CMOS," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 26, no. 3, pp. 599–603, Mar. 2018.

- [16] A. Balachandran, Y. Chen, P. Choi, and C. C. Boon, "0.058 mm<sup>2</sup> 13 Gbit/s inductorless analogue equaliser with low-frequency equalisation compensating 15 dB channel loss," *Electron. Lett.*, vol. 54, no. 2, pp. 72–74, Jan. 2018.

- [17] A. Balachandran, Y. Chen, and C. C. Boon, "A 32-Gb/s 3.53-mW/Gb/s adaptive receiver AFE employing a hybrid CTLE, edge-DFE and merged data-DFE/CDR in 65-nm CMOS," in *Proc. IEEE Asia–Pacific Conf. Circuits Syst. (APCCAS)*, Nov. 2019, pp. 221–224.

- [18] Y. Wang, B. Afshar, L. Ye, V. C. Gaudet, and A. M. Niknejad, "Design of a low power, inductorless wideband variable-gain amplifier for high-speed receiver systems," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 59, no. 4, pp. 696–707, Apr. 2012.

- [19] L. Kong, H. Liu, X. Zhu, C. C. Boon, C. Li, Z. Liu, and K. S. Yeo, "Design of a wideband variable-gain amplifier with self-compensated transistor for accurate dB-linear characteristic in 65 nm CMOS technology," *IEEE Trans. Circuits Syst. 1, Reg. Papers*, vol. 67, no. 12, pp. 4187–4198, Dec. 2020.

- [20] Y. Chen, P.-I. Mak, and Y. Zhou, "Mixed-integrator biquad for continuoustime filters," *IET Electron. Lett.*, vol. 46, no. 8, pp. 561–563, Apr. 2010.

- [21] Y. Chen, P.-I. Mak, and Y. Zhou, "Source-follower-based bi-quad cell for continuous-time zero-pole type filters," in *Proc. IEEE Int. Symp. Circuits Syst.*, May 2010, pp. 3629–3632.

- [22] Y. Chen, P.-I. Mak, S. D'Amico, L. Zhang, H. Qian, and Y. Wang, "A single-branch third-order pole-zero low-pass filter with 0.014-mm<sup>2</sup> die size and 0.8-kHz (1.25-nW) to 0.94-GHz (3.99-mW) bandwidth-power scalability," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 60, no. 11, pp. 761–765, Nov. 2013.

- [23] Y. Chenl, P.-I. Mak, L. Zhang, H. Qian, and Y. Wang, "0.013 mm<sup>2</sup>, kHzto-GHz-bandwidth, third-order all-pole lowpass filter with 0.52-to-1.11 pW/pole/Hz efficiency," *IET Electron. Lett.*, vol. 23, no. 5, pp. 978–982, May 2013.

- [24] Y. Chen, P. Mak, L. Zhang, H. Qian, and Y. Wang, "0.0012 mm<sup>2</sup>, 8 mW, single-to-differential converter with < 1.1% data cross error and < 3.4 ps RMS jitter up to 14 Gbit/s data rate," *Electron. Lett.*, vol. 49, no. 11, pp. 692–694, May 2013.

- [25] Y. Chen, P.-I. Mak, L. Zhang, H. Qian, and Y. Wang, "A fifthorder 20-MHz transistorized-*LC*-ladder LPF with 58.2-dB SFDR, 68μW/pole/MHz efficiency, and 0.13-mm<sup>2</sup> die size in 90-nm CMOS," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 60, no. 1, pp. 11–15, Jan. 2013.

- [26] Y. Chen, P.-I. Mak, L. Zhang, and Y. Wang, "A 0.07 mm<sup>2</sup>, 2 mW, 75 MHz-IF, 4th-order BPF using a source-follower-based resonator in 90 nm CMOS," *IET Electron. Lett.*, vol. 48, no. 10, pp. 552–554, May 2012.

- [27] Y. Chen, P.-I. Mak, L. Zhang, and Y. Wang, "A 0.002-mm<sup>2</sup> 6.4-mW 10-Gb/s full-rate direct DFE receiver with 59.6% horizontal eye opening under 23.3-dB channel loss at Nyquist frequency," *IEEE Trans. Microw. Theory Techn.*, vol. 62, no. 12, pp. 3107–3117, Dec. 2014.

- [28] C. Liu, Y.-P. Yan, W.-L. Goh, Y.-Z. Xiong, L.-J. Zhang, and M. Madihian, "A 5-Gb/s automatic gain control amplifier with temperature compensation," *IEEE J. Solid-State Circuits*, vol. 47, no. 6, pp. 1323–1333, Jun. 2012.

- [29] S. Ray and M. M. Hella, "A 10 Gb/s inductorless AGC amplifier with 40 dB linear variable gain control in 0.13 ?m CMOS," *IEEE J. Solid-State Circuits*, vol. 51, no. 2, pp. 440–456, Feb. 2016.

- [30] L. Kong, Y. Chen, C. C. Boon, P.-I. Mak, and R. P. Martins, "A wideband inductorless dB-linear automatic gain control amplifier using a singlebranch negative exponential generator for wireline applications," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 65, no. 10, pp. 3196–3206, Oct. 2018.

- [31] L. Kong, Y. Chen, H. Yu, Q. Pan, C. C. Boon, P.-I. Mak, and R. P. Martins, "Wideband variable-gain amplifiers based on a pseudo-current-steering gain-tuning technique," in *Proc. IEEE Asia Pacific Conf. Circuits Syst.* (APCCAS), Nov. 2019, pp. 153–156.

- [32] I. Choi, H. Seo, and B. Kim, "Accurate dB-linear variable gain amplifier with gain error compensation," *IEEE J. Solid-State Circuits*, vol. 48, no. 2, pp. 456–464, Feb. 2013.

- [33] Y. Zheng, J. Yan, and Y. Ping Xu, "A CMOS VGA with DC offset cancellation for direct-conversion receivers," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 56, no. 1, pp. 103–113, Jan. 2009.

- [34] H. Lee, K. Lee, and S. Hong, "Wideband VGAs using a CMOS transconductor in triode region," in *Proc. Eur. Microw. Conf.*, Sep. 2006, pp. 1449–1452.

- [35] O. Watanabe, S. Otaka, M. Ashida, and T. Itakura, "A 380-MHz CMOS linear-in-dB signal-summing variable gain amplifier with gain compensation techniques for CDMA systems," in *IEEE Dig. Tech. Papers Symp. VLSI Circuits*, Jun. 2002, pp. 136–139.

- [36] S. Otaka, G. Takemura, and H. Tanimoto, "A low-power low-noise accurate linear-in-dB variable-gain amplifier with 500-MHz bandwidth," *IEEE J. Solid-State Circuits*, vol. 35, no. 12, pp. 1942–1948, Dec. 2000.

- [37] K.-S. Nah and B.-H. Park, "A 50-MHz dB-linear programmable-gain amplifier with 98-dB dynamic range and 2-dB gain steps for 3 V power supply," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 11, no. 2, pp. 218–223, Apr. 2003.

- [38] C.-C. Kuo, Z.-M. Tsai, J.-H. Tsai, and H. Wang, "A 71–76 GHz CMOS variable gain amplifier using current steering technique," in *IEEE RFIC Symp. Dig.*, Jun. 2008, pp. 609–612.

- [39] T. B. Kumar, K. Ma, and K. S. Yeo, "A 4 GHz 60 dB variable gain amplifier with tunable DC offset cancellation in 65 nm CMOS," *IEEE Microw. Wireless Compon. Lett.*, vol. 25, no. 1, pp. 37–39, Jan. 2015.

- [40] C.-H. Wu, C.-S. Liu, and S.-L. Liu, "A 2 GHz CMOS variable-gain amplifier with 50 dB linear-in-magnitude controlled gain range for 10 GBase-LX4 Ethernet," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, 2004, pp. 484–485.

- [41] I.-H. Wang, W.-S. Chen, and S.-I. Liu, "10 GBase-LX CMOS automatic gain control amplifier design," in *Proc. IEEE Asian Solid-State Circuits Conf.*, Nov. 2005, pp. 505–508.

- [42] H. Liu, C. C. Boon, X. He, X. Zhu, X. Yi, L. Kong, and M. C. Heimlich, "A wideband analog-controlled variable-gain amplifier with dB-linear characteristic for high-frequency applications," *IEEE Trans. Microw. The*ory Techn., vol. 64, no. 2, pp. 533–540, Feb. 2016.

- [43] Y. Chen, P.-I. Mak, C. C. Boon, and R. P. Martins, "A 27-Gb/s time-interleaved duobinary transmitter achieving 1.44-mW/Gb/s FOM in 65-nm CMOS," *IEEE Microw. Wireless Compon. Lett.*, vol. 27, no. 9, pp. 839–841, Sep. 2017.

- [44] Y. Chen, P.-I. Mak, C. C. Boon, and R. P. Martins, "A 36-Gb/s 1.3-mW/Gb/s duobinary-signal transmitter exploiting power-efficient cross-quadrature clocking multiplexers with maximized timing margin," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 65, no. 9, pp. 3014–3026, Sep. 2018.

- [45] Y. Chen, P.-I. Mak, H. Yu, C. C. Boon, and R. P. Martins, "An area-efficient and tunable bandwidth- extension technique for a wideband CMOS amplifier handling 50+ Gb/s signaling," *IEEE Trans. Microw. Theory Techn.*, vol. 62, no. 12, pp. 3107–3117, Dec. 2017.

- [46] Y. Chen, P.-I. Mak, C. Chye Boon, and R. P. Martins, "A 0.024-mm<sup>2</sup> 45.4-GHz-bandwidth unity-gain output driver with SDD22<-10dB up to 35 GHz," in *Proc. IEEE 63rd Int. Midwest Symp. Circuits Syst. (MWS-CAS)*, Aug. 2020, pp. 687–690.

- [47] Y. Chen, P.-I. Mak, and Y. Wang, "A highly-scalable analog equalizer using a tunable and current-reusable for 10-Gb/s I/O links," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 23, no. 5, pp. 978–982, May 2015.

- [48] X. Zhao, Y. Chen, P.-I. Mak, and R. P. Martins, "A 0.0018-mm<sup>2</sup> 153%locking-range CML-based divider-by-2 with tunable self-resonant frequency using auxiliary negative-gm cell," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 65, no. 9, pp. 3014–3026, May 2019.

[49] Y. Chen, P.-I. Mak, Z. Yang, C. C. Boon, and R. P. Martins, "A 0.0071-mm<sup>2</sup> 10.8pspp-jitter 4 to 10-Gb/s 5-tap current-mode transmitter using a hybrid delay line for sub-1-UI fractional de-emphasis," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 66, no. 10, pp. 3991–4004, Oct. 2019.

**LINGSHAN KONG** received the B.Eng. degree in electrical and electronic engineering from Nanyang Technological University (NTU), Singapore, in 2014, where she is currently pursuing the Ph.D. degree.

Her research interests include analog baseband design and wireline backplane transceiver design.

**YONG CHEN** (Senior Member, IEEE) received the B.Eng. degree in electronic and information engineering from the Communication University of China (CUC), Beijing, China, in 2005, and the Ph.D. (Engineering) degree in microelectronics and solid-state electronics from the Institute of Microelectronics, Chinese Academy of Sciences (IMECAS), Beijing, in 2010.

From 2010 to 2013, he worked as a Postdoctoral Researcher with the Institute of Microelectronics,

Tsinghua University, Beijing. From 2013 to 2016, he was a Research Fellow with the VIRTUS/EEE, Nanyang Technological University, Singapore. He has been an Assistant Professor with the State Key Laboratory of Analog and Mixed-Signal VLSI (AMSV), University of Macau, Macao, China, since March 2016. His research interest includes integrated circuit designs, involving analog/mixed-signal/radio frequency (RF)/mm-wave/sub-THz/wireline.

Dr. Chen served as a member for ICSICT in 2020 and the Technical Program Committee of APCCAS from 2019 to 2020. He has been serving as a member for the Circuits and Systems for Communications (CASCOM) Technical Committee of the IEEE Circuits and Systems Society, ICTA, and NorCAS since 2020. He currently serves as a Review Committee Member for ISCAS. He was a recipient of the "Haixi" (three places across the Straits) Postgraduate Integrated Circuit Design Competition (Second Prize) in 2009. He was a co-recipient of the Best Paper Award at the IEEE Asia Pacific Conference on Circuits and Systems (APCCAS) in 2019 and the Macao Science and Technology Invention Award (First Prize) in 2020. His team reported three chip inventions at the IEEE International Solid-State Circuits Conference (ISSCC) (Chip Olympics): mm-wave PLL in 2019, VCO in 2019, and radio-frequency VCO in 2021. He has been serving as the Vice-Chair for the IEEE Macau CAS Chapter since 2019, and the Tutorial Chair of ICCS since 2020. He has served on the Conference Local Organization Committee of A-SSCC in 2019. He has been serving as an Associate Editor for the IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (TVLSI) SYSTEMS since 2019, IEEE Access since 2019, and the IET Electronics Letters (EL) since 2020, and an Editor for the International Journal of Circuit Theory and Applications (IJCTA) since 2020. He serves as a Guest Editor for the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS-II: EXPRESS BRIEFS in 2021.

**HAOHONG YU** received the B.Eng. degree in electrical and electronic engineering from Nanyang Technological University (NTU), Singapore, in 2013, where he is currently pursuing the Ph.D. degree.

His research interests include noise-cancelling broadband low-noise amplifiers and wideband amplifiers.

CHIRN CHYE BOON (Senior Member, IEEE) received the B.E. (Hons.) and Ph.D. degrees in electrical engineering from Nanyang Technological University (NTU), Singapore, in 2000 and 2004, respectively.

He was with Advanced RFIC, NTU, where he was a Senior Engineer. Since 2005, he has been with NTU, where he is currently an Associate Professor. He is involved in radio frequency and mm-wave circuits and systems design for biomed-

ical and communications applications. He has conceptualized, designed, and silicon-verified 80 circuits/chips for biomedical and communication applications. Since 2010, he has been the Program Director of radio frequency (RF) and mm-wave research with the S\$50 Million Research Center of Excellence, VIRTUS, NTU. He is the Principal Investigator for Industry/Government Research Grants of S\$8 646 178.22. He has authored over 100 refereed publications in the fields of RF and mm-wave. He has authored the book: Design of CMOS RF Integrated Circuits and Systems (2010).

Dr. Boon serves as a committee member for various conferences. He was a recipient of the Year-2 Teaching Excellence Award and the Commendation Award for Excellent Teaching Performance from the School of Electrical and Electronic Engineering, NTU. He is also an Associate Editor of the IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (TVLSI) SYSTEMS and a Golden Reviewer of the IEEE ELECTRON DEVICE LETTERS.

PUI-IN MAK (Fellow, IEEE) received the Ph.D. degree from the University of Macau (UM), Macao, China, in 2006.

He is currently a Full Professor with the Department of Electrical and Computer Engineering, Faculty of Science and Technology, UM, and an Associate Director (Research) with the Institute of Microelectronics and the State Key Laboratory of Analog and Mixed-Signal VLSI, UM. His research interests include analog and radio-frequency (RF) circuits and systems for wireless and multidisciplinary innovations.

Dr. Mak served as a member for the Board of Governors of the IEEE Circuits and Systems Society from 2009 to 2011, a TPC Member for A-SSCC from 2013 to 2016 and in 2019, an Editorial Board Member for IEEE Press from 2014 to 2016, ESSCIRC from 2016 to 2017, and ISSCC from 2017 to 2019. He has been a Fellow of the Institution of Engineering and Technology (IET), U.K., for contributions to engineering research, education, and services, since 2018, a Fellow of the IEEE for contributions to radiofrequency and analog circuits, since 2019, and a Fellow of the Royal Society of Chemistry, U.K., since 2020. He (co-)received the DAC/ISSCC Student Paper Award in 2005, the CASS Outstanding Young Author Award in 2010, the National Scientific and Technological Progress Award in 2011, the Best Associate Editor of the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS-II: EXPRESS BRIEFS for the term 2012-2013, the A-SSCC Distinguished Design Award in 2015, and the ISSCC Silkroad Award in 2016. In 2005, he was decorated with the Honorary Title of Value for Scientific Merits by the Macau Government. He has been inducted as an Overseas Expert of the Chinese Academy of Sciences since 2018. He is/was the TPC Vice Co-Chair of ASP-DAC in 2016, and the Chairman of the Distinguished Lecturer Program of the IEEE Circuits and Systems Society from 2018 to 2019. He was a Senior Editor of IEEE JOURNAL ON EMERGING AND SELECTED TOPICS IN CIRCUITS AND SYSTEMS from 2014 to 2015. He has been an Associate Editor of IEEE JOURNAL OF SOLID-STATE CIRCUITS since 2018, IEEE SOLID-STATE CIRCUITS LETTERS since 2017. He was an Associate Editor of IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS-I: REGULAR PAPERS from 2010 to 2011 and from 2014 to 2015, and IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS-II: EXPRESS BRIEFS from 2010 to 2013. He is/was Distinguished Lecturer of the IEEE Circuits and Systems Society from 2014 to 2015, and the IEEE Solid-State Circuits Society from 2017 to 2018.

RUI P. MARTINS (Fellow, IEEE) was born in April 1957. He received the bachelor's, master's, Ph.D. degrees, and the Habilitation for Full-Professor degree in electrical engineering and computers from the Department of Electrical and Computer Engineering (DECE), Instituto Superior Técnico (IST), University of Lisbon, Portugal, in 1980, 1985, 1992, and 2001, respectively.

He has been with DECE, IST, University of Lisbon, since October 1980. Since October 1992,

has been on leave from the University of Lisbon and with the DECE, Faculty of Science and Technology (FST), University of Macau (UM), Macao, China, where he has been the Chair-Professor, since August 2013. He was the Dean of FST, UM, from 1994 to 1997. He has been the Vice-Rector with UM, since September 1997. From September 2008 to August 2018, he was the Vice-Rector (Research) and from September 2018 to August 2023, the Vice-Rector (Global Affairs). Within the scope of his teaching and research activities, he has taught 21 bachelor and master courses and, in UM, has supervised (or co-supervised) 47 theses: Ph.D. (26) and Masters (21) theses. He has authored or coauthored seven books; 12 book chapters; 36 patents-USA (32), Taiwan (3), and China (1); 567 papers-in scientific journals (220) and in conference proceedings (347); and other 66 academic works, in a total of 688 publications. In 2003, he created the Analog and Mixed-Signal VLSI Research Laboratory, UM, elevated in January 2011 to the State Key Laboratory (SKLAB) of China (the first in Engineering in Macao), being its Founding Director. He was the Founding Chair of UMTEC (UM company) from January 2009 to March 2019, supporting the incubation and creation in 2018 of Digifluidic, the first UM spin-off, whose CEO is a SKLAB Ph.D. graduate. He was a Co-Founder of Chipidea Microelectronics (Macao) [now Synopsys-Macao] from 2001 to 2002.

Dr. Martins was a member of IEEE CASS from 2012 to 2013. He received two Macao Government decorations: the Medal of Professional Merit (Portuguese-1999) and the Honorary Title of Value (Chinese-2001) and the IEEE Council on Electronic Design Automation (CEDA) Outstanding Service Award in 2016. He was the Founding Chair of the IEEE Macau Section from 2003 to 2005, the IEEE Macau Joint-Chapter on Circuits and Systems (CAS)/Communications (COM) from 2005 to 2008 [2009 World Chapter of the Year of IEEE CAS Society (CASS)], the General Chair of ACM/IEEE Asia South Pacific Design Automation Conference (ASP-DAC), in 2016, the General Chair of the IEEE Asian Solid-State Circuits Conference (A-SSCC) in 2019 and the IEEE Asia-Pacific Conference on CAS (APC-CAS) in 2008, the Vice-President (VP) of Region 10 (Asia, Australia, and Pacific), from 2009 to 2011, and the VP-World Regional Activities. He was an Associate Editor of IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS-II: EXPRESS BRIEFS from 2010 to 2013. He was nominated for the Best Associate Editor for the term 2012-2013. He was the Chair of the IEEE CASS Fellow Evaluation Committee from 2013 to 2014 and in 2018, where he was the Vice-Chair in 2019 and 2021. He was a member of the IEEE Nominating Committee of Division I Director (CASS/EDS/SSCS) in 2014 and the IEEE CASS Nominations Committee from 2016 to 2017. From 2005 to 2014, he was the Vice-President of the Association of Portuguese Speaking Universities (AULP), where he was the President from 2014 to 2017. In July 2010, he was elected, unanimously, as a Corresponding Member of the Lisbon Academy of Sciences, being the only Portuguese Academician working and living in Asia.

. . .