Received January 5, 2021, accepted January 12, 2021, date of publication January 18, 2021, date of current version January 22, 2021.

Digital Object Identifier 10.1109/ACCESS.2021.3052159

## **Key Technology Practice of High-Speed Access** and Research on the Temperature Dependence of Key Time Parameters Based on **NAND Flash Memory**

ZHUO HOU<sup>®</sup>, HUIMIN CHEN<sup>®</sup>, JIAHAO DENG<sup>®</sup>, AND ZUODONG DUAN<sup>®</sup>

Science and Technology on Electromechanical Dynamic Control Laboratory, School of Mechatronic Engineering, Beijing Institute of Technology,

Beijing 100081, China

Corresponding author: Huimin Chen (laserchm@126.com)

This work was supported in part by the Foundation of Science and Technology on Applied Physical Chemistry Laboratory of China under Grant 6142602190207, and in part by the National Defense Pre-Research Field Foundation of China under Grant 61404160208.

ABSTRACT This paper focuses on the NAND flash memory as a data storage medium in the Internet of things data acquisition system, which plays an important role from beginning to end. The flow process of multi-channel sensor data sampling, holding, conversion, coding, and storage in the data acquisition system is described. The basic working principle and working process of NAND flash memory are introduced. Based on Interleaved Two-plane Program Technology, and the solution of burst massive throughput in high-speed data transmission is proposed. Compared with previously published papers, the temperature dependence of key time parameters of NAND flash memory is studied and analyzed under the condition of temperature change more concretely. The changing trend of three key time parameters of NAND type flash under different temperatures is analyzed by using appropriate test samples. At the same time, the analysis of the causes of reflection from the phenomenon is further expanded and discussed. The combination of theory and practice can provide powerful suggestions for more efficient and accurate application of NAND flash memory.

**INDEX TERMS** NAND flash, interleave two-plane program, burst massive data, temperature dependence.

#### I. INTRODUCTION

With the advent of the Internet of things [1], [2] era, the interconnection of all things has become an inevitable trend. It means that more data information needs to be processed and more sensors will be widely deployed and used [3]–[14]. As a result, the demand for data storage becomes increasingly strong. Most of the dynamic parameters of the external world sensed by sensors are finally stored in the form of digital quantities. As an indispensable member of the flash memory family, NAND flash memory plays an important role [15]–[20]. As a non-volatile storage device, it plays an important role in promoting the process of the Internet of things with low power consumption, low cost, and stable performance. As we all know, NOR [21]-[23] and NAND are the two main non-volatile flash technology in the market. INTEL first developed NOR flash technology in 1988, which

The associate editor coordinating the review of this manuscript and approving it for publication was Abdullah Iliyasu.

completely changed the situation that EPROM and EEP-ROM [24]–[26] dominate the world. Then, in 1989, Toshiba released NAND flash architecture, which emphasizes reducing the cost per bit, higher performance, and being able to easily upgrade through the interface like a disk. Compared with NOR, NAND is an ideal solution for high data storage density. NAND structure can provide very high cell density, which can achieve high storage density, and the speed of writing and erasing is also very fast.

Based on the consideration of product maturity, the traditional 2-D NAND flash memory is still used in this paper. However, it is worth noting that as a new generation of storage products, 3-D NAND flash memory is receiving high attention now. The main reason for this above is that after many years of development, NAND flash memory is not only divided into SLC, MLC, and TLC. To further improve the capacity and reduce the cost, NAND's manufacturing process is also rapidly improved, from 50nm to 16nm or even smaller. However, with the progress of technology, NAND's oxide layer is thinner, which leads to the decline of reliability. Under such a bottleneck problem, 3-D NAND flash memory was born, and several layers of 2-D NAND flash memory were superimposed together, which not only ensured the reliability but also increased the capacity. Because of the technology of 3-D NAND, some TLC products with corresponding technology have achieved the performance of MLC, which is what we often call 3-D TLC. The research on 3-D NAND flash memory is being carried out all over the world, both in application and technology [27]–[29].

## II. RESEARCH ON THE RELATIONSHIP BETWEEN THE TOTAL BANDWIDTH OF MULTI-CHANNEL ACOUISITION AND ERASURE MODE

The core task of a multi-channel sensor data acquisition system is to accurately collect and record the time series of all channel dynamic parameters. The essence of task implementation is to sample, hold, convert, encode, and store under the control of the CPU (such as programmable logic device FPGA [30]–[32]).

The multi-channel sensor data acquisition system uses flash memory based on the NAND principle. The operation of NAND flash memory mainly includes erasing, writing, and reading. Before writing data, NAND flash memory needs to be erased first. Erasing is performed on a block by block basis, and a single block, multi-block, or whole memory can be erased at one time. There are two erasure methods used in the development of a multi-channel sensor data acquisition system. One is "write while erasing", and another is "erase before writing". "Write while erasing" refers to erasing one block at a time, then writing one block, erasing and writing in turn. "Erase before writing" means that after receiving the "erase" instruction, the whole memory address space is erased first, and then the data is continuously written. The erasure method adopted depends on the maximum erasure time  $T_e$ , and the amount of data written to memory per unit time  $D_u$ , and  $F_{fifo}$  which is the capacity of FIFO that can be built-in CPU.

According to the system redundancy design principle and previous design experience. If the above three parameters meet the following formula 1, "write while erasing" can be adopted and used.

$$T_e \times D_u \le \frac{3}{4} F_{fifo} \tag{1}$$

On the contrary, when the following formula 2 is satisfied, "erase before writing" will be the choice.

$$T_e \times D_u \ge \frac{3}{4} F_{fifo} \tag{2}$$

When formula 1 is satisfied, "write while erasing" can improve the reliability of the data storage procedure. In this way, there may not be a special erase command link between the multi-channel sensor data acquisition system and the monitoring background. Acquisition systems often work independently to reduce the risk of data being erased when retrieving readings. However, if formula 2 is satisfied,

the internal FIFO data overflow of the CPU may occur during the system erasing memory, resulting in data loss.

When formula 2 is satisfied, "erase before writing" can alleviate the contradiction between insufficient system resources and a high amount of data written per unit of time. However, it also increases the possibility of data erasure due to operational errors or control link interference when retrieving readings.

For example, a multi-channel sensor data acquisition system is equipped with a 16-bit analog-to-digital conversion chip. Its total sampling rate is 1msps and the amount of data written to memory per second is 2Mbytes. The CPU adopts a programmable logic device FPGA whose internal FIFO can be up to 4Kbytes (32Kbits). The capacity of NAND flash memory is 1Gbytes, and the maximum erasing time is 2ms.

Formula 3 is as follows.

$$T_e \times D_u = 2 \times 10^{-3} s \times 2 \times \frac{10^6 bytes}{s}$$

$$= 4 \times 10^3 bytes \ge 3Kbytes = \frac{3}{4} F_{fifo}$$

(3)

In this case, it is suitable to use the "erase before writing" method.

# III. THE INTERLEAVE TWO-PLANE PROGRAM TECHNOLOGY FOR BURST MASSIVE DATA IN HIGH-SPEED DATA TRANSMISSION

The manufacturer's NAND flash memory has a nominal maximum write speed of 40Mbytes/s. However, the average write speed of the developed system is lower than this character. There are two reasons for this. One is to use programmable logic devices to control the memory, which contains many instructions, and the execution of instructions takes time. Second, the data of NAND flash memory is written on a page by page basis. Each time a page is written, it needs 'page programming time". Generally, this time parameter is  $200\mu s \sim 700\mu s$ . Therefore, it can be assumed that in this case, regardless of the time taken by the instructions, the data flows continuously to the memory and does not pass through the internal FIFO of the CPU. The capacity of each page is 4Kbytes, the peak speed is 40Mbytes/s, and the programming time is  $200\mu$ s. The expression of the average write speed  $V_P$ of the maximum data is as follows.

$$V_P = 4Kbytes/(\frac{4Kbytes}{40Mbytes/s} + 200\mu s)$$

$$\approx 13.544973Mbytes/s$$

(4)

The calculation method is given in formula 4 still contains some assumptions, but the calculation results are close to the real situation that data writing under normal mode of NAND flash memory enters the "page programming" link, which is suitable for systems with average data writing speed lower than 13.5Mbytes/s. When the sampling frequency is very high and the amount of data written per second is more than 13.5Mbytes, the manufacturer provides another solution: Interleave Two-Plane Page Program Technology.

Based on the spatial structure of NAND flash memory, erasing, writing, and reading operations of Interleave

12204 VOLUME 9, 2021

Two-Plane Page Program Technology are carried out on multiple pages in a plane interleaved manner. The capacity of the object studied and tested in this paper is 4Gbytes. The memory space of a single chip is composed of two 2Gbytes memories. The memory space consists of eight planes. The capacity of each page is 4Kbytes. The crystal frequency is 60MHz. The used frequency is 1/2 division of the crystal frequency. The specific steps of interleaved plane programming are as follow.

- A. By using Interleave Two-Plane Page Program Technology, the command and data are written to the 4Kbytes storage space of the first and second plane in the first 2Gbyte memory;

- B. By using Interleave Two-Plane Page Program Technology, the command and data are written to the 4Kbytes storage space of the first and second plane in the second 2Gbyte memory;

- C. In steps A and B, there is no waiting time between operations on two pieces of 2Gbytes memory;

- D. After step B, wait for about  $50\mu$ s and repeat steps  $A\sim D$ ;

- E. Interleave Two-Plane Page Program is done.

In practical application,  $A \sim B$  of the above steps show multiple cycles. The waiting time in step D is  $50\mu s$ . It corresponds to the page programming time of 4Kbytes on page 1 of the second plane in the second 2Gbytes memory of step B. A total of 16Kbytes of data is written to 4 pages in a single cycle. But the overall waiting time is the only  $50\mu s$ . The test data and calculation results are shown in Table 1.

**TABLE 1.** List of test data and calculation results based on Interleave Two-Plane Page Program Technology.

| Location of sequential page writing   | Time of<br>control<br>instruction | Write time of<br>4kbytes data<br>in the page | Waiting time<br>of page<br>programming | Note             |

|---------------------------------------|-----------------------------------|----------------------------------------------|----------------------------------------|------------------|

| Chip 1/plane 1 page 1                 | 0.767µs                           | 136µs                                        | 0μs                                    | Total            |

| Chip 1/plane 2 page 1                 | 0.767µs                           | 136µs                                        | 0μs                                    | 16kby            |

| Chip 2/plane 1 page 1                 | 0.767µs                           | 136µs                                        | 0μs                                    | tes              |

| Chip 2/plane 2 page 1                 | 0.767µs                           | 136µs                                        | 50μs                                   | data             |

| Total single write<br>cycle time      |                                   | 597.134μs                                    |                                        | in 4<br>pages    |

| Peak write speed of a single cycle    |                                   | 30Mbytes/s                                   |                                        | writte<br>n in a |

| Average write speed of a single cycle |                                   | single<br>cycle                              |                                        |                  |

It can be seen from Table 1 that the average write speed of a single cycle with Interleaved Two-Plane Program Technology is 27.437Mbytes/s at 1/2 frequency division of 60MHz.

# IV. RESEARCH ON THE TEMPERATURE DEPENDENCE OF KEY TIME PARAMETERS BASED ON NAND FLASH MEMORY

## A. TEST AND ANALYSIS OF TEMPERATURE DEPENDENCE OF THREE KEY TIME PARAMETERS

As mentioned above, the multi-channel sensor data acquisition system uses flash memory based on the NAND principle. Its operation mainly includes erasing, writing, and reading. The typical and maximum erasure time, page programming time, and read operation waiting time are given by the manufacturers. In the environmental adaptability test of several

test systems, it is found that the above three key time parameters will change with the environmental temperature due to the correlation between the electrical parameters of the internal circuit and the temperature [33]-[36]. No matter the temperature increases or decreases, the changing trend of the three parameters is similar, and the change range cannot be ignored. It is important to point out that these key time parameters are the objects that must be considered in the storage and test of a multi-channel sensor data acquisition system. They are related to the successful storage and reading of test data. When the temperature changes lead to the corresponding changes of these parameters and the change range cannot be ignored, designers must provide accurate parameter range for data storage link according to repeated test verification, to make reasonable prediction and planning for further design.

Table 2 is a list of tested data of three key time parameters of several NAND flash memory chips with multiple brands and capacities for many times from high to low temperature.

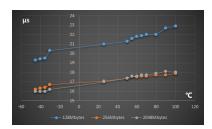

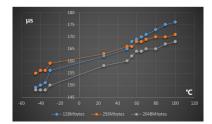

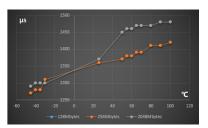

As can be seen from table 2, taking NAND flash memory programming time parameters as an example, when the temperature range changes from  $-45^{\circ}\text{C}$  to  $+100^{\circ}\text{C}$  above zero, the maximum difference of programming time is nearly  $27\mu\text{s}$  with the change of temperature. The transverse comparison curves of the same type of time parameters are shown in Fig.  $1{\sim}3$ .

When the multi-channel sensor data acquisition system stores the sampled data, FIFO is usually set to buffer the data. When the total sampling rate of the system is high and the amount of data generated per second is large, the size of FIFO must be designed from the perspective of maximum programming time to ensure that data transmission and storage will not be lost. If the temperature range of the multi-channel sensor data acquisition system is underestimated, the designed FIFO size may not guarantee the data validity under extreme temperature conditions during data transmission and storage.

### B. DISCUSSION AND RESEARCH ON THE ROOT CAUSE OF TEMPERATURE DEPENDENCE OF KEY TIME PARAMETERS BASED ON STA

Semiconductor Wafer which is used for manufacturing FPGA, NAND flash memory, and all kinds of chips is composed of numerous transistor logic gates by special technology. From the day the chip was born it is one of the common goals of all electronic designers to predict the time delay of full-custom integrated circuits. However, due to the physical phenomenon of the nonlinear and complex model and based on effective working conditions such as voltage, temperature, and process, it is not easy to achieve accurate time delay prediction.

Static Timing Analysis, STA, is the workflow of computing and predicting chip timing in electronic engineering. The process does not need to be simulated by providing input incentives. The purpose of Static Timing Analysis is to ensure the normal operation of time sequence logic. Whether for

VOLUME 9, 2021 12205

**TABLE 2.** Test value list of NAND flash key time parameters with temperature.

| storage              | Measurement                  | Temperature conditions at the time of measurement ( $^{\circ}\mathbb{C}$ ) |           |                     |             |       |  |

|----------------------|------------------------------|----------------------------------------------------------------------------|-----------|---------------------|-------------|-------|--|

| capacity             | parameter                    | 100°C 90°C 80°C 70°C €                                                     |           |                     |             |       |  |

| (Mbytes)             | name                         |                                                                            |           | est value(µ         |             |       |  |

|                      | erasure time                 |                                                                            |           |                     |             |       |  |

| 128 <sup>a</sup>     | page<br>programming          | 176                                                                        | 175       | 173                 | 171         | 170   |  |

|                      | time<br>read                 |                                                                            |           |                     |             |       |  |

|                      | operation<br>waiting time    | 22.9                                                                       | 22.7      | 22                  | 22          | 21.9  |  |

|                      | erasure time                 | 1420                                                                       | 1410      | 1410                | 1390        | 1390  |  |

| 256                  | page                         |                                                                            |           |                     |             |       |  |

|                      | programming<br>time          | 171                                                                        | 170       | 170                 | 169         | 168   |  |

|                      | read                         | 47.0                                                                       |           |                     | 48.4        | 48.4  |  |

|                      | operation<br>waiting time    | 17.9                                                                       | 17.7      | 17.7                | 17.6        | 17.6  |  |

| 2048                 | erasure time                 | 1480                                                                       | 1480      | 1470                | 1470        | 1470  |  |

|                      | page                         |                                                                            |           |                     |             |       |  |

|                      | programming<br>time          | 168                                                                        | 167       | 165                 | 165         | 164   |  |

|                      | read                         | 10                                                                         | 10.1      | 17.0                | 177         | 177   |  |

|                      | operation<br>waiting time    | 18                                                                         | 18.1      | 17.9                | 17.7        | 17.7  |  |

| storage              | at the time                  | e of                                                                       |           |                     |             |       |  |

| capacity             | Measurement<br>parameter     | measurement(°C)  60°C 55°C 50°C 26°C -30°C                                 |           |                     |             |       |  |

| (Mbytes)             | name                         | 60℃                                                                        | 55℃<br>Te | 50°C<br>est value(µ | 26℃<br>s)   | -30 C |  |

|                      | erasure time                 |                                                                            |           |                     |             |       |  |

| 128 <sup>a</sup>     | page                         |                                                                            |           |                     |             |       |  |

|                      | programming                  | 169                                                                        | 168       | 165                 | 162         | 156   |  |

|                      | read                         |                                                                            |           |                     |             |       |  |

|                      | operation                    | 21.8                                                                       | 21.6      | 21.3                | 21          | 20.3  |  |

|                      | waiting time                 |                                                                            |           |                     |             |       |  |

| 256                  | erasure time                 | 1380                                                                       | 1380      | 1370                | 1360        | 1310  |  |

|                      | page<br>programming<br>time  | 168                                                                        | 166       | 166                 | 163         | 159   |  |

|                      | read                         |                                                                            |           |                     |             |       |  |

|                      | operation                    | 17.5                                                                       | 17.6      | 17.4                | 17.1        | 16.7  |  |

|                      | waiting time                 | 1460                                                                       | 1460      | 1450                | 1270        | 1200  |  |

|                      | erasure time<br>page         | 1460                                                                       | 1460      | 1450                | 1370        | 1300  |  |

| 2048                 | programming<br>time          | 164                                                                        | 162       | 160                 | 158         | 150   |  |

|                      | read                         |                                                                            |           |                     |             |       |  |

|                      | operation                    | 17.6                                                                       | 17.6      | 17.4                | 17          | 16.2  |  |

|                      | waiting time                 | To                                                                         | mnoratura | conditions          | at the time | of    |  |

| storage              | Measurement                  | 161                                                                        | -         | asurement(          |             | . 51  |  |

| capacity<br>(Mbytes) | parameter<br>name            | -35℃                                                                       | -40°C     | -45°C               |             |       |  |

| ()                   |                              |                                                                            | Te        | est value(μ         | s)          |       |  |

| 128                  | erasure time                 |                                                                            |           |                     |             |       |  |

|                      | page<br>programming<br>time  | 151                                                                        | 150       | 149                 |             |       |  |

|                      | read                         |                                                                            |           |                     |             |       |  |

|                      | operation                    | 19.5                                                                       | 19.4      | 19.3                |             |       |  |

|                      | waiting time<br>erasure time | 1280                                                                       | 1280      | 1270                |             |       |  |

| 256                  | page                         | 1=00                                                                       | 1200      | 16/0                |             |       |  |

|                      | programming                  | 156                                                                        | 155       | 155                 |             |       |  |

|                      | time                         |                                                                            |           |                     |             |       |  |

|                      | read<br>operation            | 16.4                                                                       | 16.3      | 16.2                |             |       |  |

|                      | waiting time                 | 10.4                                                                       | 10.0      | 10.2                |             |       |  |

| 2048                 | erasure time                 | 1300                                                                       | 1300      | 1290                |             |       |  |

|                      | page .                       | 4.40                                                                       | 4.40      |                     |             |       |  |

|                      | programming<br>time          | 148                                                                        | 148       | 148                 |             |       |  |

|                      | read                         |                                                                            |           |                     |             |       |  |

|                      | operation                    | 16                                                                         | 16        | 16                  |             |       |  |

|                      | waiting time                 |                                                                            |           |                     |             |       |  |

FIGURE 1. The transverse comparison curve of read operation waiting time.

FIGURE 2. The transverse comparison curve of page programming time.

FIGURE 3. The transverse comparison curve of erasure time.

FPGA or NAND flash memory, the delay of the combinational logic circuit mainly depends on line delay and gate delay. Among them, the line delay refers to the transmission delay caused by the connection to the electrical signal. The line delay is closely related to the impedance model of the connection, sectional parasitic capacitance, inductance, and the length of the connection, etc. it depends on the final layout and wiring of the chip design. Gate delay refers to the delay caused by the specific gate unit circuit used in combinational logic in the process of electrical signal processing. But even if the chip design has been realized by a certain gate circuit and a certain physical connection, there are still variables in the line delay and gate delay, because the characteristics of the physical circuit are affected by many factors, the most important of which are temperature and voltage.

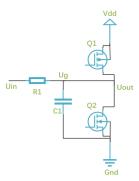

Based on the analysis above, the influence of temperature on timing delay is further discussed. Considering the parasitic capacitance and resistance of NAND flash memory or FPGA internal circuit, ignoring some non-important parameters, taking the inverter as an example, considering the input connection, the corresponding CMOS principle circuit can be approximate as shown in Figure 4.

In general, the higher the temperature is, the more intense the thermal motion of molecules will be, which is easier to

12206 VOLUME 9, 2021

FIGURE 4. The transverse comparison curve of erasure time.

hinder the movement of electrons in the conductor and semiconductor, and the most significant effect is to increase the resistance. Corresponding to the inverter circuit in Figure 4,  $R_1$  becomes larger, thus  $R_1C_1$  becomes larger. Assuming that  $V_{dd}$  remains unchanged, then.

The length of time changes from  $U_{in}$  turning from logic 0 to logic 1 to  $U_{out}$  turning from logic 1 to logic 0. Firstly, the response speed of  $U_{out}$  from logic 1 to logic 0 mainly depends on the speed of NMOS conduction under the circuit, and the condition of NMOS conduction is that  $U_g$  is greater than the threshold voltage. As the temperature increases,  $R_1C_1$  becomes larger, so the time required for  $U_g$  to increase from 0V to threshold voltage becomes longer, which will eventually lead to  $U_{out}$  changing to logic 0 after a long time.

Using a similar analysis method, the length of time changes from  $U_{in}$  turning from logic 1 to logic 0 to  $U_{out}$  turning from logic 0 to logic 1. Firstly, the response speed of  $U_{out}$  from logic 0 to logic 1 mainly depends on the speed of PMOS conduction above the circuit, and the conduction condition of PMOS is that  $U_g$  is less than the threshold voltage. As the temperature increases,  $R_1C_1$  becomes larger, so the time required for  $U_g$  to decrease from  $V_{dd}$  to threshold voltage becomes longer, which will eventually lead to  $U_{out}$  becoming logic 1 after a long time.

Through the above analysis, it can be concluded that the higher the temperature, the greater the internal delay of the chip. The test concluded that the key time parameters change with the temperature in Section 4.1 of this paper has good theoretical support. At the same time, it can also be used as one of the design suggestions to suppress the chip working in a higher temperature environment as far as possible.

#### V. SUMMARY

On the one hand, the solution of burst data acquisition has been given. But the high demand for flash memory technology is not only limited to write but also fast erase and high-speed read and so on. In the same way, they can also be solved by Interleaved Two-Plane Program Technology. On the other hand, the numerous sensors in the Internet of things have their application environment across the globe, and they are always facing the extreme weather environment. How to ensure the durability and stability of the multi-channel sensor data acquisition system, the research on the time

correlation of the key time parameters of the measurement system becomes one of the support points. In the Internet of things era, flash memory technology cannot be avoided as a data storage medium, and NAND flash memory always plays an important role.

#### **REFERENCES**

- [1] B. Citoni, F. Fioranelli, M. A. Imran, and Q. H. Abbasi, "Internet of Things and LoRaWAN-enabled future smart farming," *IEEE Internet Things Mag.*, vol. 2, no. 4, pp. 14–19, Dec. 2019, doi: 10.1109/IOTM.0001.1900043.

- [2] H. Tran-Dang, N. Krommenacker, P. Charpentier, and D.-S. Kim, "Toward the Internet of Things for physical Internet: Perspectives and challenges," *IEEE Internet Things J.*, vol. 7, no. 6, pp. 4711–4736, Jun. 2020, doi: 10.1109/JIOT.2020.2971736.

- [3] J. Sathishkumar and D. R. Patel, "Enhanced location privacy algorithm for wireless sensor network in Internet of Things," in *Proc. Int. Conf. Internet Things Appl. (IOTA)*, Pune, India, Jan. 2016, pp. 208–212, doi: 10.1109/IOTA.2016.7562723.

- [4] A. Yavari, D. Georgakopoulos, P. R. Stoddart, and M. Shafiei, "Internet of Things-based hydrocarbon sensing for real-time environmental monitoring," in *Proc. IEEE 5th World Forum Internet Things (WF-IoT)*, Limerick, Ireland, Apr. 2019, pp. 729–732, doi: 10.1109/WF-IoT.2019.8767320.

- [5] C. W. Chen, "Internet of video things: Next-generation IoT with visual sensors," *IEEE Internet Things J.*, vol. 7, no. 8, pp. 6676–6685, Aug. 2020, doi: 10.1109/JIOT.2020.3005727.

- [6] M. Liu, D. Li, Y. Zeng, W. Huang, K. Meng, and H. Chen, "Combinatorial-oriented feedback for sensor data search in Internet of Things," *IEEE Internet Things J.*, vol. 7, no. 1, pp. 284–297, Jan. 2020, doi: 10.1109/JIOT.2019.2944660.

- [7] Z. Sheng, H. Wang, C. Yin, X. Hu, S. Yang, and V. C. M. Leung, "Lightweight management of resource-constrained sensor devices in Internet of Things," *IEEE Internet Things J.*, vol. 2, no. 5, pp. 402–411, Oct. 2015, doi: 10.1109/JIOT.2015.2419740.

- [8] P. Zhang, Y. Liu, F. Wu, S. Liu, and B. Tang, "Low-overhead and high-precision prediction model for content-based sensor search in the Internet of Things," *IEEE Commun. Lett.*, vol. 20, no. 4, pp. 720–723, Apr. 2016, doi: 10.1109/LCOMM.2016.2521735.

- [9] T. Islam, S. C. Mukhopadhyay, and N. K. Suryadevara, "Smart sensors and Internet of Things: A postgraduate paper," *IEEE Sensors J.*, vol. 17, no. 3, pp. 577–584, Feb. 2017, doi: 10.1109/JSEN.2016.2630124.

- [10] T. Wang, H. Luo, W. Jia, A. Liu, and M. Xie, "MTES: An intelligent trust evaluation scheme in Sensor-Cloud-Enabled industrial Internet of Things," *IEEE Trans. Ind. Informat.*, vol. 16, no. 3, pp. 2054–2062, Mar. 2020, doi: 10.1109/TII.2019.2930286.

- [11] Y. Xu and A. Helal, "Scalable Cloud–Sensor architecture for the Internet of Things," *IEEE Internet Things J.*, vol. 3, no. 3, pp. 285–298, Jun. 2016, doi: 10.1109/JIOT.2015.2455555.

- [12] S.-H. Jo, H.-W. Cho, and H.-J. Yoo, "A fully reconfigurable universal sensor analog front-end IC for the Internet of Things era," *IEEE Sensors J.*, vol. 19, no. 7, pp. 2621–2633, Apr. 2019, doi: 10.1109/JSEN.2018.2890211.

- [13] W. Osamy, A. M. Khedr, and A. Salim, "ADSDA: Adaptive distributed service discovery algorithm for Internet of Things based mobile wireless sensor networks," *IEEE Sensors J.*, vol. 19, no. 22, pp. 10869–10880, Nov. 2019, doi: 10.1109/JSEN.2019.2930589.

- [14] G.-X. Liu, L.-F. Shi, and D.-J. Xin, "Data integrity monitoring method of digital sensors for Internet-of-Things applications," *IEEE Internet Things J.*, vol. 7, no. 5, pp. 4575–4584, May 2020, doi: 10.1109/JIOT.2020.2967504.

- [15] D. Kang et al., "256 Gb 3 B/Cell V-NAND flash memory with 48 stacked WL layers," *IEEE J. Solid-State Circuits*, vol. 52, no. 1, pp. 210–217, Jan. 2017, doi: 10.1109/JSSC.2016.2604297.

- [16] C. Kim et al., "A 512-gb 3-b/Cell 64-stacked WL 3-D-NAND flash memory," *IEEE J. Solid-State Circuits*, vol. 53, no. 1, pp. 124–133, Jan. 2018, doi: 10.1109/JSSC.2017.2731813.

- [17] D. Kang, K. Lee, S. Seo, S. Kim, J.-S. Lee, D.-S. Bae, D. H. Li, Y. Hwang, and H. Shin, "Generation dependence of retention characteristics in extremely scaled NAND flash memory," *IEEE Electron Device Lett.*, vol. 34, no. 9, pp. 1139–1141, Sep. 2013, doi: 10.1109/LED.2013. 2271351.

VOLUME 9, 2021 12207

- [18] K. Takeuchi, "Novel co-design of NAND flash memory and NAND flash controller circuits for sub-30 nm low-power high-speed solid-state drives (SSD)," *IEEE J. Solid-State Circuits*, vol. 44, no. 4, pp. 1227–1234, Apr. 2009, doi: 10.1109/JSSC.2009.2014027.

- [19] F. Wang, Y. Feng, X. Zhan, B. Chen, and J. Chen, "Implementation of data search in multi-level NAND flash memory by complementary storage scheme," *IEEE Electron Device Lett.*, vol. 41, no. 8, pp. 1189–1192, Aug. 2020, doi: 10.1109/LED.2020.3004989.

- [20] C.-S. Lin and L.-R. Dung, "A NAND flash memory controller for SD/MMC flash memory card," *IEEE Trans. Magn.*, vol. 43, no. 2, pp. 933–935, Feb. 2007, doi: 10.1109/TMAG.2006.888520.

- [21] T. Tanzawa, Y. Takano, K. Watanabe, and S. Atsumi, "High-voltage transistor scaling circuit techniques for high-density negative-gate channel-erasing NOR flash memories," *IEEE J. Solid-State Circuits*, vol. 37, no. 10, pp. 1318–1325, Oct. 2002, doi: 10.1109/JSSC.2002.803045.

- [22] W. H. Lee, D.-K. Lee, K.-S. Kim, K.-O. Ahn, and K.-D. Suh, "Mobile ion-induced data retention failure in NOR flash memory cell," *IEEE Trans. Device Mater. Rel.*, vol. 1, no. 2, pp. 128–132, Jun. 2001, doi: 10.1109/7298.956707.

- [23] K.-T. Wang, T.-S. Chao, T.-Y. Chiang, W.-C. Wu, P.-Y. Kuo, Y.-H. Wu, Y.-L. Lu, C.-C. Liao, W.-L. Yang, C.-H. Lee, T.-M. Hsieh, J.-C. Liou, S.-D. Wang, T.-P. Chen, C.-H. Chen, C.-H. Lin, and H.-H. Chen, "Physical mechanism of high-programming-efficiency dynamic-threshold sourceside injection in wrapped-select-gate SONOS for nor-type flash memory," *IEEE Electron Device Lett.*, vol. 30, no. 11, pp. 1206–1208, Nov. 2009, doi: 10.1109/LED.2009.2031601.

- [24] J. Paterson, "Adding analog, EPROM and EEPROM modules to CMOS logic technology: How modular?" in *IEDM Tech. Dig.*, Washington, DC, USA, 1989, pp. 413–416, doi: 10.1109/IEDM.1989.74310.

- [25] H.-C. Sung, T. Fu Lei, T.-H. Hsu, S. W. Wang, Y.-C. Kao, Y.-T. Lin, and C. S. Wang, "Novel single-poly EEPROM with damascene control-gate structure," *IEEE Electron Device Lett.*, vol. 26, no. 10, pp. 770–772, Oct. 2005, doi: 10.1109/LED.2005.856014.

- [26] J. Paterson, "Adding analog, EPROM and EEPROM modules to CMOS logic technology: How modular?" in *IEDM Tech. Dig.*, Washington, DC, USA, 1989, pp. 413–416, doi: 10.1109/IEDM.1989.74310.

- [27] Y. Wang, J. Tan, R. Mao, and T. Li, "Temperature-aware persistent data management for LSM-tree on 3-D NAND flash memory," *IEEE Trans. Comput.-Aided Design Integr. Circuits Syst.*, vol. 39, no. 12, pp. 4611–4622, Dec. 2020, doi: 10.1109/TCAD.2020.2982623.

- [28] Y. Wang, J. Huang, J. Yang, and T. Li, "A temperature-aware reliability enhancement strategy for 3-D charge-trap flash memory," *IEEE Trans. Comput.-Aided Design Integr. Circuits Syst.*, vol. 38, no. 2, pp. 234–244, Feb. 2019, doi: 10.1109/TCAD.2018.2808227.

- [29] Y. Luo, S. Ghose, Y. Cai, E. F. Haratsch, and O. Mutlu, "HeatWatch: Improving 3D NAND flash memory device reliability by exploiting selfrecovery and temperature awareness," in *Proc. IEEE Int. Symp. High Per*form. Comput. Archit. (HPCA), Vienna, Austria, Feb. 2018, pp. 504–517, doi: 10.1109/HPCA.2018.00050.

- [30] F. Karstens and S. Trippel, "Programmable trigger logic unit based on FPGA technology," *IEEE Trans. Nucl. Sci.*, vol. 52, no. 4, pp. 1192–1195, Aug. 2005, doi: 10.1109/TNS.2005.852669.

- [31] W. Kang Huang, F. J. Meyer, and F. Lombardi, "An approach for detecting multiple faulty FPGA logic blocks," *IEEE Trans. Comput.*, vol. 49, no. 1, pp. 48–54, Jan. 2000, doi: 10.1109/12.822563.

- [32] T. Tuan, A. Rahman, S. Das, S. Trimberger, and S. Kao, "A 90-nm low-power FPGA for battery-powered applications," *IEEE Trans. Comput. Aided Design Integr. Circuits Syst.*, vol. 26, no. 2, pp. 296–300, Feb. 2007, doi: 10.1109/TCAD.2006.885731.

- [33] Y. Yin, J. Yu, Y. Jiang, S. Li, J. Ren, G. Farrell, E. Lewis, and P. Wang, "Investigation of temperature dependence of microfiber coil resonators," *J. Lightw. Technol.*, vol. 36, no. 20, pp. 4887–4893, Oct. 15, 2018, doi: 10.1109/JLT.2018.2866000.

- [34] B. Zhao, W. Shi, D. Sun, and J. Tan, "Compensation network for temperature dependency and bandwidth expanding of magnetoelectric velocity sensor based on phase prediction compensator," *IEEE Sensors J.*, vol. 21, no. 2, pp. 1704–1714, Jan. 2021, doi: 10.1109/JSEN.2020.3016224.

- [35] S. Sen and R. M. Murray, "Temperature dependence of biomolecular circuit designs," in *Proc. 52nd IEEE Conf. Decis. Control*, Florence, Italy, Dec. 2013, pp. 1398–1403, doi: 10.1109/CDC.2013.6760078.

- [36] R. Wang, Y. T. Zhang, and J. Q. Yao, "Abnormal temperature dependence of mobility in a disordered system with traps: Experiment and theory," *IEEE Photon. J.*, vol. 7, no. 3, pp. 1–8, Jun. 2015, doi: 10.1109/JPHOT.2015.2423561.

**ZHUO HOU** was born in 1978. He received the B.E. and master's degrees from the North University of China, China, in 2001 and 2013, respectively. He is currently pursuing the Ph.D. degree with the Beijing Institute of Technology. As the first author or a responsible tutor, he has published more than 30 academic articles, including five retrieved by SCI and 11 retrieved by EI. His research direction is perception and detection technology. He is mainly engaged in the engineering

application and key technology research of dynamic parameter measurement. His research interests include high-speed target detection, preconditioning, acquisition, storage, and post-processing of dynamic parameters of multi-channel sensors. Recently, he won one-Second Prize of the National Defense Science and Technology Progress Award, one Monograph, nine invention patents, and more than ten software copyrights.

**HUIMIN CHEN** was born in 1973. He received the B.E. and Ph.D. degrees in physical electronics from the Beijing Institute of Technology (BIT), in 1998 and 2005, respectively. He is currently an Associate Professor with the Department of Armament Science and Technology, BIT. He has presided over, more than ten namely, the National Natural Fund, the Field Fund, the Key Laboratory Fund, and the Enterprise Horizontal Projects. He has published more than 40 related articles and

more than 30 articles have been included by SCI and EI, and has authorized 12 invention patents and more than 20 software copyrights. He also published the Laser Fuze Technology and the Short Range Laser Detection Technology. His main research interests include short-range laser detection and information processing, laser anti-jamming, target characteristics, and other aspects of research. He is the Youth Editorial Board Member of *Infrared and Laser Engineering* and *Aviation Weapons*.

JIAHAO DENG was born in 1958. He received the M.E. and Ph.D. degrees from the Beijing Institute of Technology (BIT), in 1985 and 1998, respectively. In 1985, he joined BIT. From 2003 to 2004, he was a Postdoctoral Researcher in time-frequency signal processing with the Queensland University of Technology. He is the Monographer on New Magnetic Detection Technology and Principles and Applications of Capacitance Detection. He is currently a Professor with the School of

Mechatronic Engineering, BIT. His main research interests include sensing, signal processing, and control technology.

**ZUODONG DUAN** was born in 1989. He received the B.E. and master's degrees from the College of Information Science and Engineering, Shandong Agricultural University, Tai'an, China, in 2014 and 2016, respectively. He is currently pursuing the Ph.D. degree with the Beijing Institute of Technology. His research interests include deep learning applications in computer vision and robotics, with specific interests in crowd analysis, drone-based vision, and SLAM.

12208 VOLUME 9, 2021