Received September 20, 2020, accepted October 12, 2020, date of publication October 16, 2020, date of current version November 18, 2020.

Digital Object Identifier 10.1109/ACCESS.2020.3031723

# 2:1 Injection-Locked Frequency Dividers Using Multi-Resonance Spiral-Inductor Resonator

# SHENG-LYANG JANG, (Senior Member, IEEE), HO-CHANG LEE<sup>(D</sup>, AND MIIN-HORNG JUANG, (Senior Member, IEEE)

Department of Electronic Engineering, National Taiwan University of Science and Technology, Taipei 106, Taiwan, R.O.C.

Corresponding author: Ho-Chang Lee (d10502006@mail.ntust.edu.tw)

This work was supported in part by the Department of Electronic Engineering, National Taiwan University of Science and Technology, Taipei, Taiwan, R.O.C.

**ABSTRACT** This article describes two low-power and wide locking range capacitive cross-coupled divideby-2 injection-locked frequency dividers (ILFDs) implemented in TSMC standard 0.18  $\mu$ m processes. The ILFDs are based on a differential VCO with one direct injection MOSFET for coupling the external signal to the spiral-inductor resonator. The first/second ILFD uses five/three on-chip inductors in series with parasitic varactors as a multi-resonance resonator. Three measured features are identified. The ILFDs have two non-overlapped locking ranges at low input power, they have two free-running oscillation frequency bands, and the frequency tuning versus gate bias of cross-coupled transistors shows the frequency tuning hysteresis. The power consumption of the 5-L ILFD core is 5.43 mW and the locking range is 6.07 GHz (116.395%) from 2.18 to 8.25 GHz at injection power  $P_{inj} = 0$  dBm. At the supply voltage of 1.1 V, the divider's freerunning oscillation frequency is 3.13 GHz. The die area of the 2<sup>nd</sup> chip is 0.865 × 0.872 mm<sup>2</sup>. The locking range at low input power is larger for the 5-L resonator ILFD.

**INDEX TERMS** Varactor-less divide-by-2 injection-locked frequency divider, frequency tuning hysteresis, distributed resonator, tunable resonator.

# I. INTRODUCTION

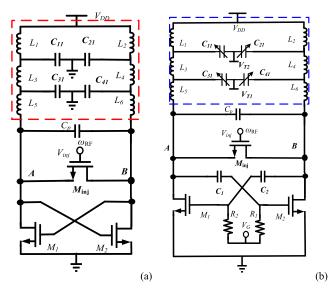

The study of LC divide-by-2 injection-locked frequency divider (ILFD) [1] attracts intensive attention because they are widely used to process frequency signal. The bottom-series injection  $\div 2$  ILFD [2] has limited locking range because the injection signal experiences a large tail capacitance to reduce the injection efficiency and the direct injection ILFD [3], [4] becomes the main stream of ILFD design. The often-cited ILFD design parameters cover phase noise, locking range and power consumption. The RF locking range can be enhanced through the resonator modification, with which the ILFD is robust to the inevitable shift of the center operating frequency caused by the process variations and supply voltages. Fig. 1(a) shows a direct-injection ILFD using distributed LC network [5] by reducing the capacitance in shunt with injection FET [6]. The distributed LC network consists of inductors  $L_1$ - $L_6$ , distributed capacitors  $(C_{11} \sim C_{41})$  and capacitor  $C_p$ . All passive elements are

The associate editor coordinating the review of this manuscript and approving it for publication was Michail Kiziroglou<sup>D</sup>.

lumped and tank resonant frequency is un-tunable. Injection FETs are also distributed to in shunt the pairs of inductors [7], the measured and simulated locking range shows singleband-like locking range. A dual-resonator ILFD [8], [9] with varactor tuning leads to wider locking range because the two locking ranges associated with the two resonant frequencies can be merged to a single-band locking range. Fig. 1(b) shows a triple-resonance resonator ILFD with varactor tuning voltages  $(V_{T1}, V_{T2})$  [10]. Triple-resonance ILFD is an extension of dual-resonance ILFD. Some publications about distributed resonator ILFD lack experimental justification because process drifting may lead to incorrect conclusion. The ILFD with varactor tuning enables the experimental verification of the multi-resonance effect on the locking range by looking at the performance variation with tuning bias. In addition,  $V_{\rm G}$ in Fig. 1(b) is an external voltage, which is helpful to vary the ILFD property.

For the circuit in Fig. 1(b), depending on the size of varactors ( $C_{11} \sim C_{41}$ ), two types of ILFD can be identified. In type 1, the size is small, as varactor capacitance increases, the oscillation frequency decreases and no dual-band tuning

FIGURE 1. Schematics of the divide-by-2 ILFDs with distributed resonator.

range exists. In type 2, the varactor size is large, as varactor capacitance increases, the oscillation frequency switches frequency bands at certain tuning voltage from high-band to low-band and dual-band tuning range exists. A dualresonance *LC* ILFD using the latter design shows that the tuning range can have two frequency bands while tuning the varactor control voltage [11]. A sharp transition in free-run oscillation frequency can be found and it is a behavior in forbidden oscillation frequency region. The net locking range can span over all the ILFD self-oscillation frequencies. The previous multi-resonance 2:1 ILFDs use analog varactors to tune the resonant frequencies for wide-band optimization and experimental verification.

This article designs wide-locking range varactor-less  $\div 2$ ILFDs with a distributed spiral resonator. The circuits use five or three on-chip inductors to exploit the effect of distributed spiral resonator as a multi-resonance resonator. The distinct of this work and others are no analog capacitors and varactors are embedded to the resonator. At low RF injection power, the two ILFDs show two measured non-overlapped locking ranges, a property of dual-the gate with bias-controlled varactor. To confirm that the ILFDs have two resonant frequencies, the gate bias of the capacitive cross-coupled FETs is used to change the ILFD oscillation frequency and the free-running oscillation frequency shows the sharp transition in frequency tuning effect and frequency tuning hysteresis [11], [12], which is an effect of dual-resonance resonator with bias-controlled varactor. At injection power of 0 dBm, the designed 5-L ÷2ILFD has one-band locking range from 2.18 GHz to 8.25 GHz. This indicates multi spiral inductors can be used to construct distributed resonator for wideband locking range design. Following this line, the ILFD circuit [13] uses only one on-chip inductor can have multiband locking ranges, because the single inductor is a multiresonance distributed resonator.

#### II. CROSS-COUPLED 2:1 ILFD WITH 5-INDUCTORS

# A. CIRCUIT DESIGN OF THE 5-L 2:1 ILFD

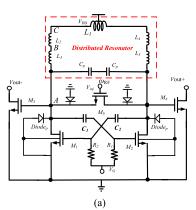

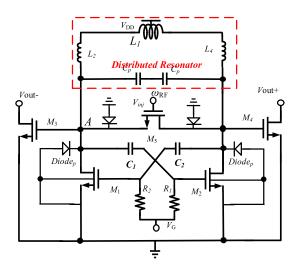

Fig. 2(a) is a circuit evolved from Fig. 1(b) by removing  $(C_{11} \sim C_{41})$  and depicts the test  $\div 2$  ILFD circuit with inductors  $L_1$ -  $L_5$  and a parasitic active capacitor  $C_p$  as the resonator. The switching transistors  $(M_1, M_2)$  in conjunction with capacitors  $(C_1, C_2)$  and resistors  $(R_1, R_2)$  are used to generate the negative resistance to compensate for the LC tank loss. FETs  $(M_3, M_4)$  are ILFD output buffers and  $M_5$ with a dc gate bias Vinj is an injection mixer. The parasitic diodes explicitly drawn in Fig. 2(a) are bias-dependent. As  $V_{\rm G}$  increases, the ILFD-core voltage swing increases, the average capacitance of  $C_p$  decreases accordingly. Based on the lumped inductor model, the above ILFD has one frequency band and one locking range. If the five inductors are remodeled to include the parasitic capacitors, the resonator is a multi-resonance resonator. Fig. 2(b) shows the differential 5-L resonator model for the ILFD. One half circuit model uses three single- $\pi$  inductors in series, the parasitic MOSFET varactor  $C_p$  and channel resistance  $R_i$  of FETs are added to the resonator. The multi-resonance resonator may have two resonant frequencies and the ILFD can have two measured locking ranges associated with two resonant frequencies. Because of parasitic MOSFET varactors, varying bias-dependent oscillation voltage swing changes the average capacitance and the oscillation frequency. The mathematical formulation of locking range [14] for single-band ILFD with a parallel *RLC* resonator has been derived before and it can be extended to a dual-resonance ILFD circuit.

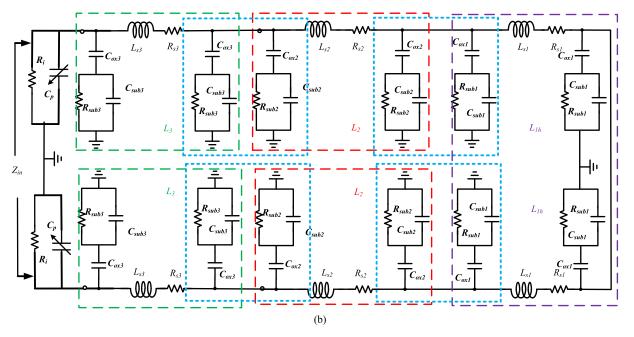

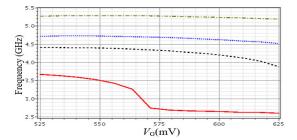

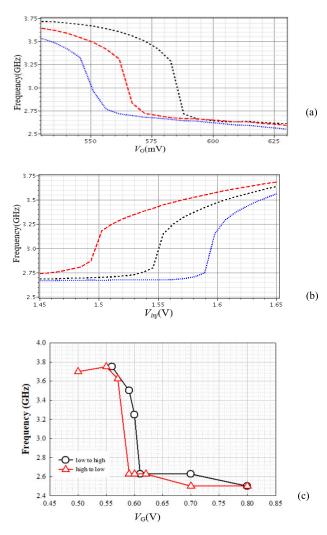

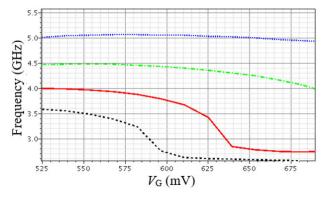

Fig. 3 depicts the simulated free-run oscillation frequency  $f_{\rm osc}$  of the prelayout divide-by-2 ILFD. The tuning range of the designed ILFD shows dual-band tuning property. Increasing  $V_{\rm G}$  leads to lower  $f_{\rm osc}$ . Removing some inductors increases  $f_{osc}$ , but the dual-band behavior disappears in the simulated voltage region. Fig. 4(a) shows simulated oscillation frequency  $f_{osc}$  of the divide-by-2 ILFD versus  $V_{\rm G}, f_{\rm osc}$  decreases as  $V_{\rm G}$  increases or  $V_{\rm inj}$  decreases because of larger voltage swing. At  $V_{inj} = 1.6$  V,  $f_{osc}$  decreases from 3.7 GHz to 2.6 GHz as  $V_{\rm G}$  increases from 0.53 V to 0.65 V. Fig. 4(b) also shows simulated  $f_{\rm osc}$  decreases as  $V_{\rm G}$ increases or Vini decreases because of larger voltage swing. At  $V_{\rm G}$  =0.575 V~0.75 V, no dual band frequency tuning is simulated and no high-band resonant frequency is present. Fig. 4(c) shows simulated oscillation frequency  $f_{osc}$  of the pre-layout divide-by-2 ILFD, it shows frequency tuning hysteresis [11], [12], which is supported by the experimental data. The frequency-band transition voltage  $V_{\rm G}$  is lower than the opposite case while  $V_{\rm G}$  is tuned from high value to low value because the average capacitance is smaller at higher  $V_{\rm G}$ . At  $V_{\rm DD}$  =1.1 V,  $V_{\rm G}$  =0.6 V,  $V_{\rm inj}$  =1.65 V, the simulated locking range at  $P_{inj} = -15$  dBm is from 4.5 GHz to 9.0 GHz, which is divided to three regions. The high-band is from 7.7 GHz to 9.0 GHz, the low-band is from 4.5 GHz to 6.4 GHz, and in between the above regions, the ILFD is locked to the input signal but the output contains other smaller unrelated frequency signal. The simulated locking range at

FIGURE 2. (a) Schematic of the 5-L divide-by-2 ILF (b) Differential 5-L resonator model of resonator with lumped elements.

**FIGURE 3.** Simulated oscillation frequency  $f_{osc}$  of the prelayout divide-by-2 ILFD. Red: designed one. Black: without 1.8 nH  $L_1$ . Blue: without 1.27 nH  $L_2$ . Green: without 1.81 nH  $L_3$ .  $V_{DD} = 1.1$  V and  $V_{ini} = 1.5$  V.

$P_{\text{inj}} = 0$  dBm is from 4.3 GHz to 10.3 GHz. No concurrent signals is simulated.

#### B. EXPERIMENTAL OF THE 5-L 2:1 ILFD

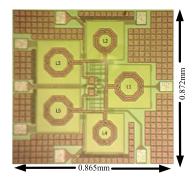

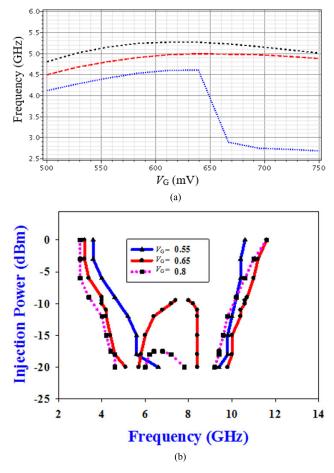

The *LC* tank  $\div$ 2 ILFD has been designed and fabricated in the TSMC 0.18  $\mu$ m SiGe BiCMOS technology. The die output buffers and input/output pads is  $0.865 \times 0.872 \text{ mm}^2$ . At  $V_{\text{DD}} = 1.1 \text{ V}$  and  $V_{\text{inj}} = 1.8 \text{ V}$ ,  $V_{\text{G}} = 0.7 \text{ V}$ , the current and power consumption of the ILFD-core are 4.94 mA and 5.434 mW respectively. Fig. 6(a) shows the input sensitivity plot for the  $\div 2$  ILFD

micrograph is shown in Fig. 5. The die size including the

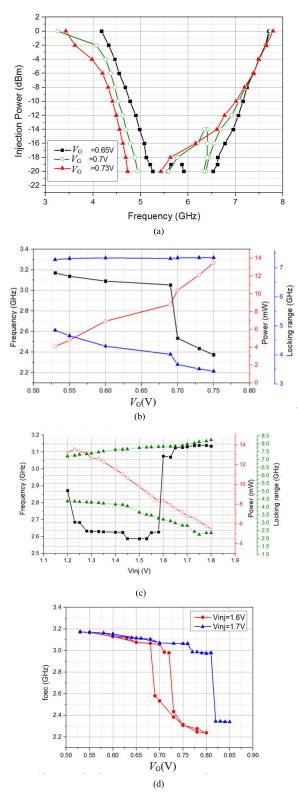

biased at  $V_{\text{DD}} = 1.1$  V,  $V_{\text{inj}} = 1.5$  V and  $V_{\text{G}} = 0.65$ , 0.7, 0.73 V. At  $V_{\text{inj}} = 1.8$  V and  $V_{\text{G}} = 0.7$  V, an external injected signal power  $P_{\text{inj}}$  of 0 dBm provides a locking range 6.07 GHz (116.395%) from 2.18 to 8.25 GHz. The maximum FOM is 21.42, and it is equal to (locking range percentage)/(power dissipation in mW). At low injection power, dual-band locking ranges are measured. At  $V_{\text{G}} = 0.65$  V and  $P_{\text{inj}}$  of -12 dBm provides a locking range 2.2 GHz from 4.9 to 7.1 GHz. Fig. 6(b) shows the locking range, oscillation frequency, and power consumption dependence on  $V_{\text{G}}$  at  $V_{\text{DD}} = 1.1$  V and  $V_{\text{inj}} = 1.5$  V. The power decreases with decreasing  $V_{\text{G}}$  because of small channel conductance. An abrupt oscillation frequency transition is found around

**FIGURE 4.** Simulated oscillation frequency  $f_{osc}$  of the prelayout divide-by-2 ILFD. (a).  $V_{DD} = 1.1$  V and  $V_{inj} = 1.6$ (black), 1.5(red), 1.4 V (blue).  $V_G = 0.7$ V. (b).  $V_{DD} = 1.1$  V and  $V_{inj} = 1.6$ V.  $V_G = 0.575$ (black), 0.585 (red), 0.565 V (blue). (c) Simulated oscillation frequency  $f_{osc}$  of the pre-layout divide-by-2 ILFD.  $V_{DD} = 1.1$  V,  $V_{inj} = 1.65$  and  $V_{buffer} = 0.8$  V.

FIGURE 5. Chip micrograph for the 5-L divide-by-2 ILFD.

$V_{\rm G}$  =0.7 V while tuning  $V_{\rm G}$ . The varactor-less ILFD has two operation frequency bands. If the five inductors in Fig. 2 are used as lumped inductors, the oscillation frequency has only one frequency band, even the bias voltages are varied to vary the capacitances of varactors. Therefore the parasitic capacitance of inductors must be accounted for. If no parasitic MOSFET varactor is present, the oscillation frequency will not have abrupt frequency change while tuning bias to change oscillation voltage swing. So tuning  $V_{\rm G}$  to 0.7 V the ILFD can exploit the overlapping of locking ranges. Fig. 6(b) shows as VG increases from 0.7 V, the ILFD free-runs at low-band, lowband-end locking range increases, while high-ended locking range changes little. Fig. 6(c) shows measured tuning range, power consumption and locking range at  $P_{inj} = 0$  dBm versus  $V_{inj}$ . Around  $V_{inj} = 1.6$  V, the circuit switches the frequency band. Both Fig. 6(b) and Fig. 6(c) show dual-band tuning range. Fig. 6(d) shows the measured tuning curve by tuning  $V_G$  in the increasing voltage and in the decreasing voltage directions. Oscillation frequency  $f_{osc}$  is a function of  $V_{\rm G}$  and  $V_{\rm inj}$  and the tuning range shows the hysteresis effect [11], [12], where the oscillation frequency depends on the direction of bias tuning direction. This is also an evidence that the ILFD uses a multi-resonance resonator. At  $V_{\rm G}$  =0.7 V and  $V_{inj} = 1.6V$  two resonant modes are possible and they depend on the voltage tuning history. At  $V_{\rm G}$  =0.7 V and  $V_{inj} = 1.7$  V only one frequency tuning curve is measured because smaller voltage swing.

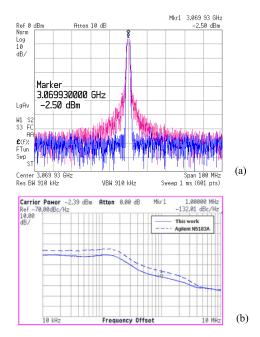

Fig. 7(a) describes two measured output spectra from the free-run frequency divider and the locked  $\div 2$  ILFD. The locked output spectrum shows a lower side-band output power and the locked circuit follows the injection source in phase noise. Fig. 7(b) plots two phase noises measured from the injection-locked circuit and the injection source. At the frequency offset of 1 MHz the locked phase noise shows - 132.01 dBc/Hz, while the phase noise of -126.36 dBc/Hz is from the injection-reference, the locked phase noise is smaller than the injection signal by 5.65 dBc/Hz.

#### III. CROSS-COUPLED 2:1 ILFD WITH 3-INDUCTORS

#### A. CIRCUIT DESIGN OF THE 3-L 2:1 ILFD

Three spiral inductors may be configured with a property similar to a resonator with five inductors for a dual-resonance ILFD. The *LC* tank ILFD shown in Fig. 8 uses single capacitive cross-coupled (CC) pair and three on-chip inductors as the resonator. The *LC* resonator comprises inductors  $L_1$ ,  $L_2$  and  $L_3$  and parasitic varactor  $C_p$ . The parasitic varactors include source-body diode and drain-body diodes of  $M_5$ , and drain-body diodes and gate-source capacitors of switching FETs  $M_1$ ,  $M_2$ . The injection signal is ac-applied to the gate of injection FET  $M_5$  with dc gate bias  $V_{inj}$ .

Fig. 9(a) shows simulated pre-layout oscillation frequency versus  $V_{\rm G}$ . Case 1 and case 2 show one tuning range of reference circuits by deleting  $L_1$  and reducing N respectively. Increasing the number of fingers N of FETs  $M_1$ ,  $M_2$  leads to low-band frequency at  $V_{\rm G}$  =0.75 V. As N increases, the oscillation frequency at  $V_{\rm G}$  =0.55 V decreases because  $C_{\rm p}$ increases. Fig. 9(a) shows dual-band tuning range similar to Fig. 3. Tuning FET and inductor size leads to dual-band tuning range. Fig. 9(b) shows the simulated sensitivity plot

**FIGURE 6.** (a) Measured input sensitivity.  $V_{DD} = 1.1 \text{ V}$  and  $V_{inj} = 1.5 \text{ V}$ .  $V_{buffer} = 0.8 \text{ V}$ . (b) Measured locking range at  $P_{inj} = 0 \text{ dBm}$ , power consumption, oscillation frequency vs  $V_{inj}$ .  $V_{DD} = 1.1 \text{ V}$  and  $V_{inj} = 1.5 \text{ V}$ . (c) Measured tuning range, power consumption and locking range at  $P_{inj} = 0 \text{ dBm}$  versus  $V_{inj}$ .  $V_{DD} = 1.1 \text{ V}$ ,  $V_b = 0.8 \text{V}$ , and  $V_G = 0.7 \text{ V}$ (d). Measured tuning range vs  $V_G$ .  $V_{DD} = 1.1 \text{ V}$  and  $V_{inj} = 1.6$ , 1.7 V.

**FIGURE 7.** (a) Measured spectra of the free-running and locked ILFD. (b). Measured phase noises of the injection-reference and locked  $\div 2$  ILFD.  $V_{DD} = 1.1$  V and  $V_{inj} = 1.5$  V,  $V_G = 0.7$  V.  $P_{inj} = 0$  dBm. Injection signal  $f_{inj} = 6.14$  GHz.

FIGURE 8. Schematic of the designed 3-LILFD.

using the foundry-supplied inductor models. The threshold voltage  $V_{\text{TH}}$  of  $M_5$  is 0.75 V and  $M_5$  is dc-biased below and near the threshold voltage. The  $V_{\text{TH}}$  of  $M_1$  is 0.53 V and  $M_1$  is dc biased above threshold voltage. At  $V_{\text{G}} = 0.65$  V, an external injected signal power of 0 dBm provides a singleband locking range 7.4 GHz from 3.2 GHz to 11.6 GHz. An external injected signal power of -12 dBm provides a lowband locking range 2.2 GHz from 4.2 GHz to 6.4 GHz and a high-band locking range 2.0 GHz from 8.4 GHz to 10.4 GHz.

At  $V_{\rm G}$  =0.55 V, a single-band locking range is found. At  $V_{\rm G}$  =0.55/0.65/0.8V the free-running oscillation

**FIGURE 9.** (a) Simulated pre-layout oscillation frequency vs  $V_{\rm G}$ .  $V_{\rm DD}$  =1.15 V and  $V_{\rm inj}$  =1.75 V. Black dashed  $L_1$  =0, N=16. Red solid, N=10. Blue dashed, N=16. N: number of MOSFET fingers. (b) Simulated pre-layout sensitivity.  $V_{\rm DD}$  =1.15 V,  $V_{\rm G}$  =0.55, 0.65, 0.8 V, and  $V_{\rm ini}$  =1.75 V.

frequency is  $f_{\rm osc} = 4.4/2.75/2.6$  GHz. As  $V_{\rm G}$  increases, the voltage swing increases,  $f_{\rm osc}$  decreases, and the oscillation frequency shows dual-band behavior because capacitor  $C_{\rm p}$  is a tunable parasitic varactor.

#### B. EXPERIMENTAL OF THE 3-L 2:1 ILFD

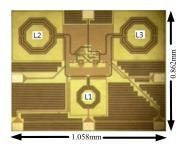

The *LC* tank 3-L 2:1 ILFD has been designed and fabricated in the TSMC 0.18  $\mu$ m CMOS technology. The chip area of the 0.18  $\mu$ m ILFD shown in Fig. 10 is 1.058  $\times$  0.862 mm<sup>2</sup>,

FIGURE 10. Chip micrograph for the 3-L 2:1 ILFD.

it uses three symmetric octagonal inductors. In the divideby-2 mode, the gate-source overdrive of  $M_5$  is close to the threshold voltage for maximum locking range and the mixer is a linear mixer.

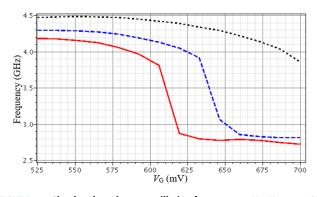

Fig. 11(a) shows the measured tuning range versus  $V_{ini}$  and  $V_{\rm G}$ . The low-band and high-band operation can be obtained by tuning  $V_{ini}$  and  $V_G$ . Low power consumption is obtained at low  $V_{\rm G}$  and by tuning  $V_{inj}$ . Fig. 11(b) shows measured tuning range at  $V_{\text{DD}} = 1.2$  V and  $V_{\text{ini}} = 1.7$  V for the 2<sup>nd</sup> ILFD. It shows frequency hysteresis loop, that is, the tuning curves are different while V<sub>G</sub> is tuned from 0 V to 1 V and from 1 V to 0 V. The high-band oscillation frequency is about 3.3 GHz and the low-band oscillation frequency is 2.4 GHz. As inductors and parasitic capacitors are not tunable in first order approximation, the tuning range is related to the parasitic varactors in MOSFETs. Increasing  $V_{\rm G}$  enlarges voltage swing and varies the average capacitance of parasitic MOSFET varactor. The drain-body and source-body diodes of  $M_3$  and the drain-body diodes of  $M_1$  and  $M_2$  are the main varactors. Gate-source and gate-body capacitors of MOSFETs form the secondary parasitic varactors

**FIGURE 11.** (a) Measured locking range versus  $V_{inj}$  or  $V_G$ .  $V_{DD} = 1.15$  V and  $V_{buffer} = 0.8$ V. (b) Measured tuning range.  $V_{DD} = 1.2$  V and  $V_G = 0.73$  V,  $V_{inj} = 1.7$  V.  $V_{buffer} = 0.8$  V.  $\div 2$  ILFD.

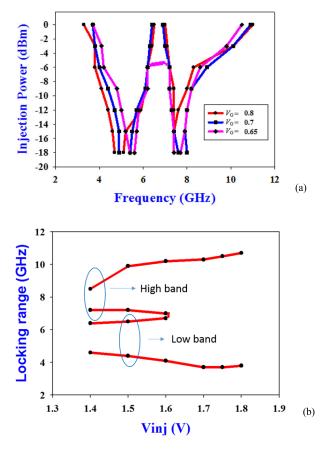

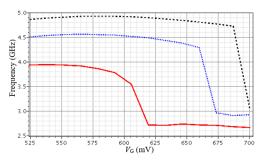

Fig. 12(a) shows the measured input sensitivity plot for the divide-by-2 ILFD biased at  $V_{DD} = 1.15$  V and three  $V_{G}s$ .  $V_{G}$  can be used to optimize the ILFD performance. At  $V_{G} = 0.65$ V, an external injected signal power of 0 dBm

**FIGURE 12.** (a) Measured input sensitivity.  $V_{DD} = 1.15$  V and  $V_{inj} = 1.75$  V. (b) Measured locking range.  $V_{DD} = 1.15$  V and  $V_G = 0.65$  V.  $P_{inj} = 0$  dBm.

provides a locking range 6.8 GHz (95.77%) from 3.7 GHz to 10.5 GHz. The current and power consumption of the ILFD without buffers are 8.3 mA and 9.545 mW respectively. At  $V_{\rm G}$  =0.7V, an external injected signal power of 0 dBm provides a low-band locking range 2.7 GHz (53.46%) from 3.7 GHz to 6.4 GHz and a high-band locking range 4 GHz (44.9%) from 6.9 GHz to 10.9 GHz. At  $V_{\rm G} = 0.8$ V, an external injected signal power of 0 dBm provides a low-band locking range 3.2 GHz (65.3%) from 3.3 GHz to 6.5 GHz and a highband locking range 4 GHz (44.4%) from 7 GHz to 11 GHz. Fig. 12(b) shows the locking range at  $P_{inj} = 0$  dBm as a function of  $V_{inj}$ . As  $V_{inj}$  increases both the high band and low-band locking ranges increases to merge the dual-band locking ranges into a signal-band locking range. At  $V_{inj}$  < 1.6 V the ILFD has dual locking ranges because injection mixer conversion gain decreases as Vini decreases. Table 1 is the performance comparison of ÷2 ILFDs. These ILFDs show good performance.

#### **IV. SIMULATION OF OTHER 2:1 ILFDs**

The section simulates an ILFD with 1-L resonator and 2-L resonator. The simulated 1-L ILFD circuit is the same as Fig. 2(a), except it uses only inductor  $L_1$ . Fig. 13 shows

TABLE 1. Performance comparison of CMOS ÷2 LC ILFDs.

| ref    | Pin<br>(dB<br>m) | V <sub>DD</sub> (V)/<br>Pdiss(mW) | FOM    | Locking range<br>GHz |

|--------|------------------|-----------------------------------|--------|----------------------|

| [1]    | 0                | 0.75/4.5                          | 8.52   | 3.14~4.63(38.35%)    |

| [8]    | 0                | 1.5/12.32                         | 8.56   | 3~9.7(105.51%)       |

| [15]   | 0                | 1.5/7.65                          | 8.55   | 7.3~14.4(65.44%)     |

| [16]   | 0                | 0.9/16.56                         | 5.6    | 3.7~10.1(92.75%)     |

| [17]   | 0                | 1.8/4.8                           | 5.23   | 20.1~25.86(25.1%)    |

| [18]   | 10               | 0.9/16.56                         | 5.6    | 3.7~10.1(92.7%)      |

| This5L | 0                | 1.1/5.434                         | 21.42  | 2.18~8.25(116.4%))   |

| This3L | 0                | 1.15/ 6.785                       | 14.116 | 3.7~10.5(95.77%)     |

**FIGURE 13.** Simulated pre-layout oscillation frequency vs  $V_{\rm G}$ .  $V_{\rm DD}$  =1.1 V and  $V_{\rm inj}$  =1.6 V.  $V_{\rm G}$  =0.525~0.675V. Inner radius=75  $\mu$ m, L=7.67nH (black dotted), Inner radius =65  $\mu$ m, L=6.35 nH (solid red), Inner radius=55  $\mu$ m, L=5.2 nH (green dash), Inner radius=45  $\mu$ m, L=4.17 nH (blue dot). 1-L ILFD.

**FIGURE 14.** Simulated pre-layout oscillation frequency vs  $V_{G}$ .  $V_{DD}$  =1.1 V,  $V_{inj}$  =1.6 V and  $V_{G}$  =0.525~0.7V. Inner radius=55  $\mu$ m, L=5.2 nH. W=90  $\mu$ m (black dash). W=112.5  $\mu$ m (blue dash). W=135  $\mu$ m (solid line). 1-L ILFD.

simulated pre-layout oscillation frequency versus  $V_{\rm G}$ . The ILFDs with L=7.67nH and L=6.35 nH shows dual-band tuning range. At L=6.35 nH,  $V_{\rm DD}$  =1.1 V and  $V_{\rm inj}$  =1.6 V, the locking range at  $P_{\rm inj}$  =0 dBm at  $V_{\rm G}$  =0.55V is from 4.2 GHz to 10.1 GHz; the locking range at  $V_{\rm G}$  =0.625V is from 4 GHz to 11.1 GHz; the locking range at  $V_{\rm G}$  =0.75V is from 3.9 GHz to 11.6 GHz. At L=6.35 nH,  $V_{\rm DD}$  =1.1 V and  $V_{\rm inj}$  =1.3 V, the locking range at  $V_{\rm G}$  =0.55V is from 4.6 GHz to 10.2 GHz; the locking range at  $V_{\rm G}$  =0.625V is from 4.4 GHz to 10.5 GHz; the locking range at  $V_{\rm G}$  =0.75V

**FIGURE 15.** Simulated pre-layout oscillation frequency vs  $V_{G}$ .  $V_{DD}$  =1.1 V,  $V_{inj}$  =1.6 V and  $V_{G}$  =0.525~0.7V. Inner radius=75  $\mu$ m, L=2.62nH (black dash), Inner radius=85  $\mu$ m, L=3.05 nH (blue dot), Inner radius=105  $\mu$ m, L=3.75 nH (red solid). 2-L ILFD. 3-turn inductor.

is from 4.0 GHz to 10.4 GHz. Fig. 14 shows simulated prelayout oscillation frequency versus  $V_{\rm G}$ . The channel width of switching transistors  $(M_1, M_2)$  is changed. At W=90  $\mu$ m,  $f_{\rm osc}$  decreases with  $V_{\rm G}$  and it shows only frequency band. At W=112.5  $\mu$ m,  $f_{osc}$  decreases with  $V_{G}$  and it shows dual frequency bands at 4.29 GHz and 2.8 GHz, the band transition  $V_{\rm G}$  is around 0.65 V. At W=135  $\mu$ m,  $f_{\rm osc}$  decreases with  $V_{\rm G}$ and it shows dual frequency bands at 4.18GHz and 2.74 GHz, the band transition V<sub>G</sub> is around 0.619 V. Increasing channel width increases the size of  $C_p$ , and increases the voltage swing to increases the value of  $C_p$ . The simulated 2-L ILFD circuit is the same as Fig. 2(a), except it uses only inductors  $L_3$ and  $L_5$ . Fig. 15 shows simulated pre-layout oscillation frequency versus  $V_{\rm G}$  for the 2-L ILFD. As inductance decreases, the oscillation frequency becomes higher and the band transition voltage V<sub>G</sub> shifts to higher voltage.

#### **V. CONCLUSION**

This article designs varactor-less  $\div$ 2 ILFDs with wide locking range and high FOM. The experimental ILFDs use either five or three on-chip inductors in series to exhibit multi-resonance locking ranges. Despite no analog varactor and varactor tuning, gate bias of switching FETs can vary the free-running ILFD oscillation frequency and the frequency tuning hysteresis effect is measured. The experimental of tuning hysteresis, dual-band oscillation frequency and dual-band locking range proves that the parasitic capacitors in inductors and FETs concurrently enable the 2:1 dual-resonance resonator ILFD function and frequency tuning is used to optimize the locking range. The 5-L ILFD shows wide locking range at -12 dBm input power. The ILFD design approach with multi-inductors and without varactors is simple and high valuable for reliable  $\div 2$  frequency divider design. By varying the FET and inductor sizes, 1-L or 2-L resonator ILFD also shows dual-band tuning range, this is important while it is often ignored in circuit operation interpretation.

#### ACKNOWLEDGMENT

The authors want to thank the Staff of the Chip Implementation Centre for the chip fabrication supports, and Xuan-You Han (2015) for chip2 design and measurement, and Cheng-Lin Li (2016) for chip1 design, and Jia Chi Weng (2017) for chip1 measurement.

### REFERENCES

- [1] Y.-H. Chuang, S.-H. Lee, R.-H. Yen, S.-L. Jang, J.-F. Lee, and M.-H. Juang, "A wide locking range and low voltage CMOS direct injection-locked frequency divider," *IEEE Microw. Wireless Compon. Lett.*, vol. 16, no. 5, pp. 299–301, May 2006.

- [2] H. Wu and A. Hajimiri, "A 19GHz 0.5mW 0.35µm CMOS frequency divider with shunt-peaking locking-range enhancement," in *IEEE ISSCC Dig. Tech. Papers*, Feb. 2001, pp. 412–413.

- [3] M. Tiebout, "A CMOS direct injection-locked oscillator topology as high-frequency low-power frequency divider," *IEEE J. Solid-State Circuits*, vol. 39, no. 7, pp. 1170–1174, Jul. 2004.

- [4] K. Yamamoto and M. Fujishima, "70GHz CMOS harmonic injectionlocked divider," in *IEEE ISSCC Dig. Tech. Papers*, Feb. 2006, pp. 2472–2481.

- [5] C.-C. Wang, C.-Z. Chen, and Y.-S. Lin, "CMOS direct injection-locked frequency divider (3.55 mW 80 GHz) with 26.3% locking range using distributed LC tank and body bias techniques," *Microw. Opt. Technol. Lett.*, vol. 53, no. 11, pp. 2694–2697, Nov. 2011.

- [6] L. C. Cho, K. H. Tsai, C. C. Hung, and S. I. Liu, "93.5~109.4GHz CMOS injection-locked frequency divider with 15.3% locking range," in *Proc. IEEE Symp. VLSI Circuits*, Jun. 2008, pp. 86–87.

- [7] A. Imani and H. Hashemi, "Distributed injection-locked frequency dividers," *IEEE J. Solid-State Circuits*, vol. 52, no. 8, pp. 2083–2093, Aug. 2017.

- [8] S.-L. Jang, Y.-J. Chen, C.-H. Fang, and W. C. Lai, "Enhanced locking range technique for frequency divider using dual-resonance RLC resonator," *Electron. Lett.*, vol. 51, no. 23, pp. 456–458, Mar. 2015.

- [9] S.-L. Jang, W.-C. Lai, G.-Y. Lin, and C. Y. Huang, "Injection-locked frequency divider with a resistively distributed resonator for wide-lockingrange performance," *IEEE Trans. Microw. Theory Techn.*, vol. 67, no. 2, pp. 505–517, Feb. 2019.

- [10] S.-L. Jang, W.-C. Cheng, and C.-W. Hsue, "Triple-resonance RLC-tank divide-by-2 injection-locked frequency divider," *Electron. Lett.*, vol. 52, no. 8, pp. 624–626, 2016.

- [11] S.-L. Jang, S.-J. Jian, and C.-W. Hsue, "Frequency tuning hysteresis of a dual-resonance divide-by-three cross-coupled injection-locked frequency divider," *IET Microw., Antennas Propag.*, vol. 12, no. 8, pp. 1302–1309, 2018.

- [12] S.-L. Jang, Y.-Y. Liu, and M.-H. Juang, "A triple-band voltage-controlled oscillator with a triple-resonance resonator," *Microelectron. J.*, vol. 83, pp. 1–5, Jan. 2019.

- [13] S. L. Jang, C.-H. Lu, and Y.-H. Chang, "Divide-by-2 injectionlocked frequency divider using distributed spiral resonator: 2: 1 Distributed spiral resonator injection-locked frequency divider," in *Proc. 7th Int. Symp. Next Gener. Electron. (ISNE)*, Taipei, Taiwan, May 2018, pp. 1–3.

- [14] B. Razavi, "A study of injection locking and pulling in oscillators," *IEEE J. Solid-State Circuits*, vol. 39, no. 9, pp. 1415–1424, Sep. 2004.

- [15] S.-L. Jang, S.-H. Huang, C.-F. Lee, and M.-H. Juang, "LC-tank colpitts injection-locked frequency divider with record locking range," *IEEE Microw. Wireless Compon. Lett.*, vol. 18, no. 8, pp. 560–562, Aug. 2008.

- [16] S.-L. Jang, F.-B. Lin, and J.-F. Huang, "Wide-band divide-by-2 injectionlocked frequency divider using MOSFET mixers DC-biased in subthreshold region," *Int. J. Circuit Theory Appl.*, vol. 43, no. 12, pp. 2081–2088, Dec. 2015.

- [17] N. Mahalingam, K. Ma, K. S. Yeo, and W. M. Lim, "Coupled dual LC tanks based ILFD with low injection power and compact size," *IEEE Microw. Wireless Compon. Lett.*, vol. 24, no. 2, pp. 105–107, Feb. 2014.

- [18] S. Lee, S. Jang, and C. Nguyen, "Low-power-consumption wide-lockingrange dual-injection-locked 1/2 divider through simultaneous optimization of VCO loaded *Q* and current," *IEEE Trans. Microw. Theory Techn.*, vol. 60, no. 10, pp. 3161–3168, Oct. 2012.

**SHENG-LYANG JANG** (Senior Member, IEEE) was born in Taiwan, Republic of China, in 1959. He received the B.S. degree from National Chiao-Tung University, Hsinchu, Taiwan, in 1981, the M.S. degree from National Taiwan University, Taipei, in 1983, and the Ph.D. degree from the University of Florida, Gainesville, in 1989. He joined the Noise Research Laboratory, University of Florida, in 1986. In 1989, he joined the Department of Electronics, National Taiwan

University of Science and Technology, Taipei, where he became a Full Professor in 1993. He has coauthored more than 300 SCI journal articles in the MOSFET devices and circuits. He also holds 17 U.S. patents.

**MIIN-HORNG JUANG** (Senior Member, IEEE) was born in Pin-Dong, Taiwan, Republic of China, in 1964. He received the B.S. and Ph.D. degrees in electronics engineering from National Chiao-Tung University, Hsinchu, Taiwan, in 1987 and 1992, respectively. From 1994 to 1996, he was with the Technology-Development Department, Mosel-Vitelic Inc., Science-Based Industry Park, Hsinchu. He is currently a Professor with the Department of Electronics Engineering,

National Taiwan University of Science and Technology, Taipei, Taiwan. He has published more than 100 refereed articles in international journals. His major research interests include nano-scale device and technology, the integration circuit design and technology, the power semiconductor devices, the flat panel display technology, and the design of optoelectronic device.

. . .

**HO-CHANG LEE** was born in Taipei, Taiwan, Republic of China, in 1971. He received the M.S. degree in electrical engineering from Tamkang University, Taiwan, in 1994. He is currently pursuing the Ph.D. degree in electronic engineering with the National Taiwan University of Science and Technology Taipei. From 2016 to 2020, he was a Research Assistant with the Laboratory of Microelectronics, National Taiwan University of Science and Technology. His research interests include

microwave and millimeter-wave circuits and transceiver systems. His current research interests include voltage control oscillator, injection locked frequency divider, phase-locked loop, microwave and millimeter-wave circuits, and transceiver systems.