Received September 15, 2020, accepted October 5, 2020, date of publication October 13, 2020, date of current version October 23, 2020. Digital Object Identifier 10.1109/ACCESS.2020.3030721

# A New Multilevel Inverter Topology With Reduced Power Components for Domestic Solar PV Applications

PREM PONNUSAMY<sup>1</sup>, (Member, IEEE), PANDARINATHAN SIVARAMAN<sup>1</sup>, DHAFER J. ALMAKHLES<sup>102</sup>, (Senior Member, IEEE), SANJEEVIKUMAR PADMANABAN<sup>103</sup>, (Senior Member, IEEE), ZBIGNIEW LEONOWICZ<sup>104</sup>, (Senior Member, IEEE), MATHESWARAN ALAGU<sup>101</sup>, (Member, IEEE), AND JAGABAR SATHIK MOHAMED ALI<sup>102,5</sup>, (Senior Member, IEEE) <sup>1</sup> Department of Electrical and Electronics Engineering, Bannari Amman Institute of Technology, Coimbatore 638401, India

<sup>2</sup>Renewable Energy Laboratory, College of Engineering, Prince Sultan University, Riyadh 11586, Saudi Arabia

<sup>3</sup>Department of Energy Technology, Aalborg University at Esbjerg, 6700 Esbjerg, Denmark

<sup>4</sup>Faculty of Electrical Engineering, Wroclaw University of Science and Technology, 50370 Wroclaw, Poland

<sup>5</sup>Department of Electrical and Electronics Engineering, SRM Institute of Science and Technology, Kanchipuram 603203, India

Corresponding authors: Jagabar Sathik Mohamed Ali (mjsathik@ieee.org) and Sanjeevikumar Padmanaban (san@et.aau.dk)

**ABSTRACT** Power electronic converters are used to nullify the input fluctuations from a solar photovoltaic unit because of intermittent solar irradiance and to make the terminal voltage grid compatible with the desired frequency. The conventional two-level converters suffer from low power quality and high voltage stress. In this article, a new multilevel inverter topology called Dual Source Multilevel Inverter (DS-MLI) with fewer power switches is proposed for solar PV power conversion systems. It can operate in symmetric and asymmetric operating modes with no cascading. This reduces the switching components required to produce several levels in the staircase voltage waveform. A closed-loop control algorithm is designed using the state-space averaging technique, and we assess the dynamic behaviour of the system under step change. We carry the simulation out in MATLAB environment. The experimental prototype of DS-MLI rated 1 kW is fabricated using FGA25N120-ANTD IGBTs, and an eco-sense made solar PV emulator is used for analysing the performance of DS-MLI while interfacing with solar PV unit. We compare the suggested scheme with its conventional counterpart in the aspects of components required, cost and efficiency, and the results are presented.

**INDEX TERMS** DS-MLI, multilevel inverter, solar PV, power conversion, fundamental frequency switching.

#### **I. INTRODUCTION**

With technology, the price of the solar PV panels and the associated accessories has reduced drastically over the years [1]. This resulted in tremendous growth in the installed capacity from 50 GWp in 2010 to 633 GWp in 2019 around the world [2]. It is expected to increase at the same pace in the years to come. Because of the intermittency in solar irradiance, the voltage delivered at the terminals of a solar PV unit will be continuously fluctuating, and power electronic converters are used to deliver a regulated terminal voltage

The associate editor coordinating the review of this manuscript and approving it for publication was Guangya Yang<sup>(D)</sup>.

under this varying irradiance [3]. The conventional two-level inverters suffer from high switching voltage stress, low power quality and efficiency, as stated in [4], [5]. Also, the twolevel inverters need an isolation transformer to prevent the EMI noise caused by common-mode voltage, as explained in [6]. To overcoming these drawbacks, multilevel inverters are being used for grid integration of solar PV units [7]. Among the three classical multilevel inverter topologies, the Cascaded H-Bridge Multilevel Inverters (CHB-MLI) is preferred for solar power conversion because of their modularity and simple control circuitry [8]. For the given 'n' number of sources, the CHB-MLI will synthesize 2n+1 level, i.e., with two DC sources it can synthesize five levels. Thus, the CHB-MLI topologies require a higher number of switches for the higher number of levels in the terminal voltage [9]. They focus the recent research on reducing the number of switches in CHB-MLI topology [10]. A Cross Connected Sources based Multilevel Inverter (CCS-MLI) topology, which requires 2n+2 switches for 'n' number of sources, is proposed in [11]. Here, the number of switches in the conduction path is high at a higher number of levels, and its asymmetric operation is yet to be explored. A sub-MLI module with reduced power components is explained in [12] wherein all the switches in the level adder are bidirectional. They discuss an envelope types basic unit which can be cascaded with many such units for the higher number of levels in the terminal voltage in [13]. But the topology requires a minimum of four independent sources. It gives a cascaded asymmetric MLI in [14] which can deliver 49 levels, but the blocking voltage across each switch is fourteen times the primary source which makes the application of this topology to higher voltage levels less likely. In the new asymmetric multilevel inverter topology suggested in [15], 12 switches are required to synthesize 21 levels in the terminal voltage in asymmetric mode. However, in the symmetric mode, it can offer only nine levels with 10 switches; also, it requires multiple independent sources, and for the addition of every source, it will add two more switches in the circuit. A crossconnected multilevel inverter is suggested in [16], but it requires cascading for asymmetric operation. The DS-MLI suggested in this article addresses the above concerns with its ability to operate in symmetric and asymmetric modes without cascading and with fewer components.

To maintain the DC-link voltage and grid current quality while interfacing the solar PV unit to the grid through DS-MLI, a suitable control loop needs to be developed. The dynamic performance of MLI with a control loop has been investigated by different authors. A Lyapunov based fast terminal sliding mode Q-V control for grid coupled hybrid solar PV and wind system is presented in [17], and this nonlinear control algorithm provides faster error tracking capability and robustness, but it lacks anti-inference ability. In [18], a fast and fixed switching frequency finite control set-model predictive control algorithm with delay compensation is used in a two-level voltage source inverter-based distributed generation system, but the multiple switching frequencies result in a sluggish response. A control algorithm for monophase cascaded H-bridge multilevel inverter it suggests based solar energy conversion system in [19], this method provides DC capacitor balancing and high-power quality during partial shading and panel mismatch conditions. A 2-cell Cascaded H-Bridge (CHB) multilevel inverter with unequal DC sources and 9- level operation is explained in [20], [21]. But all the above control techniques have drawbacks, like nonlinear characteristics and complex control. Here, a dual loop control technique with outer voltage control and inner current control to facilitate the interfacing of solar PV unit to the grid through DS-MLI is suggested. Thus, this article contributes to.

i) develop an H-Bridge based DS-MLI topology which requires fewer power switches when compared to the topologies found in recent literature and can achieve symmetric and asymmetric operation without cascading

ii) design a dual loop control scheme which gives better dynamic response under changing irradiance conditions.

We organise the rest of the paper: Section 2 and 3 explain the construction and switching operation of DS-MLI in symmetric and asymmetric mode. In section 4, and 5, the simulation of DS-MLI, and design of control loops are presented, and we analyse the stability of the system. Section 6 and 7 present the experimental results got while operating DS-MLI in isolated and grid-connected modes, and we give the conclusion in section 8.

#### **II. DUAL SOURCE MULTILEVEL INVERTER**

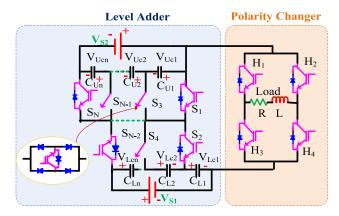

The dual-source multilevel inverter comprises only two independent voltage sources, and hence it is named so. The two independent sources  $V_{S1}$  and  $V_{S2}$  connected in level adder of the inverter circuit such that one source ( $V_{S1}$ ) in the lower arm and the other in the upper arm ( $V_{S2}$ ) as shown in the Fig.1. It bases the number of steps in the staircase waveform on the number of capacitors clamped in the lower and upper arm of the level adder. We get the polarity reversal using a polarity changer, which is an H-Bridge unit. When the voltage of both the independent sources is equal, then the inverter is said to be in symmetric mode. The inverter will be in asymmetric mode when the two voltage sources are at different voltages.

FIGURE 1. Proposed multilevel inverter topology.

The equations to determine the different design parameters for the number of capacitors (Nc) clamped to each arm, during symmetrical and asymmetrical operation of the topology is given in Table 1. From the table, we can find it that if the number of capacitors clamped in each arm is 2, the number of IGBTs required can be calculated as 9 (i.e., (2 x2) + 5). Further for asymmetrical operation, if the number of capacitors connected in the lower arm is 2 and the magnitude of V<sub>s1</sub> is fixed as V<sub>dc</sub>, then the magnitude of voltage source connected to upper arm V<sub>s2</sub> will be twice the magnitude of V<sub>s1</sub>.

#### TABLE 1. Inverter parameters.

| Parameter        | Symmetric         | Asymmetric                            |

|------------------|-------------------|---------------------------------------|

| Number of IGBTs  | $2N_{c} + 5$      | $2N_{c} + 5$                          |

| (Nswitch)        | c                 | C C                                   |

| Number of Levels | $4N_{c} + 1$      | $\{N_{c}[(N_{c} \times 2) + 2]\} + 1$ |

| (NLevel)         | · ·               |                                       |

| Voltage          | $V_{s2} = V_{s1}$ | $V_{s2} = N_c V_{s1}$                 |

| Magnitude of     | 52 51             | 52 0 51                               |

| Sources          |                   |                                       |

## III. SWITCHING SEQUENCE FOR SYMMETRIC AND ASYMMETRIC OPERATION

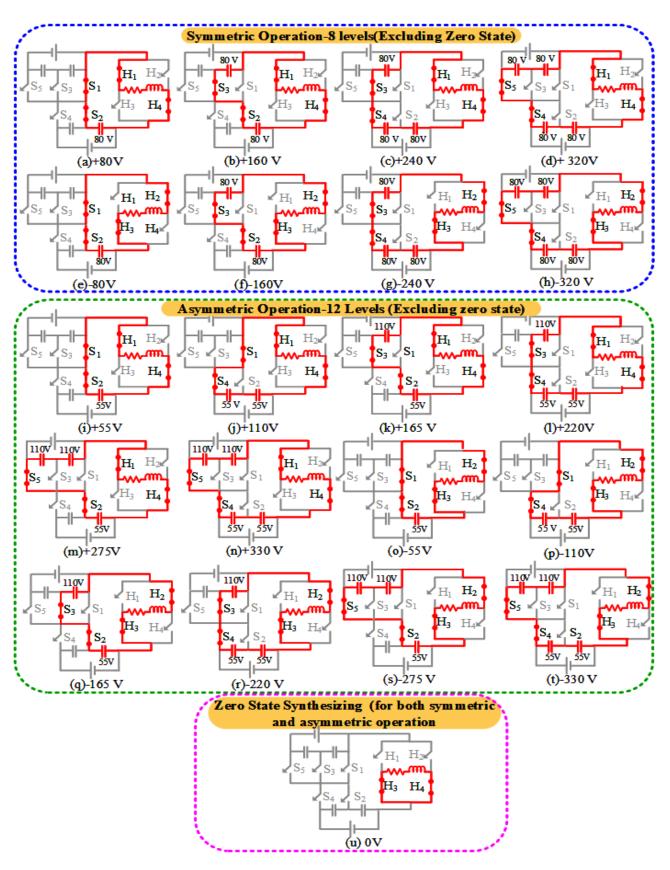

We can get the two independent voltage sources VS1 and VS2 using two solar PV units or capacitors. To understanding the symmetric operation, the voltage delivered by the two sources of DS-MLI is considered as  $V_{S1} = V_{S2} = 160V$ . For asymmetric mode, it is  $V_{S1} = 110V$  and  $V_{S2} = 220$  V. With two capacitors connected in each arm, the DS-MLI synthesises a nine-level staircase waveform during symmetric operation and thirteen levels during the asymmetric mode. The switches conducting to synthesise each level in both the modes are shown in Table 2 and Fig.2. In Table 2 'L' shows the level number. From Table 2, we observe it that the step size is 80V in symmetric operation and 55 V in asymmetric operation. For synthesising a voltage wave with 50 Hz, each step lasts for a duration of 1.25 ms in symmetric operation.

| TABLE 2. Switching sequence of DS-MLI during symmetric ar | ıd |

|-----------------------------------------------------------|----|

| asymmetric operation.                                     |    |

| Symme                 | etric mode                   | -  | Asymmetric Mode               |          |  |

|-----------------------|------------------------------|----|-------------------------------|----------|--|

| Voltage               | Switches                     | L  | Switches                      | Voltage  |  |

| Produced              | Conducting                   |    | Conducting                    | Produced |  |

| (V)                   | _                            |    | _                             | (V)      |  |

| +80                   | $S_1, S_2, H_1, H_4$         | 1  | $S_1$ , $S_2$ , $H_1$ , $H_4$ | +55      |  |

| +160                  | $S_2, S_3, H_1, H_4$         | 2  | $S_1$ , $S_4$ , $H_1$ , $H_4$ | +110     |  |

| +240                  | $S_{3}, S_{4}, H_{1}, H_{4}$ | 3  | $S_2, S_3, H_1, H_4$          | +165     |  |

| +320                  | $S_{4}, S_{5}, H_{1}, H_{4}$ | 4  | $S_{3}, S_{4}, H_{1}, H_{4}$  | +220     |  |

| - 80                  | $S_1, S_2, H_2, H_3$         | 5  | $S_2, S_5, H_1, H_4$          | +275     |  |

| - 160                 | $S_2, S_3, H_2, H_3$         | 6  | $S_4$ , $S_5$ , $H_1$ , $H_4$ | +330     |  |

| -240                  | $S_3, S_4, H_2, H_3$         | 7  | $S_1, S_2, H_2, H_3$          | -55      |  |

| - 320                 | $S_4, S_5, H_2, H_3$         | 8  | $S_1, S_4, H_2, H_3$          | -110     |  |

| 0                     | $H_1, H_2/H_3, H_4$          | 9  | $S_2, S_3, H_2, H_3$          | -165     |  |

| The additional levels |                              | 10 | $S_3, S_4, H_2, H_3$          | -220     |  |

| synthesised in        |                              | 11 | $S_2, S_5, H_2, H_3$          | -275     |  |

| asymmetric operation  |                              | 12 | S4,S5, H2,H3                  | -330     |  |

|                       |                              | 13 | $H_1, H_2/H_3, H_4$           | 0        |  |

From Table 3 and Fig. 2, we observe it that except  $S_3$  all the switches in the level adder undergoes two additional conduction periods in asymmetric mode when compared to the symmetric operation. This additional conduction delivers the additional levels in asymmetric operation.

#### TABLE 3. Switching instants of individual switches.

| Switch         | Number of times turned ON<br>in a cycle of 20 ms |   |  |  |  |  |  |  |

|----------------|--------------------------------------------------|---|--|--|--|--|--|--|

|                | Symmetric mode Asymmetric mode                   |   |  |  |  |  |  |  |

| $\mathbf{S}_1$ | 2                                                | 4 |  |  |  |  |  |  |

| $S_2$          | 4                                                | 6 |  |  |  |  |  |  |

| $S_3$          | 4                                                | 4 |  |  |  |  |  |  |

| $S_4$          | 4                                                | 6 |  |  |  |  |  |  |

| $S_5$          | 2                                                | 4 |  |  |  |  |  |  |

| H-Bridge       | 1                                                | 1 |  |  |  |  |  |  |

| Switches       |                                                  |   |  |  |  |  |  |  |

## **IV. SIMULATION OF DS-MLI**

The IGBT switch in MATLAB environment is used to simulate the Dual Source Multilevel Inverter. To achieving symmetric operation, we connect a 160 V DC source in lower and upper arms of DS-MLI. It achieves the asymmetric operation with DC sources rated 110 V and 220V, as stated earlier in section III. The IGBT switches in DS-MLI are controlled by using a fundamental frequency switching scheme called Nearest Level Modulation. In NLM method, the switching pulses for triggering the IGBTs to synthesize a voltage level is got by comparing the reference sine wave with the prior voltage level added to the nearest constant value that may range from 0.1 to 1 as shown in Fig.3a. We have established it in [22]–[24] that an NLM constant value of 0.4 is optimal since the Total Harmonic Distortion and the magnitude of lower order harmonics are less at a value of 0.4 as observed in Fig 3b.

We get the switching angle for each voltage level using (1)

$$\alpha_k = \sin^{-1} \left( \frac{A - 0.6}{N_{step}} \right) \tag{1}$$

where,

$$A = 1, 2, 3 \dots \left(\frac{N_{level} - 1}{2}\right)$$

(2)

$$N_{step} = \left(\frac{N_{level} - 1}{2}\right) \tag{3}$$

The Constant 0.6 in equation 1 is got by subtracting the nearest level constant 0.4 from 1. The values of switching angle  $\alpha_1$  to  $\alpha_4$  (for symmetric operation) and  $\alpha_1$  to  $\alpha_6$  (for asymmetric operation) can be got using (1). We can calculate the other angles concerning  $\pi$  using the sine wave symmetry.

$$\text{THD} = \frac{\sqrt{\sum_{i=3,5,7}^{\infty} V_{0i}}}{V_{of}} \tag{4}$$

where,

$$V_{0i} = \frac{2\sqrt{2V}}{\pi} \sqrt{\sum_{i=1,3,\dots\infty} \sum_{k=1}^{N_{level}} \left(\frac{\cos\left(i\alpha_k\right)}{i}\right)}$$

(5)

187485

FIGURE 2. Equivalent circuit and conduction path to synthesize different voltage step.

FIGURE 3. (a) NLM method (b) %THD Vs NLM constant.

We calculate the percentage THD of the voltage using (4) with the values  $V_{oi}$  and  $V_{of}$  which are the RMS value of harmonic and fundamental voltage component in the output voltage as given in [25].

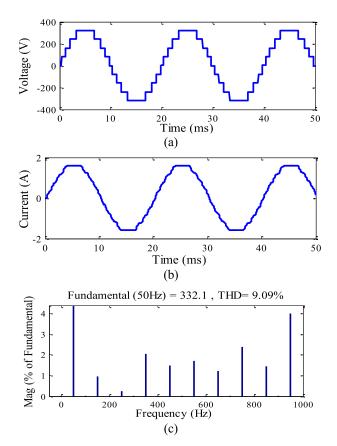

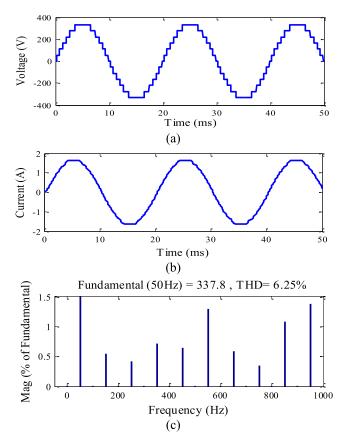

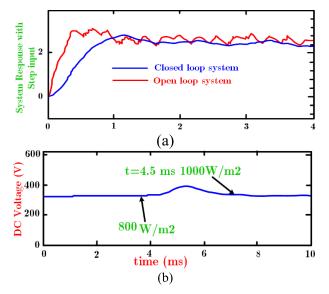

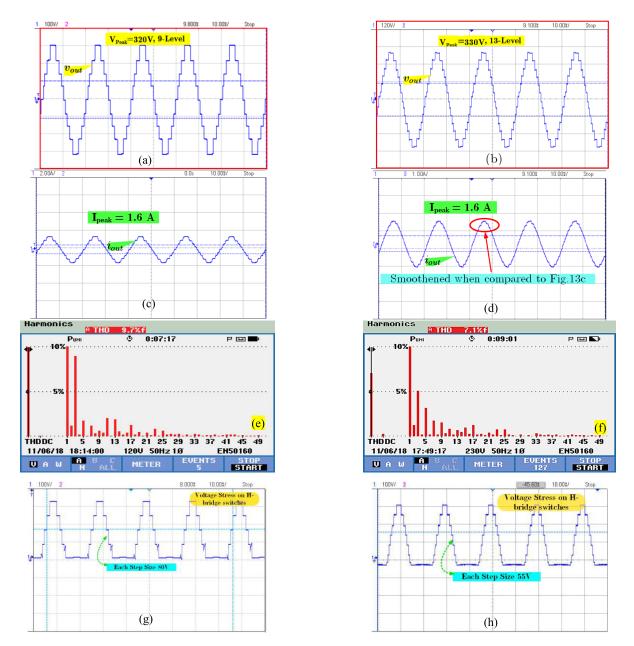

The simulation results got for symmetric operation is shown in the Fig.4. Fig.4a depicts the nine-level terminal voltage with peak value 320 V with  $N_{step} = 4$  and step size of 80 V. The load has a resistance of 200 ohms and inductance of 70 mH. Therefore, the peak value of the load current got is 1.6 Ampere as shown in the Fig.4b. We observe the Voltage THD as 9.09% in Fig.4c. The DS-MLI synthesizes 13 levels during asymmetric operation, as shown in the Fig.5a. From (4) and (5) we understand it that the number of levels in the terminal voltage waveform of an inverter is inversely proportional to its percentage THD. Thus, with the higher number of levels in the voltage waveform (330V), the percentage voltage THD of DS-MLI during asymmetric operation is only 6.25% as shown in Fig.5c. Therefore, for a load, the percentage THD is 30% less if the DS-MLI is operated in asymmetric mode.

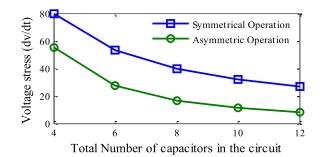

#### A. VOLTAGE STRESS

At a maximum modulation index, a two-level inverter (VSI, CSI or ZSI) needs 600V in its DC link to deliver a 230V RMS at its terminals. This maximum voltage will appear in the switches and the load alternatively during inverter switching. Which is termed as dv/dt stress. The parameter dv/dt stress varies with voltage and rate of change of time (switching frequency). Higher the stress, higher will be the heat emitted from the switch, and hence it requires more massive heat sink and load insulation [26], [27]. The case becomes worse if we use a switching scheme with switching frequency between kHz. To minimize the dv/dt stress, either the voltage

FIGURE 4. Simulation results of DS-MLI during symmetric operation. (a) 9-Level Voltage. (b) Load current. (c) Harmonic Spectrum of voltage THD.

can be reduced or we should increase the time between subsequent switching. In DS-MLI during symmetrical operation, the maximum voltage transition is restricted to 320 V/4, where 4 is the number of steps in a half cycle. In asymmetric operation, it is 55 V with 6 steps for a peak voltage of 330V. The exponential reduction in dv/dt stress with the increase in the number of capacitors during symmetric and asymmetric operation is depicted in Fig.6. From the figure, we infer it that for the same number of capacitors, the switching stress decreases drastically in asymmetric operation.

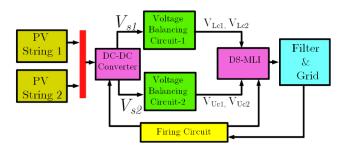

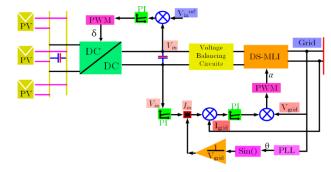

## V. INTERFACING DS-MLI WITH SOLAR PV DESIGN OF VOLTAGE BALANCING CONTROLLER

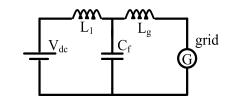

The single-phase DS-MLI fed PV grid-connected system with LCL filter is shown in Fig.7. The Control loops of DSMLI is designed using a small-signal model; here state-space averaging technique is used to develop the small-signal model. To derive the state-space model of DSMLI, following assumptions are made 1. All the switches are lossless 2. DSMLI is operated in asymmetrical mode 3. Inverter side inductance current  $I_L$ , Grid side inductance  $I_{Lg}$ and Filter capacitor voltage (V<sub>c</sub>) is state variables [28].

The equivalent circuit got after applying the assumptions to Fig.7 is shown in Fig.8, and we use it for deriving the state-space model.

FIGURE 5. Simulation results of DS-MLI during asymmetric operation. (a) 13-Level Voltage. (b) Load current. (c) Harmonic Spectrum of voltage THD.

FIGURE 6. Voltage stress got for the number of capacitors.

FIGURE 7. Schematic for interfacing solar PV strings to the grid through DS-MLI.

From Fig.8 by applying KVL and KCL, we can get the state-space model equation of the state variable inductor 187488

FIGURE 8. Equivalent circuit of the power conversion scheme.

current (I<sub>L</sub>), Grid side inductance (I<sub>Lg</sub>) and filter capacitor voltage (V<sub>c</sub>):

$$V_{dc} - V_L - V_C = 0$$

$$L \frac{di_L}{dt} = V_{dc} - V_C = \frac{dI_c}{dt} = \frac{V_{dc}}{L} - \frac{V_c}{L}$$

(6)

$$L\frac{di_{Lg}}{dt} = -V_g - V_{Cf} = \frac{dI_{Lg}}{dt} = -\frac{V_g}{L_g} - \frac{V_c}{L_g}$$

(7)

$$I_I = I_c + I_{Lg}$$

$$C\frac{dV_c}{dt} = I_L - I_{Lg}; \frac{dV_c}{dt} = -\frac{I_L}{C} - \frac{IL_g}{C}$$

(8)

From (6)- (8), the state-space model of the system is planned:

$$\frac{d}{dt} \begin{bmatrix} I_L \\ I_{Lg} \\ V_C \end{bmatrix} = \begin{bmatrix} 0 & 0 & \frac{-1}{L_1} \\ 0 & 0 & \frac{-1}{L_g} \\ \frac{1}{C} & \frac{-1}{C} & 0 \end{bmatrix} \begin{bmatrix} I_L \\ I_{Lg} \\ V_C \end{bmatrix} + \begin{bmatrix} \frac{1}{L_1} \\ \frac{1}{I_g} \\ P0 \end{bmatrix} \begin{bmatrix} V_{dc} & V_g & 0 \end{bmatrix}$$

By taking the Laplace transforms for the state variables shown in the above equation

$$SI_L(s) = -\frac{V_c(s)}{L} + \frac{V_{dc}(s)}{L}$$

(9)

$$I_L(s) = -\frac{V_c(s)}{LS} + \frac{V_{dc}(s)}{LS}$$

(10)

$$SI_{g}(s) = -\frac{V_{c}(s)}{L_{g}} + \frac{V_{g}(s)}{L_{g}}$$

(11)

$$I_{g}(s) = -\frac{V_{c}(s)}{SL_{g}} + \frac{V_{g}(s)}{SL_{g}}$$

(12)

By simplifying (9) (10), (11) & (12), the output capacitor voltage (Vc) to input DC-link voltage ( $V_{dc}$ ) transfer function is got as follows

$$\frac{V_c(s)}{V_{dc}(s)}\Big|_{V_g(s)=0} = \frac{CL_g}{SC\left[S^2LL_g+1\right]+1}$$

Which implies

$$\left. \frac{V_c\left(s\right)}{V_{dc}\left(s\right)} \right|_{V_g\left(s\right)=0} = \frac{CL_g}{S^3 CLL_g + SC + 1}$$

(13)

On substituting  $V_c(s)$  in  $I_L(s)$

$$I_L(s) = \frac{I_L(s)}{LCS^2} + \frac{I_g(s)}{LCS^2} + \frac{V_{dc}(s)}{LC}$$

Which implies

$$I_L(s)\left[\frac{LCS^2 - 1}{LCS^2}\right] = \frac{I_g(s)}{LCS^2} + \frac{V_{dc}(s)}{LC}$$

(14)

VOLUME 8, 2020

By simplifying (10) to (14), the output current ( $I_L$ ) to input DC-link voltage ( $V_{dc}$ ) transfer function is deduced as

$$\frac{I_L(s)}{V_{dc}(s)}\Big|_{I_g(s)=0} = \frac{CS}{LCS^2 - 1}$$

(15)

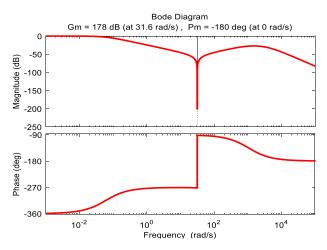

With the DC-link voltage balancing and current control transfer function got from the state-space model, the stability of the system is analysed by using a Bode plot with the parameters specified in Table 4.

#### TABLE 4. The parameters for the proposed system.

| Parameter                           | Symbol            | Value       |

|-------------------------------------|-------------------|-------------|

| AC-source voltage<br>(Grid voltage) | Vg                | 230V, 50 Hz |

| Inverter filter<br>inductance       | L                 | 0.27 mH     |

| Input filter capacitance            | С                 | 300 µF      |

| DC link capacitance                 | $C_{\text{Link}}$ | C = 0.042F  |

| DC bus voltage                      | $V_{dc}$          | 660 V       |

| Grid filter inductance              | Lg                | 0.27mH      |

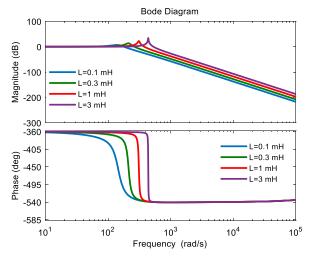

## A. ANALYSIS OF INDUCTANCE AND CAPACITANCE VARIATION AND ITS EFFECTS ON SYSTEM PERFORMANCE

In this section, the impact of inductance and capacitance on the dynamic characteristic of the DS-MLI is analysed. By using the system's transfer function, the practical value of inductor and capacitor is determined through frequency response bode plot analysis to improve the stability of the system.

## 1) EFFECT OF INDUCTANCE VARIATION

The bode plot of the system's transfer function for the variation of inductance is shown in Fig. 9.

It shows the gain margin and phase margin at different inductance values in Table 5. From Table 5; it is found that for the inductance of 0.3 mH the gain and phase margins are 29.9dB and 13.4° respectively. When the inductance value is increased beyond 1mH, it produces more oscillations, resulting in a lower phase margin, thus inducing harmonics and making the system unstable.

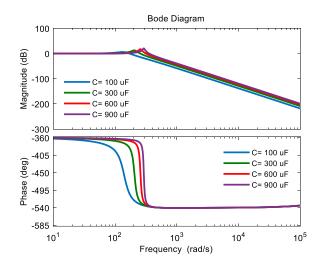

## 2) EFFECT OF CAPACITANCE VARIATION

The dynamic performance of the system is investigated by varying the capacitance value, and corresponding results are shown in Fig. 10 and Table 6 and is found that 300 micro-farad gives 49.2dB gain margin and 75.8° of phase margin respectively and hence the system is stable.

At other capacitance values, the gain margin and phase margin are low, resulting in more ripples and thus pushing the system into an unstable state.

FIGURE 9. Bode plot of inductance variation.

#### TABLE 5. Effect of inductance variation.

| Inductance | Gain Margin | Phase Margin |

|------------|-------------|--------------|

| value (mH) | (dB)        | (deg)        |

| 0.1        | 39.6        | 32.6         |

| 0.3        | 29.9        | 13.4         |

| 1          | 18.8        | 4.15         |

| 3.33       | 5.68        | 0.563        |

FIGURE 10. Bode plot of Capacitance variation.

**TABLE 6.** Effect of capacitance variation.

| Capacitance value | Gain Margin | Phase Margin |

|-------------------|-------------|--------------|

| (µF)              | (dB)        | (deg)        |

| 100               | 54.4        | 134          |

| 300               | 49.2        | 75.8         |

| 600               | 24.6        | 7.87         |

| 900               | 20.8        | 5.24         |

From the above analysis, the optimum value of inductance and capacitance are found using the DC-link voltage

FIGURE 11. (a) Voltage balancing control scheme (b) Open loop voltage control.

balancing and current control transfer function equations as 0.3mH and  $300\mu\text{F}$ , respectively. The stability of the system is analyzed by using frequency response Bode plot with the parameters specified in Table 4.

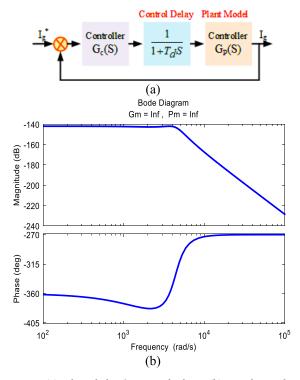

## B. DESIGN OF VOLTAGE BALANCING CONTROLLER (VBC LOOP)

The Fig.11a shows the DC-link voltage balancing control scheme of DS-MLI. The plant transfer function  $G_p$  (s) is controller using a PI controller with appropriate  $K_i$  and  $K_p$  values tuned. The voltage regulation loop includes the average voltage controller (AVC), which regulates the total active power balance between the DSMLI and the grid.

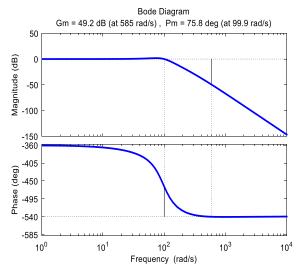

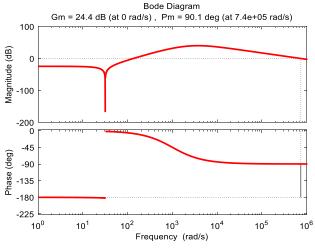

The Fig.11b shows the open-loop bode plot of the AVC with  $K_p = 0.6$ ,  $K_i = 2$  wherein the gain margin (GM) and Phase Margin (PM) are infinity and hence the AVC loop is unstable. Fig.12 shows the closed-loop bode plot of the AVC, where the proportional-integral parameters are designed as  $k_p$ , = 1.2,  $k_i$ , = 0.002 for which a gain margin (GM) of 49.2 dB and a phase margin (PM) of 75.8° is attained, thus the stability of the VBC loop is improved. The DSMLI draws maximum active power from the DC link source to uphold the DC link voltage at the preferred level. This is achieved by a dual loop control method, which regulates the DC link capacitor voltage, the grid voltage and the inverter current. In the inner current control loop, the grid current's quadrature axis component will zero in the controller to generate maximum active power at unity power factor.

FIGURE 12. Closed-loop voltage control.

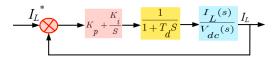

## C. CURRENT-LOOP CONTROL SCHEME

The current control scheme of DS-MLI is shown in Fig.13. The output current to we represent the input transfer function as a plant, and the Proportional-Integral (PI) controller controls it. Figure. 14 shows the bode diagram of an openloop current control transfer function. From the figure, we can observe it that the crossover frequency is high, which results in more oscillation making the system unstable. For stabilizing the system, a compensator PI controller with reference tracking is introduced in the closed-loop system. The transfer function Bode plot of the compensated closed-loop system is shown in Fig.15. In Fig.15, we observe it that the

FIGURE 13. The current Control scheme of DS-MLI.

FIGURE 14. Bode plot of open loop current control.

FIGURE 15. Bode plot of closed-loop current control.

gain margin is 24.4 dB and the phase margin is 90° which improves the stability of the system. The open-loop and the closed-loop response of DSMLI are depicted in Fig.16a. We observe it that closed-loop has less steady-state error and peak overshoot when compared to open-loop system. Thus the closed-loop system produces fewer ripples and harmonics. Further, the dynamic response of the closed-loop DSMLI is investigated by applying a step-change in irradiance from 800 W/m<sup>2</sup> to 1000 W/m<sup>2</sup> at 4.5 ms, as shown in Fig.16b. From Fig.16b, we can infer it that the system reaches a steady-state within 2.5 ms after the change in irradiance, and this ensures that the system has a fast dynamic response.

**FIGURE 16.** (a) System's response for step input (b) Dynamic response of the system with controller.

## **VI. EXPERIMENTAL RESULTS**

To validating the theoretical and simulation results, experiments are carried out with an isolated solar PV unit feeding a load through DS-MLI and with a closed-loop power conversion scheme and the results are presented in the following sections.

## A. ISOLATED OPERATION OF DS-MLI

An experimental prototype of DS-MLI rated 1kW is constructed to validate the simulation results. The components used for construction and we give their rating below in Table 7. It makes the experimental setup to feed a load with  $200\Omega$  resistance and 70mH inductance. The load voltage, load current and THD got in symmetric operation are shown in Fig 17a, 17c and 17e, respectively. From these figures, we can observe it that under the constant input voltage from the solar PV emulator, the DSMLI delivers a 9-level output voltage waveform with a THD of 9.7%. The experimental THD is slightly higher than the simulated values as the FGA25N120-ANTD switches have a finite turn ON and Turn off time unlike its simulated counterpart wherein the switches turn ON and OFF instantaneously. The Fig. 17b, 17d and 17f portrays the experimental voltage, current, and THD of asymmetric operation, respectively. Here, with an increase in steps, the THD has come down to 7.1%. We can also observe it that during the asymmetric operation, the current waveform is smoother because of the above reason. The blocking voltage across the H-Bridge switch H<sub>1</sub> is measured during symmetric and operations and presented in Fig.17. g and 17.h, from which it can be observed that the dv/dt stress is comprehensively low when compared to 230 V in the two-level inverter.

TABLE 7. Components used in the isolated operation set up.

| S.No | Component                       | Rating             | Quantity |

|------|---------------------------------|--------------------|----------|

| 1    | Capacitor                       | 80V,1000µF         | 6        |

| 2    | Capacitor                       | 200V,470 μF        | 2        |

| 3    | Inductor                        | 70mH               | 1        |

| 4    | IGBT                            | FGA25N120-<br>ANTD | 9        |

| 5    | Ecosense made solar PV emulator | 1 kW               | 1        |

| 6    | Load resistance                 | 200Ω               | 1        |

| 7    | FPGA Spartan 6<br>processor     | -                  | 1        |

## B. COMPARISON OF DS-MLI WITH OTHER TOPOLOGIES

The components required for obtaining nine levels in the output voltage for different multilevel inverter topologies presented in the literature are compared with the DS-MLI, and we present the results in Table 8.

From Table 8, we can observe it that the number of components required for DS-MLI is relatively less when compared to the other topologies. The higher number of capacitors used in the topology facilitates its asymmetrical operation without cascading. Also, it provides a tactical advantage in single point voltage regulation during grid interfacing.

FIGURE 17. Experimental results (a) (c), (e) 9-level voltage, current, THD got during symmetric operation, (b), (d), (f) 13-level voltage, current, THD got during asymmetric operation, (g) Voltage stress across H<sub>1</sub> during symmetric operation, (h) Voltage stress across H<sub>1</sub> during asymmetric operation.

TABLE 8. Comparison of components required.

| Number of<br>Components | [12] | [29] | [14] | [15] | СНВ | DSMLI |

|-------------------------|------|------|------|------|-----|-------|

| IGBTs                   | 10   | 10   | 12   | 10   | 36  | 9     |

| Drivers                 | 8    | 10   | 12   | 10   | 36  | 9     |

| Sources                 | 4    | 4    | 4    | 4    | 4   | 2     |

| Capacitors              | -    | -    | -    | -    | -   | 4     |

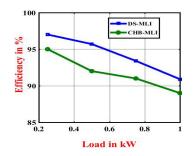

## C. EFFICIENCY COMPUTATION

An inverter will experience losses because of the turn-on and turn off time of the switches and internal switch resistance called switching and conduction losses, respectively. By using the linearized switching approximation characteristics [7], the switching and conduction losses can be calculated as follows.

#### 1) SWITCHING LOSS

The switching loss is the sum of power lost during turn-on and turn-off period of the switches. For a practical switch, we can estimate the power lost while we turn it ON as given in (16)

$$P_{sw-n} = \frac{1}{6} \left( f_s \times V_{swb} \times I_{swc} \times t_{on} \right) \tag{16}$$

Similarly, the power loss while the switch is turning off can be determined using (17)

$$P_{sw-f} = \frac{1}{6} f_s V_{swb} I_{swc} t_{off} \tag{17}$$

The total loss per switching state will be the sum of (16) and (17). Here  $f_s$  is the switching frequency of the switch,  $V_{swb}$  is the blocking voltage across the switch,  $I_{swc}$  is the conduction current through the switch,  $t_{on}$  and  $t_{off}$  are the time required for the switch to turn ON and turn off, respectively.

#### 2) CONDUCTION LOSS

The conduction loss is the power dissipated in a switch when it is in ON-state, and it can be computed by using (18)

$$P_{conduction} = \frac{V_{swc}I_{swc}}{t_{total}}(t_{total} - t_{off} - t_{on})$$

(18)

The total loss per switch  $(P_{LS})$  per switching state is the sum of equations (16) to (18). So, the total power loss across the inverter is

$$P_{Loss} = \sum_{s=1}^{9} P_{LS} \tag{19}$$

The efficiency of the inverter can be determined using the equation (20)

$$\eta = \frac{P_{load}}{P_{in} + P_{loss}} \tag{20}$$

In switch S<sub>1</sub>, for a load of 0.26 kW (rms), the blocking voltage is 160 V (peak) in a symmetric mode, and the conduction current is 1.2A. From the datasheet of FGA25N120-ANTD, the turn on and turn-off times are taken as 10 nanoseconds and 190 nanoseconds, respectively. The switching loss per switching instant is 0.00576W. The switch conducts during two switching states and thus has four switching instants and the switching loss incurred in switch  $S_1$  is 0.02304W. Similarly, the conduction loss at switch  $S_1$  is 0.50415W. The total switching loss is the continuous sum of switching loss across all the switches, and it is 0.12 W; similarly, the total conduction loss is 7.04 W. Therefore, the total loss is 7.2 W, and the efficiency estimated using (20) is nearly 97%. Similarly, the efficiency at loads 0.5kW, 0.75 kW and 1 kW are computed for DS-MLI and portrayed in Fig.18. From the Fig.18, we can find it that the efficiency of DS-MLI is higher than the CHB-MLI topology.

FIGURE 18. Efficiency curve.

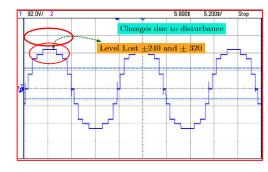

## D. ISOLATED OPERATION UNDER DISTURBANCE

The eco sense made solar PV emulator has four output channels. It connects the solar PV emulator to DS-MLI such that the outputs from two of the four channels are considered as  $V_{s1}$  and  $V_{s2}$  delivering equal voltages. Both the channels are clamped to two capacitors and used for the upper and lower arm of the DS-MLI. We subject the input irradiance of the channel connected to the upper arm of the DSMLI to a step-change in irradiance, and it shows the observation in the Fig.19.

**FIGURE 19.** Symmetrical operation of DS-MLI when  $V_{s1}$  is subjected to a disturbance.

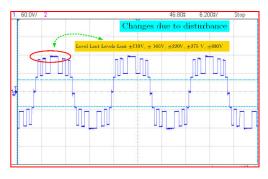

Similarly, when the step-change in irradiance applies to one of the two channels during asymmetric operations, the number of levels lost is higher when compared to symmetric operation as shown in the Fig.20.

**FIGURE 20.** Asymmetrical operation of DS-MLI when  $V_{s1}$  is subjected to a disturbance.

To maintain the DC-link voltage and grid current quality while interfacing the solar PV unit to the grid through DS-MLI, a modified single DC bus bar collector scheme is suggested and we present the experimental results in the following section.

## VII. INTERFACING OF SOLAR PV UNIT TO GRID THROUGH DS-MLI

A single DC bus bar collector-based control scheme is proposed in [30]. In this scheme, it connects the multiple solar PV strings to a common DC bus bar, with a DC-DC converter

|      |                                      |                | Unit              | Control             | Scheme            | proposed         | in [30]           | Dua               | Source M          | Iultilevel Inverter |                   |

|------|--------------------------------------|----------------|-------------------|---------------------|-------------------|------------------|-------------------|-------------------|-------------------|---------------------|-------------------|

| S.No | Components required                  | Specification  | Cost<br>in<br>USD | For<br>9-<br>levels | Cost<br>in<br>USD | For 13<br>levels | Cost<br>in<br>USD | Symmetric<br>Mode | Cost<br>in<br>USD | Asymmetric<br>Mode  | Cost<br>in<br>USD |

| 1    | Capacitor                            | 450 V,1500 μF  | 41.51             |                     |                   |                  |                   | 1                 | 41.51             | 1                   | 41.51             |

| 2    | Capacitor                            | 300 V, 1500 μF | 24.13             |                     |                   |                  |                   |                   |                   | 1                   | 24.13             |

| 3    | Capacitor                            | 200 V, 470 μF  | 1.6               |                     |                   |                  |                   | 2                 | 48.44             | 3                   | 72.66             |

| 4    | Capacitor                            | 80 V, 1000 μF  | 1.82              |                     |                   |                  |                   | 4                 | 46.24             | 2                   | 23.12             |

| 5    | Capacitor                            | 44 V, 1500 μF  | 3.05              | 4                   | 12.2              | 6                | 18.3              |                   |                   |                     |                   |

| 6    | Inductor                             | 700 µH         | 1.96              | 4                   | 7.84              | 6                | 11.76             | 1                 | 1.96              | 1                   | 1.96              |

| 7    | Inductor                             | 1.6 mH         | 1.56              |                     |                   |                  |                   | 1                 | 1.56              | 1                   | 1.56              |

| 8    | Inductor                             | 1.2 mH         | 1.02              |                     |                   |                  |                   | 1                 | 1.02              | 1                   | 1.02              |

| 9    | Diode                                | 1N3208         | 3.63              | 4                   | 14.5              | 6                | 21.78             | 9                 | 32.67             | 9                   | 32.67             |

| 10   | MOSFET                               | IRL530PBF      | 0.62              | 4                   | 2.48              | 6                | 3.72              | 1                 | 0.62              | 1                   | 0.62              |

| 11   | MOSFET                               | IRF1644GPBF    | 2.48              |                     |                   |                  |                   | 2                 | 4.96              | 2                   | 4.96              |

| 12   | IGBT                                 | FGA5N120-AD    | 1                 | 12                  | 12                | 24               | 24                | 9                 | 9                 | 9                   | 9                 |

| 13   | Flyback<br>Transformer               | -              | 15                | 4                   | 60                | 6                | 90                |                   |                   |                     |                   |

| 14   | Efficiency at 1<br>kW                | -              | -                 | 89% 91%             |                   |                  |                   |                   |                   |                     |                   |

| 15   | Approximated<br>total Cost in<br>USD | -              | -                 | 109                 | .04               | 169              | 9.56              | 103.73            | 3                 | -                   | 125.87            |

TABLE 9. Comparison of components required for closed-loop system.

FIGURE 21. Modified Single DC-Bus bar collector scheme.

connected to each string. It connects this DC bus bar to the grid through a grid-tied conventional Cascaded H-Bridge Multilevel Inverter. The DC links tapped from the common DC bus bar through a fly-back converter acts as the independent source for each H-Bridge unit. Even though the energy yield and operation range are higher in the said scheme, the efficiency is less because of multiple conversion stages involved.

A modified single DC bus bar-based control scheme with DS-MLI is used in this article, as shown in the Fig.21. In the suggested scheme, the converters connected to each string are eliminated, and the multiple fly-back converters are replaced with a single buck-boost converter and a voltage balancing circuit. Therefore, the efficiency of the system will be higher for the reduction in the number of components. Since the voltage level involved in domestic applications is

between 230 V. The voltage stress across the converter is bearable.

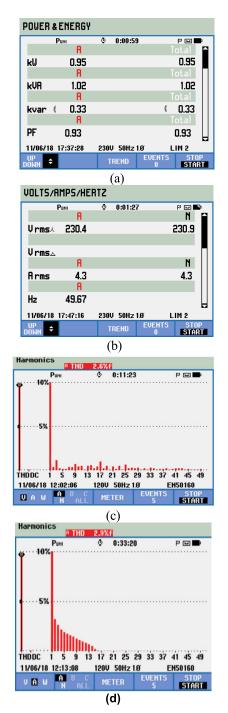

A 1kW solar PV unit is realized with an eco-sense made solar PV emulator and connected to the grid using the proposed scheme. The voltage, real power, reactive power, current and power factor observed in the grid-tied DS-MLI is shown in Fig. 22a and Fig.22b. For an RMS voltage of 230 V, the solar PV unit delivers a current of 4.3 amperes. The LC filter used in the grid side aided in eliminating the lower order harmonics and thus reducing the voltage THD to 2.6% as shown in Fig.22c. We observe the current THD as 2.9%, as shown in Fig.22d. The minimum lower order harmonic content observed in Figure 22c originates from the ripples from the DC link, which is less influential in the circuit performance. The modified single DC bus bar collector scheme with DS-MLI is compared with the single DC bus bar collector scheme with CHB-MLI in the aspects of the number of components required. We present cost and efficiency and the observations in Table 9. From Table 9, we can find it that the proposed conversion scheme requires less number of components. In particular, the multiple fly-back transformers used in the conventional conversion scheme are eliminated, which brought down the cost of the proposed conversion scheme to 125 USD, which is 30% less when compared to to conventional counterpart. The cost of the components of the proposed topology differs from the cost of the components used in [30]. Because of the specification, the components used in the two topologies differs from each other. The usage of fly-back transformers in [30] increases its cost drastically, as observed in Table 9.

FIGURE 22. (a) Voltage and Current, (b) Power and Power factor, (c) Voltage THD (d) Current THD.

## **VIII. CONCLUSION**

A multilevel inverter topology called Dual-source multilevel inverter is suggested for domestic rooftop solar PV units. The inverter topology can synthesize nine-levels and thirteen levels using nine switches during symmetric and asymmetric operation, respectively. Further, a modified single DC bus bar-based control scheme with reduced power components is suggested to interface solar PV unit to grid through DS-MLI. The transfer function of the control scheme is derived, and its

## NOMENCLATURE

| NUMENCLA            | UK | E                                                 |

|---------------------|----|---------------------------------------------------|

| $C_{f}$             | -  | Filter capacitance                                |

| DS-MLI              | -  | Dual Source Multilevel Inverter                   |

| $F_s$               | -  | Switching frequency                               |

| $G_c(s)$            | -  | Controller transfer function                      |

| $G_p(s)$            | -  | Plant transfer function                           |

| $I_l$               | -  | Current through inverter side inductance          |

| $I_{Lg}$            | -  | Current through grid side inductance              |

| $I_{swc}$           | -  | Current through the switch                        |

| I <sub>swc</sub>    | -  | Conduction current through the switch             |

| $K_i$               | -  | Integral gain                                     |

| $K_p$               | -  | Proportional gain                                 |

| Nc                  | -  | Number of capacitors clamped in                   |

|                     |    | lower/upper arm of DS-MLI                         |

| N <sub>Level</sub>  | -  | Number of levels                                  |

| Nstep               | -  | Number of steps in the positive/Negative          |

|                     |    | half cycle of the terminal voltage                |

| N <sub>switch</sub> | -  | Number of switches                                |

| <b>P</b> conduction | -  | Conduction loss                                   |

| PLL                 | -  | Phase-Locked Loop                                 |

| Ploss               | -  | The power loss of the inverter                    |

| $P_{LS}$            | -  | Power lost in each switch                         |

| $P_{sw-f}$          | -  | Power lost during turn off                        |

| $P_{sw-n}$          | -  | Power lost during turn on                         |

| PV                  | -  | Photovoltaic                                      |

| PWM                 | -  | Pulse Width Modulation                            |

| THD                 | -  | Total Harmonic Distortion                         |

| $t_{off}$           | -  | The time required for the IGBT to turn off        |

| ton                 | -  | The time required for the IGBT to turn ON         |

| $V_{0f}$            | -  | The magnitude of the fundamental voltage          |

|                     |    | component                                         |

| $V_c$               | -  | Filter capacitor voltage                          |

| $V_{dc}$            | -  | The voltage at the input dc-link                  |

| $V_L$               | -  | The voltage across the inductor                   |

| $V_{oi}$            | -  | The magnitude of harmonic voltage com-<br>ponents |

| $V_{s1}$            | -  | The magnitude of voltage delivered by the         |

| * 31                |    | DC voltage source connected in the lower          |

|                     |    | arm                                               |

| $V_{s2}$            | -  | The magnitude of voltage delivered by the         |

| 52                  |    | DC voltage source connected to the upper          |

|                     |    | arm                                               |

| $V_{swb}$           | -  | Blocking voltage across the switch                |

| $V_{swc}$           | -  | The voltage drop across the switch during         |

|                     |    | conduction                                        |

| $\alpha_k$          | -  | Switching angle                                   |

|                     |    |                                                   |

#### REFERENCES

- E. Babaei, T. Jalilzadeh, M. Sabahi, M. Maalandish, and R. S. Alishah, "High step-up DC–DC converter with reduced voltage stress on devices," *Int. Trans. Elect. Energy Syst.*, vol. 29, no. 4, 2019, Art. no. e2789.

- [2] REthinking Energy, International Renewable Energy Agency, Abu Dhabi, United Arab Emirates, 2019, p. 55.

- [3] M. T. Khosroshahi, "Crisscross cascade multilevel inverter with reduction in number of components," *IET Power Electron.*, vol. 7, no. 12, pp. 2914–2924, Dec. 2014.

- [4] J. S. M. Ali, R. S. Alishah, N. Sandeep, S. H. Hosseini, E. Babaei, K. Vijayakumar, and U. R. Yaragatti, "A new generalized multilevel converter topology based on cascaded connection of basic units," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 7, no. 4, pp. 2498–2512, Dec. 2018.

- [5] C. Meza, J. J. Negroni, D. Biel, and F. Guinjoan, "Energy-balance modeling and discrete control for single-phase grid-connected PV central inverters," *IEEE Trans. Ind. Electron.*, vol. 55, no. 7, pp. 2734–2743, Jul. 2008.

- [6] J. Rodriguez, S. Bernet, P. K. Steimer, and I. E. Lizama, "A survey on neutral-point-clamped inverters," *IEEE Trans. Ind. Electron.*, vol. 57, no. 7, pp. 2219–2230, Jul. 2010.

- [7] P. Prem, J. Sathik, P. Sivaraman, A. Mathewsaran, S. H. E. A. Aleem, "A new asymmetric dual source multilevel inverter topology with reduced power switches," *J. Chin. Inst. Eng.*, vol. 42, no. 5, pp. 460–472, Jul. 2019.

- [8] J.-S. Lai and F. Zheng Peng, "Multilevel converters—A new breed of power converters," *IEEE Trans. Ind. Appl.*, vol. 32, no. 3, pp. 509–517, 1996.

- [9] M. G. Villalva, J. R. Gazoli, and E. R. Filho, "Modeling and circuit-based simulation of photovoltaic arrays," in *Proc. Brazilian Power Electron. Conf.*, Sep. 2009, pp. 1244–1254.

- [10] H. S. Krishnamoorthy, S. Essakiappan, P. N. Enjeti, R. S. Balog, and S. Ahmed, "A new multilevel converter for megawatt scale solar photovoltaic utility integration," in *Proc. 27th Annu. IEEE Appl. Power Electron. Conf. Expo. (APEC)*, Feb. 2012, pp. 1431–1438.

- [11] K. K. Gupta and S. Jain, "Comprehensive review of a recently proposed multilevel inverter," *IET Power Electron.*, vol. 7, no. 3, pp. 467–479, Mar. 2014.

- [12] A. R. Shalchi, D. Nazarpour, S. H. Hosseini, and M. Sabahi, "Reduction of power electronic elements in multilevel converters using a new cascade structure," *IEEE Trans. Ind. Electron.*, vol. 62, no. 1, pp. 256–259, Jun. 2015.

- [13] E. Samadaei, S. A. Gholamian, A. Sheikholeslami, and J. Adabi, "An envelope type (E-type) module: Asymmetric multilevel inverters with reduced components," *IEEE Trans. Ind. Electron.*, vol. 63, no. 11, pp. 7148–7156, Nov. 2016.

- [14] I. A. Harbi, H. Z. Azazi, A. E. Lashine, and A. E. Elsabbe, "A higher levels multilevel inverter with reduced number of switches," *Int. J. Electron.*, vol. 105, no. 8, pp. 1286–1299, Aug. 2018.

- [15] T. Venkat and P. Somasundaran, "New asymmetric 21-level inverter with reduced number of switches," *J. Eng. Res. [TJER]*, vol. 16, no. 1, p. 18, May 2019.

- [16] P. Prem, V. Sugavanam, A. I. Abubakar, J. S. M. Ali, B. C Sengodan, V. Krishnasamy, and S. Padmanaban, "A novel cross-connected multilevel inverter topology for higher number of voltage levels with reduced switch count," *Int. Trans. Electr. Energy Syst.*, vol. 30, no. 6, Jun. 2020, Art. no. e12381, doi: 10.1002/2050-7038.12381.

- [17] S. B. Santra, K. Kumar, P. Biswal, and C. K. Panigrahi, "Lyapunov based fast terminal sliding mode Q-V control of grid connected hybrid solar PV and wind system," *IEEE Access*, vol. 6, pp. 39139–39153, 2018.

- [18] Y. Yang, H. Wen, and D. Li, "A fast and fixed switching frequency model predictive control with delay compensation for three-phase inverters," *IEEE Access*, vol. 5, pp. 17904–17913, 2017.

- [19] B. Sharma and J. Nakka, "Single-phase cascaded multilevel inverter topology addressed with the problem of unequal photovoltaic power distribution in isolated DC links," *IET Power Electron.*, vol. 12, no. 2, pp. 284–294, Feb. 2019.

- [20] M. F. Kangarlu and E. Babaei, "A generalized cascaded multilevel inverter using series connection of submultilevel inverters," *IEEE Trans. Power Electron.*, vol. 28, no. 2, pp. 625–636, Feb. 2013.

- [21] N. A. Behzadi, A. Namadmalan, and A. Rahdarian, "Cascaded H-bridge multilevel inverters with discrete variation of DC sources," *Int. J. Electron.*, vol. 2106, no. 10, pp. 1480–1497, 2019.

- [22] A. S. A. Ibrahim, P. Anbalagan, and J. S. M. Ali, "A new asymmetric and cascaded switched diode multilevel inverter topology for reduced switches, DC source and blocked voltage on switches," *J. Circuits, Syst. Comput.*, vol. 28, no. 4, 2018, Art. no. 1950064.

- [23] S. A. A. Ibrahim, A. Palanimuthu, and M. A. J. Sathik, "Symmetric switched diode multilevel inverter structure with minimised switch count," *J. Eng.*, vol. 2017, no. 8, pp. 469–478, Aug. 2017.

- [24] Y. Liu, H. Hong, and A. Q. Huang, "Real-time algorithm for minimizing THD in multilevel inverters with unequal or varying voltage steps under staircase modulation," *IEEE Trans. Ind. Electron.*, vol. 56, no. 6, pp. 2249–2258, Jun. 2009.

- [25] R. S. Alishah, D. Nazarpour, S. H. Hosseini, and M. Sabahi, "Novel topologies for symmetric, asymmetric, and cascade switched-diode multilevel converter with minimum number of power electronic components," *IEEE Trans. Ind. Electron.*, vol. 61, no. 10, pp. 5300–5310, Oct. 2014.

- [26] D. Eaton, J. Rama, and P. Hammond, "Neutral shift [five years of continuous operation with adjustable frequency drives]," *IEEE Ind. Appl. Mag.*, Vol. 9, no. 6, pp. 40–49, Nov. 2003.

- [27] A. R. Beig and A. Dekka, "Experimental verification of multilevel inverter-based standalone power supply for low-voltage and low-power applications," *IET Power Electron.*, vol. 5, no. 6, pp. 635–643, Jul. 2012.

- [28] G. Sen and M. E. Elbuluk, "Voltage and current-programmed modes in control of the Z-Source converter," *IEEE Trans. Ind. Appl.*, vol. 46, no. 2, pp. 680–686, 2010.

- [29] M. Jayabalan, B. Jeevarathinam, and T. Sandirasegarane, "Reduced switch count pulse width modulated multilevel inverter," *IET Power Electron.*, vol. 10, no. 1, pp. 10–17, Jan. 2017.

- [30] C. D. Fuentes, C. A. Rojas, H. Renaudineau, S. Kouro, M. A. Perez, and T. Meynard, "Experimental validation of a single DC bus cascaded H-bridge multilevel inverter for multistring photovoltaic systems," *IEEE Trans. Ind. Electron.*, vol. 64, no. 2, pp. 930–934, Feb. 2017.

**PREM PONNUSAMY** (Member, IEEE) received the B.E., M.E., and Ph.D. degrees from the Faculty of Electrical Engineering, Anna University, Chennai, in 2006, 2008, and 2018, respectively. From then, he was working as an Assistant Professor with the Department of Electrical and Electronics Engineering, Bannari Amman Institute of Technology, where he is currently working as an Associate Professor. His research interests include power systems and power converters for renewable energy stems.

**PANDARINATHAN SIVARAMAN** received the B.E. degree from Bharathiar University, in 2002, the M.Tech. degree from SASTRA University, in 2004, and the Ph.D. degree from Anna University, in 2014. He started the carrier as a Lecturer, in 2004, and currently working as an Associate Professor with the Bannari Amman Institute of Technology, India. He has published many papers in SCI and Scopus indexed journals and conferences. He also filed five national patents to his

credit. His current research interests include solar PV power conversion technology, stability analysis and controller design, EMI shielding, EV charging, and power quality.

**DHAFER J. ALMAKHLES** (Senior Member, IEEE) received the B.E. degree in electrical engineering from the King Fahd University of Petroleum and Minerals, Dhahran, Saudi Arabia, in 2006, and the master's (Hons.) and Ph.D. degrees from The University of Auckland, New Zealand, in 2011 and 2016, respectively. Since 2016, he has been with Prince Sultan University, Saudi Arabia, where he is currently the Chairman of the Department of Communications and

Networks Engineering and the Director of the Science and Technology Unit. He is also the Leader of the Renewable Energy Laboratory, Prince Sultan University. He has authored many published articles in the area of control systems and power electronics. He served as a Reviewer for many journals, including IEEE TRANSACTIONS ON FUZZY SYSTEMS, IEEE TRANSACTIONS ON CONTROL OF NETWORK SYSTEMS, IEEE TRANSACTIONS ON INDUS-TRIAL ELECTRONICS, IEEE TRANSACTIONS ON CONTROL SYSTEMS TECHNOLOGY, IEEE CONTROL SYSTEMS LETTERS, and *International Journal of Control*. His research interests include the hardware implementation of control theory, signal processing, networked control systems, nonlinear control design, unmanned aerial vehicle (UAV), and renewable energy.

**ZBIGNIEW LEONOWICZ** (Senior Member, IEEE) received the M.Sc., Ph.D., and Dr.Sci. degrees in electrical engineering from the Wroclaw University of Science and Technology, Wroclaw, Poland, in 1997 and 2001, respectively, and the Habilitation degree from the Bialystok University of Technology, Bialystok, Poland, in 2012. Since 1997, he has been with the Department of Electrical Engineering, Wroclaw University of Science and Technology, where he is

currently an Associate Professor. His current research interests include power quality, control and protection of power systems, renewables, industrial ecology, and applications of advanced signal processing methods in power systems.

**SANJEEVIKUMAR PADMANABAN** (Senior Member, IEEE) received the bachelor's degree in electrical engineering from the University of Madras, Chennai, India, in 2002, the master's degree (Hons.) in electrical engineering from Pondicherry University, Puducherry, India, in 2006, and the Ph.D. degree in electrical engineering from the University of Bologna, Bologna, Italy, in 2012.

He was an Associate Professor with VIT University, from 2012 to 2013. In 2013, he joined the National Institute of Technology, India, as a Faculty Member. In 2014, he was invited as a Visiting Researcher with the Department of Electrical Engineering, Qatar University, Doha, Qatar, funded by the Qatar National Research Foundation (Government of Qatar). He continued his research activities with the Dublin Institute of Technology, Dublin, Ireland, in 2014. Further, he served an Associate Professor with the Department of Electrical and Electronics Engineering, University of Johannesburg, Johannesburg, South Africa, from 2016 to 2018. Since 2018, he has been a Faculty Member with the Department of Energy Technology, Aalborg University at Esbjerg, Denmark. He has authored more than 300 scientific articles.

Dr. Padmanaban is a Fellow of the Institution of Engineers, India, the Institution of Electronics and Telecommunication Engineers, India, and the Institution of Engineering and Technology, U.K. He was a recipient of the Best Paper cum Most Excellence Research Paper Award from IET-SEISCON'13, IET-CEAT'16, IEEE-EECSI'19, and IEEE-CENCON'19, and five best paper awards from ETAEERE'16 sponsored Lecture Notes in Electrical Engineering, Springer book. He is an Editor/Associate Editor/Editorial Board Member of refereed journals, in particular the IEEE Systems JOURNAL, IEEE TRANSACTIONS ON INDUSTRY APPLICATIONS, IEEE Access, *IET Power Electronics, Electronics Letters* (IET), and *International Transactions on Electrical Energy Systems* (Wiley), a Subject Editorial Board Member of *Energy Sources* and *Energies* (MDPI), and the Subject Editor of *IET Renewable Power Generation, IET Generation, Transmission and Distribution*, and *Obesity Facts* journal, Canada.

**MATHESWARAN ALAGU** (Member, IEEE) received the B.E. degree in electrical and electronics engineering, the M.E. degree in power electronics and drives, and the Ph.D. degree from Anna University, Chennai, India. He is currently working as an Assistant Professor with the Department of Electrical and Electronics Engineering, Bannari Amman Institute of Technology, India, and has over ten years of teaching experience. His research interests include power converters for

renewable energy sources, industrial drives, and power quality.

JAGABAR SATHIK MOHAMED ALI (Senior Member, IEEE) was born in Thanjavur, India, in 1979. He received the B.E. degree in electronics and communication engineering from Madurai Kamaraj University, Madurai, India, in 2002, and the M.E. and Ph.D. degrees from the Faculty of Electrical Engineering, Anna University, Chennai, India, in 2004 and 2016, respectively. He is currently a Postdoctoral Fellow with the Renewable Energy Laboratory, College of Engineering, Prince

Sultan University, Riyadh, Saudi Arabia. He is a Consultant of various power electronics companies for the design of power electronics converters. He has authored more than 40 papers publications in international journals and conference proceedings. His current research interests include multilevel inverters, grid-connected inverters, and power electronics converters and its applications to renewable energy systems. He was a recipient of the Certificate of Recognition Award for the second-highest article published in IEEE journals, from 2018 to 2019, under the IEEE Madras Section.

....