Received July 24, 2020, accepted September 6, 2020, date of publication September 18, 2020, date of current version October 12, 2020. Digital Object Identifier 10.1109/ACCESS.2020.3024549

# Online Fault Diagnosis Method for High-Performance Converters Using Inductor Voltage Polar Signatures

#### LI CHEN<sup>1,2</sup>, XIAOLI ZHAO<sup>1,3</sup>, AND SHENG XUE TANG<sup>(D),2</sup>

<sup>1</sup>State Key Laboratory of Reliability and Intelligence of Electrical Equipment, School of Electrical Engineering, Hebei University of Technology, Tianjin 300130, China

<sup>2</sup>Key Laboratory of Electromagnetic Field and Electrical Apparatus Reliability of Hebei Province, School of Electrical Engineering, Hebei University of Technology, Tianjin 300130, China

<sup>3</sup>State Grid Shandong Electric Power Company, Lanling County Power Supply Company, Shandong 276000, China

Corresponding author: Sheng Xue Tang (tsx@hebut.edu.cn)

This work was supported in part by the National Natural Science Foundation of China under Grant 51377044, and in part by the Hebei Natural Science Fund Key Project under Grant E2017202284.

**ABSTRACT** Recently, the high-performance converter with wide range and high gain has been widely used in these cases such as PV power generation. On the other hand, there are more highly variable stresses on switch and diode in high-performance converter than the traditional DC-DC converters due to the wide range and high gain. Therefore, it is necessary to diagnose switch and diode faults in high-performance converter. In this paper, the switch and diode fault are analyzed and compared with traditional DC-DC converters. Then, an online diagnosis technique based on the inductor voltage polarity of the DC-DC converter is proposed. This technique only uses the inductor voltage polarity and the switch gate drive signal as signatures to diagnose short-circuit or open-circuit fault of the switch and diode. The technique is cost-effective and simple because it uses simple auxiliary windings to sense the inductor voltage polar and uses some logic circuit to generate indicators. The details of the technique are discussed through an example of the quadratic Boost converter. Experiments illustrate the correctness of the proposed technique and show its capability for switch and diode fault diagnosis.

**INDEX TERMS** Quadratic DC-DC converter, fault diagnosis, inductor voltage, and switch.

#### I. INTRODUCTION

In recent years, new energy resources such as photovoltaic (PV) cells, wind power, and fuel cell, have been widely used to reduce air pollution from oil resources and others. In these cases, the high-performance converter, such as the quadratic Boost converter, gradually replaces the traditional Boost converter for the advantages of the wide input/output range, high gain, and low cost.

On the other hand, it is vital to assure the safety and reliability of the power generation system in the new energy resource applications. Faults occur in the DC-DC converter, which will cause the power generation system malfunction or reduce the efficiency, and in some cases will cause the second faults. According to statistical research, electrolytic capacitors and power semiconductor devices are the most vulnerable components in the DC-DC converters. More

The associate editor coordinating the review of this manuscript and approving it for publication was Fengjiang Wu<sup>(b)</sup>.

than 30% of converter failures are due to semiconductor devices [1]. Therefore, switch and diode fault diagnosis is essential to achieve desirable reliability for DC-DC converter [2].

Fault detection and diagnosis techniques aiming to the different kinds of converters have attracted many researchers. The traditional non-isolated DC–DC converters faults, such as OCF (open-circuit fault) and SCF (short-circuit fault) of switch and diode, have been widely studied. For example, fast diagnosis methods for switch faults in traditional Buck circuits were investigated in Ref [3], [4]. Fault diagnoses of matrix converters were studied in Ref [5]–[7] and fault diagnoses of multi-level DC-DC converters were studied in Ref [8]–[13]. The fault diagnoses method of zero voltage switch (ZVS) DC-DC converters were studied in Ref [14]. In these diagnoses, it is critical to select and extract fault signatures in implementation of fault diagnosis. In the previous works, output voltage/current [15], inductor voltage/current [16], [17], diode voltage [18],

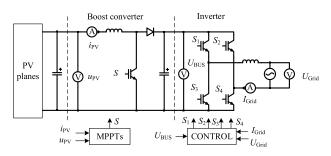

FIGURE 1. The most common configuration for grid-connected photovoltaic systems.

magnetic near field waveform [19], and on-state resistance [20] have been used as signatures for switch and diode fault diagnosis in traditional non-isolated DC-DC converters. The inductor voltages captured by an auxiliary winding combined with logic circuits have been utilized to detect switch faults in traditional non-isolated dc–dc converters [18], [21]. This technique is simple and cost-effective.

In fact, there are more highly variable stresses on switch and diode in high-performance converter than the traditional DC-DC converters due to the wide range and high gain, which make switch and diode more fault-prone. But fewer signatures mentioned can be directly applied to diagnose switch faults in the high-performance converters, such as the quadratic single-switch DC-DC converters. In some cases, output voltage/current used as signatures for fault detection is cost-effective. However, these signatures are not suitable for quadratic non-isolated DC-DC converter in the PV power system. For example, Figure 1 illustrates the output/input voltage/current of the Boost converter in the PV power generation grid-connected system, which has been measured for system operation. However, input voltage/current is subject to the PV cells for tracking maximum power points (MPPTs) and output voltage/current is subject to the DC-AC converter for power balancing [22], which results in considerable error detection rate. Secondly, a large LC filter leads to detection delay [2], [23], [24].

Aim to the fault diagnosis of the switch and diode in high performance converters, such as quadratic converters, this paper proposes a new diagnosis method, in which the voltage of the magnetic component that is easier to extract and the switch gate drive signal are selected as the fault detection signals. According to the voltage of the magnetic component before and after the failure of the switch tube and diode, fault diagnosis circuit is designed based on the characteristics of the change. This technology has the advantages of low cost, easy operation, wide fault coverage, good online performance, and fast speed. The proposed method is suitable for quadratic single-switch DC-DC converters, including but not limited to quadratic Boost converters, quadratic Buck converters, and quadratic Buck-Boost converters, and has good scalability.

The rest of this article is organized as follows. In Section 2, the existing faults diagnosis technology for the switch and diode of the Buck converter is described in brief. The basic

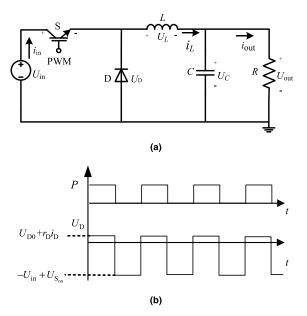

FIGURE 2. Buck converter: (a) circuit diagram; (b) gate signal and diode voltage for normal condition.

configuration and operation process of the high-performance converter are given in Section 3. In Section 4, the fault conditions of switch tubes and diodes of high-performance converters are analyzed, and fault diagnosis techniques that can judge the fault types are proposed. In Section 5, a simple logic fault diagnosis circuit is designed to perform fault diagnosis on high-performance converters. Section 6 includes some experimental results, and the final section gives conclusions.

#### II. PREVIOUS POWER DEVICE FAULT DIAGNOSIS METHODS

Reliable operation of DC-DC converters is vital for many applications. An appropriate converter monitoring scheme is required for fault detection and the adoption of effective remedial strategies. Ref [18] presents a simple diagnosis technique for open-circuits and short-circuits faults of the switch and diode in single inductance traditional Non-isolated DC-DC converter, such as Buck converter shown in Figure 2. The technique only employs diode voltage as the detection signature. In this paper, not only the diode voltage is used as signature, but also the gate driver signal is used to be processed in a simple logic circuit to generate some indicators for switch and diode fault diagnosis. Now contents of the technique using these signatures are discussed in detail.

The fault diagnosis technique in Ref [18] aims to detect four types of fault in Buck converters including switch OCF, switch SCF, diode OCF, and diode SCF.

Figure 2(a) illustrates a Buck converter in which different parameters of the converter are denoted for analysis. In Figure 2(a) parameters P,  $U_{in}$ ,  $U_D$ ,  $U_L$ , and  $U_{out}$  represent gate signal as well as voltages of input supply, diode, inductor, and output, respectively.

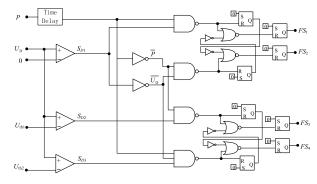

FIGURE 3. Logic circuit of the proposed fault diagnosis technique.

The converter switch, diode, inductor, capacitor, and load are denoted by S, D, L, C, and R, respectively. Currents of input supply, diode, and inductor are denoted by  $i_{in}$ ,  $i_D$ , and  $i_L$ , respectively. Waveforms of the gate drive signal P and diode voltage for the converter normal operation are depicted in Figure 2(b). In this figure, K, T,  $U_{D0}$ ,  $U_{Son}$ , and  $r_D$  denote the duty cycle of the gate signal, period of the gate signal, diode built-in potential, on state voltage drop of the switch, and diode internal resistance, respectively. Using Kirchhoff's voltage law (KVL) in Figure 2(a), the diode voltage could be expressed as  $P = 0 \Rightarrow$  Switch: OFF  $\Rightarrow U_D = U_{D0} + r_D i_D$ ,  $P = 1 \Rightarrow$  Switch: ON  $\Rightarrow U_D = -U_{in} + U_{Son}$ . Due to  $U_{D0}$  and  $r_{\rm D}i_{\rm D}$  are positive so when  $P = 0, U_{\rm D} > 0$ . Due to  $U_{\rm Son} \ll U_{\rm in}$ so when P = 1,  $U_D < 0$ . It should be noted that for the sake of simplicity, diode conduction current and on-state voltage drop of the switch are assumed to be constant in Figure 2(b).

Through the analysis of open circuit and short circuit faults of the switch tube and diode of the Boost converter, the following Equ (1) can be obtained to judge the fault condition of the Buck converter, where  $U_{th1}$  and  $U_{th2}$  can be seen in Ref [15], [18]:

$$if P = 1 and U_D > 0 \Rightarrow switch OCF if P = 0 and U_D < 0 \Rightarrow switch SCF if P = 0 and U_D > U_{th1} \Rightarrow diode OCF if P = 1 and U_{th2} < U_D < 0 \Rightarrow diode SCF$$

$$(1)$$

Figure 3 Show the Buck converter logic circuit for diagnosis, four signals denoted by  $FS_1$ ,  $FS_2$ ,  $FS_3$ , and  $FS_4$  are generated as indicators of switch OCF, switch SCF, diode OCF, and diode SCF, respectively. In fact, Equ (1) is realized through the logic circuit. Initial setting for inputs of all Reset-Set (SR) flip-flops is S = 1, R = 0. As a result, Q outputs of all flip-flops are initially at a high level. In the next step, S inputs of the flip-flops are set to zero as observed in Figure 3. The research results of previous papers show that the fault diagnosis circuit can accurately and quickly diagnose the switching tube and diode faults of the Buck converter.

However, the diode voltage as the detection signature needs to add one independently auxiliary transformer and is not suitable for high-performance converters, such as the quadratic Boost converter, shown in Figure 4.

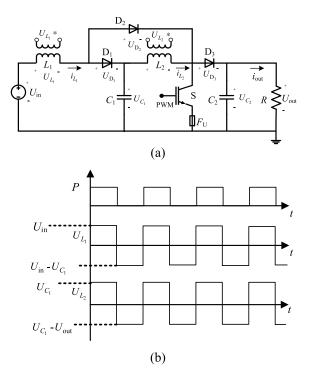

FIGURE 4. Quadratic Boost converter: (a) Quadratic Boost converter circuit diagram; (b) gate signal and inductor voltage for normal case.

## III. BASIC CONFIGURATION AND OPERATIONAL PROCESS OF HIGH-PERFORMANCE CONVERTER

In this paper, the quadratic Boost converter is discussed as an example for fault diagnosis. Figure 4 shows the quadratic Boost converter and the waveforms of inductor voltages and gate driving signals. The structure is composed of pre-stage circuit, including inductor  $L_1$ , diode  $D_1$  and  $D_2$ , capacitor  $C_1$ and switch S, and post-stage circuit including inductor  $L_2$ , capacitor  $C_2$ , diode  $D_3$  and switch S. In order to avoid the occurrence of secondary fault, the switch S is in series with fuse  $F_U$ .

In Figure 4, parameters P,  $U_{in}$ ,  $U_L$ , and  $U_{out}$  represent gate driving signal as well as voltages of input supply, inductor, and output, respectively. Currents of input supply, output, and inductor are denoted by  $i_{in}$ ,  $i_{out}$ , and  $i_L$ , respectively.

The faults considered in this paper are switch and diode faults, including switch SCF, switch OCF, diode  $D_1$  SCF, diode  $D_1$  OCF, diode  $D_2$  SCF, diode  $D_2$  OCF, diode  $D_3$  SCF, and diode  $D_3$  OCF.

Traditionally, the electrical quantities used to diagnose the fault of the DC-DC converter include the voltage across the switch, the diode voltage, the inductor voltage and current, and the output voltage. If the output voltage is selected as the fault diagnosis feature, the output voltage is easily affected by the load. Due to the existence of output filtering, the output control variable changes slowly and the diagnosis time is long. For the quadratic Boost converter, the number of diodes is large. If the diode voltage is selected, it is difficult to effectively determine the diode fault through analysis. Moreover, after the diode  $D_2$  of the quadratic Boost converter

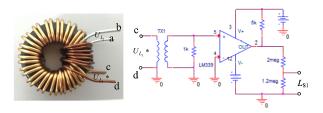

**FIGURE 5.** The auxiliary winding for L1 and sign of the post-processing circuit.

has an open-circuit fault, the circuit is equivalent to a traditional Boost converter. Therefore, it is difficult to distinguish whether the circuit is faulty using the traditional output voltage or output current as the characteristic electrical quantity for fault diagnosis. If both the inductor voltages  $U_{L_1}, U_{L_2}$ are selected as fault diagnosis characteristics at the same time, the electrical quantity can correctly reflect the fault while improving the fault diagnosis efficiency and reducing the cost. The inductor voltage can be obtained by adding auxiliary windings to the corresponding magnetic core. The auxiliary windings and signs of the post-processing circuits are shown in Fig 4(a).

In summary,  $U_{L_1}$  and  $U_{L_2}$  are selected as the electrical quantities for the fault diagnosis of the quadratic Boost converter. The follow-up diagnosis method only needs to use the polarity of  $U_{L_1}$  and  $U_{L_2}$  in combination with the drive signal P to make a logical combination to judge the open circuit and short circuit fault of the switch tube or diode. The auxiliary winding processing circuit and the circuit for obtaining the polarity of the inductor voltage is shown in Fig 5. Sign of  $U_{L_1}$  and its polarity indication signal  $L_{S1}$  is given. In fact, a sign of  $U_{L_2}$ ,  $U_{L_2} - U_{L_1}$  of their directors  $L_{S2}$ ,  $L_{S3}$  can be obtained similarly. The principle of fault diagnosis is described in the following.

According to the operation of the quadratic Boost converter, let the duty ratio  $K = T_{on}/T$ , where T is the switching period,  $T_{on}$  is switch turn-on time in one switching period, then the voltage of capacitor  $U_{C1}$  and output voltage  $U_{out}$  is calculated using Equ (2) as follows:

$$\begin{cases} U_{C_1} = \left(\frac{1}{1-K}\right) U_{\text{in}} \\ U_{\text{out}} = \left(\frac{1}{1-K}\right)^2 U_{\text{in}} \end{cases}$$

(2)

According to Equ (2), the following equations can be obviously deduced:

$$\begin{cases} U_{C_1} > U_{\text{in}} \\ U_{\text{out}} = U_{C_2} > U_{C_1} \end{cases}$$

(3)

And

$$U_{\rm out} - U_{C_1} > U_{C_1} - U_{\rm in} \tag{4}$$

Using Kirchhoff's voltage law (KVL) in Fig 4(a), the voltage of the inductors  $L_1$  and  $L_2$  under normal cases are

expressed as:

$$P = 1 \Rightarrow \begin{cases} U_{L_1} = L_1 \frac{di_{L_1}}{dt} = U_{\text{in}} > 0\\ U_{L_2} = L_2 \frac{di_{L_2}}{dt} = U_{C_1} > 0 \end{cases}$$

(5)

and

1

$$P = 0 \Rightarrow \begin{cases} U_{L_1} = L_1 \frac{di_{L_1}}{dt} = U_{\text{in}} - U_{C_1} < 0\\ U_{L_2} = L_2 \frac{di_{L_2}}{dt} = U_{C_1} - U_{\text{out}} < 0 \end{cases}$$

(6)

The signs of  $U_{L_1}$ ,  $U_{L_2}$  and  $U_{L_2} - U_{L_1}$  are related to the driving signal *P* and fault states of switch and diodes. According to Figure 4, the inductor voltages,  $U_{L_1}$ ,  $U_{L_2}$  are given in Table 1. It should be noted in Table 1 that the considered quadratic Boost converter operates in continuous-conduction mode [25].

#### IV. PROPOSED FAULT DIAGNOSIS TECHNIQUE OF HIGH-PERFORMANCE CONVERTER

A. SWITCH SCF AND OCF

#### 1) SWITCH SCF

In the case of switch SCF, when P = 1, the states of the converter are consistent with the normal states. Switch SCF is not diagnosable while P = 1. When P = 0, switch SCF occurs, which causes that currents of inductors  $L_1$  and  $L_2$  flow through the switch. According to KVL, in this case the inductor voltage values  $U_{L_1} = U_{\text{in}}$  and  $U_{L_2} = U_{C_1}$  are obtained, which are different from the values  $U_{L_1} = U_{\text{in}} - U_{C_1}$  and  $U_{L_2} = U_{C_1} - U_{\text{out}}$  in normal case, respectively. Therefore, Switch SCF is detected when P = 0. These results in the case of switch SCF are shown in Table 1.

As described in Equ (3)-(6), we easily know that  $U_{in} > 0$ and  $U_{C_1} > 0$ , and  $U_{in} - U_{C_1} < 0$  and  $U_{C_1} - U_{out} < 0$ .

Therefore, fault diagnosis logic relation of the switch SCF is:

if

$$\begin{cases} P = 0 \\ U_{L_1} > 0 \text{ or } U_{L_2} > 0 \end{cases} \Rightarrow \text{switch SCF has occurred}$$

(7)

If switch SCF occurs during P = 0, it would be detected immediately; if it occurs during P = 1, it would not be detected until the instant at which P changes to 0. Therefore, the maximum delay for switch SCF detection is KT, which is less than one switching cycle.

#### 2) SWITCH OCF

In the case of switch OCF, when P = 0, the states of the converter are consistent with the normal states. Switch OCF is not diagnosable while P = 0. When P = 1, switch OCF occurs, which causes that currents of inductors  $L_1$  and  $L_2$  not flow through the switch. According to KVL, in this case the inductor voltage values  $U_{L_1} = U_{in} - U_{C_1}$  and  $U_{L_2} = U_{C_1} - U_{out}$  are obtained, which are different from the values  $U_{L_1} = U_{in}$  and  $U_{L_2} = U_{C_1}$  in normal case, respectively. Therefore, Switch OCF is detected when P = 1. These results in case of switch OCF are shown in Table 1.

| Detection volume<br>Fault status | Р | $U_{L_1}$                    | $U_{L_2}$                                       |

|----------------------------------|---|------------------------------|-------------------------------------------------|

| Normal                           | 1 | $U_{i\mathrm{n}}$            | $U_{C_1}$                                       |

|                                  | 0 | $U_{\rm in} - U_{C_1}$       | $U_{C_1} - U_{\text{out}}$                      |

| Switch SCF                       | 1 | $U_{ m in}$                  | $U_{C_1}$                                       |

|                                  | 0 | $U_{ m in}$                  | $U_{C_1}$                                       |

| Switch OCF                       | 1 | $U_{\rm in} - U_{C_1}$       | $U_{C_1} - U_{\text{out}}$                      |

|                                  | 0 | $U_{\rm in} - U_{C_1}$       | $U_{C_1} - U_{\text{out}}$                      |

| D <sub>1</sub> SCF               | 1 | resonates                    | 0                                               |

|                                  | 0 | resonates                    | 0                                               |

| D <sub>1</sub> OCF               | 1 | $U_{ m in}$                  | $U_{C_1}$                                       |

|                                  | 0 | $U_{\rm in}$ – $U_{\rm out}$ | $U_{C_1} - U_{\text{out}}$                      |

| D <sub>2</sub> SCF               | 1 | $U_{ m in}$                  | $U_{C_1}$                                       |

|                                  | 0 | $U_{\rm in} - U_{C_1}$       | 0                                               |

| D <sub>2</sub> OCF               | 1 | $U_{\rm in} - U_{C_1}$       | $U_{C_1}$                                       |

|                                  | 0 | $U_{\rm in} - U_{C_1}$       | $U_{C_1} - U_{\text{out}}$                      |

| D <sub>3</sub> SCF               | 1 | 0                            | resonates                                       |

|                                  | 0 | 0                            | resonates                                       |

| D <sub>3</sub> OCF               | 1 | $U_{ m in}$                  | $U_{C_1}$                                       |

|                                  | 0 | $U_{\rm in} - U_{C_1}$       | $U_{C_1} - U_{\text{out}} - R_{\infty} i_{L_2}$ |

| TABLE 1. The relationship between detection variables and operat | ing |

|------------------------------------------------------------------|-----|

| status of quadratic Boost converter.                             |     |

As described previously, we know that  $U_{in} - U_{C_1} < 0$  and  $U_{C_1} - U_{out} < 0$ . Therefore, fault diagnosis logic relation of the switch OCF is:

if

$$\begin{cases} P = 1 \\ U_{L_1} < 0 \text{ or } U_{L_2} < 0 \end{cases} \Rightarrow \text{switch OCF has occurred} (8)$$

If switch OCF occurs during P = 1, it would be detected immediately; if it occurs during P = 0, it would not be detected until the instant at which P changes to 1. Therefore, the maximum delay for switch OCF detection is (1-K)T, which is less than one switching cycle.

#### B. D<sub>1</sub> SCF AND OCF

#### 1) D1 SCF

In the case of D<sub>1</sub> SCF, when P = 0, the states of converter are consistent with the normal states. When P = 1, D<sub>2</sub> turns on, D<sub>3</sub> turns off. In this case, there exist two short branches, the  $L_2$ -D<sub>1</sub>-D<sub>2</sub> branch and the  $C_1$ -D<sub>1</sub>-D<sub>2</sub>-S branch. The energy stored in  $L_2$  and  $C_1$  are discharged through D<sub>2</sub> and S rapidly, which will easily lead to the secondary failure of S and D<sub>2</sub>. Therefore, the F<sub>U</sub> shown in Fig 4 blows out at the instant of D<sub>1</sub> SCF occurrence. After that instant, whether P = 0 or P = 1, switch S branch is always open, and the branch  $L_1$ -D<sub>1</sub>- $C_1$ - $U_{in}$ resonates and  $U_{L_1}$  gradually attenuates in a period of time. At the same instant, the current  $i_{L_2}$  flows through the branch  $L_2$ -D<sub>1</sub>-D<sub>2</sub>. Considering  $r_{D_1,SCF}$  and  $r_{D_2}$  as the D<sub>1</sub> resistance after D<sub>1</sub> SCF and the diode D<sub>2</sub> on-resistance, respectively, the inductance voltage  $U_{L_2}$  in the D<sub>1</sub> SCF case is expressed as follows:

$$U_{L_2} = i_{L_2}(r_{D_1,SCF} + r_{D_2})$$

(9)

In fact,  $U_{L_2}$  is almost equal to the on-state voltage  $U_{D_2,on}$  at the instant and then quickly attenuates to zero. Therefore,  $U_{L_2}$  and P = 1 are used for detecting D<sub>1</sub> SCF. These results in case of D<sub>1</sub> SCF are shown in Table 1.

As described in Equ (9) and to reduce noise interference, we choose two threshold voltages  $U_{\text{th1}} = U_{\text{D}_2, \text{ on}}$  and  $U_{\text{th2}} = -U_{\text{D}_2, \text{ on}}$  to obtain the signature of  $U_{L_2}$  with a comparator. Therefore, fault diagnosis logic relation of the D<sub>1</sub> SCF is:

if

$$\begin{cases} P = 1 \\ U_{L_2} < U_{\text{th}1} \Rightarrow D_1 \text{ SCF has occured} \\ U_{L_2} > U_{\text{th}2} \end{cases}$$

(10)

Whether  $D_1$  SCF occurs during P = 0 or P = 1, the fault detection will be delayed after two switching cycles.

2) D1 OCF

In the case of D<sub>1</sub> OCF, when P = 1, D<sub>2</sub> turns on and D<sub>3</sub> turns off, the states of the converter are consistent with the normal states. When P = 0, the current of  $L_1$  flows through D<sub>2</sub> and D<sub>3</sub>. According to KVL, in this case the inductor voltage values  $U_{L_1} = U_{in} - U_{out}$  and  $U_{L_2} = U_{C_1} - U_{out}$  are obtained. The value  $U_{L_1} = U_{in} - U_{out}$  is different from the value  $U_{L_1} = U_{in} - U_{C_1}$  in normal case. Therefore, D<sub>1</sub> OCF is detected when P = 0. These results in the case of D<sub>1</sub> OCF are shown in Table 1.

As described in Equ (6),  $U_{L_1}$  and  $U_{L_2}$  are both less than 0 when P = 0, and the polarity of the inductor voltage is consistent with the normal state. So, the polarity of inductor voltages cannot be used as D<sub>1</sub> OCF signature. Under normal case and P = 0, according to Equ (2)-(6) we obtain  $U_{L_1} - U_{L_2}$  as follows:

$$U_{L_1} - U_{L_2} = U_{\text{in}} - 2U_{C_1} + U_{\text{out}} = \left(\frac{K}{1 - K}\right)^2 U_{\text{in}} > 0 \quad (11)$$

And when P = 0 and in case of D<sub>1</sub> OCF,  $U_{L_1} - U_{L_2}$  is as follows:

$$U_{L_1} - U_{L_2} = U_{\text{in}} - U_{C_1} = \left(-\frac{K}{I - K}\right) U_{\text{in}} < 0$$

(12)

Therefore, the polarity of  $U_{L_1} - U_{L_2}$  is used as D<sub>1</sub> OCF signature and the diagnosis logic relation of the D<sub>1</sub> OCF is as follows:

if

$$\begin{cases} P = 0\\ U_{L_1} - U_{L_2} < 0 \Rightarrow D_1 \text{ OCF has occured} \\ U_{L_2} < 0 \end{cases}$$

(13)

If  $D_1$  OCF occurs during P = 0, it would be detected immediately; if it occurs during P = 1, it would not be

detected until the instant at which P changes to 0. Therefore, maximum delay for D<sub>1</sub> OCF detection is *KT*, which is less than one switching cycle.

#### C. D<sub>2</sub> SCF AND OCF

#### 1) D<sub>2</sub> SCF

In the case of D<sub>2</sub> SCF, when P = 1, the states of the converter are consistent with normal states. D<sub>2</sub> SCF is not diagnosable when P = 1. When P = 0 and D<sub>2</sub> SCF occurs, D<sub>1</sub> turns on, D<sub>3</sub> turns off. Since D<sub>1</sub> and D<sub>2</sub> simultaneously turn on, the inductor  $L_2$  is short-circuited. Considering  $r_{D_2,SCF}$  and  $r_{D_1}$  as the D<sub>2</sub> resistance after D<sub>1</sub> SCF and the diode D<sub>1</sub> on-resistance, respectively, and according to KVL, the inductor voltage values are  $U_{L_1} = U_{in} - U_{C_1}$  and  $U_{L_2} \approx U_{D_1,on} > 0$  is different from the value  $U_{L_2} = U_{C_1} - U_{out}$  in normal case. Therefore, D<sub>2</sub> SCF is detected when P = 0. These results in case of D<sub>2</sub> SCF are shown in Table 1.

Therefore, the fault diagnosis logic relation of the  $D_2$  SCF is as follows:

if

$$\begin{cases} P = 0\\ U_{L_1} < 0 \implies D_2 \text{ SCF has occured} \\ U_{L_2} > 0 \end{cases}$$

(14)

If  $D_2$  SCF occurs during P = 0, it would be detected immediately; if it occurs during P = 1, it would not be detected until the instant at which P changes to 0. Therefore, the maximum delay for  $D_2$  SCF detection is KT, which is less than one switching cycle.

#### 2) D<sub>2</sub> OCF

In the case of D<sub>2</sub> OCF, when P = 0, the states of the converter are consistent with normal states. D<sub>2</sub> OCF is not diagnosable when P = 0. When P = 1, D<sub>2</sub> OCF occurs, D<sub>1</sub> turns on and D<sub>3</sub> turns off. According to KVL, in this case the inductor voltage values are obtained as  $U_{L_1} = U_{in} - U_{C_1}$  and  $U_{L_2} =$  $U_{C_1}$ . The value  $U_{L_1} = U_{in} - U_{C_1}$  is different from the value  $U_{L_1} = U_{in}$  in normal case. Therefore, D<sub>2</sub> OCF is detected when P = 0. These results in case of D<sub>2</sub> SCF are shown in Table 1.

Because  $U_{L_1} = U_{in} - U_{C_1} < 0$  and  $U_{L_2} > 0$  when P = 1 in case of D<sub>2</sub> OCF. Therefore, fault diagnosis logic relation of the D<sub>2</sub> OCF is as follows:

if

$$\begin{cases} P = 1 \\ U_{L_1} < 0 \implies D_2 \text{ OCF has occured} \\ U_{L_2} > 0 \end{cases}$$

(15)

If D<sub>2</sub> OCF occurs during P = 1, it would be detected immediately; if it occurs during P = 0, it would not be detected until the instant at which P changes to 1. Therefore, the maximum delay for D<sub>2</sub> OCF detection is (1-K)T, which is less than one switching cycle.

#### D. D<sub>3</sub> SCF AND OCF

#### 1) D<sub>3</sub> SCF

In the case of D<sub>3</sub> SCF, when P = 0, the states of the converter are consistent with normal states and D<sub>3</sub> SCF is not diagnosable. D<sub>3</sub> SCF occurs when P = 1, D<sub>1</sub> turns off, D<sub>2</sub> turns on. In this case, branch  $C_2$ -D<sub>3</sub>-S is short. The energy stored in  $C_2$  is discharged through D<sub>3</sub> and S rapidly, and the F<sub>U</sub> shown in Fig 4 blows out at the instant of D<sub>3</sub> SCF occurrence. After that instant, whether P = 0 or P = 1, S branch is always open and D<sub>1</sub> turns on and D<sub>2</sub> turns off. And branch  $L_2$ - $C_1$ - $C_2$  resonates for a period of time and  $U_{L_2}$  gradually attenuates in a period of time to zero. At the same instant,  $i_{L_2}$  reduces to zero and  $U_{L_1}$  reduces to 0, quickly. These results in case of D<sub>3</sub> SCF are shown in Table 1.

In order to reduce noise interference, we choose two threshold voltages  $U_{\text{th}3} = U_{\text{D}_1, \text{ on}}$  and  $U_{\text{th}4} = -U_{\text{D}_1, \text{ on}}$ to obtain the signature of  $U_{L_1}$  with a window comparator. Therefore, fault diagnosis logic relation of the D<sub>3</sub> SCF is as follows:

if

$$\begin{cases} P = 1 \\ U_{L_1} < U_{\text{th}3} \implies D_3 \text{ SCF has occured} \\ U_{L_1} > U_{\text{th}4} \end{cases}$$

(16)

Whether  $D_3$  SCF occurs during P = 0 or P = 1, fault detection will be delayed after some switching cycles.

2) D<sub>3</sub> OCF

In the case of D<sub>3</sub> OCF, when P = 1, the states of the converter are consistent with the normal states and D<sub>3</sub> OCF is not diagnosable. D<sub>3</sub> OCF occurs when P = 0, D<sub>1</sub> and D<sub>2</sub> turn on. In this case, there is no freewheeling branch for  $L_2$  to discharge energy due to D<sub>3</sub> OCF, and switch S and diode D<sub>2</sub> experience a large electric shock. Considering the off-resistance of D<sub>3</sub> to be  $r_{D_3,off}$  and according to KVL, the inductor voltage values  $U_{L_1}$  and  $U_{L_2}$  are obtained as:

$$\begin{cases} U_{L_1} = U_{\text{in}} - U_{C_1} \\ U_{L_2} = U_{C_1} - U_{\text{out}} - r_{\text{D}_3, \text{off}} i_{L_2} \end{cases}$$

(17)

are obtained. The value  $U_{L_2} = U_{C_1} - U_{\text{out}} - r_{D_3,\text{off}}i_{L_2}$  is different from the value  $U_{L_2} = U_{C_1} - U_{\text{out}}$  in normal case. Therefore, D<sub>3</sub> OCF is detected when P = 0. These results in case of D<sub>3</sub> OCF are shown in Table 1.

Since  $r_{D_3,off}$  is large, the inductor voltage  $U_{L_2}$  has an extremely large negative voltage after D<sub>3</sub> OCF occurrence. Selecting a larger threshold voltage  $U_{th5}$  ( $U_{th5} = -V_{DC}/2$ ). it is easily known that  $U_{L_1} < 0$  and  $U_{L_2} < U_{th5}$ . Therefore, fault diagnosis logic relation of the D<sub>3</sub> OCF is as follows:

if

$$\begin{cases} P = 0\\ U_{L_1} < 0 \Rightarrow D_3 \text{ OCF has occured} \\ U_{L_2} < U_{\text{th5}} \end{cases}$$

(18)

If D<sub>3</sub> OCF occurs during P = 0, it would be detected immediately; if it occurs during P = 1, it would not be detected until the instant at which P changes to 0. Therefore,

FIGURE 6. Logic circuit for diagnosis of switch faults.

maximum delay for  $D_3$  OCF detection is *KT*, which is less than one switching cycle.

There are three common quadratic DC-DC converters, that is, quadratic Boost converter, quadratic Buck converter and quadratic Buck-Boost converter. The proposed diagnosis technique can be revised for quadratic Buck converter and quadratic Buck-Boost converter.

#### **V. THE FAULT DIAGNOSIS METHOD**

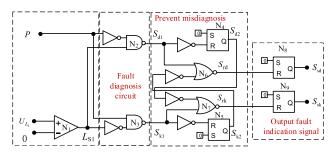

#### A. SWITCH FAULT DIAGNOSIS CIRCUIT

According to Section 3.1 analysis, the polar signature of voltage  $U_{L_2}$  and PWM signal is used for the switch faults and the fault diagnosis logic circuit, shown in Fig 6. The diagnosis circuit mainly consists of comparators, logic gates and R-S latches. The polar signature of voltage  $U_{L_1}$  is extracted by using the voltage comparator N<sub>1</sub> as the logic signal  $L_S$ , that is,  $U_{L_1} > 0$ ,  $L_{S1} = 1$ ;  $U_{L_1} < 0$ ,  $L_{S1} = 0$ . Available from Equ (7) and (8), the logic circuit is described as follows:

$$\begin{cases} P = 0, \quad L_{S1} = 1 \Rightarrow \text{switch SCF} \\ P = 1, \quad L_{S1} = 0 \Rightarrow \text{switch OCF} \end{cases}$$

(19)

It can be seen from Equ (19) that under fault states of switch S the signal P and the signal  $L_{S1}$  is an exclusive-or logic relation. Signals  $S_{sd}$  and  $S_{sk}$  in Fig 6 are used to indicate the short-circuit fault and the open circuit fault respectively, that is, the following logic expression is obtained:

$$\begin{cases} S_{\rm sd} = \overline{\overline{P}L_{\rm S1}} \\ S_{\rm sk} = \overline{P\overline{L}_{\rm S1}} \end{cases}$$

(20)

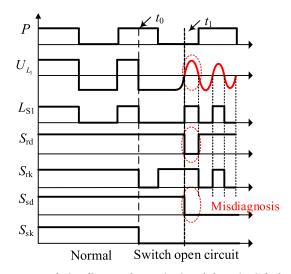

It should be pointed out that after the S OCF occurs, the parasitic capacitance of the inductor  $L_2$ , the switch S and the diode D<sub>2</sub> forms a series-resonant circuit, which leads to the signals  $S_{sd}$  and  $S_{sk}$  output error diagnosis results, shown in Fig 6 with red waveform. In order to avoid misdiagnosis, the error preprocessing circuit is added in Fig 7, and the preprocess logic relation is as follows:

$$\begin{cases} S_{\rm rd} = S_{\rm d1} \cup \overline{S_{\rm k2}} \\ S_{\rm rk} = S_{\rm k1} \cup \overline{S_{\rm d2}} \end{cases}$$

(21)

Finally, signals  $S_{rd}$ ,  $S_{rk}$  are latched in the R-S registers, and the fault indication signals  $S_{sd}$ ,  $S_{sk}$  is output.

FIGURE 7. Confusion diagram of open circuit and short-circuit faults.

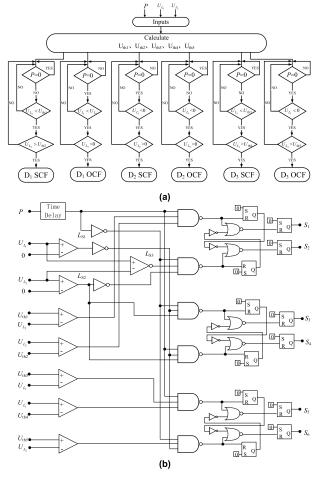

#### **B. DIODES FAULT DIAGNOSIS CIRCUIT**

Fig 8 presents the implementation of the proposed diagnosis technique for diode fault diagnosis. According to the results analyzed in Sections 4.2, 4.3, and 4.4, the logical signal P and the inductor voltages  $U_{L_1}$ , and  $U_{L_2}$  are used to diagnose diode faults. Six signals  $S_1$ ,  $S_2$ ,  $S_3$ ,  $S_4$ ,  $S_5$  and  $S_6$  are generated as indicators to represent D<sub>1</sub> SCF, D<sub>1</sub> OCF, D<sub>2</sub> SCF, D<sub>2</sub> OCF, D<sub>3</sub> SCF, and D<sub>3</sub> OCF, respectively. The conditions for P,  $U_{L_1}$  and  $U_{L_2}$  are checked, simultaneously, to generate the logical signatures. Same as section 5.1, the polarity of the inductor voltage, and can be extracted by using a voltage comparator,  $U_{L_2} > 0$ ,  $L_{S2} = 1$ ;  $U_{L_3} < 0$ ,  $L_{S3} = 0$ .

According to the Equ (10), (13), (14), (15), (16) and (18), the flowchart for diode fault diagnosis is presented in Fig 8(a), which are divided into six parallel procedures.

The proposed algorithm, shown in Fig 8(a), is implemented with a diagnosis logical circuit, shown in Fig 8(b), in which the initial setting for inputs of all Reset-set (SR) flip-flops are S = 1, R = 0, and Q outputs of all flip-flops are initially at the high level. According to the algorithm flow chart, each of diode faults is identified with three signatures and the corresponding signal  $S_i$  (i = 1...6) changes from high level to low level. Logic values for all indicators including for *S* faults are given in Table 2.

According to Table 2, signals  $S_{sd}$ ,  $S_{sk}$ ,  $S_1$ ,  $S_2$ ,  $S_3$ ,  $S_4$ ,  $S_5$ and  $S_6$  are all at a high level during normal operation of the quadratic DC-DC converter. If S SCF of the quadratic converter occurs,  $S_{sd}$  changes from 1 to 0 while other indicators remain at a high level. Similarly, in case of D<sub>1</sub> SCF occurrence,  $S_1$  becomes 0. It is obvious that when one of fault occurs there is only the corresponding indicator changing to 0 while others remaining high. Therefore, all switch or diode faults in quadratic DC-DC converter can be diagnosed by monitoring  $S_{sd}$ ,  $S_{sk}$ ,  $S_1$ ,  $S_2$ ,  $S_3$ ,  $S_4$ ,  $S_5$  and  $S_6$ .

It is worth noting that when diodes  $D_1$  SCF or  $D_3$  SCF occur, the fuse blows out. Depending on the instant that the

### IEEE Access

FIGURE 8. Implementation of the proposed fault diagnosis technique (a) diode fault diagnosis flowchart, (b) logic circuit for diode fault diagnosis.

TABLE 2. Values of the logic signals for all fault diagnosis circuits.

| Signal<br>Condition | $S_{ m sd}$ | $S_{ m sk}$ | $S_1$ | $S_2$ | $S_3$ | $S_4$ | $S_5$ | $S_6$ |

|---------------------|-------------|-------------|-------|-------|-------|-------|-------|-------|

| Normal              | 1           | 1           | 1     | 1     | 1     | 1     | 1     | 1     |

| S SCF               | 0           | 1           | 1     | 1     | 1     | 1     | 1     | 1     |

| S OCF               | 1           | 0           | 1     | 1     | 1     | 1     | 1     | 1     |

| $D_1$ SCF           | 1           | 1           | 0     | 1     | 1     | 1     | 1     | 1     |

| $D_1 OCF$           | 1           | 1           | 1     | 0     | 1     | 1     | 1     | 1     |

| $D_2 SCF$           | 1           | 1           | 1     | 1     | 0     | 1     | 1     | 1     |

| D <sub>2</sub> OCF  | 1           | 1           | 1     | 1     | 1     | 0     | 1     | 1     |

| D <sub>3</sub> SCF  | 1           | 1           | 1     | 1     | 1     | 1     | 0     | 1     |

| D <sub>3</sub> OCF  | 1           | 1           | 1     | 1     | 1     | 1     | 1     | 0     |

fault occurs, the algorithm can immediately detect or detect the fault by delay. However, the detection time will be more than one switching cycle, as described in Section 3. In Figure 8(b), a time delay unit is applied to the gate drive signal to avoid false diagnostics due to switch turn-on and turn-off delays. The delay unit has been digitally implemented and its value has been set according to the converter switch data.

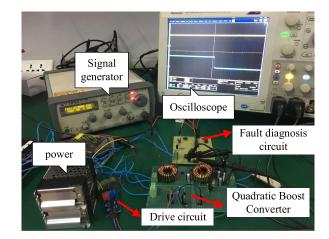

FIGURE 9. Utilized test bench.

**TABLE 3.** Experimental parameter statistics.

| Parameter            | value  |

|----------------------|--------|

| <i>U</i> in/V        | 10     |

| $L_1/\mu H$          | 150    |

| $L_2/\mu H$          | 400    |

| $C_1/\mu \mathrm{F}$ | 110    |

| $C_2/\mu \mathrm{F}$ | 47     |

| $R/\Omega$           | 50     |

| ƒ∕ KHZ               | 50     |

| duty cycle           | 0.5    |

| Switch               | IRF540 |

| Diode                | MUR460 |

|                      |        |

#### **VI. EXPERIMENTAL RESULTS**

In order to verify the effectiveness and the performance of the proposed fault diagnosis method, several experiments have been carried out on quadratic DC-DC converters. The test bench is shown in Figure 9 and the specifications are presented in Table 3. The rated current value of IRF540 is 50A, and then the rated value of  $F_U$  is set as 10A, which can assure to avoid the second failure of switch S after D<sub>1</sub> SCF or D<sub>3</sub> SCF occurrence.

In experiments, to implement the short or open fault of the converter semiconductor switches, auxiliary mechanical switches are introduced to emulate switch and diode faults. To emulate OCF, the auxiliary switch is connected in series with the device under test, while for SCF; the auxiliary switch is connected in parallel. In normal cases, the auxiliary switch in series is ON and is turned-off for OCF. Similarly, the auxiliary switch in parallel is OFF and is turned-on for SCF. The on-resistance of auxiliary mechanical switch is negligible.

The data and waveform acquisition are captured by a digital oscilloscope with attenuation probes. In this paper, experimental verifications of quadratic Boost converter, quadratic Buck converter and quadratic Buck-Boost converters are carried out. However, only some experimental results are given as follows due to page limitation.

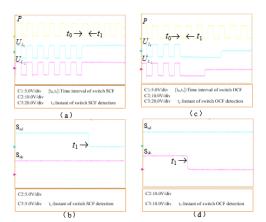

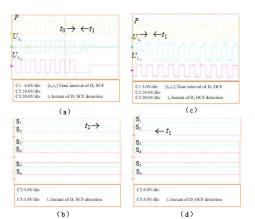

**FIGURE 10.** Switch fault experimental waveforms of quadratic Boost converter. (a) The voltage of  $L_1$ ,  $L_2$  after switch SCF occurrence; (b) logic signals corresponding to (a); (c) The voltage of  $L_1$ ,  $L_2$  after switch OCF occurrence; (d) logic signals.

#### A. SWITCH FAULT EXPERIMENTAL RESULTS

Fig. 10 shows switch fault waveforms diagrams of quadratic Boost converter, in which switch faults have occurred at an instant in  $[t_0, t_1]$  interval. It can be seen that all switch faults have been detected. Switch SCF is detected during P = 0 because logic signal  $S_{sd}$  becomes low, and switch OCF is detected during P = 1 because logic signal  $S_{sk}$  becomes low.

As the results analyzed in Section 4.1, switch SCF cannot be detected at state P = 1 and switch OCF cannot be detected at state P = 0. It is obvious that the maximum detection delay is related to the time point of fault occurrence. The maximum delay may be KT and (1-K)T, respectively, which is less than one switching cycle.

Figure 11 shows switch fault experimental waveforms of quadratic Buck converter in which switch faults have occurred at an instant in  $[t_0, t_1]$  interval. It can be seen that all switch faults have been detected. Switch SCF is detected during P = 0 because logic signal  $S_{sd}$  becomes low, and switch OCF is detected during P = 1 because logic signal  $S_{sk}$  becomes low. It is different from the quadratic Boost converter, the inductor voltage  $U_{L_1}$  is greater than the inductor voltage  $U_{L_2}$ , and  $U_{L_1} = 2U_{L_2}$  when K = 0.5.

Same as quadratic Boost converter, switch SCF cannot be detected at state P = 1 and switch OCF cannot be detected at state P = 0. It is obvious that the maximum detection delay is related to the time point of fault occurrence. The maximum delay may be KT and (1-K)T, respectively, which is less than one switching cycle.

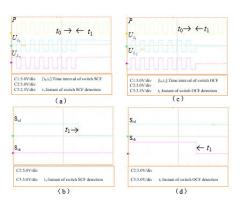

Figure 12 shows the switch fault waveform diagram of the quadratic Buck-Boost converter in which switch faults has occurred at an instant in  $[t_0, t_1]$  interval. It can be seen that all switch faults have been detected. Switch SCF is detected during P = 0 because logic signal  $S_{sd}$  becomes low, and switch OCF is detected during P = 1 because logic signal  $S_{sk}$  becomes low. It is different from the quadratic Boost converter, when K < 0.5, the quadratic Buck-Boost converter operates as a quadratic Buck converter, when K > 0.5,

**FIGURE 11.** Switch fault test waveforms of quadratic Buck converter. (a) The voltage of  $L_1$ ,  $L_2$  after switch SCF occurrence; (b) logic signals corresponding to (a); (c) The voltage of  $L_1$ ,  $L_2$  after switch OCF occurrence; (d) logic signals corresponding to (c).

**FIGURE 12.** Switch fault test waveforms of quadratic Buck-Boost converter. (a) The voltage of  $L_1$ ,  $L_2$  after switch SCF occurrence; (b) logic signals corresponding to (a); (c) The voltage of  $L_1$ ,  $L_2$  after switch OCF occurrence; (d) logic signals corresponding to (c).

the quadratic Buck-Boost converter operates as a quadratic Boost converter. This paper chooses P = 0.6.

Same as quadratic Boost converter, switch SCF cannot be detected at state P = 1 and switch OCF cannot be detected at state P = 0. It is obvious that the maximum detection delay is related to the time point of fault occurrence. The maximum delay may be KT and (1-K)T, respectively, which is less than one switching cycle.

#### **B. DIODES FAULT EXPERIMENTAL RESULTS**

Due to page limitation, the diode experimental results only are given in the quadratic Boost converter. Figure 13 shows the D<sub>1</sub> fault waveforms of the quadratic Boost converter in which D<sub>1</sub> faults have occurred at an instant in [ $t_0$ ,  $t_1$ ] interval. The D<sub>1</sub> SCF cannot be detected until  $t_2$  because  $U_{L_2}$  becomes zero after two switching cycles and the logic signal  $S_1$  becomes low in which the fuse is disconnected since the current of the switch exceeds 10A. After the D<sub>1</sub> SCF occurrence, fault detection is realized when P = 1. According to the converter diode in table 3,  $U_{th1} = 0.7$  and  $U_{th2} = -0.7$ are used in the paper and  $U_{th1} < U_{L_2} < U_{th2}$  is satisfied at  $t_2$ . The D<sub>1</sub> OCF cannot be detected until  $t_1$  because  $U_{L_1} < U_{L_2}$ at P = 0 and the logic signal  $S_2$  becomes low.

**FIGURE 13.** D<sub>1</sub> fault test waveforms diagram of quadratic Boost converter (a) The voltage of  $L_1$ ,  $L_2$  after D<sub>1</sub> SCF occurrence; (b) logic signals corresponding to (a); (c) The voltage of  $L_1$ ,  $L_2$  after D<sub>1</sub> OCF occurrence; (d) logic signals corresponding to (c).

**FIGURE 14.** D<sub>2</sub> fault test waveforms of quadratic Boost converter. (a) The voltage of  $L_1$ ,  $L_2$  after D<sub>2</sub> SCF occurrence; (b) logic signals corresponding to (a); (c) The voltage of  $L_1$ ,  $L_2$  after D<sub>2</sub> OCF occurrence; (d) logic signals corresponding to (c).

As the results analyzed in Section 4.2,  $D_1$  SCF cannot be detected at state P = 0(according to Equ (10)) and  $D_1$  OCF cannot be detected at state P = 1(according to Equ (13)). It is obvious that the maximum detection delay is related to the time point of fault occurrence. The  $D_1$  OCF's maximum delay may be *KT*, which is less than one switching cycle. But the  $D_1$  SCF will be delayed after two switching cycles.

Fig 14 shows the D<sub>2</sub> fault waveforms of a quadratic Boost converter in which D<sub>2</sub> faults have occurred at an instant in [ $t_0$ ,  $t_1$ ] interval. The D<sub>2</sub> SCF cannot be detected until  $t_1$  because  $U_{L_2}$  remains positive at P = 0 and the logic signal  $S_3$  becomes low. The D<sub>2</sub> OCF cannot be detected until  $t_1$  because  $U_{L_1}$ becomes negative and the logic signal  $S_4$  becomes low only at P = 1.

As the results analyzed in Section 4.3,  $D_2$  SCF cannot be detected at state P = 1 and  $D_2$  OCF cannot be detected at state P = 0. It is obvious that the maximum detection delay is related to the time point of fault occurrence. The maximum delay may be KT and (1-K)T, respectively, which is less than one switching cycle.

**IEEE**Access

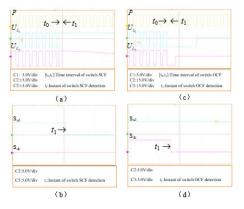

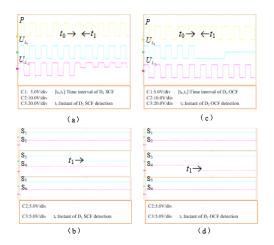

**FIGURE 15.** D<sub>3</sub> fault test waveforms of quadratic Boost converter. (a) The voltage of  $L_1$ ,  $L_2$  after D<sub>3</sub> SCF occurrence; (b) logic signals corresponding to (a); (c) The voltage of  $L_1$ ,  $L_2$  after D<sub>3</sub> OCF occurrence; (d) logic signals corresponding to (c).

Fig 15 shows the D<sub>3</sub> fault waveforms of a quadratic Boost converter in which D<sub>3</sub> faults have occurred at an instant in  $[t_0, t_1]$  interval. The D<sub>3</sub> SCF could not detected until  $t_2$ , because the  $U_{L_1}$  becomes zero after two switching cycles and the logic signal  $S_5$  becomes low in which the fuse is disconnected since the current of the switch exceeds 10A and after D<sub>3</sub> SCF. And fault detection is realized when P = 1For the converter diode in table 3, choose  $U_{th3} = 0.7$  and  $U_{th4} = -0.7$  We can see  $U_{th3} < U_{L_1} < U_{th4}$  at  $t_2$ . The D<sub>3</sub> OCF cannot be detected until  $t_1$ , because  $U_{L_2} > U_{th5}$  at P = 0and the logic signal  $S_6$  becomes low. According to Equ (17), the D<sub>3</sub> experiences a large voltage in this case, we choose  $U_{th5} = 5V$ .

As the results analyzed in Section 4.4, D<sub>3</sub> SCF cannot be detected at state P = 0 and D<sub>3</sub> OCF cannot be detected at state P = 1. It is obvious that the maximum detection delay is related to the time point of fault occurrence. The D<sub>3</sub> OCF's maximum delay may be *KT*, which is less than one switching cycle. But the D<sub>3</sub> SCF will be delayed after some switching cycles.

#### **VII. CONCLUSION**

This paper firstly studies the previous fault diagnosis technology of power devices aiming at traditional DC-DC converters. The selection of fault detection signals is diverse and cannot be universally applied to high-performance converters. This paper put forward a simple logic fault diagnosis method to detect switch and diode faults of high-performance converters. This method uses inductor voltage signal and PWM signal to identify all switches and diodes SCF and OCF in the quadratic DC-DC converter. This paper fully explains the theoretical basis and design of the diagnostic circuit. This diagnostic method has interesting advantages, including implementation in one switching cycle, with full coverage of faults, low cost, high efficiency, and strong real-time performance. The experimental results verified the accuracy and effectiveness of this method. The fault diagnosis method proposed in this paper has good scalability and

establishes a foundation for fault diagnosis of non-isolated DC-DC converters.

#### REFERENCES

- B. Lu and S. K. Sharma, "A literature review of IGBT fault diagnostic and protection methods for power inverters," *IEEE Trans. Ind. Appl.*, vol. 45, no. 5, pp. 1770–1777, Sep. 2009.

- [2] Y. Liu, J. Wang, and H. Tu, "Design and implementation of finite time nonsingular fast terminal sliding mode control for a novel high step-up DC-DC converter," *Energies*, vol. 12, no. 9, p. 1716, May 2019.

- [3] H. Givi, E. Farjah, and T. Ghanbari, "Switch fault diagnosis and capacitor lifetime monitoring technique for DC–DC converters using a single sensor," *IET Sci., Meas. Technol.*, vol. 10, no. 5, pp. 217–513, Aug. 2016.

- [4] E. Pazouki, Y. Sozer, and J. A. De Abreu-Garcia, "Fault diagnosis and fault-tolerant control operation of nonisolated DC–DC converters," *IEEE Trans. Ind. Appl.*, vol. 54, no. 1, pp. 310–320, Jan. 2018.

- [5] W. Deng, J. Wu, H. Pan, B. Li, Y. Tang, and Y. Yan, "Analysis and diagnosis of open-circuit faults in power switches of two-stage matrix converters," *J. Electr. Mach. Control*, vol. 22, no. 7, pp. 59–68, Jul. 2018.

- [6] S. Khwan-on, L. de Lillo, L. Empringham, and P. Wheeler, "Fault-tolerant matrix converter motor drives with fault detection of open switch faults," *IEEE Trans. Ind. Electron.*, vol. 59, no. 1, pp. 257–268, Jan. 2012.

- [7] S. M. A. Cruz, M. Ferreira, A. M. S. Mendes, and A. J. M. Cardoso, "Analysis and diagnosis of open-circuit faults in matrix converters," *IEEE Trans. Ind. Electron.*, vol. 58, no. 5, pp. 1648–1661, May 2011.

- [8] L. M. A. Caseiro and A. M. S. Mendes, "Real-time IGBT open-circuit fault diagnosis in three-level neutral-point-clamped voltage-source rectifiers based on instant voltage error," *IEEE Trans. Ind. Electron.*, vol. 62, no. 3, pp. 1669–1678, Mar. 2015.

- [9] J.-H. Jung, H.-K. Ku, Y.-D. Son, and J.-M. Kim, "Open-switch fault diagnosis algorithm and tolerant control method of the three-phase threelevel NPC active rectifier," *Energies*, vol. 12, no. 13, p. 2495, Jun. 2019.

- [10] E. Ribeiro, A. J. M. Cardoso, and C. Boccaletti, "Fault-tolerant strategy for a photovoltaic DC-DC converter," *IEEE Trans. Power Electron.*, vol. 28, no. 6, pp. 3008–3018, Jun. 2013.

- [11] H. Sheng, F. Wang, and C. W. Tipton, "A fault detection and protection scheme for three-level DC–DC converters based on monitoring flying capacitor voltage," *IEEE Trans. Power Electron.*, vol. 27, no. 2, pp. 685–697, Feb. 2012.

- [12] C. Shu, L. Wei, D. Rong-Jun, and C. Te-Fang, "Fault diagnosis and faulttolerant control scheme for open-circuit faults in three-stepped bridge converters," *IEEE Trans. Power Electron.*, vol. 32, no. 3, pp. 2203–2214, Mar. 2017.

- [13] B. Kaitao, A. Quntao, S. Dongyang, D. Jiandong, and S. Li, "Modular multilevel energy stroage system open circuit diagnostic method based on sub-module operation analysis," *Trans. China Electrotech. Soc.*, vol. 33, no. 6, pp. 1219–1226, Mar. 2018.

- [14] S. Young Kim, K. Nam, H.-S. Song, and H.-G. Kim, "Fault diagnosis of a ZVS DC–DC converter based on DC-link current pulse shapes," *IEEE Trans. Ind. Electron.*, vol. 55, no. 3, pp. 1491–1494, Mar. 2008.

- [15] T. Kamel, Y. Biletskiy, and L. Chang, "Real-time diagnosis for opencircuited and unbalance faults in electronic converters connected to residential wind systems," *IEEE Trans. Ind. Electron.*, vol. 63, no. 3, pp. 1781–1792, Mar. 2016.

- [16] M. Shahbazi, E. Jamshidpour, P. Poure, S. Saadate, and M. R. Zolghadri, "Open-and short-circuit switch fault diagnosis for nonisolated DC–DC converters using field programmable gate array," *IEEE Trans. Ind. Electron.*, vol. 60, no. 9, pp. 4136–4146, Sep. 2013.

- [17] E. Farjah, H. Givi, and T. Ghanbari, "Application of an efficient rogowski coil sensor for switch fault diagnosis and capacitor ESR monitoring in nonisolated single-switch DC–DC converters," *IEEE Trans. Power Electron.*, vol. 32, no. 2, pp. 1442–1456, Feb. 2017.

- [18] H. Givi, E. Farjah, and T. Ghanbari, "Switch and diode fault diagnosis in nonisolated DC–DC converters using diode voltage signature," *IEEE Trans. Ind. Electron.*, vol. 65, no. 2, pp. 1606–1615, Feb. 2018.

- [19] Y. Chen, X. Pei, S. Nie, and Y. Kang, "Monitoring and diagnosis for the DC–DC converter using the magnetic near field waveform," *IEEE Trans. Ind. Electron.*, vol. 58, no. 5, pp. 1634–1647, May 2011.

- [20] S. Dusmez and B. Akin, "An active life extension strategy for thermally aged power switches based on the pulse-width adjustment method in interleaved converters," *IEEE Trans. Power Electron.*, vol. 31, no. 7, pp. 5149–5160, Jul. 2016.

- [21] X. Pei, S. Nie, and Y. Kang, "Switch short-circuit fault diagnosis and remedial strategy for full-bridge DC–DC converters," *IEEE Trans. Power Electron.*, vol. 30, no. 2, pp. 996–1004, Feb. 2015.

- [22] Z. Yi and A. H. Etemadi, "Fault detection for photovoltaic systems based on multi-resolution signal decomposition and fuzzy inference systems," *IEEE Trans. Smart Grid*, vol. 8, no. 3, pp. 1274–1283, May 2017.

- [23] W. Sleszynski, J. Nieznanski, and A. Cichowski, "Open-transistor fault diagnostics in voltage-source inverters by analyzing the load currents," *IEEE Trans. Ind. Electron.*, vol. 56, no. 11, pp. 4681–4688, Nov. 2009.

- [24] S. Nie, X. Pei, Y. Chen, and Y. Kang, "Fault diagnosis of PWM DC–DC converters based on magnetic component voltages equation," *IEEE Trans. Power Electron.*, vol. 29, no. 9, pp. 4978–4988, Sep. 2014.

- [25] J. Leyva-Ramos, L. H. Diaz-Saldierna, J. A. Morales-Saldaña, and M. G. Ortiz-Lopez, "Switching regulator using a quadratic boost converter for wide DC conversion ratios," *IET Power Electron.*, vol. 2, no. 5, pp. 605–613, Sep. 2009.

**LI CHEN** received the M.S. degree in management engineering from Central South University, Changsha, China, in 2004, and the Ph.D. degree in electrical engineering from the Hebei University of Technology, Tianjin, China, in 2019.

From 2004 to 2020, she was a Lecturer with the College of Electrical Engineering, Hebei University of Technology. She is the author of more than ten articles. Her current research interests include fault diagnosis in electrical engineering, reliability, and power electronic techniques.

**XIAOLI ZHAO** received the M.S. degree in electrical engineering from the Hebei University of Technology, Tianjin, China, in 2020.

From 2013 to 2020, she was a Student with the College of Electrical Engineering, Hebei University of Technology. She has published two articles. Her current research interests include power electronic technique and devices reliability.

**SHENG XUE TANG** received the M.S. and Ph.D. degrees in electrical engineering from Hunan University, Changsha, China, in 2004 and 2008, respectively.

From 2009 to 2016, he was a Visiting Professor with the College of Electrical Engineering, Hebei University of Technology, Tianjin, China, where he was a Professor, from 2016 to 2020. He is the author of more than 80 articles. His current research interests include signal process-

ing in electrical engineering, power devices reliability, and microgrids and converter techniques.