Received August 18, 2020, accepted August 31, 2020, date of publication September 14, 2020, date of current version October 5, 2020. Digital Object Identifier 10.1109/ACCESS.2020.3024098

# **Towards Automatic High-Level Code Deployment** on Reconfigurable Platforms: A Survey of High-Level Synthesis Tools and Toolchains

# MOSTAFA W. NUMAN<sup>®1</sup>, BRADEN J. PHILLIPS<sup>®2</sup>, (Member, IEEE), GAVIN S. PUDDY<sup>®1</sup>, (Associate Member, IEEE), AND KATRINA FALKNER<sup>®1</sup>

<sup>1</sup>School of Computer Science, The University of Adelaide, Adelaide, SA 5005, Australia

<sup>2</sup>School of Electrical and Electronic Engineering, The University of Adelaide, Adelaide, SA 5005, Australia

Corresponding author: Mostafa W. Numan (mostafa.numan@adelaide.edu.au)

This work was supported by the Maritime Division of the Defence Science and Technology Group, Australia.

**ABSTRACT** Heterogeneous computing systems with tightly coupled processors and reconfigurable logic blocks provide great scope to improve software performance by executing each section of code on the processor or custom hardware accelerator that best matches its requirements and the system optimisation goals. This article is motivated by the idea of a software tool that can automatically accomplish the task of deploying code, originally written for a conventional computer, to the processors and reconfigurable logic blocks in a heterogeneous system. We undertake an extensive survey of high-level synthesis tools to determine how close we are to this vision, and to identify any capability gaps. The survey is structured according to a new framework that clearly expresses the relationships between the many tools surveyed. We find that none of the existing tools can deploy general high-level code without manual intervention. Logic synthesis from arbitrary high-level code remains an open problem with dynamic data structures, function pointers and recursion all presenting challenges. Other challenges include automating the tasks of code partitioning, optimisation and design space exploration.

**INDEX TERMS** Automatic code deployment, field programmable gate arrays, high level synthesis, heterogeneous platforms.

### I. INTRODUCTION

For the last four decades, Moore's law and Dennard scaling have relentlessly delivered improvements in computing performance [1]. Since the early 2000s their impact has begun to wane and alternative ways to improve performance have begun to emerge. Heterogeneous computing is a promising approach in which a group of processing nodes execute a workload in parallel. Given different kinds of nodes including multi-core CPUs, real-time processors, DSPs, GPUs, and accelerators on FPGAs or ASICs, the computing workload can be partitioned such that each part is executed on a processor that is well-matched to its requirements and the performance optimisation goals.

This article is concerned with the engineering task of writing software for a heterogeneous system and considers how close existing tools and technologies are to a fully automatic

The associate editor coordinating the review of this manuscript and approving it for publication was Christian Pilato<sup>10</sup>.

system in which high-level source code is partitioned and deployed to heterogeneous nodes with a minimum of human intervention. This is an ambitious scope so we constrain ourselves, in this article, to the task of deploying source code blocks onto custom FPGA logic.

It is possible, of course, to write software specifically for a particular heterogeneous system by manually partitioning tasks among the processors, and using the most appropriate programming language for each of the different processors. For example a Hardware Description Language (HDL) such as Verilog could be used for tasks executing on an FPGA, and CUDA for those on a GPU. An alternative, which has seen a great deal of research activity in recent years, is to use *High-Level Synthesis* (HLS) for generating hardware modules from code written in a High-Level Language (HLL) (such as C, C++ or Python).

There are benefits of using HLS instead of HDL so that the entire application is in a high-level language: simulation speed is generally faster; debugging is less difficult; it is easier to explore and evaluate design alternatives; and the high-level language may include features that cannot be easily expressed in a HDL [2].

Although current HLS tools do not always produce performance-optimised implementations, applications without stringent performance requirements can be more quickly and easily developed using HLS. HLS software developers do not necessarily need to be FPGA or HDL experts, and optimisation opportunities can be exposed to the designer that cannot be easily explored via HDL approaches. In some cases, a project that would not have been practical in HDL, given its complexity, limited time frame and small development team, can be feasible in HLS at a low performance cost compared to an HDL-based approach [3]–[5].

An HLS-based design for a heterogeneous system could be started from scratch, or use pre-existing code originally written for a conventional CPU. Either way, to effectively use current HLS technology, system developers require considerable knowledge and experience in the application domain, computer programming, and HLS design flow.

Deploying pre-existing code written for a conventional CPU onto a heterogeneous system with the aim of improving performance or efficiency is even more difficult. The code needs to be substantially restructured to be synthesisable, and to produce optimised hardware. This needs to be done for all the code: not just the application source code but also any library functions it uses. To date *Automatic Code Deployment* (ACD) tools capable of performing this challenging task without human intervention have been the subject of limited research (e.g. [6], [7]) but a considerable amount of work has been done on automating some of the more challenging, tedious and time-consuming steps in this process (e.g. [8]–[11]).

This article surveys recent toolchains and workflows for high-level synthesis to FPGA with a focus on technologies that might eventually be used for automatic code deployment. Section I introduces HLS and the motivation for heterogeneous computing based on HLS. Section II categorises different contemporary approaches to deploy compute-intensive code segments to FPGA hardware accelerators. The categories introduced in Section II are used to organise a thorough survey, in Sections III and IV, of approaches that take a candidate function expressed in a HLL and produce low-level HDL suitable for FPGA deployment. The arguments in these sections focus on contemporary HLS tools currently used in academia or industry; legacy tools are included in summary tables for completeness. Specification of a hypothetical tool for ACD to FPGA, as well as a brief summary of progress reported in the literature towards making HLS-based FPGA code deployment less dependent on human judgement and proficiency, are provided in Section V.

#### **II. HIGH-LEVEL CODE DEPLOYMENT APPROACHES**

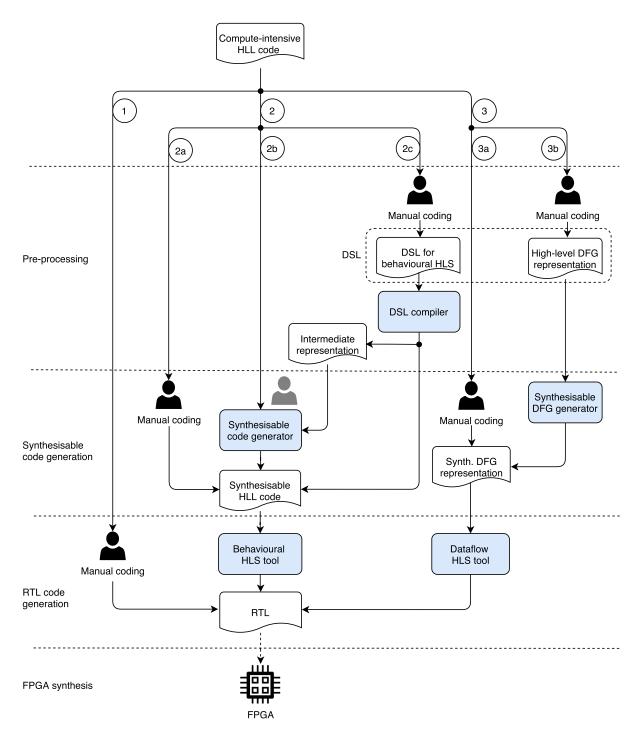

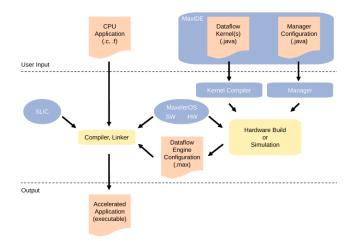

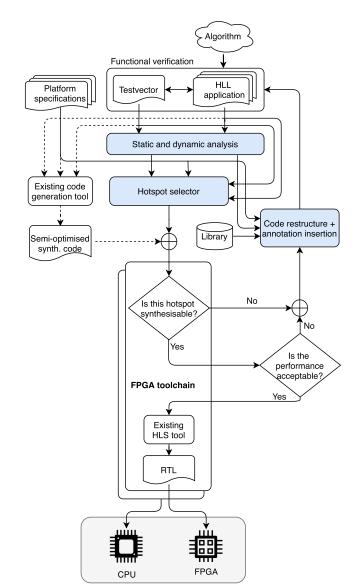

To build an FPGA-based heterogeneous system, a common practice is to begin with an application running on a CPU, which is profiled to identify functions (or code blocks) to be offloaded to the FPGAs. Careful choice of the offloaded code blocks can improve latency, throughput or energy efficiency of the application as a whole. One part of the application, which controls and synchronises the execution, usually remains on a host CPU; and compute-intensive parts are synthesised as accelerators on the FPGAs. In the past, hardware developers had to manually rewrite the compute-intensive HLL functions as custom accelerators at the Register Transfer Level of abstraction (RTL), using a Hardware Description Language (HDL) (e.g. VHDL or Verilog). Hardware synthesis for FPGAs from a manually written HDL description is a well-understood process in the literature, and is beyond the scope of this article. However, we have illustrated this method with the label (1) in FIGURE 1, to indicate that it is still one possible approach.

The manual transformation of a HLL function to RTL has some fundamental limitations:

- Understanding the HLL code and then manually writing the HDL code for the accelerator, requires repeated design effort that reduces productivity and increases time-to-market of the end product.

- Notions of timing at RTL require the developer to have a good understanding of the hardware platform. It is hard to find experts with the necessary blend of software and hardware expertise. For a hardware developer, understanding the HLL code can be as problematic as understanding hardware optimisation for a software engineer. This gap often results in an inefficient hardware implementation.

- High-level constructs that lead to an efficient implementation on a CPU can be problematic in an FPGA. For example, floating point operations, dynamic data structures, functions called by reference, and recursion can all be difficult to map to efficient hardware.

- Even small changes to the software application to fix bugs or add new features can require significant modification of the HDL code and extensive restructuring of the hardware.

- The task becomes even more challenging if there is a legacy software code base, such as in runtime libraries, that needs to be deployed on the FPGA.

- Parallelism is usually key to improved performance on FPGA but it is difficult to extract parallelism from code that was originally optimised for sequential CPUs.

Researchers have been working towards defining hardware accelerators at higher levels of abstraction using HLLs, and building tools to automatically transform HLL code to an RTL description. Common practice at present is to write the compute-intensive parts of the code as functions that use only a subset of the HLL such that they are *synthesisable* for the FPGA. C and C-based HLLs are most common because of their wide-acceptance among both software and hardware engineers.

This design flow is shown as (2) in FIGURE 1, and will be discussed in Section III. It can be divided into subcategories:

- *Behavioural High-Level Synthesis (HLS)* (2): In this approach, the hardware developer selects computeintensive functions and rewrites them to synthesisable HLL. The behavioural HLS tool then converts the functions into RTL descriptions for FPGA implementation. Tools to support this flow are surveyed in Section III-A.

- Synthesisable behavioural code generation (2): There are some tools to generate synthesisable code (sometimes just called 'HLS code') from HLL code. They

are usually 'semi-automatic' tools that require some manual code refactoring and annotation. The generated synthesisable code can be passed to HLS tools to generate RTL descriptions. This approach is discussed in Section III-B.

• Domain-Specific Language (DSL) for HLS (2): In this approach, compute-intensive HLL code is manually re-written using a DSL, and a DSL compiler translates it to synthesisable code directly, or by using a

synthesisable code generator. The generated synthesisable HLL code is then used by a HLS tool to generate an RTL description. DSL tools for HLS are discussed in Section III-C.

Dataflow descriptions are another way to express compute-intensive HLL functions for FPGA implementation. This is illustrated as design flow (3) in FIGURE 1. A dataflow description represents a system as a directed graph, known as dataflow graph (DFG), with nodes as computational units and the edges as data flow between them. The asynchronous and concurrent behaviour of the computation units provide a good match with likely implementations on FPGAs. Dataflow descriptions can be defined at different levels of abstraction. We will discuss this design flow in Section IV under two subcategories:

- *Dataflow HLS* (3): In this approach, a synthesisable DFG is manually described using a meta-language (e.g. MaxJ [12], CAL [13]), and then transformed into an RTL description using an appropriate HLS tool. Section IV-A surveys efforts using this approach.

- *High-level DFG representation* (3): Some tools allow developers to define DFGs at higher level of abstraction, and transform them to synthesisable representations. Then, using dataflow HLS they are translated to RTL descriptions. These tools usually work for particular application domains. The effort to define DFGs at high levels of abstractions are discussed in Section IV-B.

# **III. BEHAVIOURAL APPROACH FOR FPGA SYNTHESIS**

A common and straightforward approach to deploy a compute-intensive function on an FPGA is to write a behavioural description of that function in a HLL as a sequence of statements with control structures such as loops and conditions. Existing tools support a variety of HLLs including including C, C++, Java, Python, C# and Matlab and are able to transform the behavioural description into an RTL description in HDL (typically VHDL, Verilog or SystemVerilog). This design flow is labelled as (2) in FIGURE 1. Variations of this design flow are discussed in the following subsections.

# A. BEHAVIOURAL HIGH-LEVEL SYNTHESIS (HLS) (2A

High-Level Synthesis (HLS) allows developers to define hardware using a HLL (e.g. C, C++ or SystemC). A HLS tool automatically transforms the untimed HLL code to a fully timed circuit specification in HDL to perform the same function on an FPGA. The introduction of HLS in the design flow reduces the transition from the HLL code to the start of the automatic process, as can be seen from the design flow in FIGURE 1.

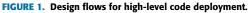

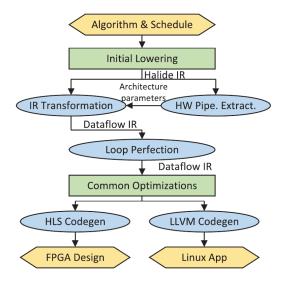

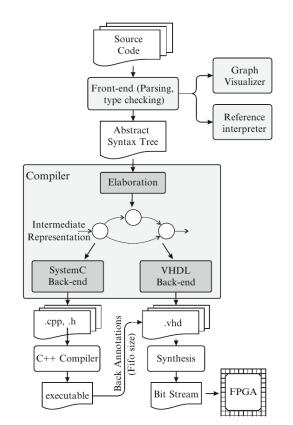

FIGURE 2 shows a generic HLS design flow to synthesise an accelerator on an FPGA as in [14], [15]. The flow starts with a behavioural description, which is written in a synthesisable way using a HLL. Not all HLL constructs are synthesisable by all HLS tools. For example, many HLS tools do not support pointers, recursion or dynamic memory

FIGURE 2. A generic HLS design flow.

allocation. After parsing the source code during compilation, the HLS tool generates an intermediate representation (IR) and performs source code optimisations such as dead-code elimination and redundant expression elimination. Most HLS tools are based on the LLVM compiler infrastructure [16], which generates a Control and Data Flow Graph (CDFG) to capture all dependencies of the IR. The HLS tool determines the right functional units, memory elements and connectivity components to use from a design library during resource allo*cation.* In the *scheduling* step, each operation from the source code is assigned to a control step, which will correspond to system clock cycles in the hardware. Next, in resource binding, the HLS tool maps operations to specific functional units, variables to memory elements, and data transfers to interconnection components such that data can be correctly computed and passed, according to the scheduling. Finally, an RTL model of the synthesised design is produced in the RTL generation step. Depending upon the scheduling and the binding information, interconnections between the circuit modules of the datapath are created, and a finite state machine (FSM) is generated to control the data flow in the datapath.

HLS has been the subject of continuous research since the 1970s, but these efforts were not notably successful until the early 2000s. The historical evolution of HLS tools and the reasons behind the success and failure of different generations of HLS development are discussed in [17], [18].

| Tool                                       | Provider            | Intro. | Update | Pedigree                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Platform                                                           | Input                                              | Output           | Design tool                                            | Domain | PR | P2P |   |   | ed fea<br>FP |   |   | DM . | AN |

|--------------------------------------------|---------------------|--------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|----------------------------------------------------|------------------|--------------------------------------------------------|--------|----|-----|---|---|--------------|---|---|------|----|

| Vivado<br>HLS [23]                         | Xilinx              | 2008   | 2019   | $\begin{array}{l} \text{xPilot (UCLA)} \\ \rightarrow  \text{AutoPilot} \\ (\text{AutoESL}) \rightarrow \\ \text{Vivado}  \text{HLS} \\ (\text{Xilinx}) \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Xilinx FP-<br>GAs                                                  | C, C++,<br>System<br>C,<br>OpenCL<br>API           | Verilog,<br>VHDL | Included<br>in Vivado<br>Design<br>Suite               | All    | •  | 0   | 0 | • | •            | • | 0 | 0    | Ð  |

| Intel<br>FPGA<br>SDK for<br>OpenCL<br>[24] | Intel (Al-<br>tera) | 2013   | 2019   | Intel acquired<br>Altera in 2015                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Hetero-<br>geneous<br>platforms<br>with Intel<br>CPUs and<br>FPGAs | OpenCL<br>kernels                                  | Verilog          | Stand-<br>alone                                        | All    | •  | 0   | 0 | • | •            | • | 0 | 0    |    |

| Intel HLS<br>Compiler<br>[35]              | Intel (Al-<br>tera) | 2017   | 2019   | Intel acquired<br>Altera in 2015                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Intel<br>FPGAs                                                     | C++                                                | Verilog          | Included<br>in Intel<br>Quartus<br>Prime<br>Design     | All    | •  | 0   | 0 | • | •            | • | O | 0    | Ð  |

| Catapult<br>HLS [36]                       | Mentor<br>Graphics  | 2004   | NI     | $\begin{array}{ll} \mbox{Catapult-} & \mbox{(Mentor} & \mbox{Graphics}) \rightarrow \\ \mbox{Catapult-} & \mbox{Catapult-} & \mbox{Catapult-} & \mbox{2011} & \mbox{-} & \mbox{Catapult} & \mbox{Catapult} & \mbox{Catapult} & \mbox{HLS} & \mbox{(Mentor} & \mbox{Graphics}, & \mbox{2015} & \mbox{2015} & \mbox{Catapult} & \mbox{Catapult} & \mbox{HLS} & \mbox{(Mentor} & \mbox{Graphics}, & \mbox{Catapult} & Cat$ | All FPGAs<br>and ASICs                                             | C++                                                | Verilog,<br>VHDL | NI                                                     | All    | 0  | 0   | 0 | • | •            | • | 0 | 0    |    |

| Stratus<br>HLS [32]                        | Cadence             | 2015   | NI     | Cynthesizer<br>(Forte) +<br>C-to-Silicon<br>Compiler<br>(Cadence) $\rightarrow$<br>Stratus HLS<br>(Cadence)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | All FPGAs<br>and ASICs                                             | C++,<br>SystemC                                    | Verilog          | NI                                                     | All    | •  | 0   | 0 | • | •            | • | 0 | 0    |    |

| CyberWork-<br>Bench<br>[43]                | NEC                 | 2011   | NI     | Based on Cy-<br>ber [44]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Xilinx<br>and Altera<br>FPGAs                                      | BDL                                                | Verilog,<br>VHDL | Stand-<br>alone                                        | All    | •  | 0   | 0 | • | •            | • | 0 | 0    | Ð  |

| C-to-<br>Hardware<br>[45]                  | Altium              | 2008   | 2019   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Xilinx,<br>Intel and<br>Microsemi<br>FPGAs                         | С                                                  | Verilog,<br>VHDL | Included<br>in Altium<br>Designer                      | All    | •  | 0   | 0 | • | •            | 0 | 0 | 0    | •  |

| Synphony<br>HLS [46]                       | Synopsys            | 2003   | 2017   | Based on<br>PICO [47]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | All FPGAs<br>and ASICs                                             | C, C++,<br>Simulink<br>models                      | Verilog,<br>VHDL | Used as a<br>blockset<br>in<br>Simulink                | DSP    | 0  | 0   | 0 | • | 0            | 0 | 0 | 0 (  | 5  |

| HDL<br>Coder<br>and<br>Verifier<br>[48]    | Mathworks           | 2012   | 2019   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Xilinx,<br>Intel and<br>Microsemi<br>FPGAs                         | Matlab<br>func-<br>tions and<br>Simulink<br>models | Verilog,<br>VHDL | Used as<br>an add-on<br>in MAT-<br>LAB and<br>Simulink | All    | 0  | 0   | 0 | • | 0            | 0 | 0 | 0 (  | 5  |

#### TABLE 1. Currently available commercial HLS tools.

NI = No Information found

PR = Pointer, P2P = Pointer-to-pointer, P2F = Pointer-to-function, FP = Floating point, FxP = Fixed-point, AP = Arbitrary bit precision

RF = Recursive function, DM = Dynamic memory allocation, AN = Annotations required

$\bullet$  = Supported,  $\bigcirc$  = Not supported,  $\bullet$  = Supported with restrictions

The authors of [18] describe a state-of-the-art HLS tool of the time, AutoPilot [19], which was later acquired by Xilinx, and renamed Vivado HLS. The major research efforts in compiling HLLs for reconfigurable computing were surveyed in [14], [20]. The paper [21] presented an evaluation of more recent HLS tools in terms of capabilities, usability and quality of results. A survey of HLS tools and compilers targeting heterogeneous high performance computing was presented in [15]. The authors of [22] provided studies to compare the performance of three commercially available HLS tools: Vivado HLS [23], Intel FPGA SDK for OpenCL [24], and MaxCompiler [12]. A comprehensive survey of commonly used open-source HLS tools appears in [25]. A recent survey on HLS tools along with a comparative study of three academic HLS tools – Bambu [26], DWARV [27] and LegUp [28] – was published in [29]. This article surveyed an exhaustive list of HLS tool including abandoned ones. Since it was published, some of the tools have merged (e.g. Forte Cynthesizer [30] and Cadence C-to-Silicon Compiler [31] are combined in Stratus HLS [32]), some have lost their importance (e.g. eXCite [33], NAPA-C [34]), and some interesting new tools have appeared in the industry and academia (e.g. Intel FPGA SDK for OpenCL [24]). We provide updated lists of the currently available commercial and academic HLS tools in TABLE 1 and TABLE 2. Here, we consider only those tools that are in

| Tool                               | Provider                                           | Intro. | Update | Pedigree                        | Platform                                                       | Input                 | Output           | Design tool                                                                                            | Domain                         | PR | P2F |   |   |   | atures<br>AP |   | DM A       | N |

|------------------------------------|----------------------------------------------------|--------|--------|---------------------------------|----------------------------------------------------------------|-----------------------|------------------|--------------------------------------------------------------------------------------------------------|--------------------------------|----|-----|---|---|---|--------------|---|------------|---|

| LegUp<br>[28], [49]                | University<br>of Toronto<br>and LegUp<br>Computing | 2011   | 2020   |                                 | Intel<br>FPGAs<br>and limited<br>support<br>to Xilinx<br>FPGAs | С                     | Verilog          | Stand-alone                                                                                            | All                            | •  | 0   | 0 | 0 | • | 0            | 0 | <u>o c</u> | 2 |

| Bambu<br>[26]                      | Politecnico di<br>Milano                           | 2012   | 2017   |                                 | All FPGAs                                                      | С                     | Verilog          | Compatible<br>with Xilinx<br>Vivado<br>Design<br>Suite,<br>Altera<br>Quartus<br>and Lattice<br>Diamond | All                            | •  | 0   | 0 | 0 | • | 0            | 0 | 00         | 5 |

| ROCCC<br>[37], [38]                | UC Riverside<br>and Jacquard<br>Computing          | 2002   | 2013   | Inspired<br>by SA-C<br>compiler | FPGAs                                                          | A sub-<br>set of C    | VHDL             | Stand-alone                                                                                            | Streaming<br>applica-<br>tions | 0  | 0   | 0 | 0 | • | 0            | 0 | 0 0        | Σ |

| GAUT<br>[39], [40]                 | Université de<br>Bretagne-Sud                      | 2008   | 2017   |                                 | Xilinx<br>and Intel<br>FPGAs                                   | C, C++                | VHDL             | Compatible<br>with Vivado<br>Design<br>Suite and<br>Synopsys<br>Design<br>Compiler                     | DSP                            | 0  | 0   | 0 | • | 0 | •            | 0 | 0          | Σ |

| Kiwi<br>Compiler<br>[41], [42]     | University of<br>Cambridge                         | 2008   | 2017   |                                 | Xilinx<br>and Altera<br>FPGAs                                  | .NET<br>byte-<br>code | Verilog          | Stand-alone                                                                                            | All                            | •  | •   | 0 | 0 | • | 0            | 0 | • •        | ) |

| Handel-C<br>Compiler<br>[50], [51] | Oxford<br>University<br>Computing<br>Laboratory    | 1996   | NI     |                                 | Xilinx<br>and Altera<br>FPGAs                                  | Handel-<br>C          | Verilog,<br>VHDL | Used in<br>DK Design<br>Suite<br>[52] from<br>Mentor<br>Graphics                                       | All                            | 0  | 0   | 0 | • | 0 | 0            | 0 | 00         | Σ |

| DWARV<br>[27]                      | Delft<br>University<br>of Technology               | 2007   | 2014   |                                 | FPGAs                                                          | С                     | VHDL             | Included in<br>Delft Work-<br>bench [53]                                                               | All                            | •  | 0   | 0 | • | • | 0            | 0 | 0          | ) |

#### TABLE 2. Currently available academic HLS tools.

NI = No Information found

PR = Pointer, P2P = Pointer-to-pointer, P2F = Pointer-to-function, FP = Floating point, FxP = Fixed-point, AP = Arbitrary bit precision

RF = Recursive function, DM = Dynamic memory allocation, AN = Annotations required

$\bullet$  = Supported,  $\bigcirc$  = Not supported,  $\bullet$  = Supported with restrictions

use, under active research and popular in industry. We also provide the pedigrees of HLS tools, if available.

The choice of a HLS tool is often dominated by available applications, price, community support and its support for FPGAs from a particular vendor, such that no specific HLS tool dominates the industry. However, Xilinx Vivado HLS [23], Intel HLS Compiler [35], Intel FPGA SDK for OpenCL [24], Mentor Catapult [36], and Cadence Stratus [32] are some popular commercial HLS tools. LegUp [28], Bambu [26], ROCCC [37], [38], GAUT [39], [40] and Kiwi Compiler (KiwiC) [41], [42] are some notable HLS tools produced as research outputs. We will discuss these commercial and academic HLS tools in this section. Other available HLS tools are mentioned in TABLE 1 and TABLE 2. It should be noted that it is generally harder to find the design details (e.g. compiler architecture) of commercial tools than those of research products. Commercial tools built upon university research outputs (e.g. Vivado HLS [23]) have more information in the literature than those built entirely in industry (e.g. Intel HLS Compiler [35]).

1) VIVADO HLS

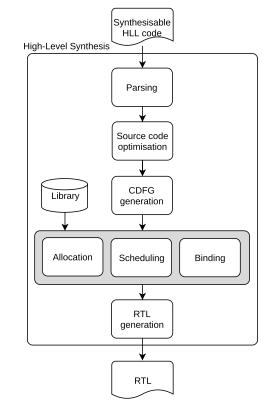

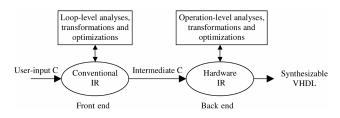

Vivado HLS [23] is a commercial HLS tool provided by Xilinx for their own FPGAs. It is based on AutoPilot [19], which was actually a commercialisation of the xPilot system [54] developed in the University of California, Los Angeles. Vivado HLS provides a design environment to generate RTL descriptions in VHDL and Verilog from synthesisable C, C++, SystemC or OpenCL HLL code. Being a commercial tool, the internal design flow of Vivado HLS is not available but it seems reasonable to assume it adopts the same design flow as AutoPilot, which is shown in FIGURE 3. Vivado HLS is based on LLVM compiler infrastructure, which compiles the HLL code to a LLVM-IR. The LLVM-IR then passes through a series of standard compilation tasks including dead-code elimination, constant propagation and loop unrolling, and hardware-specific optimisations such as bit-width optimisation for reducing code complexity and redundancy, maximising data locality and exposing parallelism. Vivado HLS uses the modified IR to perform synthesis and interconnect-centric optimisations during operation scheduling and resource binding phases taking user-specified

FIGURE 3. AutoPilot design flow [19].

constraints into account. Vivado HLS has a rich set of annotations to direct the compilation and synthesis processes to optimise performance, resource utilisation, data communication between CPU and custom hardware. It also contains many hardware-optimised libraries and APIs to support hardware developers. Finally, the IR is synthesised into RTL implementations for Xilinx FPGAs. The generated RTL can be saved in a IP library for later use. Vivado HLS also provides features to verify the functionality of the RTL against HLL description using a testbench. This HLS tool is included in Vivado Design Suite [55], and can be used with heterogeneous system development tools SDSoC [56] and SDAccel [57]. In Xilinx's recently released Vitis Unified Software Platform [58], it is named as Vitis HLS with some additional functionalities.

# 2) INTEL FPGA SDK FOR OpenCL

Open Computing Language (OpenCL) is a framework for programming parallel applications for heterogeneous platforms including processors, GPUs and FPGAs. It is an open standard maintained by the Khronos Group [59]. Altera introduced an OpenCL SDK for multi-core programming in 2013. Intel acquired Altera in 2015 and renamed the product as the Intel FPGA SDK for OpenCL [24]. Instead of executing parallel threads of expensive functions on multiple cores, this compiler generates deeply pipelined hardware circuits that can be implemented on Intel FPGAs. The tool transforms OpenCL to Verilog RTL and runtime libraries for the part of the system running on the processor. It uses LLVM-Clang [60] to parse OpenCL constructs and produces a IR. The IR passes through a series of optimisations including branch elimination, loop fusion and auto vectorisation. Users guide optimisation by inserting annotations for loop unrolling, pipelining and streaming data. The compiler automatically applies these optimisations and translates the optimised IR to Verilog RTL.

# 3) INTEL HLS COMPILER

The Intel HLS Compiler [35] transforms a high-level hardware description written in C++ to an RTL description for Intel FPGAs. In addition to standard compiler optimisations, the compiler performs optimisation tasks such as loop unrolling, data dependency and pipelining based on user-provided annotations. It allows the user to explore hardware architectures including interfaces, parallelism, memories, datapaths and loops using specific attributes and annotations. Like Vivado HLS, Intel HLS Compiler also facilitates generation of reusable IPs for system integration, and reduces FPGA development time. The tool supports software testbench verification against the generated RTL. It is included in the Intel Quartus Prime Design Software Suite [61].

# 4) CATAPULT HLS PLATFORM

The Catapult HLS Platform [36] was initially developed by Mentor Graphics as Catapult-C [62], and was later owned by Calypto Design Systems [63]. It was reacquired by Mentor Graphics in 2015. Using Catapult HLS, developers can define hardware using a subset of C++ and SystemC and generate optimised Verilog and VHDL description for FPGAs and ASICs. Catapult supports most C++ constructs including classes, structs, arrays and pointers to statically allocated objects. However, it does not support dynamic memory allocation. It allows developers to include integers of arbitrary length, fixed-point, floating-point and complex data types using Mentor Graphics's Algorithmic-C data types [64]. Hardware developers can specify parallelism, throughput and memory configuration at high levels of abstraction using attributes and annotation; however an in-depth understanding of the underlying hardware is required to achieve a good result. During hardware synthesis, Catapult performs a number of optimisations including loop unrolling, loop merging and pipelining. Catapult can automatically generate simulation infrastructure for verifying HLS-generated RTL against the original HLL source code. Catapult HLS also allows incorporating specification changes and porting to a different technology by the separation of the design functionality and the implementation details. The RTL can simply be regenerated based on the modified HLS model and new constraints.

# 5) STRATUS HLS

Stratus HLS [32] is a popular HLS tool provided by Cadence. Cadence acquired Forte Design Systems in 2014 and tied Forte's Cynthesizer [30] with its own C-to-Silicon Compiler [31] under the name Stratus HLS. The HLS tool accepts hardware specification in SystemC and C/C++ and generates a Verilog RTL utilising high-level implementation constraints. By separating these constraints from hardware functionality, Stratus HLS allows the verified HLL hardware specification to be reused as behavioural IPs without modification for different platforms and clock speeds. The HLS tool allows hardware developers to design hardware hierarchically to manage design complexity. By supporting hierarchical decomposition, it allows design and verification of multiple functions and their interfaces operating concurrently.

#### 6) CyberWorkBench

CyberWorkBench [43] is a HLS tool developed over 25 years of research in NEC. It allows developers to write SoC applications in C for the software part and in Behavioural Description Language (BDL) [65] for hardware accelerators. The BDL is an extended C language that excludes non-synthesisable constructs (such as dynamic allocation with pointers and recursions) but includes a number of hardware-specific constructs (such as user-defined variable bitwidth and explicit clock boundary specification). CyberWorkBench uses the Cyber behavioural synthesiser [44] to transform the BDL description into RTL descriptions in Verilog or VHDL. The tool provides automatic pipelining and parallelism extraction, which are guided by attributes in the source code and global synthesis options. CyberWorkBench is built based on the idea "all-in-C", as described in [66], meaning all modules including control-intensive and data-dominant circuits are described in BDL. The synthesis and verifications are also done at the higher level of abstraction. The tool has its own verifier to check functionality of the generated RTL against the BDL description.

### 7) LegUp

LegUp [28], [49] is an open-source HLS compiler developed by researchers at the University of Toronto, and now supported by LegUp Computing Inc. It accepts ANSI C code as input and generates Verilog code that can be synthesised onto FPGAs. LegUp supports FPGAs provided by Intel, Xilinx, Lattice, Microsemi and Achronix. It works in two modes: hardware-only and software-hardware modes. In hardwareonly mode, the entire input C code is synthesised to RTL. In software-hardware mode, the high-level C code is profiled using a built-in profiler [67] to identify compute-intensive functions for hardware offloading. After manual selection of the functions for hardware acceleration, LegUp synthesises a heterogeneous system comprising a processor and accelerators built on an FPGA. The tool supports most C features for FPGA synthesis but not recursion or dynamic memory allocation. LegUp is built using the LLVM framework with Clang as its frontend. It allows hardware optimisations to perform function inlining, loop unrolling and source code modifications to parallelise sequential executions using Pthreads or OpenMP annotations. However, the insertion of these annotations is a manual process.

#### 8) BAMBU

Bambu [26] is an open-source HLS framework built in Politecnico di Milano under the PandA project [68]. It takes a behavioural description in C and an XML file specifying the configurations corresponding to different stages of the design flow. It uses the *gcc* compiler to perform target and language-independent optimisations and produces IRs in the form of a call-graph and CDFG. Bambu generates hardware modules for the functions separately, reflecting the structure of the call-graph. The modules include datapaths, FSM controllers and memory interfaces. Finally, the HLS tool combines these modules to generate an HDL description and produces logic synthesis scripts for the desired toolchains, as specified in the XML file. Currently Bambu is compatible with Xilinx Vivado Design Suite [55], Intel Quartus [61] and Lattice Diamond [69]. Bambu also produces testbenches and scripts for RTL simulation that can be run in Xilinx simulators, Mentor Modelsim [70], Verilator [71] and Verilog Icarus [72].

### 9) ROCCC

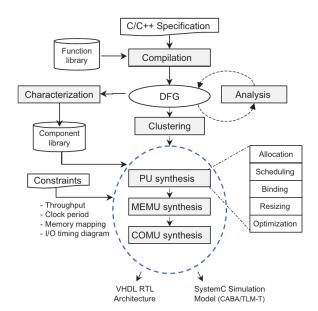

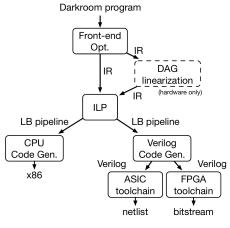

Riverside Optimizing Compiler for Configurable Circuits (ROCCC) [37], [38] is an open-source HLS compiler initially developed at the University of California Riverside. The latest versions of this tool have been developed by Jacquard Computing, who are currently maintaining it. The developers of this tool consider that it is a code accelerator instead of a HLS tool because "typically, accelerators have their semantic root in a loop nest while a general HLS tool can target any arbitrary C code. Hence, the focus of the ROCCC compiler transformations has been on loop nests" [37]. FIGURE 4 illustrates a high-level design flow of the ROCCC compiler. It does not compile entire applications to hardware, rather it allows modules and system code to be transformed to hardware. Modules refer to compute-intensive functions that can be synthesised to hardware modules. They can be reused as hardware building blocks in other modules. System code blocks perform computations on large streams of data using repeated loop iterations. The may or may not be synthesised to hardware modules but they usually result in hardware for memory interfaces. The modules and system code can be written using a subset of C constructs. Common C features including generic pointers, dynamic memory allocation, recursion, including C-library calls, and while loops are not supported by the ROCCC compiler. The compiler performs high-level transformations, such as loop and array transformations, using the SUIF compiler infrastructure [73] and generates an IR. The IR passes through the LLVM framework for low-level optimisations, such as pipelining, before VHDL

FIGURE 4. ROCCC design flow [74].

code is generated. It does not require annotations in the HLL source code to generate efficient pipelined hardware.

# 10) GAUT

GAUT [39], [40] is an open-source HLS tool developed at Université de Bretagne-Sud, France for DSP applications. It generates a RTL description in VHDL from bit-accurate high-level C/C++ code. The compiler allows developers to use the Algorithmic-C library [64] from Mentor Graphics for signed and unsigned bit-accurate integer and fixed-point variables. The design flow of GAUT is depicted in FIGURE 5. This gcc-based HLS tool generates a bit-width information annotated dataflow graph (DFG) of the application, which is then converted to GIMPLE-IR. The IR undergoes performance optimisation including dead-code elimination, redundancy eliminations and loop optimisations, and instruction-level parallelism is extracted from it. GAUT performs resource allocation, operation scheduling and binding, and storage optimisation on the IR, and finally generates a VHDL and/or SystemC description for a particular FPGA platform. During this process, GAUT uses a library of time-characterised operators that were generated using DFG and logic synthesis tools from Xilinx and Intel. The generated RTL contains a controller FSM, a datapath, and memory and communication interfaces. The tool also generates necessary scripts and data for testbenches for simulations using the Modelsim simulator. The generated RTL can be synthesised using Xilinx Vivado Design Suite [55], Intel Quartus [61] and Synopsys Design Compiler [75].

#### FIGURE 5. GAUT design flow [39].

#### 11) KIWI COMPILER

Kiwi Compiler (KiwiC) [41], [42] was developed as an open-source tool at the University of Cambridge and Microsoft Research Limited, and is now maintained by the

university. Most HLS tools accept C-like sequential programs and synthesise them for FPGAs. This HLS compiler and its associated library allow programmers to model parallel computations using a subset of the C# language and transforms them into circuits for realisation on Xilinx and Intel FPGAs. The compiler converts.NET bytecode generated as an IR from Microsoft.NET or Mono C# compilers to Verilog RTL. It maps system-level concurrency such as events, monitors and thread onto appropriate hardware implementations. The Kiwi Compiler is based on the Value State Flow Graph (VSFG) compilation technique [76]. The compilation technique exploits dynamic execution scheduling, aggressive branch prediction and loop unrolling to achieve significant performance improvements. KiwiC supports a wider subset of HLL features than many other HLS tools, including multi-dimensional arrays, threading, file-server I/O, object management and limited recursion. The tool also provides a performance predictor to allow users to explore the expected speed-up without fully synthesising the hardware.

### **B. SYNTHESISABLE HLL CODE GENERATION** (2B)

Although HLS tools allow design space exploration more quickly and easily by avoiding the restrictions of HDLs, developers still need to be aware of hardware implementation constraints while writing HLS code. Naive HLS code written without an understanding of the resultant hardware structure often yields results worse than simply running the code on a processor. Moreover, HLS tools often use C-based HLLs as inputs, and the generic C/C++ programming model does not take advantage of the concurrent nature of an FPGA. Hence, developers have to manually do complex code restructuring and insert special directives to generate synthesisable code and efficient hardware. Authors of [77] provide a guideline for transforming high-level C++ to efficient synthesisable code. But this manual process significantly impacts the productivity of system development and this situation becomes more acute for complex applications with a large base of existing code written for conventional computers.

Investigations are underway in academia and industry for generating efficient synthesisable code (i.e. HLS code) from existing HLL. After identifying compute-intensive functions, these tools analyse the source code to extract parallelism before generating synthesisable code using their own source-to-source compilers. The generated code is then fed into existing HLS tools to generate accelerator code in RTL for deployment on FPGAs. This approach is shown in FIGURE 1 on Page 174694 as design flow (2). Because this process still involves human interventions in many cases, we consider it to be "semi-automatic". The major synthesisable code generation tools are listed in TABLE 3 and will be discussed in the following subsections.

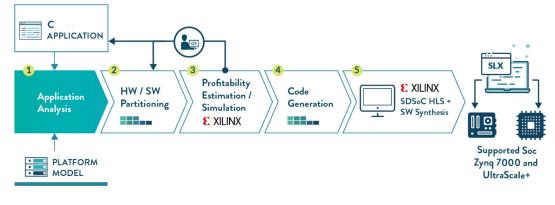

#### 1) SLX-FPGA

Silexica developed the SLX-FPGA Tool Suite [78] to help convert non-synthesisable C/C++ code to synthesisable HLS C code for Xilinx's Zynq SoC and MPSoC devices. It uses

#### TABLE 3. HLS code generation tools.

| Tool                       | Provider                                    | Open<br>source | Intro. | Update | Pedigree                         | Platform                                             | Input             | Output           | Anno-<br>tations | Target HLS                                 | Domain |

|----------------------------|---------------------------------------------|----------------|--------|--------|----------------------------------|------------------------------------------------------|-------------------|------------------|------------------|--------------------------------------------|--------|

| SLX-FPGA<br>[78]           | Silexica                                    | No             | 2017   | 2019   | Based on<br>MAPS<br>project [79] | Xilinx Zynq<br>SoC/<br>MPSoCs                        | C, C++            | HLS C            | Yes              | Vivado HLS                                 | All    |

| Merlin<br>Compiler<br>[80] | Falcon<br>Computing<br>Solutions            | No             | 2016   | 2018   |                                  | Xilinx and<br>Intel FPGAs                            | C, C++            | HLS C/<br>OpenCL | Yes              | Vivado HLS,<br>Intel<br>OpenCL<br>Compiler | All    |

| Hot & Spicy<br>[81]        | University of<br>Southern<br>California     | Yes            | 2018   | 2018   |                                  | Xilinx<br>FPGAs                                      | Python            | HLS C            | Yes              | Vivado HLS                                 | All    |

| Delft<br>Workbench<br>[53] | Delft<br>University of<br>Technology        | Yes            | 2014   | NI     |                                  | Hetetogeneous<br>platforms<br>with CPUs<br>and FPGAs | С                 | VHDL             | Yes              | DWARV<br>[27]                              | All    |

| FROST [82]                 | Massachusetts<br>Institute of<br>Technology | No             | 2017   | NI     |                                  | Xilinx<br>FPGAs                                      | FROST IR          | HLS C/C++        | No               | Vivado HLS                                 | All    |

| CAOS [83]                  | Politecnico<br>di Milano                    | Yes            | 2017   | 2019   |                                  | Xilinx<br>SoC/MPSoC                                  | C, C++,<br>OpenCL | HLS C/C++        | NI               | Vivado HLS                                 | All    |

NI = No Information found

FIGURE 6. SLX-FPGA tool flow [78].

Vivado HLS [23] and SDSoC [56] under the hood to implement the HLS code onto the Zynq devices. SLX-FPGA also works with Xilinx's recently released Vitis Unified Software Platform [58]. This tool suite is based on an academic project called MPSoC Application Programming Studio (MAPS) [79], which started in 2007 at RWTH Aachen University.

FIGURE 6 illustrates the tool flow of SLX-FPGA. It first analyses an existing conventional C/C++ application and identifies parallelisation opportunities in the form of task, data and pipeline level parallelism. It performs static analysis of the source code and dynamic analysis of the executable code, and converts the source code to a language called *C for Process Networks (CPN)*. This language is a C extension that models concurrent processes and applications. Next, it suggests a partitioning of the application between the embedded host processor and FPGA regions of the Zynq device by analysing the computation and communication behaviour of the CPN specification. The expected benefits of this partitioning are then evaluated using Xilinx's performance estimation engine. Finally, the tool suite performs source-to-source translation to emit HLS C code ("synthesisable behavioural

VOLUME 8, 2020

code" in path (2)) considering both the CPN and the mapping configuration generated by the SLX Mapper. Vendor-specific annotations for loop unrolling and pipelining are automatically inserted into the HLS code to extract parallelism and define interfaces based on optimisation decisions taken by the programmer. SLX-FPGA also provides hints for manual code restructuring to make any designated non-synthesisable functions synthesisable. The generated HLS C code then passes through the Xilinx toolchain including Vivado HSL (the "behavioural HLS tool" in path (2)) for implementation onto the Zynq devices.

SLX-FPGA provides some useful features that move the state of the art closer to the ACD, however it is still not fully automatic. It does not perform automatic code refactoring to make a non-synthesisable function synthesisable, or to optimise the performance of the generated hardware accelerator. Although the latest release of SLX-FPGA supports some Vivado HLS annotations for loop unrolling, pipelining, array partitioning and function inlining, it still does not support all of the available annotations to extract best possible performance in the generated hardware.

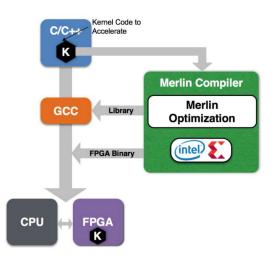

# 2) MERLIN COMPILER

Merlin Compiler [80] is a synthesisable code generation tool introduced by Falcon Computing Solutions that automates the code rewrite effort for FPGA programming. It accepts C/C++ HLL code as input and transforms it to optimised OpenCL code that can be synthesised on Xilinx and Intel FPGAs using the vendor-specific toolchains. FIGURE 7 illustrates the design flow of Merlin Compiler.

FIGURE 7. Merlin Compiler design flow [80].

Merlin Compiler can work in two modes. In manual optimisation mode, developers manually annotate the source code with a small set of OpenMP-like annotations for pipelining and parallelism. Developers who are not familiar with FPGA constructs can use automatic optimisation mode, in which they can annotate functions for acceleration, and the compiler will use a machine learning based Deep Space Exploration (DSE) to perform micro-architecture optimisations, such as global memory bursting and coalescing, memory partitioning, data reuse and data flow streaming. Merlin Compiler produces synthesisable OpenCL code (the "synthesisable behavioural code" in design flow (2b) that is transformed to binary files for FPGA configuration using Xilinx SDAccel [57] or Intel OpenCL SDK [24] (the "behavioural HLS tools" in path (2b) in the background. Although, the automatic mode can accelerate the application, there is more scope for improving performance by manually annotating the code. Moreover, in either mode the developer must still modify the code with annotations, and to include header files and initialise the Merlin runtime libraries.

Merlin compiler provides various verification strategies at different stages of the process. It generates an optimised C program before OpenCL generation, which can be compared with the input C program in CPU execution to confirm functional correctness of the accelerator. The generated OpenCL is also verified by a CPU emulation, and RTL generated by HLS is verified by co-simulation.

Merlin Compiler is available on the AWS marketplace so that FPGA-accelerated applications can be developed using

FIGURE 8. Implementation flows using the Hot & Spicy tools [81].

Amazon AWS F1 instances that contain Xilinx FPGA accelerator cards. In addition to cloud-based data centres, it also supports on-premise data centres that include Intel and Xilinx FPGA acceleration cards for data processing.

# 3) HOT & SPICY

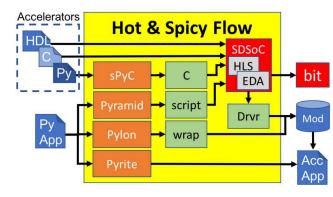

Researchers at the Information Sciences Institute, University of Southern California, have developed Hot & Spicy [81], an open-source framework and toolchain for exploiting FPGA accelerators in applications developed completely in Python. The Hot & Spicy workflow consists of: the Pythonto-C or sPyC tool, which is a source-to-source translation tool for Python syntax (at the function level) to HLS C/C++ code for the Xilinx Vivado HLS tool; the Python linker, Pylon, which generates C API wrappers/bindings for linking the Python application to C/C++ call accelerators; the Python rewriter, Pyrite, which refactors the original Python source code to make importing the accelerators possible via the wrappers generated by Pylon (instead of the Python functions, the C functions are called); and Pyramid, which generates scripts to drive the EDA implementation flow (i.e. by employing the Xilinx Vivado HLS through invoking the Xilinx SDSoC tool to generate a complete system design).

# 4) DELFT WORKBENCH

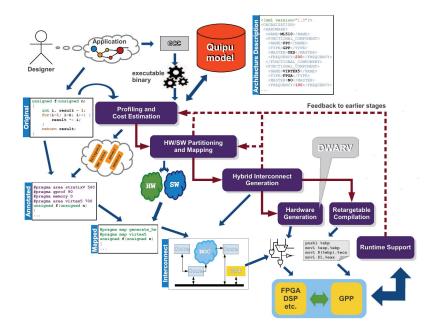

Delft Workbench (DWB) [53] is a toolchain to develop heterogeneous systems applications. As shown in FIGURE 9, a high-level application is first profiled and characterised using Quipu [84] and Quad [85] to identify candidate hardware functions. Quipu predicts the hardware resources needed to implement different functions on a reconfigurable hardware platform. Quad provides an overview of the memory access behaviour of the application. Based on the profiling information, the application is manually annotated, and partitioned and mapped to the processor and FPGA. The compute-intensive functions are mapped to the FPGA, and the reminaing functions are executed on the processor. It uses the DWARV (Delft Workbench Automated Reconfigurable VHDL) HLS compiler [27] (the "behavioural HLS tool" in path (2b) to translate the selected functions to VHDL RTL code for synthesis for the FPGA. The HLS compiler

FIGURE 9. Delft Workbench toolchain [53].

computes common expressions and ensures data locality by putting the results in registers for subsequent use, performs register allocation based on operation chaining, and allocates register and memory interfaces for parallel memory accesses. The toolchain implements a network-on-chip (NoC) based custom interconnect for communication among the accelerators. It automatically invokes the architecture-specific synthesis tools to generate bitstreams from the generated VHDL.

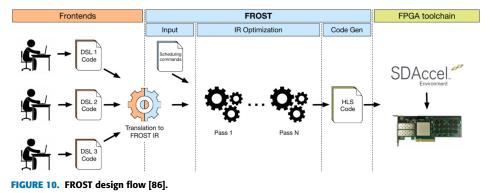

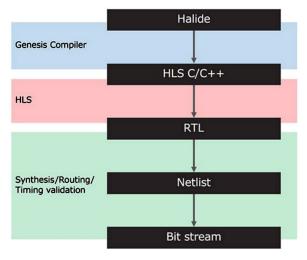

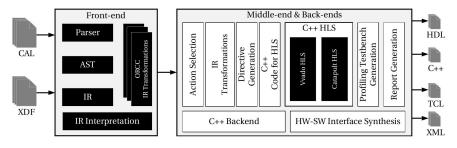

#### 5) FROST

Research publications [82], [86] introduce FROST as a common backend for Domain-Specific Language (DSL) compilers (to be discussed in Section III-C) such as Halide [87] and Tiramisu [88], targeting FPGAs. As presented in FIGURE 10, DSL compilers generate IRs (the "intermediate representation" in path (2)), and use FROST to generate efficient HLS code for Xilinx FPGAs. In these IRs, functions are represented as abstract syntax trees (ASTs). FROST takes an IR and a list of scheduling commands to produce an efficient hardware implementation. It provides a way for the hardware developer to apply guided optimisations at different design levels as well as to select the best architecture for realising the function on the target FPGA. Using the scheduling commands, a developer can specify FPGA-specific optimisations such as loop pipelining, unrolling and vectorisation, as well as the type of communication with the off-chip memory. FROST analyses the IR and manipulates function ASTs to apply FPGA-oriented transformations and optimisations. It then analyses the updated ASTs to identify libraries and variable data types for HLS code generation. FROST generates HLS-friendly C/C++ code (the "synthesisable behavioural code" in path (2)), and applies the remaining scheduling commands as HLS annotations. The generated HLS code can be synthesised and implemented on Xilinx FPGAs using the SDAccel toolchain, which involves Vivado HLS (the "behavioural HLS tool" in path (2)) in it.

# 6) CAOS

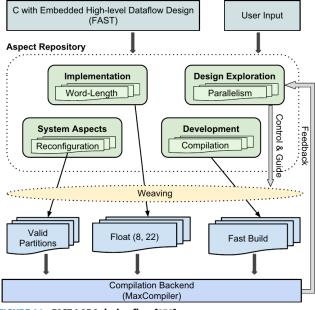

CAD as an Adaptive Open-platform Service (CAOS) [83] is a design platform developed to help application designers identify and optimise kernel functions for hardware acceleration. It also helps produce efficient, fine-tuned, accelerators for the FPGA, by generating the runtime management and the configuration files needed.

The tool takes as inputs the application code written in C/C++, datasets for code profiling, and details of the target FPGA. Users are encouraged to make use of pre-defined architectural templates, which describe the computational model of the hardware accelerator and how it communicates with the off-chip memory. This not will only improves the performance of the hardware implementation but also facilitates and improves the analyses and optimisations that might need to be carried out on the corresponding algorithms later in the CAOS workflow.

The CAOS interactive design flow consists of three phases: *frontend, function optimisation*, and *backend*. In the frontend phase, CAOS generates an IR. Using the IR and through application profiling, it then pinpoints the bottleneck functions (core/kernel functions) that may benefit from being offloaded onto the FPGA as accelerators. It also gives some hints to the designer on how the application can be partitioned into FPGA- and CPU-friendly functions. To do that, the CAOS frontend performs an applicability check which is meant to find suitable architectural templates for the application code [89].

In the functional optimisation phase, based on the architectural template suggested in the frontend phase, and using a series of static analyses and hardware resource estimations on the candidate functions for FPGA acceleration, CAOS provides performance and resource estimates for the functions offloaded to the FPGA, and suggests a range of optimisation strategies including, but not limited to, loop pipelining, loop tiling and loop unrolling. This design loop may iterate until the system developer is satisfied with the application performance and the design meets the provided constraints.

In the backend phase, CAOS produces both the runtime for executing the CPU functions and the final bitstreams needed to configure the FPGAs within the system, by leveraging the specific FPGA vendor tools (high-level synthesis and hardware synthesis tools) including Xilinx's SDAccel and Vivado HLS as well as MaxCompiler from Maxeler Technologies, based on the selected architectural template. Wherever possible, the backend can also support runtime reconfiguration of the FPGA devices through partial dynamic reconfiguration [90].

# C. DOMAIN-SPECIFIC LANGUAGE (DSL) FOR HLS (2)

Although HLS tools are improving, the benefit delivered by an FPGA hardware accelerator still depends strongly on the system developers' hardware expertise.

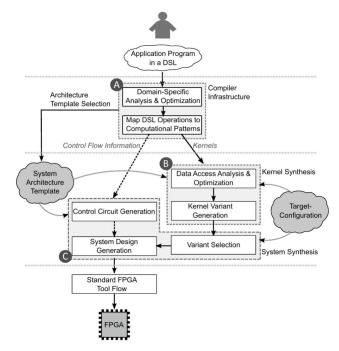

Domain-Specific Languages (DSLs) are another promising step towards design automation [91]. A DSL can be used to describe a domain-specific computing system at a higher level of abstraction than an HDL. This frees the system developers from hardware-influenced programming details so they can focus on describing the domain-specific design. At the same time the DSL can improve the efficiency of the FPGA accelerator by matching computing patterns typical of the domain with well optimised hardware. TABLE 4 shows current DSL tools for HLS.

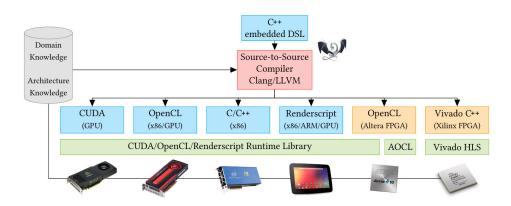

# 1) OptiML DSL

An automated design framework for realising FPGA accelerators from high-level programs written in OptiML is presented in [92], [102]. OptiML is a Scala-embedded machine learning DSL implemented using the Delite compiler framework [103], which provides a programming environment similar to MATLAB that supports machine learning code structures.