Received July 29, 2020, accepted August 9, 2020, date of publication August 19, 2020, date of current version September 1, 2020.

Digital Object Identifier 10.1109/ACCESS.2020.3017805

# Topology-Morphing Photovoltaic Microconverter With Wide MPPT Voltage Window and Post-Fault Operation Capability

DMITRI VINNIKOV<sup>1</sup>, (Senior Member, IEEE), ANDRII CHUB<sup>1</sup>, (Senior Member, IEEE), DENYS ZINCHENKO<sup>1</sup>, (Graduate Student Member, IEEE), VADIM SIDOROV<sup>1</sup>, (Student Member, IEEE), MARIUSZ MALINOWSKI<sup>1</sup>, (Fellow, IEEE), AND SERTAC BAYHAN<sup>1</sup>, (Senior Member, IEEE)

<sup>1</sup>Department of Electrical Power Engineering and Mechatronics, Tallinn University of Technology, 19086 Tallinn, Estonia

Corresponding author: Dmitri Vinnikov (dmitri.vinnikov@taltech.ee)

This work was supported in part by the Estonian Research Council under Grant PUT1443, in part by the Estonian Centre of Excellence in Zero Energy and Resource Efficient Smart Buildings and Districts (ZEBE), funded by the European Regional Development Fund under Grant 2014-2020.4.01.15-0016, and in part by the Qatar National Research Fund (a member of Qatar Foundation) under Project NPRP12S-0214-190083.

**ABSTRACT** In this paper the concept of wide input voltage range photovoltaic microconverter with post-fault operation capability is presented. This microconverter could remain operational in the case of short- or open-circuit failure of any switch of its front-end inverter. When the fault occurs, the control system automatically identifies the fault and applies the special post-fault modulation sequence thus keeping the functionality of the microconverter unchanged. The research findings are validated by the help of a 350 W experimental prototype specially developed for integration of silicon PV modules into the residential DC nanogrids with the nominal voltage of 350 V. Paper explains the multi-mode operation principle and fault identification routine. It presents the experimental efficiencies and evaluates the maximum power point tracking performance of the microconverter prior and after the short-circuit fault of an upper switch of the inverter. The daily energy yield test conducted for both cases has confirmed that the proposed approach can extend the service life of PV microconverters with a moderate impact on their performance.

**INDEX TERMS** DC-DC power converters, digital control, fault diagnosis, fault tolerance, fault-tolerant control, photovoltaic systems, power electronics, pulse width modulation, quasi-Z-source converters.

# I. INTRODUCTION

In residential and small commercial photovoltaic (PV) installations the application of module-level power electronics (MLPE) systems typically allows for better mitigation of power losses caused by various partial shading effects as well as mismatch and aging of PV modules [1]–[3]. The industrial MLPE systems today are broadly represented by the power optimizers and microinverters, which are the weather-proof devices usually located outdoors just behind the PV module or embedded in its frame [4]. Oppositely to power optimizers, which foresee a series connection of PV

The associate editor coordinating the review of this manuscript and approving it for publication was Bidyadhar Subudhi

modules, the use of a microinverter offers a possibility of direct integration of PV modules to the AC grid. Having the multistage structure, the microinverter tracks the maximum power point (MPP), steps up and inverts the output voltage of the PV module into a grid compliant AC voltage. In the last decade with the appearance of the emerging concept of the household DC distribution [5] the group of MLPE systems was expanded by the microconverters, which are used for DC integration of the PV modules [6]. In contrast to power optimizers, the microinverters and microconverters typically have a more narrow input voltage regulation range, which significantly limits their shade-tolerant performance and compatibility with different types of PV modules. However, this issue was recently addressed by the implementation of

<sup>&</sup>lt;sup>2</sup>Institute of Control and Industrial Electronics, Warsaw University of Technology, 00-662 Warsaw, Poland

<sup>&</sup>lt;sup>3</sup>Qatar Environment and Energy Research Institute, Hamad Bin Khalifa University, Doha, Qatar

advanced topology-morphing and multi-mode control principles [7]–[9], which resulted in the appearance of a novel class of the hybrid MLPE systems called Optiverter [10].

In general, being mounted just behind the PV module the MLPE devices are subjected to a harsh operating conditions.

This includes wide variation in temperatures, excess humidity, vibrations, dust and snow deposition, etc. [11]. For example, in several hot or high irradiance locations, the ambient temperature of the MLPE system could reach or ever exceed 50 °C thus elevating the internal temperature stress of the device over 75 °C. Moreover, the enclosure of MLPE device should have a high IP-rating to withstand different weather conditions like rain and wind. It has to protect the electronics from the aggressive environment within the expected lifetime, which typically exceeds 20 years [12]. For that purpose, the majority of MLPE devices are filled with a water-resistant thermal epoxy to "pot" the components and move the heat away from the hotspots to the enclosure, at the same time providing the humidity-resistant protective layer. This ensures a necessary IP rating and thermal management for the cost of maintainability as the malfunctioned or damaged potted device is unlikely to be easily repaired (Fig. 1). Typically, the faulty MLPE device is replaced with a new one according to the terms and conditions of the sales warranty or servicing contract. However, the clarification of warranty issues could be a time-consuming process resulting in the increased potential economic loss due to the downtime of the PV power system.

FIGURE 1. Photo of the disassembled PV microinverter with the thermally conducting epoxy removed at the locations of possible faults.

This paper studies the post-fault operating capability of a high-performance PV microconverter in the case of power switch failure in its front-end inverter. The topology-morphing control (TMC) is proposed as a tool for ensuring the necessary level of self-redundancy without adding extra elements to the circuit. The paper starts with the general description of the proposed microconverter and its specifications. Next, the basics of TMC and multi-mode operation principle of the microconverter are explained in Section 3. Section 4 describes the algorithm for the fast detection of the faulty switch in a front-end inverter. The experimental study in Section 5 demonstrates the performance of the proposed microconverter in the normal and post-fault operation, which is followed by the conclusions drawn in Section 6.

### **II. FAULT-TOLERANT PV MICROCONVERTER**

The idea proposed in this paper was inspired by a highperformance multi-mode series resonant PV microconverter presented in [8]. This baseline microconverter was intended for operation within an ultrawide input voltage and load range (i.e., from 10 to 60 V and from 30 to 300 W), which provided an opportunity of realization of a Global MPPT (GMPPT) based on a periodic P-V curve sweep [13]. Moreover, the ultra-wide input voltage range enabled the unique multi-module compatibility feature, which allows this microconverter to be paired with many existing PV module technologies ranging from the classic 60- and 72-cell Si panels [14] to the advanced PV roofing elements [15]. In this study, the performance of a concept from [8] is further enhanced by adding a possibility of post-fault operation, which guarantees the supply continuity in the case of failure of any of the front-end inverter switches.

### A. TOPOLOGY AND SPECIFICATIONS

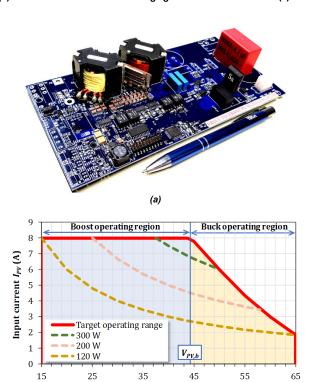

The generalized power circuit diagram of the fault-tolerant microconverter (FT-MIC) is shown in Fig. 2a. Its general view and operating power envelope are shown in Fig. 3. At the input side, the FT-MIC has an active quasi-Z-Source Network (qZSN) coupled with the Hybrid Switching Cell (HSC). This part performs the MPPT and generates the high-frequency AC voltage for supplying the step-up isolation transformer TX. The reconfigurable rectifier (RR) implemented at the output side of the FT-MIC is used for compensation of the voltage gain reduction in the post-fault operation mode.

Although this microconverter is primarily designed for feeding the PV power into the household DC nanogrid (Fig. 2b), which could also be used as a front-end of the two-stage grid-tied PV microinverters (Fig. 2c).

The general specifications of the FT-MIC are listed in Table 1. It was developed for the integration of 72- and 96-cell silicone PV modules into the residential DC nanogrids with the nominal voltage  $V_{DC} = 350$  V. The proposed approach could be also adopted for other types of PV modules and output voltages by changing the turns ratio of the isolation transformer TX. The primary side of the FT-MIC employs HSC realized on the generic Si MOSFETs. As the qZSN usually requires two magnetic elements, which would impose weight and power density constrains, the two-winding coupled inductor was implemented thus leading to a more compact and lightweight design. To improve the performance and enable the multi-mode control of the FT-MIC, the diode of the qZSN was replaced by the Si MOSFET. The output side of the microconverter is realized on SiC Schottky Barrier Diodes in combination with the mode-changing switch/relay  $S_R$ , which is used for changing the topology and resulting voltage gain of the rectifier by shorting the diode  $D_4$ . The discussed FT-MIC is essentially a series-resonant isolated buck-boost converter that uses the hybridization of properties for enabling the ultra-wide input voltage without significant deterioration of the efficiency. In the boost mode, it operates as a hybrid of the

FIGURE 2. Generalized topology of the proposed fault-tolerant PV microconverter (a) and its application possibilities in the household DC nanogrid (b) or as a front-end of the two-stage grid-tied PV microinverter (c).

**FIGURE 3.** General view of the proposed FT-MIC (a) and its operating power envelope with predefined boost and buck regions and constant power operation limits (b).

Input voltage  $V_{PV}$  (V)

quasi-Z-source and series resonant DC-DC converter (SRC), while in the buck mode, it resembles the SRC controlled by the phase-shift modulation (PSM). The series resonant tank is formed by the leakage inductance of the isolation transformer  $L_{lk}$  and capacitor  $C_2$  utilized in the RR. As the quality factor of such an integrated resonant tank is significantly lower than unity the PSM control approach with discontinuous resonant current (DcPSM) was implemented thus allowing for the balanced cost-performance tradeoff that is important for the industrial design.

# B. HYBRID SWITCHING CELL

The idea of the HSC originates from [16], where it was proposed as an alternative realization approach of the

TABLE 1. Specifications of the proposed FT-MIC.

| Operating parameters            |                                                                      |  |  |  |

|---------------------------------|----------------------------------------------------------------------|--|--|--|

| Input voltage range, $V_{PV}$   | 1565 V                                                               |  |  |  |

| Maximum input current, $I_{PV}$ | 8 A                                                                  |  |  |  |

| Rated output voltage, $V_{DC}$  | 350 V                                                                |  |  |  |

| Switching frequency, $f_{SW}$   | 95 kHz                                                               |  |  |  |

| Dead-time of inverter switches  | 50 ns                                                                |  |  |  |

| Operating power range, $P$      | 35350 W                                                              |  |  |  |

| Compo                           | nents                                                                |  |  |  |

| Microcontroller                 | ST STM32F334R8T6<br>(CortexM4,72MHz)                                 |  |  |  |

| $S_1S_4, S_{qZS}$               | ON Semiconductor / Fairchild<br>FDMS86180                            |  |  |  |

| $D_1D_4$                        | Wolfspeed C3D02060E                                                  |  |  |  |

| $S_R$                           | Single-pole normally open<br>relay IXYS CPC1968<br>0.6 μH            |  |  |  |

| $L_{lkqZS}$                     |                                                                      |  |  |  |

| $L_{mqZS}$                      | 12 μΗ                                                                |  |  |  |

| $L_{lk}$                        | 64 μΗ                                                                |  |  |  |

| $L_m$                           | 1 mH                                                                 |  |  |  |

| n                               | 8                                                                    |  |  |  |

| $C_{qZSI},C_{qZS2}$             | MLCC 26.4 μF (12 parallel KEMET C1210C225K1R)                        |  |  |  |

| $C_I$                           | MLCC 26.4 μF (12 parallel<br>KEMET C1210C225K1R)                     |  |  |  |

| $C_2$                           | Metallized Polypropylene 66 nF<br>(2 parallel EPCOS<br>B32672Z6333K) |  |  |  |

| $C_f$                           | Metalized Polyester 4.7 μF<br>WIMA MKS4G044706G                      |  |  |  |

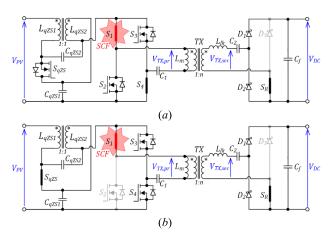

bidirectional SRC with a possibility of post-fault operation in the case of short-circuit failure (SCF) or open circuit failure (OCF) of any of its semiconductors. The HSC shown in Fig. 4a has the full-bridge structure  $(S_1 ... S_4$  in Fig. 2a), and in the case of a semiconductor switch failure, can be reconfigured to the asymmetric half-bridge by merely modifying the modulation sequence of its switches [17]. Such an idea of inherent fault tolerance considers that the damaged switch could be further used either as a conducting (SCF) or a non-conducting (OCF) circuit branch. Moreover, the opposite healthy switch in the same leg must be continuously turned off or on, thus realizing the post-fault reconfiguration of the HSC in the case of SCF or OCF, correspondingly. As the post-fault modulation sequences of the HSC are identical for both fault types and different fault locations, the SCF of  $S_1$ will be used as a case study in the remainder of this paper.

**FIGURE 4.** Hybrid switching cell (a) with examples of its reconfiguration in the case of SCF of the switch  $S_1$ : asymmetric half-bridge (b) and single-switch ISC (c).

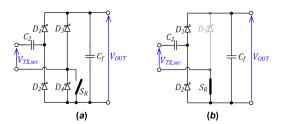

**FIGURE 5.** Reconfigurable rectifier (a) with an example of its reconfiguration into the Greinacher voltage-doubler topology by shorting the diode  $D_4$  (b).

As it was previously mentioned, in the case of SCF of  $S_1$ , the opposite switch  $S_2$  in the same leg must be continuously turned off to avoid the short-circuit of the input voltage source (Fig. 4b). As the damaged switch creates the current-conducting circuit path, one of the AC terminals of the RR becomes connected to the DC rail of the HSC. The switches  $S_3$  and  $S_4$  of the healthy leg are controlled complementary and generate the unipolar pulsed voltage  $V_1$ . For making the output AC voltage  $V_{TX,pr}$  bipolar, the HSC employs the DC blocking capacitor  $C_1$  which could also perform a function of the resonant capacitor [18].

In a similar way, the reconfiguration approach is applied to the quasi-Z-source galvanically isolated DC-DC converters (qZSC), where in the case of SCF of the switch  $S_1$ , the HSC could be reconfigured into a single-switch qZSC (Fig. 4c). In that case, the switch  $S_2$  is continuously turned off to avoid the short-circuiting of the impedance-source network. The switch  $S_4$  is permanently turned on thus connecting the DC rail of the HSC to its output AC terminal. The voltage gain is controlled by the duty cycle D of the switch  $S_3$ . During the off-state of the  $S_3$ , the transformer TX is supplied from the qZSN with the unipolar voltage pulses, and the capacitor  $C_1$  acts as the DC blocking capacitor that prevents the transformer core from the saturation [19].

### C. RECONFIGURABLE RECTIFIER

After the described post-fault reconfiguration of the HSC into a half-bridge or single-switch topology, the resulting DC voltage gain of the microconverter is reduced twofold. To keep the output voltage unchanged the FT-MIC features the reconfigurable rectifier (RR) which can compensate the gain reduction by the reconfiguration from a full-bridge to a Greinacher voltage-doubler structure (Fig. 5). For that

FIGURE 6. Normal operation of the proposed PV-MIC: operating regions, modulation methods and experimental control variables at different constant operating power levels.

purpose the mode-changing switch/relay  $S_R$  is turned on, thus connecting one of the AC terminals of the RR to the output of the microconverter. The opposite diode in the same leg ( $D_3$  in Fig. 5b) becomes reverse-biased, and the rectification is done only by the diodes  $D_1$  and  $D_2$ . Such shorting of a diode in a full-bridge rectifier offers the simplest way of the topology morphing and requires a single relay with the corresponding control circuitry. For more demanding applications, the use of a semi-controlled RR could be also considered, which can offer slightly better efficiency for the cost of a more complex realization and control [20]. Moreover, in the case of a full-controlled RR the microconverter could be kept operational even at a simultaneous failure of one of the switches in its primary and secondary sides [16].

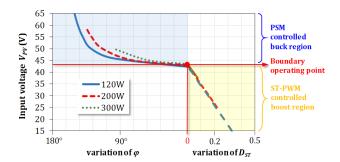

### D. MULTI-MODE CONTROL

One of the key features of the proposed FT-MIC is that it can remain operational after the SCF of OCF of any switch of the HSC. Moreover, after the fault, the microconverter can still ensure the wide DC gain range similar to the normal operation. For enabling that, the buck-boost multi-mode control was applied in both cases (Fig. 3b). Thanks to unique control flexibility offered by the qZSC [21], the buck-boost functionality was realized in a single switching stage, i.e., in the HSC. Next, the operation and control principle of the FT-MIC during the normal and post-fault operating conditions are described in detail.

### **III. NORMAL OPERATION**

Throughout its prognosed lifetime, the proposed FT-MIC will operate as a full-bridge quasi-Z-source SRC with the full-bridge rectifier (Fig. 2a). Similarly to the baseline topology [8], the input voltage regulation range is divided into two regions – boost and buck operation regions – with the boundary point  $V_{PV,b}$ , which is used for selection of the turns ratio n of the step-up isolation transformer (Fig. 3b):

$$n = \frac{V_{DC}}{V_{PV,b}}. (1)$$

As the  $V_{PV,b}$  in the given case study was set to 44 V, the isolation transformer with the turns ratio n=8 was selected for ensuring the demanded DC voltage gain.

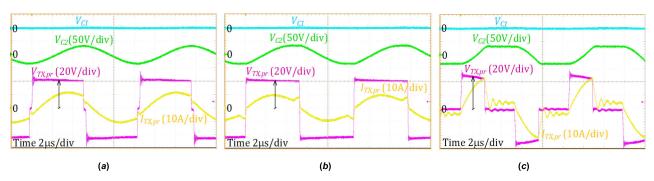

**FIGURE 7.** Experimental waveforms of the proposed FT-MIC during the normal operation at 300 W in three different operating points: in a boost region at  $V_{PV} = 40 \text{ V}$  and  $D_S = 0.046$  (a), boundary operating point  $V_{PV,b} = 44 \text{ V}$  (b) and in a buck region at  $V_{PV} = 50 \text{ V}$  and  $\varphi = 100^{\circ}$  (c).

When the operating point of the FT-MIC moves to the boost region ( $V_{PV,boost} = 15...44$  V, see Fig. 3b) it starts operation as a full-bridge quasi-Z-source SRC controlled by the shoot-through PWM (ST-PWM) at the resonant frequency. The DC voltage gain is regulated by the variation of the shoot-through duty cycle:

$$G_{N,boost} = \frac{V_{DC}}{nV_{PV}} = \frac{1}{1 - 2D_{ST}},$$

(2)

where  $D_{ST}$  is the cumulative duty cycle of the shoot-through states over the switching period T ( $D_{ST} = t_{st}/T$ ). The shoot-through states are generated by the cross-conduction of all switches of the HSC that occur twice per switching period.

If the operating point is located in the range from 44 V to 65 V (Fig. 3b), the microconverter starts operation in the buck mode, and the DcPSM regulates the output voltage at the resonant frequency. The application of this control method to the impedance-source galvanically isolated DC-DC converters was described in [22]. In the DcPSM, the switch  $S_{qZS}$  is always conducting which bypasses the qZSN, and the microconverter operates similarly to the classical voltage-source SRC. The output voltage is controlled by the phase shift angle  $\varphi$  between the leading ( $S_1$  and  $S_2$ ) and lagging ( $S_3$  and  $S_4$ ) legs of the HSC. The control characteristic of the FT-MIC in the buck mode depends strictly on the quality factor Q of the resonant network:

$$G_{N,buck} = \frac{V_{DC}}{nV_{PV}} = 0.5 \left[ A \left( \frac{2}{\pi Q} - 1 \right) + \sqrt{\left( \frac{2}{\pi Q} - 1 \right)^2 A^2 + A \frac{8}{\pi Q}} \right], \quad (3)$$

where

$$A = 0.5 - 0.5 \cdot \cos \left[ \pi \cdot (1 - \frac{\phi}{180}) \right] \quad \text{and } Q = \frac{8\pi f_{SW} L_{lk}}{R_L}.$$

(4)

Fig. 6 shows the experimental control variables of the FT-MIC for the normal operation at different power levels considering the limitations shown in Fig. 3a. In the ST-PWM boost region, the FT-MIC has linear control characteristics

with almost no dependence on the operating power. However, in the PSM buck region, the FT-MIC gain (4) strictly depends on the load  $R_L$  that is proportional to the Q-factor of the integrated series resonant tank.

The experimental operating waveforms of the FT-MIC during the normal operation at 300 W are shown in Fig. 7. Assuming  $C_1 \gg n \cdot C_2$ , the leakage inductance of the isolation transformer resonates only with the capacitor  $C_2$ , which ensures zero-current switching of the rectifier diodes. At the same time, the transformer magnetizing current provides the soft-switching of HSC transistors at any load. The voltage swing across the resonant capacitor  $C_2$  equals 68 V, which is in a good agreement with (5).

$$\Delta v_{C2(N)} = \frac{P}{2 \cdot f_{SW} \cdot V_{DC} \cdot C_2}.$$

(5)

During normal operation, the FT-MIC features a full symmetry of operation thus the average voltages of  $C_1$  and  $C_2$  remain zero within the whole operating range.

# IV. RECONFIGURATION AND POST-FAULT OPERATION

In the case of SCF of an HSC switch, the FT-MIC is reconfigured either into a single-switch qZSC or an asymmetric half-bridge converter. The topology morphing scenario depends on the operating point and is realized by applying one of the post-fault modulation sequences. The reduction of a voltage gain after the reconfiguration is compensated by the activation of the switch/relay  $S_R$ , which changes the structure of RR to a Greinaher voltage doubler rectifier (GVDR). Next, the case study scenario of the post-fault operation after the SCF of a switch  $S_1$  is discussed.

In the boost region, i.e., from 15 V to 44 V, the reconfigured FT-MIC starts operating as a single-switch qZSC with GVDR [23]. The post-fault modulation sequences of the FT-MIC in the boost region are presented in Table 2 for different faults. The selected fault scenario is visualized in Fig. 8a. The DC voltage gain is regulated by the variation of a common duty cycle D of the diagonal pair of healthy switches ( $S_2$  and  $S_3$  in the case of SCF of  $S_1$ ) controlled synchronously:

$$G_{PF,boost} = \frac{V_{DC}}{nV_{PV}} = \frac{1}{1 - 2D}.$$

(6)

**FIGURE 8.** Power circuit of the proposed PV-MIC after the reconfiguration in the case of CSF of  $S_1$ : single-switch qZSC with GVDR in the boost region (a), and asymmetric half-bridge with GVDR in the buck region (b).

The switch  $S_{qZS}$  conducts current only during the off-state of  $S_2$  and  $S_3$ . To avoid cross-conduction of the diagonal switches and  $S_{qZS}$ , the dead-time should be added between their switching transients. During the off-state of the switches  $S_2$  and  $S_3$ , the primary winding of the transformer TX is supplied from the qZSN with the unipolar voltage pulses through the capacitor  $C_1$  that acts as the DC-blocking capacitor preventing the transformer core from saturation.

In the buck region, i.e., from 44 V to 65 V, the topology of HSC is reconfigured to the asymmetric half-bridge, while the switch  $S_{qZS}$  is turned on permanently (Fig. 8b). The other switch in the leg with the SCF is turned off continuously to avoid the short circuit of the input side. The transistors in a healthy leg of the HSC are being switched alternately with a deadtime. One of these switches is conducting for a time interval shorter than half of the switching period, i.e., its duty cycle is always smaller than 0.5. The duty cycle of the opposite switch becomes larger than 0.5, which results in the asymmetrical voltage  $V_1$  at the output terminals of the inverter bridge. The capacitor  $C_1$  of the HSC is used as a DC-blocking cap to avoid the saturation of the transformer magnetic core. The resulting difference in duty cycles  $\Delta D_a$ is used as a control variable in the buck region. The post-fault modulation sequences for different fault scenarios of the FT-MIC operating in the buck region are presented in Table 3 and the selected case study with SCF of  $S_1$  is visualized in Fig. 8b. It should be noted that the qZSN in the post-fault buck mode is permanently bypassed by keeping the  $S_{aZS}$ continuously conducting. This helps to avoid the influence of the qZSN on the output voltage regulation [24] so the DC gain of the FT-MIC could be controlled similarly to that of the voltage-source series resonant converters [25], [26]:

$$G_{PF,buck} = \frac{V_{DC}}{nV_{PV}} = \frac{1}{2} \left( \left( \frac{1}{2} - B \right) C + \sqrt{\left( B - \frac{1}{2} \right)^2 C^2 + 4BC} \right), \quad (7)$$

TABLE 2. Post-fault modulation sequences in the boost region.

| Faulty<br>device | $S_I$ | $S_2$ | <b>S</b> <sub>3</sub> | S4  | $S_{qZS}$ | $S_R$ |

|------------------|-------|-------|-----------------------|-----|-----------|-------|

| $S_I$            | SCF   | PWM   | PWM                   | ON  |           |       |

| $S_2$            | PWM   | SCF   | ON                    | PWM | PWM       | OM.   |

| $S_3$            | PWM   | ON    | SCF                   | PWM |           | ON    |

| $S_4$            | ON    | PWM   | PWM                   | SCF |           |       |

TABLE 3. Post-fault modulation sequence in the buck region.

| Faulty<br>device | $S_1$ | $S_2$ | <b>S</b> 3 | S4  | $S_{qZS}$ | $S_R$ |

|------------------|-------|-------|------------|-----|-----------|-------|

| $S_I$            | SCF   | OFF   | PWM        | PWM |           |       |

| $S_2$            | OFF   | SCF   | PWM        | PWM |           | ON I  |

| $S_3$            | PWM   | PWM   | SCF        | OFF | ON        | ON    |

| $S_4$            | PWM   | PWM   | OFF        | SCF |           |       |

where

$$B = C_2 R_L f_{SW}$$

and  $C = 1 - \cos\left(\frac{\omega_r (1 - \Delta D_a)}{f_{SW}}\right)$ . (8)

Fig. 9a shows the experimental control variables of the microconverter for the post-fault operation at different power levels and considering the limitations from Fig. 3a. Similar to the normal operation, the FT-MIC features the resonant properties in the post-fault buck region, and its control characteristics depend strictly on the load conditions. In the boost region, the FT-MIC is capable of operating with the duty cycles starting from 0.12, which is imposed by the thermal limitations of passive convection cooling. The boost region can be extended to overlap with the buck region. This allows for the implementation of transition between the modes, as shown in Fig. 9b. A narrow voltage hysteresis band ensures stable operation during mode transition transients caused by the recharging of capacitors. The hysteresis transition between the microconverter modes is possible as all control variables can be pre-calculated for this.

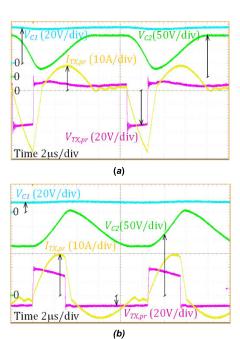

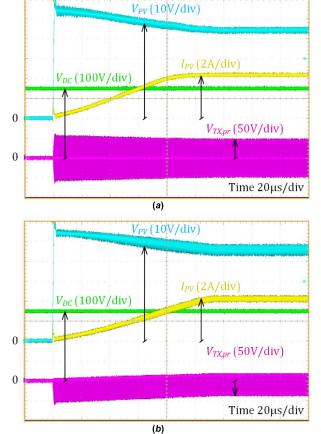

The experimental operating waveforms of the microinverter during the post-fault operation at 300 W are shown in Fig. 10. The operation asymmetry is clearly seen in both the boost (Fig. 10a) and buck (Fig. 10b) operation points. Operating voltages of capacitors  $C_1$  and  $C_2$  have the DC component, which can be calculated from equations in Table 4. The voltage swing across the resonant capacitor  $C_2$  is close to 140 V, which is in a good agreement with (9).

$$\Delta v_{C2(PF)} = \frac{P}{f_{SW} \cdot V_{DC} \cdot C_2}.$$

(9)

**FIGURE 9.** Post-fault operation of the proposed FT-MIC: operating regions, modulation methods, and experimental control variables at different constant power levels (a), and hysteresis implementation of the transition between modes (b).

**TABLE 4.** Average voltages of  $C_1$  and  $C_2$  after reconfiguration.

|       | Boost region                                                 | Buck region                                                      |

|-------|--------------------------------------------------------------|------------------------------------------------------------------|

| $C_I$ | $\frac{V_{\rho_V} \cdot (1-D)}{1-2 \cdot D}$                 | $V_{_{PV}}\cdot (0.5-\Delta D_{_a})$                             |

| $C_2$ | $\frac{V_{\scriptscriptstyle PV}\cdot n\cdot D}{1-2\cdot D}$ | $V_{\scriptscriptstyle PV} \cdot n \cdot (G - 0.5 + \Delta D_a)$ |

### **V. FAULT IDENTIFICATION ROUTINE**

There are several approaches to detect transistor faults during the converter operation. In high power circuits, where the cost of sensors is negligible compared to the cost of switches, additional measurement circuits could be used to detect the fault. In mid- and low-power circuits use of driver with fault detection feature might be used. However, the commercial drivers for MOSFETs have limited fault detection functionality. They are designed for SCF detection and, consequently, protect conventional voltage-source converters from failures in DC-link capacitors or remaining healthy switches [27]. Hence, additional measures are required for detecting the OCFs [28]. There are several methods capable of detecting both OCF and SCF at the cost of auxiliary sensors and digital signal processing: voltage sensing of magnetic components through auxiliary windings [29], diode voltage sensing [30], capacitor current sensing [31], inductor current sensing using custom Rogowski coil [32] or conventional sensors [33], etc. Their sensitivity and robustness to noise can be improved by employing artificial neural networks [34] or state observers [35], [36].

**FIGURE 10.** Experimental waveforms of the proposed FT-MIC during the post-fault operation at 300 W in the boost region at  $V_{PV}=40$  V and D=0.18 (a) and in the buck region at  $V_{PV}=50$  V and  $\Delta D_a=0.2$  (b).

FIGURE 11. Synchronous measurement of parameters for fault detection.

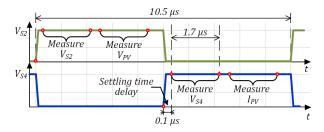

Another approach is to measure converter voltages and currents in the key points and compare them with a predefined pattern to detect a fault. This methodology is cheaper, but it has drawbacks – slow detection time and necessity to calculate patterns and values to be compared for each topology state separately. Still, this paper describes a fault detection method for the qZSC based on a measurement of a drain-source voltage across the bottom switches  $S_2$  and  $S_4$ . In addition, the input voltage and current measurements, which are used for the MPP tracking, can be also used as input signals for the fault identification routine. Relatively slow fault identification time of the microcontroller unit (MCU) is a minor drawback due to the low sensitivity of a qZSC to abnormal conditions caused by the faults.

The proposed fault identification approach is based on the detection patterns that are compared to the measured values during operation. Table 5 presents reference voltages across the switches  $S_2$  and  $S_4$  during switching states of the converter in the normal operation. It is worth mentioning that the difference between these voltages equals the transformer voltage  $V_{TX,pr}$  in the normal operation. Table 6 shows six SCF

**TABLE 5.** Voltages across switches  $S_2$  and  $S_4$  during normal operation.

| $S_I$ | $S_2$ | <b>S</b> <sub>3</sub> | S4  | $V_{S2}$    | $V_{S4}$    |

|-------|-------|-----------------------|-----|-------------|-------------|

| ON    | OFF   | OFF                   | ON  | $V_{TX,pr}$ | 0           |

| OFF   | ON    | ON                    | OFF | 0           | $V_{TX,pr}$ |

| ON    | ON    | OFF                   | OFF | 0           | 0           |

| OFF   | OFF   | ON                    | ON  | 0           | 0           |

TABLE 6. Voltages across switches during short-circuit failure.

| Fault | $S_I$ | $S_2$ | <b>S</b> <sub>3</sub> | S4  | $V_{S2}$           | $V_{S4}$           |

|-------|-------|-------|-----------------------|-----|--------------------|--------------------|

| 1     | 1 CCE | OFF   | OFF                   | ON  | $=V_{TX,pr}$       | 0                  |

| 1     | SCF   | ON    | ON                    | OFF | 0                  | $0 \neq V_{TX,pr}$ |

| 2     | ON    | SCF   | OFF                   | ON  | $0 \neq V_{TX,pr}$ | 0                  |

| 2     | OFF   | SCF   | ON                    | OFF | 0                  | $=V_{TX,pr}$       |

| 3     | SCF   | SCF   | OFF                   | ON  | $0 \neq V_{TX,pr}$ | -                  |

| 3     | SCF   | SCF   | ON                    | OFF | -                  | $0 \neq V_{TX,pr}$ |

| 4     | SCF   | OFF   | SCF                   | ON  | $0 \neq V_{TX,pr}$ | -                  |

| 4     |       | ON    | SCF                   | OFF | -                  | $0 \neq V_{TX,pr}$ |

|       | 5 SCF | OFF   | OFF<br>ON             | SCF | $=V_{TX,pr}$       | -                  |

| 3     |       | ON    |                       | SCF | -                  | $0 \neq V_{TX,pr}$ |

| 6     | ON    | CCE   | OFF                   | CCE | $0 \neq V_{TX,pr}$ | -                  |

| 0     | OFF   | SCF   | ON                    | SCF | -                  | $=V_{TX,pr}$       |

TABLE 7. MCU parameters related to fault identification routine.

| Parameter                           | Symbol       | Value |

|-------------------------------------|--------------|-------|

| ADC sampling time, ns               | samp. time   | 7.5   |

| ADC resolution, bits                | $N_{RES}$    | 12    |

| ADC sample rate, kSamples/s         | $N_{SAPM}$   | 400   |

| Calculated measurement time, ns     | $t_{meas}$   | 280   |

| Time of fault detection routine, us | $t_{handle}$ | 1.7   |

cases out of many possible in the converter. Fault 1 describes SCF of one top transistor in the bridge. Execution of the fault detection routine by the MCU is described in Fig. 11. After the fault 1 occurs, the energy can still be transferred to the load during the first half-period, like in the normal operation. However, in the second half-period, the fault could be detected due to abnormal switch voltage  $V_{S4}$  according to Fig. 11. In this state, the microconverter could be reconfigured as proposed in Fig. 8. The fault 2 describes SCF of one bottom transistor, fault 5 – SCF of a top and a bottom transistor in different bridge legs. Reconfiguration for the fault 2 would be similar to that for the fault 1. The fault 5 is one of the few cases of dual fault in semiconductors that can still be reconfigured to rover the converter, but only in the boost mode as this fault pattern is compatible with Fig. 8a. Dual-switch faults 3, 4, 6 listed in Table 6 are not reconfigurable and result in permanent damage of the microconverter. However, the faults 4 and 6 allow for safe shutdown of the microconverter. The identification of OCFs is not described for brevity but can be implemented in the same way as the identification of SCFs.

Table 7 shows the MCU parameters related to the fault detection routine. The analog to digital converter (ADC) embedded in the MCU was used for measurement of the voltages  $V_{S2}$  and  $V_{S4}$  synchronously with the PWM generation. The delays and trigger points used in this study are described in Fig. 11. High-resolution timer peripheral

FIGURE 12. Experimental waveforms during fault detection of the proposed microconverter during SCF of the switch S<sub>2</sub>.

generates PWM signals and triggers ADC measurement. The ADC routines took 61% of MCU calculation time on average. However, the fault detection implemented with hardware abstraction layer (HAL) drivers could be optimized by employing low-layer library functions. In addition, a more powerful MCU with higher clock frequency could be used to decrease detection time when needed.

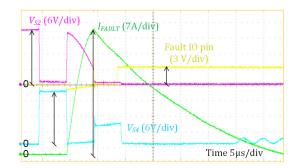

In order to test fault detection and evaluate fault tolerance, transistor  $S_2$  was short-circuited randomly. The experiment was repeated several times. The worst-case among the measured SCF fault events is presented in Fig. 12. The blue and purple waveforms correspond to the voltages  $V_{S2}$  and  $V_{S4}$ , respectively. The green waveform is the current flow through an external short circuit current path applied in parallel with the switch  $S_2$ . The same current would flow through the switch  $S_1$ . The current is rising with the slope limited by the coupled inductor of qZSN. The transistors used in the experimental prototype are rated for the peak current of 100 A, which was not exceeded in healthy switches during the SCF detection delay. Purple waveform  $V_{S2}$  shows the discharge of the qZSN capacitors due to the SCF. The yellow waveform corresponds to an MCU output pin indicating when the control system has detected the SCF.

As a result, the proposed approach provides a low-cost fault detection implementation using simple resistive dividers as sensors and MCU ADCs at no extra cost. The fault detection is fast enough to prevent destroying healthy transistors from overtemperature or secondary breakdown. Converters for high voltage step-up applications often use overrated transistors to limit the conduction losses, which in combination with the current limiting features of the qZSN allow implementing the proposed low-cost fault detection.

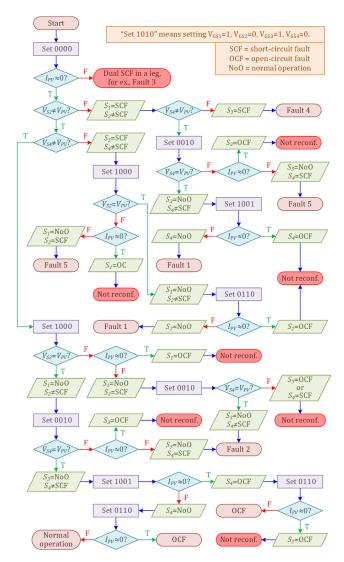

When a fault is detected, the microconverter is turned off for a short time interval to make sure that all currents and voltages reach steady-state conditions. Then, a simple approach is employed for fault identification needed to select an appropriate post-fault modulation sequence. A simplified flowchart explaining the fault identification routine is presented in Fig. 13. The main principle is in the application of different switching vectors of 1.5  $\mu$  s duration to the input-side bridge and further evaluation of converter response. The test starts with the input current measurement

FIGURE 13. Simplified flowchart for identification of faults of the semiconductor switches according to Table 6.

to check for non-recoverable short-circuit faults. In the figure, "Non reconf." corresponds to non-recoverable double faults.

# VI. EVALUATION OF THE PERFORMANCE

In this section, the experimental performance benchmarking of the proposed FT-MIC is presented for the normal and post-fault operating scenarios.

### A. POWER CONVERSION EFFICIENCY

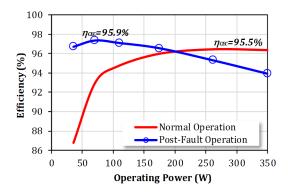

The power conversion efficiency of the proposed FT-MIC was evaluated with the help of a precision power analyzer Yokogawa WT1800. In the first test the efficiency was measured at the boundary operating point  $V_{PV,b} = 44$  V at different power levels from 10 to 100% of the rated value of 350 W. It is worth mentioning that in this point the converter operates as a series resonant DC transformer (like in Fig. 7b) thus demonstrating the highest power conversion efficiency. As it is seen from Fig. 14, during the normal operation, the

FIGURE 14. Evaluation of California Energy Commission (CEC) weighted efficiency of the proposed FT-MIC during the normal and post-fault operation at  $V_{PV.b} = 44 \text{ V}$ .

proposed FT-MIC demonstrates the efficiency of over 96% in the range from 200 to 350 W with the peak value reaching 96.5% at 250 W. On the other hand, during the post-fault operation, the FT-MIC features the efficiency over 96% in the power range from 35 to 200 W achieving the peak value of 97.3% at 70 W.

Next, the California Energy Commission (CEC) weighted efficiency  $\eta_{CEC}$  was calculated as:

$$\eta_{CEC} = 0.04 \cdot \eta_{10\%} + 0.05 \cdot \eta_{20\%} + 0.12 \cdot \eta_{30\%} + 0.21 \cdot \eta_{50\%} + 0.53 \cdot \eta_{75\%} + 0.05 \cdot \eta_{100\%}, (10)$$

where  $\eta_{10\%}$ ,  $\eta_{20\%}$ ,  $\eta_{30\%}$ ,  $\eta_{50\%}$ ,  $\eta_{75\%}$ ,  $\eta_{100\%}$  are the efficiency values measured at 10%, 20%, 30%, 50%, 75% and 100% of the rated power, correspondingly [10]. It is remarkable that having different power conversion efficiency profiles the FT-MIC during the normal and post-fault operation features almost identical CEC efficiency in the range from 95.5 % to 95.9 %.

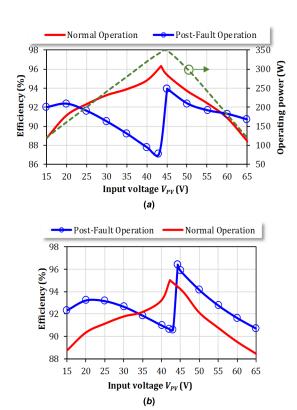

Next, the efficiency variation over the predefined input voltage range of 15...65 V was evaluated. First, the efficiency curves shown in Fig. 15a were acquired for the FT-MIC operating with the predefined power envelope of the target operating range shown in Fig. 3b. In the next test, the efficiency was evaluated under the constant power operation at 120 W (Fig. 15b). The reconfigured converter has demonstrated excellent performance in the buck mode showing up to 3% better efficiency than in the normal operation.

The transition between the boost and buck regions was realized near the input voltage of 44 V. Therefore, an efficiency step of up to 7 % can be observed at this voltage in the post-fault operating conditions due to the change of the operating mode (Fig. 15). It was found that after the post-fault reconfiguration, the proposed FT-MIC was able to continue operation and ensure the demanded output voltage within the specified target operating range.

Based on the obtained results, it could be concluded that the microconverter could operate at higher light-load efficiency in the case of post-fault operation. Depending on the thermal design, power curtailment could be used when converter

FIGURE 15. Experimental power conversion efficiencies of the proposed FT-MIC during the normal and post-fault operation for the predefined variable power envelope shown in Fig. 3b (a) and at constant power of 120 W (b).

**FIGURE 16.** I-V and P-V characteristics of the case study PV module in the NOCT conditions.

operates in the post-fault conditions and very high ambient temperature, or unusually high solar irradiance.

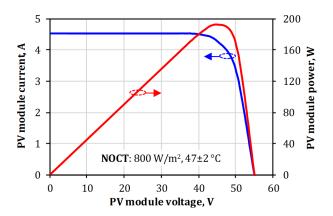

### **B. MPPT PERFORMANCE**

The study of the MPPT performance is based on a physical model of the polycrystalline Si-based PV module Solar Innova SI-ESF-M-P125-96 that contains 96 typical PV cells. It features the nameplate power rating of 275 W. Fig. 16 show example of its characteristics that correspond to the Nominal Operating Cell Temperature (NOCT) conditions: solar irradiance of 800 W/m<sup>2</sup>, air temperature of 20 °C, the air

FIGURE 17. Experimental setup for MPPT performance evaluation.

quality of 1.5, wind speed of 1 m/s, and PV cell temperature of 47  $^{\circ}$ C [37]. This corresponds to the target operating range of the proposed FT-MIC and illustrates the transition between the modes in the post-fault conditions.

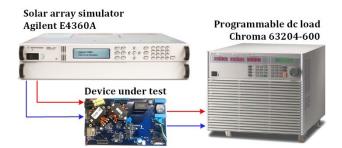

The experimental setup shown in Fig. 17 was used in this and the next subsections. It contains solar array simulator (SAS) Keysight E4360A, device under test (FT-MIC prototype from Fig. 3*a*), and programmable DC load Chroma 63204 that was set up for constant voltage mode at the typical voltage of the residential DC microgrids of 350 V.

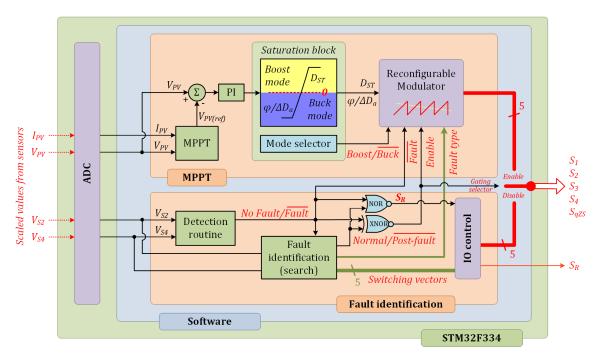

The sketch of the control system that implements the MPPT functionality along with the fault detection and identification is shown in Fig. 18. These two algorithms are decoupled, and the MPPT is executed until a fault is detected. The MPPT block utilizes a simple incremental conductance algorithm for generating the reference voltage. The PI controller ensures that the converter reaches the new reference point. The output of the PI controller is bipolar to implement the multi-mode control principle: positive output is used as the boost mode control variable, while the absolute value of the negative output signal is translated into the buck mode control variable, like in [8].

Once a fault is detected, the fault detection block changes its status output (inverse "Fault" signal), which results in disabling the main pulse-width modulator by changing the output of the XNOR block. Next, the fault identification block takes over the control of the gating signals. It performs a fault search algorithm by directly setting different switching vectors to the corresponding input/output (IO) pins of the microcontroller, according to the flowchart from Fig. 13. When the fault is identified, this block provides a fault code to the main modulator for reconfiguration of modulation sequences and enables the modulator through the XNOR block by setting the status output (inverse "Post-fault" signal) to the low level. After that, the MPPT routine can be restarted using the recovered converter. The NOR gate defines operation of the switch/relay  $S_R$ .

The MPPT is an important part of the closed-loop control system in any PV microconverter. The capability of the FT-MIC to track the maximum power point under any conditions is of superior importance. The FT-MIC prototype was configured to first operate in the normal and then in the post-fault conditions. During the test, the SAS was emulating the I-V profile from Fig. 16. It could be observed from Fig. 19

FIGURE 18. Simplified sketch of the closed-loop control system.

FIGURE 19. Experimental MPPT routine performed by FT-MIC in the normal (a) and post-fault (b) conditions with the I-V profile from Fig. 16.

that the MPPT routine performed in the normal conditions (Fig. 19a) and in the post-fault conditions (Fig. 19b) are

FIGURE 20. Case study daily profile of solar irradiance and estimated PV cell temperature.

similar in dynamic performance. There are two main differences observed in the post-fault conditions comparing to the normal conditions: the transformer voltage becomes asymmetrical; the input voltage ripple is increased as the converter input current ripple has two times lower equivalent frequency. Other than those changes, the converter can perform MPPT in roughly 120 ms.

### C. DAILY PV ENERGY YIELD TEST

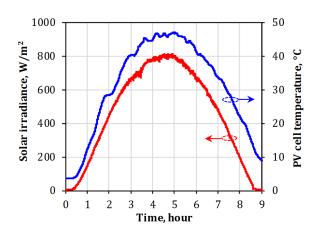

This section describes how the proposed FT-MIC can handle the long-term PV energy generation test. The daily profile of the solar irradiance and the corresponding PV cell temperature used in this subsection is presented in Fig. 20. The considered conditions correspond to a sunny summer day in the Northern European mild climate zone. The PV cell

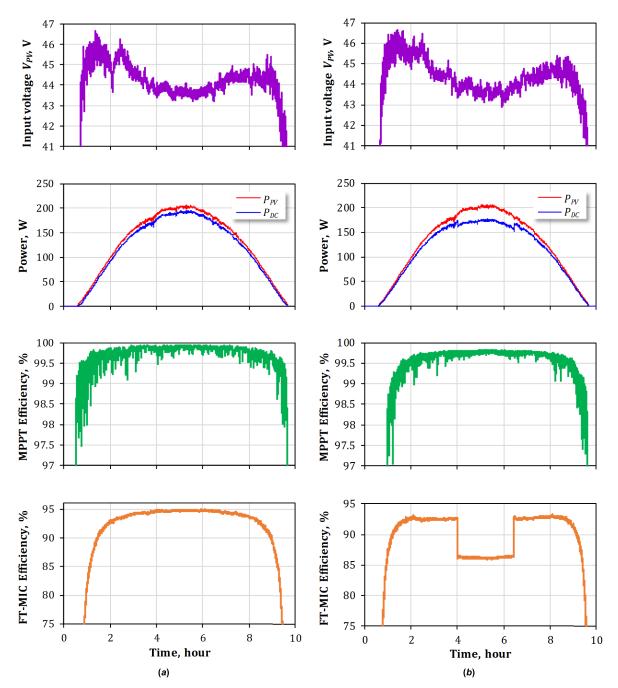

FIGURE 21. Experimental results of the daily PV energy generation test performed by the FT-MIC prototype in the normal (a) and post-fault (b) operating conditions.

temperature experiences the temperature swing of over  $40\,^{\circ}$ C, which results from roughly  $20\,^{\circ}$ C daily ambient temperature swing, and PV module heating by the sunlight. The peak solar irradiance of  $800\,\text{W/m}^2$  is typical for the given geographical region.

The daily mission profile from Fig. 20 was emulated for the case study 96-cell PV module by the SAS. A custom-made LabVIEW application was used to implement the SAS control with the resolution of one second for the mission profile and measurements. Additionally, the measured data

were logged by the precision power analyzer WT1800. The experimental results for the normal and post-fault operating conditions are presented in Fig. 21*a* and 21*b*, respectively.

Fig. 21 presents (from top to bottom): input voltage of the FT-MIC prototype, input  $(P_{PV})$  and output  $(P_{DC})$  powers of the prototype, MPPT efficiency (ratio between intravenous values of the available and extracted PV power), and the prototype electric power conversion efficiency. In both conditions, the prototype could extract roughly 1190 Wh of the energy from the SAS. The average MPPT efficiency in both

cases was over 99 %. Hence, the main difference in results is associated with the power stage efficiency.

In the normal operating conditions, the prototype was approaching maximum efficiency of 95 %, as shown in Fig. 21a. As predicted, the peak efficiency was observed at the maximum input power, i.e., the highest solar irradiance of  $800 \text{ W/m}^2$ . The daily energy yield of 1116 Wh was measured at the converter output, which corresponds to 93.8 % of 1190 Wh, the energy extracted from the SAS.

In the post-fault operating conditions, the prototype shows good MPPT performance, as shown in Fig. 21b. As the maximum power point voltage drops when the PV cell temperature is rising, the converter automatically changes its operating mode from the buck mode to the boost mode between the fourth and seventh hours. In the boost mode, the converter power loss is increased by roughly two times, which is evident from the drops in both the experimental efficiency curve and the input and output power curves. In the given case study conditions, the output energy yield drops down to 1070 Wh, which corresponds to 89.9 % of the energy received at the prototype input terminals. Therefore, the prototype would be losing an extra 3.9% of the input energy if it was recovered after a semiconductor switch fault. This is an acceptable performance deterioration, considering that the FT-MIC can continue operation after a semiconductor switch fault.

### VII. CONCLUSION

This paper proposes the adoption of the high regulation flexibility of the qZS series resonant DC-DC converter for fault-tolerant application. It was proposed and verified that the converter can sustain its operation after a fault in one of the front-end inverter transistors, and several cases of double faults. Moreover, it remains capable of operating in the wide input voltage range from 15 V to 65 V due to buck-boost voltage regulation functionality, which makes it compatible with most of the typical PV modules available on the market. The low-cost implementation of a fault detection using simple voltage dividers and ADCs embedded in a microcontroller was proposed and experimentally validated. The quasi-Z-source network limits the fault currents in healthy switches and allows for withstanding the maximum delay between a fault and converter shut down of less than a switching period. Besides, a simple fault identification based on the sequential application of switching vectors to the input-side bridge was proposed. As a result, a low-cost fault-tolerant PV microconverter was implemented.

Experimental verification of the microconverter performance showed that it has higher efficiency at the full load in the normal operation, and at a light load in the post-fault operation conditions. The peak efficiency of over 95 % was achieved in both cases. It was also demonstrated that the dynamic and static MPPT performances of the microconverter does not deteriorate after a fault and converter can track a maximum power point with over 99% accuracy. The daily PV energy production was also emulated for the case of 96-cell Si-based PV module in both normal and post-fault

operating conditions. The microconverter was able to deliver 93.8 % of the harvested PV energy to the output in the normal operation, and 89.8 % in the post-fault operation. Drop in the energy production is a result of considerable efficiency step when the microconverter switches between the buck and the boost modes. Nevertheless, it is an acceptable tradeoff considering possible lifetime extension.

The proposed idea of fault-tolerant PV microconverter could help to realize the deferred maintenance approach resulting in reduced downtimes and faster return of investments of the residential PV power systems. The future research will focus on damage accumulation rate in the microconverter components in the normal and post-fault operation and their comparison and optimization via hardware design tailoring.

### **ACKNOWLEDGMENT**

The statements made herein are solely the responsibility of the authors.

## **REFERENCES**

- S. Kouro, J. I. Leon, D. Vinnikov, and L. G. Franquelo, "Grid-connected photovoltaic systems: An overview of recent research and emerging PV converter technology," *IEEE Ind. Electron. Mag.*, vol. 9, no. 1, pp. 47–61, Mar. 2015.

- [2] N. Femia, G. Lisi, G. Petrone, G. Spagnuolo, and M. Vitelli, "Distributed maximum power point tracking of photovoltaic arrays: Novel approach and system analysis," *IEEE Trans. Ind. Electron.*, vol. 55, no. 7, pp. 2610–2621, Jul. 2008.

- [3] G. Spagnuolo, S. Kouro, and D. Vinnikov, "Photovoltaic module and submodule level power electronics and control," *IEEE Trans. Ind. Electron.*, vol. 66, no. 5, pp. 3856–3859, May 2019.

- [4] Bimal K. Bose, Power Electronics in Renewable Energy Systems and Smart Grid: Technology and Applications. Hoboken, NJ, USA: Wiley, 2019.

- [5] A. Q. Huang, M. L. Crow, G. T. Heydt, J. P. Zheng, and S. J. Dale, "The future renewable electric energy delivery and management (FREEDM) system: The energy Internet," *Proc. IEEE*, vol. 99, no. 1, pp. 133–148, Jan 2011

- [6] Z. Liang, R. Guo, J. Li, and A. Q. Huang, "A high-efficiency PV module-integrated DC/DC converter for PV energy harvest in FREEDM systems," *IEEE Trans. Power Electron.*, vol. 26, no. 3, pp. 897–909, Mar. 2011.

- [7] T. LaBella, W. Yu, J.-S. Lai, M. Senesky, and D. Anderson, "A bidirectional-switch-based wide-input range high-efficiency isolated resonant converter for photovoltaic applications," *IEEE Trans. Power Electron.*, vol. 29, no. 7, pp. 3473–3484, Jul. 2014.

- [8] D. Vinnikov, A. Chub, E. Liivik, and I. Roasto, "High-performance quasi-Z-source series resonant DC-DC converter for photovoltaic module-level power electronics applications," *IEEE Trans. Power Electron.*, vol. 32, no. 5, pp. 3634–3650, May 2017.

- [9] A. Chub, D. Vinnikov, R. Kosenko, and E. Liivik, "Wide input voltage range photovoltaic microconverter with reconfigurable buck-boost switching stage," *IEEE Trans. Ind. Electron.*, vol. 64, no. 7, pp. 5974–5983, Jul. 2017.

- [10] D. Vinnikov, A. Chub, E. Liivik, R. Kosenko, and O. Korkh, "Solar Optiverter—A novel hybrid approach to the photovoltaic module level power electronics," *IEEE Trans. Ind. Electron.*, vol. 66, no. 5, pp. 3869–3880, May 2019.

- [11] Y. Shen, A. Chub, H. Wang, D. Vinnikov, E. Liivik, and F. Blaabjerg, "Wear-out failure analysis of an impedance-source PV microinverter based on system-level electrothermal modeling," *IEEE Trans. Ind. Electron.*, vol. 66, no. 5, pp. 3914–3927, May 2019.

- [12] E. Liivik, A. Chub, A. Sangwongwanich, Y. Shen, D. Vinnikov, and F. Blaabjerg, "Wear-out failure analysis of solar optiverter operating with 60- and 72-cell Si crystalline PV modules," in *Proc. 44th Annu. Conf. IEEE Ind. Electron. Soc.*, Washington, DC, USA, Oct. 2018, pp. 6134–6140.

- [13] D. Vinnikov, R. Kosenko, A. Chub, and E. Liivik, "Shade-tolerant photovoltaic microinverter with time adaptive seamless P-V curve sweep MPPT," in *Proc. 19th Eur. Conf. Power Electron. Appl.*, Riga, Italy, Sep. 2017, pp. 1–8.

- [14] E. Liivik, D. Vinnikov, A. Chub, Y. Shen, H. Wang, and F. Blaabjerg, "Reliability study of input side capacitors in impedance-source PV micro-converters," in *Proc. 45th Annu. Conf. IEEE Ind. Electron. Soc.*, Lisbon, Portugal, Oct. 2019, pp. 5026–5032.

- [15] A. Chub, O. Korkh, R. Kosenko, and D. Vinnikov, "Novel approach immune to partial shading for photovoltaic energy harvesting from building integrated PV (BIPV) solar roofs," in *Proc. 20th Eur. Conf. Power Electron. Appl.*, Riga, Italy, 2018, pp. 1–10.

- [16] D. Vinnikov, A. Chub, O. Korkh, and M. Malinowski, "Fault-tolerant bidirectional series resonant DC-DC converter with minimum number of components," in *Proc. IEEE Energy Convers. Congr. Expo. (ECCE)*, Baltimore, MD, USA, Sep. 2019, pp. 1359–1363.

- [17] L. F. Costa, G. Buticchi, and M. Liserre, "A family of series-resonant DC-DC converter with fault-tolerance capability," *IEEE Trans. Ind. Appl.*, vol. 54, no. 1, pp. 335–344, Jan. 2018.

- [18] Y. Shen, H. Wang, Z. Qin, F. Blaabjerg, and A. A. Durra, "A reconfigurable series resonant DC-DC converter for wide-input and wide-output voltages," in *Proc. IEEE Appl. Power Electron. Conf. Expo. (APEC)*, Tampa, FL, USA, Mar. 2017, pp. 343–349.

- [19] D. Vinnikov, A. Chub, O. Korkh, and S. Kouro, "Wide input voltage range high step-up DC-DC converter with fault-tolerant operation capability," in *Proc. IEEE Int. Conf. Ind. Technol. (ICIT)*, Melbourne, VIC, Australia, Feb. 2019, pp. 1099–1104.

- [20] D. Vinnikov, A. Chub, O. Korkh, A. Blinov, and E. Liivik, "Hybrid DC-DC converters with topology morphing control and post-fault operation capability," in *Lecture Notes in Electrical Engineerin*, vol. 1. Cham, Switzerland: Springer, 2020, pp. 433–445, doi: 10.1007/978-3-030-37161-6.33

- [21] A. Chub, D. Vinnikov, F. Blaabjerg, and F. Z. Peng, "A review of galvanically isolated impedance-source DC–DC converters," *IEEE Trans. Power Electron.*, vol. 31, no. 4, pp. 2808–2828, Apr. 2016.

- [22] D. Vinnikov, A. Chub, R. Kosenko, J. Zakis, and E. Liivik, "Comparison of performance of phase-shift and asymmetrical pulsewidth modulation techniques for the novel galvanically isolated Buck–Boost DC–DC converter for photovoltaic applications," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 5, no. 2, pp. 624–637, Jun. 2017.

- [23] D. Vinnikov, A. Chub, and E. Liivik, "Single-switch galvanically isolated step-up DC-DC converter for residential photovoltaic applications," in *Proc. 42nd Annu. Conf. IEEE Ind. Electron. Soc.*, Florence, Italy, Oct. 2016, pp. 6578–6582.

- [24] D. Vinnikov, A. Chub, and L. Liivik, "Asymmetrical quasi-Z-source half-bridge DC-DC converters," in *Proc. 9th Int. Conf. Compat. Power Electron. (CPE)*, Costa da Caparica, Italy, Jun. 2015, pp. 369–372.

- [25] Z. Chen, Q. Zhou, J. Xu, and X. Zhou, "Asymmetrical pulse-width-modulated full-bridge secondary dual resonance DC-DC converter," J. Power Electron., vol. 14, no. 6, pp. 11224–12328, 2014.

- [26] W.-J. Cha, J.-M. Kwon, and B.-H. Kwon, "Highly efficient asymmetrical PWM full-bridge converter for renewable energy sources," *IEEE Trans. Ind. Electron.*, vol. 63, no. 5, pp. 2945–2953, May 2016, doi: 10.1109/TIE.2015.2510500.

- [27] A. D. Pathak, MOSFET/IGBT Drivers Theory and Applications. [Online]. Available: http://www.ixys.com/documents/appnotes/ixan0010.pdf

- [28] H. Mhiesan, J. Umuhozs, K. Mordi, R. McCann, J. C. Balda, C. Farnell, and A. Mantooth, "A method for open-circuit faults detecting, identifying, and isolating in cascaded H-bridge multilevel inverters," in *Proc. 9th IEEE Int. Symp. Power Electron. Distrib. Gener. Syst. (PEDG)*, Charlotte, NC, USA, Jun. 2018, pp. 1–5.

- [29] S. Nie, X. Pei, Y. Chen, and Y. Kang, "Fault diagnosis of PWM DC–DC converters based on magnetic component voltages equation," *IEEE Trans. Power Electron.*, vol. 29, no. 9, pp. 4978–4988, Sep. 2014.

- [30] H. Givi, E. Farjah, and T. Ghanbari, "Switch and diode fault diagnosis in nonisolated DC–DC converters using diode voltage signature," *IEEE Trans. Ind. Electron.*, vol. 65, no. 2, pp. 1606–1615, Feb. 2018.

- [31] H. Givi, E. Farjah, and T. Ghanbari, "Switch fault diagnosis and capacitor lifetime monitoring technique for DC–DC converters using a single sensor," *IET Sci., Meas. Technol.*, vol. 10, no. 5, pp. 513–527, Aug. 2016.

- [32] E. Farjah, H. Givi, and T. Ghanbari, "Application of an efficient rogowski coil sensor for switch fault diagnosis and capacitor ESR monitoring in nonisolated single-switch DC-DC converters," *IEEE Trans. Power Electron.*, vol. 32, no. 2, pp. 1442–1456, Feb. 2017.

- [33] E. Jamshidpour, M. Shahbazi, P. Poure, E. Gholipour, and S. Saadate, "Fault tolerant operation of single-ended non-isolated DC-DC converters under open and short-circuit switch faults," in *Proc. 15th Eur. Conf. Power Electron. Appl. (EPE)*, Lille, France, Sep. 2013, pp. 1–7.

- [34] A. A. Stonier and B. Lehman, "An intelligent-based fault-tolerant system for solar-fed cascaded multilevel inverters," *IEEE Trans. Energy Convers.*, vol. 33, no. 3, pp. 1047–1057, Sep. 2018.

- [35] H. Renaudineau, J.-P. Martin, B. Nahid-Mobarakeh, and S. Pierfederici, "DC-DC converters dynamic modeling with state observer-based parameter estimation," *IEEE Trans. Power Electron.*, vol. 30, no. 6, pp. 3356–3363, Jun. 2015.

- [36] S. Shao, P. W. Wheeler, J. C. Clare, and A. J. Watson, "Fault detection for modular multilevel converters based on sliding mode observer," *IEEE Trans. Power Electron.*, vol. 28, no. 11, pp. 4867–4872, Nov. 2013.

- [37] [Online]. Available: http://www.solarinnova.net/en/products/photovoltaic/modules/standard/polycrystalline/125mm/96

**DMITRI VINNIKOV** (Senior Member, IEEE) received the Dipl.Eng., M.Sc., and Dr.Sc.techn. degrees in electrical engineering from the Tallinn University of Technology, Tallinn, Estonia, in 1999, 2001, and 2005, respectively. He is currently the Research Professor and the Head of the Power Electronics Group, Department of Electrical Power Engineering and Mechatronics, Tallinn University of Technology. He is also the Head of Research and Development and the Co-Founder

of Ubik Solutions LLC—Estonian start-up company dedicated to innovative and smart power electronics for renewable energy systems. Moreover, he is one of the founders and leading researchers of ZEBE—Estonian Centre of Excellence for zero energy and resource efficient smart buildings and districts. He has authored or coauthored two books, five monographs, and one book chapter as well as more than 200 published articles on power converter design and development and is the holder of numerous patents and utility models in this field. His research interests include applied design of power electronic converters and control systems, renewable energy conversion systems (photovoltaic and wind), impedance-source power converters, and implementation of wide bandgap power semiconductors. He is the Chair of the IES/PELS Joint Societies Chapter of the IEEE Estonia Section.

**ANDRII CHUB** (Senior Member, IEEE) received the B.Sc. and M.Sc. degrees from Chernihiv State Technological University, Chernihiv, Ukraine, in 2008 and 2009, respectively, and the Ph.D. degree in electrical engineering from the Tallinn University of Technology, Estonia, in 2016.

He was a Visiting Research Fellow with Kiel University, in 2017, and a Postdoctoral Researcher with Federico Santa Maria Technical University, from 2018 to 2019. He is currently a Senior

Researcher with the Power Electronics Group, TalTech, Estonia. He has coauthored over 100 articles and book chapters on power electronics and applications. In addition, he holds several patents and utility models. His research interests include dc-dc converters, dc microgrids, renewable energy conversion systems for energy-efficient residential buildings, fault tolerance, and reliability in power electronic systems. He is an Associate Editor of the IEEE JOURNAL OF EMERGING AND SELECTED TOPICS IN INDUSTRIAL ELECTRONICS.

**DENYS ZINCHENKO** (Graduate Student Member, IEEE) received the B.Sc. and M.Sc. degrees in electrical engineering from the National Technical University of Ukraine Igor Sikorsky Kyiv Polytechnic Institute, Ukraine, in 2015 and 2017, respectively.

His experiences include three years of practical engineering work as an Embedded Developer. In 2019, he joined the Department of Electrical Power Engineering and Mechatronics, Tallinn

University of Technology, as a Junior Researcher in the Power Electronics Group. He is the author or coauthor of six scientific articles. His research interests include design, simulation of power electronic converters, and control systems, power quality, and modeling and simulations of renewable energy sources.

MARIUSZ MALINOWSKI (Fellow, IEEE) received the Ph.D. and D.Sc. degrees in electrical engineering from the Institute of Control and Industrial Electronics, Warsaw University of Technology (WUT), Warsaw, Poland, in 2001 and 2012, respectively. He was a Visiting Scholar with Aalborg University, Aalborg, Denmark; the University of Nevada, Reno, NV, USA; the Technical University of Berlin, Berlin, Germany; and ETH Zurich, Zurich, Switzerland. He is currently with

the Institute of Control and Industrial Electronics, WUT. He has coauthored over 150 technical articles and six books. His current research interests include the control and the modulation of grid-side converters, multilevel converters, smart grids, and power-generation systems based on renewable energies. He was a recipient of the Siemens Prize, in 2002 and 2007; the WUT President Scientific Prize, in 2015; the Polish Minister of Science and the Higher Education Awards, in 2003 and 2008; the Prime Minister of Poland Award for Habilitation, in 2013; and the IEEE Industrial Electronics Society (IES) David Irwin Early Career Award, in 2011, and the Bimal Bose Energy Systems Award, in 2015. His industry application received several awards and medals.

**SERTAC BAYHAN** (Senior Member, IEEE) graduated from Gazi University, Ankara, Turkey, as the Valedictorian. He received the M.S. and Ph.D. degrees in electrical engineering from Gazi University, in 2008 and 2012, respectively.

In 2008, he joined Department of the Electronics and Automation, Gazi University, as a Lecturer, where he was promoted to an Associate Professor, in 2017. From 2014 to 2018, he worked at Texas A&M University at Qatar as an Associate

Research Scientist. He is currently working with the Qatar Environment and Energy Research Institute (QEERI) as a Senior Scientist. He is also a Faculty Member with the rank of Associate Professor in the Sustainable Division, College of Science and Engineering, Hamad Bin Khalifa University. He has acquired \$13M in research funding and published more than 150 articles in mostly prestigious IEEE journals and conferences. He is also the coauthor of two books and four book chapters. Because of the visibility of his research, he has been recently elected as the Chair of IES Power Electronics Technical Committee. He was a recipient of many prestigious international awards, such as the Research Fellow Excellence Award in recognition of his research achievements and exceptional contributions to the Texas A&M University at Qatar, in 2018, the Best Paper Presentation Recognition at the 41st and 42nd Annual Conference of the IEEE Industrial Electronics Society, in 2015 and 2016, the Research Excellence Travel Awards (Texas A&M University at Qatar), in 2014 and 2015, and the Researcher Support Awards from the Scientific and Technological Research Council of Turkey (TUBITAK). He also serves as an Associate Editor for the IEEE Transactions on Industrial Electronics, the IEEE Journal of Emerging and SELECTED TOPICS IN INDUSTRIAL ELECTRONICS, and IEEE Industrial Electronics Technology News, and a Guest Editor for the IEEE Transactions on Industrial Informatics.

VADIM SIDOROV (Student Member, IEEE) was born in Kazakhstan, in 1995. He received the B.Sc. and M.Sc. degrees in power electronics from Novosibirsk State Technical University, Novosibirsk, Russia, in 2017 and 2019, respectively. He is currently pursuing the Ph.D. degree with the Power Electronics Group, Tallinn University of Technology, Tallinn, Estonia. His research interests include the power electronics systems, dc-dc converters, series resonant converters, dc-ac inverters,

and electric drive systems.