Received July 12, 2020, accepted July 24, 2020, date of publication August 3, 2020, date of current version September 4, 2020.

Digital Object Identifier 10.1109/ACCESS.2020.3013669

# IEEE 1588 for Clock Synchronization in Industrial IoT and Related Applications: A Review on Contributing Technologies, Protocols and Enhancement Methodologies

ZEBA IDREES<sup>®</sup>, JOSE GRANADOS, YANG SUN, SHAHID LATIF<sup>®</sup>, (Graduate Student Member, IEEE), LI GONG<sup>®</sup>, (Graduate Student Member, IEEE), ZHUO ZOU, (Senior Member, IEEE), AND LIRONG ZHENG, (Senior Member, IEEE)

School of Information Science and Engineering, Fudan University, Shanghai 200433, China

Corresponding authors: Zhuo Zou (zhuo@fudan.edu.cn) and Lirong Zheng (Irzheng@fudan.edu.cn)

This work was supported by NSFC grants No. 61876039 and No. 62011530132, Shanghai Municipal Science and Technology, Major Project (No. 2018SHZDZX01) and ZJ Lab, and the Shanghai Platform for Neuromorphic and AI Chip (NeuHeilium) China.

**ABSTRACT** Precise time synchronization becomes a vital constituent due to the rigorous needs of several time-sensitive applications. The clock synchronization protocol is one of the fundamental factors that can define the quality of communication. Our study starts with a brief discussion on the application domain of precise time synchronization and comes with an in-depth study of the synchronization with the main focus on the IEEE 1588 Precision Time Protocol (PTP). We have compared the well-known synchronization techniques and conclude that the PTP is the most appropriate answer to robust clock synchronization though challenges are there that requires thoughtful efforts and modification in the current version. The working mechanism and main components of the PTP network are discussed. We have established a testbench using commercially available devices and development boards to evaluate the PTP performance under different configurations. Major sources of synchronization error and other aspects contributing to precision are examined. This paper discussed numerous approaches that could enhance the performance of the PTP protocol. Structures for PTP based wireless clock synchronization required by advanced applications has also been discussed. In the end, paper focuses on the main industrial application areas in which PTP plays an important role, including WLAN, optical data centers, Smart grid, IEC 61850, etc. We conclude the paper by identifying the future trends and research directions for PTP based clock synchronization.

**INDEX TERMS** Clock synchronization, NTP, IEEE 1588 PTP, IoT, WLAN, optical data centers, smart grid, IEC 61850.

# I. INTRODUCTION

Time-dependent applications have become essential as technologies like industrial automation, robotics, and Internet of Things (IoT) have grown by many folds [1]. The rise of cloud computing and high-speed networks requires highly precise time synchronization [2]. Cheap oscillators or quartz crystals properties vary with power, aging, and heat. Therefore, two similar crystals are not guaranteed to oscillate at the

The associate editor coordinating the review of this manuscript and approving it for publication was Rashid Mehmood.

identical time/frequency. These limitations put oscillators to run slightly different than the others. Replacement of computer's built-in cheap clocks with an expensive one is not practicable for large infrastructure. Consequently, a vigorous and effective way to synchronize clocks of a disseminated structure is essential [3]. Network Time Protocol (NTP) was the most diffused solution for clock synchronization. Lately, a more precise solution, known as PTP, has been proven to be more beneficial for clock synchronization [4]. Although the PTP communication algorithm is analogous to NTP's, PTP is different in its accurate hardware-assisted time record

of the event named as time stamping [5]. PTP is one of the conceivable solutions for highly precise clock synchronization. However, there are still certain challenges that must be considered.

This paper conducted a comprehensive study and analysis of IEEE 1588 PTP based synchronization solutions for IoT and industrial applications. We have illustrated several aspects that might enhance the performance of PTP. Despite of the development that is made with these practices, highly precise clock synchronization is still an open issue, especially in wireless network communication. Other contents of the paper are ordered as follows. Section II provides a detailed background of the synchronization and its application in different emerging areas. Clock synchronization standards and comparison of the most popular synchronization techniques are also presented in this section. Section III discusses in detail the PTP algorithm, its versions, and implementation methods. Source of time error and enhancement approaches along with commercially available solutions are summarized in Section IV. Wireless PTP that is an extension to PTP is discussed in Section V. A thorough summary of the recent literature discussing software and hardware tools for PTP evaluations and different deployment techniques are listed in Section VI. Section VII presents the synchronization requirements and the role of the PTP in the area of IoT and related industrial applications including smart grid, optical data centers, and PTP based synchronization for WLAN with a specific attention on the infrastructure mode which is utmost applicable to industrial scenarios. Paper is concluded with challenges and future needs in Section VIII.

#### **II. BACKGROUND**

Coordinated Universal Time (UTC) is the mutual base for the worldwide public time. Two main modules are used to define it.

- The International Atomic Time: the time gauge that integrates the output of greatly precise atomic clocks globally.

- 2. Universal Time (UT1) astronomic time is synchronized with UT1 to keep the definite length of a day [6].

UTC high precision is delivered by atomic clocks. Though, such reference clocks are very expensive and are not feasible for common customers as they may not require high accuracy. However, even a simple sensor may own time reference [7], normally they cannot offer essential time constancy in the long term due to time drift. Consequently, it is desirable to synchronize such clocks with an accurate time reference. Following subsections discuss the synchronization types, applications, and the existing standards.

# A. SYNCHRONIZATION TYPES

In broad-spectrum, synchronization can be described in numerous ways. Clock synchronization could refer to time, frequency, or phase. It can be defined as frequency synchronization if dissimilar clocks drive to the identical state in the equivalent time interludes such as pulse per second (PPS) output. In another way, a system might utilize signals of unlike frequencies with an organized phase [7]. If a system requires clear information of time then it is called clock synchronization [6]. There are two main distributed time synchronization structures based on the continuity/discontinuity of the time. In Continuous-Time (CT) methodology transmission start/end times are interpreted constantly for the network. A highly accurate clock is essential to provide time info steadily. While Discrete-Time (DT) methods, described by the time incoherence, it defines the time slots of a fixed interval [5]. CT methods only rely on a precise clock synchronization method that makes CT approach most appropriate for high-speed networking requirements [8]–[10].

#### **B. APPLICATION AREA**

Timing demands on networking and control systems have become progressively challenging, particularly for real-time applications like nuclear fusion control, mobile communication, substation automation, and, modern manufacturing plant. The real-time market data require latency of one millisecond to pass by the cables, routers and, switches with the timestamp. Smart grid applications require time harmonization to permit many parts of the grid to attach or detach without disturbance. In IoT case, for distributed networks sensor data want to be gathered in real-time. In a softwaredefined network, highly accurate regulator clocks aid to attain accurate network apprises with a small packet loss rate [11]. Clock synchronization is one of the critical features that might control the quality of the communication. Synchronization is an essential part of the various application areas as discussed below.

#### 1) SMART GRIDS

The smart grid is an extension of the legacy power grid supporting the smart bidirectional flow of energy and data to enhance the grid efficiency and reliability. Currently, power grids have several measurement and control data that requires accuracy from 100ms to  $1\mu$ s or more [12]. The power grids have distributed and complex system with following processes that needs synchronization [13]:

- Event reconstruction.

- Synchro phasor computing.

- System deviation control for time and frequency.

- Time tagging in estimation and error discovery systems.

# 2) TELECOMMUNICATIONS

lots of possessions in advance and forthcoming wireless networks desire accurate synchronization, counting but not restricted to [13], [14].

- Time and frequency references.

- Multicast/Broadcast Single Frequency networks, Cooperative Multipoint, etc.

- Assurance of QoS over transport networks.

- Other zones contain automation of distributed systems.

#### 3) IOT AND INDUSTRIAL APPLICATIONS

The info gathered from diverse types of sensors has an important role for manufacturing and business operations in the industrial internet. Alignment in time of the data coming from different geographical areas is very important. Algorithms, employed for the investigation of the big data, must have the precise sequence of the events [1], [15]. An incongruity in computing from a specific cluster of sensors could end in the wrong alarms and judgments, needless expenditures, or even damage the equipment [14].

#### C. IMPACT OF SYNCHRONIZATION ERROR

Precise clock synchronization is mandatory for coordinated real-time chores. Desynchronized clocks in time-sensitive applications can degrade the system performance and damage the infrastructure [16]. Let us discuss the case of a smart grid that installed smart meter and other intelligent electronic devices (IEDs) at the substation, to monitor and control the instruments they need sub-millisecond clock synchronization accuracy. The absence of accurate synchronization will result in lose control and compromise the grid's safety. In the manufacturing industry if the robots working in a group on the same product lose the synchronization can result in clashes of their acts and upset the production pipeline.

Time synchronization is challenging in wireless sensor networks (WSNs) for distributed systems like structural health monitoring (SHM). Time shift causes error among the raw data from sensor nodes that affect the data integrity and can result in the incorrect mode shape identification of the structure under observation. In [17] authors illustrate the influence of time synchronization error (TSE) on the modal analysis and damage detection and concluded that TSE has a strong impression on the mode shape detection, damage localization, and damage discovery. [18] analyses the effect of clock synchronization loss on the synchro phasorsbases applications. Experimental evaluations demonstrate that a phase angle monitoring system expresses an erroneous power system state and operating time of an anti-islanding protection application also gets disturbed due to loss of time-synchronization signal input to PMUs.

The industrial networks use deterministic data transmission and reception with a predefined node location [19]. Poor synchronization among the nodes affects deterministic data exchange and destroy the whole control system. Time desynchronization in an Industrial Internet of Things (IIoT) network can affect the system performance or may result in safety compromises. clock synchronization is necessary for coordinated real-time operation, in IIoT where connectivity is the key concern hence secure clock synchronization is an imperative research issue.

# D. TIME SYNCHRONIZATION STANDARDS AND SOLUTIONS

To fulfill the synchronization needs in the modern networks many international standards have been established.

The literature highlights mainly two classes of synchronization schemes: one is hardwired and the other is protocolbased. Hard-wired practices do not need to interchange the info over the network, and are extensively accepted as they fulfill even the severe requirements [20]. However, the lack of flexibility adversely affects the overall operational costs of the system [21].

- 1) GPS-BASED TIME SYNCHRONIZATION Despite of the high accuracy it has numerous disadvantages as it entails that all the participating nodes are furnished with a GPS receiver. Outdoor GPS antennas are obligatory in many scenarios; these outdoor antennas are susceptible to vandalism and cannot be installed in underground substations [20], [22].

- 2) 1PPS OR PULSE PER MINUTE (PPM) sources are capable to deliver the utmost precision of the frequency synchronization, no additional info is communicated.

- 3) NETWORK SYNCHRONIZATION PROTOCOLS NTP is the most popular protocol and is realized by numerous communication stacks. It goes through many versions since 1985. NTP version 3 was stated in the Internet Engineering Task Force (IETF) (RFC)-1305 and the newest version NTPv4 was suggested in RFC-5905 [6], [23]. Classically, NTP synchronization accuracy is highly related to the performance of the underlying network [20], [24], [25].

- 4) SIMPLE NETWORK TIME PROTOCOL (SNTP) is a slightly less complex implementation of NTP that does not realize a few of the difficult time-tracking procedures [26]. SNTP is appropriate for embedded devices as it needs few resources as compare to the NTP at the cost of lower synchronization accuracy [27].

- 5) PTP recognized as IEEE 1588, it is another standard for precise time synchronization. This protocol provides hardware-level time precision by a customary network links, using devoted timing hardware to every port in an Ethernet environment [28]. This protocol allows attaining synchronization in the range of nanoseconds provided that all the network components like switches and routers are PTP enabled [29].

- 6) WHITE RABBIT (WR) White Rabbit (WR) protocol, also known as PTP version 3 was initiated and used at CERN (European Organization for Nuclear Research) to align the clocks of their accelerator complex. WR network achieves sub nanoseconds timing accuracy using existing standards [30].

- 7) THE INTER RANGE INSTRUMENTATION GROUP (IRIG): This approach uses codes to competently route the timing system to the consumer. Specifically, atomic frequency and GPS receivers are usually armed with an IRIG outcome [31]. The IEEE 1344 addition to IRIG-B Time codes succeeded by IEEE C37.118 describes synchronized phasor capacity for power systems. It describes the usage of PTP in power systems. ITU-T recommendation G.8265 Designates the placement of PTP standard in telecom networks for backup the essential timing precision and transmission of frequency [32], [33].

| Synchronization<br>Protocol | Precision      | Overhead | Scalability | Hardware Requirements        | Spatial Extent | Cost     | Hierarchy<br>Model        |

|-----------------------------|----------------|----------|-------------|------------------------------|----------------|----------|---------------------------|

| GPS                         | n- second      | No       | Poor        | GPS receivers, cables        | Wide Area      | High     | Client/Server             |

| NTP                         | $\mu$ second   | Yes      | Good        | No                           | Wide Area      | Low      | Distributed Client/Server |

| PTP                         | Sub-µ second   | Yes      | Good        | Optional-PTP enabled devices | Few Sub-nets   | Moderate | Master/Slave              |

| WR                          | Sub-nanosecond | Yes      | Good        | WR switches                  | Wide Area      | Moderate | Master/Slave              |

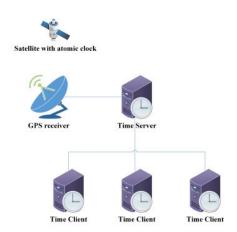

FIGURE 1. GPS-based time synchronization.

8) TIME-SENSITIVE NETWORKING (TSN) TSN working group developed a group of standards IEEE 802.1 for data broadcast over Ethernet. IEEE 802.1AS is defined to carry accurate timing and perform the synchronization in bridged LANs. G.8261, G.8262, and G.8264 make the synchronous Ethernet (SyncE) group of standards. It postulates the architecture, clocks, and messaging over the Ethernet physical layer [34], Uses includes cellular networks and access technologies. Though, the majority the time synchronization designs consider the centralized time circulation.

# E. COMPARISON OF THE WELL-KNOWN SYNCHRONIZATION MECHANISMS

In this section, most popular time synchronization technologies: GPS time synchronization, NTP, PTP, and WR are compared in terms of their architecture and other relevant properties. Table 1 list and compare these protocols in term of synchronization precision, scalability, hardware requirements, cost, and other main features.

**GPS**-based time synchronization is the finest way to attain nanosecond accuracy. A GPS satellite contains atomic clock information and GPS receivers obtain precise time information [35]. This info is dispersed to all the associated nodes as shown in Figure 1. Furthermore, inside the data centers, GPS signals reception is difficult which makes it an unattractive approach.

**NTP** was established for packet-switched networks targeting millisecond synchronization accuracy. Time messages were exchanged using the User Datagram Protocol (UDP).

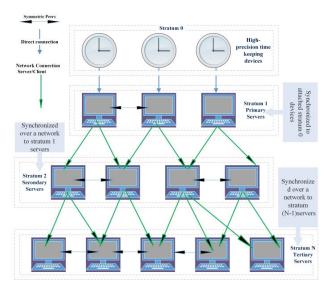

FIGURE 2. Hierarchical architecture of NTP.

A hierarchical architecture is shown in Figure 2 where the layer 1 time provider is synchronized to an atomic clock and passes down the timing data to the next level [5]. The distribution of the time information to multiple layers causes' loss of accuracy. Furthermore, each layer adds additional delay which continues to aggregates till the last layer. Consequently, NTP is not well suited for current delay-sensitive data traffic.

PTP is realized on the similar requirements that inspired NTP, but they mainly diverge in their implementation mechanism. Many factors make PTP more accurate than NTP. The first of them is that PTP has hardware-assisted time stamping which reduces the distance to physical receive/transmit ports of the reference clock. Another aspect is that PTP has many types of clock to support its synchronization accuracy these clocks include boundary clock, and transparent clock. In PTP, a grandmaster synchronizes entire slave nodes and this function eliminates all the additional delays that are practiced due to redistribution in NTP. Also, PTP uses active synchronization to compensate network introduce delays as discussed in section III.

WR is a low latency, Ethernet-based time distribution method for disseminated sensing systems. WR synchronization scheme uses the existing standards to achieve sub-nanosecond accuracy, these include Ethernet (IEEE 802.3), SyncE, PTPv2 along with precise phase measurement

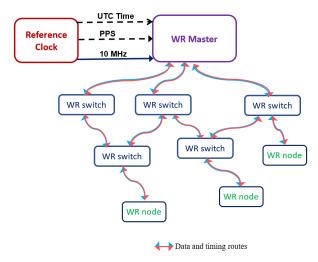

FIGURE 3. A white rabbit network.

technique [36], [37]. Just like PTP, WR is a complementary solution to GPS mainly when the sky is not accessible or ethernet based telecom infrastructure is pre-installed. This project is open source and achieves high accuracy up to sub-nanoseconds with a reliable and deterministic data delivery [38].

These properties make WR a favorable choice for smart grid application, though the accuracy is high for synchrophasor needs. The main bottleneck for WR protocol in the synchro phaser network is the absence of fiber optic cable in the electric grid, installing the fiber link in the feeder may not be a cost-efficient solution though the stability of WR over fiber optic is 950km [30]. A typical WR Network is consists of WR nodes and WR switches interconnected by fiber links. Figure 3 shows a WR network which is a standard Ethernet switched network foe data (no hierarchy) while for time synchronization it is a hierarchical model that goes from WR master down to other WR switches. In addition to standard ethernet switch properties, WR switch is also able to distribute the WR master clock using a precise phase measurement technique.

#### **III. PRECISION TIME PROTOCOL (PTP)**

PTP is based on the IEEE 1588 standard [39], a synchronization procedure for the dispersed packet-switched network, delivering accuracy around nanosecond. Data communication and synchronization are done using common cabling that results in easy deployment and permits the use of the standard network cabling [40], [41]. Cable distribution delays are not easy to measure simply by cable lengths. In a network data packet route changes dynamically and ultimately needs the correct estimation of network time delay for each packet. The additional delay could be added by other components present in the network like routers and switches and this added delay could be higher as compare to cabling delay. PTP presents a way that detect and compensate such time delays automatically [5].

TABLE 2. Functionalities of the basic PTP messages.

| Class                       | Message Type                | Purpose                                                                        |

|-----------------------------|-----------------------------|--------------------------------------------------------------------------------|

| Announce<br>Message         | Announce                    | Inform the neighbor nodes about their attributes and synchronization hierarchy |

| Synchronization<br>messages | Sync                        | Time engraved when transmitted by the master                                   |

|                             | Follow Up                   | Time engraved by master's Sync message                                         |

| Delay<br>Estimation         | Delay_Req                   | Time engraved when transmitted by the slave                                    |

| messages                    | Delay_Resp                  | Contains master Delay_Req timestamp                                            |

| Others                      | Management<br>and signaling | Query/update PTP data sets, event generation, fault generation/reporting etc.  |

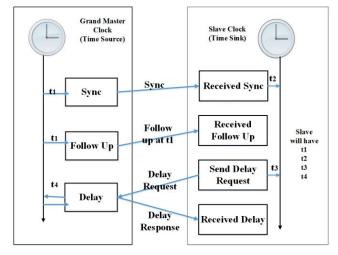

FIGURE 4. PTP message exchange algorithm.

#### A. PTP ALGORITHM

PTP uses a message exchange algorithm along with a precise time source to periodically synchronize and look over all the clocks present in the network. It starts with the Best Master Clock (BMC) algorithm to recognize the master (the highly precise clock present in the network) and slave clocks. Seeing the grandmaster clock as the source, slave clocks obtained the time data by swapping request-response with it [4], [33]. Functionalities of the basic messages exchanged among the grand master and slave clocks are listed in Table 2 for proper functionality there are few other messages for signaling and management [42]. Figure 4 depicts the PTP algorithm, and how the PTP messages are exchanged in a specific sequence [8].

After establishing the master/slave hierarchy, the master clock transmits a *Sync* message including its own timestamp, *tm*1 to all the slaves in the network. This timestamp can be sent by a single-step or a two-step process. The master clock reads the time information and instantly sends a *Sync* message to the slave clock. A supplementary *Follow\_Up* message is transmitted with the *Sync* message in two-step method which excludes the necessity to accurately read the timestamp and put to protocol message concurrently. On the reception of this *Sync* message, the slave clock records the time of arrival as *t*<sub>2</sub>. *Delay\_Req* is time stamped by the slave as *t*<sub>3</sub> and master receive them at *t*<sub>4</sub>. At last, the master clock transmits *Delay\_Resp* message to the slave clock time stamped at *t*<sub>4</sub>. Slave clock computes the offset and synchronizes with

master's time, the calculation of the clock offset and average path delay is described in equation 1 and 2 respectively.

Clock off set =

$$t_2 - t_1 - AVG$$

path delay (1)

AVG pathd elay =

$$\frac{[(t_2 - t_1) + (t_4 - t_3)]}{2}$$

(2)

# B. PTP EVOLUTION (PTP $_{V1}$ VS. PTP $_{V2}$ & PTP $_{v2.1}$ )

According to the clock type used in the PTP network, there are mainly two versions of the PTP, the first version defined in 2002 is known as  $PTP_{v1}$ . This version presented two types of clock, boundary clock (BC) and the ordinary clock (OC) [43]. The OC is the internal clock of each device in the network, while the BC is the clock that appointed to the devices between master and the slaves. Boundary clock enables the midway nodes between master and slave clocks also being synchronized. Before the slave node gets sync to the master, synchronization will be done at every hop among the master and the slave [28]. The modified version of PTP is called  $PTP_{v2}$  (revised in 2008) that offers another type of the clock in addition to the existing clocks. This clock is named as the transparent clock (TC) [44].

TC is one of the numerous enhanced features from version [4] and can resolve the queuing delay issue. Transparent clock passes the PTP messages with an additional feature of measuring their residence time in each intermediate node. The residence time is the duration from the reception of the message at the node to the time it leaves the node [33], [41]. A modification field is introduced that includes a 48-bit nanosecond share and a 16-bit sub-nanosecond portion, this correction field removes a significant percentage of calculation faults. A short Sync message interval is permissible for varied update rates as compare to 1s Sync messages in PTPv1. Fast reconfigure synchronization hierarchy is empowered in PTP devices that enable the peer-delay mechanism to compute a peer delay for each communication bond. Network resource consumption is minimized by dividing the master selection and timing info into two different but very short messages. In the new message layout, the size of the Sync message payload is 46 B, instead of 165 B [4]. PTP<sub>v2</sub> is recently revised in 2019 and come up with a slightly modified version as PTP<sub>v2.1</sub> [45]. PTP-2019 improve the PTP-2008 optional features, and it is backward compatible with the older version some of the newly introduces features are as follows [46].

- Profile isolation

- Special ports

- Mixed multicast/unicast

- High accuracy

- Security

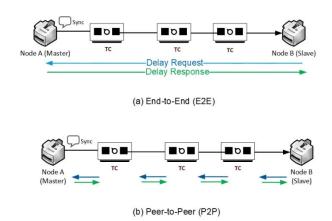

## C. DELAY MECHANISM

# 1) END-TO-END (E2E)

In this mechanism, a slave node periodically sends Delay\_Request messages to the master node and the master replies with Delay\_Request message. Path delay is estimated by using egress and ingress time stamps of the

FIGURE 5. PTP delay mechanisms.

Delay\_Request. Delay is measured for the full path from master to slave and the delay is corrected at the slave node. In Figure 5 complete delay that a sync message experience when it travels from master to slave (Node A to B) is corrected at node B.

## 2) PEER-TO-PEER (P2P)

In the case of peer-to-peer delay mechanism path delay is estimated between two neighboring PTP nodes irrespective of the type of node i.e. BC, TC OC. In general, TC stays calm in any other traffic but they actively participate in the P2P delay mechanism. Each node in the delay path estimates the delay for its preceding network link and applies correction for all pass-through event messages.

#### 3) E2E VERSUS P2P

Which delay mechanism is better? The answer to this question is not straightforward because it depends upon the network. If a network is fully PTP supported i.e. all the switches or routers are guaranteed to be PTP enabled then P2P is best otherwise E2E is a feasible choice. Figure 5 presents a visual comparison among the two mechanisms. E2E mechanism is more versatile as it can handle non-PTP switches/routers, In E2E slave measure the full distance to its master while the P2P measures the distance to the next neighbor only. This behavior becomes important in a large network where E2E could result in network bandwidth and resource wastage. P2P has another benefit that delays between master and slave is already known when network path changes as all the links measured periodically.

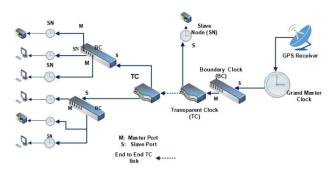

#### D. PTP NETWORK

IEEE 1588 follows master-slave architecture. It can have more than one network segment with multiple clocks. Generally, the grandmaster clock has the best oscillator with standard time and associated to an external GPS or atomic clock. Each network segment has a master clock that is mainly synchronized to the grandmaster clock. The clocks that are synchronized to the master clock are termed as slaves; they do not pass the time information to further nodes. On the

FIGURE 6. PTP clocks and their position in the network.

contrary to switches or router, master and slave clocks are end nodes in the network [47]. The worst condition of the queuing delay happens in switches or routers [48]–[50]. Figure 6 represents a complete PTP network employing all kinds of PTP clocks, their port states (Master/Slave), and the positions in the network.

#### E. PTP EMPLOYMENT TECHNIQUES

The IEEE-1588 does not provide any details about the implementation of the PTP profile. Two approaches have been accepted for the PTP over Ethernet known as PTP with software timestamps and PTP with hardware timestamps [51]. Commonly used configurations have been discussed below.

#### 1) GRANDMASTER WITH HARDWARE TIME STAMPING

With GPS grandmaster clock could be able to deliver precise nanosecond timestamp resolution and more than 30 nanoseconds accuracy [52]. The reference oscillator is employed with devoted hardware for the accurate timestamp of the received delay demand and outward sync packets [53]. In this case, 1 PPS output from the grandmaster and the slave can be likened via oscilloscope to test the synchronization accuracy.

# 2) SLAVE WITH HARDWARE TIME STAMPING

Hardware timestamps with a PTP software daemon deliver precise nanosecond timestamp resolution with devoted hardware normally in a PCIe (Peripheral Component Interconnect Express) form factor. The hardware slave got many benefits over the software slave, like a better oscillator, a 1PPS output for comparison with the master, and, devoted hardware that is robust to the latency caused by the operating system. Synchronization accuracy up to 100 nanoseconds could be achieved.

# 3) SLAVE WITH SOFTWARE TIMESTAMPING

This approach use present computer hardware along with a PTP daemon. The slave software solution is essential to recompense for the internal oscillator on the computer motherboard by software timestamping. Log file statistics are the only way to test the accuracy, due to the absence of 1PPS output. Achievable accuracy lies between  $10 \text{ to } 100\mu\text{s}$  [54].

FIGURE 7. PTP testbench setup.

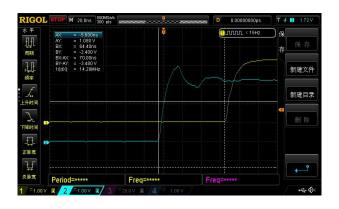

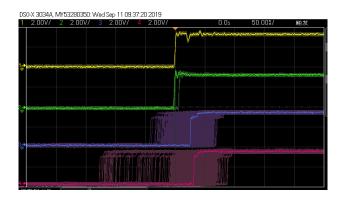

#### F. TEST BENCH

We have setup the PTP test bench as shown in Figure 7, where QULSAR QG2 gateway was configured as grandmaster and P60 chipset and M88 managed clock engine configured as a boundary clock/gateway [55].

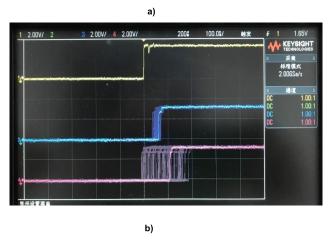

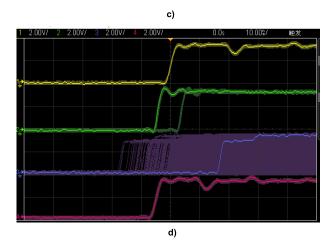

Experimentation was performed with the different configuration on the master and slave nodes, we have tested the accuracy achieved by direct connection between master and slaves and observed the effect of inserting non-PTP switch in the PTP path. The performance of M88 was also evaluated as a jitter cleaner. Figure 8 (a) depicted the synchronization drift is about 70ns when Qg2 is directly connected to the slave node at ethernet port 1. Figure 8 (b) there are two slave nodes one is directly connected to master and other is connected via a non-PTP switch, max drift is about 50ns when P60 board connected to Qg2 directly and drift of 1PPS signal is about 200ns when the master and slave are connected via a switch. So, a non-PTP switch degrades the performance.

In Figure 8 (c) there are one master (QG2) and three slave nodes (QG2, QG2, M88), results collected after running the system for about 12 hours. The results clearly present the higher drift with switch and lower drift with the M88. Figure 8(d) shows the performance of M88 as a boundary clock and jitter cleaner, yellow is the 1PPs reference signal from the master, the green is 1PPS from M88 as slave node, and the pink is 1PPS from QG2 as a slave, connected to master via M88 as a boundary cock.

Results show that it has almost the same drift as in the direct case with M88. From the test results, we conclude that a non-PTP switch lowers the PTP performance even with very accurate and expensive PTP supported equipment. M88 has a good impact on removing the jitter and can enhance the synchronization while acting as a boundary clock. All the equipment is very sensitive, and results have significant variations without any change to configurations, reasons for such variations are under observation and testing.

# IV. PTP PERFORMANCE ENHANCEMENT AND ERROR SOURCES

## A. PERFORMANCE LIMITING FACTORS

One of the main sources of time error is propagation delay asymmetry. A PTP slave approximates the prop-

FIGURE 8. a) QG2 Master directly connected to P60 slave b) Channel 1 yellow line: QG2 master reference clock, Channel 2 blue line: P60 board (Qg2→P60), Channel 3 pink line: P60 board through Switch. (Qg2→ non-PTP Switch→P60). c) Channel 1 yellow line: Qg2 master, Channel 2 green line: M88 (Qg2→M88), Channel 3 blue line: P60 board through Switch (Qg2→Switch→P60), Channel 4 pink line: another P60 board (Qg2→Switch→P60) through non-PTP Switch. d) Channel 1 yellow line: Qg2 master, Channel 2 green line: M88 as boundary clock, Channel 3 blue line: P60 board through Switch (Qg2→non-PTP Switch→P60), Channel 4 pink line: connected to another Qg2 slave (Qg2(master)->M88-> Qg2(slave).

agation delay of *Sync* requests by supposing the bidirectional delay is symmetric, this supposition though, is not usually correct. Asymmetry of the propagation delay causes an error at the physical level [56]. The propagation delay comprises of cable delay, transmit and receive latency. Moreover, this latency considerably varies amongst chip vendors because of dissimilar employment methods.

# 1) PDV (PACKET DELAY VARIATION)

One important factor that defines the superiority of the clock synchronization process is PVD. The value of the PVD represents the phase (time) difference among the master and the slave. According to [3], PDV components could be divided into some parts as discussed below.

# a: QUEUING DELAY

Queuing delay is the time spent by the transmitted message at the intermediate nodes. Estimation of the queuing delay occurred in any intermediate node is difficult to be done either in the master or slave clock as it is highly dependent upon the congestion level or the network. Queuing delay inside the switch covers the noteworthy part of the asymmetry problems, (up to milliseconds).

# b: TRANSMISSION DELAY

Is the time required by the message to travel in the medium. This delay is highly dependent upon the medium it travels. In a wired network, the cable category, its material, and length, all are involved in upsetting the transmission delay. While, in a wireless network, channel capacity, signal power, and the distance are the influencing factors.

#### c: CABLES DELAY

All the infrastructures related delays among the clocks present in the network are compensated with  $PTP_{v2}$  except the one caused by the connecting cable between the GPS antenna and grandmaster clock. Even high frequency antenna cables have high attenuation at the GPS reception frequency that puts limits on the maximum cable length. [57] proposed a solution to this issue by integrating the grandmaster clock

directly into the antenna, which eliminates the use of a coaxial antenna cable.

#### d: PROCESSING DELAY

As the transmission/reception of all the messages is on the physical layer, a small time is required to process the messages to the application layer. Though in the majority of the cases this delay is ignored as its value is very small, still, this delay might reduce the accuracy of the synchronization.

#### 2) QUANTIZATION ERROR

When dealing with analog to digital conversion it is unavoidable to encounter quantization error. Generally, the internal clock of each node yields some analog signal from the clock oscillators, these signals are used in the PTP protocol after an analog to digital conversion. The clock unit notices the signal changeovers on the gigabit media-independent interface built on its system clock to yield timestamps. Every time the PTP message passes a clock edge at the point the signaling and the sampling clock are dissimilar, it causes a non-deterministic error [58].

# 3) OSCILLATOR STABILITY

This element largely depends on the superiority of the clock itself. Clock drift is one factor that defines the quality of every clock, it is expressed in ppm (part per million). The location of the node affects the drift value, and the clocks with smaller drift are expensive. Regardless that there is a method to increase the stability of the clock with PLL (Phase Locked Loop), still there are some jitter that occurs inside the PLL itself [4].

# B. ENHANCEMENT APPROACHES IN IEEE 1588

Lots of ways have been proposed and adopted to enhance the accuracy of PTP based clock synchronization [59]. The main goal of these approaches is to decrease the PDV to the maximum possible extend. Based on the optimization level and working mechanism these enhancements mechanisms have been divided into different categories as discussed below.

# 1) BOUNDARY CLOCK OPTIMIZATION

The main issue with the boundary clock is the queuing delay, Jaspernite *et al.* [60] have suggested an idea to replace the boundary clock with a bypass clock. This bypass clock looks similar to the transparent clock, the performance gets enhanced but still not sufficient for many existing and future applications. To alleviate the exponentially accumulated timing error, [61] have advised an approach that combines the frequency compensation algorithm and the periodic offset recompense algorithm, both are optimized to diminish the synchronization error independently. They experimentally shown that the fast jitter is a leading factor that decreases the timing accuracy, and the peak to peak jitter was found to be less than one microsecond for multiple hops network.

#### 2) MODIFICATION IN IEEE 1588 MESSAGE TRANSMISSION

PTPv2 offers an improved timing accuracy with the aid of the transparent clock features and the condition of replacing the intermediate nodes with PTP supported ones. There are many proposals in the literature to resolve the PDV caused by queuing delay in the intermediate nodes without considering PTPv2 supported nodes. An approach has been proposed by Murakami *et al.* in [62] a technique that modifies the IEEE 1588 PTP transmission in a non-PTP network. Few extra PROBE messages are sent by the master clock, these messages are used as the measurement tools to estimate the queuing delay. This method encourages the offset value, but it could bring another issue, that the intermediate nodes become much busy owing to the increased packet exchange.

#### 3) FILTERING TECHNIQUE

Initially, they were developed with PTPv1 as the target to choose the minimum delay measurement from master to slave and vice versa [63]. Though this technique is still employed in the improvement of PTPv2, the main drive of the filtering in PTPv2 is not to straight alleviating the queuing delay. Hadzic et al. in [64] presented a filtering technique named as EAPF (earliest arrival packet filter) with PTP<sub>v2</sub>. The EAPF method do well in a slightly loaded network with a low probability of queuing delay, in a situation of high load it could not perform well. In [65] author recommended alternative improved filtering due to the dynamic network. The network situation is hard to forecast, this technique offered an adaptive filtering method that can change the clock recovery algorithm in the slave node rendering to the network condition. In [66] Kalman filter based a clock servo system is planned with software based PTP for WLAN.

#### 4) HARDWARE TIMESTAMPING

In PTP every message requires traveling from the application layer to the physical layer or vice versa, and this procedure needs time. According to [59] the time difference might disturb the synchronization accuracy, they have discussed that the ordinary offset measurement technique could not deliver a satisfactory result in the wireless network, offered a way to compute the offset among master and slave while bearing in mind diverse transmission speed in every link using hardware timestamping. Exel in [67] put some light on the role of the processing delay in the time synchronization. According to them, this processing delay needs to be considered in the offset calculation;  $PTP_{v1}$  does not deal with the processing delay as the main donor of inaccuracy. The examination of processing delay could lead to some beneficial results that could help to improve clock synchronization performance.

# 5) INCREASING INTERNAL CLOCK STABILITY

Most of the clock synchronization systems depends upon the internal clock either to take timestamp or to estimate the residence time. PLL has been proved to remove the likelihood of the internal clock shift, though PLL could deliver

FIGURE 9. WPTP iteration mechanism.

some errors. Therefore, another control loop is desirable, and that control loop usually is located in the slave node that is trying to synchronize. According to Du  $et\ al.$  in [68] the diversity of internal clock in the intermediate nodes would reduce the performance of  $PTP_{v2}$ , authors proposed a way to synchronize slave clock without involving the intermediate node's internal clock, using a transparent clock to measure the residence time. Presently, there are two types of control loops FLL (Frequency Locked Loop) and PLL. Zhu in [69] performed a comparison between FLL and PLL and concluded that regardless of both techniques can resolve the issue PLL shows more vigorous performance to the PDV as compare to FLL.

## **V. WIRELESS PTP**

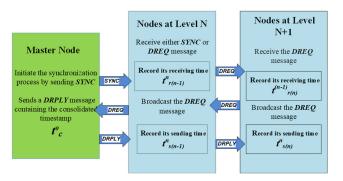

To be used in industrial measurement and control systems, the devices have to be able to synchronize wirelessly. There are many wireless technologies, the majority of them are radio-based and non-deterministic which makes them challenging for realizing the PTP. The integration of PTP with serial infrared (SIR) has been deliberated in [70]. Particularly the timestamping and encapsulation of PTP frames have been fully examined. The presented outcome shows the sub-microsecond synchronization via a wireless link. [71] advises a novel version of PTP named as wireless precision time protocol (WPTP) for multi-hop wireless networks.

The author exploits the broadcast nature of the wireless communications to overlap the synchronization procedure among adjacent levels. WPTP repeats in levels, in the first round the level-one nodes are synchronized these nodes and become masters for the next level nodes and so on as summarized in Figure 9. Only three packets are involved in the calculation and correction of clock offset, the delay computation is the same as offset, except that the node at an inferior level will send the difference of timestamps. They proposed an analytical model and the results show that the reduction in convergence time of WPTP and the number of packets to transmit does not affect the synchronization accuracy.

# A. WIRELESS PTP ISSUES

The main issue when integrating wireless techniques with PTP is the non-deterministic nature of the transmission media (air) that puts a limit on achieving high accuracy.

- 1) Another main issue is that there are no wireless integrated circuits (ICs) offered yet that are PTP responsive. Without PTP support in the wireless ICs either statistics, filtering, and a lot of computation is obligatory to resolve the determinism issue or custom-built PTP aware hardware need be developed to get sub-microsecond accuracy.

- 2) Wireless interface brings mobility that could result varying distances amongst the nodes. PTP however depends on knowing the path delay. According to the accuracy requirement and the velocity of a node, path delay measurement cycles require to be run more often.

- 3) Network topology is also important in such a network that defines the use of either PTP End to End (E2E) delay measurement or PTP Peer to Peer (P2P) delay measurement.

# VI. SUMMARY OF THE LITERATURE ON PTP BASED SYNCHRONIZATION

There have been a lot of efforts and proposals in the recent literature to evaluate and enhance the PTP performance and its employment in industrial communication. This section describes the previous work in this regard. Table 3-5 summarizes the literature work proposed to enhance the PTP and evaluate its performance in different configurations. Table 3 describes the summary of the simulation-based work, Table 4 depicts the efforts to enhance and evaluate the PTP performance with different hardware modules and commercially available devices. Table 5 encompasses the theoretical case studies and survey over PTP bases synchronization.

#### A. SOFTWARE AND HARDWARE TOOLS

OMNET++ has been often used for PTP evaluation because of its per packet discrete-event nature. Table 3 shows the different ways in which OMNET++ is employed for PTP evaluation. The work in [71] uses the Contiki Operating System and Cooja simulator for the soft implementation of wireless PTP and few other use a Linux based System-On-Chip (SoC) Platform for this purpose. The Field Programmable Gate Arrays (FPGAs), and reconfigurable devices are the best applicants to fulfill the flexibility requirements of the emergent Ethernet-based protocols and to implement substation network devices capable to chain numerous protocols [72]. These devices have hardware processing abilities to attain low switching latency and elasticity to adjust the plan to particular consumer desires, protocols updates, and composite protocols combinations. The technology presented by the reconfigurable logic is tending to the next stage of cost-efficient SoC devices [73], other PTP implementations and evaluation in literature used following (but not limited to) classes of FPGA kits/boards [74]-[77].

- Xilinx NetFPGA-1G KINTEX-7

- Xilinx FPGA KCU105

- Xilinx Zynq-7000 SoC

- Altera Cyclone III FPGA

- Development kit from Altera equipped with an EP2S60F672 3 Stratix II FPGA

| TABLE 3. Summary of the recent literature on simulation based work for PTP evaluation and deve |

|------------------------------------------------------------------------------------------------|

|------------------------------------------------------------------------------------------------|

| Category      | Reference | Aim                                                                                                                                                             | Methodology /Tools                                               | Results                                                                                                                                                       |

|---------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | [5]       | Developed a zero-overhead microsecond accuracy model for datacenters to synchronize a packet-switched optical network using PTP.                                | Simulation                                                       | Zero overhead was sustained by piggybacking time info on data packets.                                                                                        |

|               | [72]      | Aim to compare IEEE 1588 and WLAN standards to achieve a functional decision of the synchronization solution for real time applications.                        | Simulations<br>(LibPTP, OMNet++)                                 | Revealed the influence of real time traffic on the queuing delays.                                                                                            |

|               | [71]      | Proposed a wireless precision time extended version of PTPv2 for multi-hop wireless networks.                                                                   | Simulations (Contiki<br>Operating System and<br>Cooja Simulator) | Simulation results show the 50% performance improvement in convergence time without compromising the accuracy.                                                |

| Simulation    | [87]      | Synch feature of TSN was used to measure the size of frame and Development of guard band reduction mechanism.                                                   | Simulations OMNeT++                                              | The experimental results showed that with smaller guard<br>band, network delay and average latency has been<br>reduced.                                       |

| based efforts | [88]      | Introduce LibPTP, an OMNeT+++based simulation framework for PTP networks. LibPTP eases structure PTP networks using Ordinary, Boundary, and Transparent clocks. | Simulations (OMNet++))                                           | Simulations work has confirmed that both LibPLN and LibPTP offer a method to get in the domains of clock noise and time synchronization.                      |

|               | [89]      | Presents innovative methodology using Kalman filter with outlier detection and elimination followed by a linear quadratic regulator (LQR).                      | Monte Carlo simulations                                          | The simulation outcomes authorize that the suggested solution and the iWLS technique largely provide better performances than using a single input reference. |

|               | [90]      | Familiarizes a state variable clock model that use realistic parameters obtained from experimental measurements of Allan variance plots.                        | Modeling & simulations (State-variable model)                    | Results revealed various fascinating aspects in the performance of controlled clocks and delivered some design criteria.                                      |

|               | [91]      | Proposed a method that uses a dual slave clocks in a slave to measure the link propagation delay, clock skew and offset.                                        | Simulations                                                      | By precisely deriving the propagation delay, clock skew<br>and offset, the suggested approach can decrease the<br>deviation from the master clock.            |

There are numerous professional PTP based synchronization solutions a few worth mentioning are summarized in Table 6. The main vendors include Texas Instruments, National Instruments, Qulsar, Microsemi, Xilinx SOC. Their commercial products with main features and applications are briefly discussed, for detailed description reader can check the relevant reference.

# VII. SYNCHRONIZATION REQUIREMENTS AND ROLE OF PTP IN THE AREA OF INDUSTRIAL APPLICATIONS

# A. PTP FOR INDUSTRIAL IOT

The smart factory of Industry 4.0 envisages an industrial ecosystem as a cyber-physical body. Wireless communication has to accomplish rigorous necessities of industrial applications regarding extremely-low latency and very high consistency [13]. As compared to other communication systems industrial networks, usually feats deterministic data transmission/ reception (Tx/Rx) to function in real-time [78], [79]. The data Tx/Rx timings and the node locations within such networks are pre-planned [80]. To preserve a reliable data interchange among the contributing nodes, highly precise clock synchronization among them is of supreme status [19]. Clock synchronization approaches based on NTP and PTP are broadly used to guarantee precise clock synchronization between the contributing nodes [81], [82]. PTP offers better accuracy as compared to other protocols [83], the inferences of PTP have been proved in numerous current research works, with the help of well-synchronized nodes, pre-planned data Tx/Rx timings can be systematized in an industrial network for competent and real-time distribution of the control signals.

Highly precise clock synchronization is crucial for the recognition of emerging IoT real-time applications. The absence of the clocks synchronization amongst the nodes in the industrial IoT can damage system performance and can result in safety compromises. [84] offers a reliable framework for the IoT established within the realm of EPOS (Embedded Parallel Operating System). EPOS timing protocol brings clock time across a wireless sensor network in conformance with the IEEE 1588 standard. EPOS PTP is capable to retain a PAN synchronized of sub-millisecond accuracy. PTP presents tools to measure and take into account the delay asymmetry problem but obliges PTP support at all nodes that increase the system cost by many folds. [85] consider partial on-path PTP support considering the PTPv2, in which a subset of the nodes is PTP unaware they suggest a probing-based mechanism to measure the asymmetry and increase the synchronization performance in a cost-effective way.

Many computing devices with adequate resources can act as edge devices for IoT. Swarm Box is one of the examples which are recommended as a hardware platform in the Terra Swarm project. It functions as a smart gateway for devices that connect to the Internet over the Swarm Box [86]. It has dual Ethernet ports one for the local network is also furnished with hardware support for PTP, permitting nanosecond-scale clock synchronization. In [19] an enhanced PTP has been proposed to enable accurate clock synchronization for industrial wireless sensor network organized for acute control and automation applications.

They showed that including clock drift factor, the precision of clock offset approximation can be meaningfully enhanced. The wireless technologies adopted in industrial IoT scenarios are typically installed at the sensing layer and networking layer to incorporate with wired technologies at higher layers. IEEE 802.11 has become a key communication tool to inaugurate the IoT in industries. IEEE 802.11 Wireless Local Area Networks (WLANs) delivers high throughput and area coverage [112]. This enables flexible communication system

TABLE 4. Summary of the recent literature on hardware based evaluations and enhancement of PTP.

| Category    | Reference | Aim                                                                                                             | Methodology /Tools                           | Results                                                                                                      |

|-------------|-----------|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------|

|             | [76]      | To extend the clock synchronization to the nanoseconds                                                          | Implementation based on                      | Presented results prove that the realized timing system                                                      |

|             |           | range via FPGA implementation of IEEE 1588, removing                                                            | Xilinx's Kintex-7                            | is a cost-efficient mechanism to enhance the time                                                            |

|             |           | the typical accuracy confined by the Ethernet based Local                                                       | XC7K160T.                                    | accuracy up to $\pm 4$ ns.                                                                                   |

|             | [92]      | Area Network.  Commercially available PTP devices from variety of                                               | Commercially available                       | The presented methodology offers a set of tests that are                                                     |

|             | [92]      | manufacturers were compared and evaluated with respect                                                          | devices                                      | useful for system designers and researchers to evaluate                                                      |

|             |           | to performance.                                                                                                 | devices                                      | timing element.                                                                                              |

|             | [77]      | Time synchronization in mixed network is highlighted                                                            | NIOS II development kit                      | Results show the viability of the suggested design;                                                          |

|             |           | along with a description of transparent Time Gateway to                                                         | from Altera equipped with                    | certain developments may be required to contest the                                                          |

|             |           | enable the coexistence of NTP and PTP devices.                                                                  | an EP2S60F672 3 Stratix                      | time synchronization accuracy demand.                                                                        |

|             | 5.403     |                                                                                                                 | II FPGA                                      |                                                                                                              |

|             | [49]      | To examine the influence of latency and high bandwidth                                                          | Analog development                           | PTP base sync system requires expensive replacement of existing infrastructure. PTP enabled switches provide |

|             |           | traffic on PTP clock synchronization. Explore the impression of Transparent Clock, possessions of its           | boards running IXXAT<br>BF518 EZ-Kit 1588    | high accuracy only in small scale networks without                                                           |

|             |           | existence and absence.                                                                                          | software stack                               | congestion owing to absence of the traffic prioritization.                                                   |

|             |           |                                                                                                                 | boxare black                                 | tengenen e ming te desente et me trame priemamen.                                                            |

|             | [4]       | Discussed the issues with PTPV2 time synchronization in                                                         | Prototype a Gigabit                          | Results recommend that the realized transparent clock                                                        |

|             | L-3       | distributed computing and control systems with a                                                                | Ethernet switch fabricated                   | has significant impact in reaching sub microsecond                                                           |

| Hardware    |           | practical employment approach.                                                                                  | into a 21-mm2 silicon                        | accuracy. Asymmetry issues mainly comprises of                                                               |

| based       |           |                                                                                                                 | chip                                         | queuing delay in the switch.                                                                                 |

| Evaluations | [93]      | A full-hardware employment of a combined redundancy                                                             | FPGA Altera cyclone III                      | Consequences authorize the concept is cost effective                                                         |

|             |           | IEC 62439-3 with IEEE 1588 clock synchronization has                                                            |                                              | and can be used for new devices and retrofit.                                                                |

|             | [11]      | been proposed. Establishes the structural design of time synchronization                                        | Linux operating system,                      | A time synchronization solution was presented with                                                           |

|             | [11]      | network of experimental advanced superconducting                                                                | PXI-6683 cards                               | software and hardware of TSN system                                                                          |

|             |           | tokamak (EAST) poloidal field (PF) power supply control                                                         | 17X1-0005 cards                              | software and nardware of 151v system                                                                         |

|             |           | system                                                                                                          |                                              |                                                                                                              |

|             | [40]      | Developed an MTCA.4 module that can be used as a                                                                | NI PXI-6683H.                                | Firmware modification enhances the maximum                                                                   |

|             |           | timing receiver giving reference clocks in the MTCA.4                                                           | Developed PTM-1588                           | timestamping rate as it provides a dedicated DMA                                                             |

|             |           | chassis, able to generate the Pulse Per Second (PPS) signal.                                                    | timing module                                | module also expands the timestamping resolution via improving the internal clock frequency.                  |

|             | [75]      | NetFPGA based PTP module implementation to support                                                              | NetFPGA 1G boards.                           | Proposed two architectures to apprehend a PTP switch.                                                        |

|             | [,5]      | time-synchronized SDN, proposed a Low-cost solution                                                             | ricul i di i i di | representative distinctions to appreciate a rare switching                                                   |

|             |           | via PTP unaware switches with appended PTP chip.                                                                |                                              |                                                                                                              |

|             | [94]      | PTP based Timing synchronization system (TSS) module                                                            | NI PXI-6683 series                           | A new TSS has been developed by using PXI devices.                                                           |

|             |           | has been established with the PXI bus standard and FPGA                                                         | synchronization boards                       |                                                                                                              |

|             | [53]      | devices. Main focus on the modifications of the TSS,<br>Studied the IEEE1588 clock synchronization and the best | DP83640                                      | Revealed the accuracy of timestamp is the most                                                               |

|             | [55]      | master clock algorithm                                                                                          | DI 03040                                     | important factor affecting the PTP accuracy, suggested                                                       |

|             |           |                                                                                                                 |                                              | a timestamp solution based on DP83640.                                                                       |

|             | [74]      | Design of a hybrid slave clock with the transparent clock                                                       | Xilinx KCU 105                               | Demonstrations shows that the three-sigma time                                                               |

|             |           | (TC) functionality defined in the IEEE 1588 precision                                                           | evaluation board                             | uncertainty of the TC is 15.6 ns and that of the slave is                                                    |

|             |           | time protocol.                                                                                                  |                                              | 149 ns with an average transient time of 13.5 s, sustaining the standard.                                    |

|             | [95]      | REVERSEPTP, a clock synchronization structure for                                                               | Evaluated performance in                     | REVERSEPTP delivers the accuracy just like                                                                   |

|             | [>+]      | software-defined networks was introduced.                                                                       | a test bed with 34 nodes                     | conventional synchronization protocols.                                                                      |

|             |           | REVERSEPTP is built on the Precision Time Protocol                                                              |                                              |                                                                                                              |

|             | 50.63     | with theoretically reversed approach.                                                                           |                                              |                                                                                                              |

|             | [96]      | Major contribution is a new TC architecture for a FPGA-                                                         | SP605 boards with two AVNET FMC boards.      | The planned TC architecture is a practicable solution for                                                    |

|             | [73]      | based network device.  Discovers the employment of PTP on new Xilinx Zynq-                                      | Xilinx Zynq-7000                             | emerging Ethernet Switches with TC competences.  Paper concluded from the analysis that the only way to      |

|             | [,2]      | 7000. Winning advantage from the elasticity of the SoC                                                          | Aimia Zynq-7000                              | attain a precise PPS output on new Xilinx Zynq devices                                                       |

|             |           | all programmable devices.                                                                                       |                                              | is to improve in the PL section.                                                                             |

|             | [97]      | PTP Protocol for clock correction for synchronizing the                                                         | Dante devices and two                        | Functions of Zeroconf and the mDNS, the installation                                                         |

|             |           | sound of all devices with Zero Configuration Networking.                                                        | TAS3204EVM digital                           | efficiency is very high.                                                                                     |

|             |           |                                                                                                                 |                                              |                                                                                                              |

designs and the emergence of new amenities such as device localization on the factory floor. There has not been abundant support for synchronized clocks for IoT designs by IEEE 802.11. PTP over WLAN has been the chosen way to establish synchronization among the nodes. Subsection discusses the PTP employment in WLAN.

#### B. PTP PROTOCOL FOR IEEE 802.11 WLAN

The evolution of network-based wireless communication has offered lots of benefits including cost reduction, flexible network topologies, and mobility. IEEE 802.11 wireless local area network (WLAN) is one of the examples which spreads its usage in the offices and industry [8]. Though the accessibility of synchronized clocks to harmonize and

control message is not a default property of WLAN. The infrastructure mode of WLAN, that permits communication among the stations via a centralized access point (AP), is perfectly suitable for practice in centralized designs engaged in applications like smart grids and the industrial automation. Hence, the time-based necessities of the application are important to be considered. [113] states that the different kinds of industrial applications should be reinforced by industrial communication, such as the ones mentioned in Table 7 along with their generic real-time classes and particular temporal requirements as defined in [114], [115]. NTP and IEEE 1588 PTP are two generally recognized CS protocols intended for wired media and also employed for wireless synchronization [51]. The working mechanism

TABLE 5. Summary of the recent literature on theoretical case studies on PTP.

| Category                    | Reference | Aim                                                                                                                                                       | Results                                                                                                                                                                                            |

|-----------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                             | [98]      | Recognition and prevention mechanisms against the recognized PTP delay attack.                                                                            | The results illustrate the practicality of the algorithms in detecting the delay attacks directing PTP, and protecting the system functionality.                                                   |

|                             | [20]      | Investigation of the strategy and the placement strategies for the time                                                                                   | Paper has focused on the tools, structural design, and protocols that                                                                                                                              |

|                             |           | synchronization over a present heterogeneous network.                                                                                                     | are practically feasible on existing installations.                                                                                                                                                |

|                             | [99]      | Explored the PTP for Time Synchronization in the Electric Power Industry.                                                                                 | To meet the synchronization requirements of the most applications, hardware solutions are essential.                                                                                               |

|                             | [100]     | Put light on the usage of the automatic detection of the synchronization path quality for system configuration.                                           | It could be beneficial to have the values for the standard deviations and the division of the inaccuracy contributors into static and dynamic inaccuracy in a new or extended Time Inaccuracy TLV. |

|                             | [101]     | Offers an update on a joint project employing commercial equipment to send national timing signals over a telecommunication network in the United States. | Imagining a partial backup to GPS timing, where GPS can calibrate the asymmetry, and PTP is accessible when GPS is absent, this OTN system would support better than 100 ns time transfer.         |

|                             | [102]     | On the use of PTP for the media production industry. It reviews the efforts on PTP aware vs. non-aware networks perform under load.                       | Closing with the impression of design considerations, network architecture constraints and device necessities for an effective all-IP synchronized media production facility.                      |

|                             | [41]      | This paper explores the issues related to the requirements for synchronization and the solution provided by the IEEE standard.                            | PTP is easy to implement with very little administrative effort and can tolerate network and clock failure with built-in fault-tolerant mechanisms                                                 |

| Survey and                  | [103]     | Discussed time synchronization algorithm for CoAP-based home automation system networks.                                                                  | The anticipated mechanism reasonably reduces network overhead as it only uses CoAP in its place of the additional standards for time synchronization protocols.                                    |

| theoretical<br>case studies | [6]       | The chief element of the effort is the use of GNSS-based time provider in distributed manner.                                                             | GNSS-based distributed architecture is proposed along with emerging applications that benefit from such methods.                                                                                   |

|                             | [44]      | A mathematical analysis with respect to hardware limitations of the TC measurement techniques has been conducted.                                         | Results found that the std. dev. of the measurement's error is up to 5ns. Based on the results a new measurement setup that needs cheap hardware and upholds alike precision to other techniques.  |

|                             | [66]      | Kalman filter based a clock servo system is planned with software based PTP for WLAN.                                                                     | Kalman filter established delay approximation procedure is designed<br>and a reformed PI controller clock servo system is planned                                                                  |

|                             | [47]      | How network with a common source of time can act as all type of IEEE 1588 clocks.                                                                         | Equivalence of the BC and peer-to-peer TC could be deliberated as a method of observing at synchronization transport in IEEE 1588 network.                                                         |

|                             | [104]     | Proposed a technique to evaluate the enactment of a timing system based on distributed GPS.                                                               | Experiments indicate either system is chosen, excellent devices, with suitable installation are vital to gratify the $\pm 1~\mu s$ accuracy necessities.                                           |